(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6212133号

(P6212133)

(45) 発行日 平成29年10月11日(2017.10.11)

(24) 登録日 平成29年9月22日(2017.9.22)

(51) Int.Cl.

G06F 12/08 (2016.01)

F 1

G06F 12/08 507J

G06F 12/08 511E

G06F 12/08 579

請求項の数 24 (全 25 頁)

(21) 出願番号 特願2015-549790 (P2015-549790)

(86) (22) 出願日 平成25年12月20日 (2013.12.20)

(65) 公表番号 特表2016-505971 (P2016-505971A)

(43) 公表日 平成28年2月25日 (2016.2.25)

(86) 國際出願番号 PCT/US2013/077020

(87) 國際公開番号 WO2014/100632

(87) 國際公開日 平成26年6月26日 (2014.6.26)

審査請求日 平成28年5月11日 (2016.5.11)

(31) 優先権主張番号 13/721,317

(32) 優先日 平成24年12月20日 (2012.12.20)

(33) 優先権主張国 米国(US)

早期審査対象出願

前置審査

(73) 特許権者 507364838

クアルコム、インコーポレイテッド

アメリカ合衆国 カリフォルニア 921

21 サンディエゴ モアハウス ドラ

イブ 5775

(74) 代理人 100108453

弁理士 村山 靖彦

(74) 代理人 100163522

弁理士 黒田 晋平

(72) 発明者 ピーター・ジー・サッソーネ

アメリカ合衆国・カリフォルニア・921

21・サン・ディエゴ・モアハウス・ドラ

イブ・5775

最終頁に続く

(54) 【発明の名称】マルチビットウェイ予測マスクを有する命令キャッシュ

## (57) 【特許請求の範囲】

## 【請求項1】

データアレイを含む命令キャッシュであって、前記データアレイは複数のラインドライバを含み、前記複数のラインドライバは複数のウェイにそれぞれ対応する、データアレイと、

第1の予測マスク値に基づいて、マルチビットウェイ予測マスクの複数のビットを選択的に設定するように構成された制御ロジックであって、前記制御ロジックが、前記命令キャッシュに関連付けられ、前記予測マスク値の各ビットの値が、前記複数のウェイのうちの対応するウェイが有効にされるべきかどうかを示す、制御ロジックとを備え、

前記データアレイのラインドライバのうちの少なくとも1つが、前記マルチビットウェイ予測マスクに基づいて有効にされ、

前記複数のウェイのキャッシュラインのそれぞれが、対応する第2の予測マスク値を有し、前記制御ロジックが、アクセスされる前記キャッシュラインに対応する前記第2の予測マスク値を第1の前記予測マスク値に設定するようにさらに構成される、装置。

## 【請求項2】

前記予測マスク値の特定のビットが、前記特定のビットに対応する特定のキャッシュラインの内容が前記命令キャッシュから除去されるまで設定されたままである、請求項1に記載の装置。

## 【請求項3】

10

20

前記予測マスク値が電源投入時に初期値に初期化される、請求項1に記載の装置。

**【請求項 4】**

前記予測マスク値の各ビットがゼロ値に設定される、請求項3に記載の装置。

**【請求項 5】**

前記予測マスク値が特定の値に周期的に設定される、請求項1に記載の装置。

**【請求項 6】**

前記予測マスク値が、時間期間の満了後、またはいくつかのキャッシュアクセス動作後に前記初期値に設定される、請求項3に記載の装置。

**【請求項 7】**

ウェイ選択信号に応じて前記複数のラインドライバの少なくとも1つによって提供されるデータを選択するように構成されたマルチプレクサをさらに備える、請求項1に記載の装置。 10

**【請求項 8】**

前記複数のラインドライバが、複数のデータラインに結合され、前記複数のラインドライバの各々が、前記マルチビットウェイ予測マスクの異なるビットによって選択的に有効にされる、請求項1に記載の装置。

**【請求項 9】**

前記予測マスク値が、タグアレイ、レジスタ、または前記命令キャッシュのキャッシュラインに記憶される、請求項1に記載の装置。

**【請求項 10】**

前記データアレイが、セットアソシティプ命令キャッシュデータアレイを備える、請求項1に記載の装置。 20

**【請求項 11】**

キャッシュにアクセスする方法であって、

第1の予測マスク値に基づいて、マルチビットウェイ予測マスクの複数のビットを選択的に設定するステップであって、前記マルチビットウェイ予測マスクが、複数のラインドライバを有するデータアレイを含む命令キャッシュに関連付けられ、前記複数のラインドライバは複数のウェイにそれぞれ対応し、前記予測マスク値の各ビットの値が、前記複数のウェイのうちの対応するウェイが有効にされるべきかどうかを示す、ステップを含み、

前記複数のラインドライバのうちの少なくとも1つが、前記マルチビットウェイ予測マスクに基づいて有効にされ、 30

前記複数のウェイのキャッシュラインのそれぞれが、対応する第2の予測マスク値を有し、アクセスされる前記キャッシュラインに対応する前記第2の予測マスク値が、前記第1の予測マスク値に設定される、方法。

**【請求項 12】**

前記マルチビットウェイ予測マスクの適用が予測外れの結果となった後に、前記予測マスク値を更新するステップをさらに含み、前記予測マスク値が、前記予測外れ後に駆動された特定のウェイを識別するように更新される、請求項11に記載の方法。

**【請求項 13】**

前記予測マスク値が、キャッシュラインの一部として前記データアレイに記憶される、請求項11に記載の方法。 40

**【請求項 14】**

前記マルチビットウェイ予測マスクを前記データアレイのキャッシュラインに対応する前記予測マスク値に設定するステップをさらに含む、請求項11に記載の方法。

**【請求項 15】**

前記キャッシュラインがアクセスされた後に後続のキャッシュラインを判断するステップと、

前記後続のキャッシュラインに基づいて前記予測マスク値のビットを設定するステップと

をさらに含み、前記ビットが前記後続のキャッシュラインに対応する、請求項14に記載の 50

方法。

**【請求項 1 6】**

前記キャッシュラインがフェッチされた後に、前記予測マスク値を有する前記マルチビットウェイ予測マスクを前記ラインドライバに提供するステップをさらに含む、請求項14に記載の方法。

**【請求項 1 7】**

前記マルチビットウェイ予測マスクを提供するステップと同時に、タグルックアップ動作を実行するステップをさらに含む、請求項16に記載の方法。

**【請求項 1 8】**

前記データアレイの特定のキャッシュラインの内容が置換されているかどうかを判断するステップをさらに含む、請求項11に記載の方法。 10

**【請求項 1 9】**

前記特定のキャッシュラインの前記内容が前記キャッシュラインの前記内容を含むとき、前記予測マスク値を初期値に設定するステップをさらに含む、請求項18に記載の方法。

**【請求項 2 0】**

前記特定のキャッシュラインが前記予測マスク値のアサートされたビットに対応するとき、前記予測マスク値の前記アサートされたビットをディアサートするステップをさらに含む、請求項18に記載の方法。

**【請求項 2 1】**

第1の予測マスク値に基づいて、マルチビットウェイ予測マスクの複数のビットを選択的に設定するための手段であって、前記マルチビットウェイ予測マスクが、複数のラインドライバを有するデータアレイを含む命令キャッシュに関連付けられ、前記複数のラインドライバは複数のウェイにそれぞれ対応し、前記予測マスク値の各ビットの値が、前記複数のウェイのうちの対応するウェイが有効にされるべきかどうかを示す、手段と、 20

前記マルチビットウェイ予測マスクに基づいて前記複数のラインドライバのうちの少なくとも1つを有効にするための手段とを備え、

前記複数のウェイのキャッシュラインのそれぞれが、対応する第2の予測マスク値を有し、アクセスされる前記キャッシュラインに対応する前記第2の予測マスク値が、第1の前記予測マスク値に設定される、装置。 30

**【請求項 2 2】**

前記複数のラインドライバのうちの前記少なくとも1つを有効にした後に駆動された複数のウェイから特定のウェイを選択するための手段と、

前記特定のウェイの指示を出力するための手段と、

前記特定のウェイから読み出されたデータを出力するための手段とをさらに備える、請求項21に記載の装置。

**【請求項 2 3】**

コンピュータ可読記録媒体であって、プロセッサによって実行されたとき、前記プロセッサに、

第1の予測マスク値に従ってマルチビットウェイ予測マスクの複数のビットを選択的に設定することであって、前記マルチビットウェイ予測マスクが、複数のラインドライバを有するデータアレイを含む命令キャッシュに関連付けられ、前記複数のラインドライバは複数のウェイにそれぞれ対応し、前記予測マスク値の各ビットの値が、前記複数のウェイのうちの対応するウェイが有効にされるべきかどうかを示す、設定することとを行わせる命令を含み、 40

前記複数のラインドライバのうちのうのうちの少なくとも1つが、前記マルチビットウェイ予測マスクに基づいて有効にされ、

前記複数のウェイのキャッシュラインのそれぞれが、対応する第2の予測マスク値を有し、アクセスされる前記キャッシュラインに対応する前記第2の予測マスク値が、第1の前記予測マスク値に設定される、コンピュータ可読記録媒体。 50

**【請求項 24】**

前記プロセッサによって実行されたとき、前記プロセッサに、

前記予測マスク値を受信させ、

前記マルチビットウェイ予測マスクの対応するビットに基づいて、前記複数のラインド

ライバのそれぞれを選択的に有効にさせる

命令をさらに含む、請求項23に記載のコンピュータ可読記録媒体。

**【発明の詳細な説明】****【技術分野】****【0001】**

本開示は、全体的に、命令キャッシュメモリシステムを対象とする。

10

**【背景技術】****【0002】**

技術の進歩は、より小さく、より強力なコンピューティングデバイスをもたらした。例えば、現在、小型、軽量で、かつユーザによって容易に運ばれる、携帯型ワイヤレス電話、携帯情報端末(PDA: personal digital assistant)、およびページングデバイスのような、ワイヤレスコンピューティングデバイスを含む様々な携帯型パーソナルコンピューティングデバイスが存在する。より具体的には、セルラ電話およびインターネットプロトコル(IP)電話のような携帯型ワイヤレス電話は、ワイヤレスネットワークを介して音声およびデータパケットを通信することができる。さらに、多くのそのようなワイヤレス電話は、その中に組み込まれた他のタイプのデバイスを含む。例えば、ワイヤレス電話はまた、デジタルスチルカメラ、デジタルビデオカメラ、デジタルレコーダ、およびオーディオファイルプレーヤを含むことができる。また、そのようなワイヤレス電話は、インターネットにアクセスするために使用可能なウェブブラウザアプリケーションのようなソフトウェアアプリケーションを含む実行可能命令を処理することができる。そのように、これらのワイヤレス電話は、かなりの計算能力を有することができる。

20

**【0003】**

そのような計算能力は、最近または頻繁に実行されたプログラム命令を(キャッシュラインに)記憶するように構成された命令キャッシュ(icache)を含むプロセッサによって強化され得る。命令キャッシュに記憶された命令は、メインメモリからアクセスされる命令よりも迅速にプロセッサによってアクセスされ得る。命令キャッシュは、複数のウェイ(way)を含み、これらのウェイの各々は、命令キャッシュの1つまたは複数のキャッシュライン(例えば、記憶位置)に対応するドライバを含む。命令キャッシュに記憶された特定の命令にアクセスするために、すべてのドライバがマルチプレクサへのすべてのウェイを(複数のデータラインを介して)駆動するように有効に(例えば活性化)されてもよく、所望のウェイがマルチプレクサによって選択され得る。しかしながら、各命令キャッシュアクセスのためのすべてのウェイを駆動することは、単一のウェイのみが最終的に選択されるとしても、各ウェイを駆動するための電力を消費する。

30

**【0004】**

電力消費を低減するために、駆動されるべき「次のウェイ(next way)」と、その結果実行され得る次のキャッシュライン(例えば、命令)とを予測(例えば、識別)するために、ウェイ予測技術が使用される。「次のウェイ」(すなわち、実行されるべき次の命令の位置)を予測することによって、単一のウェイのみが駆動される必要がある。しかしながら、以前のウェイ予測技術は、頻繁な予測外れ(例えば、誤ったウェイを予測する)の影響を受けやすく、これは、予測外れを修正し、正しい次のウェイにアクセスするために、プロセッサが受ける性能損失および電力の不利益をもたらす。

40

**【0005】**

例えば、第1の技術は、各キャッシュライン(すなわち、単一の「次のウェイ」)に関する最後の(前の)「次のウェイ」を記憶する。単一の「次のウェイ」に基づいて、命令キャッシュは、単一の「次のウェイ」に対応する単一のドライバを有効にする。正しいウェイが駆動されない(すなわち、マルチプレクサに提供されない)とき、予測外れが生じ、(完

50

了したタグルックアップ動作または制御ロジックから提供される信号に基づいて)正しいウェイを駆動する命令キャッシュデータアレイへの第2のアクセスが実行される。第1の技術を使用するとき、所与のプログラム(例えば、複数の命令)の予測性は、不規則である可能性があるので、正しい「次のウェイ」を予測する精度には問題がある。したがって、キャッシュラインに関する最後の「次のウェイ」は、必ずしも良い予測因子(predictor)ではなく、頻繁な予測外れが生じる。

#### 【0006】

第2の技術は、ウェイ予測が正しいウェイを選択する(すなわち、識別する)ことになりそうであるかどうかを決定するために、ウェイ予測に信頼値を割り当てる。単一のウェイ予測に関する信頼値が十分に高くない場合、すべてのドライバが有効にされる。第3の技術は、予測された「次のウェイ」を、分岐タイプ命令が識別されるときに使用される分岐ターゲットバッファ(例えば、トレースキャッシュ)に記憶する。記憶され予測された「次のウェイ」は、高い正解率を有する可能性があるが、分岐は、非常に頻繁にはされない可能性があり、したがって、第3の技術は、現在の命令の実行後に分岐がある状況でのみ有用である。

10

#### 【発明の概要】

#### 【課題を解決するための手段】

#### 【0007】

フェッチされた(および実行された)最後のキャッシュラインに対応するマルチビットウェイ予測マスク(例えば、予測マスク値)を利用する命令キャッシュ(icache)のためのウェイ予測技術が開示される。マルチビットウェイ予測マスクは、フェッチされた最後のキャッシュラインに関して「次のウェイ」予測を提供することができる。マルチビットウェイ予測マスクは、nビットベクトルを含むことができ、各ビットは、命令キャッシュの1つのウェイに対応する。例えば、命令キャッシュが4つのウェイを含むとき、マルチビットウェイ予測マスクは、4ビット値を含むことができる。対応するウェイの各々は、マルチビットウェイ予測マスクに基づいて有効または無効にされるドライバ(例えば、ラインドライバ)を含むことができる。対応するキャッシュ位置に各々関連付けられたマルチビットウェイ予測マスク値は、命令キャッシュのキャッシュラインと一対一の関連を有する任意の構造に記憶され得る。例えば、特定のキャッシュラインのマルチビットウェイ予測マスクは、タグアレイ内に、キャッシュラインに対応するレジスタ内に、または、直近にフェッチされたキャッシュラインの一部として(例えば、その最後に)記憶され得る。

20

#### 【0008】

特定の実施形態では、装置は、予測マスク値に基づいて、マルチビットウェイ予測マスクのビットを選択的に設定するように構成された制御ロジックを含む。制御ロジックは、データアレイを含む命令キャッシュに関連付けられる。データアレイのラインドライバのサブセットは、マルチビットウェイ予測マスクに応じて有効にされる。ラインドライバのサブセットは、多重(multiple)ラインドライバを含む。

30

#### 【0009】

別の特定の実施形態では、方法は、予測マスク値に基づいて、マルチビットウェイ予測マスクのビットを選択的に設定するステップを含む。マルチビットウェイ予測マスクは、複数のラインドライバを有するデータアレイを含む命令キャッシュに関連付けられる。データアレイのラインドライバのサブセットは、マルチビットウェイ予測マスクに応じて有効にされる。ラインドライバのサブセットは、多重ラインドライバを含む。

40

#### 【0010】

さらなる特定の実施形態では、装置は、予測マスク値に基づいて、マルチビットウェイ予測マスクのビットを選択的に設定するための手段を含む。マルチビットウェイ予測マスクは、データアレイを含む命令キャッシュに関連付けられる。装置は、マルチビットウェイ予測マスクをデータアレイの複数のラインドライバに提供するための手段も含む。複数のラインドライバの多重ラインドライバは、マルチビットウェイ予測マスクに応じて有効にされる。

50

**【0011】**

別の特定の実施形態では、非一時的なコンピュータ可読媒体は、プロセッサによって実行されたとき、プロセッサに、予測マスク値に従ってマルチビットウェイ予測マスクのビットを選択的に設定させる命令を含む。マルチビットウェイ予測マスクは、データアレイを含む命令キャッシュに関連付けられる。データアレイの多重ラインドライバは、マルチビットウェイ予測マスクに応じて有効にされる。

**【0012】**

開示された実施形態によって提供される1つの特定の利点は、電力消費を低減し、高い予測精度を有し、以前のウェイ予測技術の欠点を克服するウェイ予測技術である。ウェイ予測技術は、電力効率とプロセッサ性能の両方に影響を与える予測外れを低減または回避する。命令キャッシュに関する予測外れの発生率は、以前のウェイ予測技術と比較して大きく低減され得る(例えば、1%未満)。

10

**【0013】**

本開示の他の様子、利点、および特徴は、以下のセクション、図面の簡単な説明、詳細な説明、および特許請求の範囲を含む、本出願の検討後に明らかになるであろう。

**【図面の簡単な説明】****【0014】**

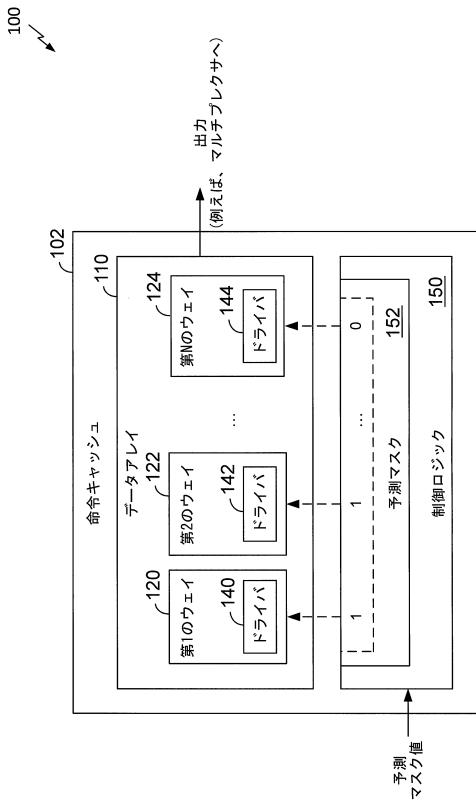

**【図1】**予測マスクを利用する命令キャッシュを含むプロセッサシステムの第1の例示的実施形態のブロック図である。

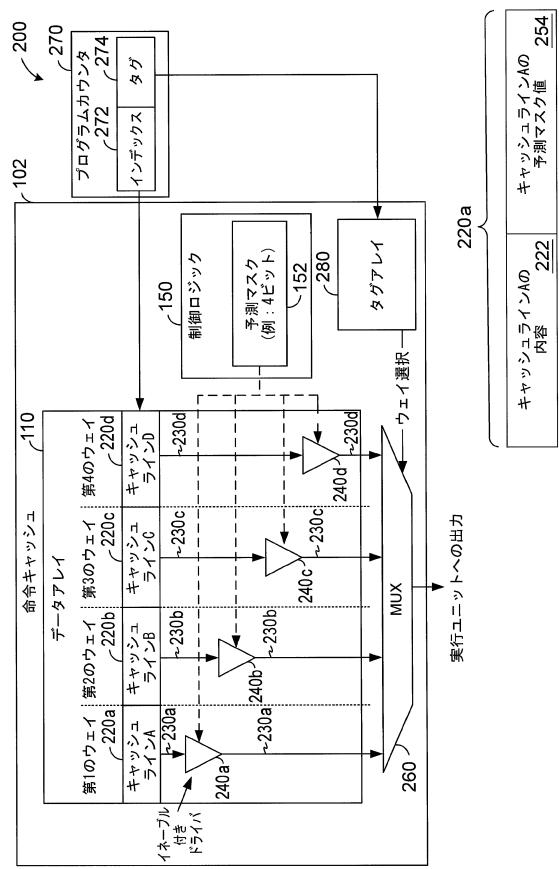

**【図2】**予測マスクを利用する命令キャッシュを含むプロセッサシステムの第2の例示的実施形態のブロック図である。

20

**【図3】**ウェイ予測を実行する方法の第1の例示的実施形態のフロー図である。

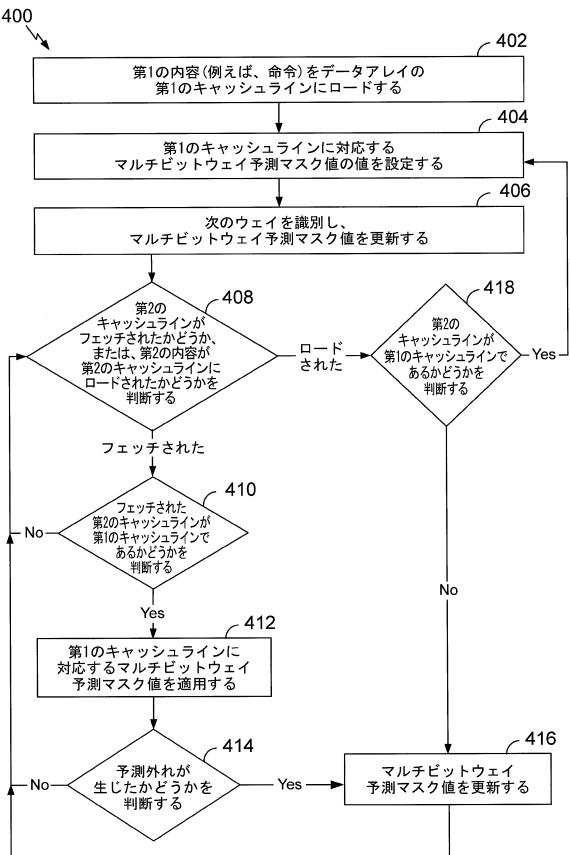

**【図4】**ウェイ予測を実行する方法の第2の例示的実施形態のフロー図である。

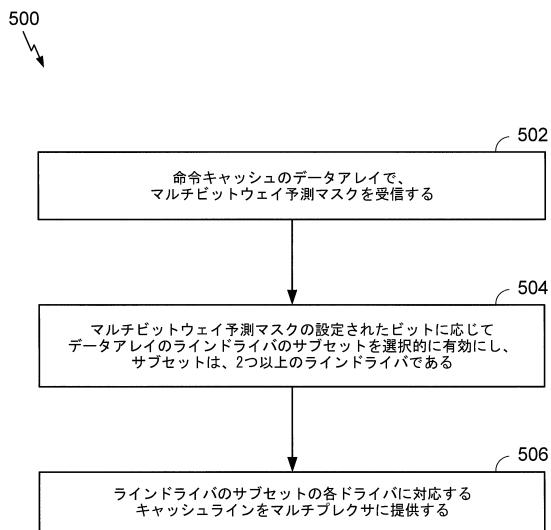

**【図5】**ウェイ予測を実行する方法の第3の例示的実施形態のフロー図である。

**【図6】**ウェイ予測を実行する命令キャッシュメモリシステムを含むワイヤレス通信デバイスの特定の実施形態のブロック図である。

**【発明を実施するための形態】****【0015】**

図1は、命令キャッシュ102(例えば、icache)を含むプロセッサシステム100の第1の特定の例示的実施形態を示す。命令キャッシュ102は、最近または頻繁に実行されたプログラム命令を(キャッシュラインに)記憶するように構成され得る。命令キャッシュ102に記憶された命令は、メインメモリ(図示せず)のような別の位置からアクセスされる命令よりも迅速にアクセスされ得る。特定の実施形態では、命令キャッシュ102は、セットアソシティブキャッシュである。命令キャッシュ102は、データアレイ110および制御ロジック150を含む。

30

**【0016】**

データアレイ110は、各々が対応するラインドライバ140～144を含む複数のウェイ120～124を含むことができる。各ラインドライバ140～144は、データアレイ110の複数のキャッシュライン(例えば、記憶位置)を含むウェイ(例えば、データアレイ110の列)に対応する。データアレイ110は、第1のラインドライバ140を有する第1のウェイ120と、第2のラインドライバ142を有する第2のウェイ122と、N番目のライドライバ144を有するN番目のウェイ124とを含むことができる。3つのラインドライバ140～144が図1に示されるが、3つよりも少ない、または3つよりも多いラインドライバが、データアレイ110に含まれ得る。特定の実施形態では、データアレイ110は、4つのウェイを含む。各ラインドライバ140～144は、各ラインドライバ140～144が対応するウェイ120～124に関連付けられた内容(データアレイ110のキャッシュラインのデータ)をそれを介して駆動する、対応するデータライン(図示せず)と結合され得る。例えば、ラインドライバ140は、第1のウェイ120に関連付けられた内容(例えば、キャッシュラインに記憶された1つまたは複数の命令のようなデータ)を駆動することができる。特定の実施形態では、ラインドライバ140～144は、ウェイ120～124の内容をデータアレイ110の出力としてマルチプレクサ(図示せず)に駆動する。マルチプレ

40

50

クサは、複数のラインドライバ140～144に応答することができ、特定のウェイ(例えば、所望のウェイ)を選択するように構成され得る。特定の実施形態では、データアレイ110は、マルチプレクサを含むことができる。

#### 【0017】

制御ロジック150は、「次のウェイ」予測をデータアレイ110に提供する予測マスク152(例えば、マルチビットウェイ予測マスク)を含むことができ、または予測マスク152へのアクセスを有することができる。「次のウェイ」予測は、フェッチされた最後のキャッシュライン(例えば、アクセスされたデータアレイ110の最後のキャッシュライン)に関連付けられてもよく、駆動されるべき「次のウェイ」、および、その結果アクセスされるべき次のキャッシュライン(例えば、実行されるべき次の命令)を予測(例えば、識別)することができる。1つまたは複数の「次のウェイ」(ウェイ120～124のすべてではない)を予測することによって、命令キャッシュ102のすべてよりも少ないラインドライバ140～144が駆動され(例えば、対応するドライバを有効にし)、これは、すべてのウェイ120～140を駆動するためにすべてのドライバ140～144を有効にするよりも低減された電力使用量をもたらす。予測マスク152の値(例えば、予測マスク値)は、1つまたは複数の次のウェイを予測するために、命令キャッシュ102のフェッチされた最後のキャッシュラインに対応してもよい。予測マスク152は、nビットベクトルを含んでもよく、ここで各ビットは命令キャッシュ102の特定のウェイに対応する。予測マスク152は、レジスタまたはバッファに記憶され得る。

#### 【0018】

制御ロジック150は、フェッチされた最後のキャッシュラインに関連付けられた予測マスク値に基づいて(例えば、予測マスク値に従って)、予測マスク152の1つまたは複数のビットを選択的に設定するように構成され得る。予測マスク152は、1つまたは複数のドライバ140～144のような、データアレイ110のラインドライバのサブセットを有効(または、無効)にすることができる。予測マスク152の複数のビットが設定されると、対応する数の複数のドライバ140～144が有効(または、無効)にされる。複数のドライバ140～144の各々は、予測マスク152の特定のビットによって、選択的に有効に(例えば、オンにもしくは活性化)されてもよく、または選択的に無効に(例えば、オフにもしくは不活性化)され得る。特定の実施形態では、ラインドライバのサブセットは、2つ以上のラインドライバである(例えば、予測マスク152は、設定された複数のビットを有し、多重ラインドライバを同時に有効にする)。

#### 【0019】

制御ロジック150は、各々がデータアレイ110のキャッシュラインに対応する複数の予測マスク値を維持するように構成され得る。複数の予測マスク値は、制御ロジック150にアクセス可能な1つまたは複数の記憶位置に格納され得る。例えば、1つまたは複数の予測マスク値は、タグアレイ内に、データアレイ110のキャッシュラインに関連付けられたレジスタ内に、それぞれのキャッシュラインの一部として、または、データアレイ110のキャッシュラインと一対一の関連を有する構造に記憶され得る。内容がデータアレイ110の特定のキャッシュラインにロードされると、制御ロジック150は、特定のキャッシュラインに対応する特定の予測マスク値を初期値に設定(例えば、初期化)することができる。さらに、制御ロジック150は、特定のキャッシュラインにロードされる内容を反映するために、必要に応じて、他の予測マスク値を更新することができる。例えば、制御ロジック150は、ウェイがもはや他のキャッシュラインの「次のウェイ」として識別されていないことを示すために、特定のキャッシュラインの以前の内容に関連付けられたウェイを「次のウェイ」として識別した別のキャッシュラインに対応する予測マスク値を更新することができる。

#### 【0020】

制御ロジック150は、最後にフェッチされた(例えば、直近にフェッチされた)データアレイ110のキャッシュラインに関連付けられた予測マスク値を受信することができる。予測マスク値は、最後のキャッシュラインがフェッチされた後、アクセスされるべき1つま

10

20

30

40

50

たは複数のウェイを予測する(例えば、識別する)ことができる。アクセスされるべき1つまたは複数のウェイは、各々、フェッチされた最後のキャッシュラインに対応する命令の後に実行されるべき1つまたは複数の命令を記憶するキャッシュラインに対応する。制御ロジック150は、予測マスク値に基づいて予測マスク152を設定することができる。例えば、データアレイ110の特定のキャッシュラインがアクセスされたとき、特定のキャッシュラインに対応する予測マスク値は、特定のキャッシュラインがアクセスされた後の次のキャッシュアクセス中に駆動されるべき1つまたは複数の「予測された」ウェイを識別する予測マスク152の値として識別および設定され得る。予測マスク152は、予測マスクに基づいて1つまたは複数のドライバ140～144を選択的に有効および/または無効にするために、データアレイ110に提供され得る。予測マスク152の結果として有効(例えば、オン)または無効(例えば、オフ)にされたドライバ140～144は、図2に関連してさらに詳述するようになされ得る。有効にされたドライバ140～144に対応するキャッシュラインの内容(例えば、命令)を、出力マルチプレクサなどに提供する(例えば、駆動する)ことができる。特定の実施形態では、フェッチされた最後のキャッシュラインに関連付けられた命令は、データアレイ110に提供されているフェッチされた最後のキャッシュラインの予測マスク値と同時に実行される。

#### 【0021】

制御ロジック150(または、マルチプレクサのような、命令キャッシュ102の他の構成要素)は、有効にされたドライバ140～144を介して提供される内容が、次に(例えば、フェッチされた最後のキャッシュラインに対応する命令の後に)実行されるべき1つまたは複数の命令を含むかどうかを判断することができる。予測マスク値に設定された、予測マスク152に従って有効にされたウェイが、次に実行されるべき1つまたは複数の命令を提供しない(例えば、予測マスクが駆動されるべき正しい次のウェイを予測しない)場合、予測外れが生じる。特定の実施形態では、制御ロジック150は、予測マスク152によって識別された予測されたウェイに対応するデータアレイ110の出力をマルチプレクサが選択するかどうかに基づいて、予測外れが生じたかどうかを判断する。

#### 【0022】

制御ロジック150は、また、1つまたは複数のドライバ140～144を有効にするためにデータアレイ110に提供されている予測マスク152(例えば、特定の予測マスク値)に基づいて予測外れが生じたかどうかを判断することによって、複数の予測マスク値を維持することができる。特定の予測マスク値がデータアレイ110に適用されたとき、制御ロジック150は、特定の予測マスク値に基づいて予測外れが生じたかどうかを判断することができる。予測外れが生じたと判断がなされたとき、以前に有効にされなかった1つまたは複数のラインドライバ140～144は、その後正しいウェイ出力を提供して予測外れから回復するために有効にされ得る。具体的な実施形態では、すべてのラインドライバ140～144は、予測外れの後に有効にされる。

#### 【0023】

制御ロジック150は、アクセスされる(例えば、駆動される)正しいウェイを識別することができ、正しいウェイに基づいて、予測外れを生じた予測マスク値を更新することができる。例えば、制御ロジック150は、予測マスク値に関連付けられたキャッシュライン(例えば、ウェイ)がアクセスされた後、正しいウェイを後続のウェイとして識別することができる。特定の実施形態では、予測外れからの回復は、フェッチされた最後のキャッシュラインに関連付けられた命令の後に実行されるべき命令を取得するために、命令キャッシュ102以外の別の記憶位置(例えば、メインメモリ)にアクセスすることを含むことができる。命令が他の記憶位置から取得(例えば、フェッチ)されると、命令は、データアレイ110の特定のウェイ120～124に関連付けられたキャッシュラインにロード(例えば、記憶)され得る。制御ロジック150は、特定のウェイを後継のウェイとして識別することができ、識別された特定のウェイに基づいて予測マスク値を更新することができる。制御ロジック150は、アクセスされた後続のキャッシュラインに対応する予測マスク値のビットを設定することによって、予測外れを生じた予測マスク値を更新することができる。したがって

、予測マスク値が後続のウェイを成功裏に予測することに失敗した場合、予測マスク値は、キャッシュラインが次にアクセスされたときに後続のウェイが「次のウェイ」(例えば、後継のウェイ)として予測されるように更新される。

#### 【0024】

動作中、制御ロジック150は、データアレイ110のキャッシュライン(例えば、ウェイ)に記憶された命令に関連付けられた命令アドレスを受信することができる。命令アドレスに基づいて、制御ロジック150は、命令アドレスに関連付けられた特定の予測マスク値を識別することができる。例えば、制御ロジック150は、各々がデータアレイ110のキャッシュラインに対応する複数の予測マスク値から、特定の予測マスク値を識別することができる。特定の予測マスク値が識別された後、制御ロジック150は、予測マスク152の値が特定の予測マスク値と同じ値になるように、識別された特定の予測マスク値に基づいて予測マスク152の1つまたは複数のビットを設定することができる。制御ロジック150は、命令アドレスに関連付けられたキャッシュラインがフェッチされた後、予測マスク値152(例えば、マルチビットウェイ予測マスク)をデータアレイ110(例えば、ラインドライバ140～144)に提供することができる。特定のラインドライバ140～144に対応する予測マスク152の各ビットは、特定のラインドライバ140～144の入力で受信された値(例えば、データ値)に基づいて特定のラインドライバを有効または無効にするために、特定のラインドライバ140～144の入力で受信され得る。10

#### 【0025】

データアレイ110は、予測マスク152を受信することができ、データアレイ110のラインドライバ140～144のサブセットは、受信された予測マスク152に基づいて選択的に有効にされ得る。例えば、特定のラインドライバ140～144は、特定のラインドライバ140～144に対応する予測マスク152のビットを受信することができる。データアレイ110は、データアレイ110の出力として、ラインドライバ140～144のサブセットの各々の有効にされたドライバに対応するウェイの内容(例えば、キャッシュラインの少なくとも一部)を提供することができる。データアレイ110の出力として提供される内容は、命令アドレスに関連付けられたキャッシュラインがフェッチされた後にアクセスされる次のウェイであるように予測されたウェイを表すことができる。20

#### 【0026】

複数のドライバ140～144のサブセットを選択的に有効にし、2つ以上の予測されたウェイ(すべてのウェイではない)を駆動することによって、電力の利益は、命令キャッシュ102の各データアクセスで実現され得る。さらに、上記で説明したウェイ予測技術を使用すると、予測外れの後、マルチビットウェイ予測マスク152のビットは、特定のキャッシュラインを後継として識別するために更新されるので、予測外れは各後継ウェイについて一度のみ生じるであろう。30

#### 【0027】

図2を参照すると、マルチビット予測マスクを利用するプロセッサシステム200が開示される。プロセッサシステム200は、プログラムカウンタ270と、命令キャッシュ(icache)102とを含むことができる。プロセッサシステム200は、命令を1つまたは複数の実行ユニット(図示せず)に提供するために、命令キャッシュ102を使用することができる。40

#### 【0028】

プログラムカウンタ270は、実行されるべき命令を識別することができる。プログラムカウンタ270は、実行されるべき命令に関連付けられたインデックス部分272およびタグ部分274を含むことができる。命令が実行されるたびに、プログラムカウンタ270は、実行されるべき次の命令を識別するように調整(例えば、インクリメント)され得る。実行されるべき次の命令のインデックス部分272は、データアレイ110に提供されてもよく、実行されるべき次の命令に関連付けられたデータアレイ110のインデックス(例えば、複数のキャッシュラインを含む行)を識別することができる。タグ部分274は、命令キャッシュ102のタグアレイ280に提供され得る。タグアレイ208は、実行されるべき次の命令に関連付けられたデータアレイの列(例えば、ウェイ)を識別するために、タグ部分274を使用することが50

できる。したがって、インデックス部分272およびタグ部分274の組合せは、実行されるべき次の命令を記憶するデータアレイ110の特定のキャッシュラインを一意に識別することができる。特定の実施形態では、プログラムカウンタ270は、インデックス部分272、タグ部分274、またはそれらの組合せを、制御ロジック150に提供することもできる。

#### 【0029】

命令キャッシュ102は、データアレイ110と、マルチプレクサ260と、制御ロジック150と、タグアレイ280とを含むことができる。データアレイ110は、データキャッシュの複数の行の特定の行に関する、図2に示すような第1のウェイ、第2のウェイ、第3のウェイ、および第4のウェイのような複数のウェイ(例えば、4つのウェイ)を含むことができる。ウェイの各々は、命令キャッシュ102の対応するキャッシュライン220a～220dに関連付けられ得る。複数のウェイは、(一連の命令としてプロセッサシステム200によって実行される)プログラムの実行中にアクセスされ得る。複数のウェイの各々は、データアレイ110のキャッシュラインに対応するドライバ240a～240d(例えば、ラインドライバ)およびデータライン230a～230dを含むことができる。例えば、第1のウェイは、キャッシュラインA(220a)に関連付けられてもよく、第1のドライバ240aおよび第1のデータライン230aを含むことができ、第2のウェイは、キャッシュラインB(220b)に関連付けられてもよく、第2のドライバ240bおよび第2のデータライン230bを含むことができ、第3のウェイは、キャッシュラインC(220c)に関連付けられてもよく、第3のドライバ240cおよび第3のデータライン230cを含むことができ、第4のウェイは、キャッシュラインD(220d)に関連付けられてもよく、第4のドライバ240dおよび第4のデータライン230dを含むことができる。

10

#### 【0030】

各ドライバ240a～240dは、対応するデータライン230a～230dを介してデータアレイ110から読み出される(例えば、駆動される)ように、対応するキャッシュライン220a～220dに記憶されたデータ(例えば、1つまたは複数の命令)を有効にすることができます。データは、データアレイ110の出力として提供され得る。例えば、ドライバ240a～240dは、図1のドライバ140～144に対応することができる。データアレイ110は、セットアソシティブ命令キャッシュデータアレイを含むことができる。特定の実施形態では、データアレイ110は、4ウェイセットアソシティブキャッシュである。

20

#### 【0031】

制御ロジック150は、予測マスク152の値を設定することができる。予測マスク152のための設定された値は、最後にアクセスされたデータアレイ110の特定のキャッシュライン220a～dに対応することができる。予測マスク152の値は、最後にフェッチされた特定のキャッシュライン220a～220dに関連する「次のウェイ」(例えば、後続のウェイ)を予測することができる。例えば、予測マスク152のための設定された値は、キャッシュラインA(220a)に対応することができる。図2の予測マスク152は、4ビットを含むことができ、ここで各ビットはそれぞれ、異なるウェイおよびその結果異なるドライバ240a～240dに対応する。例えば、左から右へ、第1のビット(例えば、最上位ビット)は第1のウェイに対応することができ、第2のビットは第2のウェイに対応することができる、などである。予測マスク152は、(例えば、論理1の値にアサートされた)設定されている1つまたは複数のビットに基づいて、有効にされるべき1つまたは複数のドライバ240a～240dを示すことができる。例えば、ドライバ240a～240dのサブセット(例えば、ラインドライバのサブセット)は、内容(例えば、対応するキャッシュライン220a～220dに記憶された1つまたは複数の命令のようなデータ)をマルチプレクサ260に提供するために、(データアレイ110に適用されている予測マスク152に応答して)有効にされ得る。

30

#### 【0032】

各キャッシュライン220a～220dは、対応する予測マスク値(例えば、対応するマルチビット予測マスク値)に関連付けられ得る。特定のキャッシュライン(例えば、キャッシュライン220a～220dのうちの1つ)に関する対応する予測マスク値は、アクセスされている特定のキャッシュラインに基づいて予測マスク152の一部の値として設定され得る。例えば、特定のキャッシュラインがアクセスされたとき、特定のキャッシュラインに対応する予測

40

50

マスク値は、特定のキャッシュラインの後に駆動されるべき1つまたは複数の「予測された」ウェイを識別するために、予測マスク152の一部の値として識別され、設定され得る。対応する予測マスク値は、命令キャッシュ102のキャッシュラインと一対一の関連を有する任意の構造に記憶され得る。例えば、1つまたは複数の対応する予測マスク値は、タグアレイ(例えば、タグアレイ280)内に、キャッシュライン220a～220dに関連付けられた(例えば、対応する)レジスタ内に、または、キャッシュラインの一部として(例えば、その後に)記憶され得る。特定の例示的な実施形態では、データアレイ110のキャッシュラインA(220a)は、キャッシュラインAの内容222(例えば、1つまたは複数の記憶された命令)と、キャッシュラインAの予測マスク値254(例えば、対応する予測マスク値)とを含む。アクセスされている(例えば、フェッチされる)キャッシュラインA(220a)に基づいて、制御ロジック150は、キャッシュラインAの予測マスク値254を選択することができ、予測マスク152の値を、キャッシュラインAの予測マスク値254に設定することができる。制御ロジック150は、キャッシュラインAの予測マスク値254を維持することができ、1つまたは複数の予測外れが生じたとき、または、内容がデータアレイ110にロードされたもしくはデータアレイ110からフェッチされたとき、キャッシュラインAの予測マスク値254を更新することができる。キャッシュラインAの予測マスク値254は、キャッシュラインA(220a)の一部として記憶されているように示されるが、キャッシュラインAの予測マスク値254は、タグアレイ280の一部として、または、キャッシュラインA(220a)に関連付けられたレジスタの一部として記憶され得ることを理解されたい。

## 【0033】

10

プロセッサシステム200の電源がオンされたとき、制御ロジック150は、予測マスク152の値を初期値(例えば、“0000”のようなゼロ値)に初期化することができる。制御ロジック150は、各予測マスク値を初期値に初期化することもできる。例えば、プロセッサシステム200の電源投入時に、制御ロジック150は、キャッシュラインAの予測マスク値254を初期値に初期化することができる。特定の実施形態では、予測マスク152がすべてゼロの値を含むとき、予測は存在せず、ドライバ240a～240dは、キャッシュラインA(220a)のフェッチに続いて駆動されない(例えば、有効にされない)。代替実施形態では、予測マスク152がすべてゼロの値を含むとき、すべてのドライバ240a～240dが駆動される。

## 【0034】

20

制御ロジック150は、特定の予測マスクに対応するキャッシュラインに内容がロードされたとき(例えば、キャッシュラインファイル)、特定の予測マスク値を初期化することもできる。例えば、制御ロジック150は、1つまたは複数の命令がキャッシュラインA(220a)にロードされた(例えば、記憶された)とき、キャッシュラインAの予測マスク値254を“0000”的初期値に設定することができる。

## 【0035】

30

制御ロジック150は、周期的に1つまたは複数の予測マスク値を初期値に設定することができる。例えば、制御ロジック150は、ある時間期間が終了した(例えば、時間期間の満了)後、または、いくつかのキャッシュアクセス動作後、1つまたは複数の予測マスク値をリセットする(例えば、ゼロ値に初期化する)こともできる。特定の実施形態では、各予測マスク値は、対応する時間期間、対応する数のキャッシュアクセス動作、またはそれらの組合せに関連付けられ得る。別の特定の実施形態では、データアレイ110全体は、対応する時間期間、対応する数のキャッシュアクセス動作、またはそれらの組合せに関連付けられ得る。例えば、キャッシュアクセス動作の数は、データアレイ110か、データアレイ110の特定の行か、または特定のキャッシュライン220a～220dのキャッシュ動作(例えば、キャッシュロード、キャッシュフェッチ、またはそれらの組合せのようなキャッシュアクセス動作)の数に関連付けられ得る。特定の実施形態では、時間期間および/またはキャッシュ動作の数は、制御ロジック150によって追跡され得る。内容が特定のキャッシュラインにロードされたとき、特定のキャッシュラインの対応する予測マスク値は初期値に設定されてもよく、特定のキャッシュラインに対応するウェイを後継のキャッシュラインとして識別するすべての他の予測マスク値が更新され得る。例えば、キャッシュラインAの予測マ

40

50

スク値254が(例えば、キャッシュラインD(220d)に関連付けられた第4のウェイが後継のウェイであることを示す)“0001”であり、内容(例えば、新しい内容)がキャッシュラインD(220d)にロードされたとき、キャッシュラインDの予測マスク値は、初期値に設定されてもよく、キャッシュラインAの予測マスク値254は、キャッシュラインD(220d)の新しい内容に対応するウェイがキャッシュラインA(220a)の実行後の「次のウェイ予測」として予測されていないことを示す“0000”に設定され得る。

#### 【0036】

内容が特定のキャッシュラインにロードされ、対応する予測マスク値が初期値に設定された後、制御ロジック150は、(例えば、後継のウェイとして特定のキャッシュラインに続いている)どのウェイが次にアクセスされるのかを判断する(例えば、識別する)ことができる。後継のウェイを判断すると、制御ロジック150は、後継のウェイを識別するように、対応する予測マスク値のピットを設定することができる。10

#### 【0037】

例えば、内容(例えば、1つまたは複数の命令)がデータアレイ110のキャッシュラインA(220a)にロードされた(および、キャッシュラインAの予測マスク値254が“0000”に初期化された)とき、制御ロジック150は、どのウェイがアクセスされるのかを判断することができる。キャッシュラインD(220d)に対応するウェイがキャッシュラインA(220a)の後継として識別されたとき、制御ロジック150は、キャッシュラインAの予測マスク値254を“0001”に設定することができる。したがって、キャッシュラインAがアクセスされ、キャッシュラインAの予測マスク値254が予測マスク152の値として設定されたとき、ドライバ240dは、キャッシュラインA(220a)の後にアクセスされているキャッシュラインD(220d)を見越して、第4のウェイ(例えば、キャッシュラインD(220d))の内容を駆動するために、選択的に有効にされ得る。キャッシュラインAの予測マスク値254の第4のウェイに対応するピットは、キャッシュラインD(220d)の内容(例えば、データ)が置き換えられる(例えば、排除もしくは除去される)まで、または、キャッシュラインAの予測マスク値254が初期値にリセットされるまで、アサートされたままでよい。代替的には、第4のウェイに対応するピットは、キャッシュラインD(220d)の内容(例えば、データ)が無効化されるまで、アサートされたままであってよい。20

#### 【0038】

制御ロジック150は、データアレイ110に適用されている予測マスク152の結果として予測外れが生じたかどうかを判断する(例えば、検出する)こともできる。例えば、予測マスク152が、データアレイ110の特定のキャッシュライン220a～220dに対応する特定の予測マスク値の値に設定されたとき、制御ロジック150は、特定の予測マスク値が予測外れをもたらしたかどうかを判断することができる。特定の予測マスク値が予測外れをもたらしたとき、制御ロジック150は、駆動されるべき正しいウェイ(例えば、有効にされるべき正しいドライバ)を識別することができ、識別された正しいウェイに基づいて特定の予測マスク値を更新することができる。30

#### 【0039】

例えば、予測マスク152が、“0001”的キャッシュラインAの予測マスク値254に設定されたとき、第4のウェイに関連付けられたドライバ240dは、キャッシュラインD(220d)の内容をマルチプレクサ260に駆動するために、選択的に有効にされ得る。制御ロジック150が、マルチプレクサ260に駆動されている第4のウェイに基づいて予測外れが生じたと判断したとき、制御ロジック150は、駆動されるべき正しいウェイを識別することができ、キャッシュラインAの予測マスク値254を更新することができる。例えば、制御ロジック150は、駆動されるべき正しいウェイを識別する、または、予測外れが生じたときに駆動されなかった1つもしくは複数のウェイを識別するマルチプレクサに信号を提供することができる。特定の実施形態では、キャッシュラインC(220c)に対応する第3のウェイは、制御ロジック150によって正しいウェイとして識別され、制御ロジック150は、キャッシュラインAの予測マスク値254を、キャッシュラインC(220c)に関連付けられた第3のウェイもキャッシュラインA(220a)の後継であるという判断を反映する“0011”に更新する。4050

## 【0040】

マルチプレクサ260は、命令キャッシュ102の出力として提供されるべき、データアレイ110の出力のうちの1つを選択することができる。命令キャッシュ102の出力は、プロセッサシステム200に関連付けられた実行ユニット(図示せず)に提供され得る。マルチプレクサ260は、タグアレイ280の出力としてウェイ選択信号を受信するように構成され得る。ウェイ選択信号に基づいて、マルチプレクサ260は、マルチプレクサ260の出力(例えば、命令キャッシュ102の出力)として提供されるべき、データアレイ110の出力のうちの1つを選択することができる。

## 【0041】

プログラムカウンタ270は、(次に実行されるべき命令に関連付けられた)タグ部分274をタグアレイ280に提供することができる。特定の実施形態では、タグ部分274は、次に実行されるべき命令に関連付けられ得る1つまたは複数のウェイを予測する(現在実行されている命令に関連付けられた)予測マスク152を適用する制御ロジック150と並行して、タグアレイ280に提供され得る。別の特定の実施形態では、タグ部分274は、予測外れの後に(例えば、予測外れに応答して)、タグアレイ280に提供され得る。タグアレイ280は、次に実行されるべき命令を含むデータアレイ110の位置(例えば、キャッシュラインまたはウェイ)を識別することができる。タグアレイ280は、ウェイ選択信号としてマルチプレクサ160に位置を提供することができる。予測マスク152がマルチプレクサ260に駆動されているデータアレイ110の2つ以上のウェイをもたらすとき、マルチプレクサは、タグアレイ280から受信したウェイ選択信号に基づいて特定のウェイを選択することができる。予測マスク152がウェイ選択信号によって識別されたウェイに対応する特定のラインドライバを有効にしなかった場合には、制御ロジック150は予測外れが生じたと判断することができる。予測外れから回復(例えば、訂正)するために、すべてのドライバ240a～240dが有効にされてもよく、マルチプレクサ260は実行ユニットに提供されるべき正しいウェイを選択することができる。代替実施形態では、タグアレイ280はウェイ選択信号を制御ロジック150およびマルチプレクサ260に提供することができる。予測外れの場合には、制御ロジック150はウェイ選択信号に基づいて単一のドライバ240a～240dを有効にすることによって、予測外れから回復することができる。制御ロジック150は正しいウェイの指示をマルチプレクサ260に提供することができる。

## 【0042】

動作中、特定の命令がデータアレイ110の特定のキャッシュライン220a～220dからフェッチされ、(実行ユニットによって)実行される。フェッチおよび/または実行されている特定の命令に基づいて、制御ロジック150は特定のキャッシュラインに対応する予測マスク値を識別する。制御ロジック150は、データアレイ110の1つまたは複数のドライバ240a～240dを選択的に有効にするために、予測マスク152を予測マスク値に設定することができる。1つまたは複数のドライバ240a～240dが有効にされたとき、1つまたは複数の有効にされたドライバ(例えば、1つまたは複数のドライバ240a～240d)に対応する選択されたキャッシュライン(例えば、1つまたは複数のキャッシュライン220a～220d)の内容がマルチプレクサ260に提供され得る。

## 【0043】

適用されている予測マスク152と並行して、プログラムカウンタ270は(次に実行されるべき命令に関連付けられた)タグ部分274をタグアレイ280に提供することができる。タグ部分274に基づいて、タグアレイ280は特定の命令の後にアクセスされるべきデータアレイ110の内容の位置(例えば、ウェイおよび/またはキャッシュライン)を決定することができる。タグアレイ280はウェイ選択信号として位置をマルチプレクサ260に提供することができる。

## 【0044】

マルチプレクサ260は、ウェイ選択信号と、予測マスク152に基づいて有効にされた1つまたは複数のドライバ(例えば、1つまたは複数のドライバ240a～240d)に対応する選択されたキャッシュライン(例えば、1つまたは複数のキャッシュライン220a～220d)の内容と

10

20

30

40

50

を受信することができる。ウェイ選択信号によって識別されたウェイがマルチプレクサ260に提供されたとき、マルチプレクサ260は識別されたウェイを選択し、マルチプレクサ260の出力としてウェイを提供する。代替的には、ウェイ選択信号によって識別されたウェイがマルチプレクサ260に提供されないとき、制御ロジック150は予測外れが生じたと判断し、正しいウェイをマルチプレクサ260に提供するために、1つまたは複数のドライバ240a～240dを有効にする。

#### 【 0 0 4 5 】

複数のドライバ240a～240dのサブセットを選択的に有効にし、2つ以上の予測されたウェイ(すべてのウェイではない)を駆動することによって、電力の利益が命令キャッシュ102の各データアクセスで実現され得る。さらに、プロセッサシステム200は、データアレイ110の各キャッシュライン220a～220dに関する予測マスク値を維持し、更新することができる。10

#### 【 0 0 4 6 】

図3を参照すると、命令キャッシュに関連付けられたウェイ予測を実行する方法300の第1の例示的実施形態のフロー図が示される。例えば、命令キャッシュは、図1の命令キャッシュ102を含むことができる。特定の実施形態では、方法300は図1の制御ロジック150によって実行され得る。

#### 【 0 0 4 7 】

ステップ302で、キャッシュラインに対応するマルチビットウェイ予測マスクが初期値に設定されてもよく、ステップ304で、キャッシュラインがフェッチされ得る。マルチビットウェイ予測マスクは、複数のキャッシュラインを有するデータアレイを含む命令キャッシュに関連付けられ得る。マルチビットウェイ予測マスクの値は、命令キャッシュのデータアレイに含まれるキャッシュラインに対応することができる。例えば、マルチビットウェイ予測マスクは予測マスク152であってもよく、データアレイは図1のデータアレイ110であってもよい。20

#### 【 0 0 4 8 】

ステップ306で、マルチビットウェイ予測マスクは、複数のラインドライバに適用され得る。データアレイの複数のラインドライバのうちのラインドライバのサブセットが、マルチビットウェイ予測マスクに応じて有効にされ得る。特定の実施形態では、サブセットは多重ラインドライバを含むことができる(例えば、予測マスクは設定された複数のビットを有し、多重ラインドライバを同時に有効にする)。例えば、複数のラインドライバは、図1のラインドライバ140～144または図2のラインドライバ240a～240dを含むことができる。マルチビットウェイ予測マスクは、キャッシュラインの一部としてデータアレイに記憶された値(例えば、キャッシュラインに対応するマルチビット予測マスク値)に設定され得る。30

#### 【 0 0 4 9 】

ステップ308で、タグルックアップ動作が実行され得る。特定の実施形態では、ステップ308でのタグルックアップ動作は、ステップ306での複数のラインドライバに適用されているマルチビットウェイ予測マスクと並行して(例えば、同時に、または少なくとも部分的に重なって)実行され得る。例えば、タグルックアップ動作は図2の命令キャッシュ102のタグアレイ280を使用して実行され得る。40

#### 【 0 0 5 0 】

ステップ310で、キャッシュラインに対応するマルチビットウェイ予測マスク値のビットが選択的に設定され得る。例えば、マルチビットウェイ予測マスク値の1つまたは複数のビットは、マルチビットウェイ予測マスク値を更新するために設定され得る。マルチビットウェイ予測マスク値の1つまたは複数のビットは、図4を参照してさらに説明するように、データアレイからアクセスする(例えば、データをロードする、またはデータをフェッチする)1つまたは複数の動作に基づいて更新され得る。更新されたマルチビットウェイ予測マスク値(例えば、設定されたビット)は、命令キャッシュの複数のキャッシュラインとの一対一の関連を提供することができる任意の構造に記憶され得る。例えば、更新され50

たマルチビットウェイ予測マスク値(例えば、設定されたビット)は、タグアレイ内に、キャッシュラインに関連付けられた(例えば、対応する)レジスタに、または、キャッシュラインの一部として(例えば、その最後もしくは最初に)記憶され得る。

#### 【0051】

キャッシュラインに対応するマルチビットウェイ予測マスク値の1つまたは複数のビットは、キャッシュラインロード動作またはキャッシュラインフェッチ動作に基づいて選択的に設定され得る。例えば、予測外れが起きたとき、マルチビットウェイ予測マスク値は、マルチビットウェイ予測マスクに対応するキャッシュラインがアクセスされた後にアクセスされる識別された後継のウェイ(例えば、正しいウェイ)に基づいて更新され得る。別の例として、データがキャッシュラインにロードされたとき、キャッシュラインに対応するマルチビットウェイ予測マスク値が初期値に設定され得る。さらに、データがキャッシュラインにロードされたとき、各々が異なるキャッシュラインに対応する1つまたは複数のマルチビットウェイ予測マスク値が更新され得る。例えば、別のキャッシュラインに対応する別のマルチビットウェイ予測マスク値が、後継のウェイとしてキャッシュラインに関連付けられたウェイを識別し、識別されたキャッシュラインの内容が変更されたとき、他のキャッシュラインに対応する他のマルチビットウェイ予測マスクは、キャッシュラインにロードされているデータに基づいて、キャッシュラインに関連付けられたウェイが後続のウェイとしてもはや識別されない(例えば、予測されない)ことを示すために更新され得る(例えば、1つまたは複数のビットが選択的に設定され得る)。

#### 【0052】

方法300によれば、ラインドライバのサブセットが選択的に有効にされるとき、1つまたは複数の予測されたウェイ(すべてのウェイではない)が駆動されてもよく、電力の利益が命令キャッシュのデータアクセス中に実現され得る。さらに、上記で説明したウェイ予測技術を使用すれば、ウェイの予測外れ(例えば、マルチビットウェイ予測マスク152によって識別されていない後継のウェイ)は、予測外れの後、キャッシュラインに対応する予測マスク値のビットが後継のウェイを識別するために設定される(例えば、更新される)ので、一度のみ生じるであろう。更新されたマルチビットウェイ予測マスク値は、キャッシュラインの次の(例えば、後続の)アクセスの後に使用する(例えば、1つまたは複数のウェイを予測する)ために記憶され得る。

#### 【0053】

図4を参照すると、命令キャッシュに関連付けられたウェイ予測を実行する方法400の別の例示的実施形態のフロー図が示される。方法400はまた、命令キャッシュに実行される1つまたは複数の動作を監視することができ、命令キャッシュの第1のキャッシュラインに対応する予測マスク値を維持することができる。例えば、命令キャッシュは図1の命令キャッシュ102を含むことができる。特定の実施形態では、方法400は図1の制御ロジック150によって実行され得る。

#### 【0054】

ステップ402で、第1の内容がデータアレイの第1のキャッシュラインにロードされてもよく、ステップ404で、第1のキャッシュラインに対応するマルチビットウェイ予測マスク値が設定され得る。データアレイの第1のキャッシュラインにデータをロードする際に、第1のキャッシュラインに対応するマルチビットウェイ予測マスク値は、初期値に設定され得る。例えば、第1のキャッシュラインは図2の第1のキャッシュライン220a～220dのうちの1つを含むことができる。特定の実施形態では、第1の内容がキャッシュラインA(220a)にロードされてもよく、キャッシュラインAの予測マスク値254が初期値に設定され得る。

#### 【0055】

ステップ406で、次のウェイが識別されてもよく、マルチビットウェイ予測マスク値が更新され得る。次のウェイは第1のキャッシュラインの後継のウェイ(例えば、後続のキャッシュライン)であってもよく、第1のキャッシュラインに対応するマルチビットウェイ予測マスク値は識別された次のウェイを後継のウェイとして示すために更新され得る。次の

10

20

30

40

50

ウェイは、第1の内容がデータアレイの第1のキャッシュラインにロードされた後にアクセスされる(例えば、内容をフェッチされる、または内容をロードされる)特定のキャッシュラインに対応することができる。

#### 【0056】

ステップ402～ステップ406で、第1の内容をロードするとともに第1のキャッシュラインに対応するマルチビットウェイ予測マスク値を更新した後、キャッシュへの後続のアクセスは、第1の内容、および第1のキャッシュラインに対応するマルチビットウェイ予測マスク値が影響を受けたかどうかを判断するために、監視され得る。例えば、後続のアクセスが第2のキャッシュラインに行われたとき、ステップ408で、第2のキャッシュラインがフェッチされたかどうか、または第2の内容が第2のキャッシュラインにロードされたかどうかの判断が行われ得る。例えば、図1の制御ロジック150は、データアレイ110がアクセスされるたびにそのような判断を行うことによって、データアレイ110を監視することができる。第2の内容が第2のキャッシュラインにロードされていると判断されたとき、処理はステップ418に進み、フェッチされた第2のキャッシュラインが第1のキャッシュラインであるかどうかの判断が行われる。ステップ418で、第2のキャッシュラインが第1のキャッシュラインであると判断されたとき、第1のキャッシュラインの内容が変更されており、第1のキャッシュラインに続く予測された次のウェイはもはや有効ではない可能性が高い。したがって、処理はステップ404に進み、ここでマルチビットウェイ予測マスク値が設定される。例えば、マルチビットウェイ予測マスク値は、第1のキャッシュラインにロードされ、第1のキャッシュラインの第1の内容を置換している第2の内容に基づいて初期値に設定され得る。特定の実施形態では、マルチビットウェイ予測マスク値の値を設定することは、マルチビットウェイ予測マスク値を初期値(例えば、ゼロ値)に設定することを含む。10

#### 【0057】

代替的には、ステップ418で、第2のキャッシュラインがアレイの第1のキャッシュラインではないと代わりに判断されたとき、処理はステップ416に進み、第1のキャッシュラインおよび/または第2のキャッシュラインのマルチビットウェイ予測マスク値が更新され得る。第2のキャッシュラインに対応する特定の予測マスク値が初期値に設定され、キャッシュの予測マスク値は、第2のキャッシュラインにロードされている第2の内容に基づいて(例えば、反映するために)更新され得る。例えば、第1のキャッシュラインに対応するマルチビットウェイ予測マスクは、第1のキャッシュラインに対応するマルチビットウェイ予測マスク値が第2のキャッシュラインに対応するウェイが予測されたウェイ(例えば、第1のキャッシュラインがアクセスされた後の後続のウェイ)であることを示すアサートされたビットを含むときに更新され得る。第1のキャッシュラインに対応するマルチビットウェイ予測マスクがアサートされたビットを含むとき、第1のキャッシュラインに対応するマルチビットウェイ予測マスクは、アサートされたビットをディアサートする(例えば、論理ゼロ値に設定する)ことによって更新され得る。したがって、第1のキャッシュラインに対応するマルチビットウェイ予測マスク値の(例えば、第2のキャッシュラインに対応するウェイに関連付けられた)特定のビット値は、第2のキャッシュラインの内容が命令キャッシュから除去される(例えば、キャッシュライン位置から除去される)まで、設定されたままである。マルチビットウェイ予測マスクが更新された後、方法400はステップ408に進む。代替実施形態では、第1のキャッシュラインに対応するマルチビットウェイ予測マスク値の値は、第2のキャッシュラインが第1のキャッシュラインではないと判断されたときには更新されない。むしろステップ418で、第2のキャッシュラインが第1のキャッシュラインではないと判断されたとき、処理はステップ408に進み、第1のキャッシュラインに対応するマルチビットウェイ予測マスク値は、第2のキャッシュラインにロードされているデータ(例えば、第2の内容)に基づいて更新されない。30

#### 【0058】

ステップ408で、第2のキャッシュラインがフェッチ(例えば、アクセス)されたと代わりに判断されたとき、処理はステップ410に進み、第2のキャッシュラインが第1のキャッシュ40

10

20

30

40

50

ュラインであるかどうかの判断が行われる。ステップ410で、第2のキャッシュラインが第1のキャッシュラインではないと判断されたとき、処理はステップ408に進む。特定の実施形態では、第2のキャッシュラインに対応する特定の予測マスク値がデータアレイに提供される。

#### 【0059】

代替的には、ステップ410で、第2のキャッシュラインが第1のキャッシュラインであると判断されたとき、ステップ412で、第1のキャッシュラインの予測マスク値がデータアレイに適用(例えば、提供)される。マルチビットウェイ予測マスク値は、複数のラインドライバを含むデータアレイに適用される(例えば、提供される)予測マスクの値として設定され得る。データアレイ(例えば、複数のラインドライバ)への予測マスクの適用は、第1のキャッシュラインがフェッチ(例えば、アクセス)された後にアクセスされる「次のウェイ」であると予測される1つまたは複数のウェイを選択的に駆動する。アクセスされるべき正しい「次のウェイ」が、「次のウェイ」であると予測される1つまたは複数のウェイに含まれていないとき、予測外れが生じる。例えば、図2を参照すると、キャッシュラインAの予測マスク値254は、予測マスク152の値として設定され得る。特定の実施形態では、第1のキャッシュラインに対応するマルチビットウェイ予測マスクは、第1のキャッシュラインがフェッチ(例えば、アクセス)された後、データアレイの複数のラインドライバに適用される。例えば、マルチビットウェイ予測マスクをデータアレイの複数のラインドライバに適用することは、図1のラインドライバ140～144に、または図2のラインドライバ240a～240dに適用されている予測マスク152を含むことができる。マルチビットウェイ予測マスクが適用された後、方法400はステップ414に進む。10

#### 【0060】

ステップ414で、予測外れが生じたかどうかの判断が行われる。「次のウェイ」が、データアレイの1つまたは複数のドライバを選択的に有効にするためにデータアレイに適用されている予測マスクの結果として駆動されなかったとき、予測外れが生じる可能性がある。例えば、上記の判断は図1の制御ロジック150によって行われ得る。予測外れが発生したと判断されたとき、処理はステップ416に進み、マルチビットウェイ予測マスク値が更新される。予測外れの後、データアレイの1つまたは複数のラインドライバが有効にされ得る。特定の実施形態では、すべてのラインドライバが有効にされる。別の特定の実施形態では、単一のラインドライバが有効にされる。別の特定の実施形態では、有効にされる1つまたは複数のラインドライバは、予測外れをもたらした以前に有効にされたラインドライバを含まない。その後、後継のウェイは、第1のキャッシュラインがアクセスされた後に駆動されるべき正しいウェイ(例えば、正しいキャッシュライン)を識別するために、完了したタグルックアップ動作に基づいてデータアレイから選択され得る。制御ロジックは、予測外れの後に駆動された後継のウェイを判断(例えば、識別)することができ、後継のウェイに基づいて第1のキャッシュラインのマルチビットウェイ予測マスク値を更新することができる。したがって、予測マスク値は、予測マスクの適用が予測外れをもたらした(例えば、正しいウェイが駆動されなかった)後に駆動された後継のウェイ(例えば、正しいウェイ)の識別に基づいて更新され得る。予測外れが生じなかつたと判断されたとき、処理はステップ408に進む。30

#### 【0061】

方法400によれば、第1のキャッシュラインに関するマルチビットウェイ予測マスク値が維持され、更新され得る。マルチビットウェイ予測マスク値は、命令キャッシュの1つまたは複数のドライバを選択的に有効にするために、予測マスクとして命令キャッシュのデータアレイに提供され得る。1つまたは複数のラインドライバを選択的に有効にする(または、無効にする)ことは、第1のキャッシュラインがアクセスされた後に駆動されるべき1つまたは複数の予測される「次のウェイ」を駆動するように動作することができる。マルチビット予測マスク値は、ロード動作もしくはフェッチ動作がデータアレイの第2のキャッシュラインに行われたかどうか、または、第2のキャッシュラインが第1のキャッシュラインであるかどうかに基づいて更新され得る。マルチビットウェイ予測マスク値を維持お4050

および更新することによって、すべての命令キャッシュよりも少ないラインドライバを選択的に有効にすることは、電力効率およびプロセッサ性能に影響を与えることができる。

#### 【0062】

図5を参照すると、命令キャッシュに関連付けられたウェイ予測を実行する方法500の第3の例示的実施形態のフロー図が示される。例えば、命令キャッシュは図1の命令キャッシュ102を含むことができる。特定の実施形態では、方法500は図1の制御ロジック150によって実行され得る。

#### 【0063】

ステップ502で、マルチビットウェイ予測マスクが命令キャッシュのデータアレイで受信され得る。例えば、マルチビットウェイ予測マスクは、図1のマルチビットウェイ予測マスク152であってもよく、データアレイは、図1のデータアレイ110であり得る。マルチビットウェイ予測マスクの値は、タグアレイ内に、レジスタ内に、または、マルチビットウェイ予測マスクが対応する命令キャッシュのキャッシュラインの一部として記憶され得る。特定の実施形態では、マルチビットウェイ予測マスクの値は、タグアレイから、レジスタから、または、命令キャッシュの制御ロジックを介して命令キャッシュのキャッシュラインから受信される。

10

#### 【0064】

ステップ504で、データアレイのラインドライバのサブセットは、マルチビットウェイ予測マスクの設定されたビットに応じて選択的に有効にされ得る。1つまたは複数のラインドライバは、予測マスクの異なるビットによって選択的に有効にされ(例えば、オンにされ、もしくは活性化され)てもよく、または、選択的に無効にされ(例えば、オフにされ、もしくは不活性化され)得る。特定の実施形態では、予測マスクの各々のアサートされたビットは、キャッシュライン(例えば、キャッシュラインの内容)をマルチプレクサに駆動するために、対応するドライバを活性化させる(例えば、オンにさせる)。サブセットは、単一のラインドライバよりも大きくてよい。例えば、サブセットは、多重ラインドライバ(例えば、複数のラインドライバ)を含むことができる。ラインドライバのサブセットは、図1のラインドライバ140～144または図2のラインドライバ240a～240dのような複数のラインドライバに含まれ得る。

20

#### 【0065】

ステップ506で、ラインドライバのサブセットの各ドライバに対応するキャッシュラインは、マルチプレクサに提供され得る。例えば、ラインドライバのサブセットの各々の有効にされたラインドライバに対応するキャッシュラインは、マルチプレクサに提供され得る。予測外れが生じたかどうか(例えば、正しいウェイがマルチプレクサに駆動されなかつたかどうか)の判断がマルチビットウェイ予測マスクに基づいて行われ得る。例えば、制御ロジックは、マルチプレクサが、マルチプレクサに提供された駆動されたウェイ(例えば、1つまたは複数のキャッシュラインの、1つまたは複数の命令のようなコンテンツ)のうちの1つを選択したかどうかを識別(例えば、検出)することができる。予測外れが生じたと判断が行われたとき、すべてのラインドライバが有効にされてもよく、正しいウェイは、完了したタグルックアップ動作に基づいて選択され得る。タグルックアップ動作は、ラインドライバのサブセットを選択的に有効にするために複数のラインドライバに提供されているマルチビットウェイ予測マスクと同時に(例えば、並行して)実行されていてもよい。追加的または代替的に、タグルックアップ動作は、選択的に有効(または、無効)にされている1つまたは複数のラインドライバと同時に実行され得る。

30

#### 【0066】

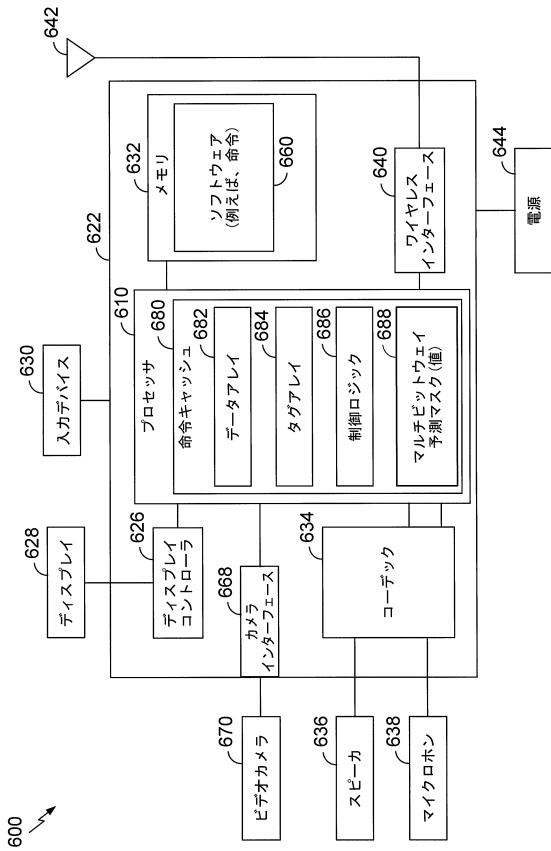

図6は、マルチビットウェイ予測マスクを利用する命令キャッシュメモリシステムを含むデバイス600(例えば、通信デバイス)の特定の実施形態のブロック図である。デバイス600は、ワイヤレス電子デバイスであってもよく、メモリ632に結合されたデジタル信号プロセッサ(DSP)のようなプロセッサ610を含むことができる。

40

#### 【0067】

プロセッサ610は、メモリ632に記憶されたソフトウェア660(例えば、1つまたは複数の

50

命令のプログラム)を実行するように構成され得る。プロセッサ610は、命令キャッシュ680を含むことができる。例えば、命令キャッシュ680は、図1の命令キャッシュ102を含むか、これに対応することができる。命令キャッシュ680は、データアレイ682と、タグアレイ684と、制御ロジック686と、マルチビットウェイ予測マスク688とを含むことができる。データアレイ682、制御ロジック686、およびマルチビットウェイ予測マスク688は、それぞれ、図1のデータアレイ110、制御ロジック150、および予測マスク152に対応することができる。データアレイ682は、図1のラインドライバ140～144または図2のラインドライバ240a～240dのような複数のラインドライバを含むことができる。タグアレイ684は、図2のタグアレイ280に対応することができる。例示的実施形態では、プロセッサ610は、図1～図2のシステムまたはその構成要素のいずれかを含むか、これに対応し、図3～図5の実施形態のいずれか、またはそれらの任意の組合せに従って動作する。例えば、図2に示すように、制御ロジック686は、データアレイ682の出力として提供されるべき予測されたウェイを有効にするためにデータアレイ682に適用されるマルチビットウェイ予測マスク688の値を設定することができる。特定の実施形態では、複数のラインドライバのサブセットは、マルチビットウェイ予測マスクに基づいて有効にされ、サブセットは、多重ラインドライバを含む。タグアレイ684は、適用されるマルチビットウェイ予測マスク688に基づいて予測外れが生じた場合に駆動されるべき正しいウェイを識別するために、タグルックアップ動作を実行することができる。特定の実施形態では、プロセッサ610は、メモリ632のような非一時的コンピュータ可読媒体に記憶されたコンピュータ実行可能命令(例えば、ソフトウェア660)を実行するように構成されてもよく、コンピュータ実行可能命令は、プロセッサ610のようなコンピュータに、予測マスク値に従ってマルチビットウェイ予測マスクのビットを選択的に設定させるために実行可能である。マルチビットウェイ予測マスクは、データアレイを含む命令キャッシュに関連付けられる。データアレイのラインドライバのサブセットは、マルチビットウェイ予測マスクに応じて有効にされる。特定の実施形態では、ラインドライバのサブセットは、単一のラインドライバである。別の特定の実施形態では、ラインドライバのサブセットは、2つ以上のラインドライバ(例えば、多重ラインドライバ)である。コンピュータ実行可能命令(例えば、ソフトウェア660)は、さらに、プロセッサ610に、予測マスク値を受信させ、多重ラインドライバを選択的に有効にさせることができる。

## 【0068】

カメラインターフェース668は、プロセッサ610に結合され、またビデオカメラ670のようなカメラに結合される。ディスプレイコントローラ626は、プロセッサ610およびディスプレイデバイス628に結合される。符号器/復号器(コーデック)634はまた、プロセッサ610に結合され得る。スピーカ636およびマイクロホン638は、コーデック634に結合され得る。ワイヤレスインターフェース640は、アンテナ642およびワイヤレスインターフェース640を介して受信されたワイヤレスデータがプロセッサ610に提供され得るように、プロセッサ610およびアンテナ642に結合され得る。

## 【0069】

特定の実施形態では、プロセッサ610、ディスプレイコントローラ626、メモリ632、コーデック634、ワイヤレスインターフェース640、およびカメラインターフェース668は、システムインパッケージまたはシステムオンチップデバイス622に含まれる。特定の実施形態では、入力デバイス630および電源644は、システムオンチップデバイス622に結合される。さらに、特定の実施形態では、図6に示すように、ディスプレイデバイス628、入力デバイス630、スピーカ636、マイクロホン638、ワイヤレスアンテナ642、ビデオカメラ670、および電源644は、システムオンチップデバイス622の外部にある。しかしながら、ディスプレイデバイス628、入力デバイス630、スピーカ636、マイクロホン638、ワイヤレスアンテナ642、ビデオカメラ670、および電源644の各々は、インターフェースまたはコントローラのような、システムオンチップデバイス622の構成要素に結合され得る。

## 【0070】

図3～図5の方法300～500は、フィールドプログラマブルゲートアレイ(FPGA)デバイス、

10

20

30

40

50

特定用途向け集積回路(ASIC)、中央処理ユニット(CPU)のような処理ユニット、デジタル信号プロセッサ(DSP)、コントローラ、別のハードウェアデバイス、ファームウェアデバイス、またはそれらの任意の組合せによって実施され得る。一例として、図3の方法300、図4の方法400、図5の方法500、またはそれらの任意の組合せは、図6に関して説明したように、メモリ632に記憶された命令を実行するプロセッサによって開始され得る。

#### 【0071】

1つまたは複数の説明した実施形態に関連して、データアレイを含む命令キャッシュに関連付けられたマルチビットウェイ予測マスクのビットを選択的に設定するための手段を含むことができる装置が開示される。ビットを選択的に設定するための手段は、図1～図2の制御ロジック150、図6のプロセッサ610および制御ロジック686、マルチビットウェイ予測マスクのビットを選択的に設定するように構成された1つもしくは複数の他のデバイスもしくは回路、またはそれらの任意の組合せを含むことができる。10

#### 【0072】

装置は、マルチビットウェイ予測マスクをデータアレイの複数のラインドライバに提供するための手段を含むこともできる。提供するための手段は、図1～図2の制御ロジック150、図6のプロセッサ610および制御ロジック686、マルチビットウェイ予測マスクを提供するように構成された1つもしくは複数の他のデバイスもしくは回路、またはそれらの任意の組合せを含むことができる。

#### 【0073】

装置は、多重ラインドライバを有効にした後に駆動された複数のウェイから特定のウェイを選択するための手段を含むこともできる。選択するための手段は、制御ロジック150、図1～図2の予測マスク152、図2のマルチブレクサ260およびタグアレイ280、図6のプロセッサ610、制御ロジック686、マルチビットウェイ予測マスク688、およびタグアレイ688、駆動された複数のウェイから特定のウェイを選択するように構成された1つもしくは複数の他のデバイスもしくは回路、またはそれらの任意の組合せを含むことができる。20

#### 【0074】

装置は、特定のウェイの指示を出力するための手段を含むこともできる。特定のウェイの指示を出力するための手段は、図1の制御ロジック150、図2のタグアレイ280、図6のタグアレイ684および制御ロジック686、特定のウェイの指示を出力するように構成された1つもしくは複数の他のデバイスもしくは回路、またはそれらの任意の組合せを含むことができる。30

#### 【0075】

装置は、特定のウェイから読み出されたデータを出力するための手段を含むこともできる。特定のウェイから読み出されたデータを出力するための手段は、図1のラインドライバ140～144、図2のラインドライバ240a～240dおよびマルチブレクサ260、特定のウェイから読み出されたデータを出力するように構成された1つもしくは複数の他のデバイスもしくは回路、またはそれらの任意の組合せを含むことができる。

#### 【0076】

1つまたは複数の開示された実施形態は、通信デバイス、固定位置データユニット、移動体位置データユニット、携帯電話、セルラ電話、コンピュータ、タブレット、ポータブルコンピュータ、またはデスクトップコンピュータを含む、デバイス600のようなシステムまたは装置で実施され得る。さらに、デバイス600は、セットトップボックス、エンターテイメントユニット、ナビゲーションデバイス、携帯情報端末(PDA)、モニタ、コンピュータモニタ、テレビジョン、チューナ、ラジオ、衛星ラジオ、音楽プレーヤ、デジタル音楽プレーヤ、携帯型音楽プレーヤ、ビデオプレーヤ、デジタルビデオプレーヤ、デジタルビデオディスク(DVD)プレーヤ、携帯型デジタルビデオプレーヤ、データもしくはコンピュータ命令を記憶もしくは取得する任意の他のデバイス、またはそれらの組合せを含むことができる。別の例示的な非限定的な例として、システムまたは装置は、携帯電話のようなリモートユニット、ハンドヘルドパーソナル通信システム(PCS)ユニット、携帯情報端末のような携帯型データユニット、全地球測位システム(GPS)対応デバイス、ナビゲー4050

ションデバイス、検針機器のような固定位置データユニット、または、データもしくはコンピュータ命令を記憶もしくは取得する任意の他のデバイス、または、それらの任意の組合せを含むことができる。

#### 【0077】

図1～図6の1つまたは複数は、本開示の教示によるシステム、装置、および/または方法を示している場合があるが、本開示は、これらの例示されたシステム、装置、および/または方法に限定されない。本開示の実施形態は、メモリ、プロセッサ、およびオンチップ回路を含む集積回路を含む任意のデバイスで適切に用いられ得る。

#### 【0078】

当業者は、さらに、本明細書に開示された実施形態に関連して説明した様々な例示的論理ブロック、構成、モジュール、回路、およびアルゴリズムステップが、電子ハードウェア、プロセッサによって実行されるコンピュータソフトウェア、またはそれらの組合せとして実現され得ることを理解するであろう。様々な例示的構成要素、ブロック、構成、モジュール、回路、およびステップは、それらの機能性の観点から、一般的に上記で説明される。そのような機能性がハードウェアまたはプロセッサ実行可能命令のどちらとして実施されるのかは、システム全体に課される特定の用途および設計の制約に依存する。当業者は、説明した機能性を各々の特定の用途のために様々な方法で実施することができるが、そのような実施の決定は、本開示の範囲からの逸脱を引き起こすと解釈されるべきではない。

#### 【0079】

本明細書に開示された実施形態に関連して説明した方法またはアルゴリズムのステップは、ハードウェアで直接、プロセッサによって実行されるソフトウェアモジュールで、またはこれら2つの組合せで具体化され得る。ソフトウェアモジュールは、ランダムアクセスメモリ(RAM)、フラッシュメモリ、読み出し専用メモリ(ROM)、プログラマブル読み出し専用メモリ(PROM)、消去可能プログラマブル読み出し専用メモリ(EPROM)、電気的消去可能プログラマブル読み出し専用メモリ(EEPROM)、レジスタ、ハードディスク、リムーバブルディスク、コンパクトディスク読み出し専用メモリ(CD-ROM)、または、当該技術上で公知の非一時的な記憶媒体の任意の他の形態内に存在することができる。例示的な記憶媒体は、プロセッサが情報を記憶媒体から読み出し、記憶媒体に書き込むことができるようになり、プロセッサに結合される。代替では、記憶媒体は、プロセッサと一体化され得る。プロセッサおよび記憶媒体は、特定用途向け集積回路 ASIC 内に存在することができる。ASIC は、コンピューティングデバイスまたはユーザ端末内に存在することができる。代替では、プロセッサおよび記憶媒体は、コンピューティングデバイスまたはユーザ端末内の別々の構成要素として存在することができる。

#### 【0080】

開示された実施形態の上記の説明は、当業者が開示された実施形態を製造または使用することを可能にするために提供される。これらの実施形態に対する様々な変更は、当業者には容易に明らかであり、本明細書で定義される原理は、本開示の範囲から逸脱することなく、他の実施形態に適用され得る。したがって、本開示は、本明細書に示された実施形態に限定されることを意図しておらず、以下の特許請求の範囲によって定義される原理および新規な特徴と一致する可能な最も広い範囲を与えられるべきである。

#### 【符号の説明】

#### 【0081】

- 100 プロセッサシステム

- 102 命令キャッシュ

- 110 データアレイ

- 120 ウェイ

- 122 ウェイ

- 124 ウェイ

- 140 ラインドライバ

10

20

30

40

50

|      |                             |    |

|------|-----------------------------|----|

| 142  | ラインドライバ                     |    |

| 144  | ラインドライバ                     |    |

| 150  | 制御ロジック                      |    |

| 152  | 予測マスク                       |    |

| 200  | プロセッサシステム                   |    |

| 220a | キャッシュラインA                   | 10 |

| 220b | キャッシュラインB                   |    |

| 220c | キャッシュラインC                   |    |

| 220d | キャッシュラインD                   |    |

| 222  | キャッシュラインAの内容                |    |

| 230a | データライン                      |    |

| 230b | データライン                      |    |

| 230c | データライン                      |    |

| 230d | データライン                      |    |

| 240a | ドライバ                        |    |

| 240b | ドライバ                        |    |

| 240c | ドライバ                        |    |

| 240d | ドライバ                        |    |

| 254  | キャッシュラインAの予測マスク値            |    |

| 260  | マルチプレクサ                     | 20 |

| 270  | プログラムカウンタ                   |    |

| 272  | インデックス部分                    |    |

| 274  | タグ部分                        |    |

| 280  | タグアレイ                       |    |

| 600  | デバイス                        |    |

| 610  | プロセッサ                       |    |

| 622  | システムインパッケージまたはシステムオンチップデバイス |    |

| 626  | ディスプレイコントローラ                |    |

| 628  | ディスプレイデバイス                  |    |

| 630  | 入力デバイス                      | 30 |

| 632  | メモリ                         |    |

| 634  | コーデック                       |    |

| 636  | スピーカ                        |    |

| 638  | マイクロホン                      |    |

| 640  | ワイヤレスインターフェース               |    |

| 642  | ワイヤレスアンテナ                   |    |

| 644  | 電源                          |    |

| 660  | ソフトウェア                      |    |

| 668  | カ梅ラインインターフェース               |    |

| 670  | ビデオカメラ                      | 40 |

| 680  | 命令キャッシュ                     |    |

| 682  | データアレイ                      |    |

| 684  | タグアレイ                       |    |

| 686  | 制御ロジック                      |    |

| 688  | マルチビットウェイ予測マスク              |    |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

---

フロントページの続き

(72)発明者 スレッシュ・ケー・ヴェンクマハンティ

アメリカ合衆国・カリフォルニア・92121・サン・ディエゴ・モアハウス・ドライブ・577

5

(72)発明者 ルシアン・コドレスク

アメリカ合衆国・カリフォルニア・92121・サン・ディエゴ・モアハウス・ドライブ・577

5

審査官 後藤 彰

(56)参考文献 特開2011-257800(JP,A)

特開2014-085890(JP,A)

特開2005-316842(JP,A)

特表2005-535955(JP,A)

特開平10-320275(JP,A)

特開平7-334423(JP,A)

米国特許出願公開第2005/0050278(US,A1)

(58)調査した分野(Int.Cl., DB名)

G 06 F 12 / 08