(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2008년03월17일

(11) 등록번호 10-0813554

(24) 등록일자 2008년03월07일

(51) Int. Cl.

*G11C 7/10* (2006.01) *G11C 8/00* (2006.01)

(21) 출원번호 10-2007-0002747

(22) 출원일자 2007년01월10일

심사청구일자 2007년01월10일

(56) 선행기술조사문헌

JP200242469 A

KR1019990055781 A

KR1020040034984 A

(73) 특허권자

주식회사 하이닉스반도체

경기 이천시 부발읍 아미리 산136-1

(72) 발명자

윤원주

경기 이천시 고담동 고담기숙사 105동 713호

이현우

경기 이천시 부발읍 신하3리 365번지 진우아파트

102동 1603호

(74) 대리인

김성남

전체 청구항 수 : 총 42 항

심사관 : 이강하

(54) 데이터 출력 스트로브 신호 생성 회로 및 이를 포함하는반도체 메모리 장치

### (57) 요 약

본 발명의 데이터 출력 스트로브 신호 생성 회로는, 제어 신호의 제어에 따라 입력 클럭의 데티비를 보정하여 보정 클럭을 출력하는 데티 사이클 보정 수단; 데이터 출력 스트로브 신호를 입력 받아 상기 제어 신호를 출력하는 데티 사이클 제어 수단; 및 상기 보정 클럭으로부터 상기 데이터 출력 스트로브 신호를 생성하는 데이터 출력 스트로브 신호 생성 수단;을 포함하는 것을 특징으로 한다.

**대표도** - 도1

## 특허청구의 범위

### 청구항 1

제어 신호의 제어에 따라 입력 클럭의 뉴티비를 보정하여 보정 클럭을 출력하는 뉴티 사이클 보정 수단; 데이터 출력 스트로브 신호를 입력 받아 상기 제어 신호를 출력하는 뉴티 사이클 제어 수단; 및 상기 보정 클럭으로부터 상기 데이터 출력 스트로브 신호를 생성하는 데이터 출력 스트로브 신호 생성 수단; 를 포함하는 것을 특징으로 하는 데이터 출력 스트로브 신호 생성 회로.

### 청구항 2

제 1 항에 있어서,

상기 제어 신호는 복수 개의 신호의 조합으로 이루어지며, 상기 뉴티 사이클 보정 수단은 상기 제어 신호에 포함된 신호 중 하이 신호와 로우 신호의 개수에 따라 상기 입력 클럭의 뉴티비를 보정하는 것을 특징으로 하는 데이터 출력 스트로브 신호 생성 회로.

### 청구항 3

제 1 항 또는 제 2 항에 있어서,

상기 뉴티 사이클 보정 수단은,

상기 제어 신호의 입력에 대응하여 외부 공급전원의 구동부로의 공급량을 제어하는 풀업부;

상기 제어 신호의 입력에 대응하여 그라운드 전원의 상기 구동부로의 공급량을 제어하는 풀다운부; 및

상기 풀업부와 상기 풀다운부로부터 공급되는 각 전원을 인가 받아 상기 입력 클럭을 구동하여 상기 보정 클럭을 출력하는 상기 구동부;

를 포함하는 것을 특징으로 하는 데이터 출력 스트로브 신호 생성 회로.

### 청구항 4

제 3 항에 있어서,

상기 풀업부는 게이트 단에 상기 제어 신호에 포함된 신호를 각각 입력 받고, 상기 외부 공급전원의 공급단과 상기 구동부 사이에 병렬로 구비되는 복수 개의 트랜지스터를 포함하는 것을 특징으로 하는 데이터 출력 스트로브 신호 생성 회로.

### 청구항 5

제 3 항에 있어서,

상기 풀다운부는 게이트 단에 상기 제어 신호에 포함된 신호를 각각 입력 받고, 상기 그라운드 전원의 공급단과 상기 구동부 사이에 병렬로 구비되는 복수 개의 트랜지스터를 포함하는 것을 특징으로 하는 데이터 출력 스트로브 신호 생성 회로.

### 청구항 6

제 3 항에 있어서,

상기 구동부는,

상기 풀업부와 상기 풀다운부로부터 공급되는 전원을 인가 받고 상기 입력 클럭을 입력 받는 제 1 인버터; 및

상기 제 1 인버터의 출력 신호를 입력 받아 상기 보정 클럭을 출력하는 제 2 인버터;

를 포함하는 것을 특징으로 하는 데이터 출력 스트로브 신호 생성 회로.

### 청구항 7

제 1 항에 있어서,

상기 듀티 사이클 제어 수단은 내부에 피드백 루프를 구비하여 상기 데이터 출력 스트로브 신호의 듀티비를 판별하고, 그에 따라 복수 개의 신호의 논리값을 증감하여 상기 제어 신호로서 출력하는 것을 특징으로 하는 데이터 출력 스트로브 신호 생성 회로.

### 청구항 8

제 1 항 또는 제 7 항에 있어서,

상기 듀티 사이클 제어 수단은,

상기 데이터 출력 스트로브 신호와 피드백 신호의 위상을 비교하여 위상 비교 신호를 생성하는 위상 비교부;

상기 위상 비교 신호에 응답하여 지연 제어 신호를 생성하는 지연 제어부;

상기 지연 제어 신호에 대응되는 만큼 상기 데이터 출력 스트로브 신호를 지연시키고 이를 반전시켜 상기 피드백 신호로서 출력하는 지연부;

상기 데이터 출력 스트로브 신호와 상기 피드백 신호를 반전시킨 후 그 위상을 비교하여 카운팅 인에이블 신호를 생성하는 듀티비 감지부; 및

상기 카운팅 인에이블 신호에 응답하여 상기 제어 신호를 생성하는 카운터;

를 포함하는 것을 특징으로 하는 데이터 출력 스트로브 신호 생성 회로.

### 청구항 9

제 8 항에 있어서,

상기 위상 비교부는 상기 데이터 출력 스트로브 신호와 상기 피드백 신호 중 어느 신호의 라이징 에지 타임이 앞서는지에 대한 정보를 담는 상기 위상 비교 신호를 출력하는 것을 특징으로 하는 데이터 출력 스트로브 신호 생성 회로.

### 청구항 10

제 8 항에 있어서,

상기 듀티 감지부는 상기 데이터 출력 스트로브 신호와 상기 피드백 신호를 각각 반전시킨 후, 두 신호의 라이징 에지를 비교하여 그 결과에 따라 상기 카운팅 인에이블 신호를 인에이블 시키는 것을 특징으로 하는 데이터 출력 스트로브 신호 생성 회로.

### 청구항 11

제 8 항에 있어서,

상기 카운터는 상기 카운팅 인에이블 신호가 인에이블 되면, 상기 제어 신호에 포함된 신호 중 하이 신호의 개수를 변경시키는 동작을 수행하는 것을 특징으로 하는 데이터 출력 스트로브 신호 생성 회로.

### 청구항 12

외부 클럭보다 소정 시간 앞선 위상을 갖는 DLL 클럭을 생성하는 DLL 회로;

상기 DLL 클럭을 전송하는 전송 라인;

상기 전송 라인으로부터 전달되는 상기 DLL 클럭의 듀티 사이클을 보정하고 이를 이용하여 데이터 출력 스트로브 신호를 생성하는 데이터 출력 스트로브 신호 생성 회로; 및

상기 데이터 출력 스트로브 신호를 입력 받아 출력 데이터를 버퍼링하는 데이터 출력 버퍼;

를 포함하는 것을 특징으로 하는 반도체 메모리 장치.

### 청구항 13

제 12 항에 있어서,

상기 데이터 출력 스트로브 신호 생성 회로는,

상기 DLL 클럭을 분할하여 라이징 클럭과 폴링 클럭을 생성하는 위상 스플리터;

제어 신호의 제어에 따라 상기 라이징 클럭의 듀티비를 보정하여 보정 라이징 클럭을 출력하는 제 1 듀티 사이클 보정 수단;

상기 제어 신호의 제어에 따라 상기 폴링 클럭의 듀티비를 보정하여 보정 폴링 클럭을 출력하는 제 2 듀티 사이클 보정 수단;

데이터 출력 스트로브 신호를 입력 받아 상기 제어 신호를 출력하는 듀티 사이클 제어 수단; 및

상기 보정 라이징 클럭과 상기 보정 폴링 클럭으로부터 상기 데이터 출력 스트로브 신호를 생성하는 데이터 출력 스트로브 신호 생성 수단;

을 포함하는 것을 특징으로 하는 반도체 메모리 장치.

#### **청구항 14**

제 13 항에 있어서,

상기 제어 신호는 복수 개의 신호의 조합으로 이루어지며, 상기 제 1 듀티 사이클 보정 수단 및 상기 제 2 듀티 사이클 보정 수단은 상기 제어 신호에 포함된 신호 중 하이 신호와 로우 신호의 개수에 따라 각각 상기 라이징 클럭 및 상기 폴링 클럭의 하이 구간과 로우 구간의 폭을 조정하는 것을 특징으로 하는 반도체 메모리 장치.

#### **청구항 15**

제 13 항 또는 제 14 항에 있어서,

상기 제 1 듀티 사이클 보정 수단은,

상기 제어 신호의 입력에 대응하여 외부 공급전원의 구동부로의 공급량을 제어하는 풀업부;

상기 제어 신호의 입력에 대응하여 그라운드 전원의 상기 구동부로의 공급량을 제어하는 풀다운부; 및

상기 풀업부와 상기 풀다운부로부터 공급되는 각 전원을 인가 받아 상기 라이징 클럭을 구동하여 상기 보정 라이징 클럭을 출력하는 상기 구동부;

를 포함하는 것을 특징으로 하는 반도체 메모리 장치.

#### **청구항 16**

제 15 항에 있어서,

상기 풀업부는 게이트 단에 상기 제어 신호에 포함된 신호를 각각 입력 받고, 상기 외부 공급전원의 공급단과 상기 구동부 사이에 병렬로 구비되는 복수 개의 트랜지스터를 포함하는 것을 특징으로 하는 반도체 메모리 장치.

#### **청구항 17**

제 15 항에 있어서,

상기 풀다운부는 게이트 단에 상기 제어 신호에 포함된 신호를 각각 입력 받고, 상기 그라운드 전원의 공급단과 상기 구동부 사이에 병렬로 구비되는 복수 개의 트랜지스터를 포함하는 것을 특징으로 하는 반도체 메모리 장치.

#### **청구항 18**

제 15 항에 있어서,

상기 구동부는,

상기 풀업부와 상기 풀다운부로부터 공급되는 전원을 인가 받고 상기 라이징 클럭을 입력 받는 제 1 인버터; 및

상기 제 1 인버터의 출력 신호를 입력 받아 상기 보정 라이징 클럭을 출력하는 제 2 인버터;

를 포함하는 것을 특징으로 하는 반도체 메모리 장치.

### 청구항 19

제 13 항 또는 제 14 항에 있어서,

상기 제 2 듀티 사이클 보정 수단은,

상기 제어 신호의 반전 신호의 입력에 대응하여 외부 공급전원의 구동부로의 공급량을 제어하는 풀업부;

상기 제어 신호의 반전 신호의 입력에 대응하여 그라운드 전원의 상기 구동부로의 공급량을 제어하는 풀다운부;

및

상기 풀업부와 상기 풀다운부로부터 공급되는 각 전원을 인가 받아 상기 폴링 클럭을 구동하여 상기 보정 폴링

클럭을 출력하는 상기 구동부;

를 포함하는 것을 특징으로 하는 반도체 메모리 장치.

### 청구항 20

제 19 항에 있어서,

상기 풀업부는 게이트 단에 상기 제어 신호의 반전 신호에 포함된 신호를 각각 입력 받고, 상기 외부 공급전원

의 공급단과 상기 구동부 사이에 병렬로 구비되는 복수 개의 트랜지스터를 포함하는 것을 특징으로 하는 반도체

메모리 장치.

### 청구항 21

제 19 항에 있어서,

상기 풀다운부는 게이트 단에 상기 제어 신호의 반전 신호에 포함된 신호를 각각 입력 받고, 상기 그라운드 전

원의 공급단과 상기 구동부 사이에 병렬로 구비되는 복수 개의 트랜지스터를 포함하는 것을 특징으로 하는 반도

체 메모리 장치.

### 청구항 22

제 19 항에 있어서,

상기 구동부는,

상기 풀업부와 상기 풀다운부로부터 공급되는 전원을 인가 받고 상기 폴링 클럭을 입력 받는 제 1 인버터; 및

상기 제 1 인버터의 출력 신호를 입력 받아 상기 보정 폴링 클럭을 출력하는 제 2 인버터;

를 포함하는 것을 특징으로 하는 반도체 메모리 장치.

### 청구항 23

제 13 항에 있어서,

상기 듀티 사이클 제어 수단은 내부에 피드백 루프를 구비하여 상기 데이터 출력 스트로브 신호의 듀티비를 판

별하고, 그에 따라 복수 개의 신호의 논리값을 증감하여 상기 제어 신호로서 출력하는 것을 특징으로 하는 반도

체 메모리 장치.

### 청구항 24

제 13 항 또는 제 23 항에 있어서,

상기 듀티 사이클 제어 수단은,

상기 데이터 출력 스트로브 신호와 피드백 신호의 위상을 비교하여 위상 비교 신호를 생성하는 위상 비교부;

상기 위상 비교 신호에 응답하여 지연 제어 신호를 생성하는 지연 제어부;

상기 지연 제어 신호에 대응되는 만큼 상기 데이터 출력 스트로브 신호를 지연시키고 이를 반전시켜 상기 피드백 신호로서 출력하는 지연부;

상기 데이터 출력 스트로브 신호와 상기 피드백 신호를 반전시킨 후 그 위상을 비교하여 카운팅 인에이블 신호를 생성하는 듀티비 감지부; 및

상기 카운팅 인에이블 신호에 응답하여 상기 제어 신호를 생성하는 카운터;

를 포함하는 것을 특징으로 하는 반도체 메모리 장치.

### 청구항 25

제 24 항에 있어서,

상기 위상 제어부는 상기 데이터 출력 스트로브 신호와 상기 피드백 신호 중 어느 신호의 라이징 에지 타임이 앞서는지에 대한 정보를 담는 상기 위상 비교 신호를 출력하는 것을 특징으로 하는 반도체 메모리 장치.

### 청구항 26

제 24 항에 있어서,

상기 듀티 감지부는 상기 데이터 출력 스트로브 신호와 상기 피드백 신호를 각각 반전시킨 후, 두 신호의 라이징 에지를 비교하여 그 결과에 따라 상기 카운팅 인에이블 신호를 인에이블 시키는 것을 특징으로 하는 반도체 메모리 장치.

### 청구항 27

제 24 항에 있어서,

상기 카운터는 상기 카운팅 인에이블 신호가 인에이블 되면, 상기 제어 신호에 포함된 신호 중 하이 신호의 개수를 변경시키는 동작을 수행하는 것을 특징으로 하는 반도체 메모리 장치.

### 청구항 28

a) 제어 신호의 제어에 따라 입력 클럭의 듀티비를 보정하여 보정 클럭을 출력하는 단계;

b) 데이터 출력 스트로브 신호를 입력 받아 상기 제어 신호를 출력하는 단계; 및

c) 상기 보정 클럭으로부터 상기 데이터 출력 스트로브 신호를 생성하는 단계;

를 포함하는 것을 특징으로 하는 데이터 출력 스트로브 신호 생성 방법.

### 청구항 29

제 28 항에 있어서,

상기 제어 신호는 복수 개의 신호의 조합으로 이루어지며, 상기 a) 단계는 상기 제어 신호에 포함된 신호 중 하이 신호와 로우 신호의 개수에 따라 상기 입력 클럭의 듀티비를 보정하는 단계인 것을 특징으로 하는 데이터 출력 스트로브 신호 생성 방법.

### 청구항 30

제 28 항에 있어서,

상기 b) 단계는 내부의 피드백 루프를 이용하여 상기 데이터 출력 스트로브 신호의 인에이블 타이밍을 판별하고, 그에 따라 복수 개의 신호의 논리값을 증감하여 상기 제어 신호로서 출력하는 단계인 것을 특징으로 하는 데이터 출력 스트로브 신호 생성 방법.

### 청구항 31

제 28 또는 제 30 항에 있어서,

상기 b) 단계는,

- b-1) 상기 데이터 출력 스트로브 신호와 피드백 신호의 위상을 비교하여 위상 비교 신호를 생성하는 단계;

- b-2) 상기 위상 비교 신호에 응답하여 지연 제어 신호를 생성하는 단계;

- b-3) 상기 지연 제어 신호에 대응되는 만큼 상기 데이터 출력 스트로브 신호를 지연시키고 이를 반전시켜 상기 피드백 신호로서 출력하는 단계;

- b-4) 상기 데이터 출력 스트로브 신호와 상기 피드백 신호를 반전시킨 후 그 위상을 비교하여 카운팅 인에이블 신호를 생성하는 단계; 및

- b-5) 상기 카운팅 인에이블 신호에 응답하여 상기 제어 신호를 생성하는 단계;

- 를 포함하는 것을 특징으로 하는 데이터 출력 스트로브 신호 생성 방법.

### 청구항 32

제 31 항에 있어서,

상기 b-1) 단계는 상기 데이터 출력 스트로브 신호와 상기 피드백 신호 중 어느 신호의 라이징 에지 타임이 앞서는지에 대한 정보를 담는 상기 위상 비교 신호를 출력하는 단계인 것을 특징으로 하는 데이터 출력 스트로브 신호 생성 방법.

### 청구항 33

제 31 항에 있어서,

상기 b-4) 단계는, 상기 데이터 출력 스트로브 신호와 상기 피드백 신호를 각각 반전시킨 후, 두 신호의 라이징 에지를 비교하여 그 결과에 따라 상기 카운팅 인에이블 신호를 인에이블 시키는 단계인 것을 특징으로 하는 데이터 출력 스트로브 신호 생성 방법.

### 청구항 34

제 31 항에 있어서,

상기 b-5) 단계는, 상기 카운팅 인에이블 신호가 인에이블 되면, 상기 제어 신호에 포함된 신호 중 하이 신호의 개수를 변경시키는 동작을 수행하는 단계인 것을 특징으로 하는 데이터 출력 스트로브 신호 생성 방법.

### 청구항 35

- a) 외부 클럭보다 소정 시간 앞선 위상을 갖는 DLL 클럭을 생성하는 단계;

- b) 상기 DLL 클럭을 전송하는 단계;

- c) 상기 b) 단계로부터 전달되는 상기 DLL 클럭의 듀티 사이클을 보정하고 이를 이용하여 데이터 출력 스트로브 신호를 생성하는 단계; 및

- d) 상기 데이터 출력 스트로브 신호를 입력 받아 출력 데이터를 버퍼링하는 단계;

- 를 포함하는 것을 특징으로 하는 반도체 메모리 장치의 제어 방법.

### 청구항 36

제 35 항에 있어서,

상기 c) 단계는,

- c-1) 상기 DLL 클럭을 분할하여 라이징 클럭과 폴링 클럭을 생성하는 단계;

- c-2) 제어 신호의 제어에 따라 상기 라이징 클럭의 듀티비를 보정하여 보정 라이징 클럭을 출력하는 단계;

- c-3) 상기 제어 신호의 제어에 따라 상기 폴링 클럭의 듀티비를 보정하여 보정 폴링 클럭을 출력하는 단계;

- c-4) 데이터 출력 스트로브 신호를 입력 받아 상기 제어 신호를 출력하는 단계; 및

- c-5) 상기 보정 라이징 클럭과 상기 보정 폴링 클럭으로부터 상기 데이터 출력 스트로브 신호를 생성하는 단계;

를 포함하는 것을 특징으로 하는 반도체 메모리 장치의 제어 방법.

### 청구항 37

제 33 항에 있어서,

상기 제어 신호는 복수 개의 신호의 조합으로 이루어지며, 상기 c-2) 단계 및 상기 c-3) 단계는 상기 제어 신호에 포함된 신호 중 하이 신호와 로우 신호의 개수에 따라 각각 상기 라이징 클럭 및 상기 폴링 클럭의 하이 구간과 로우 구간의 폭을 조정하는 것을 특징으로 하는 반도체 메모리 장치의 제어 방법.

### 청구항 38

제 33 항에 있어서,

상기 c-4) 단계는 내부의 피드백 루프를 이용하여 상기 데이터 출력 스트로브 신호의 드티비를 판별하고, 그에 따라 복수 개의 신호의 논리값을 증감하여 상기 제어 신호로서 출력하는 단계인 것을 특징으로 하는 반도체 메모리 장치의 제어 방법.

### 청구항 39

제 36 항 또는 제 38 항에 있어서,

상기 c-4) 단계는,

- c-4-가) 상기 데이터 출력 스트로브 신호와 피드백 신호의 위상을 비교하여 위상 비교 신호를 생성하는 단계;

- c-4-나) 상기 위상 비교 신호에 응답하여 지연 제어 신호를 생성하는 단계;

- c-4-다) 상기 지연 제어 신호에 대응되는 만큼 상기 데이터 출력 스트로브 신호를 지연시키고 이를 반전시켜 상기 피드백 신호로서 출력하는 단계;

- c-4-라) 상기 데이터 출력 스트로브 신호와 상기 피드백 신호를 반전시킨 후 그 위상을 비교하여 카운팅 인에이블 신호를 생성하는 단계; 및

- c-4-마) 상기 카운팅 인에이블 신호에 응답하여 상기 제어 신호를 생성하는 단계;

를 포함하는 것을 특징으로 하는 반도체 메모리 장치의 제어 방법.

### 청구항 40

제 39 항에 있어서,

상기 c-4-가) 단계는 상기 데이터 출력 스트로브 신호와 상기 피드백 신호 중 어느 신호의 라이징 에지 타임이 앞서는지에 대한 정보를 담는 상기 위상 비교 신호를 출력하는 단계인 것을 특징으로 하는 반도체 메모리 장치의 제어 방법.

### 청구항 41

제 39 항에 있어서,

상기 c-4-라) 단계는, 상기 데이터 출력 스트로브 신호와 상기 피드백 신호를 각각 반전시킨 후, 두 신호의 라이징 에지를 비교하여 그 결과에 따라 상기 카운팅 인에이블 신호를 인에이블 시키는 단계인 것을 특징으로 하는 반도체 메모리 장치의 제어 방법.

### 청구항 42

제 39 항에 있어서,

상기 c-4-마) 단계는, 상기 카운팅 인에이블 신호가 인에이블 되면, 상기 제어 신호에 포함된 신호 중 하이 신호의 개수를 변경시키는 동작을 수행하는 단계인 것을 특징으로 하는 반도체 메모리 장치의 제어 방법.

## 명세서

## 발명의 상세한 설명

### 발명의 목적

#### 발명이 속하는 기술 및 그 분야의 종래기술

- <11> 본 발명은 데이터 출력 스트로브 신호 생성 회로 및 이를 포함하는 반도체 메모리 장치에 관한 것으로, 보다 상세하게는 보다 정확한 타이밍의 데이터 출력 스트로브 신호를 생성하는 데이터 출력 스트로브 신호 생성 회로 및 이를 포함하는 반도체 메모리 장치에 관한 것이다.

- <12> 일반적으로 반도체 메모리 장치는 데이터 출력 동작을 위해 데이터 출력 버퍼를 구비한다. 그리고 데이터 출력 버퍼는 글로벌 입출력 라인을 통해 전달되는 데이터를 데이터 출력 스트로브 신호에 동기시켜 출력하는 기능을 수행한다. 데이터 출력 스트로브 신호는 DLL(Delay Locked Loop) 클럭의 라이징 에지 타임에 하이(High) 구간을 갖는 클럭(이하, 라이징 클럭) 또는 DLL 클럭의 폴링 에지 타임에 하이 구간을 갖는 클럭(이하, 폴링 클럭)으로부터 생성되며, 이와 같은 기능을 위해 데이터 출력 스트로브 신호 생성 회로가 구비된다.

- <13> 일반적으로 DLL 회로는 반도체 메모리 장치의 내부에 존재하는 지연 소자들의 지연값을 보상하기 위해 외부 클럭보다 소정 시간 앞선 위상을 갖는 DLL 클럭을 생성하고, 이를 라이징 클럭과 폴링 클럭으로 분할한 후, 각각의 드ュ티비를 50:50으로 조정하는 동작을 수행한다. 따라서 이상적으로는 데이터 출력 스트로브 신호 생성 회로에 전달되는 라이징 클럭과 폴링 클럭 각각의 드ュ티비에 변함이 없어야 하나, 클럭의 전송 라인에 존재하는 저항 및 노이즈 등의 영향으로 실제로는 각 드ュ티비가 변화하게 된다. 이처럼 라이징 클럭과 폴링 클럭 각각의 드ュ티비가 50:50이 아닌 상황에서 데이터 출력 스트로브 신호를 생성하게 되면, 데이터 출력 스트로브 신호의 인에이블 구간이 변화하게 되어 데이터 출력 버퍼의 동작을 정확히 제어할 수 없게 되며, 심할 경우 데이터 출력 동작이 수행되지 않는 오동작이 발생할 수 있다.

- <14> 그러나 종래의 기술에 따른 반도체 메모리 장치의 데이터 출력 스트로브 신호 생성 회로는 드ュ티비가 정확히 일치하지 않는 라이징 클럭과 폴링 클럭으로부터 데이터 출력 스트로브 신호를 생성하여 왔으며, 이에 따라 정확한 인에이블 구간을 갖는 데이터 출력 스트로브 신호를 출력하지 못하였다. 따라서 반도체 메모리 장치는 데이터 출력 오동작에 무방비로 노출되어 정확한 데이터 출력 동작을 담보하지 못하였고, 반도체 메모리 장치의 데이터 출력 동작의 신뢰도는 저하되었다.

#### 발명이 이루고자 하는 기술적 과제

- <15> 본 발명은 상술한 문제점을 해결하기 위하여 안출된 것으로서, 데이터 출력 동작의 신뢰도를 향상시키는 데이터 출력 스트로브 신호 생성 회로 및 이를 포함하는 반도체 메모리 장치를 제공하는 데에 그 기술적 과제가 있다.

- <16> 또한, 본 발명은 보다 정확한 인에이블 구간을 갖는 데이터 출력 스트로브 신호를 생성하는 데이터 출력 스트로브 신호 생성 회로 및 이를 포함하는 반도체 메모리 장치를 제공하는 데에 다른 기술적 과제가 있다.

### 발명의 구성 및 작용

- <17> 상술한 기술적 과제를 달성하기 위한 본 발명의 일 실시예에 따른 데이터 출력 스트로브 신호 생성 회로는, 제어 신호의 제어에 따라 입력 클럭의 드ュ티비를 보정하여 보정 클럭을 출력하는 드ュ티 사이클 보정 수단; 데이터 출력 스트로브 신호를 입력 받아 상기 제어 신호를 출력하는 드ュ티 사이클 제어 수단; 및 상기 보정 클럭으로부터 상기 데이터 출력 스트로브 신호를 생성하는 데이터 출력 스트로브 신호 생성 수단;을 포함하는 것을 특징으로 한다.

- <18> 그리고 본 발명에 따른 반도체 메모리 장치는, 외부 클럭보다 소정 시간 앞선 위상을 갖는 DLL 클럭을 생성하는 DLL 회로; 상기 DLL 클럭을 전송하는 전송 라인; 상기 전송 라인으로부터 전달되는 상기 DLL 클럭의 드ュ티 사이클을 보정하고 이를 이용하여 데이터 출력 스트로브 신호를 생성하는 데이터 출력 스트로브 신호 생성 회로; 및 상기 데이터 출력 스트로브 신호를 입력 받아 출력 데이터를 버퍼링하는 데이터 출력 버퍼;를 포함하는 것을 특징으로 한다.

- <19> 또한 본 발명의 일 실시예에 따른 데이터 출력 스트로브 신호 생성 방법은, a) 제어 신호의 제어에 따라 입력 클럭의 드ュ티비를 보정하여 보정 클럭을 출력하는 단계; b) 데이터 출력 스트로브 신호를 입력 받아 상기 제어 신호를 출력하는 단계; 및 c) 상기 보정 클럭으로부터 상기 데이터 출력 스트로브 신호를 생성하는 단계;를 포함하는 것을 특징으로 한다.

함하는 것을 특징으로 한다.

- <20> 그리고 본 발명에 따른 반도체 메모리 장치의 제어 방법은, a) 외부 클럭보다 소정 시간 앞선 위상을 갖는 DLL 클럭을 생성하는 단계; b) 상기 DLL 클럭을 전송하는 단계; c) 상기 b) 단계로부터 전달되는 상기 DLL 클럭의 둑티 사이클을 보정하고 이를 이용하여 데이터 출력 스트로브 신호를 생성하는 단계; 및 d) 상기 데이터 출력 스트로브 신호를 입력 받아 출력 데이터를 버퍼링하는 단계;를 포함하는 것을 특징으로 한다.

- <21> 이하에서는 첨부된 도면을 참조하여 본 발명의 바람직한 실시예를 보다 상세히 설명하기로 한다.

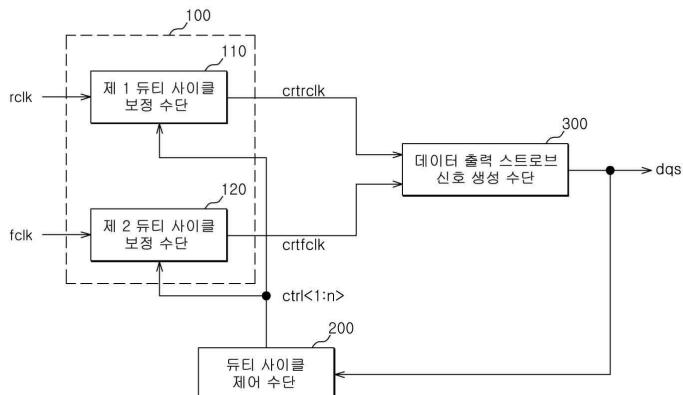

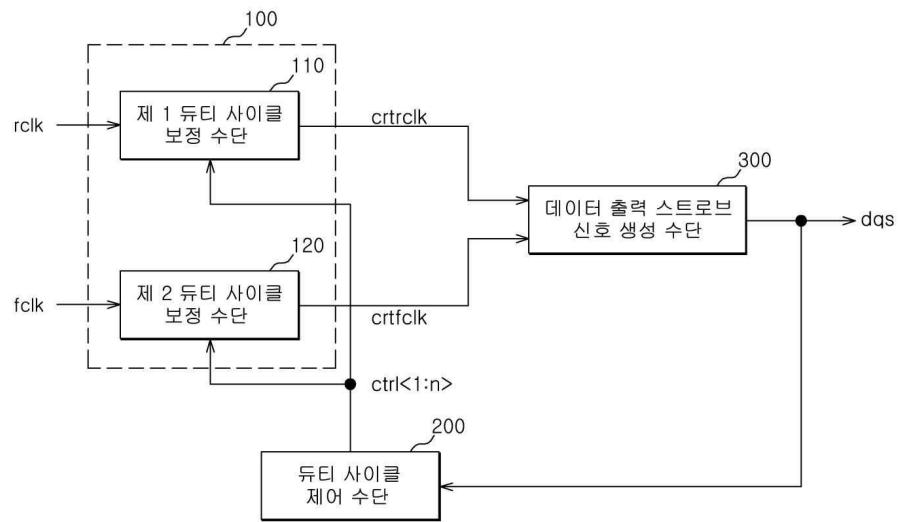

- <22> 도 1은 본 발명의 일 실시예에 따른 데이터 출력 스트로브 신호 생성 회로의 구성을 나타낸 블록도이다.

- <23> 도시한 바와 같이, 상기 데이터 출력 스트로브 신호 생성 회로는, n 개의 제어 신호( $ctrl<1:n>$ )의 제어에 따라 라이징 클럭(rclk)과 폴링 클럭(fclk)의 둑티비를 보정하여 보정 라이징 클럭(crtclk) 및 보정 폴링 클럭(crtfclk)을 출력하는 둑티 사이클을 보정 수단(100), 데이터 출력 스트로브 신호(dqs)를 입력 받아 상기 n 개의 제어 신호를 출력하는 둑티 사이클 제어 수단(200) 및 상기 보정 라이징 클럭(crtclk)과 상기 보정 폴링 클럭(crtfclk)으로부터 상기 데이터 출력 스트로브 신호(dqs)를 생성하는 데이터 출력 스트로브 신호 생성 수단(300)을 포함한다.

- <24> 여기에서 상기 둑티 사이클 보정 수단(100)은 상기 n 개의 제어 신호( $ctrl<1:n>$ )의 제어에 따라 상기 라이징 클럭(rclk)의 둑티비를 보정하여 상기 보정 라이징 클럭(crtclk)을 출력하는 제 1 둑티 사이클 보정 수단(110) 및 상기 n 개의 제어 신호( $ctrl<1:n>$ )의 제어에 따라 상기 폴링 클럭(fclk)의 둑티비를 보정하여 상기 보정 폴링 클럭(crtfclk)을 출력하는 제 2 둑티 사이클 보정 수단(120)을 포함한다.

- <25> 상기 제 1 둑티 사이클 보정 수단(110)과 상기 제 2 둑티 사이클 보정 수단(120)은 상기 n 개의 제어 신호( $ctrl<1:n>$ )에 포함된 신호 중 하이(High) 신호와 로우(Low) 신호의 개수에 따라 각각 상기 라이징 클럭(rclk)과 상기 폴링 클럭(fclk)의 둑티비를 제어한다. 예를 들어, 상기 n 개의 제어 신호( $ctrl<1:n>$ ) 중 하이 신호의 개수가 증가할수록 상기 제 1 둑티 사이클 보정 수단(110)은 상기 라이징 클럭(rclk)의 하이 구간을 넓히고 로우 구간을 좁히는 동작을 수행하고, 상기 제 2 둑티 사이클 보정 수단(120)은 상기 폴링 클럭(fclk)의 로우 구간을 넓히고 하이 구간을 좁히는 동작을 수행한다. 마찬가지로, 상기 n 개의 제어 신호( $ctrl<1:n>$ ) 중 로우 신호의 개수가 증가할수록 상기 제 1 둑티 사이클 보정 수단(110)은 상기 라이징 클럭(rclk)의 로우 구간을 넓히고 하이 구간을 좁히는 동작을 수행하고, 상기 제 2 둑티 사이클 보정 수단(120)은 상기 폴링 클럭(fclk)의 하이 구간을 넓히고 로우 구간을 좁히는 동작을 수행한다.

- <26> 상기 둑티 사이클 제어 수단(200)은 내부에 피드백 루프를 구비하여 상기 데이터 출력 스트로브 신호(dqs)의 둑티비를 관별하고, 그에 따라 상기 n 개의 제어 신호( $ctrl<1:n>$ )를 생성한다. 상기 데이터 출력 스트로브 신호(dqs)의 둑티비는 상기 보정 라이징 클럭(crtclk) 또는 상기 보정 폴링 클럭(crtfclk)의 영향을 받으므로, 상기 보정 라이징 클럭(crtclk)과 상기 보정 폴링 클럭(crtfclk) 각각의 둑티비가 50:50으로 정확히 일치되지 않은 상태에서는 상기 데이터 출력 스트로브 신호(dqs) 또한 둑티비가 일치되지 않는다. 따라서 상기 데이터 출력 스트로브 신호(dqs)의 둑티비를 관별함과 동시에 상기 n 개의 제어 신호( $ctrl<1:n>$ )를 생성하는 동작을 수행하면, 상기 n 개의 제어 신호( $ctrl<1:n>$ )의 제어에 따라 상기 제 1 둑티 사이클 보정 수단(110)에서 출력되는 상기 보정 라이징 클럭(crtclk)과 상기 제 2 둑티 사이클 보정 수단(120)에서 출력되는 상기 보정 폴링 클럭(crtfclk)의 둑티비가 일치되는 효과를 얻을 수 있게 된다.

- <27> 이와 같은 상기 둑티 사이클 제어 수단(200)의 동작은 이후 첨부된 도 3을 통해 보다 상세히 설명하기로 한다.

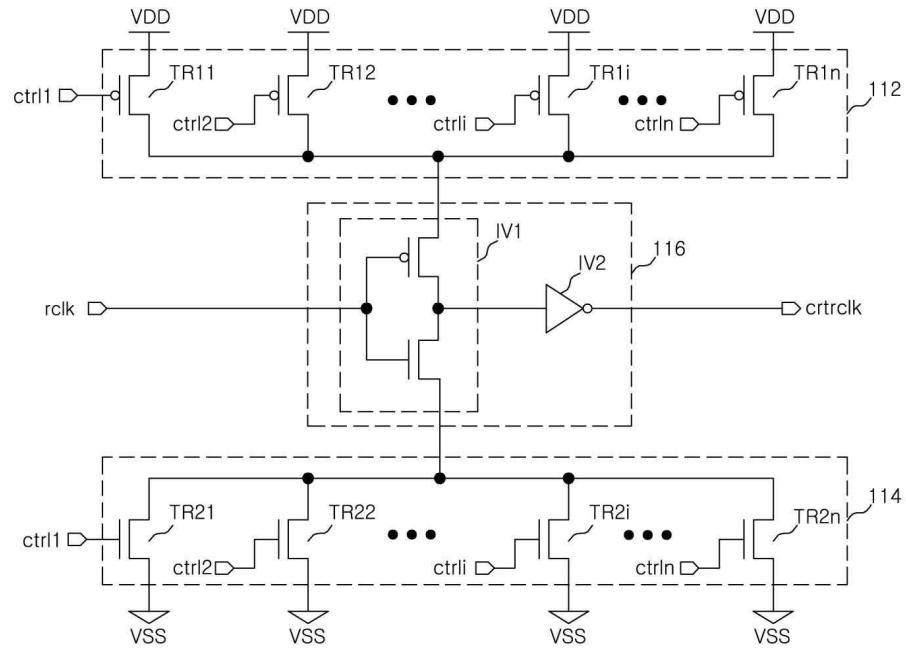

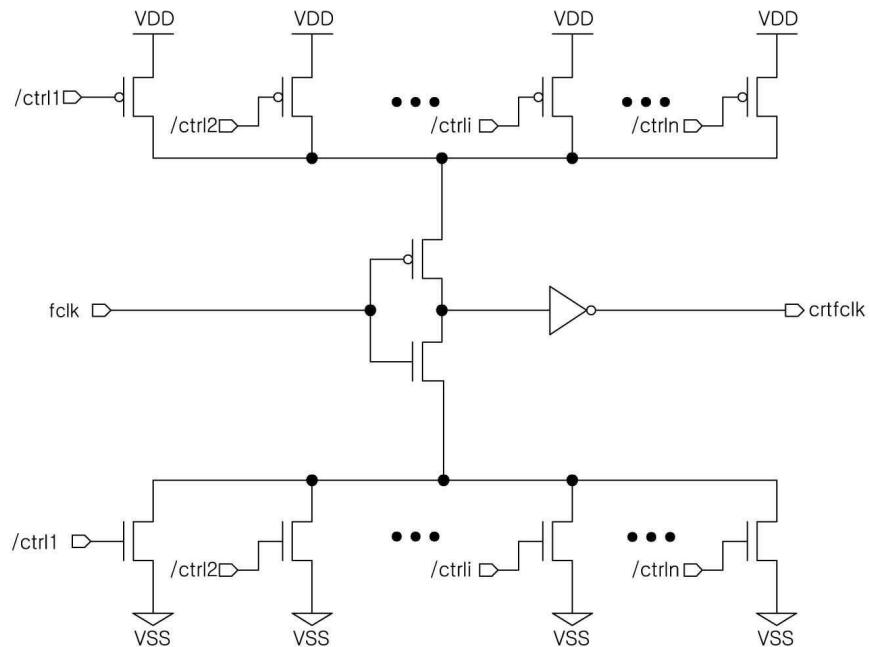

- <28> 도 2a는 도 1에 도시한 제 1 둑티 사이클 보정 수단의 상세 구성도이고, 도 2b는 도 1에 도시한 제 2 둑티 사이클 보정 수단의 상세 구성도이다.

- <29> 도시한 바와 같이, 상기 제 1 둑티 사이클 보정 수단(110)은 상기 n 개의 제어 신호( $ctrl<1:n>$ )의 입력에 대응하여 외부 공급전원(VDD)의 구동부(116)로의 공급량을 제어하는 풀업부(112), 상기 n 개의 제어 신호( $ctrl<1:n>$ )의 입력에 대응하여 그라운드 전원(VSS)의 상기 구동부(116)로의 공급량을 제어하는 풀다운부(114) 및 상기 풀업부(112)와 상기 풀다운부(114)로부터 공급되는 각 전원을 인가 받아 상기 라이징 클럭(rclk)을 구동하여 상기 보정 라이징 클럭(crtclk)을 출력하는 상기 구동부(116)를 포함한다.

- <30> 여기에서 상기 풀업부(112)는 게이트 단에 상기 n 개의 제어 신호( $ctrl<1:n>$ )를 각각 입력 받고, 상기 외부 공급전원(VDD)의 공급단과 상기 구동부(116) 사이에 병렬로 구비되는 n 개의 제 1 트랜지스터( $TR1<1:n>$ )를 포함한다.

- <31> 그리고 상기 풀다운부(114)는 계이트 단에 상기 n 개의 제어 신호( $ctrl<1:n>$ )를 각각 입력 받고, 상기 그라운드 전원(VSS)의 공급단과 상기 구동부(116) 사이에 병렬로 구비되는 n 개의 제 2 트랜지스터(TR2<1:n>)를 포함한다.

- <32> 상기 구동부(116)는 상기 풀업부(112)와 상기 풀다운부(114)로부터 공급되는 전원을 인가 받고 상기 라이징 클럭(rclk)을 입력 받는 제 1 인버터(IV1) 및 상기 제 1 인버터(IV1)의 출력 신호를 입력 받아 상기 보정 라이징 클럭(crtrclk)을 출력하는 제 2 인버터(IV2)를 포함한다.

- <33> 이와 같은 구성에 의해 상기 구동부(116)에 입력되는 상기 라이징 클럭(rclk)에 대한 듀티비 보정 동작이 수행된다. 즉, 상기 n 개의 제어 신호( $ctrl<1:n>$ ) 중 로우 신호의 개수가 증가하면 상기 풀업부(112)가 상기 구동부(116)의 상기 제 1 인버터(IV1)에 공급하는 전원의 양이 증가하게 되고, 그에 따라 상기 제 1 인버터(IV1)의 출력 신호의 하이 레벨 구간이 넓어지게 된다. 이후 상기 보정 라이징 클럭(crtrclk)은 상기 제 2 인버터(IV2)에 의해 반전되어 출력되므로 로우 레벨 구간이 넓어지게 된다.

- <34> 반면에, 상기 n 개의 제어 신호( $ctrl<1:n>$ ) 중 하이 신호의 개수가 증가하면 상기 풀다운부(114)가 상기 구동부(116)의 상기 제 1 인버터(IV1)에 공급하는 전원의 양이 증가하게 되고, 그에 따라 상기 제 1 인버터(IV1)의 출력 신호의 로우 레벨 구간이 넓어지게 된다. 이후 상기 보정 라이징 클럭(crtrclk)은 상기 제 2 인버터(IV2)에 의해 반전되어 출력되므로 하이 레벨 구간이 넓어지게 되는 것이다.

- <35> 상기 제 2 듀티 사이클 보정 수단(120) 또한 상기 제 1 듀티 사이클 보정 수단(110)과 같은 구조로 구성되나, 상기 라이징 클럭(rclk) 대신 상기 폴링 클럭(fclk)을 입력 받고, 상기 n 개의 제어 신호( $ctrl<1:n>$ )의 반전된 신호(/ $ctrl<1:n>$ )의 제어에 따라 동작하며, 상기 보정 라이징 클럭(crtrclk) 대신 상기 보정 폴링 클럭(crtfclk)을 출력한다는 점이 상이할 뿐이다.

- <36> 따라서, 상기 n 개의 제어 신호( $ctrl<1:n>$ ) 중 로우 신호의 개수가 증가하면 그 반전된 신호(/ $ctrl<1:n>$ )를 이용하므로 상기 보정 폴링 클럭(crtfclk)의 하이 레벨 구간이 넓어지게 되고, 상기 n 개의 제어 신호( $ctrl<1:n>$ ) 중 하이 신호의 개수가 증가하면 상기 보정 폴링 클럭(crtfclk)의 로우 레벨 구간이 넓어지게 된다.

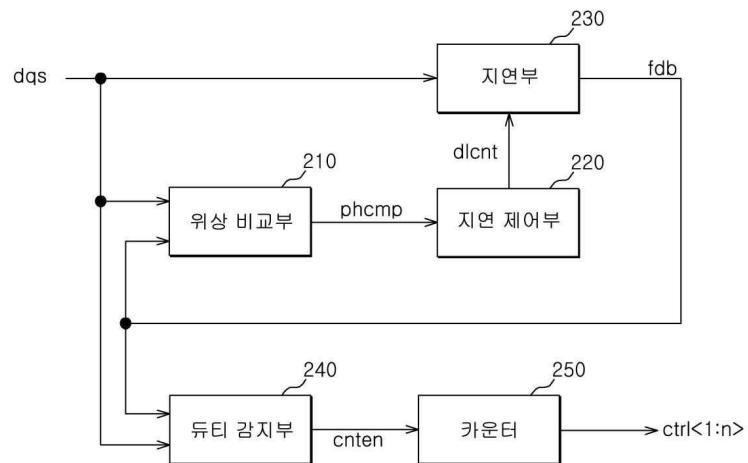

- <37> 도 3은 도 1에 도시한 듀티 사이클 제어 수단의 상세 구성도이다.

- <38> 상기 듀티 사이클 제어 수단(200)은 상기 데이터 출력 스트로브 신호(dqs)와 피드백 신호fdb)의 위상을 비교하여 위상 비교 신호(phcmp)를 생성하는 위상 비교부(210), 상기 위상 비교 신호(phcmp)에 응답하여 지연 제어 신호(dlcnt)를 생성하는 지연 제어부(220), 상기 지연 제어 신호(dlcnt)에 대응되는 만큼 상기 데이터 출력 스트로브 신호(dqs)를 지연시키고 이를 반전시켜 상기 피드백 신호(fdb)로서 출력하는 지연부(230), 상기 데이터 출력 스트로브 신호(dqs)와 상기 피드백 신호(fdb)를 반전시킨 후 그 위상을 비교하여 카운팅 인에이블 신호(cnten)를 생성하는 듀티 감지부(240) 및 상기 카운팅 인에이블 신호(cnten)에 응답하여 상기 n 개의 제어 신호( $ctrl<1:n>$ )를 생성하는 카운터(250)를 포함한다.

- <39> 상기 라이징 클럭(rclk)과 상기 폴링 클럭(fclk)의 듀티비가 각각 50:50으로 일치되지 않으면 상기 데이터 출력 스트로브 신호(dqs)의 듀티비 또한 일치하지 않게 된다. 상기 위상 비교부(210)는 이와 같은 데이터 출력 스트로브 신호(dqs)와 이로부터 지연 및 반전된 상기 피드백 신호(fdb)의 위상을 비교하여 두 신호 중 어느 신호의 라이징 에지 타임이 앞서는지에 대한 정보를 담는 상기 위상 비교 신호(phcmp)를 출력한다. 이후 상기 위상 비교 신호(phcmp)가 인에이블 되면 상기 지연 제어부(220)와 상기 지연부(230)는 상기 데이터 출력 스트로브 신호(dqs)에 조정의 지연 시간을 부여한다.

- <40> 이후 상기 듀티 감지부(240)는 상기 데이터 출력 스트로브 신호(dqs)와 상기 피드백 신호(fdb)를 입력 받아 이를 각각 반전시킨 후 두 신호의 위상을 비교하는 동작을 수행한다. 상기 지연 제어부(220)와 상기 지연부(230)에 의해 상기 데이터 출력 스트로브 신호(dqs)와 상기 피드백 신호(fdb) 각각의 라이징 에지는 점점 일치되어 가게 된다. 따라서 상기 듀티 감지부(240)에는 상기 데이터 출력 스트로브 신호(dqs)와 상기 피드백 신호(fdb)를 반전되어 입력되므로 상기 듀티 감지부(240)에 입력된 두 신호는 그 폴링 에지가 일치되어 가게 된다. 이후, 상기 듀티 감지부(240)는 두 신호의 라이징 에지를 비교하여 그 결과에 따라 상기 카운팅 인에이블 신호(cnten)를 인에이블 시키고, 이에 따라 상기 카운터(250)는 반전된 상기 데이터 출력 스트로브 신호(dqs)의 라이징 에지와 반전된 상기 피드백 신호(fdb)의 라이징 에지가 일치될 때까지 상기 n 개의 제어 신호( $ctrl<1:n>$ )의 논리값을 변경한다. 이와 같은 동작에 의해 결과적으로 상기 데이터 출력 스트로브 신호(dqs)와 상기 피드백 신호(fdb)의 듀티비가 점점 일치되어 가게 되고, 상기 보정 라이징 클럭(crtrclk)과 상기 보정 폴링 클럭(crtfclk)의 듀티비가 일치되어 감에 따라, 상기 데이터 출력 스트로브 신호(dqs)의 듀티비가 보정되는 결과가 발생한다.

- <41> 테스트 모드를 통해 상기 드티 사이클 제어 수단(200)의 동작을 바람직하게 구현할 수 있다. 즉, 테스트 모드를 통해 상기 데이터 출력 스트로브 신호(dqs)를 상기 라이징 클럭(rclk) 또는 상기 폴링 클럭(fclk)과 같은 과정으로 만들고, 이후 이를 상기 드티 사이클 제어 수단(200)에 입력하여 상기 n 개의 제어 신호(ctrl<1:n>)의 조합을 추출할 수 있다. 이 때 생성된 상기 n 개의 제어 신호(ctrl<1:n>)를 퓨즈 회로 등을 이용하여 고정시킨 후, 이를 상기 제 1 드티 사이클 보정 수단(110)과 상기 제 2 드티 사이클 보정 수단(120)에 제공함으로써, 상기 보정 라이징 클럭(crt rclk)과 상기 보정 폴링 클럭(crt fclk)의 드티비를 제어할 수도 있다.

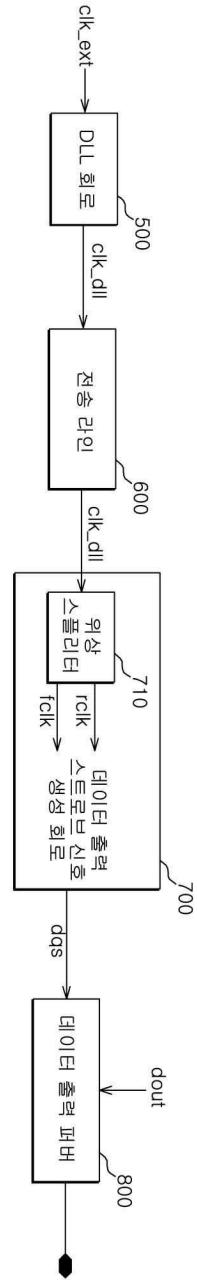

- <42> 도 4는 본 발명에 따른 반도체 메모리 장치의 구성을 나타낸 블록도이다.

- <43> 도시한 바와 같이, 본 발명의 반도체 메모리 장치는, 외부 클럭(clk\_ext)보다 소정 시간 앞선 위상을 갖는 DLL 클럭(clk\_d11)을 생성하는 DLL 회로(500), 상기 DLL 클럭(clk\_d11)을 전송하는 전송 라인(600), 상기 전송 라인(600)으로부터 전달되는 상기 DLL 클럭(clk\_d11)의 드티 사이클을 보정하고 이를 이용하여 데이터 출력 스트로브 신호(dqs)를 생성하는 데이터 출력 스트로브 신호 생성 회로(700) 및 상기 데이터 출력 스트로브 신호(dqs)를 입력 받아 출력 데이터(dout)를 버퍼링하는 데이터 출력 버퍼(800)를 포함한다.

- <44> 여기에서, 상기 데이터 출력 스트로브 신호 생성 회로(700)에는 드티 사이클이 보정되지 않은 상기 DLL 클럭(clk\_d11)을 직접 입력 받고 이를 분할하여 라이징 클럭(rclk)과 폴링 클럭(fclk)을 생성하는 위상 스플리터(710)가 포함된다. 상기 위상 스플리터(710)에서 출력되는 상기 라이징 클럭(rclk)과 상기 폴링 클럭(fclk)의 드티비를 보정하여 상기 데이터 출력 스트로브 신호(dqs)를 생성하는 구성 및 방법은 도 1에 도시한 실시예를 통해 설명된 바와 같다.

- <45> 도 1에 도시한 실시예에서의 데이터 출력 스트로브 신호 생성 회로에서는 상기 라이징 클럭(rclk)과 상기 폴링 클럭(fclk)이 정확히 반전된 형태로 전달되지 않을 수도 있다. 그러나 도 4에 도시한 실시예에서의 데이터 출력 스트로브 신호 생성 회로에서는 상기 위상 스플리터(50)가 구비됨에 따라 상기 라이징 클럭(rclk)과 상기 폴링 클럭(fclk)이 정확히 반전된 형태를 갖게 되므로, 상기 라이징 클럭(rclk)과 상기 폴링 클럭(fclk)에 대한 드티 사이클 보정 동작의 신뢰도를 보다 향상시킬 수 있게 된다.

- <46> 상술한 바와 같이, 본 발명에 따른 반도체 메모리 장치의 데이터 출력 스트로브 신호 생성 회로는 데이터 출력 스트로브 신호의 드티비를 판별하여 그에 따른 제어 신호를 생성하고, 이에 따라 라이징 클럭과 폴링 클럭 각각에 대한 드티 사이클 보정 동작을 수행하므로, 보다 정확한 인에이블 구간을 갖는 데이터 출력 스트로브 신호를 생성할 수 있다. 즉, 드티비가 50:50으로 정확히 일치하는 라이징 클럭과 폴링 클럭을 이용하여 데이터 출력 스트로브 신호를 생성하므로, 데이터 출력 동작시의 오동작의 가능성은 감소하게 되며, 이에 따라 반도체 메모리 장치의 데이터 출력 동작의 신뢰도가 향상된다.

- <47> 이와 같이, 본 발명이 속하는 기술분야의 당업자는 본 발명이 그 기술적 사상이나 필수적 특징을 변경하지 않고서 다른 구체적인 형태로 실시될 수 있다는 것을 이해할 수 있을 것이다. 그러므로 이상에서 기술한 실시예들은 모든 면에서 예시적인 것이며 한정적인 것이 아닌 것으로서 이해해야만 한다. 본 발명의 범위는 상기 상세한 설명보다는 후술하는 특허청구범위에 의하여 나타내어지며, 특허청구범위의 의미 및 범위 그리고 그 등가개념으로부터 도출되는 모든 변경 또는 변형된 형태가 본 발명의 범위에 포함되는 것으로 해석되어야 한다.

### 발명의 효과

- <48> 이상에서 설명한 본 발명의 데이터 출력 스트로브 신호 생성 회로 및 이를 포함하는 반도체 메모리 장치는, 입력 클럭의 드티비를 조정하고 이에 따라 보다 정확한 드티비를 갖는 보정 클럭을 이용하여 데이터 출력 스트로브 신호를 생성함으로써 데이터 출력 동작의 신뢰도를 향상시키는 효과가 있다.

- <49> 아울러, 본 발명의 데이터 출력 스트로브 신호 생성 회로 및 이를 포함하는 반도체 메모리 장치는, DLL 클럭을 분할하여 라이징 클럭과 폴링 클럭을 생성하고, 각각의 드티비를 조정한 후 그로부터 데이터 출력 스트로브 신호를 생성함으로써, 보다 정확한 인에이블 구간을 갖는 데이터 출력 스트로브 신호를 생성하는 효과가 있다.

### 도면의 간단한 설명

- <1> 도 1은 본 발명의 일 실시예에 따른 데이터 출력 스트로브 신호 생성 회로의 구성을 나타낸 블록도,

- <2> 도 2a는 도 1에 도시한 제 1 드티 사이클 보정 수단의 상세 구성도,

- <3> 도 2b는 도 1에 도시한 제 2 드티 사이클 보정 수단의 상세 구성도,

<4> 도 3은 도 1에 도시한 듀티 사이클 제어 수단의 상세 구성도,

<5> 도 4는 본 발명에 따른 반도체 메모리 장치의 구성을 나타낸 블록도이다.

<6> <도면의 주요 부분에 대한 부호 설명>

<7> 100 : 듀티 사이클 보정 수단 110 : 제 1 듀티 사이클 보정 수단

<8> 120 : 제 2 듀티 사이클 보정 수단 200 : 듀티 사이클 제어 수단

<9> 300 : 데이터 출력 스트로브 신호 생성 수단

<10> 400 : 위상 스플리터

## 도면

### 도면1

## 도면2a

110

## 도면2b

120

## 도면3

200

## 도면4