【公報種別】特許法第17条の2の規定による補正の掲載

【部門区分】第6部門第3区分

【発行日】令和4年7月15日(2022.7.15)

【公開番号】特開2021-12596(P2021-12596A)

【公開日】令和3年2月4日(2021.2.4)

【年通号数】公開・登録公報2021-005

【出願番号】特願2019-127080(P2019-127080)

【国際特許分類】

G 06 T 7/00(2017.01)

10

G 06 F 17/10(2006.01)

G 06 F 12/00(2006.01)

G 06 F 12/02(2006.01)

G 06 T 1/60(2006.01)

【F I】

G 06 T 7/00 350 C

G 06 F 17/10 S

G 06 F 17/10 A

G 06 F 12/00 580

20

G 06 F 12/02 580 E

G 06 T 1/60 450 F

【手続補正書】

【提出日】令和4年7月7日(2022.7.7)

【手続補正1】

【補正対象書類名】特許請求の範囲

【補正対象項目名】全文

【補正方法】変更

【補正の内容】

【特許請求の範囲】

30

【請求項1】

入力された画像データに対して階層的にフィルタ演算処理を施して複数の特徴面を算出する演算装置であって、

画像データに対してコンボリューション演算を用いたフィルタ演算処理を行う演算部と、前記演算部による1つの階層の演算結果であって、次の階層の演算対象となる複数の特徴面のデータを格納する複数のメモリを有するデータ保持部と、

前記演算部が出力する演算結果を受信し、該受信した演算結果のうち、同一特徴面の連続するラインのデータを前記複数のメモリのうちそれ異なるメモリに書き込み、同じ階層の複数の特徴面の同一座標のデータを前記複数のメモリのうちそれ異なるメモリに書き込むメモリ書き込み制御部と、

同一特徴面の連続するラインのデータを、前記データ保持部のそれ異なるメモリから読み出し、同じ階層の異なる特徴面の同一座標のデータを、前記データ保持部のそれ異なるメモリから読み出すようにして、前記演算部へ演算対象となる特徴面のデータを送信するメモリ読み出し制御部と

を備えることを特徴とする演算処理装置。

【請求項2】

前記フィルタ演算処理では、前記コンボリューション演算に使用するカーネルサイズを階層ごとに設定することができることを特徴とする請求項1に記載の演算処理装置。

【請求項3】

前記フィルタ演算処理では、前記データ保持部に格納する特徴面のライン数を階層ごとに

40

50

設定することができる特徴とする請求項 1 に記載の演算処理装置。

【請求項 4】

前記メモリ書き込み制御部は、前記データ保持部の有するメモリの数を  $M$  ( $M > 1$ )、階層における特徴面の数を  $N$  ( $N > 1$ ) とすると、 $N \bmod M = 0$  のとき、 $M$  個の特徴面を 1 組とし、同じ組内の特徴面の同一座標のデータを、それぞれ異なるメモリの同一アドレスに格納することを特徴とする請求項 1 記載の演算処理装置。

【請求項 5】

入力された画像データに対して階層的にフィルタ演算処理を施して複数の特徴面を算出する演算処理装置が行う演算処理方法であって、

前記演算処理装置の演算部が、画像データに対してコンボリューション演算を用いたフィルタ演算処理を行う演算工程と、10

前記演算処理装置のメモリ書き込み制御部が、前記演算部が出力する演算結果を受信し、該受信した演算結果のうち、同一特徴面の連続するラインのデータを、前記演算部による1つの階層の演算結果であって、次の階層の演算対象となる複数の特徴面のデータを格納する複数のメモリのうちそれぞれ異なるメモリに書き込み、同じ階層の複数の特徴面の同一座標のデータを前記複数のメモリのうちそれぞれ異なるメモリに書き込むメモリ書き込み制御工程と、

前記演算処理装置のメモリ読み出し制御部が、同一特徴面の連続するラインのデータを、前記複数のメモリにおけるそれぞれ異なるメモリから読み出し、同じ階層の異なる特徴面の同一座標のデータを、前記複数のメモリにおけるそれぞれ異なるメモリから読み出すよ20うにして、前記演算部へ演算対象となる特徴面のデータを送信するメモリ読み出し制御工程と

を備えることを特徴とする演算処理方法。

【請求項 6】

入力された画像データに対して階層的にフィルタ演算処理を施して複数の特徴面を算出する演算処理装置のコンピュータに、請求項 5 に記載の演算処理方法の各工程を実行させるためのコンピュータプログラム。

【手続補正 2】

【補正対象書類名】明細書

【補正対象項目名】0 0 5 2

30

【補正方法】変更

【補正の内容】

【0 0 5 2】

メモリ書き込み制御部 1 0 3 は、コンボリューション演算部 1 0 1 による演算結果を画素単位で受信し、データ保持部 1 0 2 へ書き込む。メモリ書き込み制御部 1 0 3 は、メモリ 0 およびメモリ 1 のライトポートのチップセレクト W C S [ 0 ]、W C S [ 1 ]、ライトイネーブル W E [ 0 ]、W E [ 1 ]、ライトアドレス W A [ 0 ]、W A [ 1 ]、ライトデータ W D [ 0 ]、W D [ 1 ]を制御する。信号名に続く [ 番号 ] はメモリの番号 (メモリ番号) を示す。メモリ 0 のメモリ番号は「0」、メモリ 1 のメモリ番号は「1」である。メモリのインターフェース信号の制御は、制御部 1 0 5 から与えられる算出対象の階層の番号と算出対象のラインの番号 (y 座標) に基づき行われる。40

【手続補正 3】

【補正対象書類名】明細書

【補正対象項目名】0 1 2 7

40

【補正方法】変更

【補正の内容】

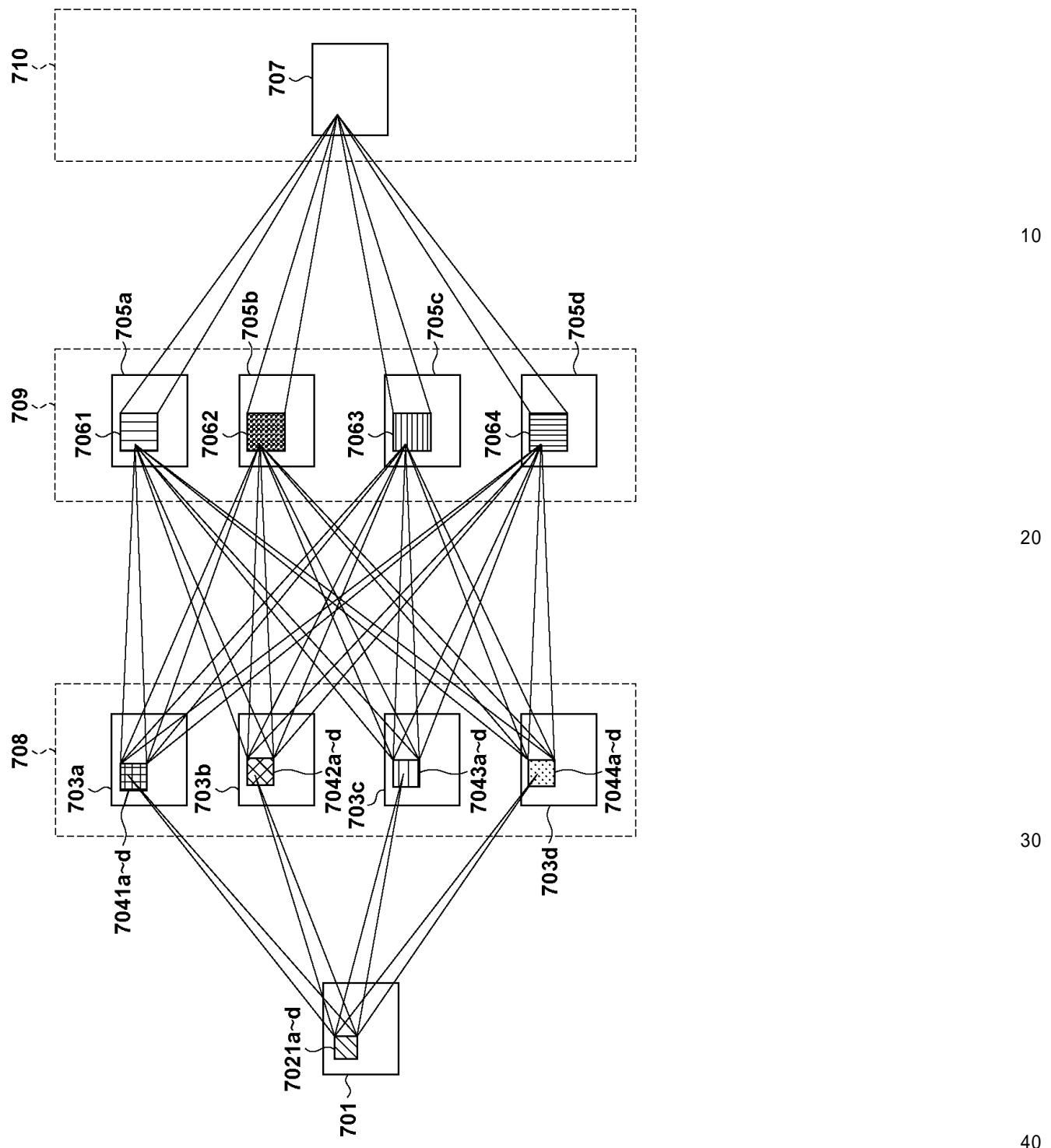

【0 1 2 7】

1 ラインの格納が終わると、ステップ S 4 1 5 にて制御部 1 0 5 は、最初の階層の特徴面 7 0 3 a ~ d が第 2 階層 7 0 9 の演算に使用するコンボリューションカーネルサイズの高さが生成されたか否かを判定する。この判定の結果、生成されていないと判定した場合に

50

は、処理はステップ S 4 0 4 に進み、特徴面 7 0 3 a ~ d 、 7 0 5 a ~ d 、 7 0 7 をさらに 1 ライン生成する。一方、ステップ S 4 1 5 の判定において、生成されたと判定した場合には、処理はステップ S 4 1 6 に進む。

【手続補正 4】

【補正対象書類名】明細書

【補正対象項目名】0 1 3 4

【補正方法】変更

【補正の内容】

【0 1 3 4】

また、メモリ読み出し制御部 1 0 4 の動作として図 3 のフローチャートも適用可能であり 10 、ステップ S 3 0 8 に示す通り、同一特徴面の連続する M ラインは異なるメモリから M ライン同時に読み出す。また、アドレスシングは 1 つのリードアドレス ( R A ) のみ管理し 、全てのメモリのアドレスはステップ S 3 0 4 で算出したメモリ番号に応じ、ステップ S 3 0 8 にて R A + 特徴面幅 × k × i ( i = 0 、 1 、 … 、メモリ数 - 1 ) で決定する。 然るに、アドレスシング回路は 1 つでよく、第 1 の実施形態と同様の効果を得ることができる。

【手続補正 5】

【補正対象書類名】図面

【補正対象項目名】図 7

【補正方法】変更

【補正の内容】

20

30

40

50

【図7】