(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-291865

(P2005-291865A)

(43) 公開日 平成17年10月20日(2005.10.20)

(51) Int.Cl.<sup>7</sup>

G O 1 R 19/165

F 1

G O 1 R 19/165

テーマコード(参考)

2 G O 3 5

L

審査請求 未請求 請求項の数 10 O L (全 9 頁)

(21) 出願番号

特願2004-106184 (P2004-106184)

(22) 出願日

平成16年3月31日 (2004.3.31)

(71) 出願人 302062931

N E C エレクトロニクス株式会社

神奈川県川崎市中原区下沼部1753番地

(74) 代理人 100103894

弁理士 家入 健

(72) 発明者 吉澤 健

神奈川県川崎市中原区下沼部1753番地

N E C エレクトロニクス株式会社内

F ターム(参考) 2G035 AA00 AB01 AC01 AC16 AD03

AD10 AD11 AD13 AD56

(54) 【発明の名称】電源電圧監視回路

## (57) 【要約】

## 【課題】

比較誤動作を抑制することが可能な電源電圧監視回路を提供すること。

## 【解決手段】

本発明にかかる電源電圧監視回路では、P型MOSトランジスタP1のドレインが電源電圧Vccと接続され、ソースがコンパレータ2の入力端子と分圧回路R1、R2を介して接続されている。またN型MOSトランジスタN1のゲートには、基準電圧回路1より出力された出力電圧が入力され、ドレインはP型MOSトランジスタP1のゲートに接続されている。N型MOSトランジスタN1は、ゲートに入力された電圧が基準電圧に到達した場合にオン状態になる。これに応じてP型MOSトランジスタP1もオン状態になり、コンパレータ2に電源電圧Vccに応じた電圧が供給され、比較動作が行われる。

【選択図】 図1

**【特許請求の範囲】****【請求項 1】**

自己電源電圧を監視する電源電圧監視回路であって、

電源電圧が入力され、当該電源電圧に応じて基準電圧を生成し出力する基準電圧回路と

、

前記基準電圧回路から出力された出力電圧と、前記電源電圧に応じて変化する電圧を入力し、両者を比較して、その比較結果を出力するコンパレータと、

前記基準電圧回路から出力された出力電圧が基準電圧に到達する前に、前記電源電圧に応じた電圧が前記コンパレータに入力されないように制御する制御手段とを備えた電源電圧監視回路。

10

**【請求項 2】**

自己電源電圧を監視する電源電圧監視回路であって、

電源電圧が入力され、当該電源電圧に応じて基準電圧を生成し出力する基準電圧回路と

、

前記基準電圧回路から出力された出力電圧と、前記電源電圧に応じて変化する電圧を入力し、両者を比較して、その比較結果を出力するコンパレータと、

前記電源電圧と前記コンパレータ間の導通を制御する第1のスイッチ手段と、

前記基準電圧回路より出力された出力電圧を入力し、当該出力電圧に応じて前記第1のスイッチ手段を制御する第2のスイッチ手段とを備え、

前記第2のスイッチ手段は、前記基準電圧回路から出力された出力電圧が基準電圧に到達する前には、前記電源電圧に応じた電圧が前記コンパレータに入力されないように前記第1のスイッチ手段を制御する電源電圧監視回路。

20

**【請求項 3】**

自己電源電圧を監視する電源電圧監視回路であって、

電源電圧が入力され、当該電源電圧に応じて基準電圧を生成し出力する基準電圧回路と

、

第1の入力端子より入力された電圧と、第2の入力端子より入力された電圧を比較して、

その比較結果を出力するコンパレータと、

前記電源電圧と前記コンパレータ間の導通を制御する第1のトランジスタと、

前記基準電圧回路より出力された出力電圧をゲートに入力し、ドレインが前記第1のトランジスタのゲートに接続された第2のトランジスタとを備え、

前記コンパレータの第1の入力端子には前記第1のトランジスタによって導通が制御された電圧が入力され、前記第2の入力端子には、前記基準電圧回路より出力された出力電圧が入力され、

前記第2のトランジスタは、前記基準電圧回路から出力された出力電圧が基準電圧に到達する前には、前記電源電圧に応じた電圧が前記コンパレータに入力されないように前記第1のトランジスタのゲートに電圧を供給する電源電圧監視回路。

30

**【請求項 4】**

前記第1のトランジスタのゲートと、前記第2のトランジスタのドレインとの間に、基準電圧回路より生成される電流源からの電流を供給したことを特徴とする請求項3記載の電源電圧監視回路。

40

**【請求項 5】**

前記第1のトランジスタのゲートと、前記第2のトランジスタのドレインとの接続点を、前記電源電圧と接続された抵抗と接続したことを特徴とする請求項3記載の電源電圧監視回路。

**【請求項 6】**

前記第1のトランジスタのゲートと、前記第2のトランジスタのドレインとの接続点を、前記電源電圧と接続された容量素子と接続したことを特徴とする請求項4又は5記載の電源電圧監視回路。

**【請求項 7】**

50

自己電源電圧を監視する電源電圧監視回路であって、

電源電圧が入力され、当該電源電圧に応じて基準電圧を生成し出力する基準電圧回路と

、

第1の入力端子より入力された電圧と、第2の入力端子に前記基準電圧回路から入力された電圧を比較して、その比較結果を出力するコンパレータと、

ドレインが前記電源電圧と接続され、ソースが前記コンパレータの第1の入力端子と分圧回路を介して接続されたP型MOSトランジスタと、

前記基準電圧回路より出力された出力電圧をゲートに入力し、ドレインが前記P型MOSトランジスタのゲートに接続され、ソースが接地され、前記ゲートに入力された電圧が基準電圧に到達した場合にオン状態になるN型MOSトランジスタとを備えた電源電圧監視回路。

10

#### 【請求項8】

前記P型MOSトランジスタのゲートと、前記N型MOSトランジスタのドレインとの間に、基準電圧回路より生成される電流源からの電流を供給したことを特徴とする請求項7記載の電源電圧監視回路。

#### 【請求項9】

前記P型MOSトランジスタのゲートと、前記N型MOSトランジスタのドレインとの接続点を、前記電源電圧と接続された抵抗と接続したことを特徴とする請求項7記載の電源電圧監視回路。

#### 【請求項10】

前記P型MOSトランジスタのゲートと、前記N型MOSトランジスタのドレインとの接続点を、前記電源電圧と接続された容量素子と接続したことを特徴とする請求項8又は9記載の電源電圧監視回路。

20

#### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

本発明は、自己電源電圧を監視するコンパレータを有する電源電圧監視回路に関する。

#### 【背景技術】

#### 【0002】

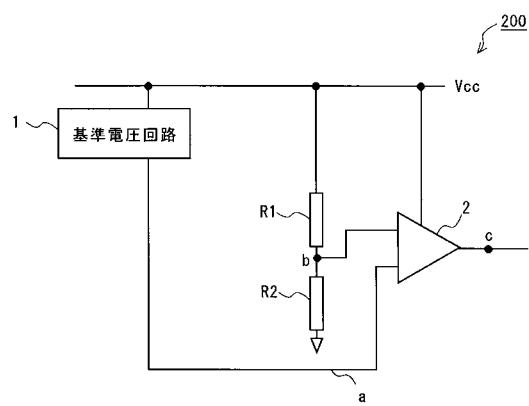

従来の電源電圧監視回路の構成について、図5を用いて説明する。この電源電圧監視回路200は、電源電圧の電位、即ち電源電位Vccを監視し、当該電源電位Vccが所定値を下回ったか否かを検出し、検出結果を出力する回路である。電源電圧監視回路200は、基準電圧回路1を有する。この基準電圧回路1は、基準電圧を生成し、コンパレータ2の一方の入力端子に出力する。また、電源電位Vccは、検出抵抗R1及び検出抵抗R2によって分圧される。分圧された電圧は、コンパレータ2の他方の入力端子に出力される。

30

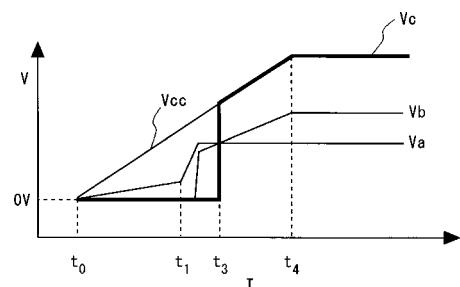

#### 【0003】

電源電位Vccを0Vから上昇させた場合における、図5のa、b、cの各点における電圧の変化について、図6を用いて説明する。時刻t0において、0Vにあった電源電位Vccが上昇を開始する。電源電位Vccは、時間に略正比例して上昇していく。電源電位Vccの上昇に伴って、基準電圧回路1も起動を開始し、その出力を示すa点における電圧Vaも時間に略正比例して上昇していく。時刻t1において電源電位Vccが基準電圧回路1の動作開始電圧に達するに伴って、電圧Vaは、急激に上昇した後、一定の基準電圧値となる。

40

#### 【0004】

電源電位Vccを分圧する検出抵抗R1と検出抵抗R2間のb点における電圧Vbは、電源電位Vccの上昇に伴って略正比例して上昇していく。電圧Vbの上昇の傾きは、基準電圧回路1から出力電圧Vaの初期傾きよりも大きい。

#### 【0005】

コンパレータ2の出力電圧である、c点の電圧Vcは、初期の段階では、電圧Vbの方

50

が電圧  $V_a$  よりも高いため、電圧  $V_b$  が基準電圧よりも低いにも拘らず、電源電位  $V_{cc}$  と同じ値を示す。

#### 【0006】

時刻  $t_1$  の後における、当該出力電圧  $V_a$  の傾きは、電圧  $V_b$  の傾きよりも大きくなるため、時刻  $t_2$  において出力電圧  $V_a$  が電圧  $V_b$  を超える。出力電圧  $V_a$  が電圧  $V_b$  を超えると、両電圧はコンパレータ2に入力されているため、コンパレータ2の出力電圧  $V_c$  は、0Vを出力することになる。

#### 【0007】

時刻  $t_2$  の後、基準電圧回路1からの出力電圧  $V_a$  が基準電圧に到達し、略一定の値となる。 $b$ 点における電圧  $V_b$  は、継続的に電源電圧  $V_{cc}$  の上昇に伴って略正比例して上昇していくため、時刻  $t_3$  には、再び電圧  $V_b$  が電圧  $V_a$  を超えることになる。電圧  $V_b$  が電圧  $V_a$  を超えると、コンパレータ2の出力電圧  $V_c$  は、0Vから  $V_{cc}$  と同じ電圧値に戻る。

10

#### 【0008】

その後、電圧  $V_b$  は、電源電位  $V_{cc}$  が所望の電圧値に達する時刻  $t_4$  まで、電源電位  $V_{cc}$  と同様にして略正比例する。また、電圧  $V_a$  は依然として基準電圧値を保っている。時刻  $t_4$  後は、電源電位  $V_{cc}$  が所望の電圧値に達して一定値をとり、同様にして電源電位  $V_{cc}$  を分圧した  $b$  点における電圧  $V_b$  も一定値をとる。コンパレータ2の出力電圧  $V_c$  は、時刻  $t_4$  後は、電源電位  $V_{cc}$  と同じ電圧値をとる。

#### 【0009】

仮に時刻  $t_5$  において、電源電位  $V_{cc}$  の電圧低下が生じたものとする。そうすると、分圧された電圧  $V_b$  も同様にして電圧低下が発生し、基準電圧  $V_a$  を下回る場合もある。このような場合に比較結果を示す  $V_c$  は、時刻  $t_6$  以降に電圧  $V_b$  が基準電圧  $V_a$  を下回った状態になると0Vを出力する。この例では、時刻  $t_6$  から時刻  $t_7$  まで0Vを出力し、時刻  $t_7$  において電圧  $V_b$  が基準電圧  $V_a$  以上となると、再び電圧  $V_c$  は  $V_{cc}$  を追従することになる。このような時刻  $t_6$  から時刻  $t_7$  までの間、コンパレータ2の出力が0Vになるのは正常な動作であり、このような構成により電源電圧を監視することができる。

20

#### 【0010】

尚、いわゆるパワーオンリセット回路（例えば特許文献1）において、電源電位を検出する回路が用いられているが、電源電位が所定値に達したことを検出し、回路をリセットするための回路であり、電源電圧の低下を検出する電源電圧監視回路を構成するものではない。

30

#### 【特許文献1】特開平9-135157号公報

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0011】

従来の電源電圧監視回路は、時刻  $t_0$  から時刻  $t_2$  までの間は、電圧  $V_b$  が基準電圧よりも低いにも拘らず、コンパレータ2の出力電圧  $V_c$  が電源電位  $V_{cc}$  と同じ電位、即ちハイ電位となり、誤動作する。コンパレータ2の誤動作は、コンパレータ2の出力に応じて動作する他の回路の誤動作に繋がる。

40

#### 【0012】

本発明の目的は、かかる問題を解消し、比較誤動作を抑制することが可能な電源電圧監視回路を提供することである。

#### 【課題を解決するための手段】

#### 【0013】

本発明にかかる電源電圧監視回路は、自己電源電圧を監視する電源電圧監視回路であって、電源電圧が入力され、当該電源電圧に応じて基準電圧を生成し出力する基準電圧回路と、前記基準電圧回路から出力された出力電圧と、前記電源電圧に応じて変化する電圧を入力し、両者を比較して、その比較結果を出力するコンパレータと、前記基準電圧回路か

50

ら出力された出力電圧が基準電圧に到達する前に、前記電源電圧に応じた電圧が前記コンパレータに入力されないように制御する制御手段とを備えたものである。

【0014】

また、本発明にかかる他の電源電圧監視回路は、自己電源電圧を監視する電源電圧監視回路であって、電源電圧が入力され、当該電源電圧に応じて基準電圧を生成し出力する基準電圧回路と、前記基準電圧回路から出力された出力電圧と、前記電源電圧に応じて変化する電圧を入力し、両者を比較して、その比較結果を出力するコンパレータと、前記電源電圧と前記コンパレータ間の導通を制御する第1のスイッチ手段と、前記基準電圧回路より出力された出力電圧を入力し、当該出力電圧に応じて前記第1のスイッチ手段を制御する第2のスイッチ手段とを備え、前記第2のスイッチ手段は、前記基準電圧回路から出力された出力電圧が基準電圧に到達する前には、前記電源電圧に応じた電圧が前記コンパレータに入力されないように前記第1のスイッチ手段を制御するものである。10

【0015】

さらに、本発明にかかる他の電源電圧監視回路は、自己電源電圧を監視する電源電圧監視回路であって、電源電圧が入力され、当該電源電圧に応じて基準電圧を生成し出力する基準電圧回路と、第1の入力端子より入力された電圧と、第2の入力端子より入力された電圧を比較して、その比較結果を出力するコンパレータと、前記電源電圧と前記コンパレータ間の導通を制御する第1のトランジスタと、前記基準電圧回路より出力された出力電圧をゲートに入力し、ドレインが前記第1のトランジスタのゲートに接続された第2のトランジスタとを備え、前記コンパレータの第1の入力端子には前記第1のトランジスタによって導通が制御された電圧が入力され、前記第2の入力端子には、前記基準電圧回路より出力された出力電圧が入力され、前記第2のトランジスタは、前記基準電圧回路から出力された出力電圧が基準電圧に到達する前には、前記電源電圧に応じた電圧が前記コンパレータに入力されないように前記第1のトランジスタのゲートに電圧を供給するものである。20

【0016】

ここで、前記第1のトランジスタのゲートと、前記第2のトランジスタのドレインとの間に、基準電圧回路より生成される電流源からの電流を供給するとい。20

【0017】

また、前記第1のトランジスタのゲートと、前記第2のトランジスタのドレインとの接続点を、前記電源電圧と接続された抵抗と接続するようにしてもよい。30

【0018】

そして、前記第1のトランジスタのゲートと、前記第2のトランジスタのドレインとの接続点を、前記電源電圧と接続された容量素子と接続するようにしてもよい。

【0019】

本発明にかかる他の電源電圧監視回路は、自己電源電圧を監視する電源電圧監視回路であって、電源電圧が入力され、当該電源電圧に応じて基準電圧を生成し出力する基準電圧回路と、第1の入力端子より入力された電圧と、第2の入力端子に前記基準電圧回路から入力された電圧を比較して、その比較結果を出力するコンパレータと、ドレインが前記電源電圧と接続され、ソースが前記コンパレータの第1の入力端子と分圧回路を介して接続されたP型MOSトランジスタと、前記基準電圧回路より出力された出力電圧をゲートに入力し、ドレインが前記P型MOSトランジスタのゲートに接続され、ソースが接地され、前記ゲートに入力された電圧が基準電圧に到達した場合にオン状態になるN型MOSトランジスタとを備えたものである。40

【0020】

ここで、前記P型MOSトランジスタのゲートと、前記N型MOSトランジスタのドレインとの間に、基準電圧回路より生成される電流源からの電流を供給することが望ましい。

【0021】

また、前記P型MOSトランジスタのゲートと、前記N型MOSトランジスタのドレイ50

ンとの接続点を、前記電源電圧と接続された抵抗と接続するようにしてもよい。

【0022】

そして、前記P型MOSトランジスタのゲートと、前記N型MOSトランジスタのドレインとの接続点を、前記電源電圧と接続された容量素子と接続してもよい。

【発明の効果】

【0023】

本発明によれば、比較誤動作を抑制することが可能な電源電圧監視回路を提供することができる。

【発明を実施するための最良の形態】

【0024】

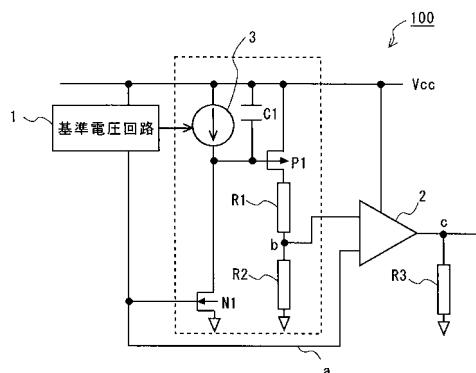

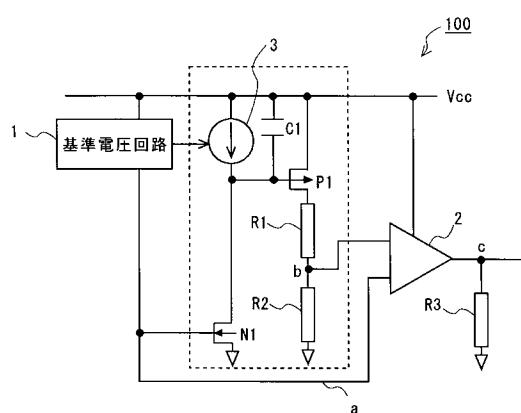

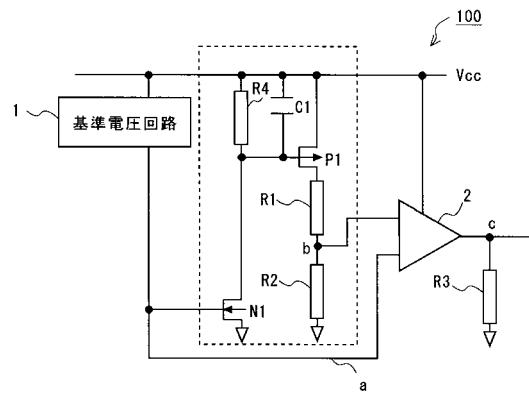

本発明の実施の形態にかかる電源電圧監視回路の構成について、図1を用いて説明する。この電源電圧監視回路100は、電源電位Vcc、即ち電源電圧を監視し、当該電源電位Vccが所定値を下回ったか否かを検出し、検出結果を出力する回路である。

【0025】

電源電圧監視回路100は、基準電圧回路1を有する。この基準電圧回路1は、電源電位Vccと接続され、当該電源電位Vccに基づいて基準電圧を生成する。この基準電圧回路1の出力端子は、コンパレータ2の一方の入力端子に接続され、基準電圧が供給されている。また、基準電圧回路1の出力は、N型MOS(Metal Oxide Semiconductor)トランジスタN1のゲートに接続され、基準電圧が供給されている。

【0026】

電源電位Vccと接地電位の間には、電流源3とN型MOSトランジスタN1が接続されている。電流源3は、基準電圧回路1において生成されるものである。具体的には、電流源3は、基準電圧回路1にあるカレントミラー回路等によって構成される。電流源3は、P型MOSトランジスタP1のゲート及びN型MOSトランジスタN1のドレインに接続されている。かかる電流源3によって、P型MOSトランジスタP1のスイッチング動作を確実にすることができます。

【0027】

また、電源電位Vccと接地電位の間には、P型MOSトランジスタP1、検出抵抗R1及び検出抵抗R2が直列に接続されている。P型MOSトランジスタP1のソースが当該電源電位Vccと接続され、かつドレインが検出抵抗R1と接続されている。また、P型MOSトランジスタP1のゲートは、容量素子C1を介して電源電位Vccと接続されている。これにより、P型MOSトランジスタP1のゲートがフローティング状態となるのを防止できる。P型MOSトランジスタP1のゲートは、電流源3の出力端子及びN型トランジスタN1のドレインとも接続されている。N型トランジスタN1のソースは接地電位と接続されている。

【0028】

検出抵抗R1と検出抵抗R2の接続点bは、コンパレータ2の他方の入力端子に接続されている。そして、検出抵抗R1と検出抵抗R2によって分圧された電圧は、コンパレータ2の他方の入力端子に出力される。

【0029】

コンパレータ2は、電源電位Vccと接続され、電源電圧が供給されるとともに、その出力端子は、出力プルダウン抵抗R3と接続され、これによりプルダウンされている。

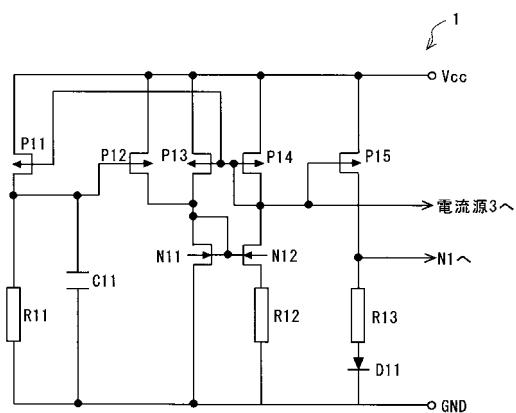

【0030】

ここで、図2を用いて、基準電圧回路1の構成例を説明する。図2に示されるように、電源電位Vccと接地電位GNDとの間にP型MOSトランジスタP13およびN型MOSトランジスタN11が直列接続で挿入された直列接続回路が構成されている。さらに、P型MOSトランジスタP14とN型MOSトランジスタN12と抵抗R12とが直列接続で挿入された直列接続回路が構成されている。

P型MOSトランジスタP13およびP14のゲートとドレインとが互に接続されている。N型MOSトランジスタN11のゲートとドレインとN型MOSトランジスタN12

10

20

30

40

50

のゲートとが互いに接続される。P型MOSトランジスタP13およびP14のゲートとP型MOSトランジスタP14のドレインの接続点は、図1に示す電流源3に接続されているとともに、P型MOSトランジスタP15のゲートに接続されている。このP型MOSトランジスタP15と抵抗R13と、この抵抗R13側をアノードとするダイオードD11とが電源電位Vccおよび接地電位GND間に直列接続で挿入され、この直列接続点の電圧が図1に示すN型MOSトランジスタN1に接続されている。

さらにP型MOSトランジスタP13と並列にP型MOSトランジスタP12が接続され、そのゲートはP型MOSトランジスタP11のドレインと接続されている。また、電源電位Vccと接地電位GNDとの間にP型MOSトランジスタP11と抵抗R11が直列接続で挿入され、P型MOSトランジスタP11のドレインは容量素子C11を介して接地電位に接続される。

10

#### 【0031】

基準電圧回路1は、このような構成によって基準電圧を発生させる。

#### 【0032】

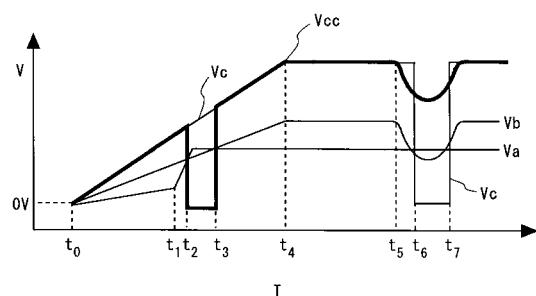

続いて、電源電位Vccを0Vから上昇させた場合における、図1のa、b、cの各点における電圧の変化について、図3を用いて説明する。時刻t0において、0Vにあった電源電位Vccが上昇を開始する。電源電位Vccは、時間に略正比例して上昇していく。

#### 【0033】

電源電位Vccの上昇に伴って、基準電圧回路1も起動を開始し、その出力を示すa点における電圧Vaも時間に略正比例して上昇していく。時刻t1において電源電位Vccが基準電圧回路1の動作開始電圧に達するに伴って、電圧Vaは、急激に上昇した後、一定の基準電圧値となる。

20

#### 【0034】

ここで、基準電圧回路1から出力される電圧Vaが基準電圧に達する前は、N型トランジスタN1はオフ状態にある。従って、N型トランジスタN1のドレインが接続されたP型トランジスタP1のゲートは電流源3によって電流が供給されてハイ電位にあるため、オフ状態にある。従って、電源電位Vccとb点間は遮断状態にあるため、コンパレータ2の他方の入力電圧は0Vとなる。

#### 【0035】

電圧Vaが上昇し、基準電圧に達すると、N型トランジスタN1がオン状態となる。N型トランジスタN1がオン状態となると、P型トランジスタP1のゲート電位が低下し、オン状態になる。そうすると、P型トランジスタP1を介して電源電圧Vccが検出抵抗R1と検出抵抗R2によって分圧される。時刻t3において、分圧された電圧Vbが基準電圧Vaを超えると、コンパレータ2から出力される電圧Vcは、電源電位Vccと等しくなる。

30

#### 【0036】

そして、時刻t4において、電源電位Vccが所望の電位まで達し一定になると、コンパレータ2の出力電圧Vcも同様に一定となる。その後の動作については、従来と同様であるため説明を省略する。

40

#### 【0037】

このように、本発明の実施の形態にかかる電源電圧監視回路100では、基準電圧回路1から出力された電圧が所定値を超えるまでは、コンパレータ2への入力を0Vとし、基準電圧回路1から出力された電圧が基準電圧に達した後に、コンパレータ2へ電源電位Vccに応じた電圧を入力し、比較動作を行うよう制御したため、電源電圧の上昇過程で生じるコンパレータ2の誤動作を防止できる。

#### 【0038】

その他の実施の形態。

図1に示す例では、電流源3を用いたが、電流源3の代りに図4に示すように抵抗R4を設けるようにしてもよい。尚、抵抗R4は、消費電力の増大を抑制するために高抵抗で

50

あることが望ましい。

【0039】

また、図1、図4に示す例においては、容量素子C1を設けているが、必ずしもこの容量素子C1は必須ではなく、例えば図4に示す回路のように時刻t0からt1までの間にP型トランジスタP1のゲート電位がフローティング状態になる恐れがない場合には、当該容量素子C1はなくてもよい。

【図面の簡単な説明】

【0040】

【図1】本発明にかかる電源電圧監視回路の回路ブロック図である。

【図2】本発明にかかる電源電圧監視回路の基準電圧回路の一構成例を示す回路図である 10

。 【図3】本発明にかかる電源電圧監視回路の各点における電位の変化を示す波形図である

。 【図4】本発明にかかる他の電源電圧監視回路の回路ブロック図である。

【図5】従来の電源電圧監視回路の回路ブロック図である。

【図6】従来の電源電圧監視回路の各点における電位の変化を示す波形図である。

【符号の説明】

【0041】

1 基準電圧回路

2 コンパレータ

3 電流源

20

【図1】

【図2】

【図3】

【図4】

【図6】

【図5】