(19)

OFICINA ESPAÑOLA DE

PATENTES Y MARCAS

ESPAÑA

(11) Número de publicación: **2 986 129**

(51) Int. Cl.:

**G10L 19/008** (2013.01)

**G10L 19/18** (2013.01)

**H03G 7/00** (2006.01)

**H03G 9/00** (2006.01)

(12)

## TRADUCCIÓN DE PATENTE EUROPEA

T3

(96) Fecha de presentación y número de la solicitud europea: **02.05.2013 E 19168175 (8)**

(97) Fecha y número de publicación de la concesión europea: **24.07.2024 EP 3547312**

(54) Título: **Sistema y método para control de rango dinámico de una señal de audio**

(30) Prioridad:

**18.05.2012 US 201261649036 P**

**25.07.2012 US 201261664507 P**

**12.10.2012 US 201261713005 P**

(45) Fecha de publicación y mención en BOPI de la traducción de la patente:

**08.11.2024**

(73) Titular/es:

**DOLBY LABORATORIES LICENSING CORPORATION (50.0%)**

**1275 Market Street**

**San Francisco, CA 94103, US y**

**DOLBY INTERNATIONAL AB (50.0%)**

(72) Inventor/es:

**RIEDMILLER, JEFFREY;**

**ROEDEN, KARL JONAS;**

**KJOERLING, KRISTOFER;**

**PURNHAGEN, HEIKO;**

**MELKOTE, VINAY y**

**SEHLSTROM, LEIF**

(74) Agente/Representante:

**LINAGE GONZÁLEZ, Rafael**

**ES 2 986 129 T3**

Aviso: En el plazo de nueve meses a contar desde la fecha de publicación en el Boletín Europeo de Patentes, de la mención de concesión de la patente europea, cualquier persona podrá oponerse ante la Oficina Europea de Patentes a la patente concedida. La oposición deberá formularse por escrito y estar motivada; sólo se considerará como formulada una vez que se haya realizado el pago de la tasa de oposición (art. 99.1 del Convenio sobre Concesión de Patentes Europeas).

**DESCRIPCIÓN**

Sistema y método para control de rango dinámico de una señal de audio

**5 Referencia cruzada a solicitudes relacionadas**

Esta solicitud reivindica prioridad de la solicitud de patente provisional de Estados Unidos n.º 61/649.036, presentada el 18 de mayo de 2012, la solicitud de patente provisional de Estados Unidos n.º 61/664.507, presentada el 25 de julio de 2012 y la solicitud de patente provisional de Estados Unidos n.º 61/713.005, 10 presentada el 12 de octubre de 2012.

Esta solicitud es una solicitud divisional europea de la solicitud de patente Euro-PCT EP 13724945.4 (referencia: D12046EP01), presentada el 2 de mayo de 2013.

**15 Campo técnico**

La invención se refiere a un método realizado por un dispositivo de decodificación de señales de audio, un dispositivo de decodificación de señales de audio y un programa de ordenador como se establece en el conjunto de reivindicaciones adjunto.

**20 Antecedentes**

Se sabe que los métodos de codificación estéreo paramétrico y multicanal son escalables y eficientes en términos de calidad de escucha, lo que los hace particularmente atractivos en aplicaciones de baja tasa de bits.

25 Sin embargo, en los casos en que las limitaciones de la tasa de bits son de naturaleza transitoria (por ejemplo, fluctuaciones de la red, variaciones de carga), el beneficio completo de los recursos de red disponibles se puede obtener mediante el uso de un formato de distribución adaptativo, en donde se usa una tasa de bits relativamente más alta durante condiciones normales y una tasa de bits más baja cuando la red funciona mal.

30 Los formatos de distribución adaptativos existentes y las técnicas de (de)codificación asociadas se pueden mejorar desde el punto de vista de su eficiencia de ancho de banda, eficiencia computacional, resistencia a errores, retardo algorítmico y, además, en la distribución de medios audiovisuales, en cuanto a cuán perceptible es un evento de conmutación de tasa de bits para una persona que disfruta de los medios decodificados. El hecho de que se pueda esperar que los decodificadores heredados sigan utilizándose en paralelo a equipos más 35 nuevos y dedicados plantea una limitación a esas posibles mejoras en la medida en que se debe mantener la compatibilidad con versiones anteriores.

Las técnicas de control de rango dinámico (DRC) para garantizar un rango dinámico más consistente durante la reproducción de una señal audiovisual son bien conocidas en la técnica. Para una descripción general, véase el 40 documento T. Carroll y J. Riedmiller, "Audio for Digital Television", publicado como capítulo 5.18 de E. A. Williams et al. (eds.), NAB Engineering Handbook, 10.<sup>a</sup> ed. (2007), Academic Press, y referencias allí citadas. Tales técnicas pueden permitir que un receptor adapte el rango dinámico de una señal audiovisual para adecuarlo a un equipo de reproducción relativamente poco sofisticado, mientras que la señal en sí se transmite con un rango dinámico completo, en beneficio de un equipo más refinado. Una implementación simple de DRC 45 puede usar un campo de metadatos que codifique un factor de ganancia en el intervalo de 0 a 1, que el decodificador puede elegir aplicar o no.

Usando técnicas DRC conocidas, se puede transmitir una señal audiovisual codificada junto con metadatos, ofreciendo al usuario la capacidad de comprimir o potenciar el rango dinámico de reproducción para adecuarlo a 50 sus preferencias o adaptar manualmente el rango dinámico al equipo de reproducción disponible. Sin embargo, las técnicas DRC conocidas pueden no ser compatibles con los métodos de codificación de tasa de bits adaptativa, y la conmutación entre dos tasas de bits a veces puede estar acompañada de inconsistencias en el rango dinámico, especialmente en equipos heredados. La presente invención aborda esta preocupación.

55 En el documento "Spatial Audio Processing" - "Ch. 6 MPEG Surround" (Jeroen Breebaart et al, en "Spatial Audio Processing", 1 de enero de 2007, John Wiley & Sons, Ltd, Inglaterra, páginas 93-115) se divulga una estructura de decodificador MPEG envolvente que comprende un decodificador espacial que genera señales de salida multicanal a partir de una señal de entrada mezclada de forma descendente.

**60 Breve descripción de los dibujos**

Ahora se describirán realizaciones de la invención, así como ejemplos no reivindicados, con referencia a los dibujos que se acompañan, en los que:

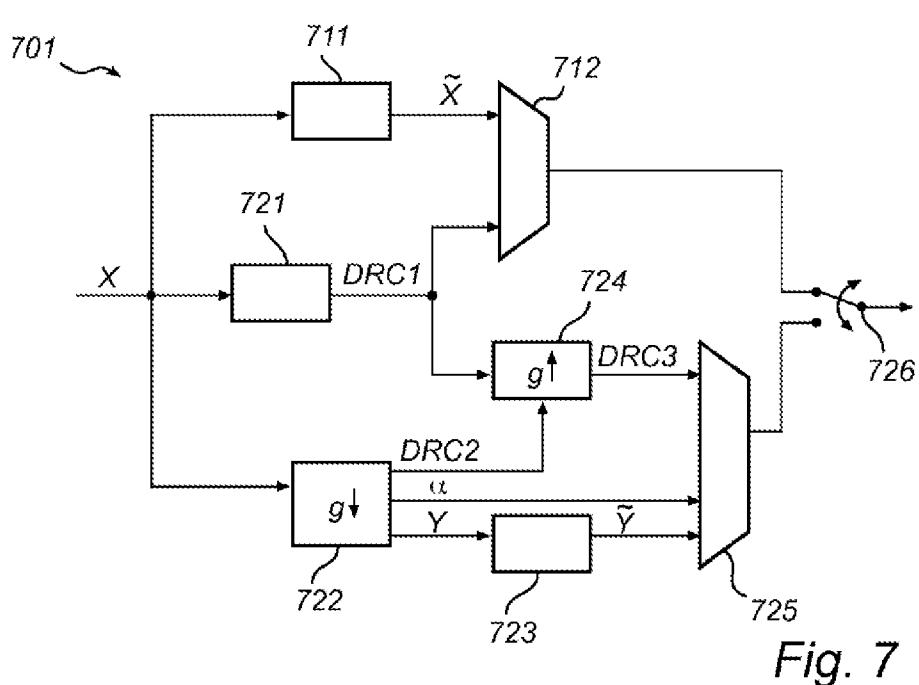

65 las figuras 1, 3, 7 y 10 son diagramas de bloques generalizados de sistemas de codificación de audio de acuerdo con ejemplos no reivindicados;

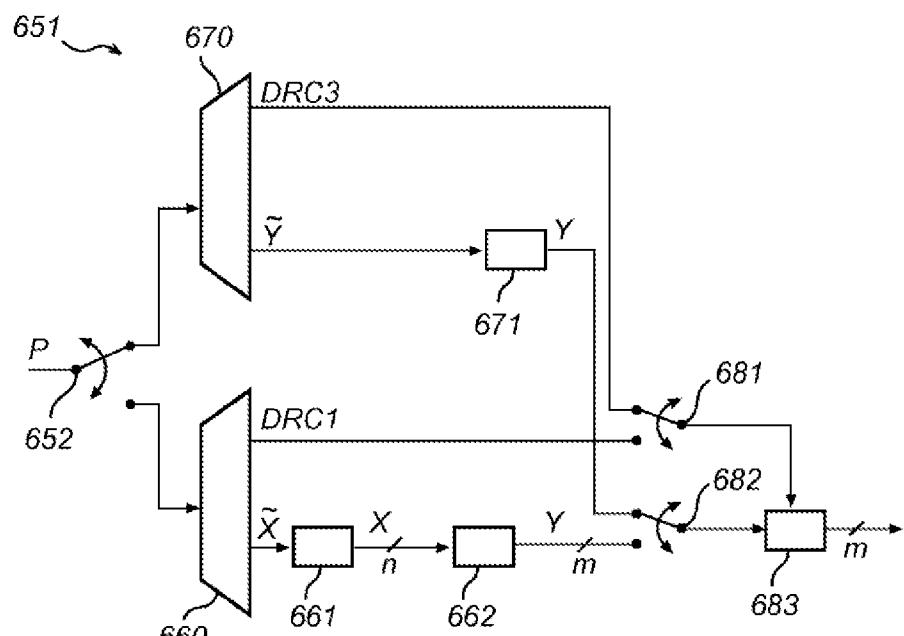

las figuras 2, 4, 6 y 13 son diagramas de bloques generalizados de sistemas de decodificación de audio de acuerdo con realizaciones de ejemplo de la invención;

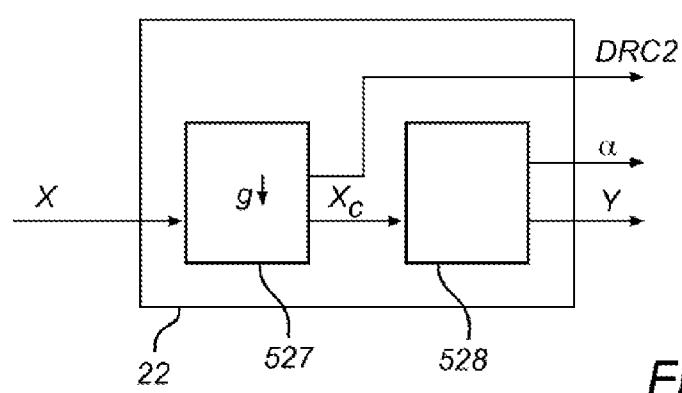

5 la figura 5 muestra una porción de una etapa de análisis paramétrico en un sistema de codificación de audio no reivindicado;

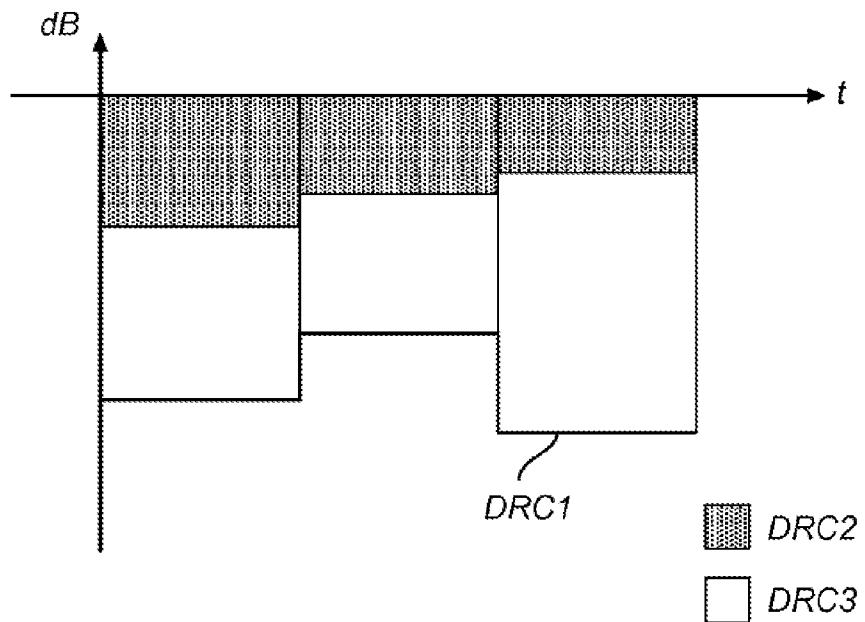

10 la figura 8 ilustra el cálculo de valores de parámetros DRC de posprocesamiento compensados sobre la base de parámetros DRC de preprocesamiento y posprocesamiento que hacen referencia a bloques de tiempo de longitudes iguales;

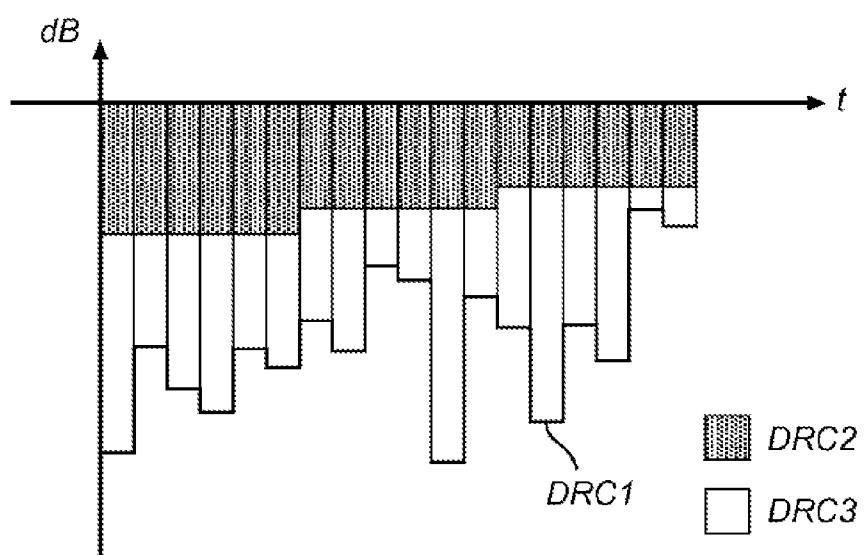

15 la figura 9 ilustra el cálculo de valores de parámetros DRC de posprocesamiento compensados sobre la base de parámetros DRC de preprocesamiento y posprocesamiento que hacen referencia a bloques de tiempo de diferentes longitudes;

15 las figuras 11 y 12 muestran una porción de una etapa de síntesis paramétrica en un sistema de decodificación de audio.

20 Todas las figuras son esquemáticas y generalmente solo muestran partes necesarias con el fin de ilustrar la invención, mientras que otras partes pueden omitirse o simplemente sugerirse. A menos que se indique lo contrario, los números de referencia iguales se refieren a partes iguales en figuras diferentes.

#### **Descripción detallada**

25 I. Descripción general

La invención se refiere a un método realizado por un dispositivo de decodificación de señales de audio, un dispositivo de decodificación de señales de audio y un programa de ordenador como se establece en el conjunto de reivindicaciones adjunto.

30 Tal como se usa en el presente documento, una "señal de audio" puede ser una señal de audio pura o una parte de audio de una señal audiovisual o una señal multimedia.

35 Los aspectos, realizaciones y ejemplos relativos a un dispositivo de codificación, un método de codificación o un formato de codificación que se presentan a continuación no son conformes a la invención y deben considerarse como ejemplos adecuados para comprender la invención tal como se establece en las reivindicaciones adjuntas.

40 Un ejemplo de realización de la presente invención propone métodos y dispositivos que permiten la distribución de medios audiovisuales de manera económica en términos de ancho de banda. En particular, una realización de ejemplo propone un formato de codificación para la distribución de medios audiovisuales que permite que tanto los receptores heredados como los equipos más recientes emitan una porción de audio que tenga un nivel de diálogo consistente. En particular, una realización de ejemplo propone un formato de codificación con tasa de bits adaptativa, en donde una comutación entre dos valores de tasa de bits no necesita estar acompañado por un cambio brusco en el nivel de diálogo, que de lo contrario podría ser un artefacto perceptible en la señal de audio o en la porción de audio de la señal durante la reproducción.

45 Una primera realización de ejemplo de la invención proporciona un sistema de decodificación para reconstruir una señal de audio X de canal n sobre la base de un flujo de bits P. El sistema de decodificación es operable al menos en un modo de codificación paramétrica y comprende:

50 • un demultiplexor para recibir el flujo de bits y emitir una señal central codificada Ÿ y uno o más parámetros de codificación multicanal, que se denotan colectivamente por  $\alpha$ ;

55 • un decodificador de señal central para recibir la señal central codificada y emitir una señal central de canal m, donde  $1 \leq m < n$ ;

• una etapa de síntesis paramétrica para recibir la señal central y los parámetros de codificación multicanal y emitir la señal de canal n, formando una combinación lineal de los canales de la señal central usando ganancias que dependen de los parámetros de codificación multicanal.

60 En esta primera realización de ejemplo, el flujo de bits comprende además uno o más parámetros DRC de preprocesamiento DRC2, que caracterizan cuantitativamente una operación de limitación de rango dinámico que se ha realizado en un codificador que produce el flujo de bits. Basándose en los parámetros DRC de preprocesamiento, el sistema de decodificación puede cancelar la limitación del rango dinámico del lado del codificador. Preferiblemente, las señales se dividen en bloques de tiempo y los parámetros DRC de preprocesamiento DRC2 se definen con una resolución de un bloque de tiempo de la señal; como tal, cada valor

de los parámetros DRC2 se aplica al menos a un bloque de tiempo, y es posible asociar cada bloque de tiempo con un valor particular que es específico para ese bloque de tiempo. Sin alejarse aún del alcance de la invención, los valores de los parámetros DRC2 pueden ser constantes para varios bloques consecutivos. Por ejemplo, el valor de los parámetros DRC2 puede actualizarse solo una vez en cada período de tiempo, que comprende una pluralidad de bloques de tiempo, durante los cuales, por lo tanto, los parámetros DRC2 son constantes.

Una ventaja asociada con la primera realización de ejemplo es que los parámetros DRC de preprocesamiento DRC2 ofrece al sistema de decodificación la opción de restaurar la señal de audio a su rango dinámico original en aquellos intervalos de tiempo en los que el codificador, por cualquier motivo, ha realizado una limitación (o compresión) del rango dinámico. La restauración puede consistir en cancelar la limitación del rango dinámico, es decir, aumentar (o potenciar) el rango dinámico. Una posible razón para limitar un rango dinámico en el codificador puede ser evitar el recorte. Si se ha de aplicar o no la restauración puede depender, por ejemplo, de la información ingresada manualmente por el usuario, de las propiedades detectadas automáticamente del equipo de reproducción, de un nivel de DRC de destino obtenido de una fuente externa o de otros factores. El nivel de DRC de destino puede expresar una fracción del control de rango dinámico de posprocesamiento original (cuantificado por los parámetros DRC de posprocesamiento DRC1) que se ha de aplicar por el sistema de decodificación. Puede expresarse mediante un parámetro  $f \in [0,1]$  que modifica la cantidad de DRC a ser aplicada de DRC1 a  $f \times DRC1$  (en unidades logarítmicas).

En una implementación simple, el parámetro DRC2 puede codificarse en forma de un factor de ganancia de amplio espectro (o banda ancha) representado en forma logarítmica como un valor dB positivo, que cuantifica la disminución de amplitud relativa que ya ha experimentado la señal. Por lo tanto, suponiendo que  $DRC2 = x > 0$ , el cambio de amplitud relativa en el lado del codificador fue  $10^{-x/20} < 1$ , de modo que la cancelación puede consistir en escalar la señal en  $10^{+x/20} > 1$  en el lado del decodificador.

La cancelación real puede ser total o parcial, dependiendo del nivel de DRC de destino y del nivel de DRC de entrada (o nivel de DRC de entrada del decodificador), es decir, el nivel de DRC que tendrá la señal de audio del canal n después de la reconstrucción en ausencia de cualquier compresión de rango dinámico o potenciación de rango dinámico. El nivel de DRC de entrada puede ser el rango dinámico original reducido en una cantidad correspondiente a los parámetros DRC de preprocesamiento DRC2. El nivel de DRC de destino puede ser el rango dinámico original reducido en una cantidad correspondiente al producto del parámetro f y los parámetros DRC de posprocesamiento DRC1, es decir,  $f \times DRC1$  (en unidades logarítmicas). En la implementación simple mencionada anteriormente, la condición  $f \times DRC1 < DRC2$  puede implicar una cancelación parcial, es decir, por una cantidad correspondiente a  $DRC2 - f \times DRC1$  en lugar de DRC2. Por ejemplo, si el nivel de DRC de destino corresponde al nivel de DRC de entrada (por ejemplo, el rango dinámico de la señal de audio codificada originalmente por el codificador que produce el flujo de bits), que puede expresarse como  $f = 0$ , entonces se requiere una cancelación completa, en una cantidad DRC2. Si el nivel de DRC de destino es menor que el nivel de DRC de entrada, como es el caso cuando  $0 < f < 1$  y  $f \times DRC1 < DRC2$ , es suficiente cancelar parcialmente la limitación del rango dinámico. Si el nivel de DRC de destino es mayor que el nivel de DRC de entrada, según  $f \times DRC1 > DRC2$ , el nivel de DRC especificado se puede lograr realizando una mayor compresión de rango dinámico en el decodificador, es decir, en una cantidad correspondiente a  $f \times DRC1 - DRC2$ . En este caso, no es necesario cancelar inicialmente el preprocesamiento del DRC. Finalmente, si el nivel de DRC de destino es la cantidad total de DRC cuantificada por DRC1, como se expresa por  $f = 1$ , entonces depende de si  $DRC1 < DRC2$  o  $DRC1 > DRC2$ , si se debe realizar una cancelación parcial de la limitación del rango dinámico del lado del codificador o una compresión adicional.

En una segunda realización de ejemplo, se proporciona un método para la reconstrucción de una señal de audio X de canal n sobre la base de un flujo de bits. De acuerdo con el método, la recepción de un flujo de bits que contiene cada uno de una señal central codificada Ÿ, uno o más parámetros de codificación multicanal  $\alpha$  y parámetros DRC de preprocesamiento DRC2 (como se definió anteriormente) desencadena las siguientes acciones:

- la señal central codificada se decodifica en una señal Y central de canal m, donde  $1 \leq m < n$ ;

- se realiza una síntesis espacial paramétrica, de modo que la señal de canal n se reconstruye basándose en la señal central y los parámetros de codificación multicanal.

De acuerdo con la segunda realización de ejemplo, la decodificación incluye la cancelación de la limitación del rango dinámico del lado del codificador basándose en los parámetros DRC2.

La primera y segunda realización de ejemplo son funcionalmente similares y generalmente comparten las mismas ventajas.

En la primera realización de ejemplo, el sistema de decodificación recibe además, como parte del flujo de bits y todavía cuando el sistema está en el modo de codificación paramétrica, uno o más parámetros DRC de posprocesamiento compensados DRC3, que cuantifican un DRC que puede ser aplicado por el decodificador. La

aplicación del DRC puede estar sujeta a la entrada manual del usuario, propiedades detectadas automáticamente del equipo de reproducción o similares; como tal, el DRC a ser aplicado por el decodificador puede efectuarse completamente, parcialmente o no efectuarse en absoluto. En términos generales, los parámetros DRC de preprocesamiento DRC2 son útiles para potenciar el rango dinámico en relación con el nivel 5 de DRC de entrada, mientras que los parámetros DRC de posprocesamiento compensados DRC3 son útiles para realizar cualquier ajuste al rango dinámico desde el nivel de DRC de entrada, incluida también la compresión de rango. Los parámetros DRC3 pueden representarse en forma logarítmica como un valor dB positivo o negativo. Por lo tanto, suponiendo que  $DRC3 = y > 0$ , el cambio de amplitud relativa que se efectuará 10 en el lado del decodificador es proporcional a  $10^{-y/20}$ , que es un escalar en el intervalo (0,1). Por el contrario, un valor negativo de DRC3 provocará un aumento de escala en el lado del decodificador.

En un desarrollo adicional de lo anterior, el sistema de decodificación incluye un procesador DRC capaz de cancelar la compresión del rango dinámico del lado del codificador basándose en el parámetro DRC2. Opcionalmente, el procesador DRC puede cancelar una fracción de la compresión del rango dinámico que se ha 15 aplicado en el lado del codificador, como se expresa mediante el parámetro f discutido anteriormente.

En un desarrollo adicional, el sistema de decodificación incluye además un preprocesador DRC que controla el procesador DRC y el decodificador de señal central y es responsable de alcanzar un nivel de DRC de destino. Como tal, el preprocesador DRC puede determinar si el nivel de DRC de destino (por ejemplo,  $f \times DRC1$ ) es 20 mayor o menor que el nivel de DRC de entrada, que puede ser el rango dinámico de la señal de audio originalmente codificada y luego reducida por el DRC del lado del codificador cuantificado por el parámetro DRC de preprocesamiento DRC2. Si, basándose en el resultado de esta determinación, es necesario potenciar la señal de audio decodificada, el preprocesador DRC (i) le indica al procesador DRC que cancele parcial o 25 totalmente la limitación del rango dinámico del lado del codificador. Si, en cambio, es necesario comprimir la señal de audio decodificada (por ejemplo,  $f \times DRC1 > DRC2$ ), el preprocesador DRC le indica al procesador DRC que (ii) efectúe parcial o completamente el DRC del lado del decodificador a ser aplicado, como se cuantifica mediante los parámetros DRC3. Si el nivel de DRC de destino no difiere significativamente del nivel de DRC de entrada (por ejemplo,  $f \times DRC1 \approx DRC2$ ), el preprocesador de DRC no necesita realizar ninguna acción. En el 30 funcionamiento normal, ambas operaciones (i) y (ii) no se realizan respecto del mismo bloque de tiempo.

En una realización de ejemplo, el sistema de decodificación puede funcionar además en un modo de decodificación discreto, para reconstruir la señal de audio sobre la base de un flujo de bits que contiene una señal X de canal n codificada. Por lo tanto, esta realización proporciona un sistema de decodificación de modo dual o de modo múltiple. Desde el punto de vista de la codificación adaptativa, el modo de codificación discreta 35 puede representar un modo de alta tasa de bits, mientras que el modo de codificación paramétrica típicamente corresponde a un modo de tasa de bits más baja.

En una realización de ejemplo, el sistema de decodificación es de tipo modo dual, es decir, puede funcionar en un modo de codificación paramétrica o en un modo de codificación discreta. El sistema de decodificación está 40 habilitado para aplicar DRC del lado del decodificador en cada uno de estos modos. En el modo de codificación discreta, el sistema de decodificación usa los parámetros DRC de posprocesamiento DRC1 como guía para el DRC. Sin embargo, en el modo de codificación paramétrica, la señal de audio de canal n se genera sobre la base de una señal central que se ha derivado potencialmente en relación con la limitación del rango dinámico en el lado del codificador, al menos en algunos bloques de tiempo. Para tener en cuenta el cambio de rango dinámico 45 que ya se ha producido (es decir, la limitación del rango dinámico en algunos bloques de tiempo), el sistema de decodificación usa los parámetros DRC de posprocesamiento compensados DRC3 como guía para el DRC. Tanto los parámetros DRC1 como DRC3 se pueden derivar del flujo de bits, pero durante el funcionamiento normal del sistema, no ambos, sino solo uno de los tipos de parámetros se puede derivar en un bloque de tiempo determinado. Incluir ambos parámetros DRC1 y DRC3 equivaldría a enviar información redundante cuando están 50 presentes los parámetros DRC2. El sistema de decodificación de esta realización de ejemplo usa el parámetro DRC2 para adaptar el parámetro DRC1 a la escala del parámetro DRC3 o para adaptar el parámetro DRC3 a la escala del parámetro DRC1. Por ejemplo, el sistema de decodificación puede incluir un compensador descendente DRC que recibe los parámetros DRC2 y DRC3 y emite, basándose en ellos, parámetros DRC de posprocesamiento restaurados a ser aplicados por el sistema de decodificador. Los parámetros DRC de posprocesamiento restaurados serán entonces comparables con (en la misma escala que) los parámetros DRC de posprocesamiento DRC1. En otras palabras, el DRC del lado del decodificador expresado por los parámetros DRC restaurados es cuantitativamente equivalente a la combinación de la limitación del rango dinámico del lado 55 del codificador de la señal central y el DRC del lado del decodificador expresado por los parámetros DRC de posprocesamiento compensados DRC3. En la implementación simple mencionada anteriormente, la relación entre los respectivos parámetros DRC puede ser la siguiente: los parámetros DRC restaurados se obtienen como DRC2 + DRC3, que es igual a DRC1.

En un ejemplo no reivindicado se proporciona un sistema de codificación para codificar una señal de audio X de canal n dividida en bloques de tiempo como un flujo de bits P. El sistema de codificación comprende:

- una etapa de análisis paramétrico para recibir la señal de canal  $n$  y emitir, basándose en ella y en un modo de codificación paramétrica del sistema de codificación, una señal central  $Y$  de canal  $m$  y uno o más parámetros de codificación multicanal  $\alpha$ , donde  $1 \leq m < n$ ; y

5     • un codificador de señal central para recibir la señal central y emitir una señal central codificada  $\tilde{Y}$ .

En el sistema de codificación, la etapa de análisis paramétrico está configurada para realizar una limitación de rango dinámico adaptativa sobre una base de segmento de tiempo y para generar parámetros DRC de preprocesamiento DRC2 que cuantifiquen la limitación de rango dinámico aplicada. El segmento de tiempo puede ser un bloque de tiempo o una pluralidad de bloques de tiempo consecutivos, tal como un período de tiempo que comprende seis bloques de tiempo. El sistema de codificación está configurado para transmitir los parámetros DRC de preprocesamiento DRC2 junto con el flujo de bits, preferiblemente pero no necesariamente como parte del mismo. Al transmitir los parámetros de preprocesamiento DRC2, el sistema de codificación permite que un sistema de decodificación que recibe el flujo de bits cancele la limitación del rango dinámico que la etapa de análisis paramétrico ha impuesto a la señal central. Si la limitación del rango dinámico se realiza a nivel de bloques de tiempo, los parámetros DRC2 tienen resolución de bloque de tiempo. Alternativamente, si la limitación del rango dinámico se realiza sobre una base de tramas, los parámetros DRC2 tienen una resolución de una trama. En otras palabras, cada bloque de tiempo está asociado a un valor específico de los parámetros DRC2 o a una referencia a un valor previamente definido, pero este valor puede actualizarse a nivel de trama o de bloque. Además, la limitación del rango dinámico en la etapa de análisis paramétrico se puede realizar directamente en la señal central (por ejemplo, aplicando la limitación del rango dinámico en la señal central) o indirectamente (por ejemplo, aplicando la limitación del rango dinámico en una señal de la que se deriva la señal central).

25 De acuerdo con un desarrollo adicional del ejemplo anterior, el sistema de codificación puede funcionar tanto en un modo de codificación paramétrica como en un modo de codificación discreta. Para habilitar DRC en el lado del decodificador, el codificador está configurado para derivar uno o más parámetros DRC de posprocesamiento DRC1 que cuantifican un DRC del lado del decodificador a ser aplicado. Los parámetros DRC1 se emiten en el modo de codificación discreta. Sin embargo, en el modo de codificación paramétrica, los parámetros DRC1 se compensan para tener en cuenta cualquier limitación del rango dinámico que ya haya sido realizada por la etapa de análisis paramétrico. La salida de este proceso de compensación incluye parámetros DRC de posprocesamiento compensados DRC3. El principio rector del proceso de compensación puede ser que el DRC del lado del decodificador expresado por los parámetros DRC de posprocesamiento sea cuantitativamente equivalente a la combinación de la limitación del rango dinámico aplicada por la etapa de análisis paramétrico (cuantificada por los parámetros DRC2) y el DRC del lado del decodificador (cuantificado por los parámetros DRC de posprocesamiento compensados DRC3). Preferiblemente, los tres tipos de parámetros se expresan en escalas compatibles, por ejemplo, usando unidades lineales o logarítmicas correspondientes. En la implementación simple mencionada anteriormente, la relación entre los parámetros DRC puede ser la siguiente (aún en escala logarítmica): los parámetros DRC de posprocesamiento compensados se obtienen como  $DRC_1 - DRC_2$ .

30     35     40

En otro ejemplo no reivindicado, un método de codificación incluye:

- recibir una señal de audio  $X$  de canal  $n$  dividida en bloques de tiempo;

- 45     • generar una señal central  $Y$  de canal  $m$  y uno o más parámetros  $\alpha$  de codificación multicanal, mientras se realiza una limitación de rango dinámico en base a un bloque de tiempo y generar uno o más parámetros DRC de preprocesamiento DRC2, que cuantifican la limitación de rango dinámico aplicada; y

- 50     • emitir un flujo de bits  $P$  que contiene la señal central, los parámetros de codificación multicanal y los parámetros DRC de preprocesamiento DRC2.

En un ejemplo adicional no reivindicado, se proporciona una estructura de datos para el almacenamiento o transmisión de una señal de audio. La estructura incluye una señal central  $Y$  de canal  $m$ , uno o más parámetros  $\alpha$  de mezcla y uno o más parámetros DRC de preprocesamiento DRC2 que cuantifican una limitación del rango dinámico del lado del codificador. La estructura es susceptible de decodificación mediante una combinación lineal de canal  $n$  de los canales de señal de mezcla descendente (y posiblemente, de canales en una señal decorrelacionada), en donde dichos uno o más parámetros de mezcla controlan al menos una ganancia en la combinación lineal, y cancelando la limitación del rango dinámico del lado del codificador. En particular, se proporciona un medio legible por ordenador que almacena información estructurada de acuerdo con la estructura de datos anterior. En la estructura de datos, los parámetros DRC de preprocesamiento DRC2 pueden codificarse como un campo de 3 bits que representa un exponente y un campo asociado de 4 bits que representa una mantisa; al decodificar, el exponente y la mantisa se combinan en un valor escalar que corresponde a un valor de ganancia. Como alternativa, los parámetros DRC de preprocesamiento DRC2 pueden codificarse como un campo de 2 bits que representa un exponente y un campo asociado de 5 bits que representa una mantisa.

55     60     65

## II. Ejemplos: Lado de codificación

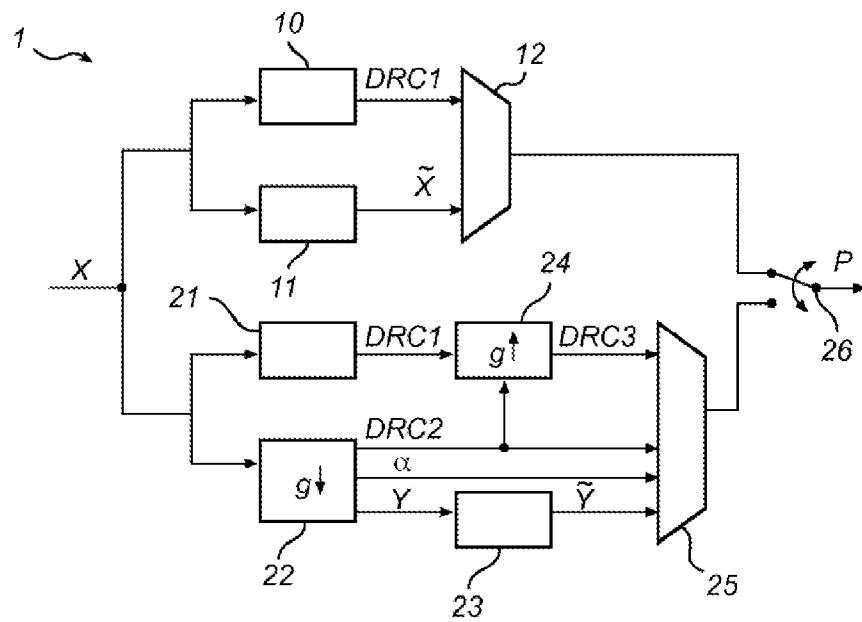

- 5 La figura 1a muestra, en forma de diagrama de bloques generalizado, un sistema 1 de codificación de modo dual de acuerdo con una realización de ejemplo. Se proporciona una señal de audio X de canal n a cada una de una porción superior, que está activa al menos en un modo de codificación discreto del sistema 1 de codificación, y una porción inferior, que está activa al menos en un modo de codificación paramétrica del sistema 1.

- 10 La porción superior generalmente consiste en un analizador DRC de modo discreto 10 dispuesto en paralelo con un codificador 11, ambos reciben la señal de audio como entrada X. Basándose en esta señal, el codificador 11 emite una señal de canal n codificada  $\tilde{X}$ , mientras que el analizador DRC 10 emite uno o más parámetros DRC de posprocesamiento DRC1 que cuantifican un DRC del lado del decodificador a ser aplicado. Las salidas paralelas de ambas unidades 10, 11 son reunidas por un multiplexor 12 de modo discreto, que emite un flujo de bits P.

- 15 La porción inferior del sistema 1 de codificación comprende una etapa 22 de análisis paramétrico dispuesta en paralelo con un analizador DRC de modo paramétrico 21 que recibe, como etapa 22 de análisis paramétrico, la señal de audio X de canal n. Basándose en la señal de audio X de canal n, la etapa 22 de análisis paramétrico genera uno o más parámetros de codificación multicanal, colectivamente denotados por  $\alpha$ , y una señal central de canal m ( $1 \leq m < n$ ) Y, que a continuación es procesada por un codificador 23 de señal central, que emite, basándose en ello, una señal central codificada  $\tilde{Y}$ . Como lo sugiere la notación  $g_1$ , la etapa 22 de análisis paramétrico efectúa una limitación de rango dinámico en bloques de tiempo donde esto es necesario. Una posible condición que controla cuándo aplicar la limitación del rango dinámico puede ser una "condición de no recorte" o una "condición dentro del rango", lo que implica, en segmentos de tiempo donde la señal central tiene alta amplitud, que la señal se procesa de manera que se ajuste dentro del rango definido. La condición puede aplicarse sobre la base de un bloque de tiempo o de un período de tiempo que comprenda varios bloques de tiempo. Preferiblemente, la condición se aplica aplicando una reducción de ganancia de amplio espectro en lugar de truncar solo los valores pico o usar enfoques similares. Como es bien sabido en la técnica, existen técnicas para hacer que una operación de limitación temporal del rango dinámico sea menos perceptible, si la limitación solo se requiere para un conjunto específico de bloques de tiempo, como por ejemplo aplicando y/o liberando la limitación gradualmente. En particular, el sistema 1 puede comprender un bucle de retroalimentación (no mostrado) configurado para suavizar los parámetros DRC. Por ejemplo, un valor de parámetro actual que se va a emitir se puede obtener como la suma de una fracción  $0 < a < 1$  del valor de parámetro del segmento anterior y una fracción ( $1 - a$ ) de un valor de parámetro resultante de la aplicación de la "condición de no recorte" en el segmento actual. Por supuesto, los parámetros DRC de posprocesamiento DRC1 y los parámetros DRC de preprocesamiento DRC2 se pueden suavizar de forma independiente y con diferentes valores de la constante a.

- 30 La figura 5 muestra una posible implementación de la etapa 22 de análisis paramétrico, que comprende un preprocesador 527 y un procesador 528 de análisis paramétrico. El preprocesador 527 es responsable de realizar la limitación del rango dinámico en la señal de canal n X, con lo que emite una señal de canal n  $X_c$  con rango dinámico limitado, que se suministra al procesador 528 de análisis paramétrico. El preprocesador 527 emite además un valor por bloque o por trama de los parámetros DRC de preprocesamiento DRC2. Junto con los parámetros  $\alpha$  de codificación multicanal y una señal central Y de canal m del procesador 528 de análisis paramétrico, los parámetros DRC2 se incluyen en la salida de la etapa 22 de análisis paramétrico.

- 35

- 40

- 45 Con referencia nuevamente a la figura 1a, se observa que el analizador DRC 10 de modo discreto funciona de manera similar al analizador DRC 21 de modo paramétrico en que emite uno o más parámetros DRC de posprocesamiento DRC1 que cuantifican un lado del decodificador a ser aplicados. Sin embargo, los parámetros DRC1 proporcionados por el analizador DRC 21 de modo paramétrico no deben incluirse en el flujo de bits en el modo de codificación paramétrica, sino que deben someterse a una compensación para tener en cuenta la limitación del rango dinámico realizada por la etapa 22 de análisis paramétrico. Para este propósito, un compensador ascendente DRC 24 recibe los parámetros DRC de posprocesamiento DRC1 y los parámetros DRC de preprocesamiento DRC2. Para cada bloque de tiempo, el compensador ascendente DRC 24 deriva un valor de uno o más parámetros DRC de posprocesamiento compensados DRC3, que son tales que la acción combinada de los parámetros DRC de posprocesamiento compensados DRC3 y los parámetros DRC de preprocesamiento DRC2 es cuantitativamente equivalente al DRC cuantificado por los parámetros DRC de posprocesamiento DRC1. En otras palabras, el compensador ascendente DRC 24 está configurado para reducir los parámetros DRC de posprocesamiento emitidos por el analizador DRC 21 en la parte de los mismos (si la hay) que ya ha sido efectuada por la etapa 22 de análisis paramétrico. Son los parámetros DRC de posprocesamiento compensados DRC3 los que se deben incluir en el flujo de bits. Siguiendo en referencia a la porción inferior del sistema 1, un multiplexor 25 de modo paramétrico recoge los parámetros DRC de posprocesamiento compensados DRC3, los parámetros DRC de preprocesamiento DRC2, los parámetros  $\alpha$  de codificación multicanal y la señal central codificada  $\tilde{Y}$  y forma, basándose en ellos, un flujo de bits P. En una posible implementación, los parámetros DRC de posprocesamiento compensados DRC3 y los parámetros DRC de preprocesamiento DRC2 pueden codificarse en forma logarítmica como valores dB que influyen en un aumento o disminución de escala de amplitud en el lado del decodificador. Los parámetros DRC de

posprocesamiento compensados DRC3 pueden tener cualquier signo. Sin embargo, los parámetros DRC de preprocesamiento DRC2, que resultan de la aplicación de una "condición de no recorte" o similar, estarán representados por un valor dB no negativo en todo momento.

- 5 Común a la porción superior e inferior del sistema 1 de codificación, un selector 26 (que simboliza cualquier medio de selección de señal implementado por hardware o software) determina, dependiendo del modo de codificación real, si el flujo de bits de la porción superior o inferior del sistema 1 de codificación debe constituir la salida final del sistema 1 de codificación. De manera similar, se puede proporcionar un conmutador (no mostrado en la figura 1a) en el lado de entrada del sistema 1 para dirigir la señal de audio X a la porción superior o inferior del sistema 1. El conmutador del lado de entrada puede accionarse en correspondencia con el conmutador 26 del lado de salida.

Con referencia a la figura 1a así como a las figuras que se discutirán a continuación, el flujo de bits P puede codificarse en un formato conforme a Dolby Digital Plus (DD+ o E-AC-3, AC-3 mejorado). El flujo de bits incluye entonces al menos los campos de metadatos dynrng y compr. De acuerdo con una especificación de DD+, dynrng tiene una resolución de un bloque de tiempo, mientras que compr tiene una resolución de una trama, que comprende cuatro o seis bloques de tiempo. Con respecto a la importancia de estos campos de metadatos, los parámetros DRC de posprocesamiento DRC1 definidos anteriormente corresponden a dynrng o compr, dependiendo, por ejemplo, de si la "compresión pesada" está activada, lo que funciona de una manera que asegura que una mezcla descendente monofónica no superará un cierto nivel de pico. En circunstancias normales, se transmiten tanto el campo dynrng como el compr y es el decodificador quien decide cuál usar. Por lo tanto, los parámetros DRC de posprocesamiento DRC1, que pueden tener una resolución por bloques o por tramas, se pueden transmitir en porciones heredadas del formato y serán comprendidos por los decodificadores heredados. Sin embargo, los parámetros DRC de preprocesamiento DRC2 carecen de una contraparte en el formato DD+ y se codifican preferiblemente en un nuevo campo de metadatos. Se recuerda que los parámetros de preprocesamiento DRC2 se relacionan con la parte de dynrng y/o compr que garantiza que la señal no se recortará cuando se mezcle del formato 5.1 ( $n = 6$ ) al formato estéreo ( $m = 2$ ). Los parámetros DRC de posprocesamiento compensados DRC3 son el resultado después de compensar el valor dynrng o compr deduciendo la prevención de recorte cuantificada por los parámetros DRC de preprocesamiento DRC2; por lo tanto, se pueden transmitir en el campo dynrng o compr en el flujo de bits DD+.

El nuevo campo de metadatos para los parámetros DRC de preprocesamiento DRC2 puede incluir 7 bits (xxxxyyy), donde los bits en las posiciones x representan un entero en [0, 3] y los bits en las posiciones y representan un entero en [0, 31]. El parámetro DRC de preprocesamiento DRC2 se obtiene como factor de ganancia  $(1+y/32)\times2^x$ .

Otro parámetro de metadatos en el formato DD+ es dialnorm, que es un nivel de sonoridad del contenido (posiblemente promediado en el tiempo). En las realizaciones de ejemplo, el nivel de referencia de salida de destino  $L_T$  es una configuración en la configuración del decodificador, posiblemente controlada por el usuario. Para alcanzar el nivel de referencia de salida de destino  $L_T$ , un sistema de decodificación debe aplicar una atenuación estática cuantificada por la dialnorm de diferencia -  $L_T$ . Para obtener la atenuación total que se debe aplicar, el sistema de decodificación debe aumentar esta diferencia con cualquier atenuación adicional estipulada por los parámetros DRC de posprocesamiento (no compensados) DRC1 o los parámetros DRC de posprocesamiento compensados DRC3 o un DRC de destino expresado como una fracción  $f \times DRC1$  de los parámetros DRC de posprocesamiento. Esto produce: dialnorm -  $L_T + DRC1$  o dialnorm -  $L_T + DRC3$  o dialnorm -  $L_T + f \times DRC1$ , respectivamente. Si una de estas tres combinaciones lineales es de signo positivo, estipula que se debe aplicar una cantidad distinta de cero de atenuación total en el sistema de decodificación; un signo negativo estipula que la señal debe ser potenciada efectivamente.

La figura 7 muestra, de acuerdo con otra realización de ejemplo, un sistema 701 de codificación que funciona de manera similar al sistema 1 de codificación mostrado en la figura 1a. Debido a que se han usado símbolos de referencia análogos y la notación relacionada con las señales es consistente con la de la figura 1a, se cree que no es necesaria una descripción detallada de los principios de funcionamiento del sistema 701 de codificación. Sin embargo, una diferencia importante radica en el hecho de que un analizador DRC 721 cumple las tareas tanto del analizador DRC 10 de modo discreto como del analizador DRC 21 de modo paramétrico en la figura 1a. Para este propósito, el analizador DRC 721 recibe la señal de audio X de canal n a codificar por el sistema 701 de codificación; suministra parámetros DRC de posprocesamiento DRC1, que genera sobre la base de la señal de audio X de canal n, tanto a un multiplexor de modo discreto 712 como a un compensador ascendente DRC 724, donde el último componente es funcionalmente equivalente al compensador ascendente DRC 24 en el sistema 1 de codificación de la figura 1a.

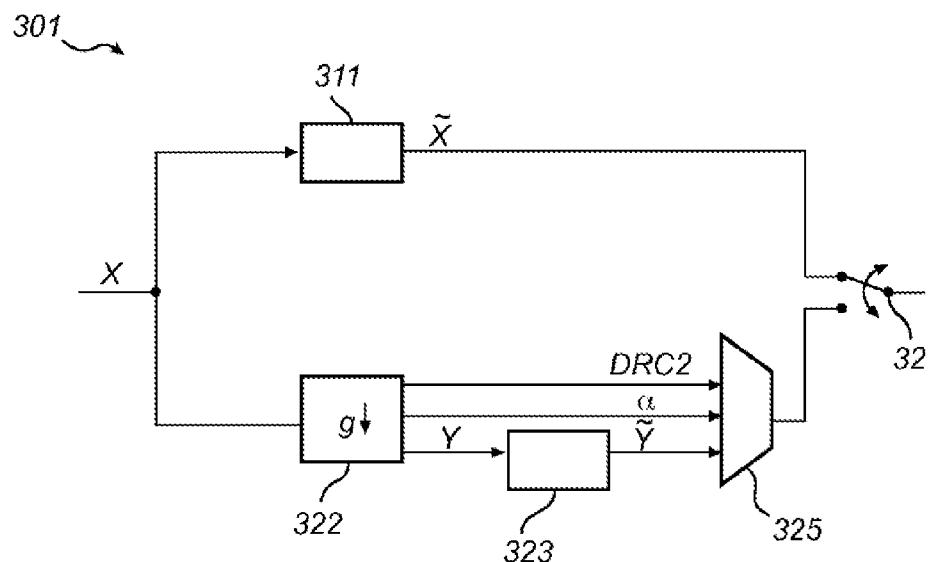

La figura 3 muestra un sistema 301 de codificación, que es relativamente más simple que el de la figura 1a en la medida en que no produce ningún parámetro DRC de posprocesamiento como salida. Como tal, un decodificador que recibe un flujo de bits P producido por el sistema 301 de codificación no necesariamente será capaz de realizar una compresión de rango dinámico. Sin embargo, un decodificador de este tipo será capaz de cancelar cualquier limitación de rango dinámico aplicada por el sistema 301 de codificación; típicamente, esto equivale a

potenciar el rango dinámico en bloques de tiempo donde la señal de audio X de canal n incluye picos de amplitud relativamente alta.

- 5 En la figura 3, la porción superior del sistema 301 de codificación, que está activa al menos en el modo de codificación discreta del sistema 301 de codificación, no necesita incluir más que un codificador 311 configurado para proporcionar una señal de canal n codificada X sobre la base de la señal de canal n X que será codificada por el sistema 301. La porción inferior, correspondiente a un modo de codificación discreto, comprende menos componentes que la porción análoga del sistema de codificación de la figura 1a, a saber, una etapa 322 de análisis paramétrico que genera, basándose en la señal de audio X de canal n, parámetros DRC de preprocesamiento DRC2, parámetros de codificación multicanal  $\alpha$  y una señal central Y de canal m. Después de que la señal central Y ha sido procesada en un codificador 323 de señal central, que la transforma en una señal central codificada  $\tilde{Y}$ , el conjunto de salidas de la etapa 322 de análisis paramétrico se combina en un flujo de bits P mediante un multiplexor 325 de modo paramétrico. Un selector 326 dispuesto aguas abajo de las porciones superior e inferior del sistema 301 de codificación es responsable de emitir el flujo de bits producido por cualquiera de las porciones superior e inferior, en dependencia del modo de codificación actual del sistema 301 de codificación.

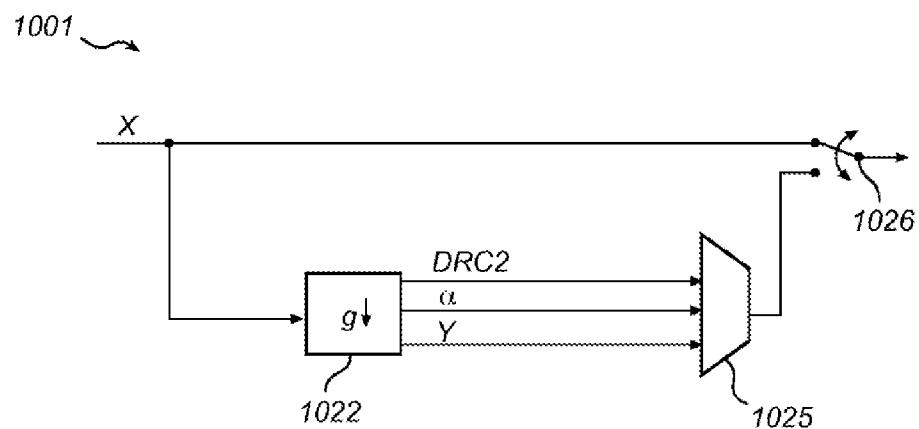

- 20 Un sistema 1001 de codificación mostrado en la figura 10 representa una simplificación adicional. Este sistema 1001 de codificación está adaptado para procesar una señal de audio X de canal n que está en un formato adecuado para almacenamiento o transporte sin ninguna operación de codificación adicional. Por lo tanto, en el modo de codificación discreta, la señal de audio X puede emitirse desde el sistema 1001 de codificación sin ningún procesamiento adicional, como lo ilustra la posición del selector 1026 que se muestra en la figura 10. En el modo de codificación paramétrica, una etapa 1022 de análisis paramétrico analiza la señal de audio X de canal n para generar parámetros DRC de preprocesamiento DRC2, parámetros de codificación multicanal  $\alpha$  y una señal central Y de canal m. La etapa 1022 de análisis paramétrico está configurada para operar sobre la señal de audio de canal n también cuando esta, como se indicó, está en un formato adecuado para transporte o almacenamiento. En el sistema 1001 de codificación de la figura 10, la señal central Y también está en un formato habilitado para transporte o almacenamiento, de modo que esta señal, junto con los parámetros de codificación multicanal  $\alpha$  y los parámetros DRC2, puede combinarse mediante un multiplexor 1025 de modo paramétrico en un flujo de bits que se emitirá desde el sistema 1001 de codificación en el modo de codificación paramétrica.

- 35 La figura 1b ilustra un sistema de codificación monomodo de acuerdo con una realización de ejemplo. Se proporciona una señal de audio X de canal n a un analizador DRC 21 y a una etapa 22 de análisis paramétrico, que están dispuestos en paralelo. A partir de la señal de audio X de canal n, la etapa 22 de análisis paramétrico genera uno o más parámetros de codificación multicanal, denominados colectivamente  $\alpha$ , y una señal central Y de canal m ( $1 \leq m < n$ ), que a continuación es procesada por un codificador 23 de señal central, que genera, basándose en ello, una señal central codificada  $\tilde{Y}$ . La etapa 22 de análisis paramétrico efectúa una limitación del rango dinámico en bloques de tiempo cuando esto es necesario. Un compensador ascendente DRC 24 recibe los 40 parámetros DRC de posprocesamiento DRC1 y los parámetros DRC de preprocesamiento DRC2. Para cada bloque de tiempo (en este ejemplo, la resolución con la que se generan los valores de los parámetros DRC de posprocesamiento DRC1 es un bloque de tiempo), el compensador ascendente DRC 24 deriva un valor de uno o más parámetros DRC de posprocesamiento compensados DRC3, que son tales que la acción combinada de los 45 parámetros DRC de posprocesamiento compensados DRC3 y los parámetros DRC de preprocesamiento DRC2 es cuantitativamente equivalente al DRC cuantificado por los parámetros DRC de posprocesamiento DRC1.

- 50 La figura 8 ilustra con mayor detalle un posible funcionamiento de los compensadores ascendentes DRC 24, 724 en las figuras 1 y 7. Cada uno de los compensadores ascendentes DRC 24, 724 está configurado para producir parámetros DRC de posprocesamiento compensados DRC3 basándose en los parámetros DRC de preprocesamiento DRC2 y los parámetros DRC de posprocesamiento DRC1. Cada barra se refiere a una trama de tiempo de la señal. Cada trama de tiempo está asociada con un valor de los parámetros DRC de preprocesamiento DRC2 y un valor de los parámetros DRC de posprocesamiento DRC1; en las figuras 8 y 9, pueden estar en unidades dB<sub>FS</sub> con signo negativo. Como indica la leyenda, las líneas continuas ilustran los 55 parámetros DRC de posprocesamiento DRC1, mientras que los otros dos tipos de parámetros DRC corresponden a diferentes patrones de sombreado. Cada valor de los parámetros DRC de posprocesamiento compensados DRC3 se produce basándose en la condición de que la acción combinada de los parámetros DRC de preprocesamiento DRC2 y los parámetros DRC de posprocesamiento compensados DRC3 sea cuantitativamente equivalente al DRC del lado del decodificador expresado por los parámetros DRC de posprocesamiento DRC1. Las figuras 8 y 9 están simplificadas en la medida en que el efecto del DRC de 60 acuerdo con un enfoque particular (cf. el artículo de Carroll y Riedmiller citado anteriormente) puede no ilustrarse fielmente mediante una cantidad escalar y lineal. Las figuras 8 y 9 probablemente transmiten una imagen bastante completa de la realización simplificada discutida anteriormente, en la que los parámetros DRC están codificados como escalares.

- 65 La figura 8 ilustra una situación en la que los parámetros DRC de posprocesamiento DRC1 son constantes dentro de cada trama de tiempo, de manera similar al parámetro compr en el formato DD+, como se explicó

anteriormente. Esto no tiene por qué ser siempre así. Por ejemplo, un analizador DRC de un tipo heredado puede configurarse para analizar un segmento de un número fijo de bloques de tiempo  $p_1$ , donde  $p_1$  puede ser igual a 4, 6, 8, 16, 24, 32, 64 o algún otro número entero significativamente menor que el número de bloques de tiempo que típicamente están presentes en un programa completo (por ejemplo, una canción, una pista, un episodio de un programa de radio). Este número  $p_1$  puede coincidir o no con el número  $p_2$  de tramas entre cada actualización de los parámetros DRC de preprocesamiento. La figura 8 se refiere al caso particular donde  $p_1 = 6$  y  $p_2 = 6$ . Preferiblemente, el número  $p_1$  es lo suficientemente pequeño como para que los parámetros DRC de posprocesamiento DRC1 se reevalúen al menos una vez por segundo de la señal de audio X, más preferiblemente varias decenas o cientos de veces por segundo de la señal de audio X.

La figura 9 muestra un caso de uso donde  $p_1 = 1$ , de manera similar al parámetro dynrng en el formato DD+. Sin embargo, la limitación del rango dinámico en la etapa 22, 722 de análisis paramétrico se realiza basándose en  $p_2 = 6$  bloques de tiempo a la vez, de modo que en consecuencia se produce un nuevo valor de los parámetros DRC de preprocesamiento DRC2 para cada sexto bloque de tiempo. Cada una de las barras más estrechas representa un bloque de tiempo. Los compensadores ascendentes 24, 724 pueden configurarse para determinar cada valor de los parámetros DRC de posprocesamiento compensados DRC3 de tal manera que el DRC del lado del decodificador expresado por los parámetros DRC de posprocesamiento DRC1 sea cuantitativamente equivalente a la combinación de la limitación de rango dinámico aplicada por la respectiva etapa 22, 722 de análisis paramétrico sobre cada bloque de tiempo y el DRC del lado del decodificador cuantificado por los parámetros DRC de posprocesamiento compensados DRC3.

### III. Realizaciones de ejemplo: Lado de decodificador

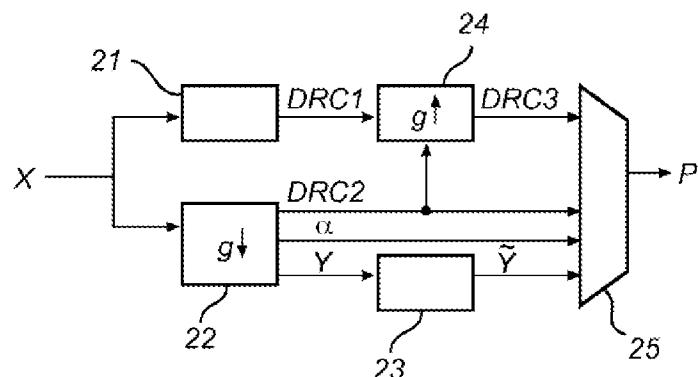

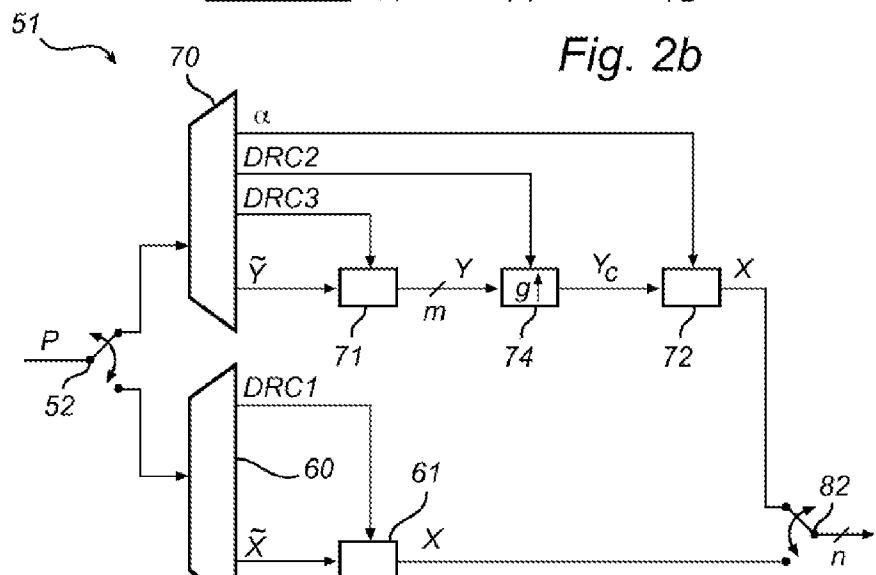

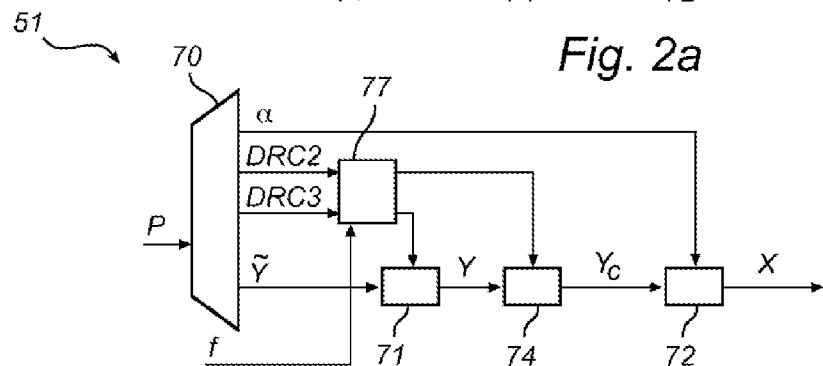

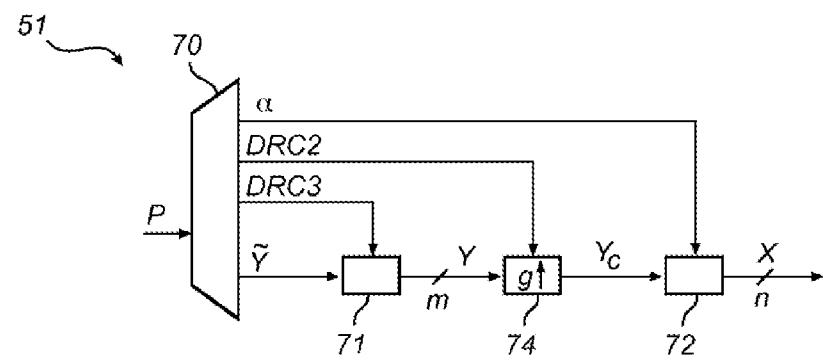

La figura 2a muestra un sistema 51 de decodificación monomodo que reconstruye una señal de audio de canal n sobre la base de un flujo de bits P. El flujo de bits P contiene una señal central codificada Ÿ, parámetros de codificación multicanal  $\alpha$ , parámetros DRC de preprocesamiento DRC2 y parámetros DRC de posprocesamiento compensados DRC3, siendo extraídas estas cantidades del flujo de bits por un demultiplexor 70 dispuesto a la entrada del sistema 51 de decodificación. Un decodificador 71 de señal central recibe la señal central codificada Ÿ y emite, basándose en ella, una señal central Y de canal m ( $1 \leq m < n$ ). En conexión con la decodificación, el decodificador 71 de señal central realiza además DRC según lo cuantificado por los parámetros DRC de posprocesamiento compensados DRC3. El decodificador 71 de señal central puede operar para efectuar una fracción del DRC completo expresado por los parámetros DRC de posprocesamiento compensados DRC3. Aguas abajo del decodificador 71 de señal central, se dispone un procesador DRC 74, que restaura el rango dinámico de la señal central, como sugiere la notación g†, cancelando la limitación del rango dinámico impuesta en el lado del codificador, como se cuantifica mediante los parámetros DRC de preprocesamiento DRC2. El procesador DRC 74 emite una señal intermedia Yc, que es equivalente a la señal central Y excepto en lo que respecta a su rango dinámico y que se introduce en una etapa 72 de síntesis paramétrica. La etapa 72 de síntesis paramétrica forma una combinación lineal de canal n de los canales m en la señal intermedia Yc, en donde las ganancias aplicadas son controlables por los parámetros de codificación multicanal  $\alpha$ , y genera una señal de audio de canal n reconstruida X. La combinación lineal en la etapa 72 de síntesis paramétrica puede incluir además una señal decorrelacionada derivada de la señal intermedia Yc o la señal central Y. La señal decorrelacionada puede además sufrir un procesamiento no lineal, tal como atenuación de artefactos. La señal decorrelacionada se puede producir en una unidad de modificación de señal central o en un decorrelacionador (no mostrado). En la realización simple esbozada en los pasajes anteriores, la cancelación en el procesador DRC 74 de la limitación del rango dinámico impuesta en el lado del codificador puede equivaler a escalar la señal de una manera de amplio espectro por un factor correspondiente a la inversa del parámetro DRC2, que cuantifica la limitación del rango de preprocesamiento.

La figura 2b muestra un sistema 51 de decodificación, algo más evolucionado que el de la figura 2a. El presente sistema 51 de decodificación dispone de un preprocesador DRC 77, que coordina la acción relacionada con DRC del decodificador 71 de señal central y del procesador DRC 74, respectivamente. Por una parte, el decodificador 71 de señal central puede comprimir el rango dinámico de la señal, hasta el límite definido por los parámetros de posprocesamiento compensados DRC3, o bien comprimir el rango dinámico. Por otra parte, el procesador DRC 74 puede potenciar el rango dinámico por completo, hasta el nivel que tenía antes de la codificación, o solo parcialmente. Con esta configuración, típicamente es posible alcanzar un nivel de DRC de destino determinado activando el procesamiento DRC solo en uno de los dos: el decodificador 71 de señal central y el procesador DRC 74. Si los parámetros de posprocesamiento compensados DRC3 indican una compresión de rango dinámico, entonces operar ambas unidades al mismo tiempo puede implicar cierto grado de contraacción mutua (cancelación mutua), lo que podría afectar negativamente la calidad de salida.

El preprocesador DRC 77 recibe tanto los parámetros DRC de preprocesamiento DRC2 como los parámetros DRC de posprocesamiento compensados DRC3. El preprocesador DRC 77 tiene además acceso a un nivel de DRC de destino predefinido o variable (por ejemplo, definido por el usuario), que se expresa mediante un parámetro f, por ejemplo,  $f \times DRC1$ , y un nivel de DRC de entrada de la señal correspondiente al rango dinámico original reducido por DRC2. El preprocesador DRC 77 decide, basándose en una comparación de los dos niveles DRC, si el nivel de DRC de destino se debe lograr mediante la compresión del rango dinámico en el

decodificador 71 de señal central o mediante la potenciación del rango dinámico en el procesador DRC 74. Para este propósito, el preprocesador DRC 77 emite señales de control dedicadas  $k_{71}$ ,  $k_{74}$ , que se suministran a cada uno del decodificador 71 de señal central y el procesador DRC 74.

- 5 A continuación se discutirá el comportamiento de las señales de control  $k_{71}$ ,  $k_{74}$  que deben suministrarse desde el preprocesador DRC 77 al decodificador 71 de señal central y al procesador DRC 74, respectivamente. La primera señal de control  $k_{71}$  controla qué fracción del DRC del lado del decodificador, cuantificada por los parámetros DRC de posprocesamiento compensados DRC3, debe ser aplicada por el decodificador 71 de señal central. En la realización simple discutida anteriormente, los cambios de ganancia relativa resultantes se dan por  $k_{71}^{DRC3}$

- 10 el factor  $10^{-20}$ , de modo que el valor máximo  $k_{71} = 1$  corresponde a la compresión máxima del rango dinámico, mientras que el valor mínimo de la señal corresponde a la ausencia de compresión del rango dinámico. La segunda señal de control  $k_{74}$  controla el grado en el cual el procesador DRC 74 debe cancelar la limitación del rango dinámico del lado del codificador. En la realización simple discutida anteriormente, el DRC 74 cambia la  $k_{74}^{DRC2}$

- 15 ganancia por el factor  $10^{-20}$ , donde el valor mínimo  $k_{74} = 0$  corresponde a la no cancelación y el valor máximo corresponde a una cancelación completa, restaurando la señal al 100 % de su rango dinámico original. El preprocesador DRC 77 puede configurarse para ejecutar un nivel de DRC de destino de manera diferente dependiendo de si corresponde a una potenciación de rango dinámico o a una compresión de rango dinámico en relación con el nivel de DRC de entrada, entendiéndose por tal el rango dinámico original reducido (o comprimido) en una cantidad DRC2. Además, el preprocesador DRC 77 puede configurarse para interpolar entre

- 20 los valores mínimos y máximos con el fin de lograr un nivel de DRC de destino que corresponda a una fracción de los parámetros DRC de preprocesamiento DRC2 o los parámetros DRC de posprocesamiento compensados DRC3. La interpolación también se puede usar para lograr un nivel de DRC de destino que se expresa como una fracción de los parámetros DRC de posprocesamiento no compensados DRC1. Cada una de las fracciones de DRC2 y DRC3 se puede calcular basándose en los parámetros f y DRC1, véase a continuación. A continuación

- 25 se describirá, en el contexto de dicha realización sencilla, cómo el preprocesador DRC 77 puede responder a un nivel de DRC de destino particular expresado como una fracción f de los parámetros DRC de posprocesamiento DRC1. En vista de la discusión en el párrafo anterior, el preprocesador DRC 77 debe asignar valores en [0,1] a los parámetros  $k_{71}$ ,  $k_{74}$  en la ecuación

$$30 \quad f \times DRC1 = k_{74} \times DRC2 + k_{71} \times DRC3,$$

donde  $f \in [0, 1]$  está predefinido,  $DRC2 \geq 0$  y  $DRC1 = DRC2 + DRC3$  (escala logarítmica). De lo anterior se desprende que DRC1 y DRC3 pueden ser positivos o negativos. Como se señaló anteriormente, generalmente es deseable evitar operar tanto el decodificador 71 de señal central como el procesador DRC 74 al mismo tiempo si la acción del decodificador 71 de señal central es compactar el rango ( $DRC3 = y > 0$ ). Esto equivale a resolver la ecuación anterior para  $k_{71} = 0$  o  $k_{74} = 0$ .

Otra posible representación es un factor de ganancia dependiente de la sonoridad, posiblemente en una escala logarítmica. Por ejemplo, un par de factores de ganancia pueden transmitirse junto con un nivel de diálogo. Se debe aplicar un primer factor de ganancia en los segmentos de tiempo más fuertes que el nivel del diálogo, mientras que el segundo factor de ganancia se debe aplicar en los segmentos de tiempo más bajos. Esto permite la compresión y extensión del rango dinámico, ya que al primer y segundo factor de ganancia se les pueden asignar valores mutuamente independientes.

- 45 La figura 2c muestra un sistema 51 de decodificación de modo dual, que está configurado para recibir un flujo de bits P que contiene una señal de audio que está codificada paramétricamente o codificada discretamente. En el modo paramétrico del sistema 51 de decodificación, una porción superior aguas abajo de un demultiplexor 70 de modo paramétrico está activa para proporcionar, de manera similar al funcionamiento del sistema mostrado en la figura 2a, una señal de audio X de canal n. En el modo discreto, el flujo de bits P se suministra a un demultiplexor 60 de modo discreto, que extrae una señal de canal n codificada X y uno o más parámetros DRC de posprocesamiento DRC1. Los selectores 52, 82 (que simbolizan cualquier medio de selección de señal implementado por hardware o software) en los lados de entrada y salida del sistema 51 de decodificación se operan de acuerdo con un modo actual; los selectores pueden operarse conjuntamente, de modo que ambos estén siempre en sus posiciones superiores o en sus posiciones inferiores. En el modo discreto, la señal de canal n codificada X es procesada por un decodificador 61, que puede ejecutar DRC de acuerdo con los parámetros DRC de posprocesamiento DRC1. La coherencia en el nivel de diálogo entre los modos de codificación discretos y paramétricos está garantizada por el hecho de que el sistema 51 de decodificación está configurado para usar los parámetros DRC de posprocesamiento compensados DRC3 en lugar de los parámetros DRC de posprocesamiento (no compensados) DRC1 en el modo paramétrico. La relación entre los parámetros DRC1 y DRC3 se ha discutido anteriormente.

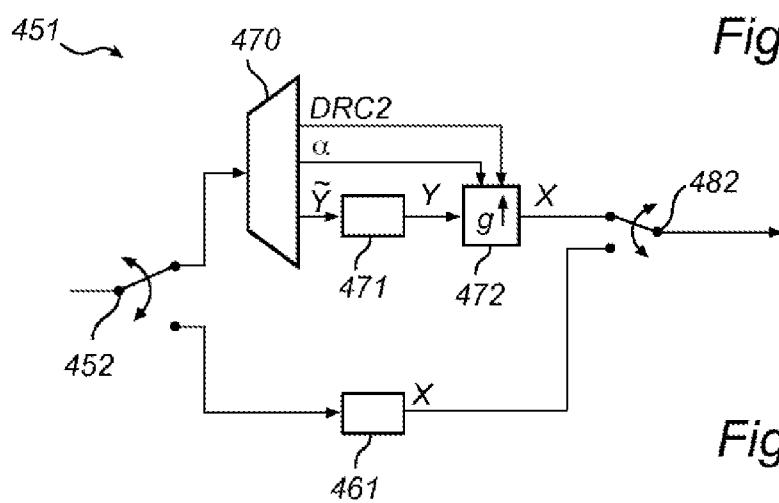

- 55 La figura 4 es un diagrama de bloques generalizado de un sistema 451 de decodificación simplificado no reivindicado, que carece de la capacidad de realizar un DRC de posprocesamiento. Sin embargo, el sistema de

decodificación 451 de la figura 4 puede cancelar la limitación de rango dinámico aplicada en el lado del codificador, tal como se cuantifica mediante los parámetros DRC de preprocessamiento DRC2. Más precisamente, una etapa 472 de síntesis paramétrica está configurada para cancelar total o parcialmente esta limitación del rango dinámico, como lo indica el símbolo gf.

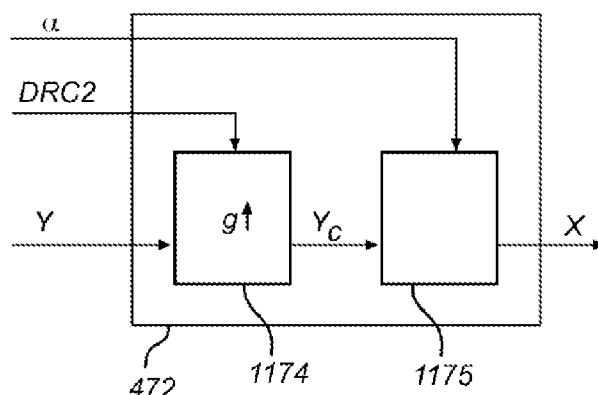

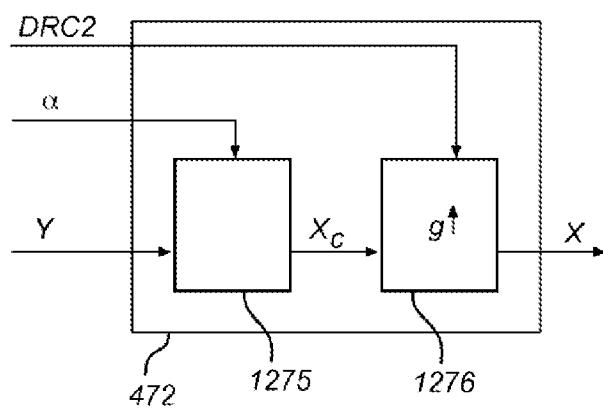

- 5 Las figuras 11 y 12 muestran dos posibles implementaciones de la etapa 472 de síntesis paramétrica que aparece en la figura 4. Implementaciones similares también son útiles en un sistema de codificación del tipo que se muestra en la figura 13, que se discute más adelante. En una primera implementación posible, como se muestra en la figura 11, un preacondicionador 1174 realiza una cancelación de limitación de rango dinámico en la señal central del canal m Y, con lo que se obtiene una señal intermedia del canal m Y<sub>c</sub>. La señal intermedia Y<sub>c</sub> se procesa luego en un procesador 1175 de síntesis paramétrica, que forma una combinación lineal de los canales en la señal intermedia Y<sub>c</sub> (y posiblemente, una señal decorrelacionada adicional), en donde las ganancias aplicadas dentro de la combinación lineal son controlables por medio de parámetros de codificación multicanal  $\alpha$ , que también se suministran al procesador 1175 de síntesis paramétrica.

- 10 15 La segunda implementación mostrada en la figura 12 representa una alternativa a esto. En la segunda implementación, la síntesis paramétrica precede a la cancelación de la limitación del rango dinámico como pasos de procesamiento. Este hecho se manifiesta en que el procesador 1275 de síntesis paramétrica está dispuesto aguas arriba de un posacondicionador 1276. Es el posacondicionador 1276 el que se encarga de cancelar la limitación del rango dinámico del lado del codificador, cuantificada por los parámetros DRC de preprocessamiento DRC2. Por lo tanto, la señal suministrada desde el procesador 1275 de síntesis paramétrica al posacondicionador 1276 se relaciona con una señal de canal n de rango dinámico limitado X<sub>c</sub>.

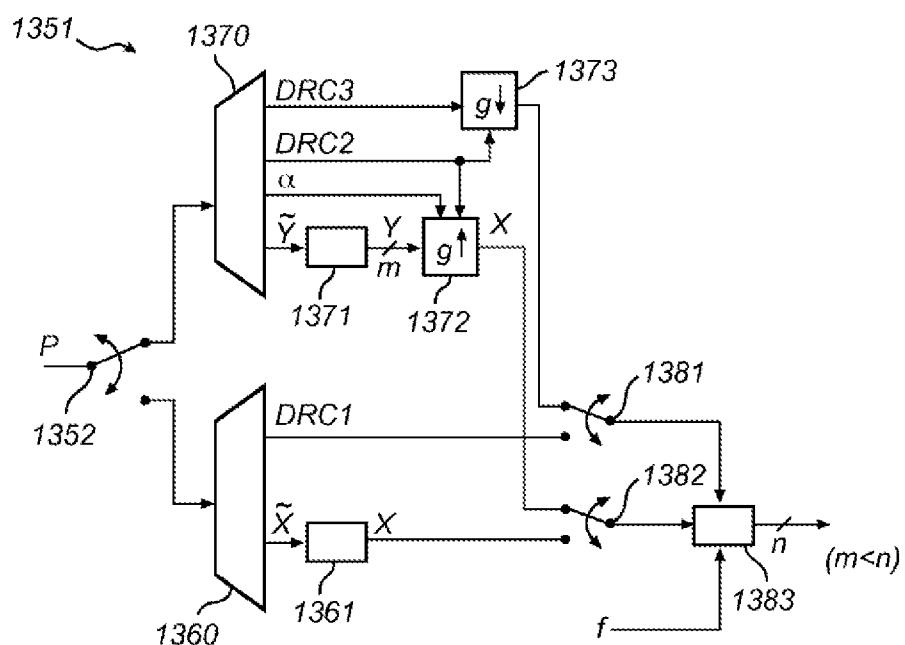

- 20 25 30 35 La figura 13 muestra, de acuerdo con una realización de ejemplo adicional, un sistema 1351 de decodificación, en el que el DRC del lado del decodificador se efectúa mediante un procesador DRC 1383 dispuesto aguas abajo de una porción de modo discreto y una porción de modo paramétrico del sistema 1351. Al igual que en los sistemas de decodificación que se han descrito con referencia a las figuras 2a, 2b, 2c y 4, el presente sistema 1351 de decodificación también es capaz de cancelar cualquier limitación de rango dinámico que se haya aplicado en el lado del codificador, tal como se cuantifica mediante los parámetros DRC de preprocessamiento DRC2. El procesador DRC 1383 está diseñado para funcionar tanto en el modo de codificación discreta, en donde los parámetros DRC de posprocesamiento (no compensados) DRC1 están contenidos en el flujo de bits recibido P, como en el modo de codificación paramétrica, en donde se reciben los parámetros DRC de posprocesamiento compensados DRC3. Se observa que el sistema 1351 de decodificación difiere del sistema 51 mostrado en la figura 2b en la medida en que el DRC de posprocesamiento se efectúa en la señal de salida del canal n, es decir, aguas abajo de la etapa 1372 de síntesis paramétrica. En el sistema 51 de la figura 2b, la operación correspondiente tiene lugar en el decodificador 71 de señal central.

- 40 45 50 55 El procesador DRC 1383 recibe un nivel de DRC de destino f de un usuario, una memoria, un diagnóstico de hardware realizado en el equipo de reproducción o alguna otra fuente de datos externa o interna. Por ejemplo, el nivel de DRC de destino f puede representar la fracción del DRC de posprocesamiento completo que el usuario desea que se realice mediante el sistema 1351 de decodificación. Como se verá, la estructura del sistema 1351 de decodificación tiene la ventaja de que solo se requiere que el procesador DRC 1383 tenga en cuenta el valor del parámetro f; esto hace que la implementación del DRC fraccionario sea conveniente. Para este propósito, se proporciona un compensador descendente DRC 1373 configurado para convertir los parámetros DRC de posprocesamiento compensados DRC3 a la escala de los parámetros DRC de posprocesamiento (no compensados) DRC1. De hecho, la señal de audio X de canal n que sale de la etapa 1372 de síntesis paramétrica habrá sufrido la cancelación de la limitación del rango dinámico del lado del codificador; por lo tanto, aplicar DRC de acuerdo con los parámetros DRC de posprocesamiento compensados DRC3 habría implicado una compresión de rango excesivamente pequeña. Para evitar este escenario, el compensador descendente DRC 1373 restaura los parámetros DRC de posprocesamiento compensados DRC3 basándose en los parámetros DRC de preprocessamiento DRC2, con lo que se obtienen los parámetros DRC de posprocesamiento restaurados y se suministran, en el modo de codificación paramétrica, al procesador DRC 1383. Como ya se señaló, el DRC del lado del decodificador expresado por los parámetros DRC restaurados es cuantitativamente equivalente a la combinación de la limitación del rango dinámico del lado del codificador, que ya se ha impuesto en la señal central, y el DRC del lado del decodificador expresado por los parámetros DRC de posprocesamiento compensados DRC3, como lo sugieren las figuras 8 y 9.

- 60 65 En una realización alternativa, el sistema 1351 de decodificación puede implementarse sin un demultiplexor 1360 de modo discreto y un decodificador 1361. Los selectores 1381, 1382 de parámetros DRC en la figura 13 se reemplazan entonces por conexiones entre el procesador DRC 1383 y cada uno de los compensadores descendentes DRC 1373, desde los cuales se reciben los parámetros DRC de posprocesamiento restaurados, y la etapa 1372 de síntesis paramétrica, que suministra la señal de audio X de canal n. Esta realización alternativa se simplifica en la medida en que opera en un único modo de decodificación paramétrica. Además, puede ser más sencillo de implementar porque se puede usar un procesador DRC de tipo heredado 1383, que no está necesariamente configurado para manejar parámetros DRC de posprocesamiento compensados.

La figura 6 muestra un sistema 651 de decodificación heredado para decodificar un flujo de bits recibido P en una señal de audio de canal m. En el modo de codificación paramétrica, una porción superior, ubicada aguas abajo del demultiplexor 670 de modo paramétrico, está activa, emitiendo una señal central de canal m codificada Y así como parámetros DRC de posprocesamiento compensados DRC3. La señal central de canal m codificada Y es decodificada por un primer decodificador 671 en una señal central Y de canal m. En el modo de codificación discreta, la señal de audio que se va a emitir es producida por una porción inferior, ubicada aguas abajo de un demultiplexor 660 de modo discreto, que extrae del flujo de bits P una señal de canal n codificada X así como parámetros DRC de posprocesamiento (no compensados) DRC1. La señal de canal n codificada X es decodificada por un segundo decodificador 661 y luego se somete a una mezcla descendente, en una etapa 662 de mezcla descendente, en una señal Y de canal m. Tanto esta señal Y como la señal Y mencionada en conexión con el modo paramétrico se suministran a un procesador DRC 683 común a ambos modos. En el modo paramétrico, las propiedades cuantitativas del procesador DRC 683 están controladas por los parámetros DRC de posprocesamiento compensados DRC3, mientras que, en el modo discreto, estas propiedades están controladas por los parámetros DRC de posprocesamiento (no compensados) DRC1. De esta manera, es posible mantener un nivel de diálogo consistente de la señal de audio del canal m que sale del sistema 651 de decodificación. Se observa que el sistema 651 de decodificación actual puede ser de tipo heredado, ya que puede tratar los parámetros DRC de posprocesamiento compensados y no compensados de una manera similar, si no idéntica.

20 IV. Símbolos de referencia en los dibujos

|                    |                                    |

|--------------------|------------------------------------|

| 1, 301, 701, 1051  | sistema de codificación            |

| 10, 710            | analizador de DRC                  |

| 11, 311, 711       | codificador                        |

| 12, 712            | multiplexor de modo discreto       |

| 21, 721            | analizador de DRC                  |

| 22, 322, 722, 1022 | etapa de análisis paramétrico      |

| 23, 323, 723       | codificador de señal central       |

| 24, 724            | compensador ascendente de DRC      |

| 25, 325, 725, 1025 | multiplexor de modo paramétrico    |

| 26, 326, 726, 1026 | selector                           |

| 527                | preprocesador                      |

| 528                | procesador de análisis paramétrico |

| 51, 451, 651, 1351 | sistema de decodificación          |

| 452, 652, 1352     | selector                           |

| 60, 660, 1360      | demultiplexor                      |

| 61, 461, 1361      | decodificador                      |

| 661                | segundo decodificador              |

| 662                | etapa de mezcla descendente        |

| 70, 470, 670, 1370 | demultiplexor                      |

| 71, 471, 1371      | decodificador de señal central     |

| 671                | primer decodificador               |

| 72, 472, 1372      | etapa de síntesis paramétrica      |

| 1373               | compensador descendente de DRC     |

| 74                 | procesador DRC                     |

| 1174               | preacondicionador                  |

| 1175, 1275         | procesador de síntesis paramétrica |

| 1276               | posacondicionador                  |

| 77                 | preprocesador de DRC               |

|                |                               |

|----------------|-------------------------------|

| 681, 1381      | selector de parámetros de DRC |

| 482, 682, 1382 | selector de señal             |

| 683, 1383      | procesador de DRC             |

|                   |                                                                         |

|-------------------|-------------------------------------------------------------------------|

| X ( $\tilde{X}$ ) | señal de canal n (señal de canal n codificada)                          |

| X <sub>c</sub>    | señal de canal n con rango dinámico limitado                            |

| Y ( $\tilde{Y}$ ) | señal de canal m (señal de canal n codificada), $1 \leq m < n$          |

| Y <sub>c</sub>    | señal intermedia                                                        |

| f                 | parámetro que indica una fracción de un DRC especificado a ser aplicado |

| g                 | cantidad límite del rango dinámico                                      |

| $\alpha$          | parámetro(s) de codificación multicanal                                 |

| DRC1              | parámetros DRC de posprocesamiento (restaurados)                        |

| DRC2              | preprocesamiento de parámetros DRC                                      |

| DRC 3             | parámetros DRC de posprocesamiento compensado                           |

| P                 | flujo de bits                                                           |

## V. Extensiones, alternativas y varios

- 5 Otras realizaciones de la presente invención resultarán evidentes para una persona experta en la técnica después de estudiar la descripción anterior. Si bien la presente descripción y los dibujos divultan realizaciones y ejemplos, la invención no está restringida a estos ejemplos específicos. Se pueden realizar numerosas modificaciones y variaciones sin alejarse del alcance de la presente invención, que está definido por las reivindicaciones adjuntas. Los posibles signos de referencia que aparezcan en las reivindicaciones no deben 10 entenderse como limitativos de su alcance.

Los sistemas y métodos divulgados anteriormente pueden implementarse como software, firmware, hardware o una combinación de ellos. En una implementación de hardware, la división de tareas entre unidades funcionales a que se refiere la descripción anterior no corresponde necesariamente a la división en unidades físicas; por el contrario, un componente físico puede tener múltiples funcionalidades y una tarea puede ser realizada por varios componentes físicos en cooperación. Ciertos componentes o todos los componentes pueden implementarse como software ejecutado por un procesador de señal digital o microprocesador, o implementarse como hardware o como un circuito integrado específico de aplicación. Tal software puede distribuirse en medios legibles por ordenador, que pueden comprender medios de almacenamiento de ordenador (o medios no transitorios) y 15 medios de comunicación (o medios transitorios). Como es bien sabido por una persona experta en la técnica, el término medios de almacenamiento de ordenador incluye medios volátiles y no volátiles, extraíbles y no extraíbles implementados en cualquier método o tecnología para el almacenamiento de información, tales como instrucciones legibles por ordenador, estructuras de datos, módulos de programa u otros datos. Los medios de almacenamiento de ordenador incluyen, pero no se limitan a, RAM, ROM, EEPROM, memoria flash u otra 20 tecnología de memoria, CD-ROM, discos versátiles digitales (DVD) u otro almacenamiento en disco óptico, cassetes magnéticos, cintas magnéticas, almacenamiento en disco magnético u otros dispositivos de almacenamiento magnético, o cualquier otro medio que pueda usarse para almacenar la información deseada y al que pueda accederse mediante un ordenador. Además, es bien sabido por el experto en la técnica que los medios de comunicación típicamente incorporan instrucciones legibles por ordenador, estructuras de datos, módulos de programa u otros datos en una señal de datos modulada, tal como una onda portadora u otro 25 mecanismo de transporte, e incluyen cualquier medio de entrega de información.

20

25

30

## REIVINDICACIONES

1.- Un método, realizado por un dispositivo (51; 451; 1351) de decodificación de señales de audio, para ajustar un rango dinámico de una señal de audio (X), comprendiendo el método:

5 recibir un flujo de bits (P) que comprende una señal de audio codificada ( $\tilde{Y}$ ) y metadatos de control de rango dinámico, DRC, generados por codificador, en donde la señal de audio codificada comprende una señal central codificada y parámetros de codificación multicanal ( $\alpha$ ), y en donde los metadatos DRC generados por codificador comprenden una pluralidad de conjuntos de parámetros DRC, comprendiendo la pluralidad de conjuntos de parámetros DRC un primer conjunto de parámetros DRC (DRC2) que cuantifican una prevención de recorte, y un segundo conjunto de parámetros DRC (DRC3) que cuantifican un DRC del lado del decodificador a ser aplicado; y

10 15 decodificar la señal de audio codificada para obtener la señal de audio, en donde la decodificación de la señal de audio codificada comprende generar una señal (X) de canal n a partir de una señal central (Y) de canal m y los parámetros de codificación multicanal ( $\alpha$ ), donde  $1 \leq m < n$ , y en donde la generación de la señal de canal n comprende decodificar la señal central codificada en la señal central de canal m, y realizar síntesis paramétrica para reconstruir la señal de canal n basándose en la señal central de canal m y los parámetros de codificación multicanal;

20 en donde el rango dinámico de la señal de audio se ajusta mediante la aplicación del primer conjunto de parámetros DRC y una fracción del segundo conjunto de parámetros DRC.

25 2.- Un dispositivo (51; 451; 1351) de decodificación de señales de audio para ajustar un rango dinámico de una señal de audio (X), comprendiendo el dispositivo de decodificación de señales de audio uno o más procesadores que:

30 35 reciben un flujo de bits (P) que comprende una señal de audio codificada ( $\tilde{Y}$ ) y metadatos de control de rango dinámico, DRC, generados por codificador, en donde la señal de audio codificada comprende una señal central codificada y los parámetros de codificación multicanal ( $\alpha$ ), y en donde los metadatos DRC generados por codificador comprenden una pluralidad de conjuntos de parámetros DRC, comprendiendo la pluralidad de conjuntos de parámetros DRC un primer conjunto de parámetros DRC (DRC2) que cuantifican una prevención de recorte, y un segundo conjunto de parámetros DRC (DRC3) que cuantifican un DRC del lado del decodificador a ser aplicado; y

40 45 decodifican la señal de audio codificada para obtener la señal de audio, en donde la decodificación de la señal de audio codificada comprende generar una señal (X) de canal n a partir de una señal central (Y) de canal m y parámetros de codificación multicanal ( $\alpha$ ), donde  $1 \leq m < n$ , y en donde la generación de la señal de canal n comprende decodificar la señal central codificada en la señal central de canal m, y realizar síntesis paramétrica para reconstruir la señal de canal n basándose en la señal central de canal m y los parámetros de codificación multicanal;

en donde el rango dinámico de la señal de audio está ajustado mediante la aplicación del primer conjunto de parámetros DRC y una fracción del segundo conjunto de parámetros DRC.

45 3.- Un programa de ordenador que tiene instrucciones que, cuando son ejecutadas por un dispositivo o sistema informático, hacen que el dispositivo o sistema informático realice el método de cualquiera de las reivindicaciones 1-2.

Fig. 1a

Fig. 1b

Fig. 3

Fig. 4

Fig. 5

Fig. 8

Fig. 9

Fig. 10

Fig. 11

Fig. 12

Fig. 13