RÉPUBLIQUE FRANÇAISE

INSTITUT NATIONAL

DE LA PROPRIÉTÉ INDUSTRIELLE

PARIS

(11) N° de publication :

(A n'utiliser que pour les

commandes de reproduction).

**2 464 562**

A1

**DEMANDE

DE BREVET D'INVENTION**

(21) **N° 79 21561**

(54) Transistor à effet de champ comprenant des chemins conducteurs réalisés sous forme de rainures recouvertes de métal et atteignant un substrat très dopé.

(51) Classification internationale (Int. Cl. 3). H 01 L 29/76, 21/30.

(22) Date de dépôt..... 28 août 1979.

(33) (32) (31) Priorité revendiquée :

(41) Date de la mise à la disposition du public de la demande ..... B.O.P.I. — « Listes » n° 10 du 6-3-1981.

(71) Déposant : Société dite : THOMSON-CSF, résidant en France.

(72) Invention de : Pierre Gibeau, Raymond Henry, Michel Laviron et Henri Derewonko.

(73) Titulaire : *Idem* (71)

(74) Mandataire : Thomson-CSF, SCPI,

173, bd Haussmann, 75360 Paris Cedex 08.

2<sup>e</sup> demande divisionnaire bénéficiant de la date de dépôt du 19 août 1976 de la demande de brevet initiale n° 76 25230 (art. 14 de la loi modifiée du 2 janvier 1968).

L'invention se rapporte aux transistors à effet de champ à structure interdigitée, et aux procédés de fabrication de tels transistors. Elle concerne notamment les transistors à effet de champ ayant leurs trois électrodes (source, grille et drain) 5 situés sur la même face d'un dispositif à semiconducteurs, et destinés à fonctionner en hyperfréquence, à des puissances relativement importantes.

On sait que les transistors de puissance ne sont réalisables, en hyperfréquence, que sous la forme de structures interdigitées. 10 Or, dans le cas de dispositifs ayant leur trois électrodes distribuées sur la même face du substrat, les connexions d'entrée ou de sortie des électrodes se croisent nécessairement dans le plan commun de distribution. On sait bien réaliser de tels croisements, par interposition de couches isolantes. Mais il en 15 résulte une complexité accrue de réalisation, et, d'autre part, on crée ainsi des capacités parasites gênantes entre connexions, ce qui est nuisible et parfois prohibitif en hyperfréquence.

On sait réaliser aussi des structures interdigitées n'ayant que deux électrodes sur une face du substrat, et possédant une 20 grille commune sur la face opposée. Mais la commande d'une telle grille manque de rapidité et ne convient donc pas toujours en hyperfréquence.

L'invention remédié à ces divers inconvénients, en simplifiant la fabrication du transistor.

25 Le transistor selon l'invention a la plus grande partie de ses électrodes situées dans le plan d'une face où chaque électrode se divise en électrodes secondaires. Il est caractérisé en ce qu'au moins une série d'électrodes secondaires est interconnectée par l'intermédiaire de chemins conducteurs occupant au moins un 30 plan différent du plan de la face précitée, lesdits chemins conducteurs émergeant soit sur une face différente, soit en des points de la même face situés en dehors de la structure interdigitée formée par les électrodes.

L'invention sera mieux comprise, et d'autres caractéristiques 35 apparaîtront, au moyen de la description qui suit, et des dessins qui l'accompagnent, parmi lesquels :

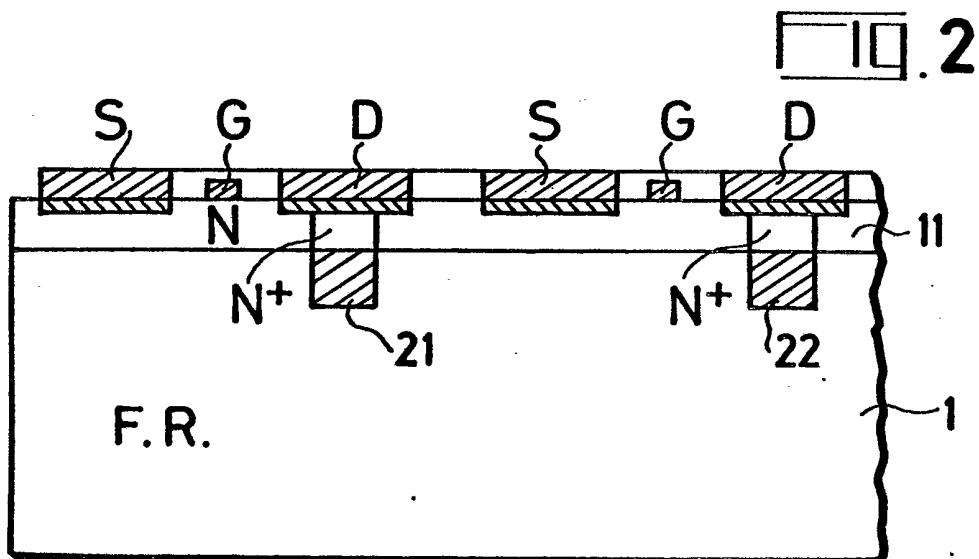

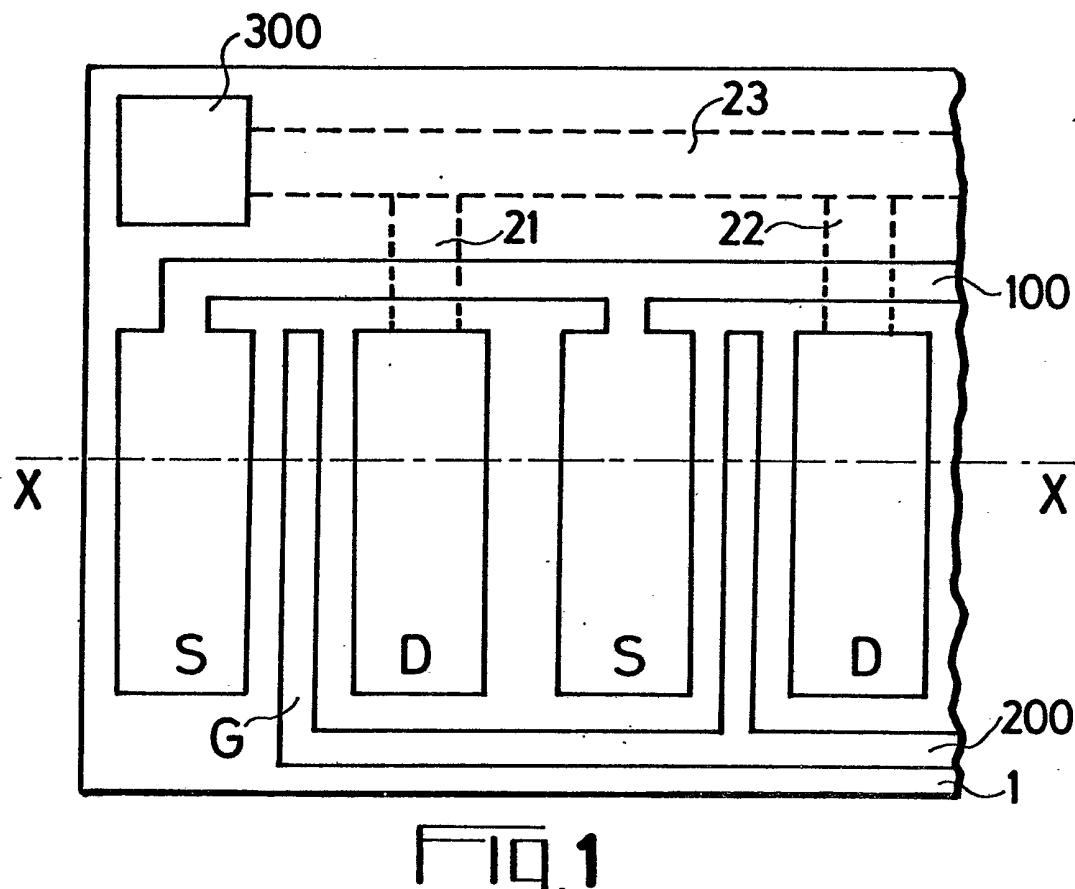

La figure 1 en plan, et la figure 2 en coupe (suivant un

plan de trace XX sur le plan de la figure 1) représente schématiquement un premier mode de réalisation ;

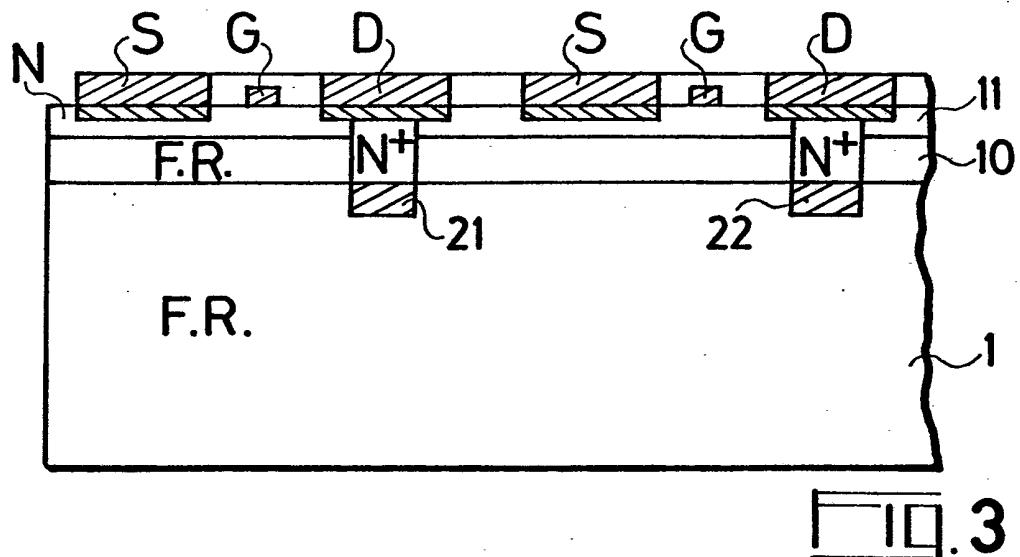

Les figures 3, 4 et 5 représentent en coupe schématique d'autres modes de réalisation de l'invention ;

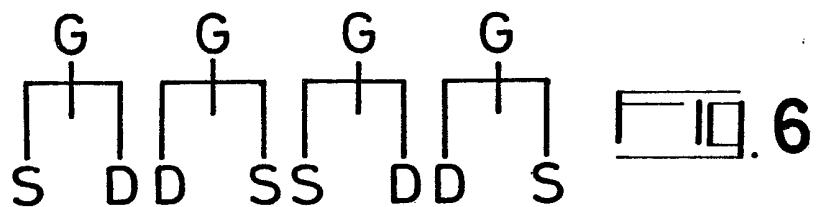

5 Les figures 6 et 7 sont des schémas explicatifs ;

La figure 8 est un schéma d'une variante de l'invention.

Dans un premier mode de réalisation, on part d'un substrat semi-conducteur en matériau monocristallin à très forte résistivité (intrinsèque ou semi-isolante), et l'on réalise des chemins 10 conducteurs sur ce substrat. Ces chemins aboutissent à une voie commune et conduisent à un point destiné à devenir le lieu d'émergence du chemin conducteur sur la face active du transistor en dehors des connexions de la structure interdigitée qui sont réalisés par les voies habituelles, en surface.

15 Ces chemins conducteurs sont réalisés par des moyens divers :

- gravure chimique ou ionique de rainures, suivies par exemple d'un dépôt semi-conducteur à faible résistivité dans les rainures ;

20 - diffusion d'impuretés dopantes à travers des fenêtres découpées dans un masque de silice adhérant fortement au substrat ;

- implantation ionique à travers les fenêtres d'un masque simplement appliqué sur le substrat.

A titre d'exemple non limitatif de ce premier mode de réalisation, soit un substrat 1 à très forte résistivité (F.R.) 25 (figures 1 et 2) sur lequel on a réalisé, par une des méthodes précitées, des chemins conducteurs 21, 22, représentant les dents d'un peigne conduisant à un manche constituant un chemin conducteur 23. On réalise ensuite une couche semi-conductrice 11 dopée par exemple N, qui, pour un transistor destiné à fonctionner en 30 hyperfréquence, est de l'ordre du micron. Puis on réalise de façon classique des électrodes à contact ohmique S et D, destinées à devenir des électrodes de source et de drain et des électrodes G à contact de type SCHOTTKY, destinées à devenir des électrodes de grille. Ces électrodes constituent les électrodes divisionnaires d'une structure interdigitée de transistor 35 à effet de champ, dont les électrodes S et G sont interconnectées par des métallisations 100 et 200 déposées en surface. Les

électrodes D, au contraire, recouvrent les chemins 21, 22 etc... en les débordant (dans l'exemple représenté figures 1 et 2). Pour assurer le contact électrique entre ces électrodes D et les chemins 21, 22, on a réalisé préalablement, par dopage, des 5 régions N<sup>+</sup> distribuées dans la couche 11 suivant un dessin qui reproduit celui des électrodes D. Ce dopage est effectué par les méthodes déjà citées de diffusion ou d'implantation ionique. Enfin on fait émerger le chemin 23 selon une métallisation 300 déposée à la surface de la couche 11 après un dopage N<sup>+</sup> préalable 10 de la région de la couche qui supporte la métallisation 300.

Dans un deuxième mode de réalisation, dont la figure 3 illustre un exemple, on réalise une couche supplémentaire 10 qui s'insère entre le substrat à très forte résistivité muni des chemins conducteurs 21, 22 et la couche 11. Cette couche 10, 15 de très forte résistivité, résulte, par exemple, d'un dépôt épitaxial. Après réalisation de la couche active 11, on procède comme dans le premier mode de réalisation. Dans cet exemple, les chemins 21, 22 sont situés à une plus grande profondeur de la surface du transistor, ce qui procure une diminution de la capacité parasite au croisement avec la métallisation 100 telle qu'elle figure dans l'exemple de la figure 1.

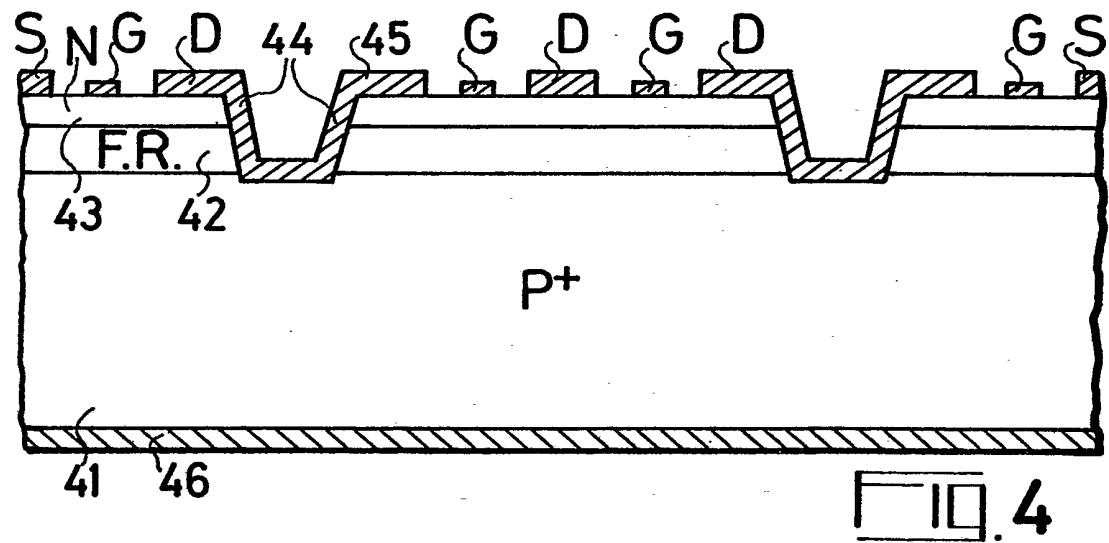

Dans un troisième mode de réalisation, dont la figure 4 illustre un exemple, on réalise sur un substrat 41, dopé P<sup>+</sup> (ou N<sup>+</sup>) ; une couche à très forte résistivité (F.R.) 42 (obtenue 25 par exemple par croissance épitaxiale, sans aucun dopant dans le cas du silicium), puis une couche 43 dopée N (par exemple par une deuxième épitaxie). On grave ensuite à l'emplacement prévu pour l'électrode drain (ou source), par voie physique ou chimique, des rainures 44 pénétrant dans les couches 42 ou 43 jusqu'au 30 matériau P<sup>+</sup> (ou N<sup>+</sup>) du substrat 41. Lors de la réalisation des électrodes, on dépose une métallisation 45 tapissant la rainure et débordant sur les deux flancs. Dans l'exemple choisi on a intercalé les électrodes de grille aussi bien dans les intervalles S D que dans les intervalles D S. Une telle disposition permet 35 d'augmenter le rendement de la structure interdigitée en doublant le courant débité par chaque électrode. En effet, dans une série de transistors telle que celle qui est représentée figure 6, on peut inverser une fois sur deux les rôles de la source et du drain.

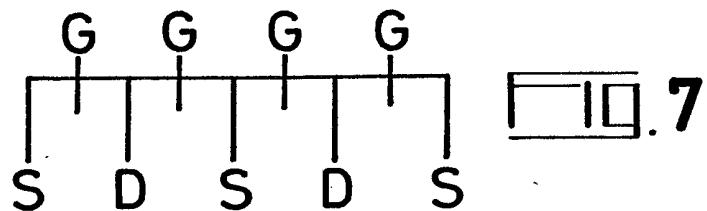

Cette inversion est réalisée en connectant les électrodes choisies comme source au pôle de l'alimentation dit "de source" c'est à dire donnant la plus basse tension continue, et les électrodes choisies comme drains au pôle de l'alimentation opposé. Dans 5 ces conditions il est possible de simplifier la structure de la figure 6 en confondant deux à deux les électrodes intermédiaires, ce qui permet d'aboutir au schéma de la figure 7, qui n'est autre que celui de la figure 4, mis à part le profil particulier des électrodes D dans ce dernier cas.

10 Dans ce mode de réalisation, toutes les sources ont un chemin conducteur commun constitué par le substrat  $P^+$ . Ce dernier est muni d'une métallisation 46 destiné à faciliter le raccordement à la source d'alimentation et aux circuits d'utilisation.

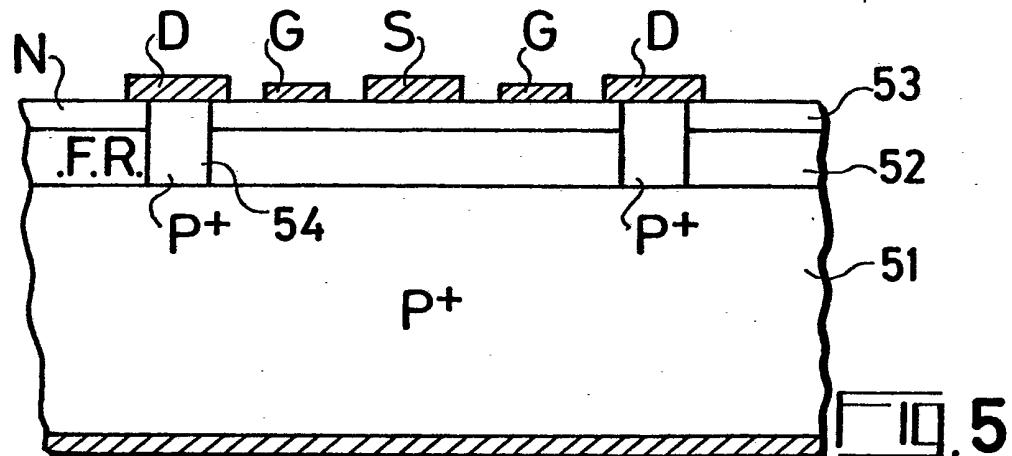

Dans un quatrième mode de réalisation, dont la figure 5 15 illustre un exemple, on a, comme dans le troisième mode, un substrat 51,  $P^+$  (ou  $N^+$ ) surmonté de deux couches 52 (semi-isolante) et 53 (dopée N), mais, au lieu de graver des rainures, on a réalisé des chemins conducteurs en matériau dopé du même type que le substrat, par dopage sélectif de régions 54, en procédant soit 20 par diffusion, soit par implantation ionique, avant de réaliser les électrodes D.

Dans les deux modes précédents, on peut prendre comme point de départ un bloc monocristallin à très forte résistivité réalisé dans le matériau choisi (silicium ou arséniure de gallium) et 25 ensuite doper les régions correspondant aux couches  $P^+$  et N. La fabrication s'en trouve simplifiée.

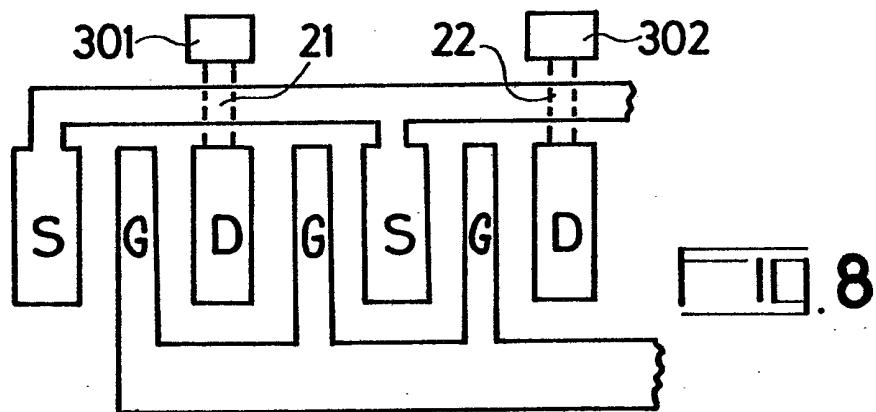

Dans un cinquième mode de réalisation, figure 8, qui est une variante de la structure de la figure 1, on ne réalise pas de chemin conducteur commun pour tous les drains. Chaque drain est connecté 30 par un chemin conducteur enterré autonome à un plot de raccordement 301 ou 302. Cette disposition permet, dans la mise en parallèle des différents doigts de la structure, d'introduire certains éléments (résistances, capacités, inductances) entre les différents doigts.

35 Dans l'exemple représenté figure 8 on a adopté aussi le schéma de la figure 7.

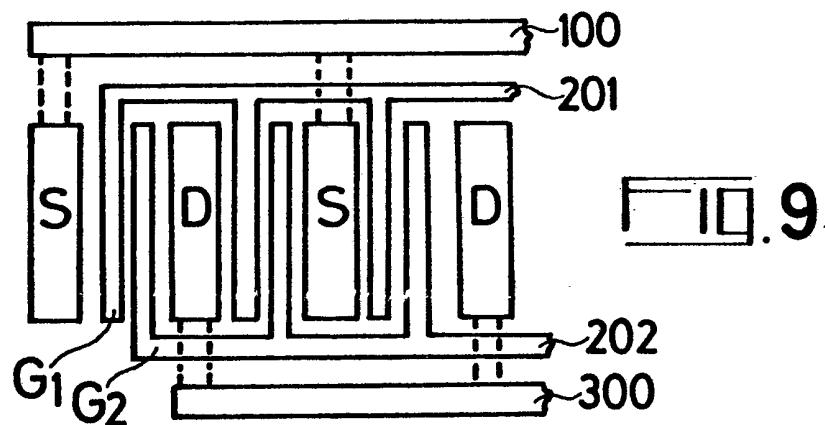

Dans un sixième mode de réalisation, dont la figure 9

illustre un exemple, on ajoute une grille supplémentaire. Les doigts des grilles  $G_1$  et  $G_2$  sont reliées en surface à des métallisations 201 et 202, sans croisement de connexions, tandis que les doigts de source S et de drain D sont reliés par chemins conducteurs "enterrés" aux métallisations 100 et 300.

5 En dehors de l'avantage déjà signalé consistant à diminuer la capacité parasite entre connexions d'électrodes, on peut citer, pour les troisième et quatrième modes de réalisation, les avantages ci-après :

10 1 - La suppression quasi-complète de l'inductance propre de l'électrode interconnectée par le substrat rendu conducteur par dopage, avantage particulièrement important lorsque l'électrode intéressée est la source (contrairement à ce qui a été représenté figures 4 et 5) ;

15 2 - La diminution de la résistance thermique, notamment dans le cas de substrat en arséniure de gallium, le dopage de ce dernier diminuant sa résistivité ;

3 - La compatibilité avec les méthodes d'amincissement du substrat pour diminuer la résistance thermique.

REVENDICATIONS

1. Transistor à effet de champ à structure interdigitée, comportant, sur une face plane, des électrodes situées au moins en partie dans le plan de ladite face, chacune des électrodes se divisant en une série d'électrodes secondaires entre lesquelles 5 sont intercalées des électrodes secondaires provenant de la division d'autres électrodes, caractérisé en ce qu'il comporte un substrat en matériau semiconducteur fortement dopé, une couche à très forte résistivité et une couche semiconductrice active, des rainures étant gravées dans la surface de ladite face assez 10 profondément pour atteindre ledit substrat et un métal étant déposé dans ladite rainures et sur les bords de celles-ci pour constituer avec le substrat, lesdits chemins conducteurs.

2. Transistor suivant la revendication 1, caractérisé en ce que l'électrode de drain est réalisé sous formes de rainures 15 atteignant le substrat.

3. Transistor suivant la revendication 1, caractérisé en ce que l'électrode de source est réalisée sous forme de rainures atteignant le substrat.

## Pl. III-3