(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6625557号

(P6625557)

(45) 発行日 令和1年12月25日(2019.12.25)

(24) 登録日 令和1年12月6日(2019.12.6)

(51) Int.Cl.

F 1

G 06 F 13/38 (2006.01)

H 04 L 29/06 (2006.01)G 06 F 13/38 320 A

G 06 F 13/38 350

H 04 L 13/00 305 C

請求項の数 15 (全 38 頁)

(21) 出願番号 特願2016-564203 (P2016-564203)

(86) (22) 出願日 平成27年4月24日 (2015.4.24)

(65) 公表番号 特表2017-514238 (P2017-514238A)

(43) 公表日 平成29年6月1日 (2017.6.1)

(86) 國際出願番号 PCT/US2015/027479

(87) 國際公開番号 WO2015/167954

(87) 國際公開日 平成27年11月5日 (2015.11.5)

審査請求日 平成30年4月5日 (2018.4.5)

(31) 優先権主張番号 61/985,276

(32) 優先日 平成26年4月28日 (2014.4.28)

(33) 優先権主張国・地域又は機関 米国(US)

(31) 優先権主張番号 14/694,618

(32) 優先日 平成27年4月23日 (2015.4.23)

(33) 優先権主張国・地域又は機関 米国(US)

(73) 特許権者 507364838

クアルコム、インコーポレイテッド

アメリカ合衆国 カリフォルニア 921

21 サンディエゴ モアハウス ドラ

イブ 5775

(74) 代理人 100108453

弁理士 村山 靖彦

(74) 代理人 100163522

弁理士 黒田 晋平

(72) 発明者 ラドウ・ピティゴイーアロン

アメリカ合衆国・カリフォルニア・921

21-1714・サン・ディエゴ・モアハ

ウス・ドライブ・5775

最終頁に続く

(54) 【発明の名称】センサーグローバルバス

## (57) 【特許請求の範囲】

## 【請求項 1】

データ通信インターフェースにおいて実行される方法であって、シリアルバスが第1の動作モードで動作している間に、前記シリアルバスに結合された複数のデバイスに第1のコマンドを送信するステップであって、前記第1のコマンドが、前記シリアルバスが第2の動作モードで動作するようにさせるために、第1のプロトコルに従って送信されるステップと、

前記シリアルバスが前記第2の動作モードで動作している間に、第2のプロトコルに従って、前記複数のデバイスのうちの第1のデバイスと通信するステップと、

前記第2の動作モードを終了させるために、前記第1のプロトコルに従って、前記複数のデバイスに第2のコマンドを送信するステップと

を含み、

前記第1のデバイスと通信するステップが、

クロック情報がシンボルのシーケンス内の連続するシンボルのペア間の遷移において符号化される、前記シンボルのシーケンス内でデータを符号化するステップと、

エキストラシンボルなしの2つのシンボルの送信が、前記シリアルバス上で望ましくないシグナリング状況を引き起こすことになり、前記エキストラシンボルを伴う前記2つのシンボルの送信が、前記シリアルバス上の前記望ましくないシグナリング状況を防止することになるとき、前記エキストラシンボルを前記シンボルのシーケンス内の前記2つのシンボル間に挿入するステップと、

10

20

前記シンボルのシーケンスを前記シリアルバス上で送信するステップと

を含み、

第2のデバイスが、前記エキストラシンボルが前記2つのシンボル間に挿入されているときに前記シリアルバスが前記第2の動作モードで動作している間は、前記シリアルバス上の通信を無視する、方法。

**【請求項 2】**

前記望ましくないシグナリング状況が、前記シリアルバスの2本のライン上の前記遷移の相対的タイミングに関係する、請求項1に記載の方法。 10

**【請求項 3】**

前記望ましくないシグナリング状況が、前記シリアルバスの1本のライン上で送信されるパルスの持続期間に関係する、請求項1に記載の方法。

**【請求項 4】**

前記望ましくないシグナリング状況が、前記第2のプロトコル以外のプロトコルによって定義された同期または開始条件に関係する、請求項1に記載の方法。 20

**【請求項 5】**

前記第1のデバイスと通信するステップが、

前記2つのシンボルを送信することが、前記2つのシンボルが前記シリアルバスを介して送信される場合、50ナノ秒よりも大きい持続期間を有するパルスを前記シリアルバスの第1のライン上で発生させることになると決定するステップと、

前記エキストラシンボルを前記シンボルのシーケンスに挿入するステップであって、前記エキストラシンボルが前記第1のライン上の前記パルスを終了させるために選択されるステップと 20

を含む、請求項1に記載の方法。

**【請求項 6】**

前記第1のプロトコルが、インター・インテグレイティド・サーキット(I2C)プロトコルと互換性があり、前記望ましくないシグナリング状況が、前記I2Cプロトコルによって定義された開始条件に関係する、請求項1に記載の方法。 30

**【請求項 7】**

前記シンボルのシーケンスの各シンボルが複数のビットを有し、各ビットが、1つのシンボル間隔に対する前記シリアルバスの1本のラインのシグナリング状態を定義する、請求項1に記載の方法。 30

**【請求項 8】**

前記シンボルのシーケンス内の連続するシンボルの各ペアが、2つの異なるシンボルを含み、前記シリアルバスの少なくとも1本のラインの前記シグナリング状態が、前記連続するシンボルの各ペアにおける第2のシンボルが送信されるとき、変化する、請求項7に記載の方法。

**【請求項 9】**

前記シリアルバスが前記第1の動作モードで動作している間に、前記複数のデバイスに第3のコマンドを送信するステップであって、前記第3のコマンドが、前記シリアルバスが第3の動作モードで動作するようにさせるために、前記第1のプロトコルに従って送信されるステップと、 40

前記シリアルバスが前記第3の動作モードで動作している間に、第3のプロトコルに従つて、前記複数のデバイスのうちの第3のデバイスと通信するステップと、

前記第3の動作モードを終了させるために、前記第1のプロトコルに従つて、前記複数のデバイスに第4のコマンドを送信するステップと

をさらに含む、請求項1に記載の方法。

**【請求項 10】**

データ通信のための装置であって、

前記装置をシリアルバスに結合するトランシーバと、

処理回路と 50

を備え、前記処理回路が、

前記シリアルバスが第1の動作モードで動作している間に、前記シリアルバスに結合された複数のデバイスに第1のコマンドを送信することであって、前記第1のコマンドが、前記シリアルバスが第2の動作モードで動作するようにさせるために、第1のプロトコルに従って送信されること、

第2のプロトコルに従って、シンボルのシーケンス内でデータを符号化することであって、クロック情報が前記シンボルのシーケンス内の連続するシンボルのペア間の遷移において符号化されること、

エキストラシンボルなしの2つのシンボルの送信が、前記シリアルバス上で望ましくないシグナリング状況を引き起こすことになり、前記エキストラシンボルを伴う前記2つのシンボルの送信が、前記シリアルバス上の前記望ましくないシグナリング状況を防止することになるとき、前記エキストラシンボルを前記シンボルのシーケンス内の前記2つのシンボル間に挿入すること、および

前記第2のプロトコルに従って、前記シンボルのシーケンスを前記シリアルバス上で送信すること、および

前記第2の動作モードを終了させるために、前記第1のプロトコルに従って、前記複数のデバイスに第2のコマンドを送信することを行いうように構成され、

第2のデバイスが、前記エキストラシンボルが前記2つのシンボル間に挿入されているときに前記シリアルバスが前記第2の動作モードで動作している間は、前記シリアルバス上の通信を無視する、装置。

#### 【請求項 1 1】

前記望ましくないシグナリング状況が、前記シリアルバスの2本のライン上の前記遷移の相対的タイミングに関係する、請求項10に記載の装置。

#### 【請求項 1 2】

前記望ましくないシグナリング状況が、前記シリアルバスの1本のライン上で送信されるパルスの持続期間に関係する、請求項10に記載の装置。

#### 【請求項 1 3】

前記望ましくないシグナリング状況が、前記第2のプロトコル以外のプロトコルによって定義された同期または開始条件に関係する、請求項10に記載の装置。

#### 【請求項 1 4】

前記シンボルのシーケンスの各シンボルが複数のビットを有し、各ビットが、1つのシンボル間隔に対する前記シリアルバスの1本のラインのシグナリング状態を定義する、請求項10に記載の装置。

#### 【請求項 1 5】

コンピュータによって実行されると、前記コンピュータに請求項1から9のいずれか一項に記載の方法を行わせる命令を含む、コンピュータ可読記憶媒体。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0 0 0 1】

関連出願の相互参照

本出願は、その内容全体が参照により本明細書に組み込まれる、2014年4月28日に米国特許庁に出願された仮特許出願第61/985,276号および2015年4月23日に米国特許庁に出願された非仮特許出願第14/694,618号の優先権および利益を主張する。

##### 【0 0 0 2】

本開示は、一般にホストプロセッサと周辺デバイスとの間のインターフェースに関し、より詳細には、センサーを接続するインターフェースに関する。

##### 【背景技術】

##### 【0 0 0 3】

セルラー電話など、モバイルデバイスの製造業者は、モバイルデバイスの構成要素を、

10

20

30

40

50

異なる製造業者を含む様々なソースから取得し得る。たとえば、モバイルコンピューティングデバイスにおけるアプリケーションプロセッサは、第1の製造業者から取得されることがある、モバイルコンピューティングデバイスによって採用されるセンサーは、1つまたは複数の他の製造業者から取得されることがある。様々な規格ベースまたはプロプライエタリなインターフェースが、モバイルデバイスおよび他の装置内の集積回路(IC)デバイスを相互接続するために定義されており、これらのインターフェースは、典型的には特定のアプリケーションまたは特定のタイプのアプリケーションを対象とする。たとえば、セルラー電話は、モバイル業界プロセッサインターフェースアライアンス(MIPI)によって規定されたカメラシリアルインターフェース規格と互換性があるか、またはそれに準拠する通信インターフェースを使用し得る。

10

#### 【0004】

特定のアプリケーションのために最適化された従来のインターフェースは、他のアプリケーションにおいて使用するのに好適ではないことがある。たとえば、MIPI規格は、マスターおよび1つまたは複数のスレーブを接続するバスとして構成された、2線式、双方向、半二重のシリアルインターフェースを使用する、カメラ制御インターフェース(CCI)を定義する。CCIは、ディスプレイに関連するデータ通信要件を扱うために最適化され、その要件は、典型的には、様々な異なるタイプのデバイスのために広く使用されているインターリング・インテグレイティド・サーキット(I2C)バスの能力を超えており、CCIシグナリングおよびプロトコルは、CCIプロトコルを使用して通信するためにI2Cバスを採用するデバイスと互換性があり得る。すなわち、CCIプロトコルは、I2Cシリアルクロック(SCL)およびシリアルデータ(SDA)ラインを使用し、CCIデバイスおよびI2Cデバイスは、I2Cバスを伴う任意の通信がI2Cプロトコルを使用している間に、2つ以上のCCIデバイスがCCIプロトコルを使用して通信することができるよう、同じバス上で配備され得る。

20

#### 【0005】

より最近のバージョンのCCIは、より高速な信号速度をサポートするために修正されたプロトコルを使用して、より高いスループットを提供することができる。一例では、CCI拡張(CCle)バスは、CCleバスの動作と互換性があるデバイスにより高いデータレートを提供するために使用され得る。そのようなデバイスは、CCleデバイスと呼ばれることがあり、CCleデバイスは、従来のCCIバスのSCLラインとSDAラインの両方において送信されるシンボルとしてデータを符号化することによって、互いに通信するときに、より高いデータレートを達成することができる。CCleデバイスおよびI2Cデバイスは、同じCCleバス上で共存し得るので、複数のデバイスがCCle符号化を使用してデータを交換し得るようになるが、レガシーI2Cデバイスを伴うデータ交換は、I2Cシグナリング規約に従って送信され得る。

30

#### 【0006】

異なるタイプの周辺装置または協働するデバイスをプロセッサに接続するバスとして構成されたシリアルインターフェース上で最適化された通信を提供することが、現在求められている。

#### 【発明の概要】

#### 【課題を解決するための手段】

40

#### 【0007】

本明細書で開示する実施形態は、異なるプロトコルおよび/またはシグナリング方式を使用して、シリアルバスを介して通信するように構成されたデバイスを結合する、シリアルバスの性能を改善することができるシステム、方法、および装置を提供する。本開示の一態様では、方法、コンピュータ可読ストレージデバイス、および装置が提供される。

#### 【0008】

本開示の一態様では、データ通信の方法は、シリアルバスが第1の動作モードで動作している間に、シリアルバスに結合された複数のデバイスに第1のコマンドを送信するステップであって、第1のコマンドが、シリアルバスが第2の動作モードで動作するようにさせるために、第1のプロトコルに従って送信されるステップと、シリアルバスが第2の動作モ

50

ードで動作している間に、第2のプロトコルに従って、複数のデバイスのうちの第1のデバイスと通信するステップと、第2の動作モードを終了させるために、第1のプロトコルに従って、複数のデバイスに第2のコマンドを送信するステップとを含む。第1のデバイスと通信するステップは、クロック情報がシンボルのシーケンス内の連続するシンボルのペア間の遷移において符号化される、シンボルのシーケンス内でデータを符号化するステップと、エキストラシンボルなしの2つのシンボルの送信が、シリアルバス上で望ましくないシグナリング状況を引き起こすことになり、エキストラシンボルを伴う2つのシンボルの送信が、シリアルバス上の望ましくないシグナリング状況を防止することになるとき、エキストラシンボルをシンボルのシーケンス内の2つのシンボル間に挿入するステップと、シンボルのシーケンスをシリアルバス上で送信するステップとを含み得る。

10

#### 【0009】

本開示の一態様では、データ通信のための装置は、装置をシリアルバスに結合するトランシーバと、処理回路とを含む。処理回路は、シリアルバスが第1の動作モードで動作している間に、シリアルバスに結合された複数のデバイスに第1のコマンドを送信するように構成され得る。第1のコマンドは、シリアルバスが第2の動作モードで動作するようにさせるために、第1のプロトコルに従って送信され得る。処理回路は、第2のプロトコルに従って、シンボルのシーケンス内でデータを符号化することであって、クロック情報がシンボルのシーケンス内の連続するシンボルのペア間の遷移において符号化されることを行うように構成され得る。処理回路は、エキストラシンボルなしの2つのシンボルの送信が、シリアルバス上で望ましくないシグナリング状況を引き起こすことになり、エキストラシンボルを伴う2つのシンボルの送信が、シリアルバス上の望ましくないシグナリング状況を防止することになるとき、エキストラシンボルをシンボルのシーケンス内の2つのシンボル間に挿入するように構成され得る。処理回路は、第2のプロトコルに従って、シンボルのシーケンスをシリアルバス上で送信すること、および、第2の動作モードを終了させるために、第1のプロトコルに従って、複数のデバイスに第2のコマンドを送信することを行うように構成され得る。

20

#### 【0010】

本開示の一態様では、データ通信インターフェースにおいて実行される方法は、シリアルバスが第1の動作モードで動作している間に、シリアルバスに結合された複数のデバイスに第1のコマンドを送信するステップであって、第1のコマンドが、シリアルバスが第2の動作モードで動作するようにさせるために、第1のプロトコルに従って送信されるステップと、シリアルバスが第2の動作モードで動作している間に、第2のプロトコルに従って、複数のデバイスのうちの第1のデバイスと通信するステップと、第2の動作モードを終了させるために、第1のプロトコルに従って、複数のデバイスに第2のコマンドを送信するステップとを含む。第2の動作モードでシリアルバスの第1のライン上で送信された有限持続期間のパルスは、複数のデバイスのうちの第2のデバイスのフィルタに有限持続期間のパルスを抑制させる持続期間を有し得る。

30

#### 【0011】

本開示の一態様では、装置は、シリアルバスが第1の動作モードで動作している間に、シリアルバスに結合された複数のデバイスに第1のコマンドを送信するための手段であって、第1のコマンドが、シリアルバスが第2の動作モードで動作するようにさせるために、第1のプロトコルに従って送信される手段と、シリアルバスが第2の動作モードで動作している間に、複数のデバイスのうちの第1のデバイスと、第2のプロトコルに従って通信するための手段と、第2の動作モードを終了させるために、第1のプロトコルに従って、複数のデバイスに第2のコマンドを送信するための手段とを含む。第2の動作モードでシリアルバスの第1のライン上で送信された有限持続期間のパルスは、複数のデバイスのうちの第2のデバイスのフィルタに有限持続期間のパルスを抑制させる持続期間を有し得る。

40

#### 【図面の簡単な説明】

#### 【0012】

【図1】複数の利用可能な規格のうちの1つに従って選択的に動作する、ICデバイス間の

50

データリンクを採用する装置を示す図である。

【図2】ICデバイス間のデータリンクを採用する装置のためのシステムアーキテクチャを示す図である。

【図3】本明細書で開示するいくつかの態様による送信機および受信機を示す図である。

【図4】本明細書で開示するいくつかの態様による符号化方式の第1の例を示す図である。

【図5】I2Cの1バイトデータ書き込み動作のタイミング図である。

【図6】I2Cデバイスと、共通のシリアルバスに接続されたセンサーグローバルバス(SGbus)デバイスとの構成を示す図である。

【図7】本明細書で開示するいくつかの態様による、シリアルバスの動作モード間、および/または、シリアルバス上で使用され得る複数のプロトコル間で遷移するための一般化された方式を示す図である。 10

【図8】SGbusシリアルインターフェース上のトランザクションの開始および終了を示す図である。

【図9】I2Cプロトコルに従って送信された複数のフレームに関連付けられたタイミングを示す図である。

【図10】意図しないSTART条件およびSTOP条件の発生を示す図である。

【図11】本明細書で開示するいくつかの態様による、共有バス上でデータを送信するための符号化方式の第2の例を示す図である。

【図12】本明細書で開示するいくつかの態様によるSGbus符号化の例を示す図である。 20

【図13】本明細書で開示するいくつかの態様によるSGbus符号化のさらなる例を示す図である。

【図14】本明細書で開示するいくつかの態様によって適応され得る処理回路を採用する装置の一例を示すブロック図である。

【図15】本明細書で開示する1つまたは複数の態様による、SGbusを使用して通信するための方法の第1の例のフローチャートである。

【図16】本明細書で開示するいくつかの態様に従って適応された処理回路を採用する装置のためのハードウェア実装形態の第1の例を示す図である。

【図17】本明細書で開示する1つまたは複数の態様による、SGbusを使用して通信するための方法の第2の例のフローチャートである。 30

【図18】本明細書で開示するいくつかの態様に従って適応された処理回路を採用する装置のためのハードウェア実装形態の第2の例を示す図である。

#### 【発明を実施するための形態】

##### 【0013】

添付の図面に関して以下に記載する詳細な説明は、様々な構成の説明として意図されており、本明細書で説明される概念が実践され得る唯一の構成を表すことは意図されていない。詳細な説明は、様々な概念の完全な理解を提供するために具体的な詳細を含む。しかしながら、これらの概念がこれらの具体的な詳細を伴わずに実践され得ることは当業者に明らかであろう。場合によっては、そのような概念を曖昧にすることを回避するために、よく知られている構造および構成要素がブロック図の形態で示されている。 40

##### 【0014】

次に、様々な装置および方法を参照して、通信システムのいくつかの態様について提示する。これらの装置および方法は、以下の発明を実施するための形態で説明され、様々なブロック、モジュール、構成要素、回路、ステップ、プロセス、アルゴリズムなど(「要素」と総称される)によって添付の図面に示される。これらの要素は、電子ハードウェア、コンピュータソフトウェア、またはそれらの任意の組合せを使用して実装され得る。そのような要素をハードウェアとして実装するか、またはソフトウェアとして実装するかは、特定の適用例および全体的なシステムに課された設計制約に依存する。

##### 【0015】

本出願で使用されるとき、「構成要素」、「モジュール」、「システム」などの用語は 50

、限定はしないが、ハードウェア、ファームウェア、ハードウェアおよびソフトウェアの組合せ、ソフトウェア、または実行中のソフトウェアのような、コンピュータ関連のエンティティを含むことを意図している。たとえば、構成要素は、限定はされないが、プロセッサ上で実行されているプロセス、プロセッサ、オブジェクト、実行可能ファイル、実行スレッド、プログラム、および/またはコンピュータであってもよい。例として、コンピューティングデバイス上で実行されているアプリケーションとコンピューティングデバイスの両方が構成要素であってもよい。1つまたは複数の構成要素は、プロセスおよび/または実行スレッド内に存在することができ、構成要素は、1つのコンピュータ上に局在化され、かつ/または2つ以上のコンピュータ間で分散されてもよい。加えて、これらの構成要素は、その上に記憶された様々なデータ構造を有する様々なコンピュータ可読媒体から実行することができる。構成要素は、ローカルシステム内の、分散システム内の、および/または、インターネットなどのネットワークにわたる別の構成要素と対話する1つの構成要素からのデータなどの、1つまたは複数のデータパケットを有する信号などに従うローカルプロセスおよび/またはリモートプロセスにより、信号を用いて他のシステムと通信する場合がある。

#### 【0016】

その上、「または」という用語は、排他的な「または」よりもむしろ包括的な「または」を意味するものとする。すなわち、別段の指定がない限り、または文脈から明白でない限り、「XはAまたはBを採用する」という句は、自然な包括的並べ替えのいずれかを意味するものとする。すなわち、「XはAまたはBを採用する」という句は、以下の場合のいずれかによって満たされる。XはAを採用する。XはBを採用する。またはXはAとBの両方を採用する。加えて、本出願および添付の特許請求の範囲で使用する冠詞「a」および「an」は、別段に指定されていない限り、または単数形を対象とすることが文脈から明白でない限り、概して「1つまたは複数の」を意味するものと解釈すべきである。

#### 【0017】

##### センサーグローバルバスの概要

広範囲の通信インターフェースに適用可能いくつかの態様を本明細書で開示し、それについて、センサーグローバルバス(SGbus)のコンテキストにおいて説明する。SGbusは、センサーと処理デバイスとを結合するために使用される2線式バスインターフェースとして配備され得る。SGbusのいくつかの例は、一定のレガシーI2CデバイスがSGbusによって使用される同じ線のペアを介して通信し得る程度まで、よく知られているI2Cバスとの後方互換性を提供する。SGbus仕様およびプロトコルを使用して通信するデバイスは、I2Cインターフェースを含む、他のインターフェースを使用して提供され得るよりも高い性能、スループット、信頼性、およびロバストネスを利用し得る。

#### 【0018】

SGbusは、低電力インターフェースの実装を通して、システム電力要件を低減することができ、ビット転送効率を上げることができる。SGbusは、低オーバーヘッドおよび効率的なバス使用に関連付けられる1つまたは複数のプロトコルを採用し、SGbusは、高速トランザクションと、インターフェースがアクティブである時間の対応する低い割合とを可能にすることができます。非アクティブである間、SGbusは、典型的には比較的低電力を消費し、そのことは部分的に、小さいシリコンフットプリントに起因し得る。SGbusを通して接続されたセンサーのセットは、必要または要望に応じて、たとえば、システムレベルにおいて複雑さを最小限に抑えるようにローカルで構成かつ管理され得る。

#### 【0019】

##### シリアルバスを採用するデバイスの例

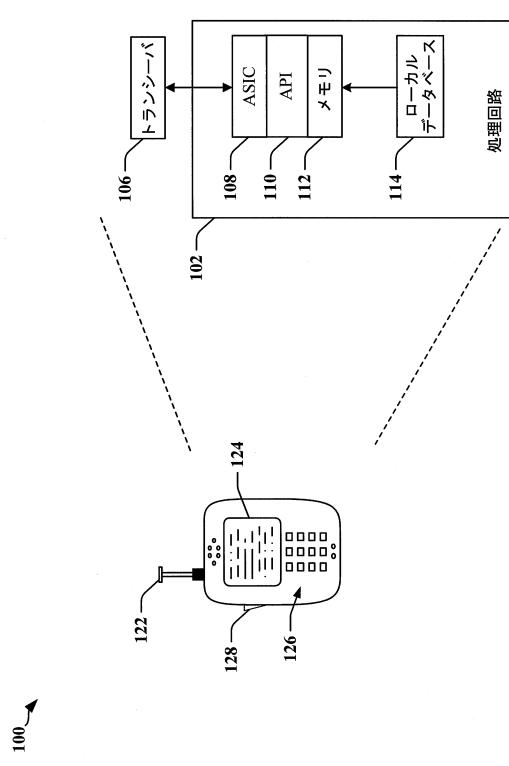

本明細書で開示するいくつかの態様は、電話、モバイルコンピューティングデバイス、ウェアラブルコンピューティングデバイス、アプライアンス、自動車用電子機器、アビオニクスシステムなど、装置の下位構成要素を含み得る電子デバイス間に配備される通信リンクに適用可能であり得る。図1は、ICデバイス間の通信リンクを採用し得る装置を示す。一例では、装置100は、無線周波数(RF)トランシーバを通じて、無線アクセสนットワ

10

20

30

40

50

ーク(RAN)、コアアクセスネットワーク、インターネットおよび/または別のネットワークと通信するワイヤレス通信デバイスを含み得る。装置100は、処理回路102に動作可能に結合された通信トランシーバ106を含み得る。処理回路102は、特定用途向けIC(ASIC)108などの1つまたは複数のICデバイスを含み得る。ASIC108は、1つまたは複数の処理デバイス、論理回路などを含み得る。処理回路102は、処理回路102によって実行され得る命令およびデータを維持し得るメモリデバイス112などのプロセッサ可読ストレージを含み得、かつ/またはそれに結合され得る。処理回路102は、オペレーティングシステムによって、および/または、ワイヤレスデバイスのメモリデバイス112などの記憶媒体内に存在するソフトウェアモジュールの実行をサポートし可能にするアプリケーションプログラミングインターフェース(API)110レイヤを通して、制御され得る。メモリデバイス112は、読み取り専用メモリ(ROM)もしくはランダムアクセスメモリ(RAM)、電気消去可能プログラマブルROM(EEPROM)、フラッシュカード、または処理システム内およびコンピューティングプラットフォーム内で使用され得る任意のメモリデバイスを含み得る。処理回路102は、装置100を構成かつ操作するために使用される操作パラメータおよび他の情報を維持し得るローカルデータベース114を含み得るか、またはそれにアクセスし得る。ローカルデータベース114は、データベースモジュール、フラッシュメモリ、磁気媒体、EEPROM、光媒体、テープ、ソフトディスクまたはハードディスクなどのうちの1つまたは複数を使用して実装され得る。処理回路はまた、他の構成要素の中でも、アンテナ122、ディスプレイ124などの外部デバイス、ボタン128、キーパッド126などのオペレータ制御に動作可能に結合され得る。

## 【0020】

10

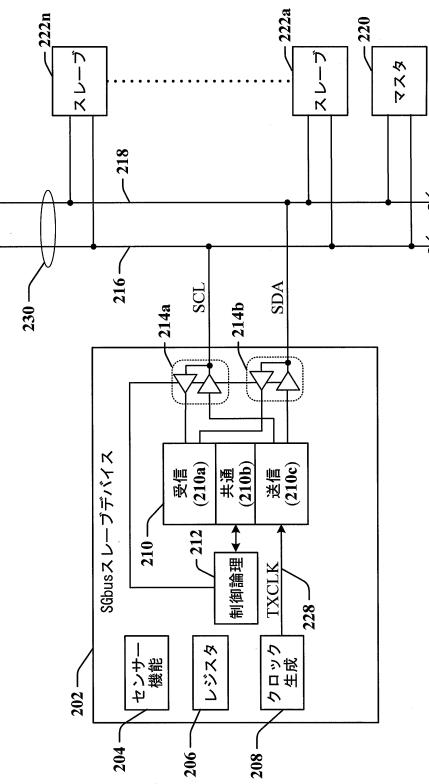

図2は、通信バスに接続された装置200のいくつかの態様を示すブロック概略図であり、この場合、装置は、ワイヤレスモバイルデバイス、モバイル電話、モバイルコンピューティングシステム、ワイヤレス電話、ノートブックコンピュータ、タブレットコンピューティングデバイス、メディアプレーヤ、ゲーミングデバイス、携帯情報端末(PDA)または他のハンドヘルドデバイス、ネットブック、ノートブックコンピュータ、テレビジョン、エンターテインメントデバイス、ウェアラブルデバイスなどのうちの1つまたは複数において実施され得る。装置200は、シリアルバス230を使用して通信する複数のデバイス202、220、および222a～222nを含み得る。シリアルバス230は、シリアルバス230によってサポートされる強化された機能のために構成されているデバイスのために、従来のI2Cバスの能力を拡張することができる。たとえば、シリアルバス230は、I2Cバスよりも高いビットレートをサポートすることができる。

## 【0021】

20

図2に示す例では、デバイス202は、シリアルバス230上でスレーブとして動作するように構成され得る。デバイス202は、1つまたは複数の汎用センサー、高速センサー、指紋センサー、画像センサー(たとえば、カメラ)、タッチスクリーンセンサーなどを含む、かつ/または管理する、センサー機能204を提供するように適応され得る。加えて、デバイス202は、構成レジスタまたは他のストレージ206と、制御論理212と、トランシーバ210と、ラインドライバ/受信機214aおよび214bとを含み得る。制御論理212は、状態機械、シーケンサ、信号プロセッサまたは汎用プロセッサなどの処理回路を含み得る。トランシーバ210は、受信機210aと、送信機210cと、タイミング、論理、およびストレージの回路および/またはデバイスを含む共通回路210bとを含み得る。一例では、送信機210cは、クロック生成回路208によって与えられたタイミングに基づいて、データを符号化および送信する。

## 【0022】

30

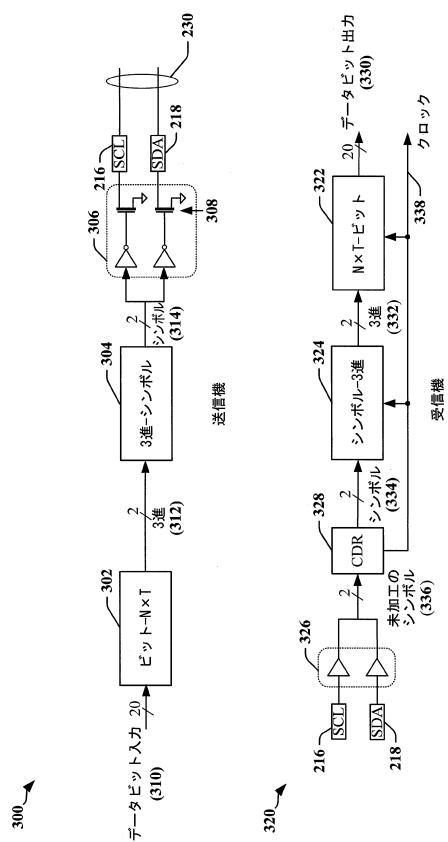

図3は、本明細書で開示するいくつかの態様に従って構成された送信機300および受信機320の一例を示すブロック図である。SGbusの動作の場合、送信機300は、入力データ310を3進(ベース3)数にトランスクードすることができ、3進数は、SCL216およびSDA218信号線上で送信されるべきシンボルにおいて符号化される。図示の例では、入力データ310の各(データワードとも呼ばれる)データ要素は、8、12、16、19、または20ビットなど、事前定義されたビット数を有し得る。トランスクーダ302は、入力データ310を受信し、データ要素ごとに单一の桁の3進数312のシーケンスを生成し得る。場合によっては、単一の桁の3

40

50

進数312のシーケンスは、複数の桁の3進数として表現され得る。単一の桁の3進数は、2ビットにおいて符号化され得、单一の桁の3進数312の各シーケンス内に12桁あり得る。3進-シンボル変換器304などのエンコーダは、ラインドライバ306のペアに与えられる2ビットシンボル314のストリームを生成する。図示の例では、ラインドライバ306は、SCL216およびSDA218信号線を駆動するオープンドレイン出力トランジスタ308を含む。いくつかの例では、ラインドライバ306は、SCL216およびSDA218信号線を駆動するプッシュプルドライバを含むか、またはそれに結合され得る。3進-シンボル変換器304によって生成された2ビットシンボル314の出力ストリームは、連続するシンボル314の各ペア間のSCL216およびSDA218信号線のうちの少なくとも1つのシグナリング状態における遷移を引き起こす。これらの遷移は、連続するシンボルのペアが2つの同一のシンボルを含まないことを保証することによって与えられる。少なくとも1つのライン216および/または218におけるシグナリング状態における遷移の可用性により、受信機320がデータシンボル314のストリームから受信クロック338を抽出することが可能になる。

#### 【 0 0 2 3 】

SGbusインターフェースでは、受信機320は、クロックおよびデータ回復(CDR)回路328を含むか、またはそれと協働し得る。受信機320は、CDR回路328に未加工の2ビットシンボル336のストリームを与えるラインインターフェース回路326を含み得る。CDR回路328は、未加工のシンボル336から受信クロック338を抽出し、2ビットシンボル334のストリームおよび受信クロック338を、受信機320の他の回路324および322に与える。いくつかの例では、CDR回路328は、複数のクロックを生成することができる。シンボル-3進変換器324などのデコーダは、受信クロック338を使用して、シンボル334のストリームを12個の3進数332のシーケンスに復号することができる。3進数332は、2ビットを使用して符号化され得る。次いで、トランスコーダ322は、12個の3進数332の各シーケンスを8、12、16、19、または20ビットの出力データ要素330に変換することができる。

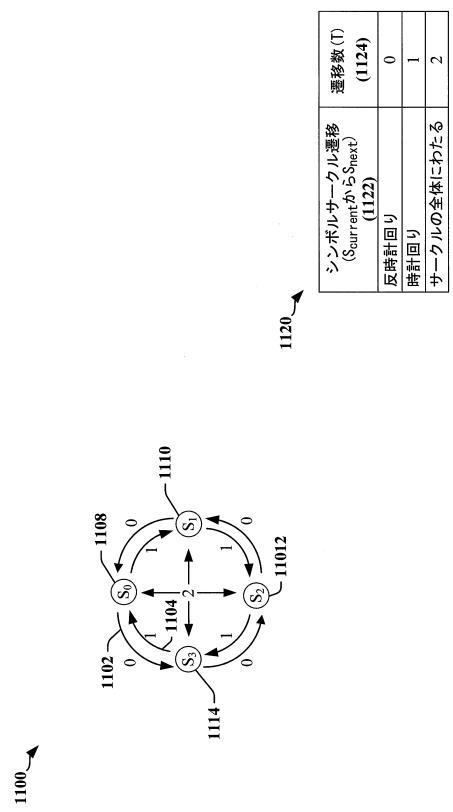

#### 【 0 0 2 4 】

##### 埋込みクロックを用いる遷移符号化方式の例

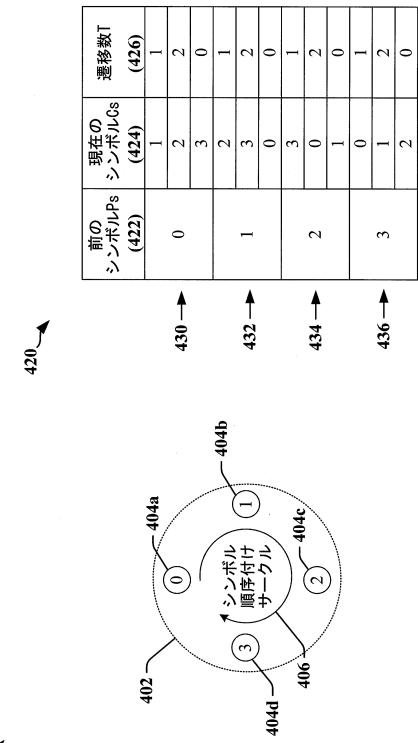

図4は、シリアルバス230上の送信のための埋込みクロックをもつシンボル314のシーケンスを生成するために、3進-シンボル変換器304によって使用され得る符号化方式400を示す図である。符号化方式400はまた、シリアルバス230から受信されたシンボルから3進遷移数を抽出するために、受信機320のシンボル-3進変換器324によっても使用され得る。SGbus符号化方式400では、シリアルバス230の2本のラインにより、4つの基本シンボル $S: \{0, 1, 2, 3\}$ の定義が可能になる。シンボル314、334のシーケンス内の任意の2つの連続するシンボルは、シリアルバス230上で異なるシグナリング状態を生成し、シンボルシーケンス0, 0, 1, 1, 2, 2、および3, 3は、連続するシンボルの無効な組合せである。したがって、各シンボル境界で3つのみの有効なシンボル遷移が利用可能であり、ここで、シンボル境界は送信クロックによって決定され、第1のシンボル(前のシンボル $P_s$ )422が終了し、第2のシンボル(現在のシンボル $C_s$ )424が開始するポイントを表す。

#### 【 0 0 2 5 】

本明細書で開示するいくつかの態様によれば、3つの利用可能な遷移には、 $P_s$ シンボル422ごとに遷移数( $T$ )426が割り当てられる。 $T_{426}$ の値は、3進数によって表され得る。一例では、遷移数426の値は、符号化方式用のシンボル順序付けサークル402を割り当てることによって決定される。シンボル順序付けサークル402は、4つの可能なシンボル用のサークル402上のロケーション404a ~ 404d、およびロケーション404a ~ 404dの間の回転の方向406を割り振る。図示の例では、回転の方向406は時計回りである。遷移数426は、有効な現在のシンボル424と直前のシンボル422との間の分離を表し得る。分離は、前のシンボル422から現在のシンボル $C_s$ 424に到達するために必要なシンボル順序付けサークル402上の回転の方向406に沿ったステップの数として定義され得る。ステップの数は、单一の桁のベース3数として表現され得る。シンボル間の3ステップの差分は、 $0_{base-3}$ として表され得ることが諒解されよう。図4のテーブル420は、この手法を採用する符号化方式をまとめたものである。

10

20

30

40

50

**【 0 0 2 6 】**

送信機300において、前に生成されたシンボル422、および遷移数426として使用される入力3進数を知ると、テーブル420は、送信されるべき現在のシンボル424をルックアップするために使用され得る。受信機320において、テーブル420は、前に受信されたシンボル422と現在受信されたシンボル424との間の遷移を表す遷移数426を決定するためのルックアップとして使用され得る。遷移数426は、3進数として出力され得る。

**【 0 0 2 7 】****シリアルバス上の共存**

複数のSGbusデバイスは、1つまたは複数のレガシーI2Cデバイスとともに同じバス230上で共存し得る。したがって、SGbusインターフェースは、レガシーI2Cデバイスによって無視されるか、検出されないか、またはさもなければ軽視され得る、シグナリング方式を定義する。たとえば、SGbusデバイスは、I2Cモードシグナリングと一致するシグナリングにおいて制御情報を送信することができ、より高速の送信速度を得るために、CCleプロトコルに従って符号化されたデータペイロードを送信することができる。SGbusデバイスは、レガシーI2Cモードを含む、データペイロードを送信するための他の符号化モードを使用し得る。代替符号化モードは、シンボルのシーケンス内の連続するシンボル間の遷移において埋め込まれたクロック情報をもつシンボルのシーケンス内でデータを符号化するために、遷移符号化を採用し得る。すなわち、データが3進数にトランスクードされ得、その場合、3進数の各桁は、バスの前のシグナリング状態(すなわち、前のシンボル)に基づいて、次のシンボルを選択する。

10

**【 0 0 2 8 】**

本明細書で開示するいくつかの態様は、異なる通信プロトコルおよび/またはシグナリングを使用して通信するデバイスのシリアルバス上の共存に関する。いくつかの例では、第1のプロトコルを使用して、シリアルバスを介して通信するように構成されたデバイスは、第2のプロトコルが、第1のプロトコルによって認識されるイベントを生成するシグナリングを採用するとき、第2のプロトコルを使用する他のデバイス間の通信を無視し得る。次に、第1のプロトコルがI2C対応または互換プロトコルであり、第2のプロトコルがCCle、SGbus、または他のプロトコルである例を使用して、いくつかの態様について説明する。

20

**【 0 0 2 9 】**

30

図5は、I2Cの1バイトデータ書き込み動作を示すタイミング図500である。マスタノードが、SCL216が高のままである間にSDA218を低に駆動することによって、START条件506を与えるとき、送信が開始される。I2Cマスタノードは、I2Cバス上のどのスレーブノードにマスタノードがアクセスすることを望むかを示すために、SDA218上で7ビットのスレーブID502と、続いて、動作が読み取り動作であるか、書き込み動作であるかを示す、読み取り/書き込みビット512とを送り、それによって、読み取り/書き込みビット512は、書き込み動作を示すために論理0にあり、読み取り動作を示すために論理1にある。IDが7ビットのスレーブID502と一致するスレーブノードのみが、書き込み(または他の)動作に応答することができる。I2Cスレーブノードがそれ自体のスレーブID502を検出するため、マスタノードは、SCL216上の8個のクロックパルスとともに、SDA218上で少なくとも8ビットを送信する。マスタノードは、SCL216が高のままである間にSDA218を高に駆動することによって、トランザクションを終了させるために、STOP条件516を与える。I2Cインターフェースは、START条件506後に「Bus-Busy」状態であり、STOP条件516後に「Bus-Free」状態であると見なされる。この挙動は、レガシーI2Cスレーブノードが、CCleプロトコルを含むいくつかのプロトコルによる送信に反応することを防止するために、活用され得る。

40

**【 0 0 3 0 】**

CCle通信は、データ送信のためにI2CバスのSCL216およびSDA218の組合せを使用し得る。CCleシンボルは、I2C送信用のSCL216上で送信されたクロック信号パルス514の各トグルに対応する時間において送信され得る。したがって、各フレーム送信期間内に送信されたクロックトグルの数は、CCle送信ごとに送信され得るシンボルの数を定義し得る。したが

50

つて、12シンボル送信は、6-SCLパルスシーケンス中に利用可能な12個のシグナリング状態において与えられ得る。

#### 【0031】

I2CバスのSCL216および/またはSDA218は、クロック信号がシンボル遷移内に埋め込まれたとき、CCl eモードにおけるデータ送信のために利用され得る。したがって、SDA218およびSCL216は、レガシーI2Cスレーブノードの機能に影響を与える前に、かつプリッジデバイスを使用してCCl e対応ノードからレガシーI2Cスレーブノードを隔離せずに、任意の12個のシンボルを送信するために使用され得る。I2Cモードでは、START条件506は、I2Cマスターによってのみ与えられ得る。CCl eモードでは、START条件506は、12シンボルワードを送信することになるどのノードによっても与えられる。

10

#### 【0032】

本明細書で開示するいくつかの態様によれば、SCL216のいくつかのシグナリング特性が活用されるとき、I2Cデバイスは、異なる通信プロトコルを採用するデバイスとともにシリアルバス上で共存し得る。たとえば、スパイク、および/または、50ns以下の持続期間をもつパルスが、I2C高速モード(Fm)またはFm+デバイスと互換性のある、またはそれに対応するデバイスによってフィルタ処理されるというI2C仕様。したがって、I2Cデバイスとともに共有されるシリアルバス上で使用されるプロトコルは、SCL216上のパルスが50ns未満の持続期間に制限される動作モードを含み得る。パルスの持続期間の制限は、SCL216上のハイの状態のクロックパルス生成を制御すること、SCL216のためのゼロ復帰シグナリング方式を実施することによって、および/または、SCL216が50nsの間にハイの状態のままであることを防止するエキストラシンボルを挿入することによって実施され得る。エキストラシンボルは、本明細書ではダミーシンボルと呼ぶことがある。一例では、いくつかのシンボルが50ns期間内に送信され得、エンコーダが、シンボルのシーケンスがSCL216を50nsの間にハイの状態に維持する可能性が高いことを検出するとき、エンコーダは、50ns高期間が完了する前に、SCL216を低になるように強制するダミーシンボルを挿入し得る。

20

#### 【0033】

ダミーシンボルの挿入は、余分なパルス(ダミーパルス)がシリアルバスの1つまたは複数の信号線上で送信されることを引き起こし得る。上記で説明したI2Cの例では、ダミーシンボルは、2つの連続するシンボルがSCL216を論理がハイの状態に維持することになると、SCL216上で論理がローの状態に強制的にするために挿入され得る。ダミーシンボルの送信後、SCL216は、2つの連続するシンボルにおける第2のシンボルに対応する論理がハイの状態に戻る。場合によっては、ゼロ復帰(RZ)シグナリングが、SCL216上で長い持続期間の正パルスを防止するために、SCL216上で使用され得る。場合によっては、ハードウェア論理は、SCL216が事前定義された時間期間の間にハイの状態のままであるとき、短い持続期間の論理がローのパルスを挿入することによって、SCL216をポリシングするように構成され得る。

30

#### 【0034】

ダミーパルスは、遷移シンボル符号化が使用されるとき、見掛けのクロックパルスの持続期間を制限する以外の目的で、シリアルバスの1つまたは複数の信号線上に挿入され得る。ダミーパルスは、同期イベントまたは条件を示し得る、求められていない状態の発生を回避するために与えられ得る。たとえば、I2C STARTおよびSTOP条件は、SDA218が変化しないままである間にSCL216が低になるときに示され得、ダミーパルスは、シリアルバスがI2C以外のプロトコルによる通信のために使用されるとき、そのような指示を防止するために、SDA218上に挿入され得る。

40

#### 【0035】

##### 通信プロトコル間の遷移

図6は、共有バス602がI2Cデバイス604<sub>1</sub>～604<sub>k</sub>、606、ならびにSGbusデバイス612、614<sub>1</sub>～614<sub>n</sub>および616<sub>1</sub>～616<sub>m</sub>を結合する構成を示す。SGbusデバイス612、614<sub>1</sub>～614<sub>n</sub>および616<sub>1</sub>～616<sub>m</sub>は、従来のように構成されたI2Cデバイス604<sub>1</sub>～604<sub>k</sub>、606と共に存することができ、SGbusデバイス612、614<sub>1</sub>～614<sub>n</sub>および616<sub>1</sub>～616<sub>m</sub>のうちのいくつかは、要望または必要

50

に応じて、従来のI2Cプロトコルを使用して通信することができる。

#### 【0036】

構成および他のバス制御メッセージを含む、共有バス602上のデータ転送は、I2Cプロトコルの変更バージョンまたはI2Cプロトコルの変形態など、第1のプロトコルを使用して開始かつ実行され得る。一例では、すべてのトランザクションは、そのトランザクションを開始するために従来のI2Cプロトコルを使用して開始され得る。

#### 【0037】

本明細書で開示するいくつかの態様によれば、共有バス602に結合されたデバイス間のデータ転送が、バス管理および/または制御コマンド間で発生するトランザクション(コンテナ)においてカプセル化されるように、共有バス602上の通信が有効にコンテナ化され得る。典型的には、現在のトランザクションに従事しているデバイスによって採用されたプロトコルを使用して通信するように構成されるデバイスは、そのトランザクションを無視するか、またはそれに気づかないことがある。

#### 【0038】

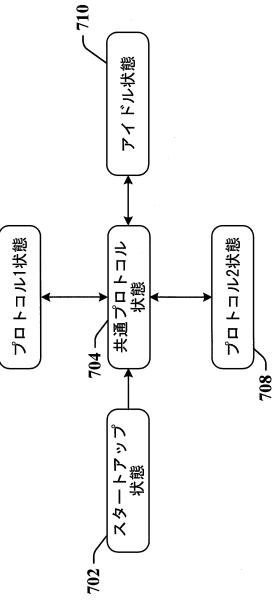

図7は、共有バス602のコンテナまたは動作モード間で遷移するための一般化された方式を示す流れ図700である。各コンテナ、動作モード、および/またはプロトコルは、共有バス602の対応する動作状態702、704、706、708、710に関連付けられ得る。バスの動作モードは、シグナリング方式、データスループット、送信フォーマットなどの間で区別することができる。異なる動作モードが、プロトコルに対して定義され得る。たとえば、12シンボルモードおよび20シンボルモードが、PCIeプロトコルに対して定義され得る。

10

#### 【0039】

動作時、共通プロトコル状態704は、すべてのバスマスタデバイスによって、および/またはバス上のすべてのデバイスによって理解される共通プロトコルを使用して、バス管理コマンドを交換するために使用される。一例では、單一プロトコルスレーブデバイスは、共通プロトコルを使用して通信することができないことがあり、したがって、バス管理コマンドを無視することがある。この後者の例では、バスマスタデバイスは、共有バス602を制御し、單一プロトコルスレーブデバイスによって理解されるプロトコルを使用して、單一プロトコルスレーブデバイスと通信し得る。

20

#### 【0040】

いくつかの例では、I2Cプロトコルが共通プロトコル状態704において使用される。他の例では、異なるプロトコルが共通プロトコル状態704において使用され得る。共有バス602は、スタートアップ状態702に初期化され得、それによって、共有バス602に結合されたデバイスが、共通プロトコルのために構成される。共通プロトコルの单一バスマスタの実装形態では、指定されたバスマスタは、共通プロトコルによって定義されたプロシージャに従って、共有バス602に結合された他のデバイスを発見かつ/または構成し得る。マルチマスタ実装形態では、1つまたは複数のマスタデバイスが、発見、構成、および/またはアビトリエーションプロセスに参加して、共通プロトコル状態704に入るときに、どのバスマスタが共有バス602を制御するかを決定し得る。バス階層の概念が採用されることがあり、その場合、1つのバスマスタデバイスが、任意の時間に共有バス602のアクティブな制御を有し、他のバスマスタデバイスが、共有バス602のグラント制御を要求し、待機する。

30

#### 【0041】

共通プロトコル状態704では、1つまたは複数のデバイスが、共有バス602の制御を求めて競合し得る。共有バス602は、共有バス602に結合されたデバイス間の通信トランザクションを可能にするために、所望のまたはアビトリエートされたプロトコル状態706、708において操作され得る。トランザクションの完了時に、共有バス602は共通プロトコル状態704に戻される。共有バス602へのアクセスを要求中であるデバイスがないとき、共有バス602はアイドル状態710に入り得る。アイドル状態では、1つまたは複数のデバイスが電源切断動作モードに入り得る。バスマスタデバイスは、いずれかのデバイスが共有バス602へのアクセスを要求中であるか否かを決定するために、共有バス602が共通プロトコル状態704に定期的に入ることを引き起こし得る。場合によっては、共有バス602は、割込みまた

40

50

は他のイベントに応答して、共通プロトコル状態704に戻され得る。

**【0042】**

プロトコル状態704、706、708に入ること、およびプロトコル状態704、706、708から出ることは、バス管理コマンドを使用して実施され得る。これらのコマンドは、シグナリング、メッセージング、または、共有バス602のアーキテクチャおよび設計に基づいて選択されたシグナリングおよびメッセージングの何らかの組合せを使用して実施され得る。

**【0043】**

データ転送は、共通プロトコル状態704、または、共有バス602に結合されたデバイスのサブセットによって使用されるプロトコル状態706、708のうちの1つにおいて発生し得る。デバイスのサブセットによって使用されるプロトコル状態706、708は、共有バス602と互換性のある任意のプロトコルであり得る。データは、ワード、フレーム、および/またはパケット単位で転送され得、柔軟なデータ転送モードが企図される。10

**【0044】**

場合によっては、アドレスが、共有バス602に結合されたデバイスに動的に割り振られ得る。一例では、共通プロトコルを使用して通信するデバイスの一意の識別情報を提供するために、およびそのようなデバイスのための優先度ランク付けを割り当てるために、動的アドレス割振りが共通プロトコル状態704において実行される。場合によっては、共通プロトコル以外のプロトコルを使用して通信するデバイスの一意の識別情報を提供するために、およびそのようなデバイスのための優先度ランク付けを割り当てるために、動的アドレス割振りが、他のプロトコル状態706、708のうちの1つまたは複数において実行される。20

**【0045】**

場合によっては、例外処理方式が共通プロトコル状態704のために定義される。たとえば、I2C互換帯域内割込みプロシージャは、共通プロトコルがI2CまたはI2Cの派生物であるときに提供され得る。

**【0046】**

場合によっては、「ホットプラグ」プロシージャが実施されることがあり、その場合、そのホットプラグプロシージャは、帯域内割込みプロシージャおよび動的アドレス割振りプロシージャを含み、かつ/または使用する。

**【0047】**

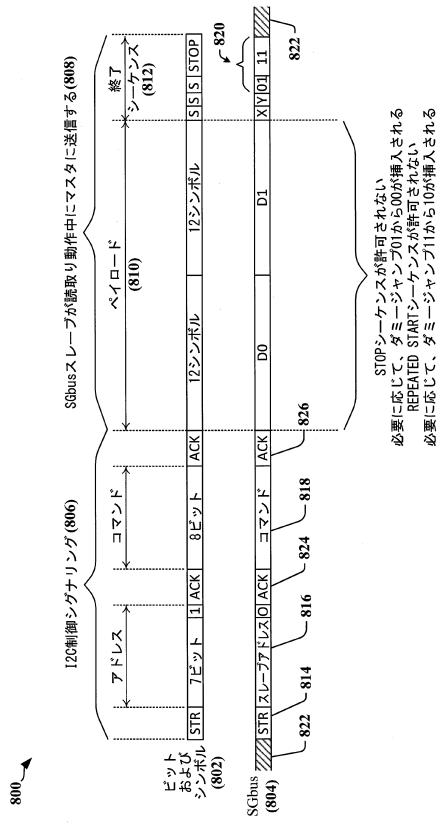

図8は、本明細書で説明するいくつかの態様による、共有バス602がそれぞれビットおよびシンボル802送信済みI2CおよびSGbusプロトコルを伴う通信トランザクションをサポートする一例のための、共有バス602上で実行されるトランザクション800を示す。最初に、共有バス602は、Bus-Free状態822であり得、制御シグナリング806は、一般に理解されるI2Cプロトコルに従って扱われる。制御シグナリング806が、824、826で肯定応答された後、SGbusデータ交換808が発生し得、その間に、データペイロード810がSGbusマスタデバイス612に送信される。終了シーケンス812は、SGbusデータ交換808(すなわち、SGbusプロトコルによるシグナリング)から、I2Cプロトコルと一致するSTOP条件820、516として認識されるシグナリングへの遷移を与える。次いで、Bus-Free状態822(図7のアイドル状態710も参照)が生じ得る。3040

**【0048】**

図示の例では、共有バス602上のトランザクション800が、アドレス816(たとえば、I2CスレーブID502を参照)と後に続くコマンドコード818の連続とに先行するI2C START条件814(図5のSTART条件506も参照)によって開始され得る。コマンドコード818は、共有バス602のために使用されるSGbus通信プロトコルによって事前定義されたバイト数を含み得る、可変長を有し得る。

**【0049】**

一例では、コマンドコード818は、選択されたデータ転送プロトコル、および/またはデータ転送プロトコルのいくつかの特性を定義するために送信され得る。この後者のコマンドコードは、後続のデータ転送のために使用されるべき複数の利用可能なデータ転送プロ50

トコルのうちの1つを識別し得る。識別されたデータ転送プロトコルは、異なるデータ転送プロトコルコマンドがバス上に挿入されるまで、トランザクションを制御し得る。

#### 【 0 0 5 0 】

START条件814の後、次のSTOP条件820(図5のSTOP条件516も参照)まで、共有バス602はビジーであると見なされる。Bus-Free状態822は、SCL216およびSDA218が所定の時間期間の間に論理がハイの状態であるとき、発生中であると定義され得る。共有バス602のビジー/フリー状態は、START条件814、506、およびSTOP条件820、516の発生に基づいて、定義または識別され得る。Bus-Free状態822は、STOP条件820、516の後の時間期間を含む持続期間を有し、その間に、データがSGbusプロトコルを使用して転送されるか、I2C互換プロトコルを使用して転送されるかにかかわらず、SCL216およびSDA218が論理がハイの状態である。一例では、その間にSCL216およびSDA218が論理がハイの状態である時間期間が、共有バス602上で使用される最も遅いクロックの周期の2倍になるように設定され得る。たとえば、I2C高速モードでは、SCL216上で送信されるクロック信号は、 $2.5 \mu s$ のクロック周期とともに、少なくとも400kHzの周波数を有し、 $5 \mu s$ 周期が、Bus-Free状態822を示すために十分であり得る。10

#### 【 0 0 5 1 】

図6に示すように、共有バス602は、レガシーI2Cマスタデバイス606と、レガシーI2Cスレーブデバイス $604_1 \sim 604_k$ と、プライマリSGbusマスタデバイス612と、SGbusスレーブデバイス $614_1 \sim 614_n$ と、SGbusセカンダリマスタデバイス $616_1 \sim 616_m$ とをサポートし得る。

プライマリSGbusマスタデバイス612は、典型的には、共有バス602上に存在するレガシーI2Cデバイス606、 $604_1 \sim 604_k$ に関係するある動作情報を用いて事前構成される。プライマリSGbusマスタデバイス612は、それにおいて動作情報および他の情報が、アプリケーションホストデバイスから受信された通信に応答して事前構成かつ/または更新され得る、不揮発性メモリを含み得る。20

#### 【 0 0 5 2 】

セカンダリSGbusマスタデバイス $616_1 \sim 616_m$ 、およびSGbusスレーブデバイス $614_1 \sim 614_n$ の各々は、任意の所望の、構成された、または事前定義された長さのランダムアドレスを内部で生成するよう構成され得る。一例では、ランダムアドレスは48ビットを有し得る。これらのデバイス $614_1 \sim 614_n$ 、 $616_1 \sim 616_m$ は、ローカルアドレスが割り当てられていないデバイスの存在を識別するために使用され得る予約済みアドレスを使用して、割込みを引き起こすことが可能であり得る。30

#### 【 0 0 5 3 】

動作時、プライマリSGbusマスタデバイス612は、一般呼出しと、後に続く動的アドレス割振りコマンドコードとを送信し得る。次いで、プライマリSGbusマスタデバイス612は、論理がハイのレベルにプルされ得るSDA218を解放しながら、共有バス602のSCL216上でクロック信号を駆動し得る。アービトレーションプロセスが後に続き、それによって、SGbusデバイス $614_1 \sim 614_n$ 、 $616_1 \sim 616_m$ は、それらの対応するランダムに選択された48ビットアドレスに従って、SDA218を駆動する。SGbusデバイス $614_1 \sim 614_n$ 、 $616_1 \sim 616_m$ のうち最低のアドレスをもつものが、I2Cプロトコルによって規定されるような同様の方式で、アービトレーションを勝ち取る。40

#### 【 0 0 5 4 】

プライマリSGbusマスタデバイス612は、SCL216上でクロック信号を駆動し続け、SDA218が解放される。次いで、SGbusデバイス $614_1 \sim 614_n$ 、 $616_1 \sim 616_m$ の中から勝ったデバイスは、1つまたは複数の特性バイトを転送し得る。特性バイトは、デバイスがスレーブデバイスのみとして機能するか否か、デバイスのタイプ(たとえば、加速度計)、データ幅(たとえば、16または12ビット幅)、および他の特性を含む、勝ったデバイスのいくつかの特性を識別する情報を含む。

#### 【 0 0 5 5 】

プライマリSGbusマスタデバイス612は、勝ったデバイスのための7ビット幅ローカルアドレスを転送し得る。このアドレスは、プライマリSGbusマスタデバイス612が識別された50

デバイスに割り当てる優先度レベルを組み込む。プライマリSGbusマスタデバイス612は、アドレスアービトレーションを求めるデバイスからの応答を受信しなくなるまで、このプロシージャを繰り返し得る。プライマリSGbusマスタデバイス612は、プロシージャに入ることを可能にした動的アドレス割振りコマンドコードを終了させる特定のコマンドコードを送ることによって、アービトレーションプロシージャを終了させ得る。

#### 【0056】

共有バス602に接続されたセカンダリSGbusマスタデバイス616<sub>1</sub>～616<sub>m</sub>は、アービトレーションプロセスを監視し、そのプロセス中に情報交換を取り込むことができ、セカンダリSGbusマスタデバイス616<sub>1</sub>～616<sub>m</sub>は、共有バス602のためのアドレス指定、優先度、および構成情報のコピーを有するようになる。それにもかかわらず、プライマリSGbusマスタデバイス612は、SGbusスレーブデバイス614<sub>1</sub>～614<sub>n</sub>から受信された情報を、セカンダリSGbusマスタデバイス616<sub>1</sub>～616<sub>m</sub>に転送し得る。10

#### 【0057】

SGbusデバイス614<sub>1</sub>～614<sub>n</sub>、616<sub>1</sub>～616<sub>m</sub>の各々は、動的アドレスを記憶するために使用され得る1つまたは複数の保持レジスタを有することができ、SGbus構成が、コールド電源投入後に使用するために確保され得るようになる。2つのSGbusデバイス614<sub>1</sub>～614<sub>n</sub>および/または616<sub>1</sub>～616<sub>m</sub>が、同じランダムな48ビットアドレスを選択し、同じ特性バイトを有する場合、2つのデバイスは同じローカルアドレスを記憶し得る。二重割当てでは、実際には、SGbusマスタデバイス612がデータ転送を必要とし、2つの異なるSGbusスレーブデバイス614<sub>1</sub>～614<sub>n</sub>によって同時に送信されたデータが異なるまで、残り得る。2つのSGbusスレーブデバイス614<sub>1</sub>～614<sub>n</sub>のうちの少なくとも1つは、共有バス602に接続された別のSGbusスレーブデバイス614<sub>1</sub>～614<sub>n</sub>と同じアドレスを有することを認識することができ、共有バス602から外れることができる。次のBus-Free状態822において、外されたSGbusスレーブデバイス614<sub>1</sub>～614<sub>n</sub>は、この要件のための専用の制御コードを使用して、新しいローカルアドレスを要求し得る。本明細書で開示するいくつかの態様によって適応され得る既存のプロシージャを含む、同じローカルアドレスの二重割当てを識別するための他のプロシージャが利用可能であり得る。たとえば、プライマリまたはメインマスタデバイスは、ローカルアドレスを必要とするデバイスの数を知らされ得、より少ないローカルアドレスが割り振られるかまたは割り当てられる場合、メインマスタは回復プロシージャを開始かつ/または実行し得る。回復プロシージャの一例では、動的アドレス割当てプロシージャが最初から再開され得る。信頼できるフォールバックプロシージャの他の例は、2つ以上のデバイスが重複アドレスを有する場合からの回復において使用するために利用可能である。2030

#### 【0058】

SGbusデバイス614<sub>1</sub>～614<sub>n</sub>および/または616<sub>1</sub>～616<sub>m</sub>の各々は、プライマリSGbusマスタデバイス612によって優先度ランク付けを割り当てられる。優先度ランクは、SGbusマスタデバイス612によって、動的に割り振られたローカルアドレスのレベルを使用して定義され得、それによって、より低いアドレス値がより高い優先度ランクを有する。

#### 【0059】

SGbusデバイス614<sub>1</sub>～614<sub>n</sub>、616<sub>1</sub>～616<sub>m</sub>の各々は、Bus-Free状態中の任意の時間に帯域内割込み要求(IRQ)をアサートすることができる。IRQアサーションプロシージャは、I2Cおよび他のI2C関連インターフェースにおいてバスアービトレーションのために使用される同様のプロシージャに対応する。しかしながら、本明細書で開示するいくつかの態様によれば、いくつかの改良および強化がIRQプロシージャのために採用され得る。40

#### 【0060】

一例では、SGbusスレーブデバイス614<sub>1</sub>～614<sub>n</sub>は、SDA218を論理がローのシグナリング状態にプルすることによって、帯域内IRQをアサートすることができる。プライマリSGbusマスタデバイス612は、SDA218を駆動されないままにしながら、SCL216上でクロック信号を駆動することを開始し得る。SDA218は、論理がハイのシグナリング状態の方にプルされ得る。SGbusスレーブデバイス614<sub>1</sub>～614<sub>n</sub>は、それ自体のアドレスを送信するために、SDA218を駆動し得る。プライマリSGbusマスタデバイス612は、IRQを認め、次いで、SGbusス50

レープデバイス $614_1 \sim 614_n$ から受信されたアドレスを使用して、反復STARTを実行する。SCL信号線924がBus-Busy状態中に高である間、およびSTOP条件908が期待されることになるとき、SDA信号線922を低に駆動することによって、反復START条件928(図9参照)が与えられる。デバイス $614_1 \sim 614_n$ 、 $616_1 \sim 616_m$ 、および/または $604_1 \sim 604_k$ は、反復START条件928を検出した後、それらのそれぞれのアドレスについてバスを監視し得る。

#### 【0061】

プライマリSGbusマスタデバイス612は、前に定義されたモードが現在所望または必要とされるモードとは異なる場合、データ転送プロトコルバイトを使用して、データ転送モードを随意に構成し得る。次いで、プライマリSGbusマスタデバイス612および割り込むSGbusスレープデバイス $614_1 \sim 614_n$ は、通信を開始し得る。バス競合はアドレス評価中に行われ、同時にバスを勝ち取ろうと試みている任意の追加のSGbusデバイス $614_1 \sim 614_n$ 、 $616_1 \sim 616_m$ 、および/または任意のレガシーI2Cデバイス $604_1 \sim 604_k$ は、そのアービトレーションに負けることになり、次のBus-Free状態822において再試行し得る。10

#### 【0062】

別の例では、セカンダリSGbusマスタデバイス $616_1 \sim 616_m$ は、SGbusスレープデバイス $614_1 \sim 614_n$ のためのものと同様であるプロシージャを使用して、帯域内IRQをアサートすることができる。プライマリSGbusマスタデバイス612が、IRQがセカンダリSGbusマスタデバイス $616_1 \sim 616_m$ によってアサートされることを認識するとき、プライマリSGbusマスタデバイス612は、SCL216を解放し、セカンダリSGbusマスタデバイス $616_1 \sim 616_m$ は、通信のためのターゲットデバイスをアドレス指定するために、即時反復START条件928を実行する。20

#### 【0063】

別の例では、レガシーI2Cマスタデバイス606は、セカンダリSGbusマスタデバイス $616_1 \sim 616_m$ について説明したものと同様であるプロシージャにおいて、IRQをアサートし得る。レガシーI2Cマスタデバイス606は、典型的には、いつそれがSGbusマスタデバイス612と競合中であるかに気づいておらず、その理由は、SGbusマスタデバイス612が等価のより高いアドレス(たとえば、111 1111)を有し、アービトレーションに負ることになるからである。いくつかの適用例では、I2Cデバイスなどのより遅いレガシーデバイスをSGbusから除外することが望ましくなり得ることは諒解されよう。たとえば、レガシーデバイスは、バス速度(スループット要件)のために、または、共存を可能にするために必要とされるプロシージャの複雑さのために、排除され得る。30

#### 【0064】

通信トランザクションを開始するプライマリSGbusマスタデバイス612は、アドレス呼出し中に、アドレスアービトレーションプロシージャを評価する。任意のSGbusスレープデバイス $614_1 \sim 614_n$ 、セカンダリSGbusマスタデバイス $616_1 \sim 616_m$ 、または、プライマリSGbusマスタデバイス612に割り込むことを試みるレガシーI2Cマスタデバイス606は、典型的に成功する。しかしながら、より低い優先度ランクを有するいかなるデバイスも、次のBus-Free状態822を待機しなければならないことがある。

#### 【0065】

場合によっては、レガシーI2Cマスタデバイス606とSGbusスレープデバイス $614_1 \sim 614_n$ との間で競合があり得る。プライマリSGbusマスタデバイス612は、START条件を見るとき(すなわち、SDA218が低になるとき)、SCL216上でクロック信号を開始する。したがって、より高い優先度ランクを有するSGbusスレープデバイス $614_1 \sim 614_n$ は、仮定によるとアービトレーションプロセスを勝ち取る。プライマリSGbusマスタデバイス612は、勝ったアドレスを含む、アービトレーションプロセスの結果を承知している。40

#### 【0066】

本明細書で開示するいくつかの態様によれば、SGbusは、1つまたは複数のSGbusマスタデバイス612、 $616_1 \sim 616_m$ 、およびレガシーI2Cマスタデバイス606が、対応するスレープデバイスのためのバス制御および管理機能を提供する、マルチマスタバスであり得る。SGbusにおいて採用されるいくつかのマルチマスタアービトレーションおよびバス制御プロシージャは、IRQプロシージャについて説明されるものなど、グローバルなルールに従い50

得る。したがって、I2Cルールは、レガシーI2Cマスタデバイス606が1つまたは複数のSGbusセカンダリマスタデバイス616<sub>1</sub>～616<sub>m</sub>と競合するとき、適用され得る。

#### 【0067】

SGbusセカンダリマスタデバイス616<sub>1</sub>～616<sub>m</sub>が、トランザクションを実行するために共有バス602の制御を獲得するとき、SGbusセカンダリマスタデバイス616<sub>1</sub>～616<sub>m</sub>は、トランザクションを実行することが必要とされる限りの間のみ、共有バス602の制御を維持する。それぞれのトランザクション後、STOP条件820は、バス制御をプライマリSGbusマスタデバイス612に復帰させる。

#### 【0068】

レガシーI2Cマスタ606は、一般にデータをレガシーI2Cスレーブデバイス604<sub>1</sub>～604<sub>k</sub>へ転送し、CCIEデータ転送プロトコルなどの他のデータ転送プロトコルが利用可能であるときでも、I2C対応プロトコルを採用する。レガシーI2Cマスタ606とSGbusデバイス614<sub>1</sub>～614<sub>n</sub>、616<sub>1</sub>～616<sub>m</sub>との間の通信は、システムレベルで管理され得る。一例では、プライマリSGbusマスタデバイス612は、レガシーI2Cマスタ606にSGbusスレーブデバイス614<sub>1</sub>～614<sub>n</sub>の存在を知らせ得る。プライマリSGbusマスタデバイス612は、SGbusスレーブデバイス614<sub>1</sub>～614<sub>n</sub>のローカルアドレスおよび特性に関する情報を提供し得る。レガシーI2Cマスタ606とSGbusスレーブデバイス614<sub>1</sub>～614<sub>n</sub>との間で得られたいかなる通信も、I2Cプロトコルと一致し得る。

#### 【0069】

本明細書で開示するいくつかの態様によれば、SGbusは、SGbusデバイス612、614<sub>1</sub>～614<sub>n</sub>、または616<sub>1</sub>～616<sub>m</sub>が、すでに動的に構成されておりオプションであるバス602に挿入され得る、ホットプラグ能力をサポートし得る。ホットプラグされたSGbusデバイス612、614<sub>1</sub>～614<sub>n</sub>、または616<sub>1</sub>～616<sub>m</sub>は、バス上で電源投入し、コールド電源投入と同様の条件を仮定し、ホットプラグされたSGbusデバイス612、614<sub>1</sub>～614<sub>n</sub>、または616<sub>1</sub>～616<sub>m</sub>は、割り当てられたローカルアドレスを最初は有していない。割り当てられたローカルアドレスを有していないデバイス612、614<sub>1</sub>～614<sub>n</sub>、または616<sub>1</sub>～616<sub>m</sub>は、ローカルアドレスを必要とするというインジケータとして事前定義されたバイトを使用して、IRQを実行し得る。IRQ、および、ホットプラグされたSGbusデバイス612、614<sub>1</sub>～614<sub>n</sub>、または616<sub>1</sub>～616<sub>m</sub>の共有バス602上の存在を検出すると、プライマリSGbusマスタデバイス612は、本明細書で説明するような、動的アドレス割振りプロシージャを実行し得る。

#### 【0070】

本明細書で開示するいくつかの態様によれば、SGbusは、I2Cプロトコル、CCIプロトコル、およびそれらの変形態、ならびに他のプロトコルを含む、複数のデータ転送プロトコルをサポートし得る。一例では、CCI拡張(CCIE)バスが、SGbus上でデータトランスポートを提供するために使用され得る。CCIE通信およびI2C通信は、共有バス602上で実行され得るので、第1の時間間隔において、データがCCIE符号化を使用して送信され得、他のデータがI2Cのシグナリング規約に従って異なる時間間隔において送信され得るようになる。SGbusは、CCIE送信がI2Cプロトコルに違反しないことを保証する物理レイヤプロトコルを採用する。

#### 【0071】

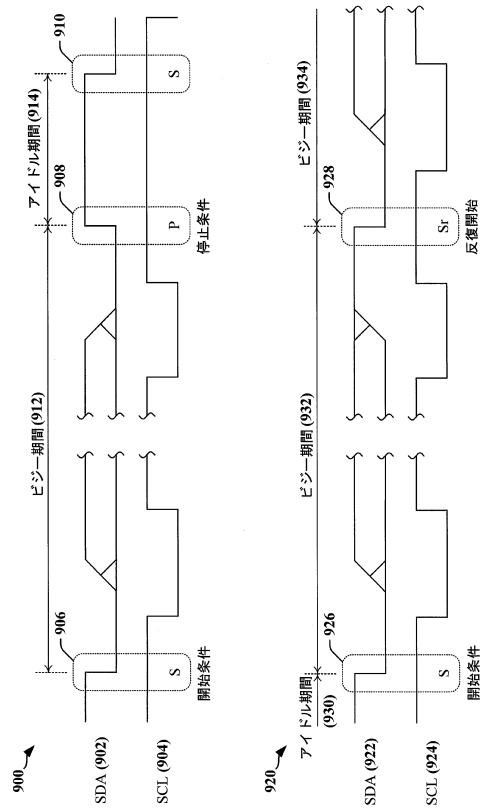

図9は、I2Cバス上の複数のデータ送信に関連付けられたタイミングを示すタイミング図900および920を含む。第1の基本的な例では、STOP条件908と連続するSTART条件910との間に経過する時間期間(アイドル期間914)が長い場合があり、それによって、従来のI2Cバスはこのアイドル期間914の間にアイドルになる。動作時には、I2Cバスマスタが第1のSTART条件906と後に続くデータとを送信するとき、ビジー期間912が開始する。ビジー期間912は、I2CバスマスタがSTOP条件908を送信するときに終了し、アイドル期間914が後に続く。アイドル期間914は、第2のSTART条件910の送信とともに終了する。

#### 【0072】

また、タイミング図920を参照すると、場合によっては、I2Cバス上の連続するデータ送信間のアイドル期間914は、STOP条件908ではなく反復START条件(Sr)928を送信することに

10

20

30

40

50

よって、数が減らされるかまたは除去され得る。反復START条件928は、先行するデータ送信を終了させ、同時に次のデータ送信の開始を示す。SDA信号線922上の状態遷移は、アイドル期間930後に生じるSTART条件926と反復START条件928とで同一である。詳細には、SDA信号線922は、SCL信号線924が高である間に、高から低に遷移する。データ送信間に反復START条件928が使用されるとき、第1のビジー期間932の直後に第2のビジー期間934が生じる。

#### 【 0 0 7 3 】

SGbusでは、データ転送セグメントは、任意のI2C、CClē、もしくは別の遷移符号化プロトコル、またはそれらの変形態を使用することができる。使用されるべきデータ転送プロトコルのタイプは、SGbusスレーブデバイス $614_1 \sim 614_n$ との通信の開始時に、SGbusマスタデバイス $612$ 、または $616_1 \sim 616_m$ によって示され得る。各SGbusスレーブデバイス $614_1 \sim 614_n$ のためのデータ転送プロトコルの選択は、実際には、SGbusマスタデバイス $612$ 、または $616_1 \sim 616_m$ によって変更されるまで、そのままである。場合によっては、プライマリSGbusマスタデバイス $612$ は、I2Cモードをデフォルトモードとして使用するために、I2CモードとCClēモードの両方で通信することができる任意のデバイスを構成し得る。10

#### 【 0 0 7 4 】

データ転送から出ることは、STOP条件820、908を共有バス602上で挿入することによって実施され得、その場合、共有バス602はBus-Free状態822に入り得る。共有バス602上のトランザクションにおいて送信されたいくつかのシンボルのシーケンスは、トランザクションにおける参加者ではない1つまたは複数のデバイス $604_1 \sim 604_k$ 、 $614_1 \sim 614_n$ 、 $616_1 \sim 616_m$ の検出論理によって、STOP条件820、908、または反復START条件928として識別され得るシグナリング状態を生成し得る。20

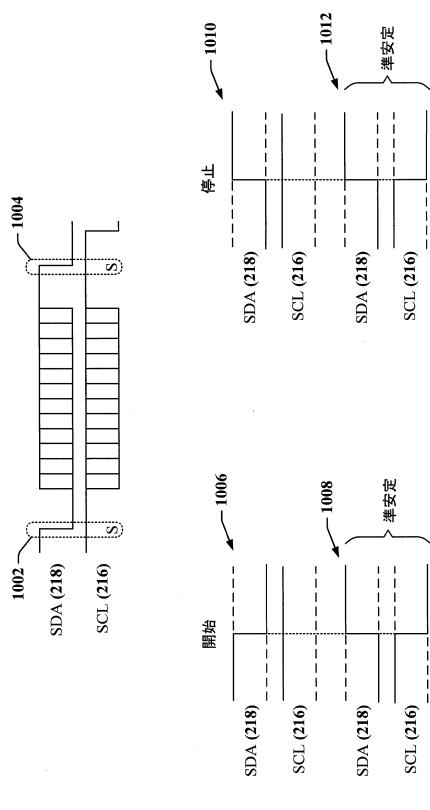

#### 【 0 0 7 5 】

図10は、通常のデータ交換中に、および/または、同期論理における図示された準安定性の問題のために生じ得る、意図しないSTART条件1008および意図しないSTOP条件1012の発生を示す。意図しないSTOP条件1012および意図しないSTART条件1008は、意図しないSTOP条件1012および意図しないSTART条件1008を引き起こし得るシンボルのシーケンスを識別するようにエンコーダを構成することによって、回避され得る。エンコーダは、意図しないおよび求められていないSTOP条件1012、ならびに/または意図しないSTART条件1008を生成することを回避するために、送信シンボルのストリームを修正し得る。一例では、コーディングプロトコルは、データ転送モードである間に意図しないSTOP条件1012を回避するために、任意の2進「01」シンボルの後、2進「00」ダミーシンボル挿入を与え得る。別の例では、コーディングプロトコルは、誤ったまたは意図しないSTART条件1008の後、レガシーI2Cデバイスにそのアドレスについて検査させ得る、意図しないSTART条件1008を回避するために、2進「11」シンボルのいずれかの発生後に2進「10」ダミーシンボル挿入を与え得る。レガシーI2Cデバイスは、アドレス一致を発見する場合、誤ったまたは意図しないSTART条件1008に応答し、それによって、CClēアクティブドライバに悪影響を及ぼすことがあることは諒解されよう。30

#### 【 0 0 7 6 】

CClēモードのデータ転送では、データ転送モードへのエントリポイント後に送られた最初のシンボルで開始する、共有バス602上で送信されたシンボルのカウントに基づいて、フレーム同期が実行され得る。SGbus動作では、反復START条件928がフレーム内の12シンボルの各シーケンスまたは20シンボルの各シーケンスの前に送られる必要はない。反復START条件928の不在によって、データスループットを高めることができる。40

#### 【 0 0 7 7 】

場合によっては、フレーム同期は、誤り検出のために使用される最後の3つの最下位ビット(LSB)「000」を検査することによって、さらに検証され得る。单一の誤りは、2進の復号された数の最後の3つの LSB を検査することによって、検出され得る。单一の誤りは、任意の12シンボルワード上のシンボル誤りに関係することがあり、その場合、どの2つの連続するシンボルも等しくない。シンボルは、2進数[SDA:SCL]として符号化され得、その50

場合、SDA218のシグナリング状態に対応するビットは、最上位ビット(MSB)位置にある。1つのシンボル誤りは、SDA218またはSCL216の一方または両方のサンプリングされたシグナリング状態における誤りの結果であり得る。

#### 【0078】

図11を参照すると、ならびに図3および図4に関して説明したように、送信機300のトランスコーダ302によって生成された3進数は、サークル402上およびその全体にわたる変位値として表され得る。一例では、時計回りの変位は3進値T=1として表され得、反時計回りの変位は3進値T=0として表され得、サークル402の全体にわたる変位(すなわち、2ステップ時計回りまたは反時計回り)は、3進値T=2として表され得る。

#### 【0079】

直接の結果として、サークル402上の隣接するシンボルのいずれかに等しいシンボルを生じるライン誤りは、新しいシンボルとは見なされず、誤りはワードレベルで識別され得る。しかしながら、単一のシンボル誤りは、2つの隣接する3進数が修正される結果となる。

#### 【0080】

本明細書で開示するいくつかの態様によれば、誤り訂正がSGbus通信のために提供され得る。データを転送するために、情報の2進列が、ベース3(3進)数としてコーディングされた、等しい数値に変換され得る。したがって、より少ない文字が、同じ情報のためにノード間で送信される必要がある。変換された3進数は多項式の和であり、ただし、因数は3の累乗であり、係数は[0,1,2]である。

#### 【0081】

#### 【数1】

$$\sum_{i=0}^{mbinary} B_i 2^i = \sum_{k=0}^{mternary} T_k 3^k$$

10

20

30

#### 【0082】

ただし、 $T_k$ =3進係数、[0,1,2]である。

#### 【0083】

1つのシンボル誤りは、2つの隣接する $T_k$ 値の改変を生じることがあり、最後の和は、次の公式によって改変され得る。

$$\pm a \times 3^n \pm b \times 3^{(n-1)} \quad (1)$$

ただし、

「n」=誤ったシンボルのランク、ならびに

「a」および「b」は、差分の係数である。

「a」および「b」係数は、以下を尊重する。

$$a \quad [0, \pm 1, \pm 2]$$

$$b \quad [0, \pm 1, \pm 2]$$

#### 【0084】

公式(1)を、次のように書くことができる。

$$(\pm 3a \pm b) \times 3^{(n-1)} \quad (2)$$

#### 【0085】

LSBの最後のビットが誤りによって不变のままで残されるために、公式(2)は、2の累乗の倍数でなければならない。整数倍ではない2の累乗の第1のランクは、1つのシンボル誤りが識別されるものとするように、いくつのLSBエンドビットが事前に知られていなければならないかを示す。因数 $3^{(n-1)}$ は、3の倍数であり、改変されない場合、LSBビットを変

40

50

化させることになる。

【0086】

関連する因数( $\pm 3a \pm b$ )の解析は、シンボル-3進コーディング図が円対称性を有するという観測に基づき得る。したがって、1点の考察がすべての4点をカバーする。たとえば、「2」が正しいシンボルである場合、いずれかの他の正しいシンボル状況では、それは、それぞれの位置をそれらの回転された値で置き換えるために十分である。以下のTable 1(表1)は、生じる可能性のある「a」係数を示し、Table 2(表2)は、生じる可能性のある「b」係数を示す。

【0087】

【表1】

10

| 正しい<br>シンボル | 過去の<br>シンボル | 正しい<br>3進 | 誤った<br>シンボル | 誤った<br>3進 | 誤った係数<br>「a」 |

|-------------|-------------|-----------|-------------|-----------|--------------|

| 2           | 1           | 1         | 3           | 2         | 1            |

|             |             |           | 0           | 0         | -1           |

|             | 0           | 2         | 3           | 0         | -2           |

|             |             |           | 1           | 1         | -1           |

|             | 3           | 0         | 1           | 2         | 2            |

|             |             |           | 0           | 1         | 1            |

Table 1

20

【0088】

【表2】

30

| 正しい<br>シンボル | 新しい<br>シンボル | 正しい<br>3進 | 誤った<br>シンボル | 誤った<br>3進 | 誤った係数<br>「b」 |

|-------------|-------------|-----------|-------------|-----------|--------------|

| 2           | 1           | 0         | 3           | 2         | 2            |

|             |             |           | 0           | 1         | 1            |

|             | 0           | 2         | 3           | 1         | -1           |

|             |             |           | 1           | 0         | -2           |

|             | 3           | 1         | 1           | 2         | 1            |

|             |             |           | 0           | 0         | -1           |

Table 2

【0089】

以下のTable 3(表3)は、生じる可能性のある「a」および「b」係数の組合せを示す。

40

【0090】

## 【表3】

| 正しい<br>シンボル | 誤った<br>シンボル | a  | a  | b  | b  |

|-------------|-------------|----|----|----|----|

| 2           | 3           | 1  | -2 | 2  | -1 |

|             | 1           | -1 | 2  | -2 | 1  |

|             | 0           | -1 | 1  | 1  | -1 |

Table 3

## 【0091】

可能性のある(a;b)ペアが、同じ可能性のある「誤ったシンボル」に関するものとして、同じ背景行に示されている。直接的な検査によって、それぞれ次のようになる組合せがあることが明らかである。

( $\pm 3a \pm b$ )=2、たとえば、(1;-1)および(-1;1)、

( $\pm 3a \pm b$ )=4、たとえば、(-2;2)および(2;-2)である。

( $\pm 3a \pm b$ )=8をもたらすことになるペアはなく、それは、(2;2)または(-2;-2)のみについて可能であったであろう。

## 【0092】

したがって、LSBエンドにおける任意の既知の3ビットは、任意の1つの単一のシンボル誤りを検出することができる。たとえば、「000」が使用され得るが、任意の他の3つの既知のビットが同じ役割を果たし得る。SDA218またはSCL216におけるいかなる誤りも、最後の3ビットによって検出され得る。

## 【0093】

本明細書で開示するいくつかの態様によれば、補足の誤り検査は、データ転送が進行中である間にSTOP条件908または反復START条件928の誤った識別を回避するために、必要に応じて、シンボル2進「01」から2進「00」への強制的な変換、または、シンボル2進「11」から2進「10」への強制的な変換に基づき得る。複数の12シンボルまたは20シンボルフレームのデータ転送全体の完了時に、STOP条件820、908を生成するために、4つのシンボルが挿入され得、そのうちの最後の2つが、2進「01」と後に続く2進「11」であり得る。

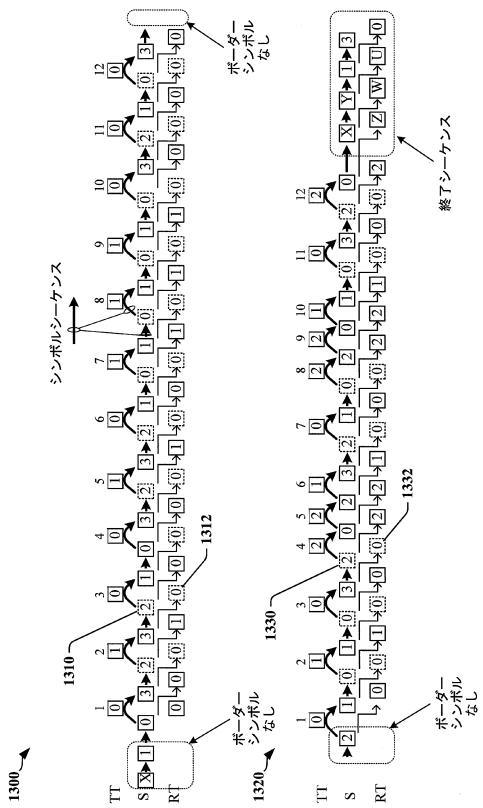

## 【0094】

図12および図13を参照すると、CCIEの前の実装形態と現在説明しているSGbusとの間のいくつかの違いが強調され得る。たとえば、2つのコーディングスタイルは、異なるシンボルを生成し得るが、復号された3進係数は、どちらの場合も同じである。別の例では、SGbusは、共有バス602上の意図しない(および求められていない)STOP条件908および反復START条件928(すなわち、2進「01」から2進「11」への遷移、または2進「11」から2進「10」への変換)を回避する。次いで、いくつかのデータストリームでは、SGbusは、シンボルを送信に追加し、それによってデータスループットを低減する。CCIEインターフェースは、12シンボルフレームごとに送信される境界シーケンスを有するが、SGbusは、フレームごとではなく、データ転送全体の終了において、ただ1つの終了シーケンスを有する。

## 【0095】

第1の例では、図12のタイミング図1200は、送信機300のトランスコード302によって3進-シンボル変換器304(図3参照)に与えられた、3進送信機(Tx)遷移数1202のシーケンスを示す。変換器は、シリアルバス230を介した受信機320への送信のために、シンボル1204のストリームを生成する。受信機320のシンボル-3進変換器324は、3進受信機(Rx)遷移数1206を生成する。Tx遷移数1202と、シンボル1204と、Rx遷移数1206との数の間に直接的な関係

がある。

#### 【 0 0 9 6 】

第2の例では、図12のタイミング図1220は、第1のSGbusデータフレームの送信を示し、それによって、送信機(Tx)3進数1222のシーケンスがトランスクーダ302によって3進-シンボル変換器304(図3参照)に与えられる。ここで、3進-シンボル変換器304は、挿入された追加のシンボル1230を含むシンボル1224のストリームを生成する。受信機320のシンボル-3進変換器324は、3進受信機(Rx)遷移数1226を生成する。シンボル-3進変換器324は、トランスクーダ322によって抽出される追加の数1232を含むRx遷移数1226を生成する。

#### 【 0 0 9 7 】

図13は、タイミング図1300および1320における第3の例および第4の例を含み、それによつて、第3のタイミング図1300は中間および/または最悪状況SGbusフレームに関係し、第4のタイミング図1320は最後のSGbusデータフレームに関係する。これらのタイミング図1300、1320では、3進-シンボル変換器304は、挿入された追加のシンボル1310および1330を含むシンボル1304、1324のストリームを生成する。受信機320のシンボル-3進変換器324は、3進Rx遷移数1306、1326を生成する。シンボル-3進変換器324は、トランスクーダ322によって抽出される追加の3進数1312および1332を含む、Rx遷移数1306、1326を生成する。

10

#### 【 0 0 9 8 】

異なるデータ転送モードが、バスクライアントの性質に基づいて使用するために選択されたモードとともに、共有シリアルバス上で使用するために利用可能であり得る。一例では、12シンボルフレームを使用する修正されたCCIEデータ転送モードが、I2Cデバイスがバス上に存在しないか、または参加中ではないときに利用可能であり、このモードではダミー変換の必要はない。別の例では、I2Cデバイスは共有バス602上に存在し、修正されたCCIEデータ転送モードが、12シンボルフレームおよびダミー変換とともに採用される。このデータ転送モードの特性は、I2Cクライアントの能力に依存し得る。

20

#### 【 0 0 9 9 】

別の例では、すべてのタイプのI2Cデバイスが、共有バス602に結合されると仮定され得、20シンボルの修正されたCCIEデータ転送モードが使用され得、反復START条件928が各20シンボルフレームの前に挿入される。このモードでは、ダミー変換が挿入されず、レガシーI2Cマスターが共有バス602に接続され得ない。また別の例では、レガシーI2Cデバイスのみが共有バス602上にあり、プライマリマスターデバイスはI2Cモードでバスを制御し、すべてのデータ転送は、バスの能力により、I2Cモードを使用する。

30

#### 【 0 1 0 0 】

本明細書で開示するように、SGbusは、2本のラインを使用して、マルチドロップおよびマルチマスター能力を提供し得る、高速シリアルインターフェースバスであり得る。従来のクロック信号は必要とされず、両方のラインを使用して送信されるシンボルは、データとともに符号化される。クロック情報は、連続するシンボルの各ペア間の2本の信号線のうちの少なくとも1つのシグナリング状態における遷移を保証することによって、シンボルのストリームにおいて埋め込まれる。SGbusプロトコルは、コマンドコードを使用し得る。帯域内割込み能力が提供され、低レイテンシの非同期ホットプラグがサポートされる。SGbusデバイスは、I2Cデバイスと同じバス上に共存し、同じ物理バスに接続され得るレガシーI2Cデバイスに適用される同じ制限に従うことができる。

40

#### 【 0 1 0 1 】

一態様では、SGbusは、コンテナアーキテクチャを使用して通信し、それによって、データ転送がバス管理要素間でカプセル化される。データは、バスに接続されたクライアントデバイスによって必要とされるかまたは選好されるように、複数のプロトコルのうちの1つを使用して転送され得る。一例では、データは、CCIEプロトコルを使用して転送され得、別の例では、データは、I2C対応プロトコルに従って転送され得る。データペイロードは、典型的には、CCIEプロトコルを使用して搬送されるが、対応するI2Cモードプロトコルにおいて、レガシーI2Cスレーブがアドレス指定され得、ペイロードがトランスポートされ得る。

50

**【 0 1 0 2 】**

SGbusプロトコルに関連付けられたバス管理機能は、バスアービトレーション、帯域内割込み、ホットプラグ、マルチマスタ、およびデータ転送モードに対する出入りを含む。

**【 0 1 0 3 】**

SGbusマスタデバイスは、動的アドレス割当て能力を有し得る。SGbusマスターは、帯域内割込みのために使用されるクロック生成器、バスに接続されたデバイスのアドレスおよび特性を保持するためのレジスタベースのメモリを含み得る。SGbusマスタデバイスは、I2Cデータ転送プロトコルまたはPCIeデータ転送プロトコルのいずれかを使用して通信し得る。

**【 0 1 0 4 】**

SGbusスレーブは、動的にアドレス指定可能であり得、それが接続されるバスのためのそのアドレスを要求かつ受信することが可能であり得る。SGbusスレーブデバイスは、少なくともPCIeプロトコルをサポートし、いくつかの例では、SGbusスレーブデバイスは、レガシーI2Cプロトコルを使用して通信することが可能であり得る。

**【 0 1 0 5 】**

SGbusは、送信中に最適化された(バイトごとの最小量のエネルギー)を提供することができる、PCIeスタイルのコーディングを採用するデータ転送プロトコルを含む、高速データ転送プロトコルをサポートする。帯域内IRQプロシージャがサポートされ得、最小レイテンシ制限(典型的には、 $10\mu s$ )が課され得る。ハートビートタイプの信号の必要がないので、効率の向上が得られ得る。非同期のホットプラグ能力が提供され得る。

10

**【 0 1 0 6 】**

場合によっては、システム設計の柔軟性の向上が、ローカルシステム設計レベルにおける構成によって達成される。動的アドレス指定によって、グローバルアドレス指定エンティティへの依存性が低減または除去される。動的アドレス指定は、ランダムアドレス生成器を採用し、それによって製造のオーバーヘッドを軽減する。

20

**【 0 1 0 7 】**

SGbusのいくつかの実装形態は、すべてのレガシーI2Cデバイスと十分に共存することができる。しかしながら、いくつかの低速および超低コストのレガシーI2Cデバイスの存在は、レガシーI2Cマスターの使用を妨げることがある。レガシーI2Cデバイスは、あらゆるPCIeコード化フレームについて、ライン上でそれらのアドレス一致を評価する必要がない。

30

**【 0 1 0 8 】**

場合によっては、拡張された能力および速度の向上を、1つまたは複数の補助ラインの追加によって得ることができ、より多数へのコーディングベースにおける変更が可能になる。たとえば、単一の追加のリンクライン、0~7シンボルが転送され得、相対的ジャンプが0から6までであり、したがって、ベース7におけるコーディングが可能になる。

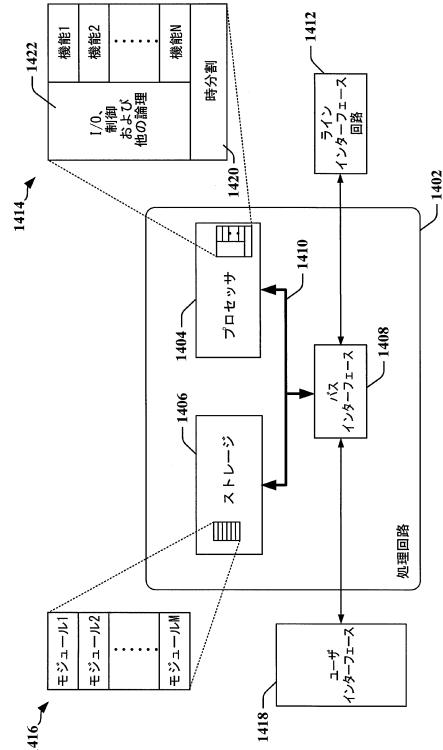

**【 0 1 0 9 】**

処理回路およびそれらの構成のいくつかの態様の例

図14は、本明細書で開示する1つまたは複数の機能を実行するように構成され得る処理回路1402を採用する装置のためのハードウェア実装形態の簡略化された例を示す概念図1400である。本開示の様々な態様によれば、本明細書で開示するような要素、または要素の任意の部分、または要素の任意の組合せは、処理回路1402を使用して実装され得る。処理回路1402は、ハードウェアモジュールとソフトウェアモジュールの何らかの組合せによって制御される1つまたは複数のプロセッサ1404を含み得る。プロセッサ1404の例は、マイクロプロセッサ、マイクロコントローラ、デジタル信号プロセッサ(DSP)、フィールドプログラマブルゲートアレイ(FPGA)、プログラマブル論理デバイス(PLD)、状態機械、シーケンサ、ゲート論理、個別ハードウェア回路、および本開示全体にわたって説明する様々な機能を実行するように構成された他の適切なハードウェアを含む。1つまたは複数のプロセッサ1404は、特定の機能を実行し、ソフトウェアモジュール1416のうちの1つによって構成され、増強され、または制御され得る専用プロセッサを含み得る。1つまたは複数のプロセッサ1404は、初期化中にロードされたソフトウェアモジュール1416の組合せを介

40

50

して構成され、動作中に1つまたは複数のソフトウェアモジュール1416のローディングまたはアンローディングによってさらに構成される場合がある。

#### 【0110】

図示の例では、処理回路1402は、バス1410によって概略的に表されるバスアーキテクチャを用いて実装され得る。バス1410は、処理回路1402の特定の適用例および全体的な設計制約に応じて、任意の数の相互接続バスおよびブリッジを含み得る。バス1410は、1つまたは複数のプロセッサ1404およびストレージ1406を含む様々な回路を互いにリンクさせる。ストレージ1406は、メモリデバイスおよび大容量ストレージデバイスを含んでもよく、本明細書ではコンピュータ可読媒体および/またはプロセッサ可読媒体と呼ばれる場合がある。バス1410は、タイミングソース、タイマー、周辺機器、電圧調整器、および電力管理回路などの様々な他の回路をリンクさせることもできる。バスインターフェース1408は、バス1410と1つまたは複数のトランシーバ1412との間のインターフェースを提供してもよい。トランシーバ1412は、処理回路によってサポートされるネットワーキング技術ごとに提供され得る。場合によっては、複数のネットワーキング技術が、トランシーバ1412の中に見出される回路または処理モジュールの一部または全部を共有してもよい。各トランシーバ1412は、伝送媒体を介して様々な他の装置と通信するための手段を提供する。装置の性質に応じて、ユーザインターフェース1418(たとえば、キーパッド、ディスプレイ、スピーカ、マイクロフォン、ジョイスティック)が設けられてもよく、直接またはバスインターフェース1408を通じてバス1410に通信可能に結合されてもよい。10

#### 【0111】

プロセッサ1404は、バス1410を管理すること、およびストレージ1406を含む場合があるコンピュータ可読媒体に記憶されたソフトウェアの実行を含む場合がある一般的な処理を担当してもよい。この点で、プロセッサ1404を含む処理回路1402は、本明細書で開示する方法、機能および技法のうちのいずれかを実装するために使用され得る。ストレージ1406は、ソフトウェアを実行するとき、プロセッサ1404によって操作されるデータを記憶するために使用されてよく、ソフトウェアは、本明細書で開示する方法のうちの任意の1つを実施するように構成されてよい。20

#### 【0112】

処理回路1402における1つまたは複数のプロセッサ1404は、ソフトウェアを実行することができる。ソフトウェアは、ソフトウェア、ファームウェア、ミドルウェア、マイクロコード、ハードウェア記述言語と呼ばれるか、または他の名称で呼ばれるかどうかにかかわらず、命令、命令セット、コード、コードセグメント、プログラムコード、プログラム、サブプログラム、ソフトウェアモジュール、アプリケーション、ソフトウェアアプリケーション、ソフトウェアパッケージ、ルーチン、サブルーチン、オブジェクト、実行可能ファイル、実行スレッド、プロシージャ、関数、アルゴリズムなどを意味するように広く解釈されるべきである。ソフトウェアは、コンピュータ可読の形でストレージ1406中または外部コンピュータ可読媒体中に存在することができる。外部コンピュータ可読媒体および/またはストレージ1406は、非一時的コンピュータ可読媒体を含んでもよい。非一時的コンピュータ可読媒体は、例として、磁気ストレージデバイス(たとえば、ハードディスク、フロッピーディスク、磁気ストリップ)、光ディスク(たとえば、コンパクトディスク(CD)またはデジタル多用途ディスク(DVD))、スマートカード、フラッシュメモリデバイス(たとえば、「フラッシュドライブ」、カード、スティック、またはキードライブ)、ランダムアクセスメモリ(RAM)、読み取り専用メモリ(ROM)、プログラマブルROM(PROM)、消去可能PROM(EPROM)、電気的消去可能PROM(EEPROM)、レジスタ、リムーバブルディスク、ならびに、コンピュータがアクセスし読み取ることができるソフトウェアおよび/または命令を記憶するための任意の他の適切な媒体を含む。コンピュータ可読媒体および/またはストレージ1406は、例として、搬送波、伝送路、ならびに、コンピュータがアクセスし読み取ることができるソフトウェアおよび/または命令を送信するための任意の他の適切な媒体も含み得る。コンピュータ可読媒体および/またはストレージ1406は、処理回路1402中に存在するか、プロセッサ1404中に存在するか、処理回路1402の外部に存在するか、304050

または処理回路1402を含む複数のエンティティにわたって分散され得る。コンピュータ可読媒体および/またはストレージ1406は、コンピュータプログラム製品において具現化され得る。例として、コンピュータプログラム製品は、パッケージング材料中のコンピュータ可読媒体を含み得る。当業者は、特定の適用例および全体的なシステムに課された設計制約全体に応じて、本開示全体にわたって提示された記載の機能を最もよく実装する方法を認識されよう。

#### 【0113】

ストレージ1406は、本明細書でソフトウェアモジュール1416と呼ばれる場合がある、ロード可能なコードセグメント、モジュール、アプリケーション、プログラムなどにおいて維持かつ/または編成されるソフトウェアを維持することができる。ソフトウェアモジュール1416の各々は、処理回路1402にインストールまたはロードされ、1つまたは複数のプロセッサ1404によって実行されると、1つまたは複数のプロセッサ1404の動作を制御するランタイムイメージ1414に寄与する命令およびデータを含み得る。実行されるとき、いくつかの命令は、処理回路1402に、本明細書で説明するいくつかの方法、アルゴリズムおよびプロセスに従って機能を実行させてよい。

10

#### 【0114】

ソフトウェアモジュール1416のうちのいくつかは、処理回路1402の初期化中にロードされてもよく、これらのソフトウェアモジュール1416は、本明細書で開示する様々な機能の実行を可能にするように処理回路1402を構成することができる。たとえば、いくつかのソフトウェアモジュール1416は、プロセッサ1404の内部デバイスおよび/または論理回路1422を構成することができ、トランシーバ1412、バスインターフェース1408、ユーザインターフェース1418、タイマー、数学的コプロセッサなどの外部デバイスへのアクセスを管理することができる。ソフトウェアモジュール1416は、割込みハンドラおよびデバイスドライバと対話し、処理回路1402によって提供される様々なリソースへのアクセスを制御する、制御プログラムおよび/またはオペレーティングシステムを含み得る。リソースには、メモリ、処理時間、トランシーバ1412へのアクセス、ユーザインターフェース1418などが含まれ得る。

20

#### 【0115】

処理回路1402の1つまたは複数のプロセッサ1404は、多機能とすることができる、それにより、ソフトウェアモジュール1416のうちのいくつかがロードされ、異なる機能または同じ機能の異なるインスタンスを実行するように構成される。1つまたは複数のプロセッサ1404は、さらに、たとえば、ユーザインターフェース1418、トランシーバ1412、およびデバイスドライバからの入力に応答して開始されるバックグラウンドタスクを管理するように適応され得る。複数の機能の実行をサポートするために、1つまたは複数のプロセッサ1404は、マルチタスク環境を実現するように構成される場合があり、それにより、複数の機能の各々が、必要または要望に応じて、1つまたは複数のプロセッサ1404によってサービスされるタスクのセットとして実装される。一例では、マルチタスク環境は、異なるタスク間でプロセッサ1404の制御を渡す時分割プログラム1420を使用して実装される場合があり、それにより、各タスクは、任意の未処理動作の完了後、および/または割込みなどの入力に応答して、時分割プログラム1420に1つまたは複数のプロセッサ1404の制御を戻す。タスクが1つまたは複数のプロセッサ1404の制御を有するとき、処理回路は、事実上、制御するタスクに関連付けられた機能によって対処される目的に特化される。時分割プログラム1420は、オペレーティングシステム、ラウンドロビンベースで制御を移すメインループ、機能の優先度付けに従って1つもしくは複数のプロセッサ1404の制御を割り振る機能、および/または、1つもしくは複数のプロセッサ1404の制御を処理機能に提供することによって外部イベントに応答する割込み駆動のメインループを含み得る。

30

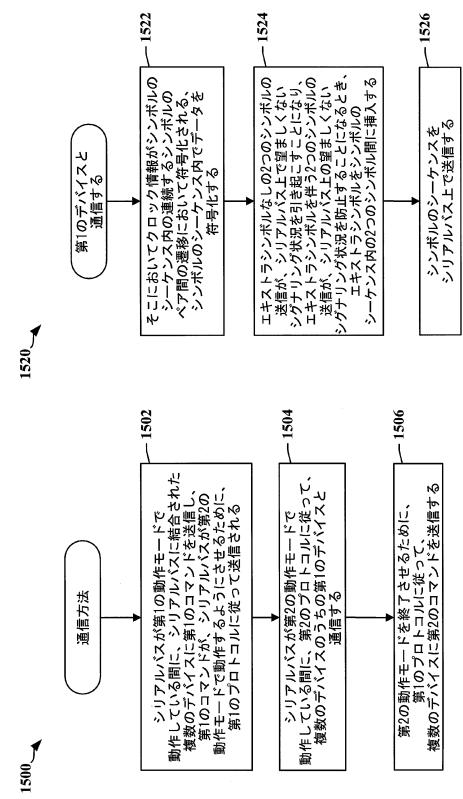

#### 【0116】

図15は、SGbusシリアルインターフェース上のデータ通信のための方法のいくつかの態様を示す、フローチャート1500、1520を含む。この方法の様々なステップは、バスマスターデバイス220、図2に示すバススレーブデバイス202、図3に示すデバイス300もしくは320、

40

50

および/または本明細書で説明する他のデバイスの何らかの組合せを含むデバイスによつて実行され得る。

#### 【0117】

ブロック1502で、マスタデバイスは、シリアルバスが第1の動作モードで動作している間に、シリアルバスに結合された複数のデバイスに第1のコマンドを送信し得る。第1のコマンドは、シリアルバスが第2の動作モードで動作するようにさせるために、第1のプロトコルに従って送信され得る。

#### 【0118】

ブロック1504で、マスタデバイスは、シリアルバスが第2の動作モードで動作している間に、第2のプロトコルに従って、複数のデバイスのうちの第1のデバイスと通信し得る(10 フローチャート1520参照)。

#### 【0119】

ブロック1506で、マスタデバイスは、第2の動作モードを終了させるために、第1のプロトコルに従って、複数のデバイスに第2のコマンドを送信し得る。

#### 【0120】

場合によっては、第1のデバイスと通信することは、2つのシンボルを送信することが、2つのシンボルがシリアルバスを介して送信される場合、50ナノ秒よりも大きい持続期間を有するパルスをシリアルバスの第1のライン上で発生させることになると決定すること、および、エキストラシンボルをシンボルのシーケンスに挿入することであって、エキストラシンボルが第1のライン上のパルスを終了させるために選択されることを含む。20

#### 【0121】

第2のデバイスは、エキストラシンボルが2つのシンボル間に挿入されているときにシリアルバスが第2の動作モードで動作している間は、シリアルバス上の通信を無視し得る。

#### 【0122】

一例では、シンボルのシーケンスの各シンボルは複数のビットを有し、各ビットは、1つのシンボル間隔に対するシリアルバスの1本のラインのシグナリング状態を定義する。シンボルのシーケンス内の連続するシンボルの各ペアは、2つの異なるシンボルを含む。シリアルバスの少なくとも1本のラインのシグナリング状態は、連続するシンボルの各ペアにおける第2のシンボルが送信されるとき、変化し得る。

#### 【0123】

別の例では、シリアルバスが第1の動作モードで動作している間に、第3のコマンドが複数のデバイスに送信され得る。第3のコマンドは、シリアルバスが第3の動作モードで動作するようにさせるために、第1のプロトコルに従って送信され得る。マスタデバイスは、シリアルバスが第3の動作モードで動作している間に、第3のプロトコルに従って、複数のデバイスのうちの第3のデバイスと通信し得る。マスタデバイスは、第2の動作モードを終了させるために、第1のプロトコルに従って、複数のデバイスに第4のコマンドを送信し得る。30

#### 【0124】

第2のフローチャート1520は、第1のデバイスと通信することに関する。ブロック1522で、マスタデバイスは、クロック情報がシンボルのシーケンス内の連続するシンボルのペア間の遷移において符号化される、シンボルのシーケンス内でデータを符号化し得る。40

#### 【0125】

ブロック1524で、エキストラシンボルなしの2つのシンボルの送信が、シリアルバス上で望ましくないシグナリング状況を引き起こすことになり、エキストラシンボルを伴う2つのシンボルの送信が、シリアルバス上の望ましくないシグナリング状況を防止することになるとき、マスタデバイスは、エキストラシンボルをシンボルのシーケンス内の2つのシンボル間に挿入し得る。

#### 【0126】

ブロック1526で、マスタデバイスは、シンボルのシーケンスをシリアルバス上で送信し得る。50

**【 0 1 2 7 】**

一例では、望ましくないシグナリング状況は、シリアルバスの2本のライン上の遷移の相対的タイミングに関係する。

**【 0 1 2 8 】**

別の例では、望ましくないシグナリング状況は、シリアルバスの1本のライン上で送信されるパルスの持続期間に関係する。

**【 0 1 2 9 】**

別の例では、望ましくないシグナリング状況は、第2のプロトコル以外のプロトコルによって定義された同期またはSTART条件に関係する。

**【 0 1 3 0 】**

第1のプロトコルは、I2Cプロトコルに適合するか、またはそれと互換性があり得、その場合、望ましくないシグナリング状況は、I2Cプロトコルによって定義されたSTART条件に関係する。

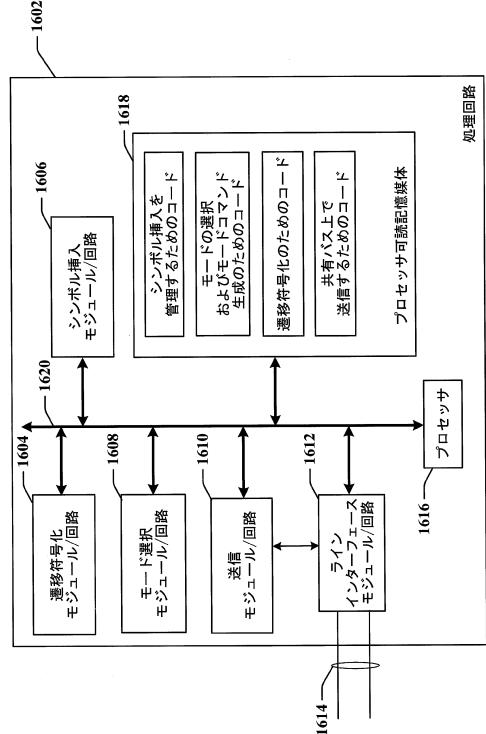

**【 0 1 3 1 】**

図16は、処理回路1602を採用する装置1600のためのハードウェア実装形態の簡略化された例を示す図である。処理回路は通常、マイクロプロセッサ、マイクロコントローラ、デジタル信号プロセッサ、シーケンサおよび状態機械のうちの1つまたは複数を含み得るプロセッサ1616を有する。処理回路1602は、バス1620によって概略的に表されるバスアーキテクチャを用いて実装され得る。バス1620は、処理回路1602の特定の適用例および全体的な設計制約に応じて、任意の数の相互接続バスおよびブリッジを含み得る。バス1620は、プロセッサ1616、様々なモジュールまたは回路1604、1606、1608、1610、コネクタまたは線1614を介して通信するように構成可能なラインインターフェース回路1612、およびコンピュータ可読記憶媒体1618によって表される、1つまたは複数のプロセッサおよび/またはハードウェアモジュールを含む様々な回路を互いにリンクさせる。バス1620は、タイミングソース、周辺装置、電圧調整器、および電力管理回路などの様々な他の回路をリンクさせることもできるが、これらの回路は当技術分野でよく知られており、したがってこれ以上は説明しない。

**【 0 1 3 2 】**

プロセッサ1616は、コンピュータ可読記憶媒体1618上に記憶されたソフトウェアの実行を含む全体的な処理を担当する。ソフトウェアは、プロセッサ1616によって実行されると、処理回路1602に、任意の特定の装置について上記で説明した様々な機能を実行させる。コンピュータ可読記憶媒体1618はまた、コネクタまたは線1614を介して送信されたシンボルから復号されるデータを含む、ソフトウェアを実行するときにプロセッサ1616によって操作されるデータを記憶するためにも使用され得る。処理回路1602は、モジュール1604、1606、1608、1610のうちの少なくとも1つをさらに含む。モジュール1604、1606、1608、1610は、プロセッサ1616内で実行されている、コンピュータ可読記憶媒体1618内に存在する/記憶されるソフトウェアモジュール、プロセッサ1616に結合された1つもしくは複数のハードウェアモジュール、またはそれらの何らかの組合せであり得る。モジュール1604、1606、1608、および/または1610は、マイクロコントローラ命令、状態機械構成パラメータ、またはそれらの何らかの組合せを含み得る。

**【 0 1 3 3 】**

1つの構成では、ワイヤレス通信のための装置1600は、シリアルバスが第1の動作モードで動作している間に、シリアルバスに結合された複数のデバイス(たとえば、コネクタまたは線1614)に第1のコマンドを送信することであって、その場合、第1のコマンドが、シリアルバスが第2の動作モードで動作するようにさせるために、第1のプロトコルに従って送信されることを行うように構成される、モジュールおよび/または回路1608、1610を含む。装置1600はまた、第2のプロトコルに従って、シンボルのシーケンス内でデータを符号化することであって、クロック情報がシンボルのシーケンス内の連続するシンボルのペア間の遷移において符号化されることを行うように構成される、モジュールおよび/または回路1604を含み得る。装置1600はまた、エキストラシンボルなしの2つのシンボルの送

10

20

30

40

50

信が、シリアルバス上で望ましくないシグナリング状況を引き起こすことになり、エキストラシンボルを伴う2つのシンボルの送信が、シリアルバス上の望ましくないシグナリング状況を防止することになるとき、エキストラシンボルをシンボルのシーケンス内の2つのシンボル間に挿入するように構成されるモジュールおよび/または回路1606を含み得る。装置1600はまた、第2のプロトコルに従って、シンボルのシーケンスをシリアルバス上で送信するように構成されるモジュールおよび/または回路1608、1610、1612を含み得る。装置1600はまた、第2の動作モードを終了させるために、第1のプロトコルに従って、複数のデバイスに第2のコマンドを送信するために構成されるモジュールおよび/または回路1608、1610を含み得る。

## 【0134】

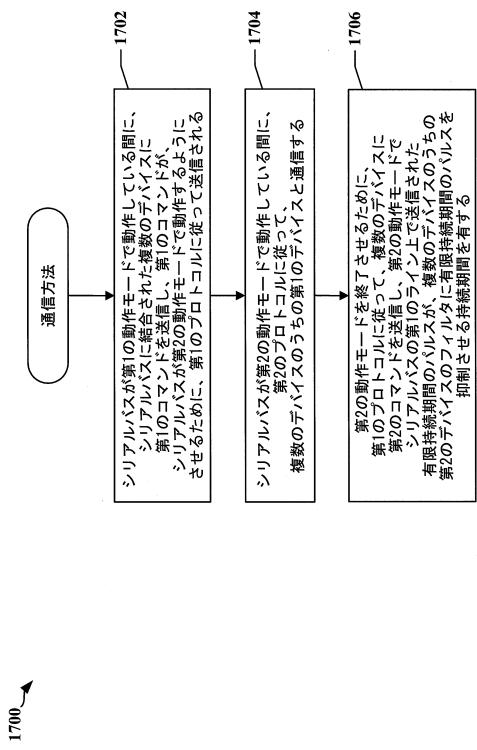

10

図17は、SGbusシリアルインターフェース上のデータ通信のための方法を示すフローチャート1700である。この方法の様々なステップは、バスマスタデバイス220、図2に示すバススレーブデバイス202、図3に示すデバイス300もしくは320、および/または本明細書で説明する他のデバイスの何らかの組合せを含むデバイスによって実行され得る。

## 【0135】

ブロック1702で、マスタデバイスは、シリアルバスが第1の動作モードで動作している間に、シリアルバスに結合された複数のデバイスに第1のコマンドを送信し得る。第1のコマンドは、第1のプロトコルに従って送信され得る。第1のコマンドは、シリアルバスが第2の動作モードで動作するようにされ得る。

## 【0136】

20

ブロック1704で、マスタデバイスは、シリアルバスが第2の動作モードで動作している間に、第2のプロトコルに従って、複数のデバイスのうちの第1のデバイスと通信し得る。

## 【0137】

ブロック1706で、マスタデバイスは、第2の動作モードを終了させるために、第1のプロトコルに従って、複数のデバイスに第2のコマンドを送信し得る。

## 【0138】

第2の動作モードでシリアルバスの第1のライン上で送信された有限持続期間のパルスは、複数のデバイスのうちの第2のデバイスのフィルタに有限持続期間のパルスを抑制させる持続期間を有し得る。第2のデバイスは、有限持続期間のパルスが抑制されているときにシリアルバスが第2の動作モードで動作している間は、シリアルバス上の通信を無視し得る。

30

## 【0139】

一例では、第1の動作モードは、I2C通信モードである。有限持続期間のパルスは、50ナノ秒よりも大きくなき持続期間を有し得る。有限持続期間のパルスは、シリアルバスのSCL線上で送信され得る。

## 【0140】

40

別の例では、第2のプロトコルに従って通信することは、マルチビットシンボルのシーケンス内でデータを符号化することであって、各マルチビットシンボルの各ビットが、1つのシンボル間隔に対するシリアルバスの1本のラインのシグナリング状態を定義することを含む。マスタデバイスは、シンボルのシーケンス内の2つ以上の連続するシンボルを送信することが、2つ以上の連続するシンボルがシリアルバスを介して送信される場合、50ナノ秒よりも大きい持続期間を有するパルスを第1のライン上で発生させることになると決定し得る。したがって、マスタデバイスは、エキストラシンボルをシンボルのシーケンスに挿入することができ、エキストラシンボルは、50ナノ秒よりも大きい持続期間を有するパルスの発生を防止するために選択される。各マルチビットシンボルの1ビットは、有限持続期間のパルスが対応するシンボル間隔において第1のライン上で送信されるか否かを定義し得る。

## 【0141】

別の例では、第2の動作モードは、CCIE通信モードである。

## 【0142】

50

別の例では、第1のデバイスはセンサーを含み、第2の動作モードは、複数の異なるセンサーを結合するのに適したプロトコルをサポートする。

#### 【 0 1 4 3 】

別の例では、マスタデバイスは、シリアルバスが第1の動作モードで動作している間に、複数のデバイスに第3のコマンドを送信し得る。第3のコマンドは、シリアルバスが第3の動作モードで動作するようにさせるために、第1のプロトコルに従って送信され得る。次いで、マスタデバイスは、シリアルバスが第3の動作モードで動作している間に、複数のデバイスのうちの第3のデバイスと、第3のプロトコルに従って通信し得る。マスタデバイスは、その後、第2の動作モードを終了させるために、第1のプロトコルに従って、複数のデバイスに第4のコマンドを送信し得る。第2の動作モードで第1のライン上で送信された有限持続期間のパルスは、複数のデバイスのうちの第2のデバイスのフィルタに有限持続期間のパルスを抑制させる持続期間を有する。10

#### 【 0 1 4 4 】

別の例では、第1のマスタデバイスは、クロック情報がシンボルのシーケンス内の連続するシンボルのペア間の遷移において符号化される、シンボルのシーケンス内でデータを符号化すること、エキストラシンボルなしの2つのシンボルの送信が、シリアルバス上で望ましくないシグナリング状況を引き起こすことになり、エキストラシンボルを伴う2つのシンボルの送信が、シリアルバス上の望ましくないシグナリング状況を防止することになるとき、エキストラシンボルをシンボルのシーケンス内の2つのシンボル間に挿入すること、および、シンボルのシーケンスをシリアルバス上で送信することによって、第1のデバイスと通信し得る。20

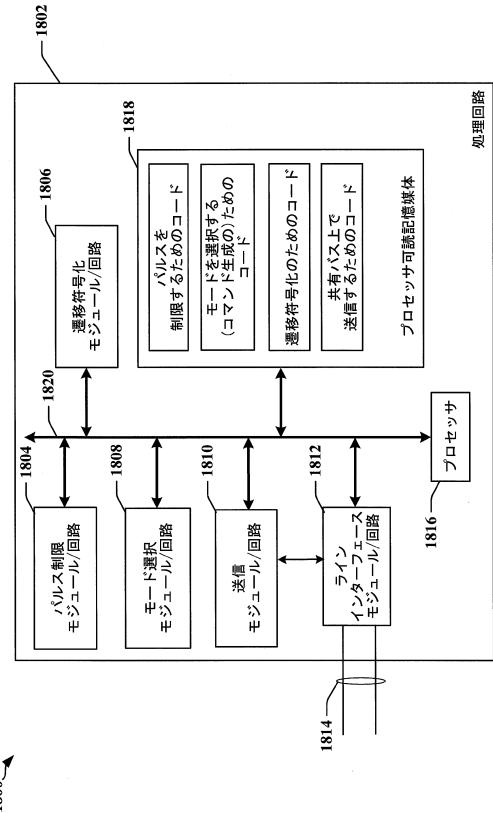

#### 【 0 1 4 5 】

図18は、処理回路1802を採用する装置1800のためのハードウェア実装形態の簡略化された例を示す図である。処理回路は通常、マイクロプロセッサ、マイクロコントローラ、デジタル信号プロセッサ、シーケンサおよび状態機械のうちの1つまたは複数を含み得るプロセッサ1816を有する。処理回路1802は、バス1820によって概略的に表されるバスアーキテクチャを用いて実装され得る。バス1820は、処理回路1802の特定の適用例および全体的な設計制約に応じて、任意の数の相互接続バスおよびブリッジを含み得る。バス1820は、プロセッサ1816、様々なモジュールまたは回路1804、1806、1808、1810、コネクタまたは線1814を介して通信するように構成可能なラインインターフェース回路1812、およびコンピュータ可読記憶媒体1818によって表される、1つまたは複数のプロセッサおよび/またはハードウェアモジュールを含む様々な回路を互いにリンクさせる。バス1820は、タイミングソース、周辺装置、電圧調整器、および電力管理回路などの様々な他の回路をリンクさせることもできるが、これらの回路は当技術分野でよく知られており、したがってこれ以上は説明しない。30

#### 【 0 1 4 6 】

プロセッサ1816は、コンピュータ可読記憶媒体1818上に記憶されたソフトウェアの実行を含む全体的な処理を担当する。ソフトウェアは、プロセッサ1816によって実行されると、処理回路1802に、任意の特定の装置について上記で説明した様々な機能を実行させる。コンピュータ可読記憶媒体1818はまた、コネクタ1814を介して送信されたシンボルから復号されるデータを含む、ソフトウェアを実行するときにプロセッサ1816によって操作されるデータを記憶するためにも使用され得る。処理回路1802は、モジュール1804、1806、1808、1810のうちの少なくとも1つをさらに含む。モジュール1804、1806、1808、1810は、プロセッサ1816内で実行されている、コンピュータ可読記憶媒体1818内に存在する/記憶されるソフトウェアモジュール、プロセッサ1816に結合された1つもしくは複数のハードウェアモジュール、またはそれらの何らかの組合せであり得る。モジュール1804、1806、1808、および/または1810は、マイクロコントローラ命令、状態機械構成パラメータ、またはそれらの何らかの組合せを含み得る。40

#### 【 0 1 4 7 】

1つの構成では、ワイヤレス通信のための装置1800は、シリアルバスが第1の動作モード50

で動作している間に、シリアルバスに結合された複数のデバイス(たとえば、コネクタまたは線1814)に第1のコマンドを送信することであって、その場合、第1のコマンドが、シリアルバスが第2の動作モードで動作するようにさせるために、第1のプロトコルに従って送信されることを行うように構成される、モジュールおよび/または回路1808、1810を含む。装置1800はまた、シリアルバスが第2の動作モードで動作している間に、複数のデバイスのうちの第1のデバイスと、第2のプロトコルに従って通信するために構成されるモジュールおよび/または回路1806、1810と、第2の動作モードを終了させるために、第1のプロトコルに従って、複数のデバイスに第2のコマンドを送信するために構成されるモジュールおよび/または回路1808、1810と、複数のデバイスのうちの第2のデバイスのフィルタに有限持続期間のパルスを抑制させる持続期間を有する、第2の動作モードでシリアルバスの第1のライン上で送信するための有限持続期間のパルスを提供するように構成されるモジュールおよび/または回路1804、1810とを含み得る。

#### 【 0 1 4 8 】

開示したプロセスにおけるステップの特定の順序または階層は、例示的な手法の実例であることを理解されたい。設計上の選好に基づいて、プロセスにおけるステップの特定の順序または階層は再構成されてもよいことを理解されたい。さらに、いくつかのステップは、組み合わせられるか、または省略される場合がある。添付の方法クレームは、見本の順序における様々なステップの要素を提示しており、提示された特定の順序または階層に限定されることを意味するものではない。

#### 【 0 1 4 9 】

上記の説明は、本明細書で説明する様々な態様を当業者が実践できるようにするために提供される。これらの態様に対する様々な変更形態は、当業者に容易に明らかになり、本明細書において規定される一般原理は、他の態様に適用される場合がある。したがって、特許請求の範囲は本明細書に示された態様に限定されるものではなく、文言通りの特許請求の範囲に整合するすべての範囲を与えられるべきであり、単数形の要素への言及は、そのように明記されていない限り、「唯一無二の」を意味するものではなく、「1つまたは複数の」を意味するものである。別段に明記されていない限り、「いくつかの」という用語は1つまたは複数の、を指す。当業者に知られているまたは後で当業者に知られることになる、本開示全体にわたって説明する様々な態様の要素の構造的および機能的なすべての均等物は、参照により本明細書に明確に組み込まれ、特許請求の範囲によって包含されることが意図される。その上、本明細書で開示するものは、そのような開示が特許請求の範囲において明示的に記載されているかどうかにかかわらず、公に供することは意図されていない。いかなるクレーム要素も、要素が「ための手段」という語句を使用して明確に列挙されていない限り、ミーンズプラスファンクションとして解釈されるべきではない。

#### 【 符号の説明 】

#### 【 0 1 5 0 】

- 100、200、1600、1800 装置

- 102、1402、1602、1802 処理回路

- 106 通信トランシーバ

- 108 特定用途向けIC(ASIC)

- 110 アプリケーションプログラミングインターフェース(API)

- 112 メモリデバイス

- 114 ローカルデータベース

- 122 アンテナ

- 124 ディスプレイ

- 126 キーパッド

- 128 ボタン

- 202 デバイス、バススレーブデバイス

- 204 センサー機能

- 206 構成レジスタまたは他のストレージ

10

20

30

40

50

|                                                                                 |    |

|---------------------------------------------------------------------------------|----|

| 208 クロック生成回路                                                                    |    |

| 210、1412 トランシーバ                                                                 |    |

| 210a 受信機                                                                        |    |

| 210b 共通回路                                                                       |    |

| 210c 送信機                                                                        |    |

| 212 制御論理                                                                        |    |

| 214a、214b ラインドライバ/受信機                                                           |    |

| 216 SCL、線                                                                       |    |

| 218 SDA、線                                                                       |    |

| 220 デバイス、バスマスタデバイス                                                              | 10 |

| 222a~222n デバイス                                                                  |    |

| 230 シリアルバス、バス                                                                   |    |

| 300 送信機、デバイス                                                                    |    |

| 302 トランスコーダ                                                                     |    |

| 304 3進-シンボル変換器                                                                  |    |

| 306 ラインドライバ                                                                     |    |

| 308 オープンドレイン出力トランジスタ                                                            |    |

| 310 入力データ                                                                       |    |

| 312、332 3進数                                                                     |    |

| 314 2ビットシンボル、連続するシンボル、データシンボル、シンボル                                              | 20 |

| 320 受信機、デバイス                                                                    |    |

| 322 回路、トランスコーダ                                                                  |    |

| 324 回路、シンボル-3進変換器                                                               |    |

| 326、1812 ラインインターフェース回路                                                          |    |

| 328 クロックおよびデータ回復(CDR)回路                                                         |    |

| 330 出力データ要素                                                                     |    |

| 334 2ビットシンボル、シンボル                                                               |    |

| 336 未加工の2ビットシンボル、未加工のシンボル                                                       |    |

| 338 受信クロック                                                                      |    |

| 400 符号化方式、SGbus符号化方式                                                            | 30 |

| 402 シンボル順序付けサークル、サークル                                                           |    |

| 404a~404d ロケーション                                                                |    |

| 406 回転の方向                                                                       |    |

| 420 テーブル                                                                        |    |

| 422 第1のシンボル(前のシンボルPs)、Psシンボル、直前のシンボル、前のシンボル<br>、前に生成されたシンボル、前に受信されたシンボル         |    |

| 424 第2のシンボル(現在のシンボルCs)、有効な現在のシンボル、現在のシンボル、<br>現在受信されたシンボル                       |    |

| 426 遷移数(T)                                                                      |    |

| 502 7ビットのスレーブID、スレーブID、I2CスレーブID                                                | 40 |

| 506、926 START条件                                                                 |    |

| 512 読取り/書き込みビット                                                                 |    |

| 514 クロック信号パルス                                                                   |    |

| 516、820 STOP条件                                                                  |    |

| 602 共有バス、バス                                                                     |    |

| 604 <sub>1</sub> ~604 <sub>k</sub> I2Cデバイス、レガシーI2Cスレーブデバイス、レガシーI2Cデバイス、<br>デバイス |    |

| 606 I2Cデバイス、レガシーI2Cマスタデバイス、レガシーI2Cデバイス、レガシーI2<br>Cマスター                          |    |

| 612 SGbusデバイス、SGbusマスタデバイス、プライマリSGbusマスタデバイス                                    | 50 |

|                                         |                                                                     |    |

|-----------------------------------------|---------------------------------------------------------------------|----|

| 614 <sub>1</sub> ~ 614 <sub>n</sub>     | SGbusデバイス、SGbusスレーブデバイス、デバイス                                        |    |

| 616 <sub>1</sub> ~ 616 <sub>m</sub>     | SGbusデバイス、SGbusセカンダリマスタデバイス、セカンダリSGbusマ<br>スタデバイス、デバイス、SGbusマスタデバイス |    |

| 702                                     | 動作状態、スタートアップ状態                                                      |    |

| 704                                     | 動作状態、共通プロトコル状態、プロトコル状態                                              |    |

| 706、708                                 | 動作状態、プロトコル状態                                                        |    |

| 710                                     | 動作状態、アイドル状態                                                         |    |

| 800                                     | トランザクション                                                            |    |

| 802                                     | ビットおよびシンボル                                                          |    |

| 806                                     | 制御シグナリング                                                            | 10 |

| 808                                     | SGbusデータ交換                                                          |    |

| 810                                     | データペイロード                                                            |    |

| 812                                     | 終了シーケンス                                                             |    |

| 814                                     | I2C START条件、START条件                                                 |    |

| 816                                     | アドレス                                                                |    |

| 818                                     | コマンドコード                                                             |    |

| 822                                     | Bus-Free状態                                                          |    |

| 824、826                                 | 肯定応答                                                                |    |

| 906                                     | 第1のSTART条件                                                          |    |

| 908                                     | STOP条件、意図しない(および求められていない)STOP条件                                     | 20 |

| 910                                     | START条件、第2のSTART条件                                                  |    |

| 912                                     | ビジー期間                                                               |    |

| 914、930                                 | アイドル期間                                                              |    |

| 922                                     | SDA信号線                                                              |    |

| 924                                     | SCL信号線                                                              |    |

| 928                                     | 反復START条件、即時反復START条件、Sr                                            |    |

| 932                                     | 第1のビジー期間                                                            |    |

| 934                                     | 第2のビジー期間                                                            |    |

| 1008                                    | 意図しないSTART条件、誤ったまたは意図しないSTART条件                                     |    |

| 1012                                    | 意図しないSTOP条件、意図しないおよび求められていないSTOP条件                                  | 30 |

| 1202                                    | 3進送信機(Tx)遷移数、Tx遷移数                                                  |    |

| 1204、1224、1304、1324                     | シンボル                                                                |    |

| 1206、1226、1306、1326                     | 3進受信機(Rx)遷移数、Rx遷移数                                                  |    |

| 1222                                    | 送信機(Tx)3進数                                                          |    |

| 1230、1310、1330                          | 追加のシンボル                                                             |    |

| 1232                                    | 追加の数                                                                |    |

| 1312、1332                               | 追加の3進数                                                              |    |

| 1404、1616、1816                          | プロセッサ                                                               |    |

| 1406                                    | ストレージ                                                               |    |

| 1408                                    | バスインターフェース                                                          | 40 |

| 1410、1620、1820                          | バス                                                                  |    |

| 1414                                    | ランタイムイメージ                                                           |    |

| 1416                                    | ソフトウェアモジュール                                                         |    |

| 1418                                    | ユーザインターフェース                                                         |    |

| 1420                                    | 時分割プログラム                                                            |    |

| 1422                                    | 論理回路                                                                |    |

| 1604、1606、1608、1610、1804、1806、1808、1810 | モジュールおよび/または回路                                                      |    |

| 1612                                    | ラインインターフェース回路、モジュールおよび/または回路                                        |    |

| 1614、1814                               | コネクタまたは線                                                            |    |

| 1618、1818                               | コンピュータ可読記憶媒体                                                        | 50 |

【図1】

【図2】

【図3】

【図4】

【 図 5 】

【 四 7 】

【 図 8 】

【図6】

【図 9】

【図 10】

【図 11】

【 図 1 3 】

【図14】

【 図 1 5 】

【 図 1 6 】

【図17】

【図18】

---

フロントページの続き

(72)発明者 リチャード・ドミニク・ウィートフェルト

アメリカ合衆国・カリフォルニア・92121-1714・サン・ディエゴ・モアハウス・ドライ

ヴ・5775

(72)発明者 ダグラス・ウェイン・ホフマン

アメリカ合衆国・カリフォルニア・92121-1714・サン・ディエゴ・モアハウス・ドライ

ヴ・5775

審査官 和平 悠希

(56)参考文献 特表2002-535882(JP,A)

特開2013-187865(JP,A)

特開2002-077306(JP,A)

米国特許出願公開第2006/0290381(US,A1)

(58)調査した分野(Int.Cl., DB名)

G 06 F 13 / 38

H 04 L 29 / 06