등록특허 10-2114012

**(19) 대한민국특허청(KR)**

**(12) 등록특허공보(B1)**

(45) 공고일자 2020년05월22일

(11) 등록번호 10-2114012

(24) 등록일자 2020년05월18일

- (51) 국제특허분류(Int. Cl.)

*H01L 29/66* (2006.01) *H01L 21/02* (2006.01)

*H01L 21/322* (2006.01) *H01L 21/324* (2017.01)

*H01L 27/11521* (2017.01) *H01L 27/1156*

(2017.01)

*H01L 27/12* (2006.01) *H01L 29/786* (2006.01)

- (52) CPC특허분류

*H01L 29/66742* (2013.01)

*H01L 21/02554* (2013.01)

- (21) 출원번호 10-2018-7033988(분할)

- (22) 출원일자(국제) 2011년02월15일

심사청구일자 2018년11월23일

- (85) 번역문제출일자 2018년11월23일

- (65) 공개번호 10-2018-0128518

- (43) 공개일자 2018년12월03일

- (62) 원출원 특허 10-2018-7015965

원출원일자(국제) 2011년02월15일

심사청구일자 2018년06월05일

- (86) 국제출원번호 PCT/JP2011/053614

- (87) 국제공개번호 WO 2011/108381

국제공개일자 2011년09월09일

- (30) 우선권주장

JP-P-2010-049263 2010년03월05일 일본(JP)

- (56) 선행기술조사문헌

KR1020080114802 A\*

US20060108636 A1\*

US07601984 B2\*

\*는 심사관에 의하여 인용된 문헌

전체 청구항 수 : 총 8 항

심사관 : 최정민

(54) 발명의 명칭 표시 장치

**(57) 요 약**

본 발명의 목적은 매우 신뢰할 수 있는 반도체 장치를 제공하는 것이다. 다른 목적은 매우 신뢰할 수 있는 반도체 장치의 제작 방법을 제공하는 것이다. 또 다른 목적은 낮은 전력 소비를 갖는 반도체 장치를 제공하는 것이다. 또 다른 목적은 낮은 전력 소비를 갖는 반도체 장치의 제작 방법을 제공하는 것이다. 또한, 다른 목적은 (뒷면에 계속)

**대 표 도** - 도2

높은 대량 생산성으로 제작될 수 있는 반도체 장치를 제공하는 것이다. 다른 목적은, 대량 생산성으로 제작될 수 있는 반도체 장치의 제작 방법을 제공하는 것이다. 산화물 반도체층에 남아있는 불순물이 제거되어 산화물 반도체층이 극히 높은 순도를 갖도록 정제된다. 구체적으로, 할로겐 원소를 산화물 반도체층으로 첨가한 후, 산화물 반도체층으로부터 불순물을 제거하기 위하여 열 처리가 수행된다. 할로겐 원소는 불소인 것이 바람직하다.

(52) CPC특허분류

*H01L 21/02565* (2013.01)

*H01L 21/02631* (2013.01)

*H01L 21/3228* (2013.01)

*H01L 21/324* (2013.01)

*H01L 27/11521* (2013.01)

*H01L 27/1156* (2013.01)

*H01L 27/1203* (2013.01)

*H01L 27/1225* (2013.01)

*H01L 29/7869* (2013.01)

---

## 명세서

### 청구범위

#### 청구항 1

게이트 전극과,

상기 게이트 전극 위의 게이트 절연층과,

상기 게이트 절연층 위의 In과 Ga과 Zn을 갖는 산화물 반도체층과,

상기 산화물 반도체층과 접속하는 소스 전극 및 드레인 전극과,

상기 소스 전극 또는 상기 드레인 전극의 한쪽과 접속되는 화소 전극을 갖고,

상기 산화물 반도체층은  $1 \times 10^{18}$  atoms/cm<sup>3</sup> 이하의 농도로 할로겐 원소를 포함하고,

소스와 드레인 사이의 전압이 3.5V, 온도 25°C에서, 채널폭 1μm 당 오프 상태 전류 밀도는 100zA/μm 이하인 트랜지스터를 갖는, 표시 장치.

#### 청구항 2

게이트 전극과,

상기 게이트 전극 위의 게이트 절연층과,

상기 게이트 절연층 위의 In과 Ga과 Zn을 갖는 산화물 반도체층과,

상기 산화물 반도체층과 접속하는 소스 전극 및 드레인 전극과,

상기 소스 전극 또는 상기 드레인 전극의 한쪽과 접속되는 화소 전극을 갖고,

상기 산화물 반도체층은  $1 \times 10^{18}$  atoms/cm<sup>3</sup> 이하의 농도로 불소를 포함하고,

소스와 드레인 사이의 전압이 3.5V, 온도 25°C에서, 채널폭 1μm 당 오프 상태 전류 밀도는 100zA/μm 이하인 트랜지스터를 갖는, 표시 장치.

#### 청구항 3

제 1 항 또는 제 2 항에 있어서,

상기 게이트 전극이 몰리브덴, 티타늄, 탄탈, 텉스텐, 알루미늄, 구리, 네오디뮴, 스칸듐 중 적어도 하나를 포함하는 적층막인, 표시 장치.

#### 청구항 4

제 1 항 또는 제 2 항에 있어서,

상기 게이트 절연층이 산화 실리콘층 또는 질화 실리콘층을 포함하는 적층막인, 표시 장치.

#### 청구항 5

제 1 항 또는 제 2 항에 있어서,

상기 소스 전극 및 상기 드레인 전극은 상기 게이트 절연층과 상기 산화물 반도체층에 접하는, 표시 장치.

#### 청구항 6

제 1 항 또는 제 2 항에 있어서,

상기 소스 전극 및 상기 드레인 전극이 알루미늄, 크롬, 구리, 탄탈, 티타늄, 몰리브덴, 텉스텐 중 적어도 하나를 포함하는 적층막인, 표시 장치.

## 청구항 7

제 1 항 또는 제 2 항에 있어서,

상기 표시 장치가 상기 화소 전극을 포함하는 액정 소자를 갖는, 표시 장치.

## 청구항 8

제 1 항 또는 제 2 항에 있어서,

상기 산화물 반도체층은 진성인, 표시 장치.

## 발명의 설명

### 기술 분야

[0001] 본 발명은 산화물 반도체를 포함하는 반도체 장치에 관한 것이다. 본 발명은 또한 반도체 장치의 제작 방법에 관한 것이다. 여기서 반도체 장치들은 반도체 특성들을 사용하는 것에 의해 기능하는 일반적인 소자들과 장치들을 나타낸다는 것에 주의한다.

### 배경 기술

[0002] 절연 표면을 갖는 기판 위에 형성된 반도체층을 이용하여 트랜지스터가 형성되는 기술이 공지되어 있다. 예를 들면, 트랜지스터가 실리콘계 반도체 재료를 포함하는 박막을 이용하여 유리 기판 위에 형성되고 트랜지스터가 액정 표시 장치 등에 적용되는 기술이 공지되어 있다.

[0003] 액정 표시 장치에 이용되는 트랜지스터는 일반적으로 비정질 실리콘 또는 다결정 실리콘과 같은 반도체 재료를 이용하여 형성된다. 비정질 실리콘을 포함하는 트랜지스터들은 낮은 전계 효과 이동도를 가지나, 비정질 실리콘을 이용하는 경우에 더 큰 유리 기판이 이용될 수 있다. 한편, 다결정 실리콘을 포함하는 트랜지스터들은 높은 전계 효과 이동도를 가지나; 그들은 레이저 어닐링과 같은 결정화 단계를 거쳐야 할 필요가 있고 따라서 더 큰 유리 기판들에 대해 항상 적절하지는 않다.

[0004] 다른 재료로서, 산화물 반도체가 관심을 끌고 있다. 산화 아연과 산화 아연을 포함하는 재료들이 산화물 반도체 재료들로 공지되어 있다. 각각이  $10^{18} / \text{cm}^3$  보다 낮은 전자 캐리어 농도를 갖는 비정질 산화물(산화물 반도체)을 이용하여 형성되는 박막 트랜지스터들이 특히 문서들 1 내지 3에 개시된다.

[0005] [참조]

[0006] [특허 문서]

[0007] [특허 문서 1] 일본 특허 공개 공보 2006-165527

[0008] [특허 문서 2] 일본 특허 공개 공보 2006-165528

[0009] [특허 문서 3] 일본 특허 공개 공보 2006-165529

### 발명의 내용

#### 해결하려는 과제

[0010] 반도체 특성들을 사용하는 트랜지스터들은 시간에 따른 열화에 의해 유발되는, 임계 전압에서의 작은 변동과, 작은 오프 상태 전류, 등을 갖는 것이 바람직하다. 예를 들어, 시간에 따른 열화에 의해 유발되는, 임계 전압에서의 큰 변동을 갖는 트랜지스터가 반도체 장치로 이용되면, 상기 반도체 장치의 신뢰성이 낮아진다. 또한, 큰 오프 상태 전류를 갖는 트랜지스터가 반도체 장치로 이용되면, 반도체 장치의 전력 소비가 증가된다.

[0011] 매우 신뢰할 수 있는 반도체 장치를 제공하는 것이 본 발명의 목적이다. 매우 신뢰할 수 있는 반도체 장치의 제작 방법을 제공하는 것이 다른 목적이다.

[0012] 낮은 전력 소비를 갖는 반도체 장치를 제공하는 것이 또 다른 목적이다. 낮은 전력 소비를 갖는 반도체 장치의 제작 방법을 제공하는 것이 또 다른 목적이다.

- [0013] 또한, 높은 대량 생산성으로 제작될 수 있는 반도체 장치를 제공하는 것이 다른 목적이다. 높은 대량 생산성으로 제작될 수 있는 반도체 장치의 제작 방법을 제공하는 것이 다른 목적이다.

- [0014] 상술된 목적들을 성취하기 위하여, 본 발명가들은 산화물 반도체를 포함하는 반도체층을 갖는 반도체 장치에서, 산화물 반도체층에 포함된 불순물들의 농도가 임계 전압의 변동과 오프 상태 전류의 증가에 영향을 끼친다는 사실에 주목한다. 불순물들의 예들로서, 수소와, 물과 같은 수소를 포함하는 물질이 주어질 수 있다. 수소를 포함하는 물질은 산화물 반도체층의 금속에 수소를 공급하여, 불순물 준위(level)가 형성된다.

- [0015] 산화물 반도체층에 포함된 대부분의 불순물들은 산화물 반도체층이 형성된 후 고온(예를 들면, 600°C)에서 열처리를 수행하는 것에 의해 제거될 수 있다. 그러나, 산화물 반도체에 포함된 금속에 강하게 결합되는 불순물(예를 들면, 수소 또는 수산기)은 강한 결합력으로 인해 산화물 반도체층에 남아있다. 반도체층이 불순물이 남아있는 산화물 반도체를 포함할 때, 오프 상태 전류의 증가와 같은 문제가 발생한다.

- [0016] 상술된 목적들을 성취하기 위하여, 산화물 반도체층에 남아있는 불순물이 제거되어 산화물 반도체층이 극히 높은 순도를 갖도록 정제된다. 구체적으로, 불순물에 강하게 결합될 수 있는 물질이 산화물 반도체층에 첨가된 후에, 산화물 반도체층으로부터 수소를 포함하는 안정한 물질을 제거하기 위하여 열 처리가 수행된다. 불순물에 강하게 결합될 수 있는 물질은 예를 들면, 할로겐 원소를 포함하는 물질인 것이 바람직하다. 높은 운동 에너지를 갖는 할로겐 원소가 산화물 반도체층에 첨가되면, 예를 들어, 산화물 반도체의 금속과 수소 사이의 결합, 금속과 수산기 사이의 결합, 또는 금속에 결합되는 수산기의 산소와 수소 사이의 결합이 끊어질 수 있다.

- [0017] 불순물에 강하게 결합될 수 있는 물질을 산화물 반도체층으로 첨가하는 것에 의해 금속과 불순물 사이의 결합이 끊어질 때, 일부 경우들에서 금속 원자 상에서 맹글링 결합(dangling bond)이 생성될 수 있다. 맹글링 결합은 캐리어들의 생성을 유발하고, 따라서 캐리어 밀도가 증가된다. 임계 전압의 감소로 인해 노멀리 온(normally on)이 되는 경향이 있으므로, 높은 캐리어 밀도를 갖는 산화물 반도체층을 포함하는 반도체 장치는 바람직하지 않다.

- [0018] 상술된 문제는 또한 할로겐 원소를 산화물 반도체층으로 첨가하는 것에 의해 해결된다. 할로겐 원소가 금속 원자 상의 맹글링 결합에 결합하여 맹글링 결합이 종결되므로, 캐리어들의 생성이 감소될 수 있다.

### 과제의 해결 수단

- [0019] 즉, 본 발명의 실시예는 반도체 장치의 제작 방법이며, 상기 방법은, 절연 표면을 갖는 기판 위에 게이트 전극을 형성하고; 상기 게이트 전극 위에 게이트 절연층을 형성하고; 상기 게이트 전극과 중첩하고 상기 게이트 절연층과 접하는 산화물 반도체층을 형성하고; 할로겐 원소를 상기 산화물 반도체층으로 첨가하고; 할로겐 원소가 첨가된 상기 산화물 반도체층 상에서 제 1 열 처리를 수행하고; 열 처리가 수행된 산화물 반도체층과 접하고 각각이 상기 게이트 전극과 중첩하는 단부를 갖는 소스 전극 및 드레인 전극을 형성하고; 산화물 반도체층의 표면과 접하고 상기 산화물 반도체층의 채널 형성 영역과 중첩하는 절연층을 형성하는 단계들을 포함한다.

- [0020] 본 발명의 다른 실시예는 반도체 장치의 제작 방법이며, 상기 방법은, 절연 표면을 갖는 기판 위에 소스 전극 및 드레인 전극을 형성하고; 상기 소스 전극의 단부 및 상기 드레인 전극의 단부를 덮는 산화물 반도체층을 형성하고; 할로겐 원소를 상기 산화물 반도체층으로 첨가하고; 할로겐 원소가 첨가된 상기 산화물 반도체층 상에서 제 1 열 처리를 수행하고; 상기 소스 전극의 단부 및 상기 드레인 전극의 단부와 중첩하고 상기 열 처리가 수행되는 상기 산화물 반도체층과 접하는 게이트 절연층을 형성하고; 상기 게이트 절연층과 접하고 상기 소스 전극의 단부 및 상기 드레인 전극의 단부와 중첩하는 게이트 전극을 형성하는 단계들을 포함한다.

- [0021] 반도체 장치의 제작 방법의 상기 실시예들에서, 제 1 열 처리 후에 산소가 산화물 반도체층으로 첨가될 수 있다. 산화물 반도체의 주성분들 중 하나인 산소가 공급될 수 있으므로, 산소를 산화물 반도체층에 첨가하는 것이 바람직하다. 또한, 산화물 반도체층으로의 산소의 첨가 후에 제 2 열 처리가 수행될 수 있다. 산소의 첨가와 제 2 열 처리에 의해, 할로겐 원소의 첨가와 제 1 열 처리에 의해 제거되지 않았던 불순물들이 제거될 수 있고; 따라서, 산화물 반도체층이 정제될 수 있으며 전기적으로 i-형(진성) 또는 실질적으로 i-형 산화물 반도체층이 될 수 있다.

- [0022] 반도체 장치의 제작 방법의 상기 실시예들에서, 제 1 열 처리는 250°C보다 높거나 같고 600°C보다 낮거나 같은 온도에서 수행되는 것이 바람직하다.

- [0023] 반도체 장치의 제작 방법의 상기 실시예들에서, 산화물 반도체층을 형성하는 단계 후에 열 처리가 수행될 수 있다. 산화물 반도체층의 형성 후에 수행된 열 처리에 의해, 산화물 반도체층의 수소 또는 수분과 같은 불순물들

이 제거되거나 배기(exhaust)될 수 있다. 열 처리 후에 할로겐 원소가 첨가되는 경우에, 산화물 반도체층에 포함된 불순물들의 농도가 더욱 감소될 수 있다.

[0024] 또한, 본 발명의 다른 실시예는 반도체 장치의 제작 방법이며, 반도체 장치의 제작 방법의 상술된 실시예들 중 임의의 것을 이용하여, 제 1 트랜지스터 위에 형성된 절연막 위에 제 2 트랜지스터를 형성하는 단계들을 포함한다.

[0025] 본 발명의 또 다른 실시예는 절연 표면 위의 게이트 전극; 상기 절연 표면과 상기 게이트 전극 위의 게이트 절연층; 상기 게이트 절연층 위의  $10^{15}$  atoms/cm<sup>3</sup>보다 높거나 같고  $10^{18}$  atoms/cm<sup>3</sup>보다 낮거나 같은 할로겐 원소 농도를 갖는 산화물 반도체층; 상기 게이트 절연층과 상기 산화물 반도체층 위의 소스 전극 및 드레인 전극; 및 산화물 반도체층의 일부와 접하고, 상기 게이트 절연층, 상기 산화물 반도체층, 상기 소스 전극, 및 상기 드레인 전극 위의 절연층을 포함하는 반도체 장치이다.

[0026] 본 발명의 또 다른 실시예는 절연 표면 위의 소스 전극 및 드레인 전극; 상기 절연 표면, 상기 소스 전극, 및 상기 드레인 전극 위의  $10^{15}$  atoms/cm<sup>3</sup>보다 높거나 같고  $10^{18}$  atoms/cm<sup>3</sup>보다 낮거나 같은 할로겐 원소 농도를 갖는 산화물 반도체층; 상기 절연 표면, 상기 소스 전극, 상기 드레인 전극, 및 상기 산화물 반도체층 위의 게이트 절연층; 및 상기 게이트 절연층 위의 게이트 전극을 포함하는 반도체 장치이다.

[0027] 반도체 장치의 상기 실시예들에서, 불소가 할로겐 원소로 바람직하다. 이는 불소와 수소 사이의 결합 에너지가 다른 할로겐 원소들 중 임의의 것과 수소 사이의 결합 에너지보다 높고 더 안정하기 때문이다.

### 발명의 효과

[0028] 본 발명의 실시예는 매우 신뢰할 수 있는 반도체 장치를 제공할 수 있다. 또한, 본 발명의 다른 실시예는 매우 신뢰할 수 있는 반도체 장치의 제작 방법을 제공할 수 있다.

[0029] 본 발명의 실시예는 낮은 전력 소비를 갖는 반도체 장치를 제공할 수 있다. 또한, 본 발명의 다른 실시예는 낮은 전력 소비를 갖는 반도체 장치의 제작 방법을 제공할 수 있다.

[0030] 본 발명의 실시예는 높은 대량 생산성으로 제작될 수 있는 반도체 장치를 제공할 수 있다. 또한, 본 발명의 실시예는 높은 대량 생산성으로 제작될 수 있는 반도체 장치의 제작 방법을 제공할 수 있다.

### 도면의 간단한 설명

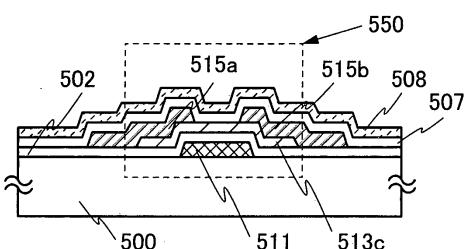

[0031] 도 1a 및 도 1b는 실시예의 반도체 장치의 구조를 도시한 도면.

도 2a 내지 도 2e는 실시예의 반도체 장치의 제작 방법을 도시한 도면.

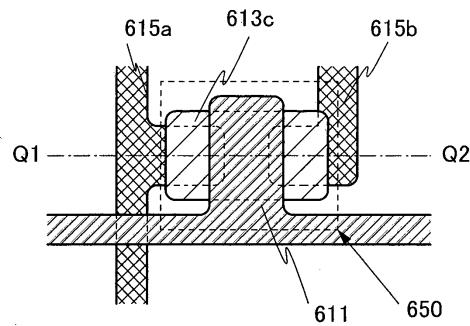

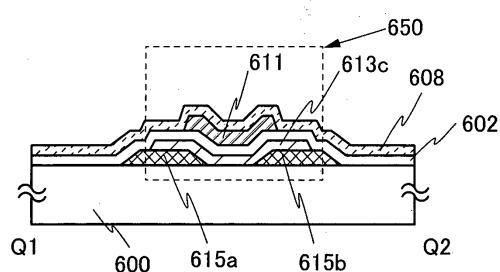

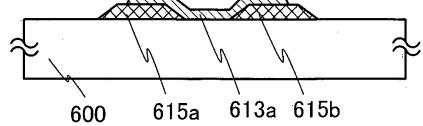

도 3a 및 도 3b는 실시예의 반도체 장치의 구조를 도시한 도면.

도 4a 내지 도 4e는 실시예의 반도체 장치의 제작 방법을 도시한 도면.

도 5a 및 도 5b는 실시예의 반도체 장치의 구조를 도시한 도면.

도 6a 내지 도 6d는 실시예의 반도체 장치의 제작 방법을 도시한 도면.

도 7a 내지 도 7c는 실시예의 반도체 장치의 제작 방법을 도시한 도면.

도 8a 내지 도 8d는 실시예의 반도체 장치의 제작 방법을 도시한 도면.

도 9a 내지 도 9c는 실시예의 반도체 장치의 제작 방법을 도시한 도면.

도 10a 및 도 10b는 실시예의 반도체 장치의 구조를 도시한 도면.

도 11a 내지 도 11c는 실시예의 반도체 장치의 제작 방법을 도시한 도면.

도 12a 내지 도 12c는 실시예의 반도체 장치의 제작 방법을 도시한 도면.

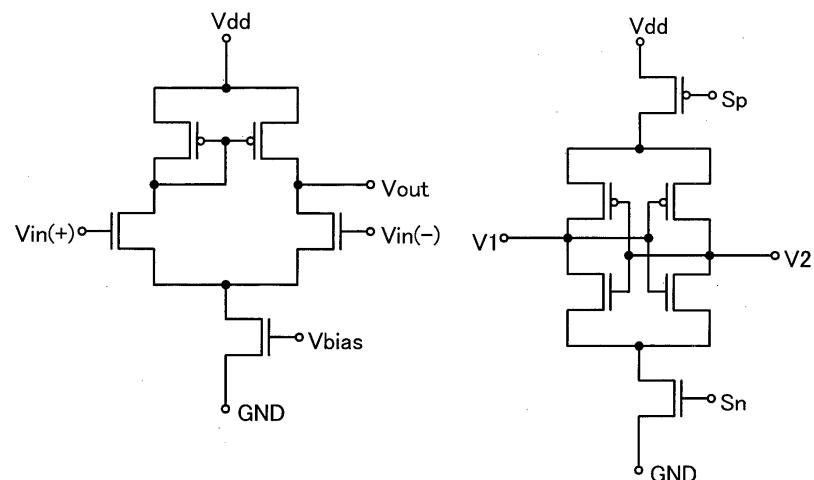

도 13a1, 도 13a2, 및 도 13b는 실시예의 반도체 장치들의 회로도들.

도 14a 및 도 14b는 실시예의 반도체 장치들의 회로도들.

도 15a 내지 도 15c는 실시예의 반도체 장치들의 회로도들.

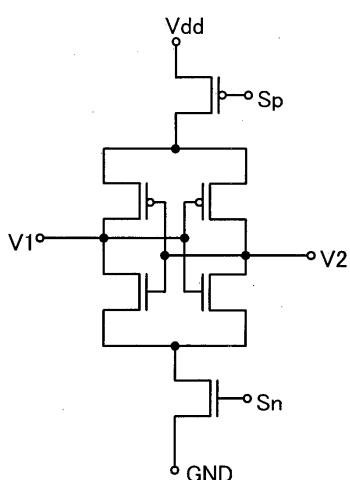

도 16a 내지 도 16f는 실시예의 반도체 장치를 포함하는 전자 기기들을 도시한 도면.

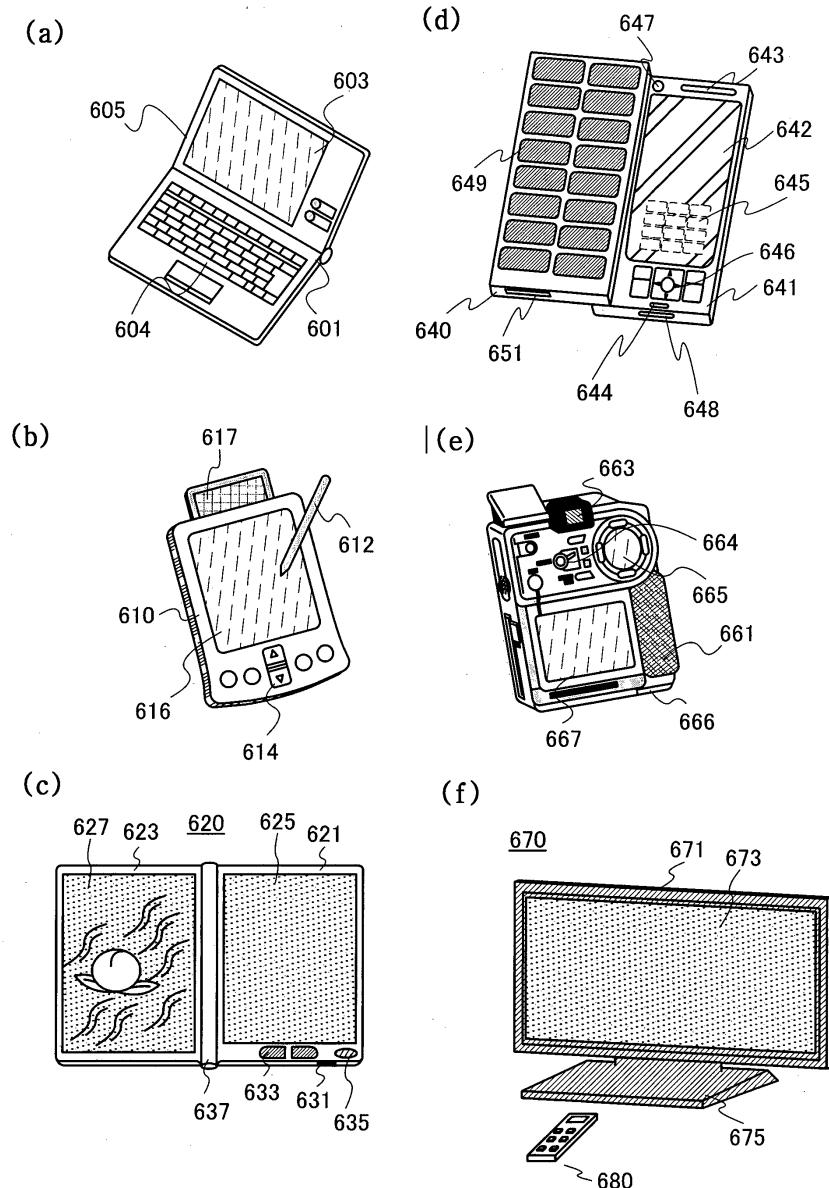

도 17은 시뮬레이션 모델의 예를 도시하는 개략도.

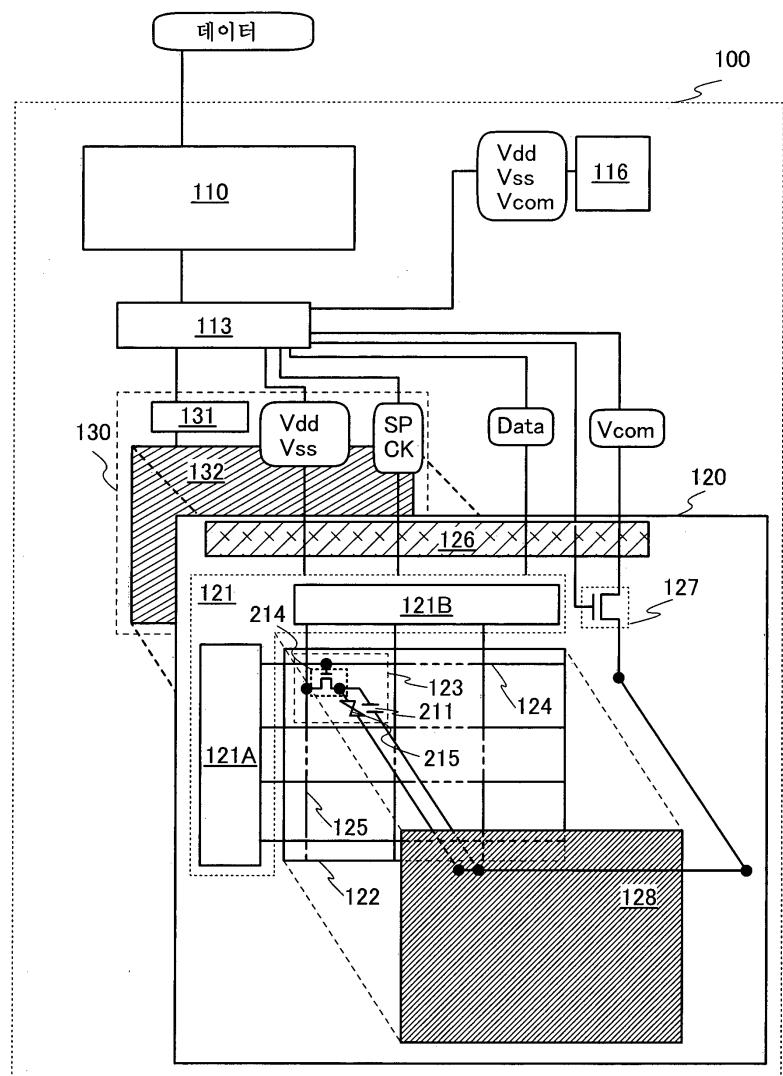

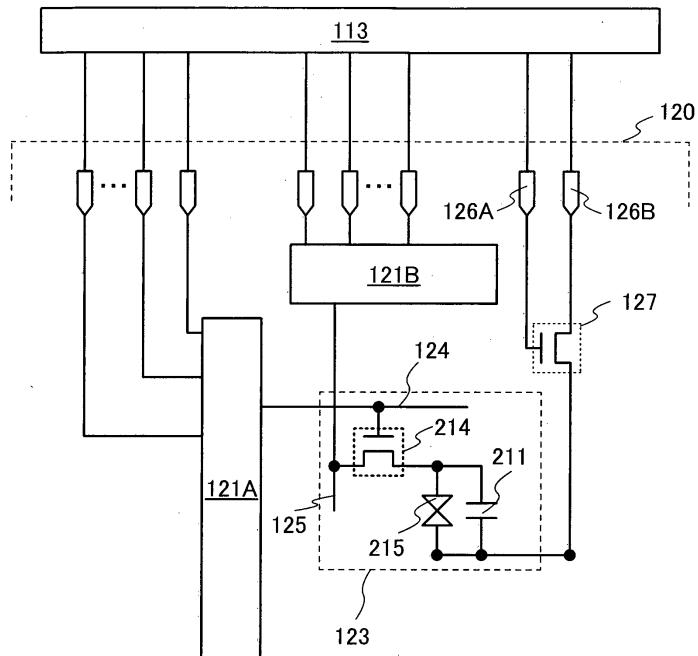

도 18은 실시예의 액정 표시 장치의 구조를 도시하는 블록도.

도 19는 실시예의 액정 표시 장치의 구조를 도시한 도면.

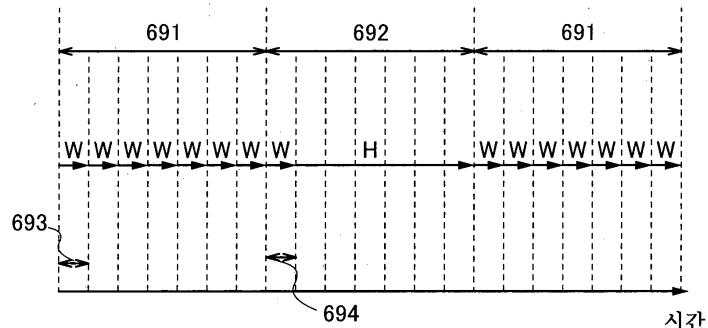

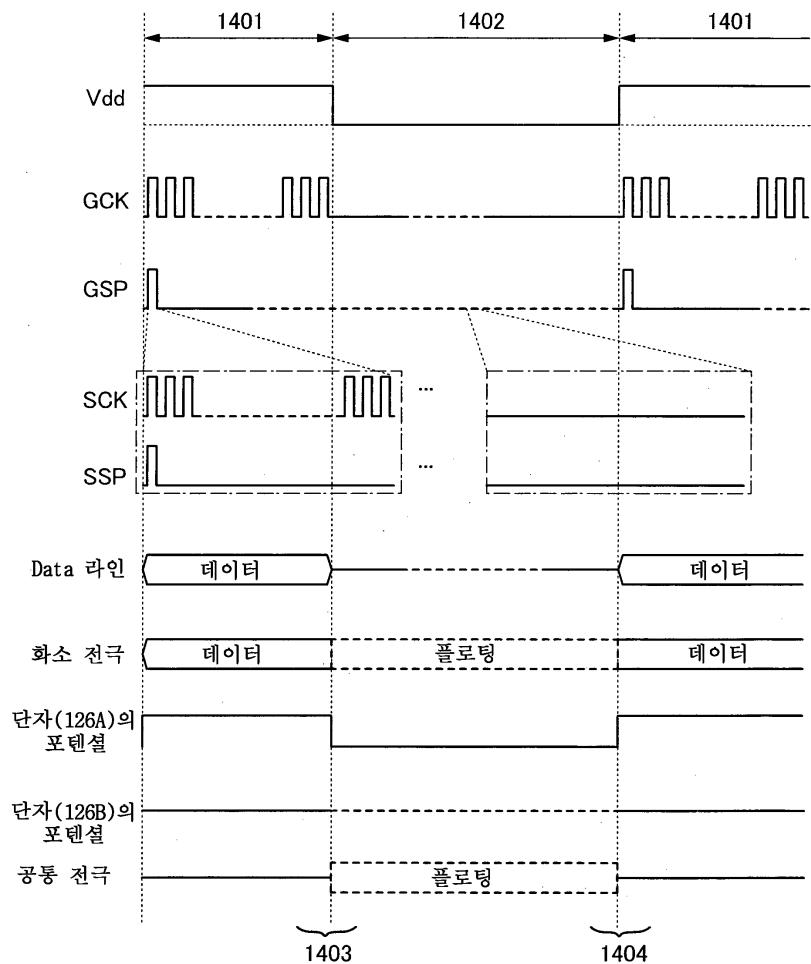

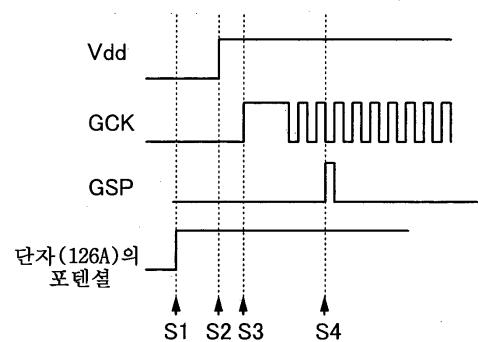

도 20은 실시예의 액정 표시 장치의 동작들을 도시하는 타이밍도.

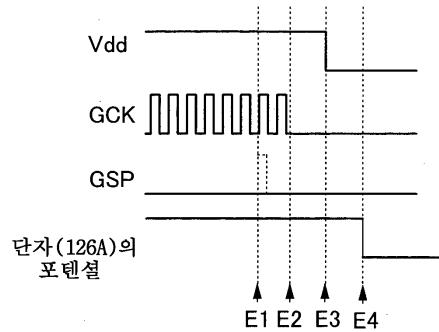

도 21a 및 도 21b는 실시예의 액정 표시 장치의 표시 제어 회로의 동작들을 도시하는 타이밍도들.

도 22는 실시예의 움직이는 이미지를 표시하는 기간과 정지 이미지를 표시하는 기간의 프레임 기간들에서 이미지 신호들을 기록하는 빙도를 개략적으로 도시한 도면.

### 발명을 실시하기 위한 구체적인 내용

[0032] 실시예들이 도면들을 참조하여 상세하게 설명될 것이다. 본 발명은 다음 설명에 제한되지 않으며, 모드들 및 상세한 설명들은 본 발명의 정신과 범주로부터 벗어남이 없이 다양한 방법들로 변화될 수 있다는 것이 당업자에 의해 쉽게 이해된다는 것에 주의한다. 따라서, 본 발명은 실시예들의 설명으로 제한되는 것으로 이해되지 않는다. 이하로 설명된 본 발명의 구조들에서, 동일한 부분들 또는 유사한 기능들을 갖는 부분들은 상이한 도면들에서 동일한 번호들로 표시되며, 그의 상세한 설명은 반복되지 않는다.

[0033] (실시예 1)

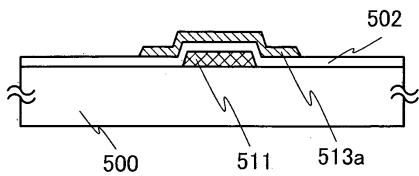

[0034] 본 실시예에서, 불순물들을 제거하기 위하여 불소를 산화물 반도체층으로 첨가하고 이후 산화물 반도체층이 열처리를 거치게 하는 것에 의해 산화물 반도체층을 정제하는 방법을 이용하는 보텀 게이트형 트랜지스터의 제작방법이 도 1a 및 도 1b와 도 2a 내지 도 2e를 참조하여 설명될 것이다.

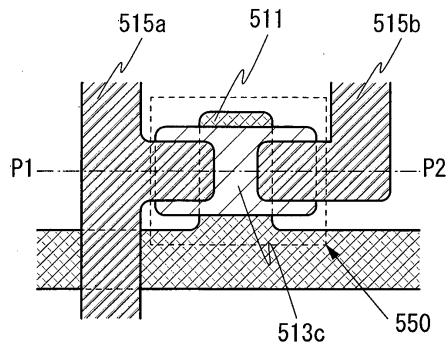

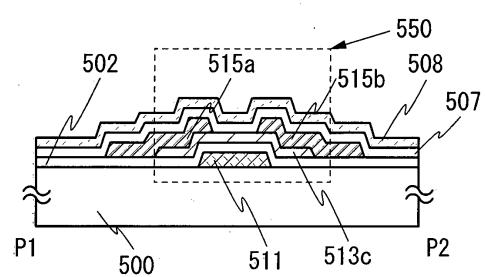

[0035] 도 1a 및 도 1b는 본 실시예에서 제작되는 보텀 게이트형 트랜지스터(550)의 구조를 도시한다. 도 1a는 트랜지스터(550)의 상면도이고, 도 1b는 트랜지스터(550)의 단면도이다. 도 1b는 도 1a의 선(P1-P2)을 따라 얻어진 단면도에 대응한다는 것에 주의한다.

[0036] 트랜지스터(550)에서, 게이트 전극(511)과 상기 게이트 전극(511)을 덮는 게이트 절연층(502)이 절연 표면을 갖는 기판(500) 위에 제공된다. 상기 게이트 전극(511)과 중첩하는 정제된 산화물 반도체층(513c)이 상기 게이트 절연층(502) 위에 제공된다. 또한, 소스 및 드레인 전극으로 기능하는 제 1 전극(515a) 및 제 2 전극(515b)이 산화물 반도체층(513c)과 접하여 제공되어 각각이 상기 게이트 전극(511)과 중첩하는 단부를 갖게 된다. 또한, 상기 산화물 반도체층(513c)과 접하고 그의 채널 형성 영역과 중첩하는 절연층(507), 및 상기 트랜지스터(550)를 덮는 보호 절연층(508)이 제공된다.

[0037] 본 실시예에서 이용된 산화물 반도체는 i-형(진성) 산화물 반도체 또는 실질적으로 i-형(진성) 산화물 반도체이다. 상기 i-형(진성) 또는 실질적으로 i-형 산화물 반도체는 n-형 불순물로 기능하는 수소가 제거되고, 산화물 반도체가 정제되어 산화물 반도체의 주성분들이 아닌 불순물들을 가능하면 거의 함유하지 않도록 하는 방식으로 얻어진다.

[0038] 상기 정제된 산화물 반도체는 극히 적은 캐리어들을 포함하고, 그의 캐리어 농도는  $1 \times 10^{14} / \text{cm}^3$ 보다 낮고, 바람직하게는  $1 \times 10^{12} / \text{cm}^3$ 보다 낮고, 더욱 바람직하게는  $1 \times 10^{11} / \text{cm}^3$ 보다 낮다는 것에 주의한다. 이러한 적은 캐리어들은 오프 상태에 있는 전류(오프 상태 전류)가 충분히 작아질 수 있게 한다.

[0039] 구체적으로, 상기 산화물 반도체층을 포함하는 상기 트랜지스터에서, 오프 상태의 소스와 드레인 사이의 채널 폭의 마이크로미터 당 누설 전류 밀도(오프 상태 전류 밀도)는 3.5V의 소스-드레인 전압과 주위 온도(예를 들면, 25°C)에서  $100\text{zA}/\mu\text{m}$ ( $1 \times 10^{-19} \text{ A}/\mu\text{m}$ )보다 작거나 같아질 수 있고, 바람직하게는  $10\text{zA}/\mu\text{m}$ ( $1 \times 10^{-20} \text{ A}/\mu\text{m}$ )보다 작거나 같아질 수 있으며, 더욱 바람직하게는  $1\text{zA}/\mu\text{m}$ ( $1 \times 10^{-21} \text{ A}/\mu\text{m}$ )보다 작거나 같아질 수 있다.

[0040] 또한, 상기 정제된 산화물 반도체층을 포함하는 상기 트랜지스터에서, 오프 상태 전류의 온도 의존성은 거의 관찰되지 않으며, 오프 상태 전류는 고온 상태 하에서도 극히 작게 남아 있다.

[0041] 다음, 상기 기판(500) 위의 상기 트랜지스터(550)의 제작 방법이 도 2a 내지 도 2e를 참조하여 설명될 것이다.

- [0042] 먼저, 도전막이 절연 표면을 갖는 상기 기판(500) 위에 형성된 후, 게이트 전극(511)을 포함하는 배선층이 제 1 포토리소그래피 단계에 의해 형성된다. 본 명세서에서 설명된 트랜지스터의 제작 공정의 포토리소그래피 단계들 중 임의의 단계에서 잉크젯 방법에 의해 레지스트 마스크가 형성될 수 있다는 것에 주의한다. 잉크젯 방법에 의한 레지스트 마스크의 형성은 포토마스크를 필요로 하지 않으며; 따라서, 제작 비용이 감소될 수 있다.

- [0043] 본 실시예에서, 유리 기판이 절연 표면을 갖는 기판(500)으로 이용된다.

- [0044] 기저막이 되는 절연막이 상기 기판(500)과 상기 게이트 전극(511) 사이에 제공될 수 있다. 상기 기저막은 상기 기판(500)으로부터 불순물 원소(예를 들면, 리튬 또는 나트륨과 같은 알칼리 금속, 및 칼슘과 같은 알칼리 토금 속)의 확산을 방지하는 기능을 가지며, 질화 실리콘막, 산화 실리콘막, 질화산화 실리콘막, 및 산화질화 실리콘막 중 하나 또는 그 이상을 포함하는 단층 구조 또는 적층된 구조를 갖도록 형성될 수 있다.

- [0045] 게이트 전극(511)이 몰리브덴, 티타늄, 탄탈, 텡스텐, 알루미늄, 구리, 네오디뮴, 또는 스칸듐과 같은 금속 재료, 또는 그의 주성분으로서 이러한 금속 재료들 중 임의의 것을 함유하는 합금 재료를 포함하는 단층 구조 또는 적층된 구조를 갖도록 형성될 수 있다.

- [0046] 알루미늄 또는 구리를 이용하는 경우에, 그들이 내화 금속(refractory metal) 재료와 조합하여 사용되어 내열성 문제 및 부식성(corrosive) 문제를 방지하도록 하는 것이 바람직하다는 것에 주의한다. 내화 금속 재료로서, 몰리브덴, 티타늄, 크롬, 탄탈, 텡스텐, 네오디뮴, 스칸듐, 등이 이용될 수 있다.

- [0047] 구리를 사용하는 경우에, 구리-마그네슘-알루미늄(Cu-Mg-Al) 합금이 기저가 되는 층에 제공되고 그 위에 구리가 형성되는 구조가 바람직하다. Cu-Mg-Al 합금의 제공은 구리와 산화물막과 같은 기저(base) 사이의 부착성을 증가시키는 효과를 갖는다.

- [0048] 다음, 게이트 절연층(502)이 게이트 전극(511) 위에 형성된다. 상기 게이트 절연층(502)은 플라즈마 CVD법, 스퍼터링법, 등에 의해 산화 실리콘층, 질화 실리콘층, 산화질화 실리콘층, 질화산화 실리콘층, 산화 알루미늄층, 질화 알루미늄층, 산화질화 알루미늄층, 질화산화 알루미늄층, 또는 산화 하프늄층을 포함하는 단층 구조 또는 적층 구조를 갖도록 형성될 수 있다.

- [0049] 본 실시예의 산화물 반도체로서, 불순물들을 제거하는 것에 의해 얻어지는 i-형 또는 실질적으로 i-형 산화물 반도체가 이용된다. 이러한 정제된 산화물 반도체는 계면 상태 밀도(interface state density)와 계면 전하에 극히 민감하며; 따라서, 산화물 반도체층과 게이트 절연층 사이의 계면이 중요하다. 그러한 이유로, 정제된 산화물 반도체와 접하는 상기 게이트 절연층은 고품질을 가질 필요가 있다.

- [0050] 예를 들어, 조밀하고, 높은 내전압(withstand voltage)과 고품질을 갖는 절연층이 형성될 수 있기 때문에, 마이크로파들(예를 들면, 2.45GHz의 주파수)을 이용하는 고밀도 플라즈마 CVD법이 채용되는 것이 바람직하다. 정제된 산화물 반도체와 고품질 게이트 절연층은 서로 가까이 접촉하며, 따라서 양호한 계면 특성들을 얻도록 계면 상태 밀도가 감소될 수 있다.

- [0051] 말할 필요도 없이, 방법이 상기 게이트 절연층으로서 고품질 절연층의 형성을 가능하게 한다면, 스퍼터링법 또는 플라즈마 CVD법과 같은 다른 막 형성 방법이 채용될 수 있다. 또한, 그의 막 품질과, 절연층과 산화물 반도체 사이의 계면의 특성이 절연층의 형성 후에 수행된 열 처리에 의해 개선되는 절연층이 게이트 절연층으로서 형성될 수 있다. 임의의 경우에, 절연층이 절연층과 산화물 반도체 사이의 계면의 계면 상태 밀도를 감소시킬 수 있고 게이트 절연층으로서 양호한 막 품질을 가질 뿐만 아니라 양호한 계면을 형성할 수 있다면, 임의의 절연층이 이용될 수 있다.

- [0052] 게이트 절연층(502)은 나중에 형성될 산화물 반도체층(513c)과 접한다는 것에 주의한다. 수소가 산화물 반도체 층(513c)에서 확산할 때, 반도체 특성들이 악화되고; 따라서, 상기 게이트 절연층(502)은 수소, 수산기, 및 수분을 함유하지 않는 것이 바람직하다. 상기 게이트 절연층(502)과 산화물 반도체막이 가능하면 적게 수소, 수산기, 및 수분을 함유하기 위하여, 산화물 반도체막의 막 형성의 전처리(pretreatment)로서, 게이트 전극(511)이 형성되는 기판(500) 또는 게이트 절연층(502)까지 층들이 형성되는 기판(500)이 스퍼터링 장치의 예열(heating) 챔버에서 예열되어 형성되어, 기판(500)에 흡수된 수소 또는 수분과 같은 불순물들이 제거되고 배기되는 것이 바람직하다. 예열 챔버에 제공된 배기 유닛으로서, 크라이오펌프(cryopump)가 바람직하다. 이러한 예열 처리는 생략될 수 있다는 것에 주의한다. 또한, 상기 예열은 제 1 전극(515a)과 제 2 전극(515b)이 그 위에 형성되었으나 절연층(507)은 아직 형성되지 않은 상태의 기판(500) 상에서 유사한 방식으로 수행될 수 있다.

- [0053] 다음, 2nm보다 크거나 같고 200nm보다 작거나 같은, 바람직하게는 5nm보다 크거나 같고 30nm보다 작거나 같은

두께를 갖는 산화물 반도체막이 게이트 절연층(502) 위에 형성된다.

[0054] 스팍터링법에 의해 산화물 반도체막이 형성되기 전에, 게이트 절연층(502)의 표면에 부착되는 가루 물질들(또한 입자들 또는 먼지로 불림)이 아르곤 가스가 주입되고 플라즈마가 생성되는 역 스팍터링(reverse sputtering)에 의해 제거되는 것이 바람직하다는 것에 주의한다. 역 스팍터링은 타겟 측으로의 전압의 인가없이, 아르곤 분위기에서 RF 전원을 이용하여 기관 측으로 전압이 인가되어, 기관의 표면을 변경시키기 위해 기관의 근처에 플라즈마가 생성되도록 하는 방법을 말한다. 아르곤 분위기 대신, 질소 분위기, 헬륨 분위기, 산소 분위기, 등이 이용될 수 있다는 것에 주의한다.

[0055] 산화물 반도체막이 금속 산화물 타겟을 이용하여 스팍터링법에 의해 형성된다. 또한, 상기 산화물 반도체막이 희가스(예를 들면, 아르곤) 분위기, 산소 분위기, 또는 희가스(예를 들면, 아르곤)와 산소를 함유하는 혼합 분위기 하에서 스팍터링법에 의해 형성될 수 있다.

[0056] 산화물 반도체막을 위해 이용된 산화물 반도체로서, 다음 금속 산화물들: In-Sn-Ga-Zn-O계 산화물 반도체와 같은 4원계 금속 산화물; In-Ga-Zn-O계 산화물 반도체, In-Sn-Zn-O계 산화물 반도체, In-Al-Zn-O계 산화물 반도체, Sn-Ga-Zn-O계 산화물 반도체, Al-Ga-Zn-O계 산화물 반도체, 또는 Sn-Al-Zn-O계 산화물 반도체와 같은 3원계 금속 산화물; In-Zn-O계 산화물 반도체, Sn-Zn-O계 산화물 반도체, Al-Zn-O계 산화물 반도체, Zn-Mg-O계 산화물 반도체, Sn-Mg-O계 산화물 반도체, In-Mg-O계 산화물 반도체, 또는 In-Ga-O계 산화물 반도체와 같은 2원계 금속 산화물; In-O계 산화물 반도체, Sn-O계 산화물 반도체, 또는 Zn-O계 산화물 반도체와 같은 단원계 금속 산화물; 등 중 임의의 것이 이용될 수 있다. 또한, SiO<sub>2</sub>가 상기 산화물 반도체에 함유될 수 있다. 산화물 반도체 막으로의 결정화를 방해하는 산화 실리콘(SiO<sub>x</sub>(x>0))의 첨가는 제작 공정에서 산화물 반도체막의 형성 후에 열처리가 수행될 때 산화물 반도체막의 결정화를 억제할 수 있다. 여기서, 예를 들어, In-Ga-Zn-O계 산화물 반도체는 인듐(In), 갈륨(Ga), 및 아연(Zn)을 함유하는 산화물막을 의미하며, 그의 조성비에 특별한 제한은 없다. In-Ga-Zn-O계 산화물 반도체는 In, Ga, 및 Zn 이외의 원소를 함유할 수 있다.

[0057] 산화물 반도체막으로서, InM<sub>m</sub>O<sub>n</sub>(ZnO)<sub>m</sub>(m>0, m은 자연수가 아니다)의 화학식에 의해 표현된 박막이 이용될 수 있다. 여기서, M은 Ga, Al, Mn, 및 Co로부터 선택된 하나 이상의 금속 원소들을 나타낸다. 예를 들어, M은 Ga, Ga 및 Al, Ga 및 Mn, Ga 및 Co, 등일 수 있다.

[0058] In-Zn-O계 재료가 산화물 반도체로 이용되는 경우에, 사용된 타겟은 원자비(atomic ratio)로 In:Zn = 50:1 내지 1:2(몰 비(molar ratio)로 In<sub>2</sub>O<sub>3</sub>:ZnO = 25:1 내지 1:4), 바람직하게는 원자비로 In:Zn = 20:1 내지 1:1(몰 비로 In<sub>2</sub>O<sub>3</sub>:ZnO = 10:1 내지 1:2), 더욱 바람직하게는 In:Zn = 15:1 내지 1.5:1(몰 비로 In<sub>2</sub>O<sub>3</sub>:ZnO = 15:2 내지 3:4)의 조성비를 갖는다. 예를 들어, In:Zn:O = X:Y:Z의 원자비를 갖는 In-Zn-O계 산화물 반도체를 형성하기 위해 사용된 타겟에서, Z > 1.5X+Y의 관계가 만족된다.

[0059] 본 실시예에서 이용된 산화물 반도체는 In을 함유하는 산화물 반도체인 것이 바람직하고, In과 Ga를 함유하는 산화물 반도체인 것이 더욱 바람직하다. i-형(진성) 산화물 반도체층을 얻기 위하여, 탈수화(dehydration) 또는 탈수소화(dehydrogenation)가 효과적이다. 본 실시예에서, 스팍터링법에 의해 In-Ga-Zn-O계 산화물 타겟을 이용하여 산화물 반도체막이 형성된다.

[0060] 스팍터링법에 의해 산화물 반도체막을 형성하기 위한 타겟으로서, 예를 들면, 1:1:1[몰 비]의 조성비로 In<sub>2</sub>O<sub>3</sub>, Ga<sub>2</sub>O<sub>3</sub>, 및 ZnO를 함유하는 산화물 타겟이 In-Ga-Zn-O 막을 형성하기 위해 사용된다. 상기 타겟의 재료와 조성에는 제한이 없으며, 예를 들어, 1:1:2[몰 비]의 조성비로 In<sub>2</sub>O<sub>3</sub>, Ga<sub>2</sub>O<sub>3</sub>, 및 ZnO를 함유하는 산화물 타겟 또는 1:1:4[몰 비]의 조성비로 In<sub>2</sub>O<sub>3</sub>, Ga<sub>2</sub>O<sub>3</sub>, 및 ZnO를 함유하는 산화물 타겟이 이용될 수 있다.

[0061] 산화물 타겟의 충전률은 90%보다 높거나 같고 100%보다 낮거나 같으며, 바람직하게는 95%보다 높거나 같고 99.9%보다 낮거나 같다. 높은 충전률을 갖는 금속 산화물 타겟의 이용으로, 치밀한 산화물 반도체막이 형성될 수 있다. 또한, 타겟의 순도는 99.99%보다 높거나 같은 것이 바람직하며, 여기서 불순물들, 예를 들면, Li 또는 Na와 같은 알칼리 금속과 Ca와 같은 알칼리 토금속이 특히 감소되는 것이 바람직하다.

[0062] 산화물 반도체막의 형성시 이용된 스팍터링 가스로서, 수소, 물, 수산기, 또는 수소화물(hydride)과 같은 불순물들이 제거되는 고순도 가스가 사용되는 것이 바람직하다. 구체적으로, -60°C보다 낮거나 같은 이슬점을 갖는 고순도 가스가 바람직하다.

- [0063] 감압하의 막 형성 챔버에 기판이 위치되고, 기판 온도가 100°C보다 높거나 같고 600°C보다 낮거나 같은, 바람직하게는 200°C보다 높거나 같고 400°C보다 낮거나 같은 온도로 설정된다. 기판이 가열되는 상태에서 산화물 반도체막을 형성하는 것에 의해, 형성된 산화물 반도체막에 함유된 불순물들의 농도가 감소될 수 있다. 게다가, 스퍼터링에 의한 손상도 감소될 수 있다. 이후, 막 형성 챔버의 잔류 수분이 제거되는 동안, 수소와 수분이 제거된 스퍼터링 가스가 주입되고, 상기 타겟을 이용하여 상기 기판(500) 위에 상기 산화물 반도체막이 형성된다. 막 형성 챔버의 잔류 수분을 제거하기 위하여, 크라이오펌프, 이온 펌프, 또는 티타늄 승화 펌프와 같은 흡착 진공 펌프(entrapment vacuum pump)가 이용되는 것이 바람직하다. 배기 수단은 콜드 트랩이 제공된 터보 펌프일 수 있다. 크라이오펌프로 배기되는 막 형성 챔버에서, 예를 들면, 수소, 물과 같은 수소를 함유하는 화합물(보다 바람직하게는, 또한 탄소를 함유하는 화합물), 등이 제거되어, 막 형성 챔버에서 형성된 산화물 반도체막에 함유된 불순물들의 농도가 감소될 수 있다.

- [0064] 스퍼터링법을 위한 분위기는 희가스(전형적으로 아르곤) 분위기, 산소 분위기, 또는 희가스와 산소를 함유하는 혼합 분위기일 수 있다.

- [0065] 막 형성 조건들의 예로서, 기판과 타겟의 거리는 100mm, 압력은 0.6Pa, 직류(DC) 전원은 0.5kW이고, 분위기는 산소 분위기(산소 유량비는 100%)이다. 막 형성동안 생성된 가루 물질들(또한 입자들 또는 먼지로도 불림)이 감소될 수 있고 막 두께가 균일하게 될 수 있으므로 펄스-직류 전원이 바람직하다는 것에 주의한다.

- [0066] 또한, 스퍼터링 장치의 처리 챔버의 누설율(leakage rate)이  $1 \times 10^{-10} \text{ Pa} \cdot \text{m}^3/\text{초}$ 보다 작거나 같게 설정될 때, 스퍼터링법에 의한 형성 하에서 알칼리 금속 또는 수소화물과 같은 불순물들의 산화물 반도체막으로의 진입이 감소될 수 있다.

- [0067] 또한, 배기 시스템으로서 흡착 진공 펌프의 이용으로, 배기 시스템으로부터 알칼리 금속, 수소, 물, 수산기, 또는 수소화물과 같은 불순물들의 역류(counter flow)가 감소될 수 있다.

- [0068] 산화물 반도체층에 함유된 불순물들, 예를 들어, Li 또는 Na와 같은 알칼리 금속과 Ca와 같은 알칼리 토금속이 감소되는 것이 바람직하다는 것에 주의한다. 구체적으로, 산화물 반도체층에 함유된 Li, Na, 및 K의 불순물 농도들은 SIMS을 사용하여 측정될 때 각각  $5 \times 10^{15} \text{ cm}^{-3}$  보다 낮거나 같고, 바람직하게는  $1 \times 10^{15} \text{ cm}^{-3}$  보다 낮거나 같다.

- [0069] 알칼리 금속과 알칼리 토금속은 산화물 반도체에 대한 악성(adverse) 불순물들이며 거의 함유되지 않는 것이 바람직하다. 산화물 반도체와 접하는 절연막이 산화물일 때, 알칼리 금속, 특히, Na이 산화물에 확산되어 Na<sup>+</sup>가 된다. 또한, Na는 금속과 산소 사이의 결합을 끊거나 산화물 반도체의 결합으로 들어간다. 결과적으로, 트랜지스터 특성들의 악화(예를 들면, 임계 값의 네거티브(negative) 측으로의 시프트(트랜지스터가 노멀리 온(normally on)이 되게 함) 또는 이동도의 감소)가 유발된다. 부가적으로, 이는 또한 특성들의 변동을 유발한다. 이러한 문제는 특히 산화물 반도체의 수소 농도가 충분히 낮은 경우에 현저하다. 따라서, 알칼리 금속의 농도는 산화물 반도체에 함유된 수소의 농도가  $5 \times 10^{19} \text{ cm}^{-3}$  보다 낮거나 같은 경우에, 특히  $5 \times 10^{18} \text{ cm}^{-3}$  보다 낮거나 같은 경우에, 상기 범위에서 설정되도록 강력하게 요구된다.

- [0070] 다음, 산화물 반도체막이 제 2 포토리소그래피 단계에 의해 섬형 산화물 반도체층(513a)으로 처리된다.

- [0071] 콘택트 홀이 상기 게이트 절연층(502)에 형성되는 경우에, 상기 콘택트 홀을 형성하는 단계가 산화물 반도체막의 처리와 동시에 수행될 수 있다.

- [0072] 산화물 반도체막의 에칭은 건식 에칭, 습식 에칭, 또는 건식 에칭과 습식 에칭 모두일 수 있다는 것에 주의한다. 산화물 반도체막의 습식 에칭을 위해 이용된 에천트(etchant)로서, 예를 들면, 인산, 아세트산, 및 질산의 혼합 용액, 등이 이용될 수 있다. 게다가, ITO07N(KANTO CHEMICAL CO., INC.에 의해 제조)이 또한 이용될 수 있다. 도 2a는 본 단계의 단면도임에 주의한다.

- [0073] 건식 에칭을 위해 이용된 에칭 가스로서, 염소를 함유하는 가스(예를 들면, 염소(Cl<sub>2</sub>), 삼염화붕소(BCl<sub>3</sub>), 사염화실리콘(SiCl<sub>4</sub>), 사염화탄소(CCl<sub>4</sub>), 등)가 이용되는 것이 바람직하다. 대안적으로, 불소를 함유하는 가스(예를 들면, 사불화탄소(CF<sub>4</sub>), 육불화황(SF<sub>6</sub>), 삼불화질소(NF<sub>3</sub>), 삼불화메탄(CHF<sub>3</sub>), 등); 브롬화수소(HBr); 산소(O<sub>2</sub>); 헬륨(He) 또는 아르곤(Ar)과 같은 희가스가 첨가되는 이러한 가스들 중 임의의 가스; 등이 이용될 수 있다.

- [0074] 건식 에칭 방법으로서, 평행 평판 RIE(reactive ion etching)법 또는 ICP(inductively coupled plasma) 에칭법

이 이용될 수 있다. 막들을 원하는 모양들로 예칭할 수 있도록 하기 위하여, 예칭 조건(코일형 전극에 인가된 전력량, 기판 측 상의 전극에 인가된 전력량, 기판 측 상의 전극의 온도, 등)이 적절하게 조절된다.

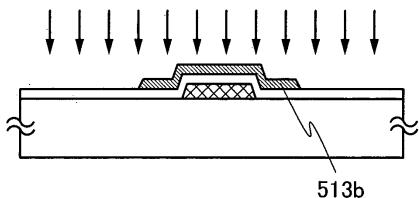

[0075] 다음, 불소가 상기 산화물 반도체층(513a)에 첨가된다. 불소의 이러한 첨가는 다음 방식으로 수행될 수 있다: 불소를 함유하는 가스가 플라즈마 상태로 만들어지고 플라즈마에 포함된 이온 종들(ion species)이 추출되고 가속되어 이온빔의 형태인 이온 종들이 산화물 반도체층으로 첨가된다. 예를 들어, 첨가된 불소 이온들의 양은  $10^{-13}$  ion/cm<sup>2</sup>보다 많거나 같을 수 있으며  $10^{-15}$  ion/cm<sup>2</sup>보다 적거나 같을 수 있다.

[0076] 불소를 함유한 가스로서, 예를 들면, 사불화탄소(CF<sub>4</sub>), 육불화황(SF<sub>6</sub>), 삼불화질소(NF<sub>3</sub>), 또는 삼불화메탄(CHF<sub>3</sub>); 헬륨 또는 아르곤과 같은 희가스가 첨가되는 이러한 가스들 중 임의의 가스; 등이 이용될 수 있다.

[0077] 본 실시예에서 불소를 첨가하는 예가 설명되었지만, 본 발명의 실시예에는 이러한 예로 제한되지 않으며, 다른 할로겐 원소들이 또한 첨가될 수 있다. 예를 들어, 염소를 함유하는 가스(예를 들면, 염소(Cl<sub>2</sub>), 삼염화붕소(BCl<sub>3</sub>), 사염화실리콘(SiCl<sub>4</sub>), 또는 사염화탄소(CCl<sub>4</sub>))를 이용하여 염소가 첨가될 수 있다.

[0078] 염소를 첨가할 때의 압력은  $10^{-4}$  Pa보다 높거나 같고  $10^2$  Pa보다 낮거나 같을 것이 바람직하다.

[0079] 플라즈마 도핑 장치의 이용으로, 불소를 첨가할 때의 압력은  $10^{-2}$  Pa보다 높거나 같고  $10^2$  Pa보다 낮거나 같을 수 있다. 플라즈마 생성 방법으로서, 유도 결합 플라즈마(ICP)법과 같은 여기(excitation)법이 채용될 수 있다. 예를 들어, ICP 여기 방법을 채용하는 플라즈마 도핑 장치가 이용되는 경우에, 고주파수 전압이 안테나와 기판 측 상의 전극 모두로 인가되고, 이후, 고주파수 플라즈마가 안테나 측 상에 생성되어, 플라즈마에 포함된 이온 종들이 기판 측 상의 전극으로 인가된 고주파수 전압에 의해 생성된 바이어스 전압에 의해 가속된다. 따라서, 이온빔 형태의 이온 종들이 상기 기판 위의 상기 산화물 반도체층으로 주입될 수 있다. 대안적으로, 불소의 첨가가 건식 예칭 장치로 유사하게 수행될 수 있다.

[0080] 예를 들어, 플라즈마 처리가 다음 조건들에서 60초 동안 수행되어 불소가 첨가될 수 있다: 삼불화질소(NF<sub>3</sub>)가 가스로 이용되고, 안테나로 인가된 전력은 600W, 기판 측 상의 전극으로 인가된 전력은 100W, 압력은 1.35Pa, 그리고 가스의 유량은 70 sccm.

[0081] 이온 도핑 장치가 이용될 때, 불소를 첨가할 때의 압력은  $10^{-3}$  Pa보다 높거나 같고  $10^{-2}$  Pa보다 낮거나 같을 수 있다. 가속 전압은 10keV보다 높거나 같고 100keV보다 낮거나 같을 수 있다. 이온 도핑 장치를 이용하여 불소를 첨가하는 경우에, 불소를 함유하는 가스가 플라즈마 상태로 만들어지고, 이온 종들이 미리 정해진 전계의 작용에 의해 플라즈마로부터 추출되며, 추출된 이온 종들이 질량 분리(mass separation) 없이 가속되어 이온빔의 형태로 산화물 반도체층으로 주입된다. 이온 도핑 장치는 이하에 서술될 이온 주입 장치보다 더 큰 면적으로 이온빔 조사가 가능하고, 따라서, 이온 도핑 장치를 이용하여 불소의 첨가가 수행될 때, 택트 시간(takt time)이 짧아질 수 있다.

[0082] 또한, 이온 주입 장치가 이용될 때, 불소를 첨가할 때의 압력은  $10^{-4}$  Pa보다 높거나 같고  $10^{-3}$  Pa보다 낮거나 같을 수 있다. 가속 전압은 100keV보다 높거나 같고 300keV보다 낮거나 같을 수 있다. 이온 주입 장치를 이용하여 불소를 첨가하는 경우에, 불소를 함유하는 가스가 플라즈마 상태로 만들어지고, 이온 종들이 플라즈마로부터 추출되고, 질량 분리가 수행되어, 미리 정해진 질량을 갖는 이온 종들이 가속되어 이온빔의 형태로 산화물 반도체층으로 주입된다. 질량 분리기를 포함하는 이온 주입 장치를 이용하여 불소의 첨가가 수행될 때, 금속 원소와 같은 불순물이 불소와 함께 산화물 반도체층으로 첨가되는 것이 방지될 수 있다.

[0083] 불소가 산화물 반도체층(513a)으로 첨가될 때, 예를 들면, 산화물 반도체의 금속과 수소 사이의 결합, 금속과 수산기 사이의 결합, 또는 금속에 결합되는 수산기의 산소와 수소 사이의 결합이 끊어질 수 있다. 산화물 반도체층(513a)은 금속으로부터 탈착되는(detached) 불순물을 포함하는 산화물 반도체층(513b)이 된다(도 2b).

[0084] 산화물 반도체층(513a)으로의 불소의 첨가 전에, 예열 처리가 그 위에서 수행되어 산화물 반도체층(513a)의 수소 또는 수분과 같은 불순물이 탈착되고 배기될 수 있다. 예열 챔버에 제공된 배기 유닛으로서, 크라이오펌프가 바람직하다는 것에 주의한다. 예열 처리의 온도는 250°C보다 높거나 같고 500°C보다 낮거나 같다. 불소의 첨가가 예열 처리 후에 수행되는 경우에, 산화물 반도체층에 포함된 불순물들의 농도가 더욱 감소될 수 있다.

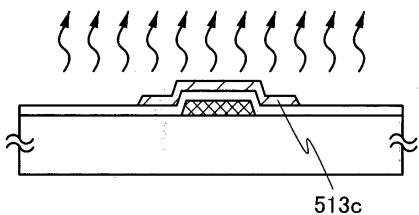

[0085] 이후, 제 1 열 처리가 금속으로부터 탈착되는 불순물을 포함하는 산화물 반도체층(513b) 상에서 수행된다. 이러

한 제 1 열 처리에 의해, 금속으로부터 탈착된 불순물이 산화물 반도체층으로부터 제거될 수 있다. 예를 들어, 첨가된 불소와 금속으로부터 탈착된 수소 또는 수산기 사이의 반응에 의해 생성되는 수소 불소화물 등이 제거될 수 있다. 생성된 수소 불소화물 등을 가열에 의해 제거하는 방법은 할로겐 원소의 첨가없이 금속에 강하게 결합되는 수소 또는 수산기를 직접 제거하는 방법(예를 들면, 고온 열 처리)보다 쉽다.

[0086] 제 1 열 처리의 온도는 250°C보다 높거나 같고 750°C보다 낮거나 같다. 본 실시예에서, 산화물 반도체층으로의 불소의 첨가가 산화물 반도체층으로부터의 불순물의 제거를 용이하게 하므로, 제 1 열 처리가 저온에서 수행될 수 있다. 상기 제 1 열 처리가 고온에서 수행되면, 처리가 단시간에 수행될 수 있다.

[0087] 여기서, 기판이 열 처리 장치들 중 하나인 전기노(electric furnace)로 도입되고, 한 시간 동안 질소 분위기 하에서 450°C의 산화물 반도체층 상에서 열 처리가 수행되어, 이후, 산화물 반도체층이 공기로 노출되지 않아 산화물 반도체층으로의 물 및 수소의 진입이 방지된다. 따라서, 산화물 반도체층(513c)이 얹어진다(도 2c).

[0088] 열 처리 장치는 전기노로 제한되지 않으며, 저항 히터(resistance heater)와 같은 히터로부터의 열 전도 또는 열 복사에 의해 물체를 가열하는 장치가 이용될 수 있다는 것에 주의한다. 예를 들어, GRTA(gas rapid thermal anneal) 장치 또는 LRTA(lamp rapid thermal anneal) 장치와 같은 RTA(rapid thermal anneal) 장치가 이용될 수 있다. LRTA 장치는 할로겐 램프, 메탈 할라이드 램프, 제논 아크 램프, 탄소 아크 램프, 고압 나트륨 램프, 또는 고압 수은 램프와 같은 램프로부터 방출된 빛(전자기파)의 복사에 의해 물체를 가열하는 장치이다. GRTA는 고온 가스를 이용한 열 처리를 위한 장치이다. 고온 가스로서, 질소, 또는 아르곤과 같은 희가스와 같은, 열 처리에 의해 물체와 반응하지 않는 불활성 가스가 이용된다. 열 처리를 위하여 RTA(rapid thermal anneal)법을 이용할 때, 탈수화 또는 탈수소화가 단시간에 수행될 수 있고; 따라서, 처리가 유리 기판의 변형점(strain point)보다 높은 온도에서도 수행될 수 있다.

[0089] 제 1 열 처리에서, 물, 수소, 등이 질소 또는 헬륨, 네온, 또는 아르곤과 같은 희가스의 분위기에 함유되지 않는 것이 바람직하다는 것에 주의한다. 열 처리 장치로 주입되는 질소 또는 헬륨, 네온, 또는 아르곤과 같은 희가스의 순도는 6N(99.9999%) 또는 그 이상이 바람직하며, 7N(99.99999%) 또는 그 이상이 바람직하다(즉, 불순물 농도는 1ppm보다 작거나 같고, 바람직하게는 0.1ppm보다 작거나 같다).

[0090] 게다가, 산화물 반도체층이 제 1 열 처리에 의해 가열된 후, 고순도 산소 가스, 고순도 N<sub>2</sub>O 가스, 또는 초건조(ultra dry) 공기(캐비티 링 다운 레이저 분광법(cavity ring down laser spectroscopy;CRDS) 시스템의 이슬점 측정기의 이용으로 측정이 수행되는 경우에, 수분량은 20ppm(이슬점으로 환산하면 -55°C)보다 적거나 같고, 바람직하게는 1ppm보다 적거나 같고, 더욱 바람직하게는 10ppb보다 적거나 같다)가 동일한 노(furnace)로 주입될 수 있다. 산소 가스와 N<sub>2</sub>O 가스는 물, 수소, 등을 포함하지 않는 것이 바람직하다. 열 처리 장치로 주입되는 산소 가스 또는 N<sub>2</sub>O 가스의 순도는 6N보다 크거나 같은 것이 바람직하며, 더욱 바람직하게는 7N보다 크거나 같다(즉, 산소 가스 또는 N<sub>2</sub>O 가스의 불순물들의 농도는 바람직하게는 1ppm보다 작거나 같고, 더욱 바람직하게는 0.1ppm보다 작거나 같다). 산소 가스 또는 N<sub>2</sub>O 가스의 반응에 의해, 산화물 반도체에 포함된 주성분들 중 하나이고 탈수화 또는 탈수소화에 의한 불순물들의 제거 단계와 동시에 감소되었던 산소가 공급되어, 산화물 반도체층이 정제되고 전기적으로 i-형(진성)인 산화물 반도체가 될 수 있다.

[0091] 불소의 첨가는 산화물 반도체막이 섬형으로 처리되기 전에 수행될 수 있다. 이러한 경우에, 제 2 포토리소그래피 단계 전 또는 후에 제 1 열 처리가 수행될 수 있다.

[0092] 제 1 열 처리는 불소의 첨가 후 및 산화물 반도체층 위에 다른 층의 형성 전에 수행되는 것이 바람직하다는 것에 주의한다. 그러나, 상기 제 1 열 처리는 그것이 불소의 첨가 다음인 한, 상기 타이밍 대신 다음 타이밍들 중 임의의 것에서 수행될 수 있다: 게이트 절연층이 상기 산화물 반도체층 위에 적층된 후; 상기 게이트 전극이 상기 게이트 절연층 위에 형성된 후.

[0093] 콘택트 홀이 게이트 절연층(502)에 형성되는 경우에, 콘택트 홀을 형성하는 단계는 제 1 열 처리가 상기 산화물 반도체막 상에 수행되기 전 또는 후에 수행될 수 있다.

[0094] 상기 단계들을 통해, 상기 산화물 반도체층의 수소의 농도가 감소될 수 있으며 상기 산화물 반도체층이 정제될 수 있다. 따라서, 상기 산화물 반도체층이 안정화될 수 있다. 게다가, 열 처리는 캐리어 밀도가 극히 낮은 넓은 밴드 갭(band gap)을 갖는 산화물 반도체막을 형성하는 것을 가능하게 한다. 따라서, 트랜지스터가 대형 크기의 기판을 이용하여 제작될 수 있고, 생산성이 증가될 수 있다. 게다가, 수소 농도가 감소된 정제된 산화물 반도체막을 이용하는 것에 의해, 높은 내전압과 극히 낮은 오프 상태 전류를 갖는 트랜지스터를 제작하는 것이 가능하

다. 상기 열 처리는 그것이 산화물 반도체층이 형성된 후에 수행되는 한, 어떠한 때라도 수행될 수 있다.

[0095] 산화물 반도체막이 가열되는 경우에, 상기 산화물 반도체막의 재료 또는 가열 조건들에 의존하긴 하지만, 일부 경우들에서, 판형(plate-shaped) 결정들이 상기 산화물 반도체막의 표면에서 형성된다는 것에 주의한다. 상기 판형 결정은 상기 산화물 반도체막의 표면과 실질적으로 수직인 방향의 c-축 배향된 판형 결정인 것이 바람직하다.

[0096] 게다가, 먼저 형성되는 산화물 반도체층과 접하는 하지 부재의 재료로 산화물, 질화물, 금속, 등 중 임의의 것이 사용될 때에라도, 산화물 반도체층으로서, 큰 두께를 갖는 결정 영역(단결정 영역), 즉, 막의 표면에 수직으로 c-축 배향되는 결정 영역을 갖는 산화물 반도체층이 막 형성을 두 번, 열 처리를 두 번 수행하는 것에 의해 형성될 수 있다. 예를 들어, 3nm 내지 15nm의 두께를 갖는 제 1 산화물 반도체막이 형성된 후에, 불소의 제 1 첨가가 수행되고, 이후 450°C보다 높거나 같고 850°C보다 낮거나 같은 온도에서, 질소, 산소, 희가스, 또는 건조 공기 대기 하에서 제 1 열 처리가 수행되어, 표면을 포함하는 영역에 결정 영역(판형 결정을 포함)을 갖는 제 1 산화물 반도체막이 형성된다. 이후, 상기 제 1 산화물 반도체막보다 큰 두께를 갖는 제 2 산화물 반도체막이 형성된 후에, 불소의 제 2 첨가가 수행되고, 이후 450°C보다 높거나 같고 850°C보다 낮거나 같은 온도에서 제 2 열 처리가 수행되어, 결정 성장의 시드(seed)로서 상기 제 1 산화물 반도체막의 사용으로 결정 성장이 윗 방향으로 진행하고 전체적인 제 2 산화물 반도체막이 결정화된다. 이 때, 불소의 제 2 첨가에 의해 불소가 상기 제 1 산화물 반도체막으로 첨가되면, 상기 제 1 산화물 반도체막의 결정성 영역은 감소되거나 없어질(lost) 수 있다. 따라서, 적절한 조건들(예를 들면, 가속 전압)을 선택하여 불소의 제 2 첨가에서 불소가 상기 제 1 산화물 반도체막으로 첨가되지 않도록 하는 것이 필요하다.

[0097] 또한, 막의 표면에 수직으로 c-축 배향되는 결정 영역을 갖는 산화물 반도체층이 산화물 반도체가 c-축 배향되는 온도로 기판이 가열되면서 산화물 반도체층을 형성하는 것에 의해 형성될 수 있다. 이러한 막 형성 방법으로, 단계들의 수는 감소될 수 있다. 기판을 가열하는 온도는 막 형성 장치에 따라 달라지는 다른 막 형성 조건들에 따라 적절하게 설정될 수 있으며; 예를 들어, 막 형성이 스퍼터링 장치로 수행될 때, 기판 온도는 250°C보다 크거나 같은 온도로 설정될 수 있다.

[0098] 다음, 소스 전극 및 드레인 전극이 되는 도전막(소스 전극 및 드레인 전극과 동일한 층에 형성된 배선을 포함하는)이 게이트 절연층(502)과 산화물 반도체층(513c) 위에 형성된다. 소스 전극과 드레인 전극으로 이용된 도전막으로서, 예를 들면, Al, Cr, Cu, Ta, Ti, Mo, 및 W로부터 선택된 원소를 함유하는 금속막, 그의 주성분으로서 상기 원소들 중 임의의 것을 함유하는 금속 질화물막(질화 티타늄막, 질화 몰리브덴막, 또는 질화 텉스텐막), 등이 이용될 수 있다. Al, Cu, 등의 금속막을 채용하는 경우에, 내열성 및 부식성의 문제들을 방지하기 위하여, Ti, Mo, W, Cr, Ta, Nd, Sc, 또는 Y와 같은 내화 금속의 막 또는 이들 내화 금속들 중 임의의 것의 금속 질화물막(질화 티타늄막, 질화 몰리브덴막, 또는 질화 텉스텐막)이 금속막의 하부층 및 상부층 중 하나 또는 모두 상에 적층될 수 있다. 특히, 상기 산화물 반도체층과 접하는 측 상에 티타늄을 함유하는 도전막을 제공하는 것이 바람직하다.

[0099] 또한, 상기 도전막은 단층 구조 또는 둘 또는 그 이상의 층들을 포함하는 적층 구조를 가질 수 있다. 예를 들어, 실리콘을 함유하는 알루미늄막의 단층 구조; 알루미늄막과 그 위에 적층된 티타늄막의 2층 구조; 티타늄막, 알루미늄막, 및 티타늄막이 이러한 순서로 적층되는 3층 구조; 등이 주어질 수 있다.

[0100] 대안적으로, 상기 도전막은 도전성 금속 산화물을 이용하여 형성될 수 있다. 도전성 금속 산화물로서, 산화 인듐, 산화 주석, 산화 아연, 산화 인듐과 산화 주석의 합금, 산화 인듐과 산화 아연의 합금, 또는 실리콘이나 산화 실리콘을 함유하는 금속 산화물 재료들 중 임의의 것이 사용될 수 있다.

[0101] 상기 도전막이 형성된 후 열 처리가 수행되는 경우에, 상기 도전막은 열 처리를 견디기에 충분히 높은 내열성을 갖는 것이 바람직하다는 것에 주의한다.

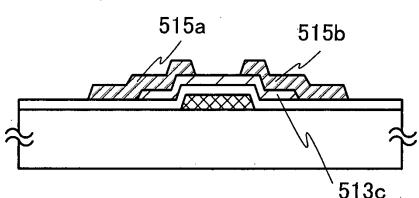

[0102] 레지스트 마스크가 제 3 포토리소그래피 단계에 의해 상기 도전막 위에 형성되고, 각각이 소스 또는 드레인 전극으로 기능하는 제 1 전극(515a)과 제 2 전극(515b)이 선택적인 에칭에 의해 형성되며, 이후 상기 레지스트 마스크가 제거된다(도 2d).

[0103] 제 3 포토리소그래피 단계에서 상기 레지스트 마스크 형성시 자외선 광, KrF 레이저 광, 또는 ArF 레이저 광을 이용하여 광 노출이 수행될 수 있다. 나중에 형성될 트랜지스터의 채널 길이(L)는, 산화물 반도체층(513c) 위에서 서로 인접한 제 1 전극과 제 2 전극의 하단부들(bottom end portions) 사이의 거리에 의해 결정된다. 25nm보다 작은 채널 길이(L)에 대해 광 노출이 수행되는 경우에, 상기 제 3 포토리소그래피 단계에서 상기 레지스트

마스크 형성시에 몇 나노미터 내지 몇십 나노미터의 극히 짧은 파장을 갖는 초자외선 광을 이용하여 광 노출이 수행될 수 있다. 초자외선 광에 의한 광 노출시, 해상도가 높고 초점 심도(focus depth)가 크다. 따라서, 나중에 형성될 트랜지스터의 채널 길이(L)는 10nm 내지 1000nm가 될 수 있고, 따라서 회로의 동작 속도가 증가될 수 있다.

[0104] 포토리소그래피 단계에서 이용된 포토마스크들의 수를 감소시키고 포토리소그래피 단계들의 수를 감소시키기 위하여, 광이 이를 통해 다양한 강도들을 갖도록 투과되는 광 노출 마스크인 멀티톤(multi-tone) 마스크를 이용하여 형성된 레지스트 마스크의 사용으로 에칭 단계가 수행될 수 있다. 상기 멀티톤 마스크의 이용으로 형성된 레지스트 마스크는 복수의 두께들을 갖고 또한 에칭에 의해 모양이 변화될 수 있으며; 따라서, 레지스트 마스크가 상이한 패턴들로의 처리를 위한 복수의 에칭 단계들에서 사용될 수 있다. 따라서, 적어도 두 종류들의 상이한 패턴들에 대응하는 레지스트 마스크가 하나의 멀티톤 마스크에 의해 형성될 수 있다. 그러므로, 광 노출 마스크들의 수가 감소될 수 있고 대응하는 포토리소그래피 단계들의 수가 또한 감소될 수 있으며, 따라서 절차의 간략화가 구현될 수 있다.

[0105] 도전막이 에칭될 때 산화물 반도체층(513c)을 에칭하거나 분할하지 않도록 에칭 조건들이 최적화되는 것이 바람직하다는 것에 주의한다. 그러나, 단지 도전막 만이 에칭되고 산화물 반도체층(513c)은 전혀 에칭되지 않는 에칭 조건들을 얻는 것은 힘들다. 일부 경우들에서, 상기 도전막이 에칭될 때, 산화물 반도체층(513c)의 일부만이 에칭되어 홈(groove) 부분(오목한 부분)을 갖는 산화물 반도체층(513c)이 된다.

[0106] 본 실시예에서, Ti막이 도전막으로 이용되고 In-Ga-Zn-O계 산화물 반도체막이 상기 산화물 반도체층(513c)으로 이용된다. 이러한 조합의 경우에, 암모늄 과산화수소수 혼합물(암모니아, 물, 및 과산화수소수 용액의 혼합액)이 에천트로 이용되어, 도전막이 선택적으로 에칭될 수 있다.

[0107] 다음, 산화물 반도체층의 노출부의 표면으로 흡수된 물 등이 N<sub>2</sub>O, N<sub>2</sub>, 또는 Ar과 같은 가스를 이용하여 플라즈마 처리에 의해 제거될 수 있다. 대안적으로, 플라즈마 처리는 산소와 아르곤의 혼합 가스를 이용하여 수행될 수 있다. 플라즈마 처리가 수행되는 경우에, 산화물 반도체층의 일부와 접하는 보호 절연막이 되는 절연층(507)이 공기로의 노출없이 형성된다.

[0108] 절연층(507)은 수분, 수소, 및 산소와 같은 불순물들을 가능한 한 거의 함유하지 않는 것이 바람직하며, 단층의 절연막 또는 적층된 복수의 절연막들을 이용하여 형성될 수 있다.

[0109] 절연층(507)은 물과 수소와 같은 불순물들이 상기 절연층(507)으로 진입하지 않는, 스퍼터링법과 같은 적절한 방법에 의해 적어도 1nm의 두께로 형성될 수 있다. 수소가 상기 절연층(507)에 함유될 때, 산화물 반도체층으로의 수소의 진입 또는 수소에 의한 산화물 반도체층에서의 산소의 추출이 유발되고, 따라서 산화물 반도체층의 백채널(backchannel)은 n-형(더 낮은 저항을 갖는)이 되며; 따라서, 기생 채널이 형성될 수 있다. 따라서, 가능한 한 거의 수소를 함유하지 않는 상기 절연층(507)을 형성하기 위해 수소가 이용되지 않는 막 형성 방법이 채용되는 것이 중요하다.

[0110] 높은 배리어 특성을 갖는 재료를 이용하여 절연층(507)이 형성되는 것이 바람직하다. 예를 들어, 질화실리콘막, 질화산화 실리콘막, 질화 알루미늄막, 질화산화 알루미늄막, 산화 알루미늄막, 산화 갈륨막, 등이 높은 배리어 특성을 갖는 절연막으로 이용될 수 있다. 높은 배리어 특성을 갖는 절연막이 이용될 때, 수분 또는 수소와 같은 불순물이 섬형 산화물 반도체층(513b), 게이트 절연층(502), 상기 섬형 산화물 반도체층(513b)과 다른 절연층 사이의 계면, 및 그의 부근으로 진입하는 것이 방지될 수 있다.

[0111] 절연층(507)으로 산화 실리콘막, 산화질화 실리콘막, 산화질화 알루미늄막, 등을 이용하는 것이 또한 바람직하다.

[0112] 예를 들어, 스퍼터링법에 의해 형성된 100nm의 두께를 갖는 산화 알루미늄막이 스퍼터링법에 의해 형성된 200nm의 두께를 갖는 산화 갈륨막 위에 적층되는 구조를 갖는 절연막이 형성될 수 있다. 막 형성 동안의 기판 온도는 실온보다 높거나 같고 300°C보다 낮거나 같은 범위 내에 있을 수 있다. 또한, 절연막은 화학량론비를 초과하는 더 많은 산소를 함유하는 것이 바람직하며, 화학량론비의 1배보다 크고 2배보다 작은 비율인 것이 바람직하다. 절연막이 이러한 방식으로 과잉 산소를 함유하는 경우에, 산소가 상기 산화물 반도체막(513b)과의 계면으로 공급될 수 있고; 따라서, 산소 결손이 감소될 수 있다.

[0113] 본 실시예에서, 스퍼터링법에 의해 절연층(507)으로서 산화 실리콘막이 200nm의 두께로 형성된다. 막 형성 동안의 기판 온도는 실온보다 높거나 같고 300°C보다 낮거나 같은 범위에 있을 수 있으며 본 실시예에서는 100°C로

설정된다. 산화 실리콘막이 희가스(전형적으로, 아르곤) 분위기, 산소 분위기, 또는 희가스와 산소를 함유하는 혼합 분위기 하에서 스퍼터링법에 의해 형성될 수 있다. 타겟으로서, 산화 실리콘 타겟 또는 실리콘 타겟이 이용될 수 있다. 예를 들어, 산소를 함유하는 분위기 하에서 스퍼터링법에 의해 실리콘 타겟을 이용하여 산화 실리콘막이 형성될 수 있다.

[0114] 산화물 반도체막의 막 형성과 동시에 절연층(507)의 막 형성 챔버의 잔류 수분을 제거하기 위하여, 흡착 진공 펌프(크라이오펌프와 같은)가 이용되는 것이 바람직하다. 크라이오펌프를 이용하여 배기된 막 형성 챔버에서 절연층(507)이 형성될 때, 절연층(507)의 불순물 농도가 감소될 수 있다. 게다가, 절연층(507)의 막 형성 챔버의 잔류 수분을 제거하기 위한 배기 유닛으로서, 콜드 트랩이 제공된 터보 펌프가 이용될 수 있다.

[0115] 수소, 물, 수산기, 또는 수소화물과 같은 불순물들이 제거된 고순도 가스가 절연층(507)의 막 형성을 위한 스퍼터링 가스로 이용되는 것이 바람직하다.

[0116] 다음, 제 2 열 처리(산화물 반도체층의 막 형성 및 열 처리가 각각 두번씩 수행되는 경우에는 제 3 열 처리)가 불활성 가스 분위기 또는 산소 가스 분위기에서 수행될 수 있다. 열 처리는 질소, 초건조 공기, 또는 희가스(아르곤, 헬륨, 등)의 분위기하에서 바람직하게는 200°C보다 높거나 같고 400°C보다 낮거나 같은 온도에서 수행된다. 가스에서의 물의 함유량은 20ppm보다 적거나 같은 것이, 바람직하게는 1ppm보다 적거나 같은 것이, 더욱 바람직하게는 10ppb보다 적거나 같은 것이 바람직하다. 대안적으로, RTA 처리가 제 1 열 처리에서와 같이 단시간 동안 고온에서 수행될 수 있다. 상기 제 1 열 처리에 의해 상기 산화물 반도체층(513c)에서 산소 결손이 생성되는 때에라도, 산소를 함유한 절연층(507)이 제공된 후에 열 처리를 수행하는 것에 의해, 상기 절연층(507)으로부터 상기 산화물 반도체층(513c)으로 산소가 공급된다. 이후, 산소를 상기 산화물 반도체층(513c)으로 공급하는 것에 의해, 도너(donor)가 되는 산소 결손이 상기 산화물 반도체층(513c)에서 감소되고 화학량론비가 만족될 수 있다. 결과적으로, 상기 산화물 반도체층(513c)이 실질적으로 i-형이 되도록 만들어질 수 있으며 산소 결손으로 인한 트랜지스터의 전기적 특성들의 변동이 감소될 수 있고, 이는 전기적 특성들의 개선을 가져온다. 이러한 제 2 열 처리의 타이밍은 그것이 상기 절연층(507)의 형성 후인 한 특별히 제한되지 않으며, 이러한 제 2 열 처리는 수지막의 형성을 위한 열 처리 또는 투광성 도전막의 저항의 감소를 위한 열 처리와 같은 다른 단계와의 더블링(doubling)에 의해 단계들의 수를 증가시키지 않고도 수행될 수 있어서, 상기 산화물 반도체층(513c)이 실질적으로 i-형이 되도록 만들어질 수 있다.

[0117] 또한, 산소 분위기 하에서 산화물 반도체층(513c)이 열 처리를 거치도록 하는 것에 의해 상기 산화물 반도체층(513c)에서 도너가 되는 산소 결손이 감소될 수 있으며 산소가 산화물 반도체로 첨가된다. 열 처리는, 예를 들면, 100°C보다 높거나 같고 350°C보다 낮은, 바람직하게는 150°C보다 높거나 같고 250°C보다 낮은 온도에서 수행된다. 산소 분위기 하에서 열 처리를 위해 이용된 산소 가스는 물, 수소, 등을 포함하지 않는 것이 바람직하다. 대안적으로, 열 처리 장치로 주입되는 산소 가스의 순도는 바람직하게는 6N(99.9999%)보다 높거나 같고, 바람직하게는 7N(99.99999%)보다 높거나 같은 것이 바람직하다(즉, 산소의 불순물 농도는 1ppm보다 작거나 같고, 바람직하게는 0.1ppm보다 작거나 같다).

[0118] 본 실시예에서, 제 2 열 처리(바람직하게 200°C보다 높거나 같고 400°C보다 낮거나 같은 온도에서, 예를 들면, 250°C보다 높거나 같고 350°C보다 낮거나 같은 온도에서)가 불활성 가스 분위기 또는 산소 가스 분위기 하에서 수행된다. 예를 들어, 상기 제 2 열 처리가 질소 분위기 하에서 250°C에서 1시간 동안 수행된다.

[0119] 제 2 열 처리는 다음 효과를 갖는다. 상기 제 1 열 처리에 의해, 일부 경우들에서, 수소, 수분, 수산기, 또는 수소화물(또한 수소 화합물로도 불림)과 같은 불순물이 산화물 반도체층으로부터 의도적으로 제거되고, 산화물 반도체의 주성분들 중 하나인 산소가 감소된다. 상기 제 2 열 처리가 상기 제 1 열 처리를 거친 산화물 반도체층으로 산소를 공급하기 때문에, 상기 산화물 반도체층이 전기적으로 i-형(진성) 반도체가 되도록 정제된다.

[0120] 상술된 바와 같이, 불소가 산화물 반도체막으로 첨가되고 불소가 산화물 반도체막으로 첨가된 후에 제 1 열 처리가 수행되어, 수소, 수분, 수산기, 또는 수소화물(또한 수소 화합물로도 불림)과 같은 불순물들이 산화물 반도체층으로부터 의도적으로 제거될 수 있다. 따라서, 상기 산화물 반도체층이 전기적으로 i-형(진성) 또는 실질적으로 i-형 반도체층이 되도록 정제된다. 상기 공정을 통해, 트랜지스터(550)가 형성된다.

[0121] 일부 경우들에서, 본 실시예의 트랜지스터는 산화물 반도체층에 할로겐 원소를 포함할 수 있다. 상기 산화물 반도체층의 할로겐 원소가 금속 원자 상의 맹글링 결합으로 쉽게 결합하여 맹글링 결합이 종결되므로, 캐리어들의 생성이 감소될 수 있다. 예를 들어, 산화물 반도체층은  $10^{15}$  atoms/cm<sup>3</sup>보다 높거나 같고  $10^{18}$  atoms/cm<sup>3</sup>보다 낮거나 같은 농도로 불소를 포함할 수 있다.

- [0122] 많은 결함(defect)들을 갖는 산화 실리콘층이 절연층(507)으로 이용될 때, 산화 실리콘층의 형성 후의 제 2 열 처리는 산화물 반도체층에 함유된 수소 또는 수분과 같은 불순물들을 산화 실리콘층으로 확산시키는 효과를 가져서, 상기 산화물 반도체층에 함유된 불순물이 더욱 감소될 수 있다.

- [0123] 과잉 산소를 포함하는 산화 실리콘층이 절연층(507)으로 이용되는 경우에, 상기 절연층(507)의 형성 후에 수행되는 열 처리는 상기 절연층(507)의 산소를 산화물 반도체층(513b)으로 이동시키고, 상기 산화물 반도체층(513b)의 산소 농도를 개선시키며 상기 산화물 반도체층(513b)을 정제하는 효과를 갖는다.

- [0124] 보호 절연층(508)이 절연층(507) 위에 부가적으로 형성될 수 있다. 상기 보호 절연층(508)은 예를 들면, RF 스퍼터링법에 의해 형성된다. RF 스퍼터링법은 높은 대량 생산성을 가지므로, 상기 보호 절연층의 막 형성 방법으로 이용되는 것이 바람직하다. 상기 보호 절연층으로서, 수분과 같은 불순물들을 함유하지 않고 외부로부터 불순물들의 침입을 막는 무기 절연막이 이용되고; 예를 들면, 질화 실리콘막 또는 질화 알루미늄막이 이용된다. 본 실시예에서, 상기 보호 절연층(508)은 질화 실리콘막을 이용하여 형성된다(도 2e).

- [0125] 본 실시예에서, 보호 절연층(508)으로서, 절연층(507)까지 층들이 형성된 기판(500)을 100°C 내지 400°C의 온도로 가열하고, 수소와 수분이 제거된 고순도 질소를 함유하는 스퍼터링 가스를 주입하고, 실리콘 반도체의 타겟을 이용하는 것에 의해 질화 실리콘막이 형성된다. 이러한 경우에 또한, 상기 절연층(507)의 것과 유사한 방식으로 상기 보호 절연층(508)의 형성에서 처리 챔버의 잔류 수분이 제거되는 것이 바람직하다.

- [0126] 보호 절연층의 형성 후에, 대기에서 100°C보다 높거나 같고 200°C보다 낮거나 같은 온도로 1시간 내지 30시간 동안 열 처리가 또한 수행될 수 있다. 이러한 열 처리는 고정된 가열 온도에서 수행될 수 있다. 대안적으로, 가열 온도의 다음 변화가 복수회 반복적으로 수행될 수 있다: 가열 온도가 실온으로부터 100°C보다 높거나 같고 200°C보다 낮거나 같은 온도로 증가되고 이후 실온으로 감소된다.

- [0127] 본 실시예를 이용하여 제작된 정제된 산화물 반도체층을 포함하는 트랜지스터는 임계 전압의 작은 변동을 갖는다. 따라서, 본 실시예에서 예로 설명된 반도체 장치의 제작 방법을 이용하여, 매우 신뢰할 수 있는 반도체 장치가 제공될 수 있다. 또한, 높은 대량 생산성으로 제작될 수 있는 반도체 장치가 제공될 수 있다.

- [0128] 또한, 오프 상태 전류가 감소될 수 있기 때문에 낮은 전력 소비를 갖는 반도체 장치가 제공될 수 있다.

- [0129] 본 실시예는 본 명세서에서 설명된 다른 실시예들 중 임의의 것과 적절하게 조합될 수 있다.

- [0130] (실시예 2)

- [0131] 본 실시예에서, 불순물들을 제거하기 위해 불소를 산화물 반도체층으로 첨가하고 이후 산화물 반도체층을 열 처리를 거치게 하는 것에 의해 산화물 반도체층을 정제하는 방법을 이용한 탑 게이트(top gate) 트랜지스터의 제작 방법이 도 3a 및 도 3b와 도 4a 내지 도 4e를 참조하여 설명될 것이다.

- [0132] 도 3a 및 도 3b는 본 실시예에서 제작되는 탑 게이트형 트랜지스터(650)의 구조를 도시한다. 도 3a는 상기 트랜지스터(650)의 평면도이고, 도 3b는 상기 트랜지스터(650)의 단면도이다. 도 3b는 도 3a의 선(Q1-Q2)에 따라 얻어진 단면도에 대응한다는 것에 주의한다.

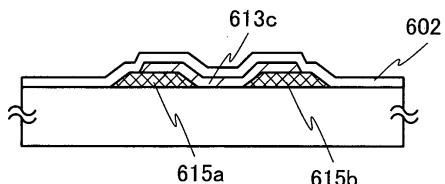

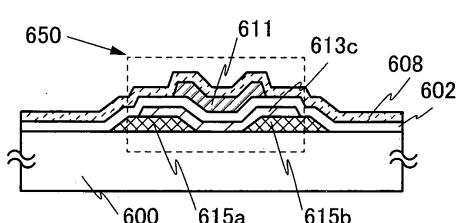

- [0133] 트랜지스터(650)에서, 절연 표면을 갖는 기판(600) 위에, 각각이 소스 또는 드레인 전극으로 기능하는 제 1 전극(615a)과 제 2 전극(615b)이 제공된다. 상기 제 1 전극(615a)과 상기 제 2 전극(615b)의 단부들을 덮는 정제된 산화물 반도체층(613c)과, 산화물 반도체층(613c)을 덮는 게이트 절연층(602)이 제공된다. 게다가, 게이트 절연층(602)과 접하고 상기 제 1 전극(615a) 및 상기 제 2 전극(615b)의 단부들과 중첩하는 게이트 전극(611)과, 상기 게이트 전극(611)과 접하고 상기 트랜지스터(650)를 덮는 보호 절연층(608)이 제공된다.

- [0134] 다음, 기판(600) 위에 트랜지스터(650)를 제작하는 방법이 도 4a 내지 도 4e를 참조하여 설명될 것이다.

- [0135] 다음, 소스 전극 및 드레인 전극이 되는 도전막(상기 소스 전극 및 상기 드레인 전극과 동일한 층에 형성된 배선을 포함하는)이 절연 표면을 갖는 기판(600) 위에 형성된다. 소스 전극과 드레인 전극으로 이용된 도전막으로서, 예를 들면, Al, Cr, Cu, Ta, Ti, Mo, 및 W로부터 선택된 원소를 함유하는 금속막 또는 그의 주성분으로서 상기 원소들 중 임의의 것을 함유하는 금속 질화물막(질화 티타늄막, 질화 몰리브덴막, 또는 질화 텉스텐막)이 이용될 수 있다. Al, Cu, 등의 금속막을 채용하는 경우에, Ti, Mo, W, Cr, Ta, Nd, Sc, 또는 Y와 같은 내화 금속의 막 또는 이를 내화 금속들 중 임의의 것의 금속 질화물막(질화 티타늄막, 질화 몰리브덴막, 또는 질화 텉스텐막)이 금속막의 하부층 및 상부층 중 하나 또는 모두 상에 적층될 수 있다. 특히, 산화물 반도체층과 접하는 층 상에 티타늄을 함유하는 도전막을 제공하는 것이 바람직하다.

- [0136] 레지스트 마스크가 제 1 포토리소그래피 단계에 의해 도전막 위에 형성되고, 각각이 소스 또는 드레인 전극으로 기능하는 제 1 전극(615a)과 제 2 전극(615b)이 선택적인 에칭에 의해 형성되며, 이후 레지스트 마스크가 제거된다.

- [0137] 본 실시예에서, 유리 기판이 절연 표면을 갖는 기판(600)으로 이용된다.

- [0138] 기저막이 되는 절연막이 기판(600)과 제 1 전극(615a) 및 제 2 전극(615b) 사이에 제공될 수 있다. 상기 기저막은 상기 기판(600)으로부터 불순물 원소의 확산을 방지하는 기능을 가지며, 질화 실리콘막, 산화 실리콘막, 질화산화 실리콘막, 및 산화질화 실리콘막의 하나 또는 그 이상을 포함하는 단층 구조 또는 적층 구조를 갖도록 형성될 수 있다.

- [0139] 다음, 2nm보다 크거나 같고 200nm보다 작거나 같은, 바람직하게는 5nm보다 크거나 같고 30nm보다 작거나 같은 두께를 갖는 산화물 반도체막이 각각이 소스 또는 드레인 전극이 되는 제 1 전극(615a) 및 제 2 전극(615b) 위에 형성된다.

- [0140] 스퍼터링법에 의해 산화물 반도체막이 형성되기 전에, 제 1 전극(615a) 및 제 2 전극(615b)의 표면들과, 기판(600)의 노출부의 절연 표면 상에 부착되는 가루 물질들(또한 입자들 또는 먼지로 불림)이 아르곤 가스가 주입되고 플라즈마가 생성되는 역 스퍼터링에 의해 제거되는 것이 바람직하다는 것에 주의한다.

- [0141] 본 실시예에서 설명된 산화물 반도체막이 실시예 1에서 설명된 산화물 반도체막의 것과 유사한 재료, 방법, 및 조건들을 이용하여 형성될 수 있다. 구체적으로, 산화물 반도체막을 위해 이용된 산화물 반도체, 막 형성 방법, 타겟 구성, 타겟 충전률, 스퍼터링 가스의 순도, 막 형성 동안의 기판 온도, 스퍼터링 장치의 배기 유닛, 스퍼터링 가스의 구성, 등이 실시예 1의 것과 유사할 수 있다. 따라서, 실시예 1이 상세한 설명들을 위해 참조될 것이다.

- [0142] 다음, 산화물 반도체막이 제 2 포토리소그래피 단계에 의해 섬형 산화물 반도체층(613a)으로 처리된다.

- [0143] 산화물 반도체막의 에칭은 건식 에칭, 습식 에칭, 또는 건식 에칭과 습식 에칭 모두일 수 있다는 것에 주의한다. 산화물 반도체막의 습식 에칭을 위해 이용된 에센트로서, 예를 들면, 인산, 아세트산, 및 질산의 혼합 용액, 등이 이용될 수 있다. 또한, ITO07N(KANTO CHEMICAL CO., INC.에 의해 제조)이 또한 이용될 수 있다. 도 4a는 본 단계의 단면도임에 주의한다.

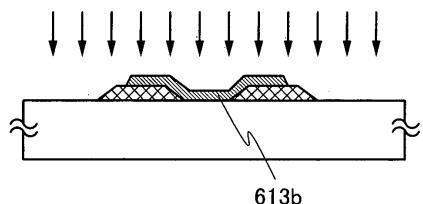

- [0144] 다음, 불소가 산화물 반도체층(613a)으로 첨가된다. 실시예 1의 것과 유사한 재료, 방법, 및 조건이 불소의 첨가에 적용될 수 있다. 따라서, 상세한 설명들을 위하여, 실시예 1이 참조될 수 있다. 불소가 상기 산화물 반도체층(613a)으로 첨가될 때, 예를 들면, 산화물 반도체의 금속과 수소 사이의 결합, 금속에 결합되는 수산기의 산소와 수소 사이의 결합, 또는 금속과 수산기 사이의 결합이 끊어질 수 있다. 상기 산화물 반도체층(613a)은 금속으로부터 탈착되는 불순물을 포함하는 산화물 반도체층(613b)이 된다(도 4b).

- [0145] 실시예 1에서와 같이, 산화물 반도체층(613a)으로의 불소의 첨가 전에 예열 처리가 수행될 수 있다.

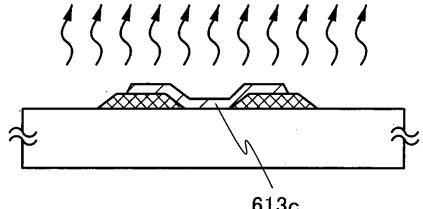

- [0146] 이후, 제 1 열 처리가 금속으로부터 탈착되는 불순물을 포함하는 산화물 반도체층(613b) 상에 수행된다(도 4c). 실시예 1의 것과 유사한 방법 및 조건이 상기 제 1 열 처리에 적용될 수 있다. 따라서, 상세한 설명들을 위하여, 실시예 1이 참조될 수 있다. 이러한 제 1 열 처리에 의하여, 금속으로부터 탈착된 불순물이 상기 산화물 반도체층(613b)으로부터 제거될 수 있다. 예를 들어, 첨가된 불소와 금속으로부터 탈착된 수소 또는 수산기 사이의 반응에 의해 생성되는 수소 불소화물 등이 제거될 수 있다. 생성된 수소 불소화물 등을 가열에 의해 제거하는 방법은 할로겐 원소의 첨가 없이 금속에 강하게 결합되는 수소 또는 수산기를 직접 제거하는 방법보다 쉽다.

- [0147] 산화물 반도체막이 섬형으로 처리되기 전에 불소의 첨가가 수행될 수 있다. 이러한 경우에, 제 2 포토리소그래피 단계 전 또는 후에 제 1 열 처리가 수행될 수 있다.

- [0148] 제 1 열 처리는 불소의 첨가 후 산화물 반도체층 위에 다른 층의 형성 전에 수행되는 것이 바람직하다는 것에 주의한다. 그러나, 제 1 열 처리는 그것이 불소의 첨가 후인 한 상기 타이밍 대신 다음 타이밍들 중 임의의 것에서 수행될 수 있다: 게이트 절연층이 상기 산화물 반도체층 위에 적층된 후; 및 게이트 전극이 상기 게이트 절연층 위에 형성된 후.

- [0149] 게다가, 산화물 반도체층으로서, 산화물, 질화물, 금속, 등 중 임의의 것이 먼저 형성되는 산화물 반도체층과 접하는 하지 부재의 재료로 이용되는 때에라도, 큰 두께를 갖는 결정 영역(단결정 영역), 즉, 막의 표면에 수직

하게 c-축 배향되는 결정 영역을 갖는 산화물 반도체층이 두번의 막 형성과 두번의 열 처리를 수행하는 것에 의해 형성될 수 있다. 결정 영역을 갖는 상기 산화물 반도체층이 실시예 1에서 설명된 형성 조건들 하에서 형성될 수 있다. 따라서, 상세한 설명들을 위하여, 실시예 1이 참조될 수 있다.

[0150] 다음, 산화물 반도체층의 노출부의 표면으로 흡수된 물 등이 N<sub>2</sub>O, N<sub>2</sub>, 또는 Ar과 같은 가스를 이용하여 플라즈마 처리에 의해 제거될 수 있다. 산화물 반도체층과 접하는 게이트 절연층(602)이 플라즈마 처리 후에 대기로의 노출 없이 형성된다.

[0151] 본 실시예의 산화물 반도체로서, 불순물들이 제거된 i-형 또는 실질적으로 i-형 산화물 반도체가 이용된다. 이러한 정제된 산화물 반도체는 계면 상태 밀도와 계면 전하에 극히 민감하고; 따라서, 산화물 반도체층과 게이트 절연층 사이의 계면이 중요하다. 그러한 이유로, 정제된 산화물 반도체층과 접하는 게이트 절연층은 고품질을 가질 필요가 있다.

[0152] 게이트 절연층(602)이 물과 수소와 같은 불순물들이 게이트 절연층(602)으로 진입하지 않는, 스퍼터링법과 같은, 적절한 방법에 의해 적어도 1nm의 두께로 형성될 수 있다. 수소가 게이트 절연층(602)에 함유될 때, 산화물 반도체층으로의 수소의 진입 또는 수소에 의한 산화물 반도체층에서의 산소의 추출이 유발되고, 따라서 산화물 반도체층의 채널이 n-형(저저항화됨)이 되며; 따라서, 기생 채널이 형성될 수 있다. 그러므로, 가능한 한 거의 수소를 함유하지 않는 게이트 절연층(602)을 형성하기 위하여 수소가 이용되지 않는 막 형성 방법이 이용되는 것이 중요하다.

[0153] 본 실시예에서, 스퍼터링법에 의해 게이트 절연층(602)으로서 산화 실리콘막이 형성된다. 막 형성 동안의 기관온도는 실온보다 높거나 같고 300°C보다 낮거나 같은 범위에 있을 수 있으며 본 실시예에서는 100°C로 설정된다. 산화 실리콘막이 희가스(전형적으로, 아르곤) 분위기, 산소 분위기, 또는 희가스와 산소를 함유하는 혼합 분위기 하에서 스퍼터링법에 의해 형성될 수 있다. 타겟으로서, 산화 실리콘 타겟 또는 실리콘 타겟이 이용될 수 있다. 예를 들어, 산소를 함유하는 분위기 하에서 스퍼터링법에 의해 실리콘 타겟을 이용하여 산화 실리콘막이 형성될 수 있다. 산화물 반도체층과 접하여 형성되는 게이트 절연층(602)으로서, 수분 또는 수소와 같은 불순물들을 포함하지 않고 외부로부터 이러한 불순물들의 진입을 막는 무기 절연막이 이용된다. 전형적으로, 산화 실리콘막, 산화질화 실리콘막, 산화 알루미늄막, 산화질화 알루미늄막, 등이 이용된다.

[0154] 산화물 반도체막의 막 형성과 동시에 게이트 절연층(602)의 막 형성 챔버에서 잔류 수분을 제거하기 위하여, 흡착 진공 펌프(크라이오펌프와 같은)가 이용되는 것이 바람직하다. 크라이오펌프를 이용하여 배기된 막 형성 챔버에서 상기 게이트 절연층(602)이 형성될 때, 상기 게이트 절연층(602)의 불순물 농도가 감소될 수 있다. 게다가, 상기 게이트 절연층(602)의 막 형성 챔버의 잔류 수분을 제거하기 위한 배기 유닛으로서, 콜드 트랩이 제공된 터보 펌프가 이용될 수 있다.

[0155] 수소, 물, 수산기, 또는 수소화물과 같은 불순물들이 제거되는 고순도 가스가 게이트 절연층(602)의 막 형성을 위한 스퍼터링 가스로 이용되는 것이 바람직하다. 도 4d는 본 단계의 단면도임에 주의한다.

[0156] 다음, 게이트 절연층(602)에 콘택트 홀을 형성하는 경우에, 콘택트 홀이 제 3 포토리소그래피 단계에 의해 게이트 절연층(602)에 형성된다. 콘택트 홀은 도 4e에 도시되지 않는다는 것에 주의한다.

[0157] 이후, 도전막이 게이트 절연층(602) 위에 형성되고, 게이트 전극(611)을 포함하는 배선층이 제 4 포토리소그래피 단계를 통해 형성된다.

[0158] 게이트 전극(611)이 몰리브덴, 티타늄, 탄탈, 텅스텐, 알루미늄, 구리, 네오디뮴, 또는 스칸듐과 같은 금속 재료 또는 그의 주성분으로서 이러한 재료들 중 임의의 것을 함유하는 합금 재료를 이용하여 단층 구조 또는 적층 구조를 갖도록 형성될 수 있다. 상술된 공정을 통하여, 트랜지스터(650)가 형성된다.

[0159] 일부 경우들에서, 본 실시예의 트랜지스터는 산화물 반도체층에 할로겐 원소를 포함할 수 있다. 산화물 반도체층의 할로겐 원소가 금속 원자 상의 댕글링 결합으로 쉽게 결합하고 상기 댕글링 결합이 종결되므로, 캐리어들의 생성이 감소될 수 있다.

[0160] 보호 절연층(608)이 게이트 전극(611) 위에 형성될 수 있다. 예를 들어, 상기 보호 절연층(608)이 RF 스퍼터링 법에 의해 형성된다. 상기 RF 스퍼터링법은 높은 대량 생산성을 이를 수 있으므로, 상기 보호 절연층의 형성 방법으로 바람직하다. 상기 보호 절연층으로서, 수분과 같은 불순물들을 함유하지 않고 외부로부터 불순물들의 진입을 막는 무기 절연막이 이용되고; 예를 들면, 질화 실리콘막 또는 질화 알루미늄막이 이용된다. 본 실시예에서, 상기 보호 절연층(608)으로서 질화 실리콘막이 형성된다. 도 4e는 본 단계의 단면도이다.

- [0161] 본 실시예에서, 보호 절연층(608)으로서, 게이트 전극(611)까지 층들이 형성된 기판(600)을 100°C 내지 400°C의 온도로 가열하고, 수소와 수분이 제거된 고순도 질소를 함유하는 스퍼터링 가스를 주입하고, 실리콘 반도체의 타겟을 이용하는 것에 의해 질화 실리콘막이 형성된다. 이러한 경우에 또한, 게이트 절연층(602)의 것과 유사한 방식으로 상기 보호 절연층(608)의 형성에서 처리 챔버의 잔류 수분이 제거되는 것이 바람직하다.

- [0162] 보호 절연층의 형성 후에, 대기중에서 100°C보다 높거나 같고 200°C보다 낮거나 같은 온도로 1시간 내지 30시간 동안 열 처리가 또한 수행될 수 있다. 이러한 열 처리는 고정된 가열 온도에서 수행될 수 있다. 대안적으로, 가열 온도의 다음 변화가 복수회 반복적으로 수행될 수 있다: 가열 온도가 실온으로부터 100°C보다 높거나 같고 200°C보다 낮거나 같은 온도로 증가되고 이후 실온으로 감소된다.

- [0163] 본 실시예를 이용하여 제작된 정제된 산화물 반도체층을 포함하는 트랜지스터는 임계 전압의 작은 변동을 갖는다. 따라서, 본 실시예에서 예로 설명된 반도체 장치의 제작 방법을 이용하여, 매우 신뢰할 수 있는 반도체 장치가 제공될 수 있다. 또한, 높은 대량 생산성으로 제작될 수 있는 반도체 장치가 제공될 수 있다.

- [0164] 또한, 오프 상태 전류가 감소될 수 있기 때문에 낮은 전력 소비를 갖는 반도체 장치가 제공될 수 있다.

- [0165] 본 실시예는 본 명세서에서 설명된 다른 실시예들 중 임의의 것과 적절하게 조합될 수 있다.

- [0166] (실시예 3)

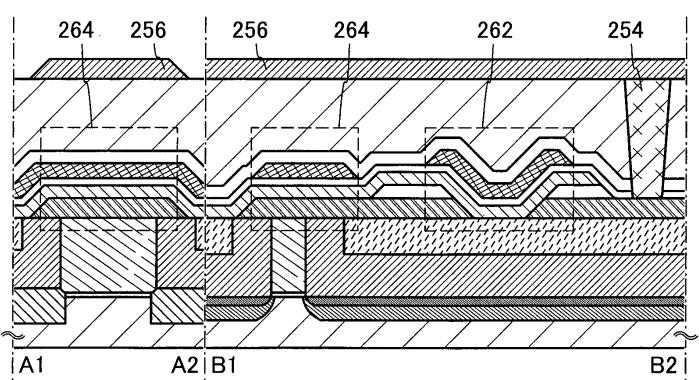

- [0167] 본 실시예에서, 불순물을 제거하기 위해 불소를 산화물 반도체층에 첨가하고 이후 산화물 반도체층이 열 처리를 거치게 하는 것에 의한, 실시예 1의 방법과 상이한, 산화물 반도체층을 정제하는 방법을 이용한 보텀 게이트 (bottom-gate)형 트랜지스터의 제작 방법이 도 10a 및 도 10b, 도 11a 내지 도 11c, 그리고 도 12a 내지 도 12c를 참조하여 설명될 것이다.

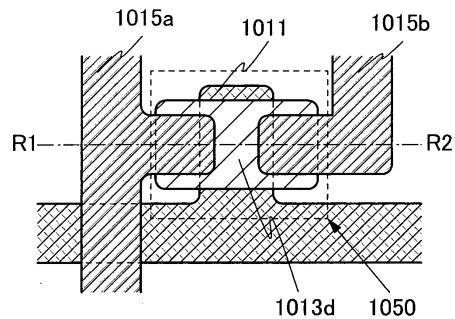

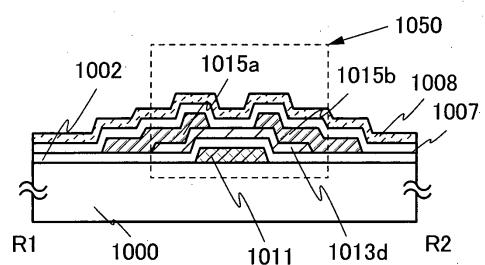

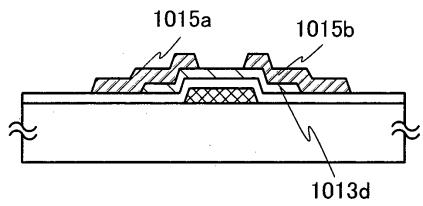

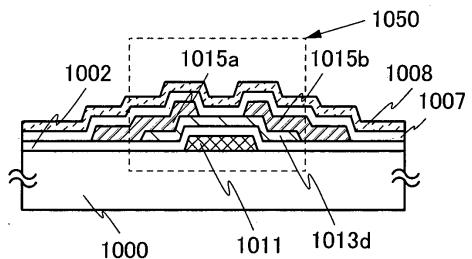

- [0168] 도 10a 및 도 10b는 본 실시예에서 제작되는 보텀 게이트형 트랜지스터(1050)의 구조를 도시한다. 도 10a는 트랜지스터(1050)의 상면도이고, 도 10b는 트랜지스터(1050)의 단면도이다. 도 10b는 도 10a의 선(R1-R2)에 따라 얻어진 단면도에 대응한다는 것에 주의한다.

- [0169] 트랜지스터(1050)에서, 게이트 전극(1011)과, 상기 게이트 전극(1011)을 덮는 게이트 절연층(1002)이 절연 표면을 갖는 기판(1000) 위에 제공된다. 상기 게이트 전극(1011)과 중첩하는 정제된 산화물 반도체층(1013d)이 상기 게이트 절연층(1002) 위에 제공된다. 게다가, 소스 및 드레인 전극으로 기능하는 제 1 전극(1015a)과 제 2 전극(1015b)이 산화물 반도체층(1013d)과 접하여 제공되어 각각이 상기 게이트 전극(1011)과 중첩하는 단부를 갖게 된다. 또한, 산화물 반도체층(1013d)과 접하고 그의 채널 형성 영역과 중첩하는 절연층(1007)과, 트랜지스터(1050)를 덮는 보호 절연층(1008)이 제공된다.

- [0170] 다음, 기판(1000) 위의 트랜지스터(1050)의 제작 방법이 도 11a 내지 도 11c와 도 12a 내지 도 12c를 참조하여 설명될 것이다.

- [0171] 먼저, 절연 표면을 갖는 기판(1000) 위에 도전막이 형성된 후, 제 1 포토리소그래피 단계에 의해 게이트 전극(1011)을 포함하는 배선층이 형성되고, 게이트 전극(1011) 위에 게이트 절연층(1002)이 형성된다. 실시예 1의 게이트 전극(511)과 게이트 절연층(502)을 위한 것과 유사한 방법들 및 조건들이 게이트 전극(1011)과 게이트 절연층(1002)에 적용될 수 있다. 따라서, 상세한 설명들을 위하여, 실시예 1이 참조될 수 있다.

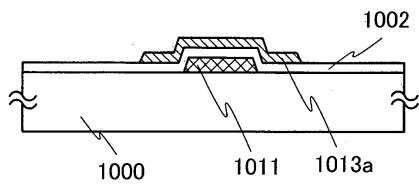

- [0172] 다음, 2nm보다 크거나 같고 200nm보다 작거나 같은, 바람직하게는 3nm보다 크거나 같고 50nm보다 작거나 같은 두께를 갖는 산화물 반도체막이 게이트 절연층(1002) 위에 형성되고, 산화물 반도체막이 제 2 포토리소그래피 단계에 의해 섬형 산화물 반도체층(1013a)으로 처리된다(도 11a). 본 실시예에서 예로 설명된 산화물 반도체층(1013a)은 실시예 1에서 설명된 산화물 반도체층(513a)의 것과 유사한 재료, 방법, 및 조건들을 이용하여 형성될 수 있다. 따라서, 상세한 설명들을 위하여, 실시예 1이 참조될 수 있다.

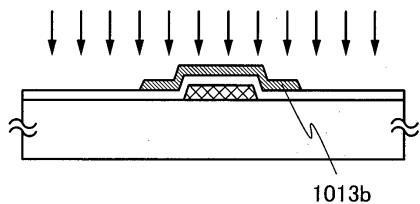

- [0173] 다음, 불소가 산화물 반도체층(1013a)으로 첨가된다. 불소의 첨가를 위하여, 실시예 1의 것과 유사한 재료, 방법, 및 조건이 적용될 수 있다. 따라서, 상세한 설명들을 위하여, 실시예 1이 참조될 수 있다. 불소가 상기 산화물 반도체층(1013a)으로 첨가될 때, 예를 들면, 산화물 반도체의 금속과 수소 사이의 결합, 금속에 결합되는 수산기의 산소와 수소 사이의 결합, 또는 금속과 수산기 사이의 결합이 끊어질 수 있다. 여기서, 상기 산화물 반도체층(1013a)은 금속으로부터 탈착되는 불순물을 포함하는 산화물 반도체층(1013b)이 된다(도 11b).

- [0174] 실시예 1에서와 같이, 산화물 반도체층(1013a)으로의 불소의 첨가 전에 예열 처리가 수행될 수 있다.

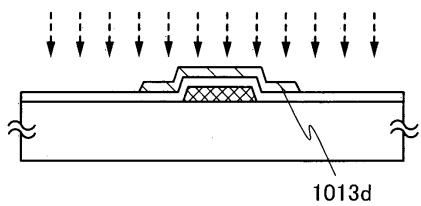

- [0175] 이후, 제 1 열 처리가 금속으로부터 탈착되는 불순물을 포함하는 산화물 반도체층(1013b) 상에서 수행되어, 산

화물 반도체층(1013c)이 얹어진다(도 11c). 상기 제 1 열 처리를 위하여, 실시예 1의 것과 유사한 방법 및 조건이 적용될 수 있다. 따라서, 상세한 설명들을 위하여, 실시예 1이 참조될 수 있다. 이러한 제 1 열 처리에 의하여, 금속으로부터 탈착된 불순물이 상기 산화물 반도체층(1013b)으로부터 제거될 수 있다.

[0176] 다음, 산소가 산화물 반도체층(1013c)으로 첨가되어, 산화물 반도체층(1013d)이 얹어진다(도 12a). 이온 주입법, 이온 도핑법, 등에 의해 고에너지로 갖는 산소가 첨가될 수 있다.

[0177] 산소 가스를 이용하여 이온 주입법에 의해 산소가 첨가되는 경우에, 가속 전압은 5keV보다 높거나 같고 100keV보다 낮거나 같을 수 있고, 첨가된 산소 이온들의 양은  $1 \times 10^{14} [\text{atoms/cm}^2]$ 보다 많거나 같고  $5 \times 10^{17} [\text{atoms/cm}^2]$ 보다 적거나 같을 수 있다.

[0178] 이온 주입법, 이온 도핑 방법, 등에 의해 산화물 반도체로 고에너지를 갖는 산소를 첨가하는 것에 의해, 상기 산화물 반도체의 주성분들 중 하나인 산소가 공급될 수 있다.

[0179] 산소의 첨가 후에, 산화물 반도체층 상에서 제 2 열 처리가 수행될 수 있다. 이러한 제 2 열 처리에 의해, 금속으로부터 탈착된 불순물이 산화물 반도체층으로부터 제거될 수 있다. 예를 들어, 첨가된 산소와 금속으로부터 탈착된 수소 또는 수산기 사이의 반응에 의해 생성되는 물이 제거될 수 있다. 생성된 물을 가열에 의해 제거하는 방법은 금속에 강하게 결합되는 수소 또는 수산기를 직접 제거하는 방법보다 쉽다. 산소의 첨가와 제 2 열 처리에 의해, 불소의 첨가와 제 1 열 처리에 의해 제거되지 않았던 불순물들이 제거될 수 있으며; 따라서, 산화물 반도체층이 정제되고 전기적으로 i-형(진성) 또는 실질적으로 i-형 산화물 반도체층이 될 수 있다.

[0180] 게다가, 산화물 반도체층으로서, 산화물, 질화물, 금속, 등 중 임의의 것이 먼저 형성되는 산화물 반도체층과 접하는 하지 부재의 재료로 이용되는 때에라도, 큰 두께를 갖는 결정 영역(비-단결정 영역), 즉, 막의 표면에 수직하게 c-축 배향되는 결정 영역을 갖는 산화물 반도체층이 두번의 막 형성과 두번의 열 처리를 수행하는 것에 의해 형성될 수 있다. 예를 들어, 3nm 내지 15nm의 두께를 갖는 제 1 산화물 반도체막이 형성된 후에, 불소의 제 1 첨가가 수행되고, 이후 질소, 산소, 희가스, 또는 건조 공기 분위기 하에서, 450°C보다 높거나 같고 850°C보다 낮거나 같은, 바람직하게는 550°C보다 높거나 같고 750°C보다 낮거나 같은 온도에서, 제 1 열 처리가 수행되어, 표면을 포함하는 영역에서 결정 영역(판형 결정을 포함)을 갖는 제 1 산화물 반도체막이 형성된다. 이후, 제 1 산화물 반도체막보다 큰 두께를 갖는 제 2 산화물 반도체막이 형성된 후, 불소의 제 2 첨가가 수행되고, 이후 450°C보다 높거나 같고 850°C보다 낮거나 같은, 바람직하게는 600°C보다 높거나 같고 700°C보다 낮거나 같은 온도에서 제 2 열 처리가 수행되어, 결정 성장의 시드로서 제 1 산화물 반도체막의 이용으로 결정 성장이 윗방향으로 진행하고 전체적인 제 2 산화물 반도체막이 결정화된다. 이후, 산소의 첨가가 수행된다. 산소의 첨가는 또한 제 2 산화물 반도체막이 형성되기 전에 수행될 수 있다. 불소의 제 2 첨가에 의해 불소가 상기 제 1 산화물 반도체막으로 첨가되면, 상기 제 1 산화물 반도체막의 결정 영역이 감소되거나 없어질 수 있다. 따라서, 불소의 제 2 첨가시 불소가 상기 제 1 산화물 반도체막으로 첨가되지 않도록 적절한 조건들(예를 들면, 가속 전압)을 선택하는 것이 필요하다.

[0181] 다음, 소스 전극 및 드레인 전극이 되는 도전막(소스 전극 및 드레인 전극과 동일한 층에서 형성된 배선을 포함)이 게이트 절연층(1002)과 산화물 반도체층(1013d) 위에 형성된다. 이후, 제 3 포토리소그래피 단계에 의해 레지스트 마스크가 도전막 위에 형성되고, 각각이 소스 또는 드레인 전극으로 기능하는 제 1 전극(1015a)과 제 2 전극(1015b)이 선택적인 에칭에 의해 형성되며, 이후 레지스트 마스크가 제거된다(도 12b). 실시예 1의 제 1 전극(515a)과 제 2 전극(515b)을 위한 방법 및 조건들이 제 1 전극(1015a) 및 제 2 전극(1015b)을 위한 것에 적용될 수 있다. 따라서, 상세한 설명들을 위하여, 실시예 1이 참조될 수 있다.

[0182] 다음, 실시예 1에서 설명된 절연층(507)의 것과 유사한 방법 및 재료를 이용하여 절연층(1007)이 형성된다.

[0183] 다음, 제 2 열 처리(산화물 반도체층의 막 형성과 열 처리가 각각 두번씩 수행되는 경우에는 제 3 열 처리)가 불활성 가스 분위기 또는 산소 가스 분위기에서 수행될 수 있다. 열 처리는 200°C보다 높거나 같고 400°C보다 낮거나 같은 온도에서 수행되는 것이 바람직하며, 예를 들면 250°C보다 높거나 같고 350°C보다 낮거나 같은 온도에서 수행된다. 예를 들어, 제 2 열 처리가 질소 분위기 하에서 한시간 동안 250°C에서 수행된다. 제 2 열 처리가 수행될 때, 산화물 반도체층의 일부가 절연층(1007)과 접하는 상태에서 가열된다.

[0184] 상술된 바와 같이, 불소가 산화물 반도체막으로 첨가되고 불소가 산화물 반도체막으로 첨가된 후에 제 1 열 처리가 수행되어, 수소, 수분, 수산기, 또는 수소화물(또한 수소 화합물로도 불림)과 같은 불순물들이 산화물 반도체층으로부터 의도적으로 제거될 수 있다. 산소를 상기 산화물 반도체막으로 첨가하는 것에 의해, 상기 산화

물 반도체층의 주성분들 중 하나인 산소가 공급될 수 있다. 따라서, 산화물 반도체층이 정제되어 전기적으로 i-형(진성) 또는 실질적으로 i-형 반도체층이 된다. 상기 공정을 통하여, 트랜지스터(1050)가 형성된다.

[0185] 일부 경우들에서, 본 실시예의 트랜지스터는 산화물 반도체층에 할로겐 원소를 포함할 수 있다. 산화물 반도체층의 할로겐 원소는 금속 원자 상의 댕글링 결합에 쉽게 결합하고 댕글링 결합이 종결되기 때문에, 캐리어들의 생성이 감소될 수 있다.

[0186] 다수의 결합들을 갖는 산화 실리콘층이 절연층(1007)으로 이용될 때, 산화 실리콘층의 형성 후의 열 처리는 산화물 반도체층에 함유된 수소, 수분, 또는 수소화물과 같은 불순물을 산화 실리콘층으로 확산시키는 효과를 가져서 상기 산화물 반도체층에 함유된 불순물이 더욱 감소될 수 있다.

[0187] 보호 절연층(1008)이 절연층(1007) 위에 부가적으로 형성될 수 있다. 상기 보호 절연층(1008)은 실시예 1에서 설명된 보호 절연층(508)의 것과 유사한 재료 및 방법을 이용하여 형성될 수 있다. 따라서, 상세한 설명들을 위하여, 실시예 1이 참조될 수 있다. 본 실시예에서, 상기 보호 절연층(1008)은 질화 실리콘막을 이용하여 형성된다(도 12c).

[0188] 본 실시예를 이용하여 제작된 정제된 산화물 반도체층을 포함하는 트랜지스터는 임계 전압의 작은 변동을 갖는다. 따라서, 본 실시예의 예로 설명된 반도체 장치의 제작 방법을 이용하여, 매우 신뢰할 수 있는 반도체 장치가 제공될 수 있다. 또한, 높은 대량 생산성으로 제작될 수 있는 반도체 장치가 제공될 수 있다.

[0189] 또한, 오프 상태 전류가 감소될 수 있기 때문에 낮은 전력 소비를 갖는 반도체 장치가 제공될 수 있다.

[0190] 본 실시예는 본 명세서에서 설명된 다른 실시예들 중 임의의 것과 적절하게 조합될 수 있다.

[0191] (실시예 4)

[0192] 본 실시예에서, 본 발명의 실시예에 따른 반도체 장치의 구조 및 제작 방법이 도 5a 및 도 5b, 도 6a 내지 도 6d, 도 7a 내지 도 7c, 도 8a 내지 도 8d, 및 도 9a 내지 도 9c를 참조하여 설명될 것이다. 본 실시예에서 예로 설명된 반도체 장치는 메모리 장치로 이용될 수 있다는 것에 주의한다.

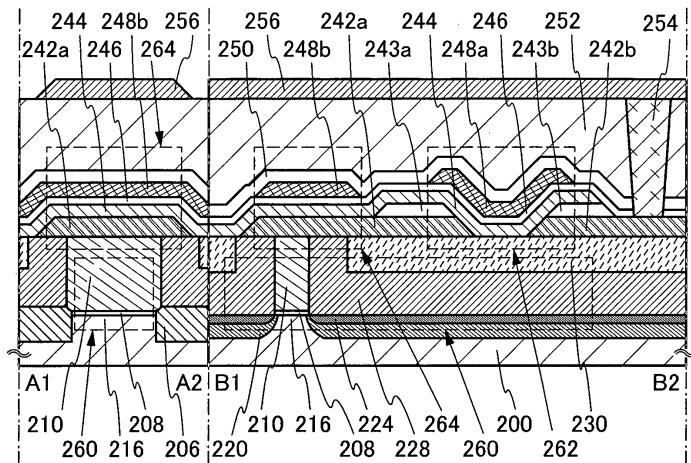

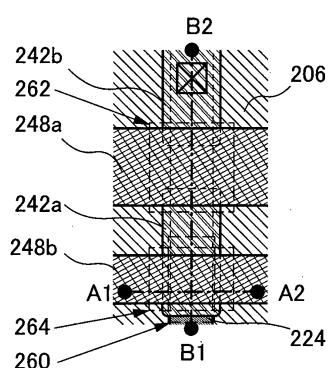

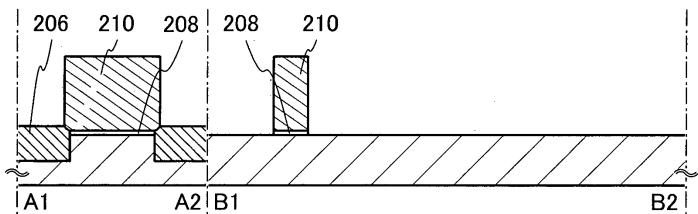

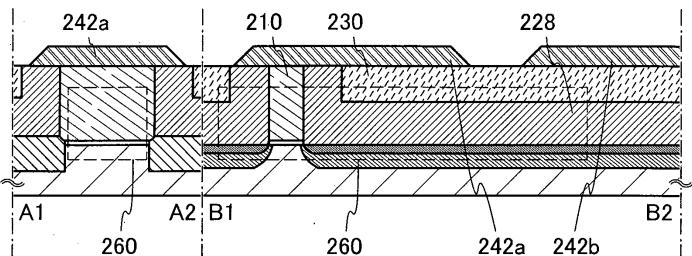

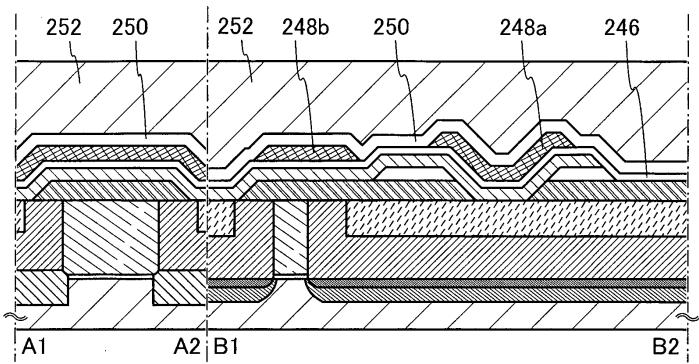

[0193] 본 실시예의 예로 설명된 반도체 장치의 구조가 도 5a 및 도 5b에 도시된다. 도 5a는 반도체 장치의 단면도이고, 도 5b는 반도체 장치의 평면도이다. 도 5a는 도 5b의 선 A1-A2와 선 B1-B2를 따라 얻어진 단면도라는 것에 주의한다.

[0194] 예로 설명된 반도체 장치는 하부에 제 1 반도체 재료를 포함하는 트랜지스터(260)와, 상부에 제 2 반도체 재료를 포함하는 트랜지스터(262)와, 커패시터(264)를 포함한다. 트랜지스터(260)의 게이트 전극(210)은 트랜지스터(262)의 제 1 전극(242a)에 직접 접속된다.

[0195] 트랜지스터(262)와 커패시터(264)가 제공되어 트랜지스터(260)와 중첩하는 경우에, 고집적화(high integration)가 성취될 수 있다. 예를 들어, 최소 피처(feature) 크기가 F라고 주어지면, 배선과 전극 사이의 접속을 고안하는 것에 의해 메모리 셀에 의해 점유된 면적은  $15F^2$  내지  $25F^2$ 가 될 수 있다.

[0196] 트랜지스터(260)에 포함된 제 1 반도체 재료와 트랜지스터(262)에 포함된 제 2 반도체 재료는 상이할 수 있다. 예를 들어, 단결정 반도체가 고속 동작이 가능한 트랜지스터(260)를 형성하기 위한 제 1 반도체 재료로 이용될 수 있으며, 산화물 반도체가 충분히 작은 오프 상태 전류를 갖고 장시간 전하를 보유하는 것이 가능한 트랜지스터(262)를 형성하기 위한 제 2 반도체 재료로 이용될 수 있다.

[0197] 제 1 반도체 재료 및 제 2 반도체 재료로서, 예를 들면, 산화물 반도체 또는 산화물 반도체 이외의 반도체 재료가 이용될 수 있다. 산화물 반도체 이외의 반도체 재료로서, 실리콘, 게르마늄, 실리콘 게르마늄, 탄화 실리콘, 갈륨 비소, 등이 이용될 수 있다. 대안적으로, 유기 반도체 재료 등이 이용될 수 있다.

[0198] 본 실시예에서, 단결정 실리콘이 제 1 반도체 재료로 사용되어 트랜지스터(260)가 고속으로 동작될 수 있고 산화물 반도체가 제 2 반도체 재료로 사용되어 트랜지스터(262)가 작은 오프 상태 전류를 가질 수 있는 경우가 설명될 것이다.

[0199] 트랜지스터(260)의 게이트 전극(210)이 트랜지스터(262)의 제 1 전극(242a)에 접속되는 구조를 갖는 반도체 장치가 메모리 장치로 양호하다. 트랜지스터(262)가 오프 상태에 있을 때, 트랜지스터(260)의 게이트 전극(210)의 포텐셜은 극히 장시간 동안 보유될 수 있다. 커패시터(264)가 제공될 때, 트랜지스터(260)의 게이트 전극(210)으로 공급된 전하가 쉽게 보유될 수 있으며 보유된 데이터의 판독이 쉽게 수행될 수 있다. 게다가, 이러한 반도

체 재료를 포함하고 고속의 동작이 가능한 트랜지스터(260)로, 데이터가 고속으로 판독될 수 있다.

[0200] 본 실시예에서 예로 설명된 반도체 장치에 포함된 모든 트랜지스터들은 여기서 n-채널형 트랜지스터들이지만, p-채널형 트랜지스터들이 이용될 수 있다는 것은 말할 필요가 없다. 여기서 개시된 본 발명의 기술적 특징은 충분히 작은 오프 상태 전류를 갖는 산화물 반도체를 포함하는 트랜지스터와 충분히 고속 동작이 가능한 산화물 반도체 이외의 반도체 재료를 포함하는 트랜지스터가 함께 제공된다는 것이다. 따라서, 반도체 장치를 위해 이용된 재료 또는 반도체 장치의 구조와 같은, 특정 조건들을 여기서 설명된 조건들로 제한할 필요는 없다.

[0201] 트랜지스터(260)는 제 1 반도체 재료를 포함하는 기판(200)에 제공된 채널 형성 영역(216)과, 채널 형성 영역(216)이 그 사이에 개재되는 불순물 영역들(220)을 포함한다. 또한, 트랜지스터(260)는 불순물 영역들(220)과 접하는 금속 화합물 영역들(224)과, 채널 형성 영역(216) 위에 제공된 게이트 절연층(208)과, 상기 게이트 절연층(208) 위에 제공된 게이트 전극(210)을 포함한다. 일부 경우들에서, 그의 소스 전극 및 드레인 전극이 도면에 명확하게 도시되지 않은 트랜지스터가 편의를 위해 트랜지스터로 불려질 수 있다는 것에 주의한다. 또한, 이러한 경우에, 트랜지스터들 사이의 접속의 설명에서, 소스 영역 및 드레인 영역은 일부 경우들에서, 소스 전극 및 드레인 전극으로 각각 불려질 수 있다. 다시 말해, 본 명세서에서, "소스 전극"이라는 용어는 소스 영역을 포함할 수 있으며, "드레인 전극"이라는 용어는 드레인 영역을 포함할 수 있다.

[0202] 또한, 소자 분리 절연층(206)이 기판(200) 위에 제공되어 트랜지스터(260)를 둘러싸고, 절연층(228)과 절연층(230)이 트랜지스터(260) 위에 제공된다. 도시되지 않았으나, 트랜지스터(260)의 금속 화합물 영역들(224)의 일부가 소스 전극 또는 드레인 전극으로 기능하는 전극을 통해 배선(256) 또는 다른 배선과 접속된다. 그의 소스 전극 및 드레인 전극이 도면에 명확하게 도시되지 않은 트랜지스터가 편의를 위해 트랜지스터로 불려질 수 있다는 것에 주의한다.

[0203] 고집적화를 얻기 위하여, 트랜지스터(260)는 도 5a 및 도 5b에 도시된 바와 같이 측벽(sidewall) 절연층을 갖지 않는 것이 바람직하다. 한편, 상기 트랜지스터(260)의 특성들이 강조되는 경우에, 측벽 절연층이 게이트 전극(210)의 측면 상에 제공될 수 있고, 불순물 영역들(220)이 불순물 영역들(220)과 상이한 불순물 농도를 가지며 측벽 절연층과 중첩하는 영역에 제공되는 불순물 영역을 포함할 수 있다.

[0204] 본 실시예에서, 제 1 반도체 재료를 포함하는 기판(200)으로서 단결정 실리콘 기판이 이용된다. 실리콘 등의 단결정 반도체 기판을 이용하는 경우에, 반도체 장치의 판독 동작이 더 고속으로 수행될 수 있다.

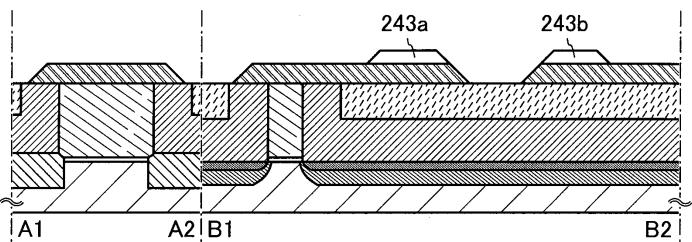

[0205] 트랜지스터(262)는 제 2 반도체 재료로서 정제된 산화물 반도체층을 포함한다. 상기 트랜지스터(262)는 절연층(230) 위에 소스 전극 및 드레인 전극으로 기능하는 제 1 전극(242a) 및 제 2 전극(242b)을 포함하고, 상기 제 1 전극 및 상기 제 2 전극과 전기적으로 접속된 산화물 반도체층(244)을 포함한다. 또한, 상기 트랜지스터(262)는 상기 산화물 반도체층(244)을 덮는 게이트 절연층(246)과, 상기 게이트 절연층(246) 위에 위치되고 상기 산화물 반도체층(244)과 중첩하는 게이트 전극(248a)을 포함한다. 게다가, 절연층(243a)이 제 1 전극(242a)과 산화물 반도체층(244) 사이에 제공되어 게이트 전극(248a)과 중첩하고, 절연층(243b)이 상기 제 2 전극(242b)과 상기 산화물 반도체층(244) 사이에 제공되어 상기 게이트 전극(248a)과 중첩한다.

[0206] 절연층(243a)과 절연층(243b)은 게이트 전극과 소스 또는 드레인 전극 사이에서 생성된 커파시턴스를 감소시킨다. 그러나, 절연층(243a)과 절연층(243b)이 없는 구조가 또한 채용될 수 있다.

[0207] 여기서, 산화물 반도체층(244)은 그로부터 수소와 같은 불순물을 충분히 제거하는 것에 의해 정제되는 산화물 반도체층인 것이 바람직하다. 구체적으로, 상기 산화물 반도체층(244)의 수소의 농도는 예를 들면,  $5 \times 10^{19}$  atoms/cm<sup>3</sup> 보다 낮거나 같고, 바람직하게는  $5 \times 10^{18}$  atoms/cm<sup>3</sup> 보다 낮거나 같고, 더욱 바람직하게는  $5 \times 10^{17}$  atoms/cm<sup>3</sup> 보다 낮거나 같다. 상기 산화물 반도체층(244)의 수소의 상기 농도는 2차 이온 질량 분석법(secondary ion mass spectroscopy; SIMS)에 의해 측정된다는 것에 주의한다. 수소의 농도를 충분히 감소시키는 것에 의해 정제되고 산소 결손으로 인한 에너지 캡의 결함 준위가 충분한 양의 산소를 공급하는 것에 의해 감소되는 산화물 반도체층(244)에서, 수소, 산소 결손, 등으로부터 결과된 캐리어 농도는  $1 \times 10^{12} / \text{cm}^3$  보다 작고, 바람직하게는  $1 \times 10^{11} / \text{cm}^3$  보다 작고, 더욱 바람직하게는  $1.45 \times 10^{10} / \text{cm}^3$  보다 작다.

[0208] 오프 상태 전류는 산화물 반도체층(244)을 포함하는 트랜지스터에서 충분히 작을 수 있다. 예를 들어, 상기 산화물 반도체층(244)이 30nm의 두께와 2μm의 채널 길이를 갖는 트랜지스터에서, 실온(25°C)에서 1μA의 채널 길이 당 오프 상태 전류(게이트 바이어스: -3V)는 100zA(1zA(베토암페어; zeptoampere)는  $1 \times 10^{-21} \text{ A}$ 와 같다)보다 작

거나 같고, 바람직하게는 10zA보다 작거나 같다.

[0209] 본 실시예에서, 불소가 산화물 반도체층으로 침가된 후 산화물 반도체층이 열 처리를 거치게 되어 그로부터 불순물을 제거하는 방법을 채용하는 것에 의해 정제된 산화물 반도체층이 형성된다. 이러한 방식으로 정제된 산화물 반도체를 이용하는 것에 의해, 탁월한 오프 상태 전류 특성들을 갖는 트랜지스터(262)가 얻어질 수 있다. 실시예 2가 산화물 반도체층(244)의 상세한 설명들을 위해 참조될 수 있다.

[0210] 섬형을 갖도록 처리되는 산화물 반도체층(244)이 미세화(miniaturization)로 인한 소자들 사이의 누설 전류를 억제하기 위하여 도 5a 및 도 5b의 트랜지스터(262)에서 사용되지만, 섬형을 갖도록 처리되지 않은 상기 산화물 반도체층(244)을 포함하는 구조가 채용될 수 있다. 산화물 반도체층이 섬형을 갖도록 처리되지 않는 경우에, 공정에서의 에칭으로 인한 상기 산화물 반도체층(244)의 오염이 방지될 수 있다.

[0211] 예로서 도 5a 및 도 5b에 도시된 반도체 장치에서, 트랜지스터(260)의 게이트 전극(210)의 상부 표면이 절연층(228)의 표면 상에 노출되고, 트랜지스터(262)의 소스 또는 드레인 전극으로 기능하는 제 1 전극(242a)에 직접 접속된다. 상기 게이트 전극(210)은 접촉을 위해 부가적으로 제공되는 개구부(opening)와 전극을 통해 상기 제 1 전극(242a)과 접속될 수 있다. 그러나, 직접 접속의 경우에, 접촉 면적이 감소될 수 있고 반도체 장치의 고집적화가 성취될 수 있다.

[0212] 예를 들어, 메모리 장치로서 본 실시예의 반도체 장치를 이용하는 경우에, 단위 면적당 저장 커패시티의 증가를 위해 고집적화가 중요하다. 게다가, 접촉을 위해 부가적으로 형성되는 개구부와 전극을 형성하기 위해 필요한 단계는 생략될 수 있으며; 따라서, 반도체 장치를 제작하기 위한 공정이 간략화될 수 있다.

[0213] 도 5a 및 도 5b의 커패시터(264)는 소스 또는 드레인 전극으로 기능하는 제 1 전극(242a)과, 산화물 반도체층(244)과, 게이트 절연층(246)과, 전극(248b)을 포함한다. 즉, 상기 제 1 전극(242a)은 커패시터(264)의 하나의 전극으로 기능하고, 전극(248b)은 커패시터(264)의 다른 전극으로 기능한다.

[0214] 예로서 도 5a 및 도 5b에 도시된 커패시터(264)에서, 산화물 반도체층(244)과 게이트 절연층(246)이 제 1 전극(242a)과 전극(248b) 사이에 개재되지만; 단지 게이트 절연층(246) 만이 더 큰 용량을 위해 개재될 수 있다. 또한, 상기 커패시터(264)는 절연층(243a)의 것과 유사한 방식으로 형성된 절연층을 포함하는 구조를 가질 수 있다. 커패시터가 필요하지 않은 경우에, 상기 커패시터(264)가 없는 구조를 채용하는 것이 가능하다.

[0215] 또한, 절연층(250)이 트랜지스터(262)와 커패시터(264) 위에 제공되고, 절연층(252)이 상기 절연층(250) 위에 제공된다. 게이트 절연층(246), 절연층(250), 절연층(252), 등에 형성된 개구부에서, 전극(254)이 제공된다. 배선(256)이 상기 절연층(252) 위에 제공되어, 상기 전극(254)을 통해 제 2 전극(242b)으로 전기적으로 접속된다. 상기 배선(256)은 상기 제 2 전극(242b)과 직접 접촉하도록 구성될 수 있다는 것에 주의한다.

[0216] 게다가, 금속 화합물 영역(224)에 접속된 전극(도시되지 않음)이 제 2 전극(242b)에 접속될 수 있다. 이러한 경우에, 전극(254)과 금속 화합물 영역(224)에 접속된 전극이 배치되어 서로 중첩하게 되면, 반도체 장치의 고집적화가 성취될 수 있다.

#### <반도체 장치의 제작 방법>

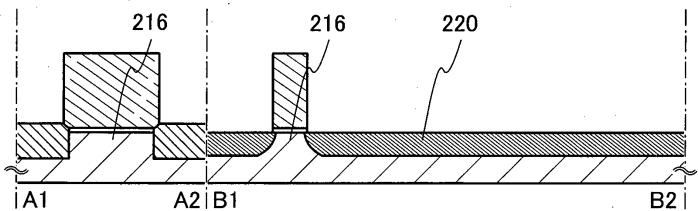

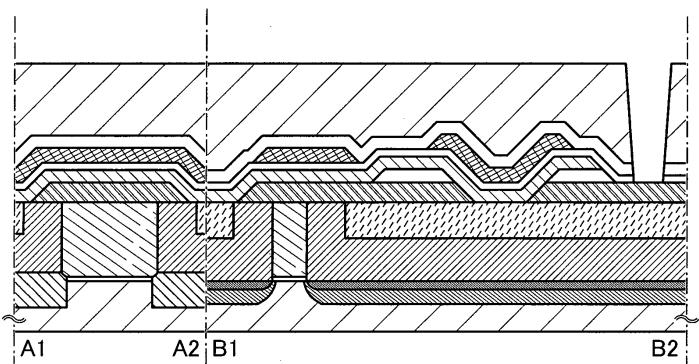

[0218] 다음, 반도체 장치의 제작 방법의 예가 설명될 것이다. 먼저, 하부 트랜지스터(260)의 제작 방법이 도 6a 내지 도 6d와 도 7a 내지 도 7c를 참조하여 이하에 설명되고, 이후 상부 트랜지스터(262)와 커패시터(264)의 제작 방법이 도 8a 내지 도 8d와 도 9a 내지 도 9c를 참조하여 설명될 것이다.

#### <하부 트랜지스터의 제작 방법>

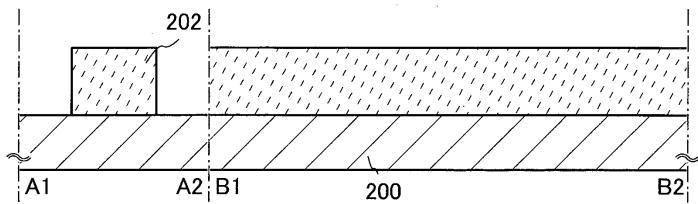

[0220] 먼저, 반도체 재료를 포함하는 기판(200)이 준비된다(도 6a). 반도체 재료를 포함하는 상기 기판(200)으로서, 실리콘, 탄화 실리콘, 등의 단결정 반도체 기판 또는 다결정 반도체 기판; 실리콘 게르마늄 등의 화합물 반도체 기판; SOI 기판; 등이 이용될 수 있다. 여기서, 단결정 실리콘 기판이 반도체 재료를 포함하는 상기 기판(200)으로 이용되는 경우의 예가 설명될 것이다.

[0221] 일반적으로, "SOI 기판"이라는 용어는 실리콘 반도체층이 절연 표면 상에 제공되는 기판을 의미한다. 본 명세서 등에서, 상기 "SOI 기판"이라는 용어는 그의 카테고리에 실리콘 이외의 재료를 이용하여 형성된 반도체층이 절연 표면 위에 제공되는 기판을 또한 포함한다. 즉, 상기 "SOI 기판"에 포함된 반도체층은 실리콘 반도체층에 제한되지 않는다. 또한, 상기 SOI 기판은 반도체층이 절연층을 사이에 개재하여 유리 기판과 같은 절연 기판 위에 제공되는 구조를 갖는 기판을 또한 포함한다.

- [0222] 트랜지스터(260)가 더 고속에서 동작할 수 있으므로 반도체 재료를 포함하는 기판(200)으로서 단결정 실리콘 기판과 같은 단결정 반도체 기판을 이용하는 것이 바람직하다.

- [0223] 소자 분리 절연층들을 형성하기 위한 마스크가 되는 보호층(202)이 기판(200) 위에 형성된다(도 6a). 상기 보호층(202)으로서, 예를 들면, 산화 실리콘, 질화 실리콘, 또는 산화질화 실리콘과 같은 재료를 포함하는 절연층이 이용될 수 있다. 이러한 단계 전 및 후에, 트랜지스터의 임계 전압을 제어하기 위하여 n-형 도전성을 주는 불순물 원소 또는 p-형 도전성을 주는 불순물 원소가 상기 기판(200)으로 첨가될 수 있다는 것에 주의한다. 상기 기판(200)에 포함된 상기 반도체 재료가 실리콘일 때, 예를 들면, 인, 비소, 등이 n-형 도전성을 주는 불순물로 이용될 수 있고, 봉소, 알루미늄, 갈륨, 등이 p-형 도전성을 주는 불순물로 이용될 수 있다.

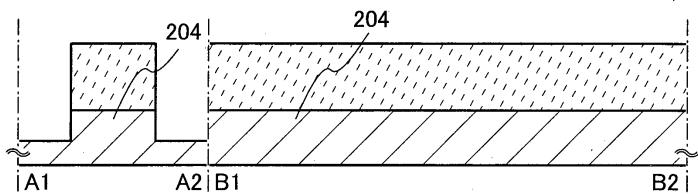

- [0224] 다음, 마스크로서 보호층(202)을 이용하여 에칭에 의해 상기 보호층(202)으로 덮이지 않은 영역(즉, 노출된 영역)의 기판(200)의 일부가 제거된다. 따라서, 다른 반도체 영역으로부터 떨어진 반도체 영역(204)이 형성된다(도 6b). 에칭으로서, 건식 에칭이 채용되는 것이 바람직하지만, 습식 에칭이 채용될 수 있다. 에칭 가스와 에천트는 에칭될 층의 재료에 따라 적절하게 선택될 수 있다.

- [0225] 이후, 절연층이 반도체 영역(204)을 덮도록 형성되고, 상기 반도체 영역(204)과 중첩하는 영역의 절연층이 선택적으로 제거되어, 소자 분리 절연층(206)이 형성된다(도 6c). 상기 절연층은 산화 실리콘, 질화 실리콘, 산화질화 실리콘 등을 이용하여 형성된다. 절연층을 제거하는 방법으로서, 화학적 기계적 폴리싱(CMP), 에칭 처리, 등과 같은 폴리싱 처리가 주어질 수 있으며, 상기 처리들 중 임의의 것이 홀로 또는 함께 이용될 수 있다. 상기 보호층(202)은 상기 반도체 영역(204)의 형성 후 또는 상기 소자 분리 절연층(206)의 형성 후 제거된다는 것에 주의한다.

- [0226] 소자 분리 절연층(206)의 형성 방법으로서, 절연층이 선택적으로 제거되는 방법 뿐만 아니라 산소 등의 주입에 의해 절연 영역이 형성되는 방법이 이용될 수 있다는 것에 주의한다.

- [0227] 다음, 절연층이 반도체 영역(204)의 표면 위에 형성되고, 도전성 재료를 포함하는 층이 상기 절연층 위에 형성된다.

- [0228] 절연층이 나중에 게이트 절연층이 되고, 예를 들면, 반도체 영역(204)의 표면 상에서 열 처리(열 산화(thermal oxidation) 처리 또는 열 질화 처리)에 의해 형성될 수 있다. 고밀도 플라즈마 처리가 열 처리 대신 채용될 수 있다. 고밀도 플라즈마 처리는 예를 들면, He, Ar, Kr, 또는 Xe와 같은 희가스와 산소, 산화 질소, 암모니아, 질소, 및 수소 중 임의의 것의 혼합 가스를 이용하여 수행될 수 있다. 말할 필요도 없이, 상기 절연층은 CVD(화학적 증착) 방법, 스퍼터링법, 등을 이용하여 형성될 수 있다. 상기 절연층은 산화 실리콘, 산화질화 실리콘, 질화 실리콘, 산화 하프늄, 산화 알루미늄, 산화 탄탈, 산화 이트륨, 하프늄 실리케이트( $HfSi_xO_y$ ( $x>0$ ,  $y>0$ )), 질소가 첨가되는 하프늄 실리케이트( $HfSi_xO_y$ ( $x>0$ ,  $y>0$ )), 질소가 첨가되는 하프늄 알루미네이트( $HfAl_xO_y$ ( $x>0$ ,  $y>0$ )), 등 중 임의의 것을 함유하는 막을 포함하는 단층 구조 또는 적층 구조를 갖는 것이 바람직하다. 상기 절연층은 예를 들면, 1nm보다 크거나 같고 100nm보다 작거나 같은, 바람직하게는 10nm보다 크거나 같고 50nm보다 작거나 같은 두께를 가질 수 있다.

- [0229] 도전성 재료를 포함하는 층이 알루미늄, 구리, 티타늄, 탄탈, 또는 텉스텐과 같은 금속 재료를 이용하여 형성될 수 있다. 도전성 재료를 포함하는 층이 다결정 실리콘과 같은 반도체 재료를 이용하여 형성될 수 있다. 도전성 재료를 포함하는 층의 형성 방법에는 특별한 제한은 없으며, 증착법, CVD법, 스퍼터링법, 또는 스판 코팅법과 같은 다양한 막 형성 방법들이 채용될 수 있다. 본 실시예는 도전성 재료를 포함하는 층이 금속 재료를 이용하여 형성되는 경우의 예를 보여준다는 것에 주의한다.

- [0230] 그 후, 절연층과 도전성 재료를 포함하는 층이 선택적으로 에칭되어, 게이트 절연층(208)과 게이트 전극(210)이 형성된다(도 6c).

- [0231] 다음, 인(P), 비소(As), 등이 반도체 영역(204)으로 첨가되어, 채널 형성 영역(216) 및 불순물 영역들(220)이 형성된다(도 6d). n-채널형 트랜지스터를 형성하기 위하여 인 또는 비소가 여기에 첨가되고; 봉소(B) 또는 알루미늄(AI)과 같은 불순물 원소가 p-채널형 트랜지스터를 형성하는 경우에 첨가될 수 있다는 것에 주의한다. 여기서, 첨가된 불순물의 농도는 적절하게 설정될 수 있으며; 반도체 소자의 크기가 극히 감소될 때에는 농도는 높게 설정되는 것이 바람직하다.

- [0232] 측벽 절연층이 게이트 전극(210)의 주변에 형성될 수 있어서 불순물 원소가 상이한 농도로 포함되는 불순물 영역이 형성될 수 있다는 것에 주의한다.

- [0233] 다음, 금속층(222)이 게이트 전극(210), 불순물 영역들(220), 등을 덮도록 형성된다(도 7a). 진공 증착법, 스퍼터링법, 및 스픈 코팅법과 같은 다양한 막 형성 방법들 중 임의의 것이 상기 금속층(222)의 형성 방법으로 적용 가능하다. 상기 금속층(222)은 반도체 영역(204)에 포함된 반도체 재료와의 반응에 의하여 낮은 저항의 금속 화합물이 되는 금속 재료를 이용하여 형성되는 것이 바람직하다. 이러한 금속 재료로서, 예를 들면, 티타늄, 탄탈, 텉스텐, 니켈, 코발트, 백금, 등이 이용될 수 있다.

- [0234] 다음, 열 처리가 수행되어, 금속층(222)이 반도체 재료와 반응한다. 따라서, 불순물 영역들(220)과 접하는 금속 화합물 영역들(224)이 형성된다(도 7a). 다결정 실리콘 등을 이용하여 게이트 전극(210)이 형성되는 경우에, 금속 화합물 영역이 또한 상기 금속층(222)과 접하는 상기 게이트 전극(210)의 영역에 형성된다는 것에 주의한다.

- [0235] 열 처리로서, 예를 들면, 플래시 램프(flash lamp)의 조사(irradiation)가 채용될 수 있다. 다른 열 처리 방법이 이용될 수 있다는 것은 말할 필요도 없지만, 금속 화합물의 형성시 화학적 반응의 제어 가능성을 개선시키기 위하여 열 처리가 극히 단시간에 완성될 수 있는 방법이 이용되는 것이 바람직하다. 금속 화합물 영역들은 금속 재료와 반도체 재료의 반응에 의해 형성되고 충분히 높은 도전성을 갖는다는 것에 주의한다. 금속 화합물 영역들의 형성은 전기 저항을 충분히 감소시키고 소자 특성들을 개선시킬 수 있다. 금속 화합물 영역들(224)의 형성 후에 금속층(222)은 제거된다는 것에 주의한다.

- [0236] 이후, 상기 단계들에서 형성된 구성성분들을 덮도록 절연층(228)과 절연층(230)이 형성된다(도 7b). 상기 절연층(228)과 상기 절연층(230)은 산화 실리콘, 산화질화 실리콘, 또는 산화 알루미늄과 같은 무기 절연 재료를 포함하는 재료를 이용하여 형성될 수 있다. 특히, 낮은 유전 상수(낮은-k) 재료를 이용하여 상기 절연층(228)과 상기 절연층(230)이 형성되는 것이 바람직하며, 그에 의해, 전극들 또는 배선들의 중첩에 의해 유발된 커페시턴스가 충분히 감소될 수 있다. 이러한 재료들 중 임의의 것을 포함하는 다공성 절연층이 상기 절연층(228)과 상기 절연층(230)을 위해 이용될 수 있다는 것에 주의한다. 다공성 절연층은 고밀도를 갖는 절연층보다 낮은 유전 상수를 갖고; 따라서, 전극들 또는 배선들로 인한 커페시턴스가 더욱 감소될 수 있다.

- [0237] 게다가, 질화산화 실리콘 또는 질화 실리콘과 같은, 대량의 질소를 함유하는 무기 절연 재료를 포함하는 층이 절연층(228) 또는 절연층(230)에 포함될 수 있다. 따라서, 하부 트랜지스터(260)에 포함된 재료에 함유된 물 또는 수소와 같은 불순물이 나중에 형성되는 상부 트랜지스터(262)의 산화물 반도체층(244)으로 진입하는 것이 방지될 수 있다. 이러한 경우에, 나중 단계에서 수행된 CMP 처리에 의해서만 대량의 질소를 함유하는 무기 절연 재료를 포함하는 층을 제거하는 것은 어려우며; 따라서, CMP 처리와 에칭 처리가 함께 이용되는 것이 바람직하다는 것에 주의한다.

- [0238] 예를 들어, 산화질화 실리콘 및 산화 실리콘이 각각 절연층(228)과 절연층(230)을 형성하기 위해 이용될 수 있다. 이러한 방식으로, 산화질화 실리콘 또는 산화 실리콘과 같은, 대량의 산소를 함유하는 무기 절연 재료만이 상기 절연층(228)과 상기 절연층(230)을 형성하기 위해 이용될 때, 나중 단계에서 상기 절연층(228)과 상기 절연층(230) 상에서 CMP 처리가 쉽게 수행될 수 있다.

- [0239] 절연층(228)과 절연층(230)의 적층 구조가 여기서 채용되었으나; 여기서 개시된 본 발명의 실시예는 이에 제한되지 않는다는 것에 주의한다. 단층 구조 또는 셋 또는 그 이상의 층들을 포함하는 적층 구조가 또한 이용될 수 있다. 예를 들어, 다음 구조가 채용될 수 있다: 산화질화 실리콘 및 산화 실리콘이 상기 절연층(228)과 상기 절연층(230)을 위해 각각 이용되고, 질화산화 실리콘막이 상기 절연층(228)과 상기 절연층(230) 사이에 형성된다.

- [0240] 그 후에, 트랜지스터(262)의 형성 전의 처리로서, CMP 처리가 절연층(228)과 절연층(230) 상에서 수행되어, 상기 절연층(228)과 상기 절연층(230)의 표면들이 평탄화되고 게이트 전극(210)의 상부 표면이 노출된다(도 7c).

- [0241] CMP 처리는 한번 또는 복수회 수행될 수 있다. CMP 처리가 복수회 수행될 때, 제 1 폴리싱이 높은 폴리싱 속도로 수행되고, 뒤이어 낮은 폴리싱 속도의 마지막 폴리싱이 수행되는 것이 바람직하다. 상이한 폴리싱 속도들을 갖는 폴리싱을 조합하는 것에 의해, 절연층(228)과 절연층(230)의 표면들의 평탄화가 더욱 개선될 수 있다.

- [0242] 대량의 질소를 함유하는 무기 절연 재료가 절연층(228)과 절연층(230)의 적층 구조에 포함되는 경우에, CMP 처리에 의해서만 무기 절연 재료를 제거하는 것은 어려우며; 따라서, CMP 처리와 에칭 처리가 함께 사용되는 것이 바람직하다. 대량의 질소를 함유하는 무기 절연 재료를 위한 에칭 처리로서, 건식 에칭 또는 습식 에칭이 이용될 수 있다. 그러나, 소자들의 미세화의 관점에서, 건식 에칭이 이용되는 것이 바람직하다. 게다가, 에칭 조건들(에칭 가스, 에천트, 에칭 시간, 온도, 등)이 적절하게 설정되어 각각의 절연층들의 에칭 속도들이 균일해지고 게이트 전극(210)으로의 높은 에칭 선택도(selectivity)가 얻어질 수 있는 것이 바람직하다. 또한, 건식 에칭을 위한 에칭 가스로서, 예를 들어, 불소를 함유하는 가스(삼불화메탄( $\text{CHF}_3$ )), 헬륨(He) 또는 아르곤(Ar)과

같은 희가스가 첨가되는 불소를 함유한 가스, 등이 이용될 수 있다.

[0243] 게이트 전극(210)의 상부 표면이 절연층(228)의 표면 상에 노출될 때, 상기 게이트 전극(210)의 상부 표면과 상기 절연층(228)의 표면이 하나의 표면에 포함되는 것이 바람직하다.

[0244] 전극, 배선, 반도체층, 절연층, 등이 상기 단계들 전 및 후에 또한 형성될 수 있다는 것에 주의한다. 예를 들어, 금속 화합물 영역들(224)의 일부와 접속되고 트랜지스터(260)의 소스 또는 드레인 전극으로 기능하는 전극이 형성될 수 있다. 게다가, 절연층과 도전층이 적층되는 다층 배선 구조가 배선 구조로 채용될 수 있으며, 따라서 고집적화된 반도체 장치가 실현될 수 있다.

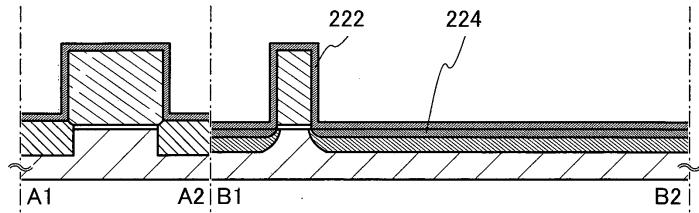

[0245] <상부 트랜지스터의 제작 방법>

[0246] 이후, 도전층이 게이트 전극(210), 절연층(228), 절연층(230), 등의 위에 형성되고, 상기 도전층이 선택적으로 에칭되어, 소스 또는 드레인 전극으로 기능하는 제 1 전극(242a)과 소스 또는 드레인 전극으로 기능하는 제 2 전극(242b)이 형성된다(도 8a). 상기 제 1 전극(242a)과 상기 제 2 전극(242b)은 실시예 2에서 설명된 소스 및 드레인 전극들로 기능하는 전극들의 것과 유사한 재료 및 방법을 이용하여 형성될 수 있다. 따라서, 상세한 설명들을 위하여, 실시예 2가 참조될 수 있다.

[0247] 이 때, 에칭이 수행되어 제 1 전극(242a)과 제 2 전극(242b)의 단부들이 테이퍼 형상(tapered shape)을 갖는다. 상기 제 1 전극(242a)과 상기 제 2 전극(242b)의 단부들이 테이퍼 형상을 갖는 경우에, 단부들은 나중에 형성될 산화물 반도체층에 의해 쉽게 덮여질 수 있고 상기 산화물 반도체층의 단절(disconnection)이 방지될 수 있다. 또한, 나중에 형성될 게이트 절연층의 커버리지(coverage)가 개선되고 상기 게이트 절연층의 단절이 방지될 수 있다.

[0248] 여기서, 테이퍼각(taper angle)은, 예를 들면,  $30^{\circ}$  보다 크거나 같고  $60^{\circ}$  보다 작다. 층이 단면에 수직한 방향(기판의 표면과 수직한 평면)으로부터 관찰되는 경우에, 테이퍼각은 테이퍼 형상을 갖는 층(예를 들면, 제 1 전극(242a))의 측면과 하부 표면에 의해 형성된 경사각(tilt angle)이라는 것에 주의한다.

[0249] 상부 트랜지스터의 채널 길이(L)는 제 1 전극(242a)의 하부 에지부와 제 2 전극(242b)의 하부 에지부 사이의 거리에 의해 결정된다. 25nm보다 작은 채널 길이(L)를 갖는 트랜지스터가 형성되는 경우에 사용된 마스크를 형성하기 위한 광 노출을 위하여, 그의 파장이 몇 나노미터 내지 몇십 나노미터만큼 짧은 초자외선 광을 이용하는 것이 바람직하다는 것에 주의한다. 초자외선 광에 의한 광 노출에서, 해상도는 높고 초점 심도는 크다. 이러한 이유들로, 나중에 형성될 트랜지스터의 채널 길이(L)는 10nm보다 크거나 같고 1000nm( $1\mu\text{m}$ )보다 작거나 같은 범위에 있을 수 있고, 회로는 더 고속으로 동작할 수 있다. 또한, 미세화가 반도체 장치의 낮은 전력 소비를 이끌 수 있다.

[0250] 여기서, 트랜지스터(262)의 제 1 전극(242a)과 트랜지스터(260)의 게이트 전극(210)은 서로 직접 접속된다(도 8a).

[0251] 다음, 절연층(243a)과 절연층(243b)이 제 1 전극(242a)과 제 2 전극(242b) 위에 각각 형성된다(도 8b). 상기 절연층(243a)과 상기 절연층(243b)이 다음 방식으로 형성된다: 상기 제 1 전극(242a)과 상기 제 2 전극(242b)을 덮는 절연층이 형성되고 선택적으로 에칭된다. 상기 절연층(243a)과 상기 절연층(243b)은 나중에 형성된 게이트 전극의 일부와 중첩하도록 형성된다. 이러한 절연층이 제공될 때, 상기 게이트 전극과 상기 소스 또는 드레인 전극 사이의 커패시턴스가 감소될 수 있다.

[0252] 절연층(243a)과 절연층(243b)이 산화 실리콘, 산화질화 실리콘, 질화 실리콘, 또는 산화 알루미늄과 같은 무기 절연 재료를 포함하는 재료를 이용하여 형성될 수 있다. 특히, 게이트 전극과 소스 또는 드레인 전극 사이의 커패시턴스가 충분히 감소될 수 있기 때문에 낮은 유전 상수를 갖는 재료(낮은-k 재료)가 상기 절연층(243a)과 상기 절연층(243b)을 형성하는데 사용되는 것이 바람직하다. 이러한 재료를 이용하여 형성된 다공성 절연층이 상기 절연층(243a)과 상기 절연층(243b)으로 이용될 수 있다는 것에 주의한다. 다공성 절연층은 고밀도를 갖는 절연층보다 낮은 유전 상수를 가지며; 따라서, 게이트 전극과 소스 또는 드레인 전극 사이의 커패시턴스가 더욱 감소될 수 있다.

[0253] 게이트 전극과 소스 또는 드레인 전극 사이의 커패시턴스의 감소의 관점에서, 절연층(243a)과 절연층(243b)이 형성되는 것이 바람직하지만; 상기 절연층(243a)과 상기 절연층(243b)이 없는 구조가 채용될 수 있다는 것에 주의한다.

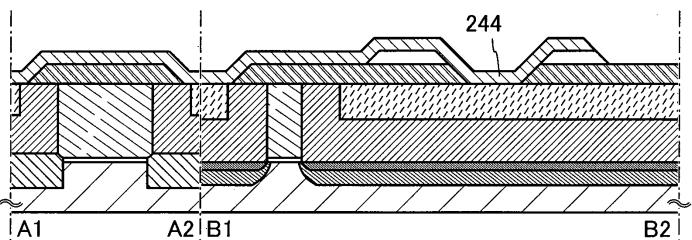

[0254] 다음, 제 1 전극(242a)과 제 2 전극(242b)을 덮도록 산화물 반도체층이 형성되고, 이후 산화물 반도체층이 선택

적으로 예칭되어, 산화물 반도체층(244)이 형성된다(도 8c). 상기 산화물 반도체층(244)이 실시예 2에서 설명된 산화물 반도체층의 것과 유사한 재료 및 방법을 이용하여 형성될 수 있다. 상세한 설명들을 위하여, 실시예 2가 참조될 수 있다.

[0255] 실시예 2에서 설명된 것과 같이, 산화물 반도체층이 스퍼터링법에 의해 형성되기 전에, 주입된 아르곤 가스로 플라즈마가 생성되는 역 스퍼터링이 수행되는 것이 바람직하고, 따라서 산화물 반도체층이 형성될 표면(예를 들면, 절연층(230)의 표면)에 부착된 먼지가 제거된다는 것에 주의한다.

[0256] 형성된 산화물 반도체층으로 불소가 첨가되고, 열 처리(제 1 열 처리)가 수행된다. 불소를 첨가하기 위한 처리의 방법과 열 처리(제 1 열 처리)의 방법에 대해, 실시예 2에서 설명된 장치들 및 방법들 중 임의의 것이 적용될 수 있다. 따라서, 상세한 설명들을 위하여, 실시예 2가 참조될 수 있다.

[0257] 침착된 산화물 반도체층으로의 불소의 첨가와 열 처리(제 1 열 처리)를 통해, 잔류 불순물이 감소될 수 있고, 따라서 i-형(진성) 또는 실질적으로 i-형 산화물 반도체층이 얻어질 수 있다. 잔류 불순물이 감소된 i-형(진성) 또는 실질적으로 i-형 산화물 반도체층을 포함하는 트랜지스터는 임계 전압에서의 작은 변동과 작은 오프 상태 전류와 같은 극히 탁월한 특성들을 구현할 수 있다.

[0258] 본 실시예의 상부 트랜지스터는 일부 경우들에서 산화물 반도체층에 불소를 포함할 수 있다. 상기 산화물 반도체층의 할로겐 원소는 짹지어지지 않은(unpaired) 전자를 갖는 금속 원자로 쉽게 결합되어 맹글링 결합이 종결된다. 따라서, 불순물로 존재하는 수소 또는 수산기와 금속 원자가 결합되는 것이 방지될 수 있으며, 불순물 준위의 형성이 방지될 수 있다.

[0259] 산화물 반도체층의 예칭은 열 처리(제 1 열 처리) 전 또는 후에 수행될 수 있다는 것에 주의한다. 전식 예칭이 소자의 미세화의 관점에서 바람직하지만, 습식 예칭이 또한 이용될 수 있다. 예칭 가스와 에천트는 예칭될 층의 재료에 따라 적절하게 선택될 수 있다. 소자의 누출이 문제가 아닌 경우에, 산화물 반도체층은 섬형 산화물 반도체층으로 처리될 필요가 없다는 것에 주의한다.

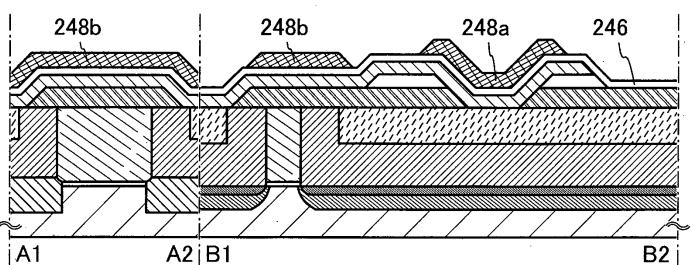

[0260] 다음, 산화물 반도체층(244)과 접하는 게이트 절연층(246)이 형성되고, 이후 게이트 전극(248a)과 전극(248b)이 각각 상기 게이트 절연층(246) 위의 상기 산화물 반도체층(244)과 중첩하는 영역과 제 1 전극(242a)과 중첩하는 영역에서 형성된다(도 8d). 상기 게이트 절연층(246)은 실시예 2에서 설명된 게이트 절연층의 것과 유사한 재료 및 방법을 이용하여 형성될 수 있다.

[0261] 형성된 게이트 절연층(246)은 불활성 가스 분위기 또는 산소 분위기에서 제 2 열 처리를 거치게 되는 것이 바람직하다. 상기 제 2 열 처리는 실시예 2에서 설명된 것과 유사한 방식으로 수행될 수 있다. 상기 제 2 열 처리는 트랜지스터의 전기적 특성들의 변동을 감소시킬 수 있다. 또한, 게이트 절연층(246)이 산소를 함유하는 경우에, 산소가 산화물 반도체층(244)의 산소 결손들을 감소시키도록 상기 산화물 반도체층(244)으로 공급될 수 있으며, 따라서 i-형(진성) 또는 실질적으로 i-형 산화물 반도체층이 형성될 수 있다.

[0262] 본 실시예에서, 게이트 절연층(246)의 형성 후에 제 2 열 처리가 수행되고; 상기 제 2 열 처리의 타이밍은 이에 제한되지 않는다는 것에 주의한다. 예를 들어, 상기 제 2 열 처리가 게이트 전극의 형성 후에 형성될 수 있다.

[0263] 상술된 바와 같이, 불소의 첨가 후에 제 1 열 처리를 수행하는 것에 의해, 산화물 반도체층(244)이 정제될 수 있으며 따라서 산화물 반도체층(244)의 주성분들 이외의 불순물들이 가능한 한 포함되지 않게 된다.

[0264] 실시예 2에서 설명된 게이트 전극(611)의 것과 유사한 재료 및 방법을 이용하여 게이트 전극(248a)이 형성될 수 있다. 게다가, 상기 게이트 전극(248a)의 형성과 동시에, 상기 전극(248b)이 도전층을 선택적으로 예칭하는 것에 의해 형성될 수 있다. 상세한 설명들을 위해, 실시예 2가 참조될 수 있다.

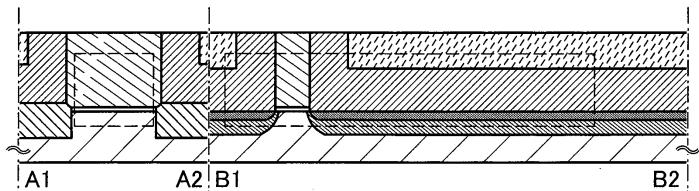

[0265] 다음, 절연층(250)과 절연층(252)이 게이트 절연층(246), 게이트 전극(248a), 및 전극(248b) 위에 형성된다(도 9a). 절연층(250)과 절연층(252)은 실시예 1에서 설명된 절연층(507)과 보호 절연층(508)의 것과 유사한 재료들 및 방법들을 이용하여 형성될 수 있다. 상세한 설명들을 위하여, 실시예 1이 참조될 수 있다.

[0266] 다음, 제 2 전극(242b)에 도달하는 개구부가 게이트 절연층(246), 절연층(250), 및 절연층(252)에 형성된다(도 9b). 개구부는 마스크 등을 이용한 선택적 예칭에 의해 형성된다.

[0267] 이후, 전극(254)이 개구부에 형성되고, 상기 전극(254)과 접하는 배선(256)이 절연층(252) 위에 형성된다.

[0268] 예를 들어, 전극(254)이 다음 방식으로 형성될 수 있다: 도전층이 PVD(물리적 증착)법, CVD법, 등에 의해 개구부를 포함하는 영역에 형성되고, 이후, 도전층이 예칭 처리, CMP, 등에 의해 부분적으로 제거된다.

- [0269] 구체적으로, PVD법에 의해 개구부들을 포함하는 영역에 얇은 티타늄막이 형성되고 CVD법에 의해 얇은 질화 티타늄막이 형성되며, 이후 텅스텐막이 개구부로 매립되어(embedded) 형성되는 방법을 채용하는 것이 바람직하다. 여기서, PVD법에 의해 형성된 티타늄막은, 하부 전극(여기서, 제 2 전극(242b)) 등과의 접촉 저항을 감소시키기 위하여, 티타늄막이 형성되는 표면 상에 형성된 산화물막(예를 들면, 자연 산화물막)을 감소시키는 기능을 갖는다. 티타늄막의 형성 후에 형성된 질화 티타늄막은 도전성 재료의 확산을 막는 배리어 기능을 갖는다. 배리어막이 티타늄, 질화 티타늄, 등을 이용하여 형성된 후, 구리막이 도금법(plating)에 의해 형성될 수 있다.

- [0270] 전극(254)이 도전층의 일부를 제거하는 것에 의해 형성되는 경우에, 도전층의 표면이 처리되어 평坦해지는 것이 바람직하다는 것에 주의한다. 예를 들어, 얇은 티타늄막 또는 얇은 질화 티타늄막이 개구부들을 포함하는 영역에 형성되고 이후 텅스텐막이 개구부에 매립되도록 형성될 때, 파잉 텅스텐, 티타늄, 질화 티타늄, 등이 제거될 수 있으며 표면의 평탄화가 다음 CMP 처리에 의해 개선될 수 있다. 전극(254)의 표면을 포함하는 표면이 이러한 방식으로 평탄화되는 경우에, 전극, 배선, 절연층, 반도체층, 등이 나중 단계들에서 양호하게 형성될 수 있다.

- [0271] 실시예 2에서 설명된 게이트 전극(611)에 포함된 배선의 것과 유사한 재료 및 방법을 이용하여 배선(256)이 형성될 수 있다. 상세한 설명들을 위해, 실시예 2가 참조될 수 있다.

- [0272] 상기 단계들을 통하여, 정제된 산화물 반도체층(244)을 포함하는 트랜지스터(262)와 커패시터(264)가 완성된다(도 9c).

- [0273] 정제된 진성 산화물 반도체층(244)의 사용으로, 트랜지스터의 오프 상태 전류가 충분히 작게 만들어질 수 있다. 이후, 이러한 트랜지스터를 이용하는 것에 의해, 극히 장시간 동안 메모리 데이터가 저장될 수 있는 반도체 장치가 얻어질 수 있다.

- [0274] 예로서 상술된 본 실시예의 방법을 이용하여, 하부에 산화물 반도체 이외의 반도체 재료를 포함하는 트랜지스터와 상부에 산화물 반도체를 포함하는 트랜지스터를 포함하는 반도체 장치가 제작될 수 있다.

- [0275] 게이트 전극(210)과 제 1 전극(242a)이 서로 직접 접속될 때, 접촉 면적이 감소될 수 있으므로, 반도체 장치의 더 높은 접착화가 성취될 수 있다. 따라서, 메모리 장치로 이용될 수 있는 반도체 장치의 단위 면적당 저장 용량이 증가될 수 있다.

- [0276] 본 실시예에서 설명된 구조들, 방법들, 등은 다른 실시예들에서 설명된 구조들, 방법들, 등의 임의의 것과 적절하게 조합될 수 있다.

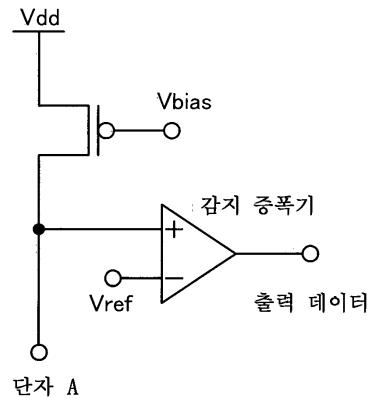

- [0277] (실시예 5)

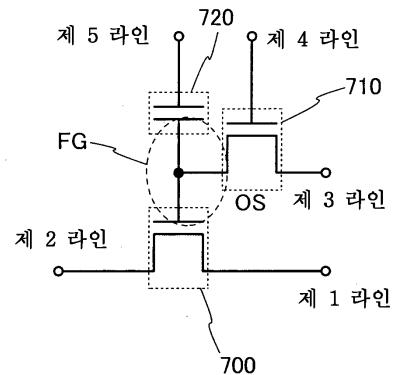

- [0278] 본 실시예에서, 여기서 개시된 본 발명의 실시예에 따른 반도체 장치의 응용 예들이 도 13a1, 도 13a2, 및 도 13b를 참조하여 설명될 것이다. 여기서, 메모리 장치의 예들이 설명될 것이다. 회로도에서, 트랜지스터가 산화물 반도체를 포함한다는 것을 나타내기 위하여 "OS"가 트랜지스터 옆에 기록된다는 것을 주의한다.

- [0279] 도 13a1에 도시된 반도체 장치에서, 제 1 배선(제 1 라인)이 트랜지스터(700)의 소스 전극으로 전기적으로 접속되고, 제 2 배선(제 2 라인)이 트랜지스터(700)의 드레인 전극으로 전기적으로 접속된다. 제 3 배선(제 3 라인)이 트랜지스터(710)의 소스 전극과 드레인 전극 중 다른 하나로 전기적으로 접속되고, 제 4 배선(제 4 라인)이 상기 트랜지스터(710)의 게이트 전극으로 전기적으로 접속된다. 상기 트랜지스터(700)의 게이트 전극과 상기 트랜지스터(710)의 상기 소스 전극 및 상기 드레인 전극 중 하나가 커패시터(720)의 전극들 중 하나로 전기적으로 접속된다. 제 5 배선(제 5 라인)이 커패시터(720)의 다른 전극으로 전기적으로 접속된다.

- [0280] 여기서, 산화물 반도체를 포함하는 트랜지스터가 트랜지스터(710)로 이용된다. 여기서, 산화물 반도체를 포함하는 트랜지스터로서, 예를 들면, 상기 실시예에서 설명된 트랜지스터(262)가 이용될 수 있다. 산화물 반도체를 포함하는 트랜지스터는 상당히 작은 오프 상태 전류의 특성을 갖는다. 따라서, 트랜지스터(710)가 턴 오프될 때, 상기 트랜지스터(700)의 게이트 전극의 포텐셜이 극히 장시간 동안 보유될 수 있다. 커패시터(720)를 제공하는 것에 의해, 트랜지스터(700)의 게이트 전극에 주어진 전하의 보유와 보유된 데이터의 판독이 쉽게 수행될 수 있다. 여기서, 상기 커패시터(720)로서, 예를 들어, 상기 실시예에서 설명된 상기 커패시터(264)가 이용될 수 있다.

- [0281] 게다가, 산화물 반도체 이외의 반도체 재료를 포함하는 트랜지스터가 트랜지스터(700)로 이용된다. 산화물 반도체 이외의 반도체 재료로서, 예를 들면, 실리콘, 게르마늄, 실리콘 게르마늄, 탄화 실리콘, 갈륨 비소, 등이 이용될 수 있고, 단결정 반도체가 사용되는 것이 바람직하다. 대안적으로, 유기 반도체 재료 등이 이용될 수 있다. 이러한 반도체 재료를 포함하는 트랜지스터는 고속으로 쉽게 동작될 수 있다. 여기서, 산화물 반도체 이

외의 반도체 재료를 포함하는 트랜지스터로서, 예를 들면, 상기 실시예에서 설명된 트랜지스터(260)가 이용될 수 있다.

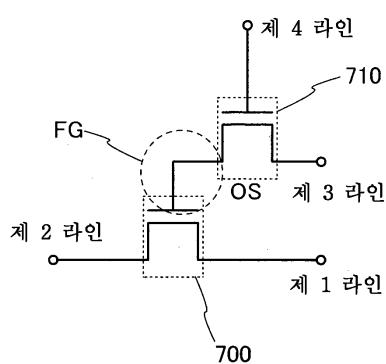

[0282] 대안적으로, 도 13b에 도시된 바와 같은 커패시터(720)가 없는 구조가 채용될 수 있다.

[0283] 도 13a1에 도시된 반도체 장치는 트랜지스터(700)의 게이트 전극의 포텐셜이 보유될 수 있는 장점을 사용하여, 다음 방식으로 데이터를 기록, 보유 및 판독할 수 있다.

[0284] 먼저, 데이터의 기록과 보유가 설명될 것이다. 먼저, 제 4 배선의 포텐셜이 트랜지스터(710)가 온(on)이 되는 포텐셜로 설정되어, 트랜지스터(710)가 턴 온된다. 따라서, 제 3 배선의 포텐셜이 트랜지스터(700)의 게이트 전극과 커패시터(720)로 공급된다. 즉, 미리 정해진 전하가 상기 트랜지스터(700)의 상기 게이트 전극으로 주어진다(기록). 여기서, 상이한 포텐셜들을 공급하는 두 전하들(이후, 낮은 포텐셜을 공급하는 전하( $Q_L$ )로 불리고 높은 포텐셜을 공급하는 전하( $Q_H$ )로 불린다) 중 하나가 상기 트랜지스터(700)의 게이트 전극으로 주어진다. 셋 또는 그 이상의 상이한 포텐셜들을 주는 전하들이 저장 커패시터를 개선시키기 위해 인가될 수 있다는 것에 주의한다. 그 후, 제 4 배선의 포텐셜이 트랜지스터(710)가 오프(off)되는 포텐셜로 설정되어, 트랜지스터(710)가 턴오프된다. 따라서, 트랜지스터(700)의 게이트 전극으로 주어진 전하가 보유된다(보유).

[0285] 트랜지스터(710)의 오프 상태 전류가 상당히 작기 때문에, 트랜지스터(700)의 게이트 전극의 전하가 장시간 동안 보유된다.

[0286] 둘째로, 데이터의 판독이 설명될 것이다. 미리 정해진 포텐셜(일정한 포텐셜)이 제 1 배선으로 공급되는 동안 적절한 포텐셜(판독 포텐셜)을 제 5 배선에 공급할 때, 제 2 배선의 포텐셜은 트랜지스터(700)의 게이트 전극에서 유지된 전하의 양에 따라 변화한다. 이는 일반적으로, 트랜지스터(700)가 n-채널형 트랜지스터일 때,  $Q_H$ 가 상기 트랜지스터(700)의 상기 게이트 전극에 주어진 경우의 명백한 임계 전압( $V_{th,H}$ )이  $Q_L$ 이 상기 트랜지스터(700)의 상기 게이트 전극에 주어지는 경우의 명백한 임계 전압( $V_{th,L}$ )보다 낮기 때문이다. 여기서, 명백한 임계 전압이란 상기 트랜지스터(700)를 턴 온하기 위해 필요한, 제 5 배선의 포텐셜을 의미한다. 따라서, 제 5 배선의 포텐셜이  $V_{th,H}$ 와  $V_{th,L}$ 사이의 중간 포텐셜인 포텐셜( $V_0$ )로 설정될 때, 상기 트랜지스터(700)의 상기 게이트 전극으로 주어진 전하가 결정될 수 있다. 예를 들어,  $Q_H$ 가 기록에 주어지는 경우에, 제 5 배선의 포텐셜이  $V_0(>V_{th,H})$ 으로 설정될 때, 트랜지스터(700)가 턴 온된다.  $Q_L$ 이 기록에 주어지는 경우에, 제 5 배선의 포텐셜이  $V_0(<V_{th,L})$ 로 설정되는 때에라도, 상기 트랜지스터(700)는 오프 상태에 머무른다. 따라서, 보유된 데이터가 제 2 배선의 포텐셜로부터 판독될 수 있다.

[0287] 메모리 셀들이 이용되도록 배열되는 경우에, 의도된 메모리 셀로부터만 데이터를 판독하는 것이 필요하다는 것에 주의한다. 따라서, 미리 정해진 메모리 셀의 데이터가 판독되고 다른 메모리 셀들의 데이터가 판독되지 않기 위하여, 트랜지스터들(700)이 메모리 셀들 사이에서 별별로 접속되는 경우에, 게이트 전극의 상태에 상관없이 상기 트랜지스터(700)가 오프되는 포텐셜, 즉,  $V_{th,H}$ 보다 낮은 포텐셜이 그의 데이터가 판독되지 않은 메모리 셀들의 제 5 배선들로 공급될 수 있다. 상기 트랜지스터들(700)이 메모리 셀들 사이에서 직렬로 접속되는 경우에, 게이트 전극의 상태에 상관없이 상기 트랜지스터(700)가 온되는 포텐셜, 즉,  $V_{th,L}$ 보다 높은 포텐셜이 그의 데이터가 판독되지 않은 메모리 셀들의 제 5 배선들로 공급될 수 있다.

[0288] 세번째로, 데이터의 재기록이 설명될 것이다. 데이터의 재기록은 상술된 데이터의 기록 및 보유의 것과 유사한 방식으로 수행된다. 즉, 제 4 배선의 포텐셜이 트랜지스터(710)가 온상태로 되는 포텐셜로 설정되어, 트랜지스터(710)가 온상태로된다. 따라서, 제 3 배선의 포텐셜(새로운 데이터와 관련된 포텐셜)이 상기 트랜지스터(700)의 게이트 전극과 상기 커패시터(720)로 공급된다. 그 후에, 제 4 배선의 포텐셜이 트랜지스터(710)가 오프가 되는 포텐셜로 설정되어, 트랜지스터(710)가 턴 오프된다. 따라서, 새로운 데이터와 관련된 전하가 상기 트랜지스터(700)의 상기 게이트 전극으로 주어진다.

[0289] 여기서 개시된 본 발명에 따른 반도체 장치에서, 상술된 바와 같이 데이터의 다른 기록에 의해 데이터가 직접 재기록될 수 있다. 따라서, 플래시 메모리 등에서 요구된 높은 전압의 이용으로 플로팅 게이트로부터 전하를 추출하는 것은 불필요하고, 따라서 소거 동작으로 인한 동작 속도의 감소가 억제될 수 있다. 다시 말하면, 반도체 장치의 고속 동작이 구현될 수 있다.

[0290] 트랜지스터(710)의 소스 전극 또는 드레인 전극이 트랜지스터(700)의 게이트 전극에 전기적으로 접속되어, 비휘

발성 메모리 소자로 이용되는 플로팅 게이트 트랜지스터의 플로팅 게이트의 것과 유사한 기능을 갖게 된다는 것에 주의한다. 따라서, 트랜지스터(710)의 소스 전극 또는 드레인 전극이 트랜지스터(700)의 게이트 전극으로 전기적으로 접속되는 도면의 일부가 일부 경우들에서 플로팅 게이트부(FG)라고 불린다. 트랜지스터(710)가 오프일 때, 플로팅 게이트부(FG)는 절연체에 매립되는 것으로 여겨질 수 있고 따라서 플로팅 게이트부(FG)에서 전하가 보유된다. 산화물 반도체를 포함하는 상기 트랜지스터(710)의 오프 상태 전류의 양은 실리콘 반도체 등을 포함하는 트랜지스터의 오프 상태 전류의 양의 십만분의 일보다 작거나 같고; 따라서 상기 트랜지스터(710)로부터의 누설 전류로 인해 플로팅 게이트부(FG)에 누적된 전하의 손실은 무시할만 하다. 즉, 산화물 반도체를 포함하는 트랜지스터(710)로, 전력이 공급되지 않고 데이터를 유지할 수 있는 비휘발성 메모리 장치가 구현될 수 있다.

[0291] 예를 들어, 트랜지스터(710)의 오프 상태 전류가 실온에서  $10zA(1 zA(\text{펩토암페어}))$ 는  $1 \times 10^{-21} A$ 보다 작거나 같고 커패시터(720)의 커패시턴스는 약  $10fF$ 일 때, 데이터는  $10^4$  초 또는 그보다 길게 보유될 수 있다. 보유 시간은 트랜지스터 특성들과 커패시턴스 값에 의존한다는 것은 말할 필요도 없다.

[0292] 또한, 그러한 경우에, 종래의 플로팅 게이트 트랜지스터에서 주목받지 못한, 게이트 절연막(터널 절연막)의 악화 문제가 일어나지 않는다. 즉, 종래에는 문제라고 여겨졌던, 플로팅 게이트로의 전자의 주입으로 인한 게이트 절연막의 악화가 해결될 수 있다. 이는 이론적으로 기록 횟수에 제한이 없다는 것을 의미한다. 또한, 종래 플로팅 게이트 트랜지스터에서 기록 또는 소거를 위해 필요한 고전압이 필요하지 않다.

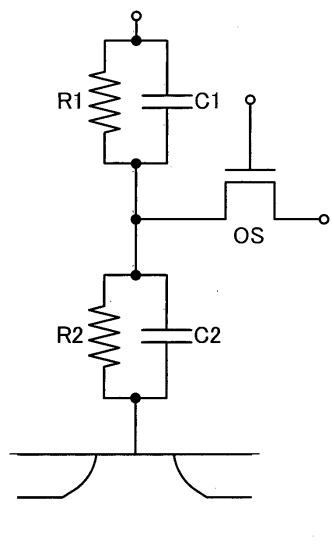

[0293] 도 13a1의 반도체 장치의 트랜지스터들과 같은 구성성분들은 도 13a2에 도시된 바와 같은 저항 및 커패시터를 포함하는 것으로 여겨질 수 있다. 즉, 도 13a2에서, 트랜지스터(700)와 커패시터(720)는 각각 저항과 커패시터를 포함하는 것으로 여겨진다. R1과 C1은 각각 커패시터(720)의 저항 값과 커패시턴스 값을 나타낸다는 것에 주의한다. 저항 값(R1)은 상기 커패시터(720)에 포함된 절연층의 저항 값에 대응한다. 또한, R2와 C2는 각각 상기 트랜지스터(700)의 저항 값과 커패시턴스 값을 나타낸다. 저항 값(R2)은 상기 트랜지스터(700)가 온일 때 게이트 절연층의 저항 값에 대응한다. 상기 커패시턴스 값(C2)은 소위 게이트 커패시턴스(게이트 전극과 소스 전극 및 드레인 전극의 각각의 사이에서 형성된 커패시턴스 및 게이트 전극과 채널 형성 영역 사이에서 형성된 커패시턴스)의 커패시턴스 값에 대응한다.

[0294] 트랜지스터(710)가 오프인 경우에 소스 전극과 드레인 전극 사이의 저항 값(또한 유효 저항이라고도 불림)은 ROS에 의해 표기된다. 트랜지스터(710)의 게이트 누설이 상당히 작은 조건 하에서 R1과 R2가  $R1 \geq ROS$  및  $R2 \geq ROS$ 의 관계들을 만족할 때, 전하를 보유하는 기간(또한 데이터 보유(retention) 기간이라고도 불림)이 트랜지스터(710)의 오프 상태 전류에 의해 주로 결정된다.

[0295] 한편, 상기 관계들이 만족되지 않을 때, 트랜지스터(710)의 오프 상태 전류가 충분히 작을 때라도 충분한 보유 기간을 확보하는 것은 어렵다. 이는 트랜지스터(710)의 오프 상태 전류 이외의 누설 전류(예를 들면, 소스 전극과 게이트 전극 사이에서 생성된 누설 전류)가 크기 때문이다. 따라서, 본 실시예에서 개시된 반도체 장치가 상기 관계들을 만족하는 것이 바람직하다.

[0296] 또한, C1과 C2는 관계:  $C1 \geq C2$ 를 만족하는 것이 바람직하다. 이는, C1이 크다면, 제 5 배선에 의해 플로팅 게이트부(FG)의 포텐셜을 제어할 때 제 5 배선의 포텐셜이 상기 플로팅 게이트부(FG)로 효율적으로 공급될 수 있기 때문이며, 따라서 제 5 배선으로 공급된 포텐셜들 사이(예를 들면, 판독 포텐셜과 비-판독 포텐셜)의 차이가 작게 만들어질 수 있다.

[0297] 상기 관계가 만족될 때, 보다 양호한 반도체 장치가 구현될 수 있다. R1과 R2는 트랜지스터(700)의 게이트 절연층과 커패시터(720)의 절연층에 의해 제어된다는 것에 주의한다. C1과 C2에 대해서도 동일하게 말할 수 있다. 따라서, 게이트 절연층의 재료, 두께, 등이 상기 관계들을 만족하도록 적절하게 설정되는 것이 바람직하다.

[0298] 본 실시예의 반도체 장치에서, 플로팅 게이트부(FG)는 플래시 메모리 등의 플로팅 게이트 트랜지스터의 플로팅 게이트의 것과 동등한 기능을 갖지만, 본 실시예의 플로팅 게이트부(FG)는 플래시 메모리 등의 플로팅 게이트의 것과 본질적으로 상이한 특성을 갖는다. 플래시 메모리에서, 게이트를 제어하기 위해 인가된 전압이 높기 때문에, 포텐셜이 인근 셀의 플로팅 게이트에 악영향을 끼치는 것을 방지하기 위하여 셀들 사이에 적절한 거리를 유지할 필요가 있다. 이는 반도체 장치들의 고집적화를 저해하는 요소들 중 하나이다. 이러한 요소는 플래시 메모리의 다음 기본 원리에 기인한다: 터널링 전류가 높은 전계의 인가에 의해 생성된다.

[0299] 또한, 플래시 메모리의 상기 원리 때문에, 절연막의 열화가 진행되고 따라서 제기록 횟수들(대략  $10^4$  내지  $10^5$  회) 상의 제한의 다른 문제가 발생한다.

- [0300] 여기서 개시된 본 발명에 따른 반도체 장치는 산화물 반도체를 포함하는 트랜지스터의 스위칭에 의해 동작되며 터널링 전류에 의한 전하 주입의 상술된 원리를 이용하지 않는다. 즉, 플래시 메모리와 달리, 전하의 주입을 위한 높은 전계는 필요하지 않다. 따라서, 고집적화를 용이하게 하는, 인근 셀 상의 제어 게이트로부터의 높은 전계의 영향을 고려할 필요가 없다.

- [0301] 또한, 터널링 전류에 의한 전하 주입이 사용되지 않기 때문에, 메모리 셀의 열화의 원인이 존재하지 않는다. 다시 말해, 여기서 개시된 본 발명에 따른 반도체 장치는 플래시 메모리보다 높은 내구성과 신뢰성을 갖는다.

- [0302] 게다가, 본 발명에 따른 반도체 장치는 높은 전계가 필요하지 않고 (부스터 회로(booster circuit)와 같은) 큰 주변 회로가 필요하지 않은 플래시 메모리에 대한 장점들을 갖는다.

- [0303] 커패시터(720)에 포함된 절연층의 유전 상수( $\epsilon r1$ )가 트랜지스터(700)에 포함된 절연층의 유전 상수( $\epsilon r2$ )와 다른 경우에,  $2 \cdot S2 \geq S1$ (바람직하게,  $S2 \geq S1$ )이 만족되면서  $C1 \geq C2$ 를 만족시키는 것은 쉽고, 여기서  $S1$ 은 커패시터(720)에 포함된 절연층의 면적이고  $S2$ 는 트랜지스터(700)의 게이트 커패시턴스를 형성하는 절연층의 면적이다. 즉, 커패시터(720)에 포함된 절연층의 면적이 작다는 것이 만족되면서  $C1 \geq C2$ 를 만족시키는 것은 쉽다. 구체적으로, 예를 들어, 산화 하프늄과 같은 높은-k 재료로 형성된 막 또는 산화 하프늄과 같은 높은-k 재료로 형성된 막과 산화물 반도체로 형성된 막을 포함하는 적층이 상기 커패시터(720)에 포함된 절연층을 위해 이용되어  $\epsilon r1$ 이 10 또는 그 이상, 바람직하게는 15 또는 그 이상으로 설정될 수 있고, 산화 실리콘의 게이트 커패시턴스를 형성하는 절연층으로 이용되어  $\epsilon r2$ 가 3 내지 4로 설정될 수 있다.

- [0304] 이러한 구조들의 조합은 여기서 개시된 본 발명에 따른 반도체 장치의 더 높은 집적화를 가능하게 한다.

- [0305] 전자들이 다수 캐리어들인 n-채널형 트랜지스터가 상기 서술에서 이용되며; 정공들이 다수 캐리어들인 p-채널형 트랜지스터가 n-채널형 트랜지스터 대신 이용될 수 있다는 것은 말할 필요가 없다는 것에 주의한다.

- [0306] 상술된 바와 같이, 여기서 개시된 본 발명의 실시예에 따른 반도체 장치는 오프 상태에서 소스 및 드레인 사이의 누설 전류(오프 상태 전류)가 작은 기록 트랜지스터와, 상기 기록 트랜지스터의 것과는 상이한 반도체 재료를 포함하는 판독 트랜지스터와, 커패시터를 포함하는 비휘발성 메모리 셀을 갖는다.

- [0307] 기록 트랜지스터의 오프 상태 전류는 주위 온도(예를 들면, 25°C)에서 바람직하게는  $100zA(1 \times 10^{-19} A)$ 보다 작고, 더 바람직하게는  $10 zA(1 \times 10^{-20} A)$ 보다 작거나 같고, 더욱 더 바람직하게는  $1 zA(1 \times 10^{-21} A)$ 보다 작거나 같다. 일반적인 실리콘 반도체의 경우에, 이러한 작은 오프 상태 전류를 성취하는 것은 어렵다. 그러나, 적절한 조건 하에서 산화물 반도체를 처리하는 것에 의해 얻어진 트랜지스터에서, 작은 오프 상태 전류가 성취될 수 있다. 따라서, 산화물 반도체를 포함하는 트랜지스터가 기록 트랜지스터로 이용되는 것이 바람직하다.

- [0308] 게다가, 산화물 반도체를 포함하는 트랜지스터는 작은 서브임계 스윙(subthreshold swing)(S 戛)을 갖고, 따라서 이동도가 비교적 낮을 때에도 스위칭 속도가 충분히 높을 수 있다. 따라서, 기록 트랜지스터로서 트랜지스터를 이용하는 것에 의해, 플로팅 게이트부(FG)로 주어진 기록 펠스의 상승은 매우 가파르게 될 수 있다. 또한, 오프 상태 전류가 작기 때문에, 플로팅 게이트부(FG)에서 보유된 전하의 양이 감소될 수 있다. 즉, 기록 트랜지스터로서 산화물 반도체를 포함하는 트랜지스터를 이용하는 것에 의해, 데이터의 재기록이 고속으로 수행될 수 있다.

- [0309] 판독 트랜지스터의 오프 상태 전류에는 제한이 없지만, 판독 속도를 증가시키기 위하여 고속으로 동작하는 트랜지스터가 판독 트랜지스터로 이용되는 것이 바람직하다. 예를 들어, 1 나노초 또는 그보다 낮은 스위칭 속도를 갖는 트랜지스터가 판독 트랜지스터로 이용되는 것이 바람직하다.

- [0310] 이러한 방식으로, 산화물 반도체를 포함하는 트랜지스터가 기록 트랜지스터로 이용되고, 산화물 반도체 이외의 반도체 재료를 포함하는 트랜지스터가 판독 트랜지스터로 이용될 때, 메모리 장치로 이용될 수 있는, 장시간 데이터를 보유하고 고속으로 데이터를 판독하는 것이 가능한 반도체 장치가 얻어질 수 있다.

- [0311] 본 실시예에서 설명된 구조들, 방법들, 등이 다른 실시예들에서 설명된 구조들, 방법들, 등 중 임의의 것과 적절하게 조합될 수 있다.

- [0312] (실시예 6)

- [0313] 본 실시예에서, 여기서 개시된 본 발명의 실시예의 반도체 장치의 적용 예들이 도 14a 및 도 14b 및 도 15a 내지 도 15c를 참조하여 설명될 것이다.

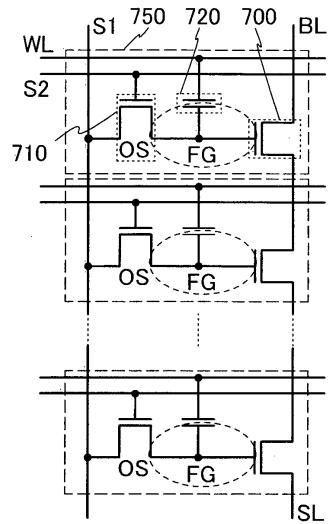

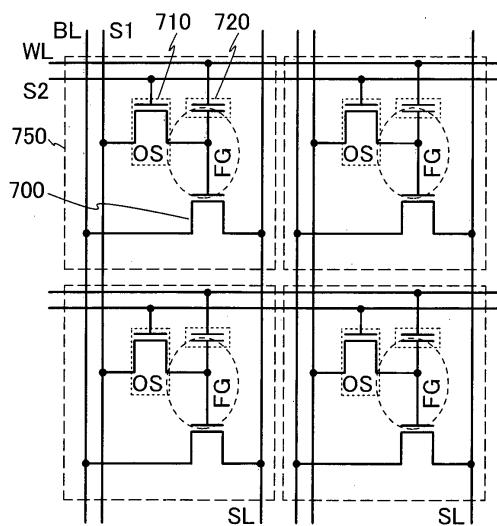

- [0314] 도 14a 및 도 14b는 각각 도 13a1에 도시된 복수의 반도체 장치들(이후로 또한 메모리 셀들(750)로 불림)을 포함하는 반도체 장치들의 회로도들의 예들이다. 도 14a는 상기 메모리 셀들(750)이 직렬로 접속되는 소위 NAND 반도체 장치의 회로도이고, 도 14b는 메모리 셀들(750)이 병렬로 접속되는 소위 NOR 반도체 장치의 회로도이다.

- [0315] 도 14a의 반도체 장치는 소스 라인(SL), 비트 라인(BL), 제 1 신호 라인(S1), 복수의 제 2 신호 라인들(S2), 복수의 워드 라인들(WL), 및 복수의 메모리 셀들(750)을 포함한다. 도 14a에서, 하나의 소스 라인(SL)과 하나의 비트 라인(BL)이 제공되었으나; 본 실시예는 이러한 구조에 제한되지 않는다. 복수의 소스 라인들(SL)과 복수의 비트 라인들(BL)이 제공될 수 있다.

- [0316] 메모리 셀들(750)의 각각에서, 트랜지스터(700)의 게이트 전극, 트랜지스터(710)의 소스 전극 및 드레인 전극 중 하나, 그리고 커패시터(720)의 전극들 중 하나가 서로 전기적으로 접속된다. 제 1 신호 라인(S1)과 트랜지스터(710)의 소스 전극 및 드레인 전극 중 다른 하나가 서로 전기적으로 접속되며, 제 2 신호 라인(S2)과 트랜지스터(710)의 게이트 전극이 서로 전기적으로 접속된다. 워드 라인(WL)과 커패시터(720)의 전극들 중 다른 하나가 서로 전기적으로 접속된다.