(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4199352号

(P4199352)

(45) 発行日 平成20年12月17日(2008.12.17)

(24) 登録日 平成20年10月10日(2008.10.10)

(51) Int.Cl.

G01R 31/28 (2006.01)

H03K 19/00 (2006.01)

F 1

G01R 31/28

H03K 19/00V

B

請求項の数 3 (全 9 頁)

(21) 出願番号 特願平10-365662

(22) 出願日 平成10年12月22日(1998.12.22)

(65) 公開番号 特開平11-281715

(43) 公開日 平成11年10月15日(1999.10.15)

審査請求日 平成17年12月20日(2005.12.20)

(31) 優先権主張番号 068582

(32) 優先日 平成9年12月23日(1997.12.23)

(33) 優先権主張国 米国(US)

(73) 特許権者 590000879

テキサス インスツルメンツ インコーポ

レイテッド

アメリカ合衆国テキサス州ダラス、ノース

セントラルエクスプレスウェイ 135

OO

(74) 代理人 100066692

弁理士 浅村 皓

(74) 代理人 100072040

弁理士 浅村 肇

(74) 代理人 100094673

弁理士 林 銘三

(74) 代理人 100091339

弁理士 清水 邦明

最終頁に続く

(54) 【発明の名称】高電圧インターフェースに用いられるカスコード回路用のテスト容易化回路

## (57) 【特許請求の範囲】

## 【請求項 1】

単一トランジスタの最大電圧ストレス・レベル以上の外部電圧で用いられる試験可能なカスコード出力バッファ回路であって、当該出力バッファ回路は；

前記外部電圧と接地との間に接続されたバイアス回路網であって、前記最大電圧ストレス・レベルに等しい第一のバイアス電圧と、前記外部電圧と当該最大電圧ストレスとの差に等しい第二バイアス電圧とを生成するバイアス回路網と、

アクティブ・デバイスのカスコード構成であって、ソースが前記外部電圧に接続され、ゲートが第一入力に接続され、及びドレインが第一の中間ノードに接続された第一のスイッチング・トランジスタと、ソースが前記第一の中間ノードに接続され、ゲートが前記第二のバイアス電圧に接続され、及びドレインが前記出力バッファ回路の出力ノードに接続された第一のカスコード・トランジスタと、ソースが前記出力ノードに接続され、ゲートが前記第一のバイアス電圧に接続され、及びドレインが第二の中間ノードに接続された第二のカスコード・トランジスタと、及びソースが前記第二の中間ノードに接続され、ゲートが第二の入力に接続され、及びドレインが接地された第二のスイッチング・トランジスタとを有するアクティブ・デバイスのカスコード構成と、

非導通で前記第一及び第二のカスコード・トランジスタの通常動作を示し、導通で前記第一カスコード・トランジスタ又は前記第二のカスコード・トランジスタ何れかのショートを示すテスト回路であって、当該テスト回路は、

ソースが前記外部電圧に接続され、ゲートが前記第一バイアス電圧に接続され、及び

10

20

ドレインが第三の中間ノードに接続された第一バイアス・トランジスタと、ソースが前記第三の中間ノードに接続され、ゲートが前記第一中間ノードに接続され、及びドレインが第四の中間ノードに接続された第一のテスト・トランジスタと、及びソースが前記第三の中間ノードに接続され、ゲートが前記第二の中間ノードに接続され、及びドレインが前記第四の中間ノードに接続された第二のテスト・トランジスタと、及びソースが前記第四の中間ノードに接続され、ゲートが前記第二のバイアス電圧に接続され、及びドレインが接地された第二バイアス・トランジスタとを備え、

たことを特徴とする出力バッファ回路。

#### 【請求項 2】

請求項 1 に記載の出力バッファ回路であって、

10

前記第一入力は前記外部電圧と前記第二のバイアス電圧との間の電圧を有し、

前記第二の入力は前記第一バイアス電圧と接地との間の電圧を有する、

ことを特徴とする出力バッファ回路。

#### 【請求項 3】

請求項 1 に記載の出力バッファ回路であって、

前記第一スイッチング・トランジスタ、前記第一カスコード・トランジスタ、前記第二バイアス・トランジスタ、及び前記第一テスト・トランジスタは P M O S トランジスタであり、前記第二スイッチング・トランジスタ、前記第二カスコード・トランジスタ、前記第一バイアス・トランジスタ、及び前記第二テスト・トランジスタは N M O S トランジスタ、

であることを特徴とする出力バッファ回路。

20

#### 【発明の詳細な説明】

##### 【0001】

##### 【発明の属する技術分野】

本発明は、一般に、テスト容易化回路に関し、より詳しくは、高電圧インターフェースとして使用されるカスコード回路用のテスト容易化回路に関する。

##### 【0002】

##### 【従来の技術】

より低い動作電圧を使用するより新しい技術のデバイス（たとえば、C M O S デバイス）が普及しつつある。それにもかかわらず、古い技術のデバイスとインターフェースする必要が依然として存在する。これらの古いデバイスは、典型的には、単一のトランジスタが許容できる範囲よりも一般に高いより高い動作範囲（たとえば、4 . 5 V から 5 . 5 V ）を有する。いくつかの場合、この高い電圧を許容するように設計されたバッファ回路が、これらの古いデバイスとインターフェースするために使用される。しかしながら、これらの高電圧許容バッファ回路は、より高い電圧レベルとインターフェースするためにレベルシフトを使用することを要するいくつかの新しいC M O S デバイスのためには、不適当である。

30

##### 【0003】

いくつかの低電圧デバイスは、より高い動作電圧を有するデバイスとインターフェースするために、レベルシフト出力を含んでいる。これらのレベルシフト出力は、5 ボルトを許容するトランジスタを使用する。レベルシフトはまた、スイッチング・トランジスタ上の許容できる電圧ストレス・レベルを維持するために、カスコード・トランジスタを使用することによっても達成され得る。しかしながら、カスコード・トランジスタに欠陥があると（たとえば、ドレン - ソース間で短絡していると）、このスイッチング・トランジスタは、一般に、電圧ストレスにより故障する。通常のカスコード設計では、欠陥のあるカスコード・デバイスを容易に検出できない。したがって、通常のカスコード構成がテスト中に適切に作動したとしても、現場において電圧のオーバ・ストレスにより初期故障するかもしれない。

40

##### 【0004】

##### 【発明が解決しようとする課題】

したがって、高電圧インターフェイス回路に使用されるカスコード・デバイス用のテスト容

50

易化回路への需要が起こってきた。本発明によるテスト容易化回路は、内蔵カスコード・トランジスタが正しく動作しているかどうかについて、現場に入る前に決定することを可能にする。

#### 【0005】

##### 【課題を解決するための手段】

本発明の一実施形態によれば、テスト容易化回路網を有するレベルシフト回路が開示される。このレベルシフト回路は、能動デバイスのカスコード構成と、カスコード構成をバイアスするように配置されたバイアス回路網とを含む。カスコード構成は、少なくとも、第1のスイッチング・トランジスタと、第2のスイッチング・トランジスタと、第1および第2のスイッチング・トランジスタ上の電圧ストレスを制限するように配列された第1のカスコード・トランジスタおよび第2のカスコード・トランジスタとを含む。テスト回路網がカスコード・トランジスタの一つまたは両方における短絡の指示を供給するように、テスト回路網はカスコード構成およびバイアス回路網に接続されている。10

#### 【0006】

本発明の他の実施形態によれば、カスコード・デバイス用のテスト容易化回路が開示される。このテスト容易化回路は、少なくとも、一組のトランジスタ対と、一組のバイアス・トランジスタ対とを含む。各トランジスタ対は、第1のテスト・トランジスタと、第2のテスト・トランジスタとを含む。第1のテスト・トランジスタのドレインは第2のテスト・トランジスタのソースに接続され、第1のテスト・トランジスタのソースは第2のテスト・トランジスタのドレインに接続されている。バイアス・トランジスタ対は、一組のテスト・トランジスタ対の第1および第2テスト・トランジスタへ接続されて第1および第2のテスト・トランジスタ上の電圧ストレスを制限する第1および第2のバイアス・トランジスタを含む。トランジスタ対の一組がカスコード回路装置へ接続されると、本発明によるテスト容易化回路はカスコード回路装置内の欠陥の指示を行う。20

#### 【0007】

上述した本発明の実施形態は、種々の技術的な利点を提供する。たとえば、上述した実施形態によるテスト容易化回路は、テストされるカスコード・デバイスの技術的長所を許容するという技術的な利点を提供する。その上、上述した実施形態によるテスト容易化回路は、カスコード・デバイスを使用するレベルシフト回路の信頼性を増加して、そのようなレベルシフト回路が現場において初期故障しないようにすることを助ける。その他の技術的長所は、以下の図面、説明および特許請求の範囲により当業者に明らかになるであろう。30

#### 【0008】

##### 【発明の実施の形態】

本発明の特徴および目的とそれらを達成する仕方とは、以下に、添付図面を用いて詳細に説明される。

カスコード回路装置のトランジスタは、とりわけ、スイッチング・デバイス上の電圧ストレスを制限するために効果的に使用される。そのような回路装置において、カスコード・トランジスタに欠陥があれば問題が生ずる。なぜならば、スイッチング・デバイスは、カスコード・デバイスが制限するように設計されているあらゆる電圧ストレスに晒されるからである。本発明の実施形態によるテスト回路は、内蔵トランジスタが欠陥（たとえば、ドレインからソースへの短絡）について現場へ送られる前にテストされるようにして、現場における回路の信頼性を改良する。本発明の実施形態によるテスト回路は、レベルシフト回路内で使用されるカスコード構成に関連して説明される。しかしながら、本発明の実施形態によるテスト回路は、多数の異なる回路装置に関して有用であることを理解すべきである。40

#### 【0009】

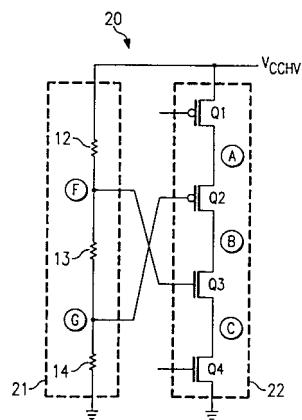

図1は、図2に示すレベルシフト回路20とともに使用されるテスト回路10を図示する。レベルシフト回路20は、高電圧デバイスを低電圧デバイスにインターフェースできるようにする機能を遂行し、バイアス回路網21およびスイッチング回路網22を含む。レベ50

ルシフト回路 2 0 のスイッチング回路網 2 2 は、カスコード・トポロジでカスコード・トランジスタ Q 2 , Q 3 を使用して、スイッチング・トランジスタ Q 1 , Q 4 の電圧ストレスを制限する。バイアス回路網 2 1 は、トランジスタ Q 1 , Q 2 , Q 3 , Q 4 にスレッショルド電圧を設定する。バイアス電圧は、各トランジスタをオーバー・ストレスから保護し、テスト回路を漏洩電流レベルに保ち、出力スイッチング性能を最大化するように、選択される。図 2 の回路の特定の実施形態について、 $V_{CCHV}$  が 5 V で、最大トランジスタ・ストレス・レベルが 3 . 3 V であると仮定する。最適性能は、カスコード・トランジスタ Q 2 , Q 3 上の最大  $V_{GS}$  で得られる。その後、バイアス電圧は、 $F = 3 . 3 V$  、 $G = (5 - 3 . 3) = 1 . 7 V$  である。これらの電圧がテスト回路に適合するかどうかを決定するため、チェックが必要である。

10

#### 【 0 0 1 0 】

スイッチング・トランジスタ Q 1 のソースは高電圧電源  $V_{CCHV}$  に接続され、トランジスタ Q 1 のドレインはカスコード・トランジスタ Q 2 のソースに接続され、スイッチング・トランジスタ Q 1 のゲートは、 $V_{CCHV}$  と接点 G の電圧との間で動作する先行ステージのプリドライバ回路に接続されている。カスコード・トランジスタ Q 2 のドレインはカスコード・トランジスタ Q 3 のドレインに接続され、カスコード・トランジスタ Q 2 のゲートは接点 G でバイアス回路網 2 1 に接続されている。カスコード・トランジスタ Q 3 のソースはスイッチング・トランジスタ Q 4 のドレインに接続され、カスコード・トランジスタ Q 3 のゲートは接点 F でバイアス回路網 2 1 に接続されている。スイッチング・トランジスタ Q 4 のゲートは接点 F の電圧と接地（グランド）との間で作動する先行ステージのプリドライバ回路に接続されている。レベルシフト回路の一つの特定の実施形態において、スイッチング・トランジスタ Q 1 , Q 4 はそれぞれ PMOS および NMOS トランジスタであり、カスコード・トランジスタ Q 2 , Q 3 はそれぞれ PMOS および NMOS トランジスタである。しかしながら、特定のレベルシフト回路装置と特定のタイプのトランジスタの選択とは例示のためだけであることを理解すべきである。他の回路構成およびトランジスタのタイプが可能である。

20

#### 【 0 0 1 1 】

バイアス回路網 2 1 はカスコード・トランジスタ Q 2 , Q 3 を作動にし、カスコード・トランジスタ Q 2 , Q 3 についてドレインからソースへの電圧ドロップを調節して、スイッチング・トランジスタ Q 1 , Q 4 が晒される電圧範囲をカスコード・トランジスタ Q 2 , Q 3 が制限するようとする。図 2 に示す実施形態において、バイアス回路網 2 1 は、高電圧電源  $V_{CCHV}$  と接地との間に接続された一連の抵抗 1 2 , 1 3 , 1 4 を含む。抵抗 1 2 , 1 3 , 1 4 は、高電圧電源  $V_{CCHV}$  を分割し、カスコード・トランジスタ Q 2 , Q 3 の動作に適當な電圧を有する接点 F , G を供給する。図 2 に見られるように、接点 F , G からの電圧は、カスコード・トランジスタ Q 3 , Q 2 のゲートを駆動するためにそれぞれ使用される。バイアス回路網 2 1 は図 2 に抵抗回路網として示されているが、バイアス回路網は、たとえば抵抗回路網の類似のタイプをもたらすように構成された複数のトランジスタを含んでもよい。典型的には、ノード B は、スイッチング回路網 2 2 からの出力用のボンド・パッド上の利用できる唯一のノードであるので、テスト回路を使用することが必要である。

30

#### 【 0 0 1 2 】

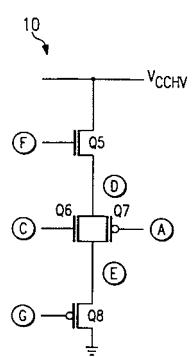

テスト回路 1 0 の一実施形態を図 1 に示す。テスト回路 1 0 は、2 つのテスト・トランジスタ Q 6 , Q 7 と、2 つのバイアス・トランジスタ Q 5 , Q 8 とを含む。テスト・トランジスタ Q 6 , Q 7 のドレインは共通ノードに接続され、テスト・トランジスタ Q 6 , Q 7 のソースは共通ノードに接続されている。第 1 のバイアス・トランジスタ Q 5 のドレインは  $V_{CCHV}$  に接続され、第 1 のバイアス・トランジスタ Q 5 のソースはがテスト・トランジスタ Q 6 , Q 7 のドレインに接続されている。第 2 のバイアス・トランジスタ Q 8 のソースはテスト・トランジスタ Q 6 , Q 7 のソースに接続され、第 2 のバイアス・トランジスタ Q 8 のドレインは接地に接続されている。バイアス・トランジスタ Q 5 , Q 8 のゲートはバイアス回路網 2 1 の接点 F , G に接続されていて、これにより、テスト・トランジスタ

40

50

Q<sub>6</sub>, Q<sub>7</sub>の1つが作動になると、バイアス・トランジスタQ<sub>5</sub>, Q<sub>8</sub>がバイアスされて電流を導くようになっている。

#### 【0013】

この構成において、テスト・トランジスタQ<sub>6</sub>, Q<sub>7</sub>はそれぞれ、接点C, Aの電圧により制御されるスイッチとして作動することにより、テスト回路10を通る電流の流れを制御する。バイアス・トランジスタQ<sub>5</sub>, Q<sub>8</sub>は、テスト・トランジスタQ<sub>6</sub>, Q<sub>7</sub>のストレスを制限するためと、テスト・トランジスタQ<sub>6</sub>, Q<sub>7</sub>にかかる電圧ストレスを制限するための、二重の目的を達成する。テスト回路10のこの実施形態において、バイアス・トランジスタQ<sub>5</sub>およびテスト・トランジスタQ<sub>6</sub>はNMOSトランジスタであり、バイアス・トランジスタQ<sub>8</sub>およびテスト・トランジスタQ<sub>7</sub>はPMOSトランジスタである。<sup>10</sup>しかしながら、トランジスタQ<sub>5</sub>, Q<sub>6</sub>, Q<sub>7</sub>, Q<sub>8</sub>用に使用されるトランジスタのタイプは多数の要素により決定され、それらの要素には、たとえば、カスコード・トランジスタQ<sub>2</sub>, Q<sub>3</sub>用に使用されるトランジスタのタイプや、テスト回路10とともに使用される特定の回路の仕様が含まれる。

#### 【0014】

テスト回路10の動作は、図1および図2を参照すると最も良く理解される。上述したように、テスト回路10は、欠陥(たとえば、カスコード・トランジスタQ<sub>2</sub>, Q<sub>3</sub>のいずれかにドレインからソースへの短絡があること)を指示する。つまり、カスコード・トランジスタQ<sub>2</sub>, Q<sub>3</sub>が正常に機能している限り、接点Cにおける電圧はテスト・トランジスタQ<sub>6</sub>をオンにするのに充分なほどなく、また、接点Aにおける電圧はテスト・トランジスタQ<sub>7</sub>をオンにするのに充分なほど低くない。<sup>20</sup>したがって、カスコード・トランジスタQ<sub>2</sub>, Q<sub>3</sub>が正常に機能する限り、テスト・トランジスタQ<sub>6</sub>, Q<sub>7</sub>は本質的に開放回路であるので、テスト回路10には電流が流れない。これは次のように検査される。NMOSトランジスタをオンにする電圧が0.6Vであり、接点Gが前述した1.7Vであれば、接点Eは、電流が流れるためには、(1.7 + 0.6) = 2.3Vよりも大きくなければならない。テスト・トランジスタQ<sub>6</sub>に電流が流れるならば、接点Cにおける電圧は(2.3 + 0.6) = 2.9Vよりも大きくなければならない。カスコード・トランジスタQ<sub>3</sub>はソース・フォロワとして作動するので、接点Cにおける電圧はF - 0.6V = 2.7Vに等しく、これはテスト回路内に電流を維持するのに必要な計算された2.9Vよりも低い。同様にして、電流がテスト・トランジスタQ<sub>7</sub>に流れていなことが示され、これにより、テスト回路はV<sub>DDHV</sub>をロードしていないことが示される。この特定の例において、マージンは非常にタイトであり、テスト回路が電流を引かないことを保証するためには、接点F, Gにおける電圧レベルの調節が必要である。<sup>30</sup>

#### 【0015】

しかしながら、カスコード・トランジスタQ<sub>2</sub>, Q<sub>3</sub>の一つにドレインからソースへの短絡があれば、テスト回路10はそうした短絡の指示を供給する。たとえば、カスコード・トランジスタQ<sub>2</sub>にドレインからソースへの短絡があれば、スイッチング・トランジスタQ<sub>4</sub>がオンのときに接点Aの電圧は接地に引かれる。接点Aの電圧が接地に引かれると、テスト・トランジスタQ<sub>7</sub>がオンになり、また、電流はテスト回路10をV<sub>DDHV</sub>から接地へ流れる。テスト回路は、この電流が検出されるのに充分なほど大きいように設計され、こうして、電流の流れはカスコード・トランジスタQ<sub>2</sub>またはカスコード・トランジスタQ<sub>3</sub>内の欠陥の指示をもたらす。カスコード・トランジスタQ<sub>3</sub>にドレインからソースへの短絡があれば、スイッチング・トランジスタQ<sub>1</sub>がオンのときに、接点Cでの電圧がV<sub>CCHV</sub>へ引かれる。接点Cでの電圧がV<sub>CCHV</sub>へ引かれれば、テスト・トランジスタQ<sub>6</sub>がオンになり、これもテスト回路10を通る電流の流れを生ずる。<sup>40</sup>したがって、テスト回路10は、このユニットのテスト段階で内蔵されたカスコード・デバイス内の欠陥を検出できるようにし、これにより、そのようなカスコード・トランジスタを組み込んだ回路の信頼性を増強する。

#### 【0016】

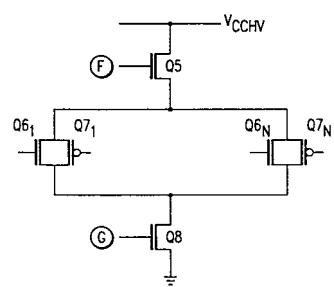

他の実施形態において、複数のテスト・トランジスタ対Q<sub>6</sub>, Q<sub>7N</sub>を調節トランジスタ

Q5, Q8とともにグループ化できる。図3に示すように、これらのテスト・トランジスタ対は、それらが共通ノードにおいて調節トランジスタQ5, Q8に接続されるように、接続される。この装置において、各トランジスタ対は、カスコード・デバイスの一つの特定の対内の欠陥についてテストするために使用される。複数のトランジスタ対は多重カスコード出力トランジスタ回路のテストを提供する。

#### 【0017】

本発明を詳細に説明してきたが、特許請求の範囲により画定される範囲の意図から逸脱することなく種々な変更、置き換え、代替が可能であることを理解すべきである。

#### 【0018】

以上の説明に関してさらに以下の項を開示する。

10

(1) ゲーティング・トランジスタおよびカスコード・トランジスタを含む、能動デバイスのカスコード構成と、

該カスコード構成をバイアスするように配列されたバイアス回路網と、

前記カスコード構成および前記バイアス回路網に結合された、前記カスコード・トランジスタ内の短絡の指示を供給するテスト回路網と、

を含むカスコード回路。

#### 【0019】

(2) レベルシフト回路であって、

能動デバイスのカスコード構成であって、

第1のスイッチング・トランジスタおよび第2のスイッチング・トランジスタと、

20

該第1および第2のスイッチング・トランジスタの電圧ストレスを制限するように配列された第1のカスコード・トランジスタおよび第2のカスコード・トランジスタとを含む、カスコード構成と、

該カスコード構成をバイアスするように配列されたバイアス回路網と、

前記カスコード構成および前記バイアス回路網に接続された、前記カスコード・トランジスタの1つまたは両方内の短絡の指示を供給するテスト回路網と、

を含む、レベルシフト回路。

#### (3) 前記テスト回路網が、

前記第1のスイッチング・トランジスタおよび前記第1のカスコード・トランジスタに接続された第1のテスト・トランジスタと、

30

前記第2のスイッチング・トランジスタおよび前記第2のカスコード・トランジスタに接続された第2のテスト・トランジスタと、

前記複数のテスト・トランジスタ上の電圧スイングを制限するように配列された、前記複数のトランジスタについてスレッショルド電圧を設定するように配列された複数のアクティブ・デバイスとを含む、第2項記載の回路。

(4) 前記第1のテスト・トランジスタのゲートが前記第1のスイッチング・トランジスタのドレインおよび前記第1のカスコード・トランジスタのソースに接続され、

前記第2のテスト・トランジスタのゲートが前記第2のスイッチング・トランジスタのドレインおよび前記第2のカスコード・トランジスタのソースに接続されている、第3項記載の回路。

40

#### 【0020】

(5) 前記バイアス回路網が抵抗回路網を含む、第1項の回路。

(6) 前記第1のスイッチング・トランジスタおよび前記第1のカスコード・トランジスタがPMOSトランジスタであり、前記第2のスイッチング・トランジスタおよび前記第2のカスコード・トランジスタがNMOSトランジスタである、第2項の回路。

#### 【0021】

(7) カスコード・デバイス用のテスト容易化回路であって、

少なくとも一組のトランジスタ対を含み、各対が、

第1のテスト・トランジスタと、

第2のテスト・トランジスタであって、前記第1のテスト・トランジスタのドレインが前

50

記第2のテスト・トランジスタのソースに接続され、前記第1のテスト・トランジスタのソースが前記第2のテスト・トランジスタのドレインに接続されている、少なくとも一組のトランジスタ対と、

テスト・トランジスタ対の第1および第2のテスト・トランジスタに接続された第1の調節トランジスタおよび第2の調節トランジスタを含み前記第1および第2のテスト・トランジスタ上の電圧ストレスを制限する調節トランジスタ対と、

前記複数のトランジスタ対の一組が、カスコード回路装置に接続され、該カスコード回路装置内の欠陥についての指示を提供する、テスト容易化回路。

(8) 前記カスコード回路装置内に欠陥があれば、前記テスト容易化回路に電流が流れ

る、第7項記載のテスト容易化回路。 10

(9) 前記第1の調節トランジスタが前記第1のテスト・トランジスタについてスレッショルド電圧を設定する、第7項記載のテスト容易化回路。

(10) 前記第2の調節トランジスタが前記第2のテスト・トランジスタについてスレッショルド電圧を設定する、第7項記載のテスト容易化回路。

(11) 各テスト・トランジスタ対がカスコード回路装置へ接続されて該カスコード回路装置内の欠陥の指示を提供する複数のテスト・トランジスタ対をさらに含む、第7項のテスト容易化回路。

#### 【0022】

(12) テスト回路(10)は、内蔵カスコード・トランジスタQ2, Q3内の欠陥をテストできるように供給される。それは、たとえばレベルシフト回路の一部を形成する。テスト回路(10)は、調節トランジスタQ5, Q8に接続されたテスト・トランジスタQ6, Q7を含む。Q2とQ3が正しく機能しているときは、テスト回路(10)には電流が流れない。しかしながら、Q2またはQ3のいずれかまたは両方にドレインからソースへの短絡があると、テスト回路(10)に電流が流れ、こうして、欠陥の指示を供給する。

20

#### 【図面の簡単な説明】

【図1】本発明の一実施形態によるレベルシフト回路用のテスト回路の概略回路図である。

【図2】本発明の一実施形態によるテスト回路とともに使用し得るレベルシフト回路の概略回路図である。 30

【図3】本発明の他の実施形態による多重レベルシフト回路用のテスト回路の概略回路図である。

#### 【符号の説明】

10 テスト回路

20 レベルシフト回路

21 バイアス回路網

22 スイッチング回路網

Q1, Q4 スイッチング・トランジスタ

Q2, Q3 カスコード・トランジスタ

Q5, Q8 バイアス・トランジスタ

Q6, Q7 テスト・トランジスタ

12, 13, 14 抵抗

40

【図1】

【図2】

【図3】

---

フロントページの続き

(72)発明者 ブレンハード エイチ . アンドレセン

アメリカ合衆国 テキサス州ダラス , モスクレスト 10333

(72)発明者 フレデリック ジー . ウォル

アメリカ合衆国 テキサス州ガーランド , クナイト レーン 3705

審査官 藤原 伸二

(56)参考文献 特開平08-043498 (JP, A)

(58)調査した分野(Int.Cl. , DB名)

G01R 31/28-31/3193

G01R 31/26

H03K 19/00-19/096

H01L 21/822

H01L 27/04

H01L 21/64-21/66

G06F 11/22-11/26