등록특허 10-2557501

(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2023년07월20일

(11) 등록번호 10-2557501

(24) 등록일자 2023년07월17일

- (51) 국제특허분류(Int. Cl.)

*H10K 99/00* (2023.01) *B22F 3/105* (2006.01)

*B22F 3/14* (2006.01) *B22F 3/15* (2006.01)

*C23C 14/14* (2006.01) *C23C 14/20* (2006.01)

*C23C 24/04* (2006.01) *C23C 28/00* (2006.01)

*G02F 1/1333* (2006.01) *G02F 1/1345* (2006.01)

*H01L 27/12* (2006.01)

- (52) CPC특허분류

*H10K 77/111* (2023.02)

*B22F 3/105* (2013.01)

- (21) 출원번호 10-2019-7036521

- (22) 출원일자(국제) 2018년04월19일

심사청구일자 2021년01월18일

- (85) 번역문제출일자 2019년12월10일

- (65) 공개번호 10-2020-0008575

- (43) 공개일자 2020년01월28일

- (86) 국제출원번호 PCT/AT2018/000026

- (87) 국제공개번호 WO 2018/204944

국제공개일자 2018년11월15일

- (30) 우선권주장

GM 104/2017 2017년05월11일 오스트리아(AT)

## (56) 선행기술조사문헌

JP2015119175 A\*

KR1020150017270 A\*

WO2004038049 A1\*

\*는 심사관에 의하여 인용된 문헌

전체 청구항 수 : 총 22 항

심사관 : 정미나

## (54) 발명의 명칭 금속 플라이를 갖는 층 구조를 포함하는 가요성 부품

**(57) 요 약**

본 발명은 층 평면 내에서 Mo-계 층의 전기 전도도를 유지하기 위한 첨가제의 이용에 관한 것이며, Mo-계 층은, 단일의 또는 반복적인 곱힘 하중, 인장 하중 및/또는 비틀림 하중을 받는 가요성 기관에, (직접 또는 하나 이상의 중간 층들을 통해) 적용되며, 첨가제는 Cu, Ag, Au 또는 이들의 혼합물이다. 또한, 본 발명은 가요성 기관

(뒷면에 계속)

**대 표 도** - 도2

및, MoX를 함유하는 금속 플라이를 갖는, 층 구조를 갖는 코팅된 가요성 부품으로서, X는 Cu, Ag, Au로 이루어진 그룹으로부터 하나 이상의 원소인, 코팅된 가요성 부품에 관한 것이며, 그러한 부품을 제조하기 위한 방법에 관한 것이다.

(52) CPC특허분류

- B22F 3/14* (2013.01)

*B22F 3/15* (2013.01)

*C23C 14/14* (2013.01)

*C23C 14/205* (2013.01)

*C23C 24/04* (2013.01)

*C23C 28/322* (2013.01)

*C23C 28/345* (2013.01)

*C23C 28/3455* (2013.01)

*G02F 1/133305* (2013.01)

-

## 명세서

### 청구범위

#### 청구항 1

Mo-계 층의 평면 내에서 상기 Mo-계 층의 전기 전도도를 유지하기 위해 첨가제 X를 이용하는 방법으로서,

상기 Mo-계 층은 적어도 50 wt.% Mo를 함유하며,

상기 Mo-계 층은, 직접 또는 하나 이상의 중간 층들을 통해, 단일의 또는 반복적인 굽힘, 인장, 및/또는 비틀림 응력을 받는 가요성 기판(100, 200)에 적용되며,

상기 첨가제는 Cu, Ag, Au 또는 이들의 혼합물이며,

상기 Mo-계 층 내에서 X는 혼합 결정의 형태로 용해되어 있는 것을 특징으로 하는, Mo-계 층의 평면 내에서 상기 Mo-계 층의 전기 전도도를 유지하기 위해 첨가제 X를 이용하는 방법.

#### 청구항 2

- 가요성 기판(100, 200)

- 직접 또는 하나 이상의 중간 층들을 통해 기판(100, 200)에 배치되고, 일측에서 금속 플라이에 직접 인접하는 반도체 또는 전기 절연 플라이를 갖고 다른 일측에서 금속 플라이에 직접 인접하는 반도체 또는 전기 절연 플라이를 갖는 금속 플라이를 구비하는, 적어도 하나의 층 구조

를 포함하는 코팅된 가요성 부품으로서,

상기 금속 플라이는:

- MoX로 제조된 단일 층

- Cu-계 층과 조합하여 MoX로, 또는 Al-계 층과 조합하여 MoX로, 제조된 2층 시스템, 및

- 개재된 Cu-계 층을 갖는 2개의 MoX 층들로, 또는 개재된 Al-계 층을 갖는 2개의 MoX 층들로, 제조된 3층 시스템

중 어느 하나로부터 형성되며,

상기 MoX 층은 적어도 50 wt.% Mo를 함유하며,

X는 Cu, Ag, Au로 이루어진 그룹으로부터 하나 이상의 원소이며,

MoX 층 내에서 X는 혼합 결정의 형태로 용해되어 있는 것을 특징으로 하는, 코팅된 가요성 부품.

#### 청구항 3

제2항에 있어서,

적어도 하나의 MoX 층에서, X는 원소 Cu이고, 이 MoCu 층은 0.5 at% 초과 및 50 at% 미만의 Cu를 함유하는 것을 특징으로 하는, 코팅된 가요성 부품.

#### 청구항 4

제2항 또는 제3항에 있어서,

적어도 하나의 MoX 층에서, X는 원소 Ag이고, 이 MoAg 층은 10 at% 초과 및 50 at% 미만의 Ag를 함유하는 것을 특징으로 하는, 코팅된 가요성 부품.

#### 청구항 5

제2항 또는 제3항에 있어서,

적어도 하나의 MoX 층에서, X는 원소 Au이고, 이 금속 MoAu 층은 5 at% 초과 및 20 at% 미만의 Au를 함유하는 것을 특징으로 하는, 코팅된 가요성 부품.

#### 청구항 6

제2항 또는 제3항에 있어서,

개개의 MoX 층은 200  $\mu\text{Ohmcm}$  미만의 층 저항  $\rho$ 를 갖는 것을 특징으로 하는, 코팅된 가요성 부품.

#### 청구항 7

제2항 또는 제3항에 있어서,

가요성 기판(100, 200)은 전기 절연 플라이들과 별도로 형성되는 것을 특징으로 하는, 코팅된 가요성 부품.

#### 청구항 8

제2항 또는 제3항에 있어서,

가요성 기판(100, 200) 상에 배치되는 층 구조는 금속 플라이에 직접 인접하는 반도체 또는 전기 절연 플라이들 중 하나에 의해 형성되는 것을 특징으로 하는, 코팅된 가요성 부품.

#### 청구항 9

제2항 또는 제3항에 있어서,

금속 플라이에 직접 인접하는 반도체 또는 전기 절연 플라이들 중 적어도 하나가 층들(140, 150, 220, 250)로서 형성되는 것을 특징으로 하는, 코팅된 가요성 부품.

#### 청구항 10

제2항 또는 제3항에 있어서,

금속 플라이의 두께는 1  $\mu\text{m}$  미만인 것을 특징으로 하는, 코팅된 가요성 부품.

#### 청구항 11

제2항 또는 제3항에 있어서,

가요성 기판(100, 200)은 투명한 것을 특징으로 하는, 코팅된 가요성 부품.

#### 청구항 12

제2항 또는 제3항에 있어서,

금속 플라이가 전체적으로 50  $\mu\text{Ohmcm}$  미만의 층 저항  $\rho$ 를 갖는 것을 특징으로 하는, 코팅된 가요성 부품.

#### 청구항 13

제2항 또는 제3항에 있어서,

가요성 기판(100, 200)은:

- 폴리머

- 얇은 유리

- 금속 포일

- 광물 재료

로 이루어진 그룹으로부터 적어도 하나의 재료를 포함하는 것을 특징으로 하는, 코팅된 가요성 부품.

#### 청구항 14

제2항 또는 제3항에 있어서,

금속 플라이는, 2% 탄성 신장( $\epsilon$ )에서, 1.2 미만의, 측정 초기에서의 전기 저항( $R_0$ )에 대한 전기 저항( $R$ )의 비( $R/R_0$ )를 갖는 것을 특징으로 하는, 코팅된 가요성 부품.

### 청구항 15

제2항 또는 제3항에 있어서,

가요성 기판(100, 200)은 적어도 하나의 도체 트랙 구조를 가지면서, 금속 플라이는 상기 적어도 하나의 도체 트랙 구조의 일부인 것을 특징으로 하는, 코팅된 가요성 부품.

### 청구항 16

제2항 또는 제3항에 있어서,

금속 플라이는 TFT 구조의 일부인 것을 특징으로 하는, 코팅된 가요성 부품.

### 청구항 17

제2항 또는 제3항에 있어서,

금속 플라이는 액티브 매트릭스 구조의 일부인 것을 특징으로 하는, 코팅된 가요성 부품.

### 청구항 18

제2항 또는 제3항에 있어서,

코팅된 가요성 부품은: 가요성 LCD 디스플레이 스크린, 가요성 OLED 디스플레이 스크린, 가요성 전기영동 디스플레이 스크린(e-Paper, E-Ink®), 가요성 태양 전지, 전기변색 가요성 필름, 가요성 박막 배터리로 이루어진 그룹으로부터 선택되는 하나의 부품인 것을 특징으로 하는, 코팅된 가요성 부품.

### 청구항 19

제2항에 따른 코팅된 가요성 부품을 제조하기 위한 방법으로서,

적어도 다음의 단계들:

- 가요성 기판(100, 200)을 제공하는 단계

- 적어도 하나의 MoX 층을 증착시킴으로써, 직접 또는 하나 이상의 중간 층들을 통해, 가요성 기판(100, 200)을 코팅하는 단계

를 포함하며,

상기 MoX 층은 적어도 50 wt.% Mo를 함유하며, 상기 MoX 층은 0.5 at% 초과의 X를 함유하며, X는 Cu, Ag, Au로 이루어진 그룹으로부터 하나 이상의 원소이며,

MoX 층 내에서 X는 혼합 결정의 형태로 용해되어 있는 것을 특징으로 하는, 코팅된 가요성 부품을 제조하기 위한 방법.

### 청구항 20

제1항에 있어서,

적어도 다음의 단계들:

- 가요성 기판(100, 200)을 제공하는 단계

- 적어도 하나의 MoX 층을 증착시킴으로써, 직접 또는 하나 이상의 중간 층들을 통해, 가요성 기판(100, 200)을 코팅하는 단계

를 포함하며,

상기 MoX 층은 적어도 50 wt.% Mo를 함유하며, 상기 MoX 층은 0.5 at% 초과의 X를 함유하며, X는 Cu, Ag, Au

로 이루어진 그룹으로부터 하나 이상의 원소이며,

Mo-계 층 내에서 X는 혼합 결정의 형태로 용해되어 있는 것을 특징으로 하는, Mo-계 층의 평면 내에서 상기 Mo-계 층의 전기 전도도를 유지하기 위해 첨가제 X를 이용하는 방법.

### 청구항 21

제19항에 있어서,

적어도 하나의 MoX 층의 중착은 PVD 방법에 의해 구현되는 것을 특징으로 하는, 코팅된 가요성 부품을 제조하기 위한 방법.

### 청구항 22

제20항에 있어서,

적어도 하나의 MoX 층의 중착은 PVD 방법에 의해 구현되는 것을 특징으로 하는, Mo-계 층의 평면 내에서 상기 Mo-계 층의 전기 전도도를 유지하기 위해 첨가제 X를 이용하는 방법.

### 청구항 23

삭제

## 발명의 설명

### 기술 분야

[0001]

본 발명은 청구항 제1항의 전제부의 특징들을 갖는 층 평면(layer plane) 내의 Mo-계 층의 전기 전도도를 유지하기 위한 첨가제의 이용, 청구항 제2항의 전제부의 특징들을 갖는 코팅된 가요성 부품(coated flexible component), 및 청구항 제20항의 전제부의 특징들을 갖는 코팅된 가요성 부품을 제조하기 위한 방법에 관한 것이다.

### 배경 기술

[0002]

가요성, 유연성 부품 분야의 기술 발전은 박막 재료 분야의 발전과 밀접하게 연관되어 있다. 특히, 이러한 발전은, 예를 들어, 액정 디스플레이(TFT-LCDs), AM-OLEDs(active matrix organic light-emitting diodes, 능동형 유기발광 다이오드), 또는 micro-LED(light-emitting diodes) 디스플레이 스크린과 같은, 전자 디스플레이 스크린의 능동 제어("active matrix", 액티브 매트릭스)를 위한 구조의 일부로서, 전자 소자, 특히 박막 부품, 예를 들어, 박막 트랜지스터(thin-film transistors, TFT)의 분야에서 더 많은 개별을 가능하게 한다. 액티브 매트릭스 구조는, 예를 들어, x-선 방사선을 위한 센서 어레이와 같은, 그 밖의 다른 응용분야에 또한 이용될 수 있다. 이러한 응용분야에서, 전기 도체 트랙들(electrical conductor tracks)이, 행("gate lines"; "rows") 및 열("signal lines"; "column lines"; "data lines")으로서, 매트릭스 내에 배치된다. 도체 트랙들은 한 지점에서 다른 지점으로 전기 신호, 전류, 또는 전압을 전송하기 위한 전기 전도성 경로를 제공한다.

[0003]

각각의 액티브 매트릭스 행 또는 열은 길고 좁은 도체 트랙으로 이루어지며(예를 들어, 수 센티미터 내지 최대 거의 2 미터의 길이, 수 마이크로미터 내지 최대 수십 마이크로미터의 폭, 및 수십 나노미터 내지 수백 나노미터의 총 층 두께를 가짐), 이를 각각, 각각 TFT의 게이트("control electrode") 또는 소스/드레인 전극("inflow and outflow electrode")을 형성하는, 박막 트랜지스터의 영역에서 하나 이상의 연장부를 갖는다. 도체 트랙들은 TFT의 게이트 또는 소스/드레인 전극들을 기판의 에지 영역에 연결하며, 거기에는 외부 접촉을 위한 접촉 영역("contact pads"), 또는 디스플레이 스크린을 제어하기 위한 게이트 및 데이터 드라이버 구조(행 및 열 드라이버)가 배치된다.

[0004]

액티브 매트릭스 제어의 도움으로, 각각의 개별 픽셀의 휘도는 하나(예를 들어, TFT-LCD) 또는 다수(예를 들어, AM-OLED 디스플레이 스크린) TFTs에 걸쳐 개별적으로 조절될 수 있으며; 이 경우 긴 게이트 및 신호 도체 트랙들을 따라 전압 강하가 가능한 한 작은 것이 결정적인데, 그렇지 않은 경우 길이-의존성의, 바람직하지 않은 휘도 차이가 픽셀에서 발생할 것이기 때문이다. (인간의 눈은 휘도 차이에 매우 민감하게 반응한다.)

[0005]

유연성, 가요성, 또는 피벗 가능한 기판 상에 배치된 액티브 매트릭스 구조의 경우, 특히 긴 행 및 열 도체 트랙들은 높은 변형 및/또는 굽힘 및/또는 비틀림 응력을 받으며, 이러한 응력을 훨씬 더 작은 공간 범위(일반적으

로 수 마이크로미터 내지 수십 마이크로미터의 애지 길이를 갖는 직사각형 영역)로 인해 TFT 구조 내의 게이트 및 소스/드레인 전극들에서 훨씬 더 작다. 이러한 응력으로 인해, 특히 취성 도체 트랙 재료들의 경우, 여려 자릿수만큼 전기 저항의 증가가 빠르게 발생할 수 있다. 이에 따라, 도체 트랙을 따라 배치된 TFTs에는 더이상 정해진 전압이 균일하게 공급되지 않으며, 디스플레이 스크린 응용분야에서 길이-의존성의 휘도 차이가 발생할 수 있다. 극단적인 경우, 도체 트랙은 전기 전도성을 완전히 잃고, 픽셀의 전체 불량이 발생한다.

[0006] 특히, 예를 들어, 휴대폰, 태블릿 PC, 및 PDAs(personal digital assistants)와 같은, 모바일 적용을 위한 디스플레이 스크린의 경우, 이미지 콘텐트를 표시하기 위한 실제 장치에 추가로 훨씬 더 많은 주변 전기 회로들이 디스플레이 스크린 기판에 통합된다. 이것들은, 예를 들어, 게이트 전극(게이트 드라이버)을 제어하기 위한 회로, 소스/드레인 전극(데이터 드라이버)을 제어하기 위한 회로, DC-DC 변환기, 디지털-아날로그 변환기, 타이밍 컨트롤러, 또는 버퍼 및 인터페이스 회로일 수 있다. 그러한 디스플레이 스크린과 그 제어 유닛의 조합은 system-on-panel(SOP)(system on display screen panel)이라고 지칭되며, 또는, 기판이 유리로 이루어진 경우에는, system-on-glass(SOG)라고 지칭된다. 별도의 하우징을 포함하는 외부 접적 회로(integrated circuits, ICs)로서 구현하는 대신에, 기판 상에 직접 디스플레이 스크린을 제어하기 위한 주변 전기 회로들을 배치하는 것이 유리하다; 주요 장점들로는 보다 낮은 제조 비용, 보다 낮은 전력 소비, 보다 낮은 공간 요구사항, 및 보다 큰 신뢰성이 있다.

[0007] System-on-panel 디스플레이 스크린은 흔히 저온 폴리실리콘(low-temperature polysilicon, LTPS)에 의해 구현되지만, 예를 들어 비정질 실리콘, 또는 금속 산화물과 같은, 그 밖의 다른 반도체를 이용하여 또한 가능하다.

[0008] 기판 상에 배치된 주변 회로들의 일부는 전기 도체 트랙, 게이트 라인 및 신호 라인을 통해, 개별 픽셀들의 TFTs에 연결되며, 그 길이는 디스플레이 스크린 크기에 따라 수 밀리미터 내지 200 cm일 수 있다. 변형, 굽힘, 또는 비틀림 응력 하에서 도체 트랙들의 저항 변화는, 디스플레이 스크린의 전체 행 또는 열, 또는 개별 픽셀들의 불량을 방지하기 위해, 또는 디스플레이의 휘도 또는 색상("mura")에서 바람직하지 않은 차이를 방지하기 위해, 가능한 한 최소이어야 한다.

[0009] 플렉시블 터치 스크린(예를 들어, 저항성 또는 용량성 센서)은 매트릭스로 배치된 x 및 y 전극을 또한 이용하지만, 일반적으로 능동 TFT 구조를 갖지 않는다. 수 센티미터 내지 수 미터 크기의 대형 센서들에서는, 매우 길고 좁은 도체 트랙 구조가 또한 사용되며, 예를 들어, 10 ~ 100 cm의 길이와 5 ~ 50 μm의 폭을 갖는다. 변형, 굽힘, 또는 비틀림 응력 하에서 도체 트랙들의 저항 변화(증가)는 이 응용분야에서도 가능한 한 최소이어야 하는데, 그렇지 않은 경우(예를 들어, 신호 대 잡음비의 감소로 인해) 센서의 불량이 발생할 수 있기 때문이다.

[0010] WO 2016/032175 (도 7)에서는, 굽힘 응력을 받는 도체 트랙들에서 기계적 인장을 감소시키기 위해, 비선형의, 예를 들어, 사인곡선형(sinoidal), 파형(wavy), 구형파형(square-wave), 사형(meandering), 또는 톱니형(sawtooth-wave) 도체 트랙 구조들이 제안된다. 크랙의 전파를 방지하기 위해, 추가 분기 및 재통합 도체 트랙 구조들이 제안된다(전술한 문헌에서 도 8c). 그러나, 이러한 구조들 모두는 단순한 선형 도체 트랙보다 더 많은 공간을 필요로 하고, 전류는 전체적으로 두 지점 사이의 보다 긴 경로를 커버해야 하며, 이는 추가적인 전압 강하 또는 신호 대 잡음비의 감소를 초래할 수 있다.

[0011] 또한, 새로운 통합 프로세스의 개발에 있어서의 진보는 가요성 기판과 전자장치의 조합, 그리고 추가 결과로서 보다 유연한 전자 부품의 제조를 또한 가능하게 한다. 해당 유형의 종래 기술은 AT 15 048 U1에 의해 형성된다. 종래 기술에 대한 추가 정보를 위해 이 문헌이 참조된다.

## 발명의 내용

### 해결하려는 과제

[0012] 본 발명의 목적은, 단일의 또는 반복적인 굽힘, 인장, 및/또는 비틀림 응력을 받는, 가요성 기판에 적용되는, 금속 플라이(metallic ply)의 전기 전도도의 유지이다. 특히, 본 발명의 목적은 가요성 기판 상에 전기 도체 트랙(금속 플라이)을 제공하는 것이며, 여기서 도체 트랙의 전기 저항은 변형, 굽힘, 또는 비틀림 응력의 경우에 도체 트랙을 따라, 즉, 플라이 평면 내에서, 가능한 한 적게, 특히 10% 미만만큼, 변화된다.

### 과제의 해결 수단

[0013] 이러한 목적은 청구항 제1항에 따른 이용, 청구항 제2항에 따른 코팅된 가요성 부품, 및 청구항 제20항의 특징들을 갖는 코팅된 가요성 부품을 제조하기 위한 방법에 의해 달성된다. 본 발명의 유리한 실시형태들은 종속항

들에서 정의된다.

#### [청구항 1]

Mo-계 층의 평면 내에서 상기 Mo-계 층의 전기 전도도를 유지하기 위해 첨가제를 이용하는 방법으로서,

상기 Mo-계 층은 적어도 50 wt.% Mo를 함유하며,

상기 Mo-계 층은, 직접 또는 하나 이상의 중간 층들을 통해, 단일의 또는 반복적인 굽힘, 인장, 및/또는 비틀림 응력을 받는 가요성 기판(100, 200)에 적용되며,

상기 첨가제는 Cu, Ag, Au 또는 이들의 혼합물인 것을 특징으로 하는, Mo-계 층의 평면 내에서 상기 Mo-계 층의 전기 전도도를 유지하기 위해 첨가제를 이용하는 방법.

#### [청구항 2]

- 가요성 기판(100, 200)

- 직접 또는 하나 이상의 중간 층들을 통해 기판(100, 200)에 배치되고, 일측에서 금속 플라이에 직접 인접하는 반도체 또는 전기 절연 플라이를 갖고 다른 일측에서 금속 플라이에 직접 인접하는 반도체 또는 전기 절연 플라이를 갖는 금속 플라이를 구비하는, 적어도 하나의 층 구조

를 포함하는 코팅된 가요성 부품으로서,

상기 금속 플라이는:

- MoX로 제조된 단일 층

- Cu-계 층과 조합하여 MoX로, 또는 Al-계 층과 조합하여 MoX로, 제조된 2층 시스템, 및

- 개재된 Cu-계 층을 갖는 2개의 MoX 층들로, 또는 개재된 Al-계 층을 갖는 2개의 MoX 층들로, 제조된 3층 시스템

중 어느 하나로부터 형성되며,

상기 MoX 층은 적어도 50 wt.% Mo를 함유하며,

X는 Cu, Ag, Au로 이루어진 그룹으로부터 하나 이상의 원소인 것을 특징으로 하는, 코팅된 가요성 부품.

#### [청구항 3]

제2항에 있어서,

적어도 하나의 MoX 층에서, X는 원소 Cu이고, 이 MoCu 층은 0.5 at% 초과 및 50 at% 미만의 Cu를 함유하는 것을 특징으로 하는, 코팅된 가요성 부품.

#### [청구항 4]

제2항 또는 제3항에 있어서,

적어도 하나의 MoX 층에서, X는 원소 Ag이고, 이 MoAg 층은 10 at% 초과 및 50 at% 미만의 Ag를 함유하는 것을 특징으로 하는, 코팅된 가요성 부품.

#### [청구항 5]

제2항 또는 제3항에 있어서,

적어도 하나의 MoX 층에서, X는 원소 Au이고, 이 금속 MoAu 층은 5 at% 초과 및 20 at% 미만의 Au를 함유하는 것을 특징으로 하는, 코팅된 가요성 부품.

#### [청구항 6]

제2항 또는 제3항에 있어서,

Mo 층 내에서 X는 혼합 결정의 형태로 용해되어 있는 것을 특징으로 하는, 코팅된 가요성 부품.

#### [청구항 7]

제2항 또는 제3항에 있어서,

개개의 MoX 층은  $200 \mu\text{Ohmcm}$  미만의 총 저항  $\rho$ 를 갖는 것을 특징으로 하는, 코팅된 가요성 부품.

[청구항 8]

제2항 또는 제3항에 있어서,

가요성 기판(100, 200)은 전기 절연 플레이들과 별도로 형성되는 것을 특징으로 하는, 코팅된 가요성 부품.

[청구항 9]

제2항 또는 제3항에 있어서,

가요성 기판(100, 200) 상에 배치되는 층 구조는 금속 플레이에 직접 인접하는 반도체 또는 전기 절연 플레이들 중 하나에 의해 형성되는 것을 특징으로 하는, 코팅된 가요성 부품.

[청구항 10]

제2항 또는 제3항에 있어서,

금속 플레이에 직접 인접하는 반도체 또는 전기 절연 플레이들 중 적어도 하나가 층들(140, 150, 220, 250)로서 형성되는 것을 특징으로 하는, 코팅된 가요성 부품.

[청구항 11]

제2항 또는 제3항에 있어서,

금속 플레이의 두께는  $1 \mu\text{m}$  미만인 것을 특징으로 하는, 코팅된 가요성 부품.

[청구항 12]

제2항 또는 제3항에 있어서,

가요성 기판(100, 200)은 투명한 것을 특징으로 하는, 코팅된 가요성 부품.

[청구항 13]

제2항 또는 제3항에 있어서,

금속 플레이가 전체적으로  $50 \mu\text{Ohmcm}$  미만의 총 저항  $\rho$ 를 갖는 것을 특징으로 하는, 코팅된 가요성 부품.

[청구항 14]

제2항 또는 제3항에 있어서,

가요성 기판(100, 200)은:

- 폴리머

- 얇은 유리

- 금속 포일

- 광물 재료

로 이루어진 그룹으로부터 적어도 하나의 재료를 포함하는 것을 특징으로 하는, 코팅된 가요성 부품.

[청구항 15]

제2항 또는 제3항에 있어서,

금속 플레이이는, 2% 탄성 신장( $\epsilon$ )에서, 1.2 미만의, 측정 초기에서의 전기 저항( $R_0$ )에 대한 전기 저항( $R$ )의 비 ( $R/R_0$ )를 갖는 것을 특징으로 하는, 코팅된 가요성 부품.

[청구항 16]

제2항 또는 제3항에 있어서,

가요성 기판(100, 200)은 적어도 하나의 도체 트랙 구조를 가지면서, 금속 플라이는 상기 적어도 하나의 도체 트랙 구조의 일부인 것을 특징으로 하는, 코팅된 가요성 부품.

[청구항 17]

제2항 또는 제3항에 있어서,

금속 플라이는 TFT 구조의 일부인 것을 특징으로 하는, 코팅된 가요성 부품.

[청구항 18]

제2항 또는 제3항에 있어서,

금속 플라이는 액티브 매트릭스 구조의 일부인 것을 특징으로 하는, 코팅된 가요성 부품.

[청구항 19]

제2항 또는 제3항에 있어서,

코팅된 가요성 부품은: 가요성 LCD 디스플레이 스크린, 가요성 OLED 디스플레이 스크린, 가요성 전기영동 디스플레이 스크린(e-Paper, E-Ink®), 가요성 태양 전지, 전기변색 가요성 필름, 가요성 박막 배터리로 이루어진 그룹으로부터 선택되는 하나의 부품인 것을 특징으로 하는, 코팅된 가요성 부품.

[청구항 20]

제2항에 따른 코팅된 가요성 부품을 제조하기 위한 방법으로서,

적어도 다음의 단계들:

- 가요성 기판(100, 200)을 제공하는 단계

- 적어도 하나의 MoX 층을 증착시킴으로써, 직접 또는 하나 이상의 중간 층들을 통해, 가요성 기판(100, 200)을 코팅하는 단계

를 포함하며,

상기 MoX 층은 적어도 50 wt.% Mo를 함유하며, 상기 MoX 층은 0.5 at% 초과의 X를 함유하며, X는 Cu, Ag, Au로 이루어진 그룹으로부터 하나 이상의 원소인 것을 특징으로 하는, 코팅된 가요성 부품을 제조하기 위한 방법.

[청구항 21]

제1항에 있어서,

적어도 다음의 단계들:

- 가요성 기판(100, 200)을 제공하는 단계

- 적어도 하나의 MoX 층을 증착시킴으로써, 직접 또는 하나 이상의 중간 층들을 통해, 가요성 기판(100, 200)을 코팅하는 단계

를 포함하며,

상기 MoX 층은 적어도 50 wt.% Mo를 함유하며, 상기 MoX 층은 0.5 at% 초과의 X를 함유하며, X는 Cu, Ag, Au로 이루어진 그룹으로부터 하나 이상의 원소인 것을 특징으로 하는, Mo-계 층의 평면 내에서 상기 Mo-계 층의 전기 전도도를 유지하기 위해 첨가제를 이용하는 방법.

[청구항 22]

제20항에 있어서,

적어도 하나의 MoX 층의 증착은 PVD 방법에 의해 구현되는 것을 특징으로 하는, 코팅된 가요성 부품을 제조하기 위한 방법.

[청구항 23]

제21항에 있어서,

적어도 하나의 MoX 층의 증착은 PVD 방법에 의해 구현되는 것을 특징으로 하는, Mo-계 층의 평면 내에서 상기 Mo-계 층의 전기 전도도를 유지하기 위해 첨가제를 이용하는 방법.

[0014] 본 발명에 의해, 가요성 부품의 단일의 또는 반복적인 굽힘 및/또는 인장 및/또는 비틀림 응력의 경우에, Mo-계 (몰리브덴-계) 층 또는 층 평면 내의 금속 플라이의 전기 전도도가 유지되는 것이 보장된다. 이는 연성 (ductility)의 증가에 의해 수행된다.

[0015] 제2항에 정의된 바와 같이, 복수의 금속 플라이들이 가요성 기판 상에 또한 제공될 수 있으며, 반도체 또는 전기 절연 플라이가 양면에 직접 인접한다는 제한이 각각의 금속 플라이에 대해 적용되고, 금속 플라이 자체는 단일 층, 2층 시스템, 또는 3층 시스템으로서 제2항에 따라 형성된다.

[0016] Mo-계 층 또는 MoX 층은 적어도 50 wt.% Mo를 함유하며, 특히 적어도 60 wt.% Mo를 함유한다.

[0017] MoX 층은 상이한 X를 함유하는 MoX 부분층들을 갖는 복수의 MoX로 이루어질 수 있다.

[0018] 전기 전도도의 유지 외에도, 연성의 상승은 기계적 손상 허용오차의 증가를 가져온다. 예를 들어, 다층 복합재에서 박리의 위험이 줄어든다.

[0019] 물론, Mo-계 층(MoX 층)은 첨가물 X를 제외하고 순수 Mo일 필요는 없으며, 오염물질들이 또한 존재할 수 있고, 특히, PVD(physical vapour deposition, 물리적 기상 증착) 방법, 특히 스퍼터링 방법(음극 스퍼터링)의 공정 분위기에서 비롯되는 오염물질들(예를 들어, Ar, O, N, C)이 존재할 수 있다. 그러나, 금속 오염물질은 0.5 at % 미만이어야 한다.

[0020] 언급되는 원소들 Cu, Ag, Au 중에서, Cu가 특히 바람직하다. 여기서 보다 낮은 at% 농도가 바람직한 효과를 달성하기 위해 이미 충분하다. 또한, Ag 및 Au보다 더 비용-효율적이다.

[0021] 본 발명에 따르면, 층 구조는 일측에서 금속 플라이에 직접 인접하는 반도체 또는 전기 절연 층을 갖고 다른 일측에서 금속 플라이에 직접 인접하는 반도체 또는 전기 절연 층을 갖는 금속 플라이를 구비하며, 이러한 특징들은 적어도 코팅된 가요성 부품의 소정의 영역에서 충족된다 (반드시 가요성 부품의, 특히 가요성 전자 부품의, 모든 영역에서 충족되어야 하는 것은 아니다). 또 다른 가능한 인접 층들이 이하에서 보다 상세하게 설명된다. 이와 관련하여 "전기 절연"은 전기 저항이 1 메가옴(megaohm)보다 큰 것을 의미하는 것으로 이해된다.

[0022] 유연성 및 "가요성"은 여기서 부품의 이용과 관련하여 특성에 불리한 영향없이 굽힘 응력을 흡수하는, 그리고/ 또는 그러한 응력을 견디는, 특성으로서 이해되어야 한다. 이에 따라, 충분히 가요성인 부품은 충분히 향상된 연성을 또한 갖는다.

[0023] 본 발명의 의미에서, 충분히 향상된 연성은, 부품 및/또는 물론 또한 포함된 층 또는 층들이 크래킹(cracking) 또는 크랙 성장(crack growth)에 대한 증가된 내성을 가지며, 이에 따라 크랙들은 소정의 신장까지는 형성되지 않거나 보다 큰 신장에서만 형성되거나 또는 변경된 크랙 경로를 갖는다는 것을 의미하는 것으로 이해되어야 한다.

[0024] 연성 및 그에 따라 추가 결과로서 유연성을 설명하기 위해, 임계 신장(critical elongation; 임계 연신율)이 본 발명의 범위에서 사용된다. 임계 신장은, 가요성 기판 상의 층 또는 층들의 전기 저항 R이 초기 상태에 비해 10% 만큼 증가된 ( $R/R_0=1.1$ ), 신장  $\epsilon_k$ 로서 정의된다. 충분히 높은 유연성을 갖는 부품들에서, 임계 신장  $\epsilon_k$ 는 상당히 증가하며, 이에 따라 층 또는 층들의 전도도는 상당히 더 오래 유지된다.

[0025] 본 발명의 범위에서, 가요성 기판은, 굽힘 응력의 적용시, 그 위에 증착된 층 또는 그 위에 증착된 층들(코팅)에서 신장  $\epsilon$ 을 야기하는, 기판으로서 이해되어야 한다. 층 또는 층들이 기판보다 훨씬 더 얇은 경우, 신장은 대략  $\epsilon = ds/2R$ 로 기술된다 ( $ds$ 는 기판의 두께이고  $R$ 은 굽힘 반경이다). 층 또는 층들이 기판에 비해 매우 얇은 경우, 층에서의 또는 층들에서의 신장은 오로지 인장 또는 압력 응력과 거의 동일하게 설정될 수 있다. 예를 들어, 가요성 기판은, 예를 들어, 폴리이미드(polyimide), 폴리카보네이트(polycarbonate), 폴리에틸렌 테레프탈레이트(polyethylene terephthalate), 폴리에틸렌 나프탈레이트(polyethylene naphthalate), 폴리에테르су폰(polyethersulfone), 폴리아릴레이트(polyarylate), 또는 폴리시클릭 올레핀(polycyclic olefin)과 같은, 하나 이상의 폴리머 재료에 기초하여 구성될 수 있다. 하나 이상의 폴리머 재료에 기초한 대부분의 가요성 기판은 8 GPa 이하의 탄성 계수를 갖는다. 얇은 유리(1  $\mu\text{m}$  미만의 두께를 갖는 유리), 금속 필름, 예를 들어, 1  $\mu\text{m}$  미만의 두께를 갖는 강판, 1  $\mu\text{m}$  미만의 두께를 갖는 알루미늄, 구리, 또는 티타늄 포일, 또는 광물 재료, 예를 들어, 운모가 또한 본 발명에 따른 가요성 부품을 위해 적합한 가요성 기판들이다.

- [0026] 본 발명에 적합한 가요성 기판은 다른 한편으로 하나의 층 또는 복수의 층들 그리고/또는 하나 또는 복수의 재료들로 이루어질 수 있다. 이러한 기판은 다른 재료들로 제조된 하나 이상의 층들로 완전히 또는 부분적으로 미리 코팅될 수도 있다.

- [0027] 이러한 부품은 바람직하게는 코팅된 가요성 전자 부품이다. 예를 들어, 금속 증기 장벽 층(metallic vapour barrier layers) 또는 광학 층을 갖는 패키징 필름과 같은, 코팅된 가요성 부품과 달리, 코팅된 가요성 전자 부품은 전류를 전도하는 적어도 하나의 층을 갖는다. 예를 들어, 가요성 회로, 가요성 디스플레이 스크린, 가요성 센서 요소, 가요성 박막 커패시터, 가요성 박막 배터리, 또는 간단한 전기 전도성 필름, 예를 들어, 가요성 인쇄 회로 기판의 경우에 그러하다. 본 발명에 따라 설계될 수 있는 이러한 가요성 전자 부품들의 예는 도입부에 기술되어 있다.

- [0028] 본 발명에 따른 코팅된 가요성 부품의 금속 플라이이는 바람직하게는 1  $\mu\text{m}$  미만의 두께를 갖는다. 금속 플라이이는 바람직하게는 5 nm의 최소 두께를 가지며, 보다 바람직하게는 적어도 10 nm의 두께를 갖는다. 5 내지 300 nm의 두께가 또한 바람직하며, 5 내지 100 nm의 두께가 더욱더 바람직하다. 이러한 층 두께는 금속 플라이이가 접착 측진제 층 또는 확산 장벽 층으로서 사용되는 경우에 특히 유리하다. 대안적으로, 150 내지 400 nm의 두께 범위가 바람직하다. 150 내지 400 nm의 층 두께는 디스플레이 스크린에, 예를 들어, 게이트 전극 층으로서, 본 발명에 따른 코팅된 가요성 부품의 이용에 특히 적합하다.

- [0029] 제2항에 그리고 경우에 따라 개선형태들 중 하나에 명시된 바와 같은, 하나의 또는 복수의 금속 플라이(플라이들)는 박막 트랜지스터(TFT)의 일부일 수 있다.

- [0030] 본 발명에 따른 부품의 일 예시적인 실시형태에서, 적어도 하나의 MoX 층에서, X는 원소 Cu이고 이러한 MoCu 층은 0.5 at% 초과 및 50 at% 미만의 Cu를, 바람직하게는 1 at% 초과 및 20 at% 미만의 Cu를, 함유하는 것이 제공될 수 있다. 이 경우 금속 플라이의 모든 MoX 층들이 MoCu로 제조되는 것이 특히 바람직하게는 제공된다.

- [0031] 본 발명에 따른 부품의 일 예시적인 실시형태에서, 적어도 하나의 MoX 층에서, X는 원소 Ag이고 이러한 MoAg 층은 10 at% 초과 및 50 at% 미만의 Ag를, 바람직하게는 20 at% 초과 및 50 at% 미만의 Ag를, 함유하는 것이 제공될 수 있다. 이 경우 금속 플라이의 모든 MoX 층들이 MoAg로 제조되는 것이 특히 바람직하게는 제공된다.

- [0032] 본 발명에 따른 부품의 일 예시적인 실시형태에서, 적어도 하나의 MoX 층에서, X는 원소 Au이고 이러한 MoAu 층은 5 at% 초과 및 20 at% 미만의 Au를 함유하는 것이 제공될 수 있다. 이 경우 금속 플라이의 모든 MoX 층들이 MoAu로 제조되는 것이 특히 바람직하게는 제공된다.

- [0033] 본 발명에 따른 부품의 일 예시적인 실시형태에서, 개개의 MoX 층은 200  $\mu\text{Ohmcm}$  미만의, 바람직하게는 100  $\mu\text{Ohmcm}$  미만의, 특히 바람직하게는 50  $\mu\text{Ohmcm}$  미만의, 층 저항(layer resistance)  $\rho$ 를 갖는 것이 제공될 수 있다.

- [0034] 본 발명에 따른 부품의 일 예시적인 실시형태에서, 금속 플라이에 직접 인접하는 반도체 또는 전기 절연 플라이들 중 적어도 하나가 층들로서 형성되는 것이 제공될 수 있다. 직접 인접하는 반도체 또는 전기 절연 플라이들을 모두가 층들로서 형성되는 것이 제공될 수 있다.

- [0035] 본 발명에 따른 부품의 일 예시적인 실시형태에서, 금속 플라이가 전체적으로 50  $\mu\text{Ohmcm}$  미만의, 바람직하게는 10  $\mu\text{Ohmcm}$  미만의, 특히 바람직하게는 3.5  $\mu\text{Ohmcm}$  미만의, 층 저항  $\rho$ 를 갖는 것이 제공될 수 있다.

- [0036] 본 발명에 따른 방법에서, 0.5 at% 초과 및 50 at% 미만의 X를 함유하는 적어도 하나의 MoX 층이 증착되며, 여기서 X는 Cu, Ag, Au로 이루어진 그룹으로부터 하나 또는 복수의 원소이다. 이 경우, MoX 층은 제2항에서 정의된 바와 같은 금속 플라이를 형성할 수 있거나, 그것의 일부일 수 있다.

- [0037] 적어도 하나의 MoX 층 및/또는 금속 플라이의 증착은 다양한 유형의 증착 방법들을 통해 구현될 수 있다. 예를 들어, 그러한 코팅은 물리적 또는 화학적 기상 증착을 통해 구현될 수 있다.

- [0038] 그러나, 적어도 하나의 MoX 층 및/또는 금속 플라이의 증착이 PVD 방법, 특히 스퍼터링 방법에 의해 구현되는 경우가 유리하다. PVD(physical vapour deposition; physical gas phase deposition) 방법들은 공지되어 있는 박막 코팅 기술들이며, 거기에서 코팅 재료의 입자들은 기상(vapour phase)으로 변환되고 이어서 기판 상에 증착된다. PVD 방법에 의한 증착에 의해 특히 균질한 코팅이 증착될 수 있으며, 그 특성들은 코팅된 표면에 걸쳐 동일하고 등방성이다. 이 방법의 추가 장점은 이에 따라 구현될 수 있는 낮은 기판 온도이다. 이에 따라, 예를 들어, 폴리머의 코팅이 가능하게 된다. 또한, PVD 층들은 기판 상에 매우 우수한 접착력으로 구별된다.

- [0039] MoX 층 및/또는 금속 플라이가 스퍼터링 방법(또한: 음극 스퍼터링 방법)을 통해 증착되는 경우가 특히 바람직하다. 스퍼터링 공정은 보다 큰 면적의 균질한 코팅을 위해 비교적 용이하게 이용될 수 있으며, 이에 따라 대량 생산을 위한 비용-효율적인 방법이다.

- [0040] 본 발명에 따른 방법이 다음의 단계:

- [0041] - 0.5 at % 이상 및 50 at % 미만의 X를 함유하는, 몰리브덴에 기초한 타깃을 제공하는 단계

- [0042] 를 추가로 포함하는 경우가 매우 특히 바람직하다.

- [0043] 0.5 at % 이상 및 50 at % 미만의 X를 함유하는, 몰리브덴에 기초한 타깃의 제공은 적어도 하나의 MoX 층 및/또는 적어도 하나의 금속 플라이의 증착 전에 수행된다. 이에 따라, MoX 층 및/또는 금속 플라이는 제공된 타깃으로부터 증착된다.

- [0044] 이 경우 타깃은 코팅 설비용 코팅 소스로서 이해되어야 한다. 하나의 바람직한 방법에서, 사용되는 타깃은 스퍼터링 방법을 위한 스퍼터링 타깃이다.

- [0045] 코팅의 화학 조성은 사용되는 타깃의 화학 조성을 통해 결정된다. 그러나, 타깃 내에 함유된 원소들의 약간 상이한 스퍼터링 거동(스퍼터링 수율)으로 인해, 타깃 조성으로부터 코팅 조성의 편차가 발생할 수 있다.

- [0046] 예를 들어, MoCu 타깃으로부터 Cu의 우선 스퍼터링에 의해, 증착된 코팅에서 Cu 함량이 약간 증가될 수 있다. 예를 들어, 10 at % 초과의 Cu를 함유해야 하는 코팅을 생성하기 위해, 상응하는 타깃은 10 at % 미만의 Cu를 함유할 수도 있다.

- [0047] 단일 타깃의 이용에 대한 대안으로, 금속 플라이는 개별 타깃들의 공동-증착, 바람직하게는 공동 스퍼터링(co-sputtering)을 통해 증착될 수도 있다. 이 경우, 코팅의 화학 조성은 상이한 타깃들의 선택을 통해 추가로 제어될 수 있다.

- [0048] 금속 플라이의 증착에 적합한 스퍼터링 타깃의 제조는, 예를 들어, 분말 야금에 의해 수행될 수 있다.

- [0049] 스퍼터링 타겟을 제조할 수 있는 분말 야금 경로는 열간 프레싱(hot pressing; HP) 또는 방전 플라즈마 소결(spark plasma sintering; SPS)과 같은 열간 프레싱 기술을 기반으로 한다. 두 경우 모두, 분말 혼합물이 프레스(press)의 몰드(mould)에 넣어지고, 몰드 내에서 가열되며, 고온에서 높은 프레스 압력으로 소결/치밀화되어 고밀도 부품(dense component)이 된다. 이 경우, 균일한 입자들을 갖는 균질한 미세구조가 얻어지며, 그것은 우선적인 배향(텍스처(texture))을 갖지 않는다.

- [0050] 스퍼터링 타겟을 제조하기 위한 유사한 분말-야금 경로는 열간 정수압 프레스법(hot isostatic pressing; HIP)이다. 이 경우, 압축될 재료는 변형가능하고 치밀한 용기(일반적으로 강철 캔)에 넣어진다. 그것은 이 경우 분말, 분말 혼합물, 또는 (압축된 분말 형태의) 성형체(green body)일 수 있다. 이러한 용기 내에 배치된 재료는 보호 가스(예를 들어, 아르곤) 하에서 높은 온도 및 압력에서 압력이 가해지는 가압조 내의 용기 안에서 소결/압축된다. 가스 압력을 모든 면으로부터 작용하며, 이에 따라 이 절차는 정수압 프레스법이라고 지칭된다. 일반적인 공정 파라미터는, 예를 들어, 1100°C 및 100 MPa과 3시간의 유지 시간이다. 이 경우, 균일한 입자들을 갖는 균질한 미세구조가 얻어지며, 그것은 우선적인 배향(텍스처)을 갖지 않는다.

- [0051] 분말-야금 경로를 통해 스퍼터링 타겟을 제조하기 위한 또 다른 옵션은 소결 및 후속 성형이다. 이 경우, 분말 반가공품이 수소 또는 진공 하에서 고온에서 소결된다. 소결 이후, 99% 초과의 높은 상대 밀도를 얻기 위해, 예를 들어, 압연 또는 단조와 같은, 성형 단계가 수행된다. 이 경우, 길쭉한 입자들을 갖는 미세구조가 얻어지며, 그것은 우선적인 배향(텍스처)을 갖는다. 경우에 따라 후속 응력-제거 어닐링(low-tension annealing) 또는 재결정 어닐링의 경우, 균일한 입자들을 갖는 균질한 미세구조가 얻어지지만, 여전히 그것은 우선적인 배향(텍스처)을 갖는다.

- [0052] 분말-야금 경로를 통해 스퍼터링 타겟을 제조하기 위한 또 다른 옵션은 열 용사 방법(thermal spraying method), 예를 들어, 냉가스 용사(cold gas spraying) 또는 진공 플라즈마 용사(vacuum plasma spraying; VPS)에 의해, 해당 지지 구조체, 예를 들어, 플레이트 또는 튜브에 분말 또는 분말 혼합물을 도포하는 것이다.

### 발명의 효과

- [0053] 본 발명에 의하면, 단일의 또는 반복적인 굽힘, 인장, 및/또는 비틀림 응력을 받는, 가요성 기판에 적용되는, 금속 플라이(metallic ply)의 전기 전도도가 유지된다. 특히, 본 발명에 의하면, 가요성 기판 상에 전기 도체

트랙(금속 플라이)이 제공되며, 여기서 도체 트랙의 전기 저항은 변형, 굽힘, 또는 비틀림 응력의 경우에 도체 트랙을 따라, 즉, 플라이 평면 내에서, 가능한 한 적게, 특히 10% 미만만큼, 변화된다.

### 도면의 간단한 설명

[0054]

본 발명은 이하에서 예시적인 실시형태들에 기초하여 그리고 도면들에 기초하여 보다 상세히 설명될 것이다.

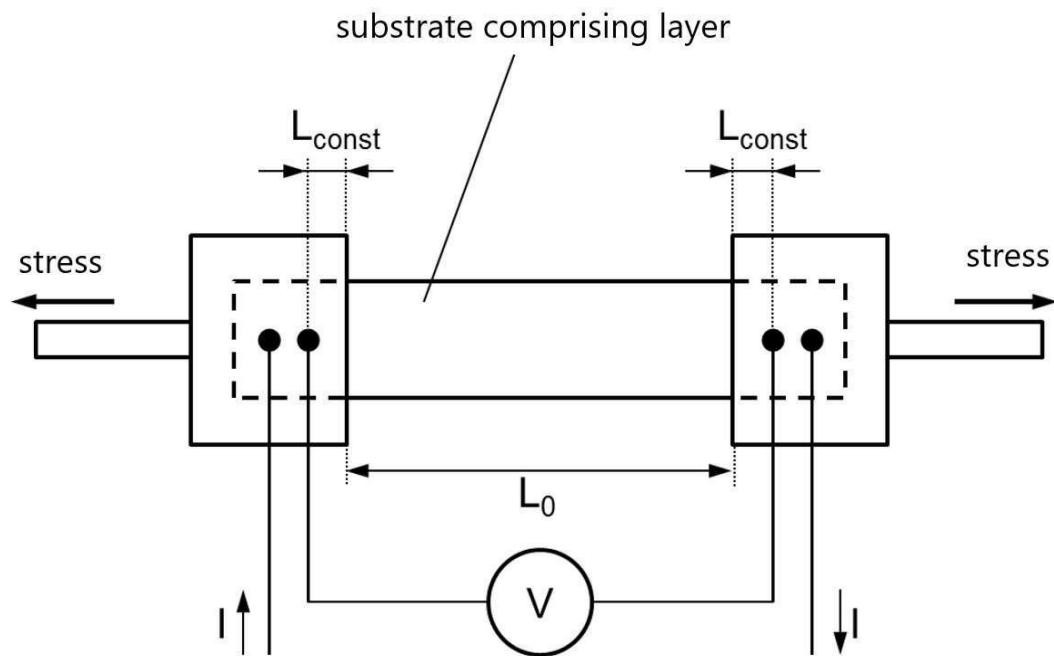

도 1은 임계 과단신율(critical elongation at fracture)  $\varepsilon_k$ 를 측정하기 위해 이용되는 전기 저항 측정을 갖는 단일-축 인장 실험의 개략적인 구조를 도시한다.

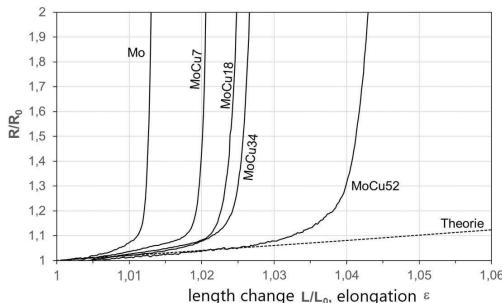

도 2는 Mo 및 MoCu 합금들에 대한  $R/R_0$  곡선들을, 총 내의 Cu 함량의 함수로서, 도시한다.

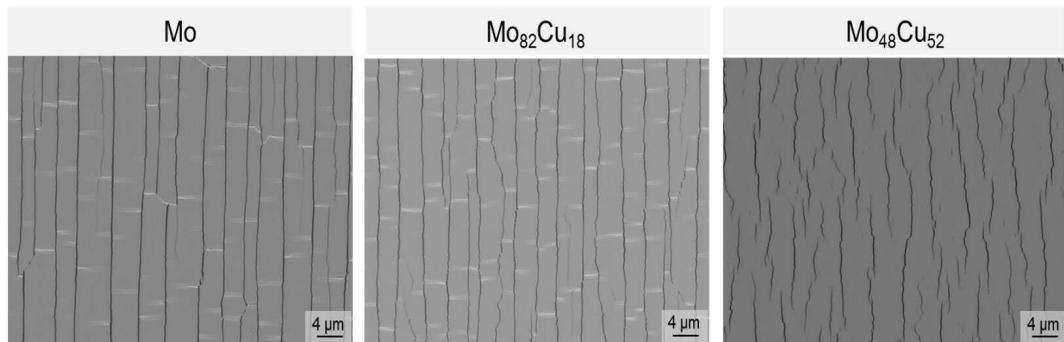

도 3은, 15%의 최대 신장 이후, Mo 층 및 다양한 MoCu 층들의 크래킹의 전자 현미경 이미지를 도시한다.

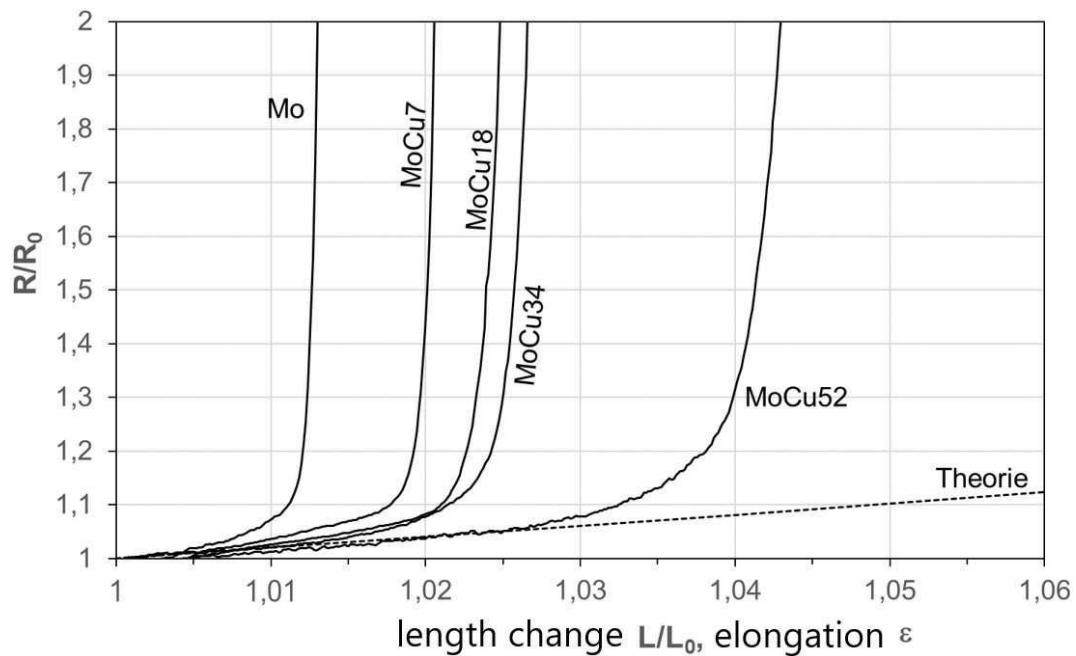

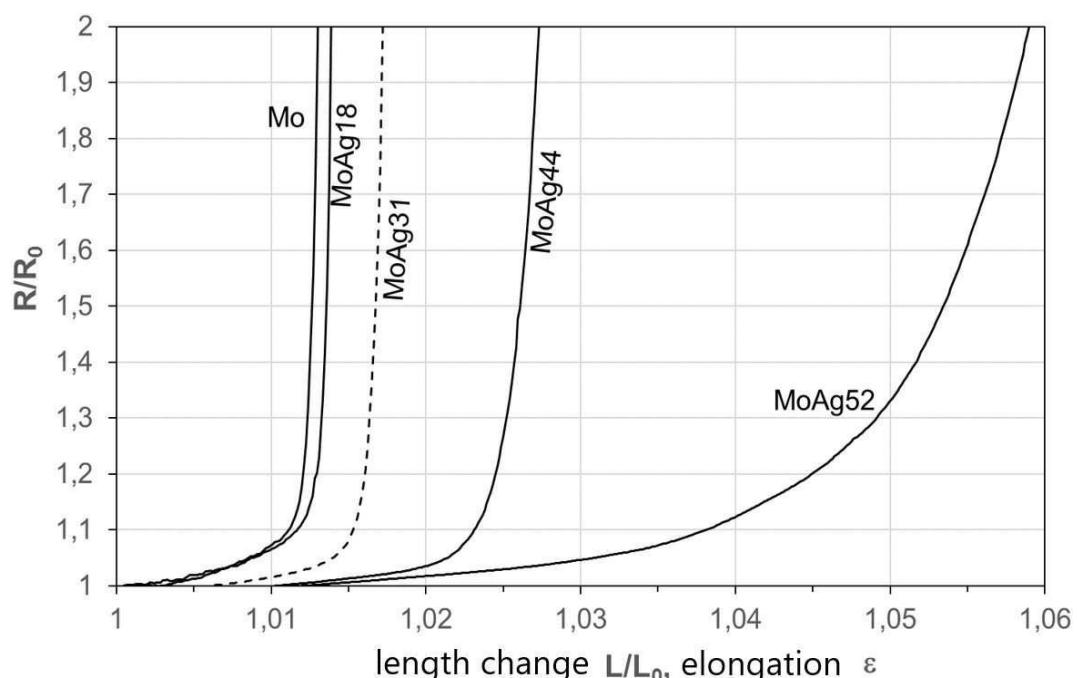

도 4는 Mo 및 MoAg 합금들에 대한  $R/R_0$  곡선들을, 총 내의 Ag 함량의 함수로서, 도시한다.

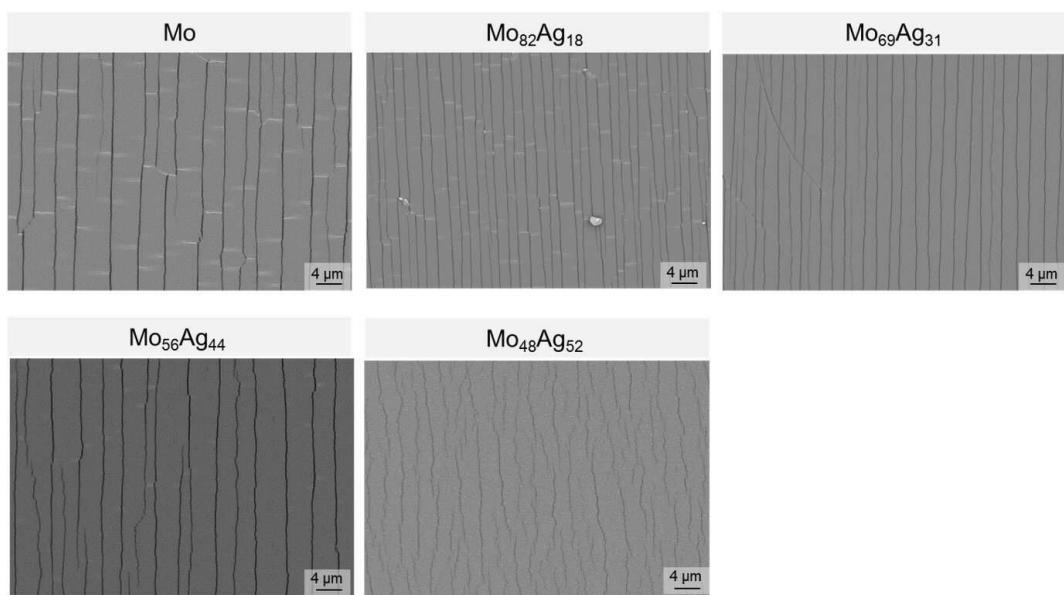

도 5는, 15%의 최대 신장 이후, Mo 층 및 다양한 MoAg 층들의 크래킹의 전자 현미경 이미지를 도시한다.

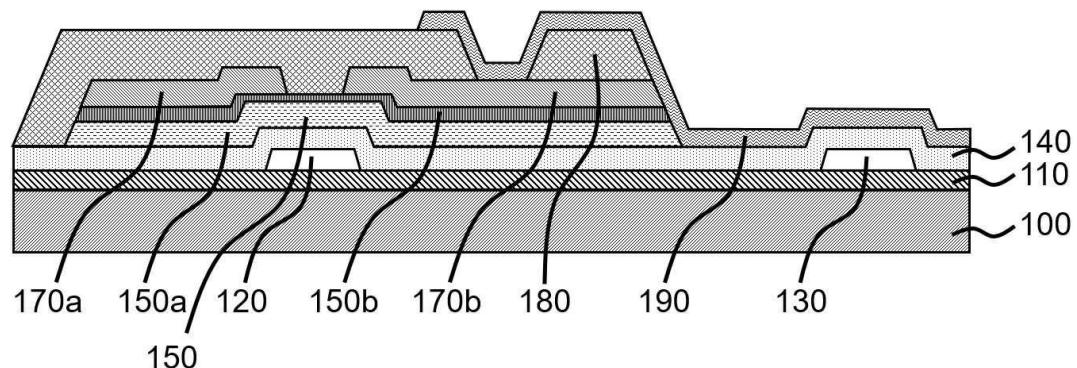

도 6은 하부 게이트 박막 트랜지스터(bottom gate thin-film transistor)의 층 구조를 단면도로 도시한다.

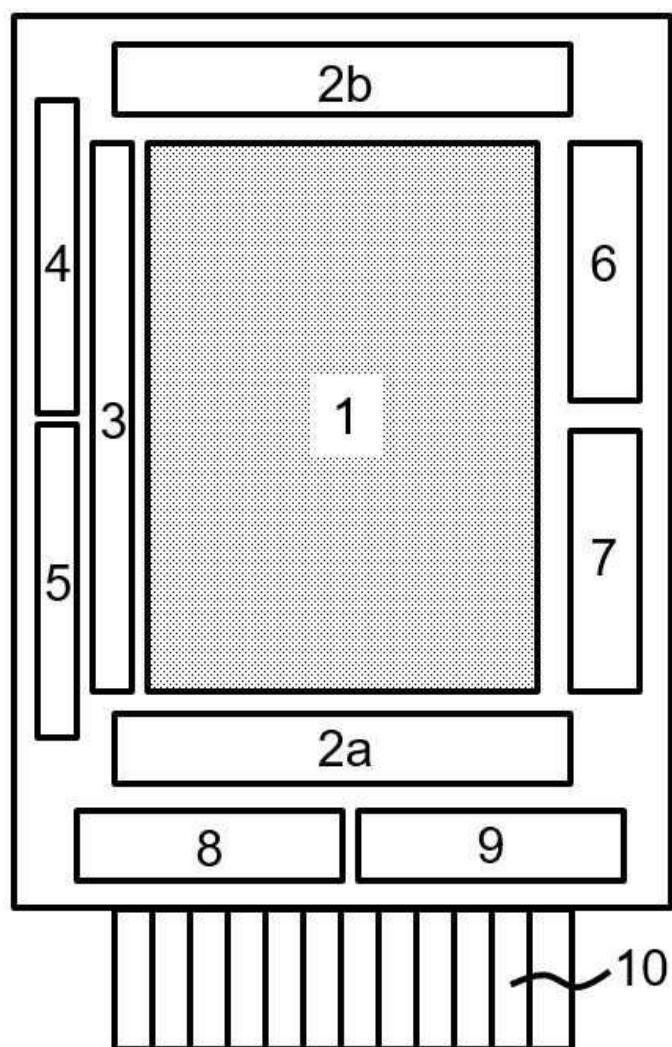

도 7은 System-on-panel 디스플레이 스크린의 개략적인 블록 선도를 도시한다 (위에서).

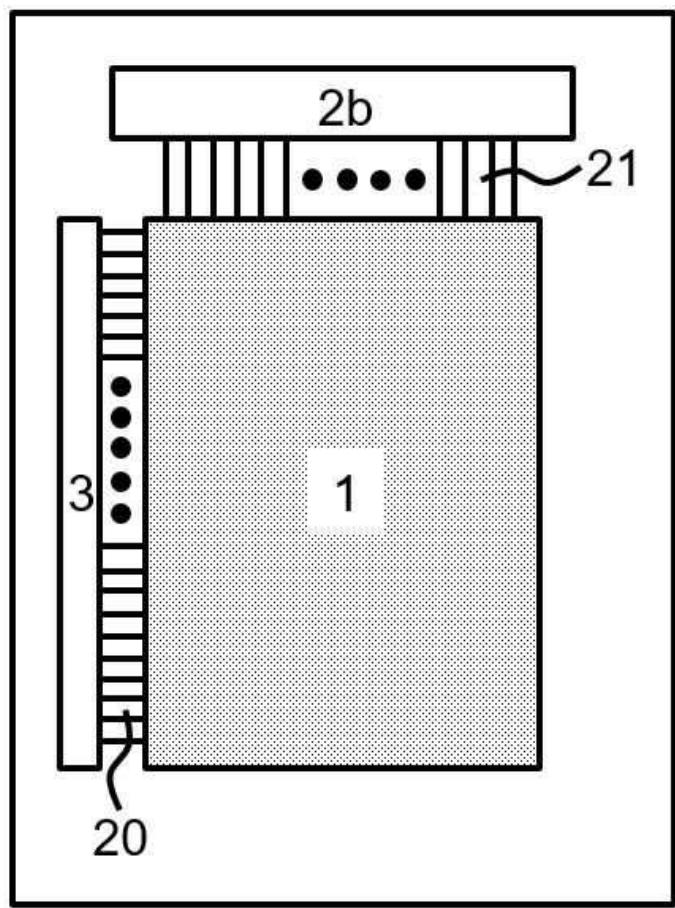

도 8은 System-on-panel 디스플레이 스크린의 세부 사항을 도시하며, 이는 드라이버 회로들과 TFT 디스플레이 스크린 영역 사이의 도체 트랙 구조를 위에서 도시한다.

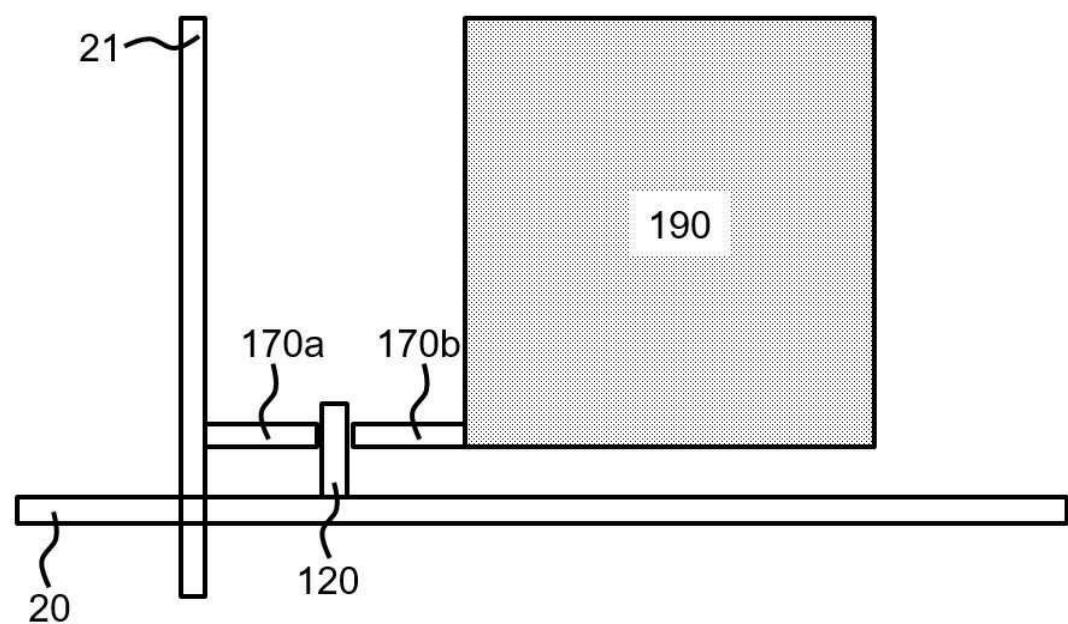

도 9는 TFT 디스플레이 스크린 구조의 세부사항을 도시하며 (위에서; 평면도), 이는 TFT의 게이트 및 소스/드레인 전극들이 게이트 및 데이터 라인들에 어떻게 연결되는지를 도시한다.

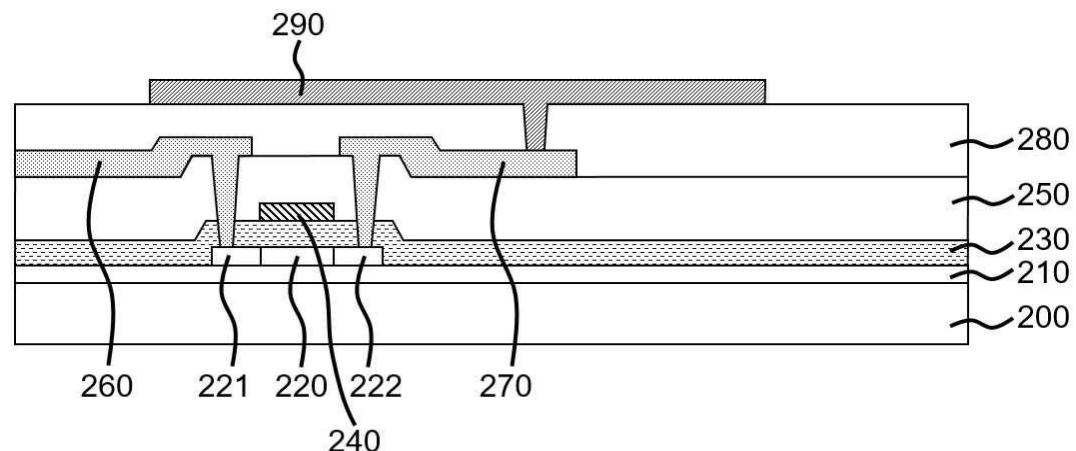

도 10은 티 게이트 LTPS-TFT(top gate LTPS-TFT)의 층 구조를 단면도로 도시한다.

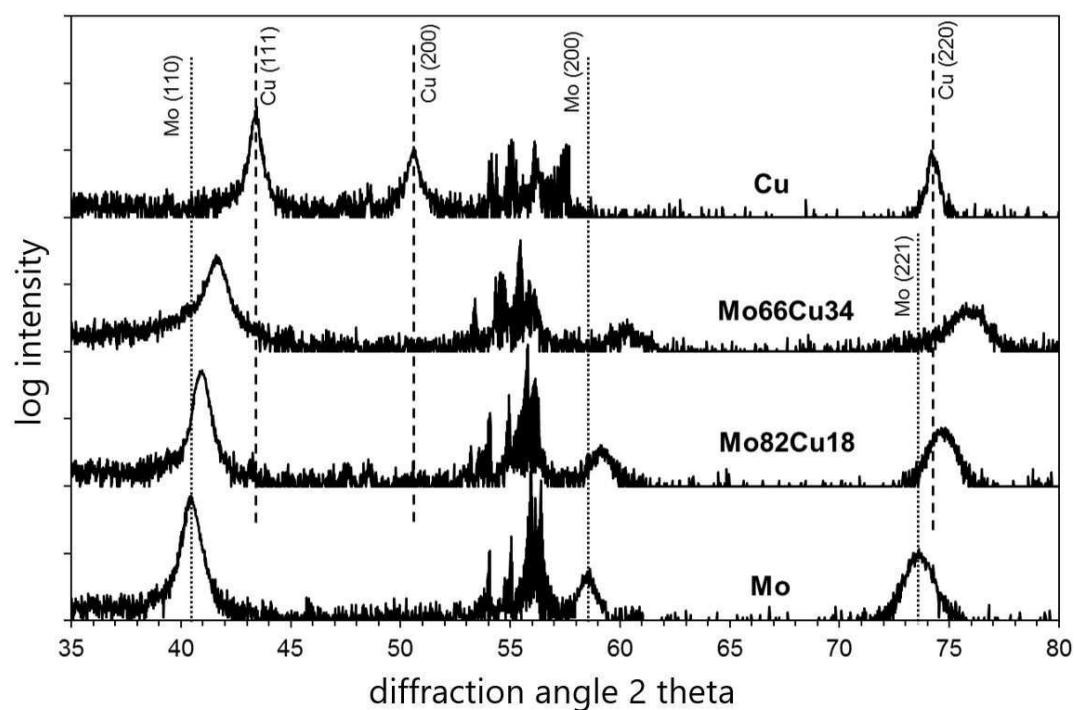

도 11은 실리콘 웨이퍼 상의 스퍼터링된 500 nm-두께 MoCu 박막의 x-선 회절도를 도시한다.

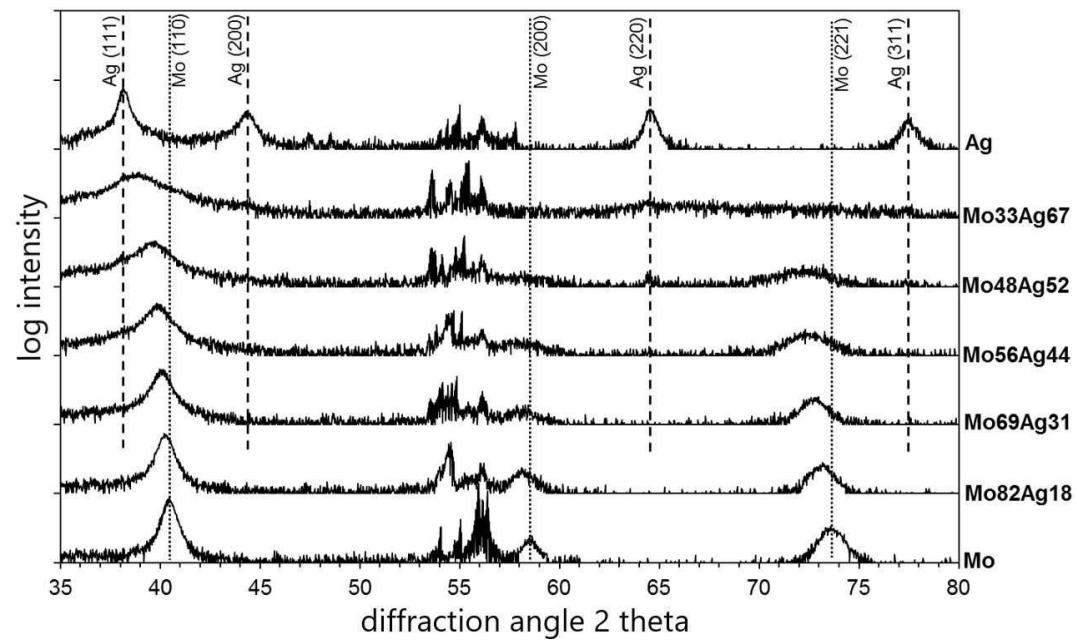

도 12는 실리콘 웨이퍼 상의 스퍼터링된 500 nm-두께 MoAg 박막의 x-선 회절도를 도시한다.

### 발명을 실시하기 위한 구체적인 내용

[0055]

실시예 1:

[0056]

일련의 여러 실험에서, 몰리브덴에 기초한 상이한 금속 층들이 폴리이미드 기판 상에 증착되었다. 이 경우, 상이한 화학 조성을 갖는 층들이 제조되었다.

[0057]

몰리브덴에 기초한 금속 층들의 조성이 테이블 1에 요약되어 있다.

[0058]

테이블 1: 스퍼터링된 MoCu 층들의 화학 조성

|         | Mo [at%] | Cu [at%] |

|---------|----------|----------|

| Layer 1 | 93       | 7        |

| Layer 2 | 82       | 18       |

| Layer 3 | 66       | 34       |

| Layer 4 | 48       | 52       |

[0059]

50 nm 두께를 갖는 몰리브덴 층의 형태로, 순수 Mo가 몰리브덴-계 합금을 위한 기준 재료로서 사용되었다.

[0060]

모든 층들은 실온에서 폴리이미드(PI, 예를 들어 "Kapton®")로 제조된 50  $\mu\text{m}$  두께의 필름 상에 증착되었다. 이 경우, 결과에 대한 상이한 공정 조건들의 영향을 가능한 한 배제하기 위해, 공정 파라미터들은 일정하게 유지되었다. 결과에 대한 기하학적 효과의 영향을 회피하기 위해, 층 두께는 50 nm로 일정하게 유지되었다.

[0062] 기판 표면은 완전히 코팅되었고, 어떠한 보다 작은 구조들도 예를 들어 애칭 방법에 의해 생성되지 않았다.

[0063] MTS Tyron 250® 범용 시험기를 이용하여 폴리이미드 기판 상의 층 샘플들에서 단축 인장 시험(uniaxial tension test)이 수행되었다. 실험 설정은 도 1에 개략적으로 도시되어 있다. 이 경우, 기판들은 15%의 최대 신장  $\epsilon$  까지 탄성 변형되었다. 인장 시험 동안, 층들의 전기 저항  $R$ 은 4점법(four-point method)을 이용하여 연속적으로 기록되었다. 측정 초기에서의 전기 저항은  $R_0$ 라고 지칭된다. 이 경우, 초기 상태에서의 샘플 길이(클램프들 사이의 자유 길이)는 20 mm이었으며, 폭은 5 mm이었다.

[0064] 측정 설정은 도 1에 개략적으로 도시되어 있다. 이 경우,  $L_{\text{const}}$ 는 고정 클램핑된 길이를 나타내며, 그 안에서는 신장이 일어나지 않는다. 임계 신장은 신장  $\epsilon_k$ 로서 정의되었으며, 거기에서 가요성 기판 상의 층들의 전기 저항  $R$ 은 초기 상태에 비해 10%만큼 증가되었으며, 즉,  $R/R_0 = 1.1$  이었다.

[0065] 이 인장 시험에 의해 확인된 임계 신장  $\epsilon_k$ 는 테이블 2에 열거되어 있다.

[0066] 테이블 2: 조사된 Mo 및 MoCu 층들의 임계 신장  $\epsilon_k$ , 및 순수 Mo로 제조된 기준 샘플과의 차이. 또한, 비전도성 블규산 유리(Corning Eagle XG®) 상의 500 nm 두께 층의 층 저항이 표시되어 있다.

| 재료          | 임계 신장 $\epsilon_k$ | $\Delta\epsilon_k$ | 층 저항 $\rho$ ( $\mu\text{Ohmcm}$ ) |

|-------------|--------------------|--------------------|-----------------------------------|

| Mo          | 1.10%              | 기준                 | 22                                |

| MoCu 7 at%  | 1.76%              | 0.66               | 77                                |

| MoCu 18 at% | 2.09%              | 0.99               | 119                               |

| MoCu 34 at% | 2.13%              | 1.03               | 132                               |

| MoCu 52 at% | 3.23%              | 2.13               | 97                                |

[0067]

[0068] 도 2는 적용된 신장  $\epsilon$  과 관련하여 초기 저항에 비해 전기 저항( $R/R_0$ )의 상승을 도시한다. 곡선 "theory"는 샘플의 형상 변화를 통해서만 발생하는 전기 저항의 증가를 나타낸다. 기준 재료에 대해 측정된 곡선에서 알 수 있는 바와 같이, 전기 저항은 신장이 증가함에 따라 매우 강하게 상승한다.

[0069]

전술한 인장 시험 후, 시험된 층들은 광학 현미경 및 주사 전자 현미경으로 조사되었다. 이 경우, 층에서 발생한 크랙들의 형상 및 크랙들 사이의 평균 거리가 평가되었다.

[0070]

예를 들어 순수 Mo와 같은, 취성 재료에 기초한 층에서, 취성 재료 거동에 전형적인 크랙 패턴이 인장 응력 하에서 샘플의 파괴 시 일반적으로 발생한다. 그것은, 하중 방향에 거의 직각으로 형성되는, 평행하게 연장 형성되는 선형 크랙들의 네트워크를 특징으로 한다. 그러한 크랙 패턴은, 예를 들어, 도 3(Mo, 좌측)에서 볼 수 있다. 이러한 선형 크랙들은 일반적으로 샘플의 전체 폭에 걸쳐 한쪽에서 다른 쪽으로 그리고 층의 전체 두께를 통해 연장 형성된다. 이러한 크랙들은 관통형 크랙(through thickness crack; TTC)이라고도 지칭된다. TTC는 층의 전기 전도도를 실질적으로 감소시키는데, 최악의 경우에 연속적인 전도성 연결이 층 내에 더이상 존재하지 않기 때문이다.

[0071]

불량 기준  $R/R_0 = 1.1$ 로부터 테이블 2에서 추론될 임계 신장은, 층 내의 Cu 함량이 증가함에 따라 층의 연성이 증가된다는 것을 보여준다. 연성의 이러한 증가는 재료 내에서 보다 용이한 변위 이동(easier displacement movement)에 의해 야기되는 것으로 추정된다. 이에 따라, 임계 신장이 증가되고, TTC의 발생이 감소된다.

[0072]

일례로서, 도 2는 샘플 MoCu 7 at %의 저항 곡선  $R/R_0$ 를 도시한다. 크랙들의 외양은 여전히 TTC에 해당하지만, 임계 신장  $\epsilon_k$ 는 이미 상당히 증가되어 있다.

[0073]

임계 신장  $\epsilon_k$ 의 증가 외에 관찰될 수 있는 또 다른 효과는, 크랙의 외양이 취성으로부터 연성 재료 거동으로 변한다는 것이다. 연성 재료 거동에 일반적인 크랙들은, 크랙들이 더이상 선형이지 않고 오히려 지그재그형 경로

를 보다 많이 갖는다는 점에서, 인식될 수 있다. 크랙 선단에서 크랙의 방향 변화는 그러한 크랙 거동의 가능한 설명이다.

[0074] 도 3(중간 이미지, MoCu 18 at %)에서, MoCu 18 at %의 경우, 크랙들은 실질적으로 평행하지만 더 이상 직선으로 연장 형성되지 않는다는 것을 볼 수 있다. 도 3(우측 이미지, MoCu 52 at %)에서는 이미 더 많은 연성 크랙 패턴을 명확히 볼 수 있다. 더 많은 연성 특성을 갖는 크랙들은 일반적으로 전체 층 두께를 통해 연장 형성되지만, 반드시 전체 샘플 폭에 걸쳐 연장 형성되는 것은 아니며, 이에 의해 재료 내에 전도성 연결들이 여전히 남아 있게 된다. 이 경우,  $R/R_0$  곡선의 기울기는, 도 2에서 볼 수 있는 바와 같이, 더 낮다 (곡선은 덜 빠르게 상승한다).

[0075] 이에 따라, 몰리브덴에 기초한 층에서 작은 Cu 함량에서부터, 임계 신장  $\varepsilon_k$ 는 이미 상당히 증가되고, 크랙들의 발생은 감소된다. Cu 함량의 추가 증가 시, 크래킹 거동은 취성으로부터 연성의 방향으로 변화된다. 이에 따라, Mo에 대한 첨가제로서 Cu는, 특히 적은 첨가도 Mo-계 층의 연성의 실질적인 증가를 가져오고 Cu가 재료로서 비교적 비용-효율적이라는 점에서, 구별된다.

[0076] 도 11은 각각 18 at %와 34 at %의 Cu 함량을 갖는 2개의 MoCu 층의 x-선 회절도를 도시한다. 각각 순수한 Mo 또는 Cu 층의 회절도가 참조로서 또한 포함되어 있다. 모든 층들은 실온에서 (기판 가열없이) 실리콘 웨이퍼 상에 DC 스퍼터링에 의해 증착되었으며, 500 nm의 두께를 갖는다. 결정 구조는,  $2^\circ$  의 입사각으로 스침 입사 모드(grazing incidence mode)에서, Cu-K $\alpha$  x-선 방사선 소스를 구비한, Bruker-AXS D8 회절계를 이용하여 기록되었다. 각각 참조로서, 체심 입방 구조(cI) 몰리브덴(공간군(space group) Im-3m)의 x-선 반사의 위치가 수직 점선으로 도시되어 있으며, 면심 입방 구조(cF) 구리(공간군 Fm-3m)의 반사 위치가 수직 파선으로 도시되어 있다; 데이터는 ICDD(International Centre for Diffraction Data)의 데이터베이스에서 가져온 것이다. 도 11에서 볼 수 있는 바와 같이, 높은 구리 함량을 갖는 2개의 시스템 MoCu 18 at % 및 MoCu 34 at %는 별도의 Cu 상(separate Cu phase)을 갖지 않는데, 해당 반사가 회절도에 존재하지 않기 때문이다. 이에 따라, Cu는 혼합 결정의 형태로 몰리브덴 내에 강제-용해되어 있는 것으로 추정될 수 있으며, 즉, 구리 원자들은 몰리브덴 격자 공간들을 차지한다. 이 방식으로 구리 원자들은 Mo 격자의 왜곡을 가져온다. 2개의 Mo (110) 및 Mo (200) 반사는 왜곡된 Mo 격자를 또한 나타내며, 이 반사들은 왜곡되지 않은 기준과 비교하여 보다 높은 회절(2 theta) 각도 쪽으로 이동되어 있는데, Cu 원자(원자 반경 128 pm)가 Mo 원자(140 pm)보다 더 작기 때문이다.

[0077] 또한, 테이블 2의 마지막 칼럼에, 다양한 Mo 또는 MoCu 박막들의 층 저항  $\rho$  ( $\mu\text{Ohmcm}$ )가 표시되어 있다 (절연 유리 기판 상의 500 nm 층 두께). 측정을 위해, 비표면 저항(specific surface resistance)  $R_s$  ( $\text{Ohm}/\text{Sheet}$ )는 4점법에 의해 측정되었고 층 두께를 곱하였다. MoCu 층들의 층 저항은 34 at %의 Cu 함량까지 증가하고, 이후에는 Cu 함량이 증가함에 따라 다시 감소한다. 모든 MoCu 층들은 150  $\mu\text{Ohmcm}$  미만의 층 저항을 갖는다.

[0078] MoCu/Cu 또는 MoCu/Al로 제조된 다중-플라이 층들의 경우, 긴 도체 트랙을 따른 층 저항은 보다 나은 전도도를 갖는 각각의 재료 Cu 또는 Al에 의해 특히 측정된다. (비전도성 유리 기판 상에 증착된) 50 nm MoCu 34 at % 및 그 위의 300 nm Cu로 제조된 2-플라이 층은 2.0  $\mu\text{Ohmcm}$ 의 층 저항을 갖는다. 50 nm MoCu 34 at % 및 그 위의 300 nm Al로 제조된 2-플라이 층은 3.1  $\mu\text{Ohmcm}$ 의 층 저항을 갖는다.

[0079] 조사된 층들의 기계적 특성들은 여전히 더 최적화될 수 있는 것으로 추정된다. 이에 따라, 표적화된 열처리를 통해, 몰리브덴에 기초한 증착 층들의 미세구조 및 내부 응력 상태는 더 최적화될 수 있는 가능성이 있다. 층들의 성장은 증착 조건들의 표적화된 설정을 통해 의도적으로 영향을 받을 수도 있고, 연성의 추가 증가가 달성될 수 있을 가능성이 매우 많다.

[0080] 실시예 2:

[0081] 일련의 여러 실험에서, 몰리브덴에 기초한 상이한 금속 층들이 폴리아미드 기판 상에 증착되었다. 이 경우, 상이한 화학 조성을 갖는 층들이 제조되었다.

[0082] 몰리브덴에 기초한 금속 층들의 조성이 테이블 3에 요약되어 있다.

[0083] 테이블 3: 스퍼터링된 MoAg 층들의 화학 조성

|         | Mo [at%] | Ag [at%] |

|---------|----------|----------|

| Layer 1 | 82       | 18       |

| Layer 2 | 69       | 31       |

| Layer 3 | 56       | 44       |

| Layer 4 | 48       | 52       |

[0084] [0085] 50 nm 두께를 갖는 몰리브덴 층의 형태로, 순수 Mo가 몰리브덴-계 합금을 위한 기준 재료로서 사용되었다.

[0086] 모든 층들은 실온에서 폴리아미드(PI, 예를 들어 "Kapton®")로 제조된 50 μm 두께의 필름 상에 증착되었다. 이 경우, 결과에 대한 상이한 공정 조건들의 영향을 가능한 한 배제하기 위해, 공정 파라미터들은 일정하게 유지되었다. 결과에 대한 기하학적 효과의 영향을 회피하기 위해, 층 두께는 50 nm로 일정하게 유지되었다.

[0087] 기판 표면은 완전히 코팅되었고, 어떠한 보다 작은 구조들도 예를 들어 애칭 방법에 의해 생성되지 않았다.

[0088] 실시예 1에서 설명된 바와 같은, 인장 시험에 의해 확인된 임계 신장  $\epsilon_c$ 가 테이블 4에 열거되어 있다.[0089] 테이블 4: 조사된 Mo 및 MoAg 층들의 임계 신장  $\epsilon_c$ , 및 순수 Mo로 제조된 기준 샘플과의 차이. 또한, 비전도성 봉규산 유리(Corning Eagle XG) 상의 500 nm 두께 층의 층 저항이 표시되어 있다.

| 재료          | 임계 신장 $\epsilon_c$ | $\Delta\epsilon_c$ | 층 저항 $\rho$ ( $\mu\text{Ohmcm}$ ) |

|-------------|--------------------|--------------------|-----------------------------------|

| Mo          | 1.10%              | 기준                 | 22                                |

| MoAg 18 at% | 1.16%              | 0.06               | 96                                |

| MoAg 31 at% | 1.52%              | 0.42               | 138                               |

| MoAg 44 at% | 2.31%              | 1.21               | 111                               |

| MoAg 52 at% | 3.81%              | 2.71               | 101                               |

[0090] [0091] 전술한 인장 시험 후, 시험된 층들은 광학 현미경 및 주사 전자 현미경으로 조사되었다. 이 경우, 층에서 발생한 크랙들의 형상 및 크랙들 사이의 평균 거리가 평가되었다.

[0092] 예를 들어 순수 Mo와 같은, 취성 재료에 기초한 층에서, 인장 응력 하에서 샘플의 파괴 시 크랙 패턴이 일반적으로 발생하며, 이는 취성 재료 거동에 전형적이다. 그것은, 응력 방향에 거의 직각으로 형성되는, 평행하게 연장 형성되는 선형 크랙들의 네트워크를 특징으로 한다. 그러한 크랙 패턴은, 예를 들어, 도 5(Mo, 좌측)에서 볼 수 있다. 그러한 크랙 패턴은, 예를 들어, 도 3(Mo, 좌측)에서 볼 수 있다. 이러한 선형 크랙들은 일반적으로 샘플의 전체 폭에 걸쳐 한쪽에서 다른 쪽으로 그리고 층의 전체 두께를 통해 연장 형성된다. 이러한 크랙들은 관통형 크랙(through thickness crack; TTC)이라고도 지칭된다. TTC는 층의 전기 전도도를 실질적으로 감소시키는데, 최악의 경우에 연속적인 전도성 연결이 층 내에 더이상 존재하지 않기 때문이다. 기준 재료에 대해 측정된 곡선에서 알 수 있는 바와 같이, 전기 저항은 신장이 증가함에 따라 매우 강하게 상승한다.

[0093] 이는, 적용된 신장  $\epsilon$ 과 관련하여 초기 저항에 비해 전기 저항( $R/R_0$ )의 상승을 도시하는, 도 4로부터 추론될 수 있다.[0094] 불량 기준  $R/R_0 = 1.1$ 로부터 테이블 4에서 추론될 수 있는 임계 신장은, 18 at % 초파의 층 내 임계 Ag 함량으로부터, 층의 연성이, 도 4 및 테이블 4로부터 알 수 있는 바와 같이, 상당히 증가된다는 것을 보여준다. 연성

의 이러한 증가는 재료 내에서 보다 용이한 변위 이동에 의해 야기되는 것으로 추정된다. 추가 결과로서, 이는 임계 신장의 증가와 TTC의 발생 감소를 가져온다. 이에 따라, Mo에 대한 첨가제로서 Ag는, 특히, 보다 많은 첨가가 Mo-계 층의 연성의 매우 높은 증가를 가져온다는 점에서, 구별된다.

[0095] 일례로서, 도 4는 다양한 MoAg 샘플들의 저항 곡선  $R/R_0$ 를 도시한다. 크랙들의 외양은, 도 5(상단 우측)로부터 알 수 있는 바와 같이, 여전히 TTC에 해당하지만, 임계 신장  $\epsilon_k$ 는 이미 상당히 증가되어 있다.

[0096] 임계 신장  $\epsilon_k$ 의 증가 외에 관찰될 수 있는 또 다른 효과는, 크랙의 외양이 취성으로부터 연성 재료 거동으로 변한다는 것이다. 연성 재료 거동에 일반적인 크랙들은, 크랙들이 더이상 선형이지 않고 오히려 지그재그형 경로를 보다 많이 갖는다는 점에서, 인식될 수 있다. 크랙 선단에서 크랙의 방향 변화는 그러한 크랙 거동의 가능한 설명이다.

[0097] 도 5(이미지 MoAg 44 at%)에서, MoAg 44 at%의 경우, 크랙들은 실질적으로 평행하지만 더이상 직선으로 연장 형성되지 않는다는 것을 볼 수 있다. 도 5(MoAg 52 at%)에서는 이미 더 많은 연성 크랙 패턴을 명확히 볼 수 있다. 더 많은 연성 특성을 갖는 크랙들은 일반적으로 전체 층 두께를 통해 연장 형성되지만, 반드시 전체 샘플 폭에 걸쳐 연장 형성되는 것은 아니며, 이에 의해 재료 내에 전도성 연결들이 여전히 남아 있게 된다. 이 경우,  $R/R_0$  곡선의 기울기는, 도 4에서 볼 수 있는 바와 같이, 더 낮다 (곡선은 덜 빠르게 상승한다).

[0098] 18 at%의 몰리브덴에 기초한 층 내의 임계 Ag 함량으로부터, 임계 신장  $\epsilon_k$ 는 상당히 증가되고, 크랙들의 발생은 감소된다. Ag 함량의 추가 증가 시, 크래킹 거동은 취성으로부터 연성의 방향으로 변화된다.

[0099] 도 12는 증착된 MoAg 층들의 x-선 회절도를 도시한다. 층 증착 및 결정 구조의 분석은 MoCu 시스템(도 11)과 유사하게 수행되었다. 각각 순수한 Mo 또는 Ag 층의 회절도가 참조로서 또한 포함되어 있다. 도 12에는, 각각 참조로서, 체심 입방 구조(cI) 몰리브덴(공간군 Im-3m)의 x-선 반사의 위치가 수직 점선으로 도시되어 있으며, 면심 입방 구조(cF) 은(공간군 Fm-3m)의 반사 위치가 수직 파선으로 도시되어 있다; 데이터는 ICDD(International Centre for Diffraction Data)의 데이터베이스에서 가져온 것이다. 도 12에서 볼 수 있는 바와 같이, MoAg 시스템들은 최대 44 at%의 은 함량까지 별도의 Ag 상을 갖지 않는데, 해당 반사가 회절도에 존재하지 않기 때문이다. 이에 따라, Ag가 혼합 결정의 형태로 몰리브덴 내에 강제-용해되어 있는 것으로 추정될 수 있으며, 즉, 은 원자들은 몰리브덴 격자 공간들을 차지한다. 이 방식으로 은 원자들은 Mo 격자의 왜곡을 가져온다. 2개의 Mo (110) 및 Mo (200) 반사는 왜곡된 Mo 격자를 또한 나타내며, 이 반사들은 왜곡되지 않은 기준과 비교하여 보다 낮은 회절 (2 theta) 각도 쪽으로 이동되어 있는데, Ag 원자(원자 반경 165 pm)가 Mo 원자(140 pm)보다 더 크기 때문이다. (220) 은 반사는 MoAg 52 at% 층에서 표시된 바와 같이 단지 인식 가능한데, 이는 cI-몰리브덴 매트릭스에서 별도의 은 상(separate silver phase)의 초기 석출을 나타낸다.

[0100] 이에 따라, MoCu 또는 MoAg 박막에서, 구리 또는 은(원소 X)은, 각각, cI-몰리브덴 격자 내에 강제-용해되어 있다. 순금(pure gold)의 결정 구조는 Cu 및 Ag의 것(공간군 Fm-3m)과 동일하다. 세 가지 원소들 모두 화학 원소 주기율표의 동일한 부분군(11족)에 있으며, 많은 면에서 유사한 화학적 및 물리적 거동을 보인다. 이에 따라, 40 at% 미만의 Au 함량을 갖는 스퍼터링된 MoAu 박막들은, 금 원자들이 cI-Mo 매트릭스 내에 강제-용해되어 있는, 혼합 결정의 형태로 또한 제공되는 것으로 추정될 수 있다.

[0101] 또한, 테이블 4의 마지막 칼럼에, 다양한 Mo 또는 MoAg 박막들의 층 저항  $\rho$  ( $\mu\text{Ohmcm}$ )가 표시되어 있다 (절연 유리 기판 상의 500 nm 층 두께). 측정을 위해, 비표면 저항  $Rs$  ( $\text{Ohm}/\text{Sheet}$ )는 4점법에 의해 측정되었고, 층 두께를 곱하였다. MoAg 층들의 층 저항은 31 at%의 Ag 함량까지 증가하고, 이후에는 Ag 함량이 증가함에 따라 다시 감소한다. 모든 MoAg 층들은 150  $\mu\text{Ohmcm}$  미만의 층 저항을 갖는다.

[0102] MoAg/Cu 또는 MoAg/Al로 제조된 다중-플라이 층들의 경우, 긴 도체 트랙을 따른 층 저항은 각각 보다 나은 전도성 재료 Cu 또는 Al에 의해 특히 측정된다. (비전도성 유리 기판 상에 증착된) 50 nm MoAg 31 at% 및 그 위의 300 nm Cu로 제조된 2-플라이 층은 2.0  $\mu\text{Ohmcm}$ 의 층 저항을 갖는다. 50 nm MoAg 31 at% 및 그 위의 300 nm Al로 제조된 2-플라이 층은 3.1  $\mu\text{Ohmcm}$ 의 층 저항을 갖는다.

[0103] 제2항에 그리고 경우에 따라 개선형태들 중 하나에 명시된 바와 같은, 하나의 또는 복수의 금속 플라이(플라이들)는 박막 트랜지스터(TFT)의 일부일 수 있다. 그러한 전기 박막 부품의 층 구조는 도 6에 단면도로 도시되어 있다. TFT는 반도체 층(150), 게이트 전극(120), 소스 전극(170a) 및 드레인 전극(170b)으로 이루어지며, 이들 3개의 금속 전도성 전극 층들 중 적어도 하나는 본 발명에 따른 금속 플라이로 이루어진다. 게이트 전극(120)

은 전기 절연 층(게이트 절연체, 게이트 유전체)(140)에 의해 반도체 층(150)으로부터 분리된다. 소스 전극(170a)은 전기 절연 패시베이션 층(180)에 의해 드레인 전극(170b)으로부터 분리된다. 또한, 이 패시베이션 층(180)은 (이하에서 설명되는 콘택홀(contact hole)을 제외하고) 픽셀 전극 층(190)으로부터 소스/드레인 전극들(170a/170b)을 또한 분리한다.

[0104] 도 6에서 일 실시형태에 따라 도시된 바와 같은, 하부-게이트 TFT의 일반적인 층 구조가 이하에서 설명될 것이다. TFT 층 구조는 가요성 기판(100) 상에 배치된다. 먼저, 가요성 기판(100)의 상부면 상의 있을 수 있는 불균일을 보상하기 위해, 또는 예를 들어 확산 또는 침투에 의해 반도체 층(150) 안으로 원하지 않는 오염물질들의 침투를 방지하기 위해, 가요성 기판(100) 상에 전체 기판(100)을 덮는 베퍼 층(110)이 배치될 수 있다. 베퍼 층은, 예를 들어, 산화 규소 또는 질화 규소를 함유하는 단일-플라이 또는 다중-플라이 층으로 이루어질 수 있다. 게이트 전극(120)은 베퍼 층(110) 위에 배치된다. 전압을 인가함으로써, 반도체 층(150)에서의 전기장 효과의 결과로서, 전기 전도성 채널이 형성될 수 있으며, 이는 소스 전극(170a)을 드레인 전극(170b)에 전기 전도성으로 연결한다. 게이트 전극(120)은 본 발명에 따른 금속 플라이로 이루어질 수 있으며, 또는 단일-플라이 또는 다중-플라이 층으로 제조된 종래 기술에 해당하는 금속화로 이루어질 수 있으며, 이는 적어도 알루미늄(Al), 구리(Cu), 은(Ag), 금(Au), 백금(Pt), 몰리브덴(Mo), 텉스텐(W), 티타늄(Ti), 크롬(Cr), 니오븀(Nb), 탄탈(Ta)을 포함한다.

[0105] 게이트 전극(120) 위에는 전기 절연 층(게이트 유전체)(140)가 배치된다. 이러한 전기 절연 층(140)은, 예를 들어, 산화 규소, 질화 규소, 산화 알루미늄, 또는 전기 절연성 유기 물질, 예를 들어 벤조사이클로부텐(benzocyclobutene; BCB) 또는 아크릴 함유 물질로 제조된 층을 포함할 수 있다.

[0106] 반도체 층(150)은 전기 절연 층(게이트 유전체)(140)과 인접하고, 예를 들어, 비정질 실리콘(a-Si), 폴리실리콘, 인듐-갈륨-아연 산화물(IGZO)과 같은 금속 산화물 반도체, 또는 유기 반도체를 포함할 수 있다. a-Si를 포함하는 반도체 층(150a)의 경우, 이러한 층 위에 n<sup>+</sup> 도핑된 반도체 층(150b)이 배치될 수도 있으며, 예를 들어 인-도핑된 a-Si(phosphorus-doped a-Si)를 포함하는 반도체 층이 배치될 수도 있다. IGZO와 같은 금속 산화물 반도체를 포함하는 반도체 층(150a)의 경우, 도핑된 반도체 층(150b)은 일반적으로 생략된다.

[0107] 반도체 층(150) 위에는 소스 및 드레인 전극 층들(170a 및 170b)이 배치된다. 이러한 층들은 본 발명에 따른 금속 플라이로 이루어질 수 있으며, 또는 단일-플라이 또는 다중-플라이 층으로 제조된 종래 기술에 해당하는 금속화로 이루어질 수 있으며, 이는 적어도 알루미늄(Al), 구리(Cu), 은(Ag), 금(Au), 백금(Pt), 몰리브덴(Mo), 텉스텐(W), 티타늄(Ti), 크롬(Cr), 니오븀(Nb), 탄탈(Ta)을 포함한다.

[0108] 반도체 층(150) 및 소스/드레인 전극 층들(170a/170b) 위에는 패시베이션 층(180)이 배치된다. 이러한 전기 절연 패시베이션 층(180)은, 예를 들어, 산화 규소, 질화 규소, 산화 알루미늄, 또는 전기 절연성 유기 물질, 예를 들어 벤조사이클로부텐(BCB) 또는 아크릴 함유 물질로 제조된 층을 포함할 수 있다.

[0109] 패시베이션 층(180)은 콘택홀(contact hole)에 의해 단절되며, 콘택홀은 인접하는 픽셀 전극 층(190)을 드레인 전극(170b)에 전기적으로 연결한다. 픽셀 전극 층(190)은 전기 전도성이 있고, 광학적으로 투명한 층으로서 또는 광학적으로 반사층으로서 형성될 수 있으며, 단일-플라이 또는 다중-플라이로서 구현될 수 있다. 픽셀 전극 층(190)이 광학적으로 투명한 층으로서 형성되는 경우, 예를 들어, ITO(indium-tin oxide), IZO(indium-zinc oxide), ZnO(zinc oxide), 또는 AZO(aluminium-zinc oxide)를 포함할 수 있다. 픽셀 전극 층(190)이 광학적으로 반사층으로서 형성되는 경우, Al, Ag, Mg, Pt, Pd, Au, Nd, Ni, Ir로 제조된 반사층, 그리고 또한 ITO(indium-tin oxide), IZO(indium-zinc oxide), ZnO(zinc oxide), 또는 AZO(aluminium-zinc oxide)를 포함하는 층을 포함할 수 있다.

[0110] 여기서 설명된 TFT는 플렉시블 TFT-LCD 디스플레이 스크린 또는 OLED 디스플레이 스크린의 일부일 수 있다.

[0111] 제2항에 그리고 경우에 따라 개선형태들 중 하나에 명시된 바와 같은, 하나의 또는 복수의 금속 플라이(플라이들)는 SOP(system-on-panel) 시스템의 일부일 수 있으며, 거기에서는 TFT 액티브-매트릭스 디스플레이가 기판 상에 주변 전자 제어 유닛들과 함께 배치된다. 도 7에 SOP가 도시되어 있다. 디스플레이 유닛(1)은, 예를 들어, LCD(liquid crystal display), OLED(organic light-emitting diode), 무기 LED(inorganic light-emitting diode), 또는 전기영동 디스플레이 스크린("E-Ink®"; "e-paper")로 이루어질 수 있다. 디스플레이 유닛(1)은, 이미지 콘텐트가 표시되는, 디스플레이 스크린의 실제 가시 부분을 나타낸다. 이러한 영역 주위에는 기판 상에 복수의 드라이버 및 제어 회로들이 배치되며, 이들은 일반적으로 하우징의 불투명한 부분 뒤에 숨겨져 있어서, 사용자에게 보이지 않는다. 원칙적으로, 이하에서 설명되는 하나 또는 복수의 전자 회로들이 SOP 상에 배치될

수 있으며, 이러한 목록은 완전한 것이 아니고 사용되는 디스플레이 유닛에 따라 제어를 위해 추가 회로들이 필요할 수 있다.

[0112] 디스플레이 유닛(1)을 제어하기 위해, 수평의 데이터 드라이버 회로(열 드라이버; column driver)(2a/b)가 기판 상에 배치될 수 있으며, 이는 데이터 라인들(미도시)을 통해 TFT(미도시)의 소스/드레인 전극들(170a/b)에 연결된다. 게이트 전극(120)들을 제어하기 위해, 기판 상에 게이트 드라이버 구조(행 드라이버; row driver)(3)가 위치될 수 있으며, 이는 게이트 라인들(미도시)을 통해 TFT(미도시)의 게이트 전극(120)들에 연결된다.

[0113] 또한, 주변 영역에 DC-DC 변환기 회로(4)가 배치될 수 있으며, 이는 보다 낮은 입력 전압을 보다 높은 출력 전압으로 변환한다; TFT-LCD 디스플레이 스크린의 제어를 위해, 예를 들어, +3.3 내지 +5.0 V의 전압이 입력부에 인가될 수 있으며, 이는 액정(liquid crystal)을 제어하는 데 필요한 -40 내지 +40 V 범위의 보다 높은 출력 전압으로 변환된다 ("차지 펌프; charge pump").

[0114] 또한, SOP 상에 전기 회로(5)가 배치될 수 있으며, 이는 디스플레이 유닛(1)을 위해 기준 전압(Vcom, 예를 들어, LCD 디스플레이 스크린의 경우 +5V)을 제공한다.

[0115] 또한, 기판 상에 타이밍 제어기 회로(TCon)(6), 디지털-아날로그 변환기 회로(7), 방전 스테이지(8), 그리고 Vcom 버퍼 회로(9)가 배열될 수도 있다.

[0116] SOP는 접촉 영역(10)을 통해 디스플레이 제어 전자 기기의 다른 부품들 또는 그래픽 카드에 연결된다. 주변 회로들(2 내지 9)은 본 발명에 따른 금속 플라이(미도시)를 이용하여 디스플레이 유닛(1) 및 접촉 영역("pad contacts")(10)에 상호 연결된다.

[0117] 도 8에는, 디스플레이 유닛(1)의 접촉이 예로서 도시되어 있다. 행 드라이버(3)는 전기 도체 트랙(20)들을 통해 디스플레이 유닛(1)에 연결되어 있고, 열 드라이버(2b)는 전기 도체 트랙(21)들을 통해 디스플레이 유닛(1)에 연결되어 있다. 하나 또는 둘 모두의 도체 트랙(20 또는 21)은, 제2항에 그리고 경우에 따라 개선형태들 중 하나에 명시된 바와 같은, 본 발명에 따른 금속 플라이로 이루어질 수 있다.

[0118] 도 9는 게이트 및 데이터 라인들과 TFT(thin-film transistor)의 접촉을 도시한다. 게이트 도체 트랙(20)은, TFT의 게이트 전극(120)을 형성하는, TFT의 영역에서의 연장부를 갖는다. 데이터 도체 트랙(21)은, TFT의 소스 전극(170a)을 형성하는, TFT의 영역에서의 연장부와, TFT의 드레인 전극(170b)을 형성하는, 그리고 꽉 채운 전극(190)에 연결되는, 소스 전극에 의해 단절되는 영역을 갖는다. 하나 또는 둘 모두의 도체 트랙(20 또는 21) 및 /또는 TFT 전극들(120, 170a/b)은, 제2항에 그리고 경우에 따라 개선형태들 중 하나에 명시된 바와 같은, 본 발명에 따른 금속 플라이로 이루어질 수 있다.

[0119] 또한, 제2항에 그리고 경우에 따라 개선형태들 중 하나에 명시된 바와 같은, 하나의 또는 복수의 금속 플라이(플라이들)는 저온 폴리실리콘(LTPS) 박막 트랜지스터(TFT)의 일부일 수 있으며, 그것의 층 구조는 도 10에 단면도로 예로서 도시되어 있다. 도 6으로부터의 TFT 구조와 비교하면, 이 경우에는 상부-게이트 TFT이며, 즉, 게이트 전극(240)은 반도체 층(220) 위에 배치되며, 아래에 배치되지 않는다. LTPS-TFTs는 바람직하게는 상부-게이트 TFT로서 구현된다. LTPS 반도체는 비정질 실리콘( $0.5 \sim 1.5 \text{ cm}^2/\text{Vs}$ )과 비교하여 상당히 더 높은 전하 운반체 이동도(charge carrier mobility)( $50 \sim 200 \text{ cm}^2/\text{Vs}$ )를 갖는다. 이에 따라, 그러한 TFT는, 예를 들어 OLEDs 또는 마이크로-LEDs와 같은, 전류-구동 디스플레이를 제어하기 위해 이용될 수도 있다.

[0120] 이하에서는 상부-게이트 LTPS TFT의 층 구조가 예로서 설명될 것이다. LTPS-TFT는 가요성 기판(200)상에 배치된다. 먼저, 가요성 기판(200)의 상부면 상의 있을 수 있는 불균일을 보상하기 위해, 또는 예를 들어 확산 또는 침투에 의해, 반도체 층(220) 안으로 또는 도핑된 반도체 영역들(221(소스 전극) 및 222(드레인 전극)) 안으로 원하지 않는 오염물질들의 침투를 방지하기 위해, 가요성 기판(200) 상에 전체 기판(200)을 덮는 베퍼 층(210)이 배치될 수 있다. 베퍼 층(210)은, 예를 들어, 산화 규소, 질화 규소, 또는 산질화 규소(silicon oxynitride)를 포함하는 단일-플라이 또는 다중-플라이 층으로 이루어질 수 있다. 기판의 조성에 따라, 베퍼 층은 생략될 수도 있다.

[0121] 베퍼 층(210) 상에는 반도체 층(220)이 배치되며, 이 반도체 층은 도핑되지 않은 다결정 실리콘으로 이루어질 수 있다. 이러한 층(220)("channel area"라고도 함)에 인접하여 일측에 소스 전극(221)이 위치되고 다른 일측에 드레인 전극(222)이 위치되며, 이들은 각각 도핑된 폴리실리콘으로 이루어질 수 있다. 도핑은, 예를 들어, 이온 주입에 의해 수행될 수 있다; 예를 들어, 봉소(B) 또는  $\text{B}_2\text{H}_6$ 의 이용에 의해, p-도핑이 달성될 수 있다. 그

러나, TFT의 실시형태에 따라, 도핑의 유형(p 또는 n) 및/또는 도편트(dopant)의 종류는 달라질 수 있다.

[0122] 반도체 층들(220, 221, 및 222) 위에 게이트 절연체 층(230)이 배치된다. 이러한 게이트 절연체 층(230)은, 예를 들어, 질화 규소 또는 산화 규소로 이루어질 수 있다. 게이트 절연체 층(230) 상에는 게이트 전극(240)이 채널 영역(반도체 층(220))과 (수직 방향으로) 적어도 소정의 중첩 영역을 갖도록 배치된다. 게이트 전극(240)은 본 발명에 따른 금속 플라이로 이루어질 수 있으며, 또는 단일-플라이 또는 다중-플라이 층으로 제조된 종래 기술에 해당하는 금속화로 이루어질 수 있으며, 이는 적어도 알루미늄(Al), 구리(Cu), 은(Ag), 금(Au), 백금(Pt), 몰리브덴(Mo), 텉스텐(W), 티타늄(Ti), 크롬(Cr), 니오븀(Nb), 탄탈(Ta)을 포함한다. 게이트 전극(240)은 게이트 라인들(미도시)을 통해 제어 전자 기기(미도시), 특히, 행 드라이버에 연결된다.

[0123] 게이트 전극(240) 및/또는 게이트 절연체 층(230) 상에는 절연 층(250)이 적용되며, 이는 게이트 절연체 층(230)과 유사한 재료, 예를 들어, 질화 규소 또는 산화 규소로 이루어질 수 있다. 절연 층(250) 및 게이트 절연체 층(230)에는 관통 홀(through hole)들이 제공되며, 이는 소스 및 드레인 전극들(221/222)이 반도체 층에 (전기적으로) 액세스 가능하게 한다.

[0124] 제어 및/또는 접촉 소스 전극(260)과 제어 및/또는 접촉 드레인 전극 층(270)이 절연 층(250) 위에 배치되고, 전술된 관통 홀들을 통해 반도체의 소스/드레인 전극들(221/222)에 연결된다. 제어 및/또는 접촉 소스/드레인 전극 층들(260/270)은 본 발명에 따른 금속 플라이로 이루어질 수 있으며, 또는 단일-플라이 또는 다중-플라이 층으로 제조된 종래 기술에 해당하는 금속화로 이루어질 수 있으며, 이는 적어도 알루미늄(Al), 구리(Cu), 은(Ag), 금(Au), 백금(Pt), 몰리브덴(Mo), 텉스텐(W), 티타늄(Ti), 크롬(Cr), 니오븀(Nb), 탄탈(Ta)을 포함한다. 제어 및/또는 접촉 소스 전극 층(260)은 데이터 라인들(신호 라인들; 미도시)을 통해 제어 전자 기기, 특히, 열 드라이버(미도시)에 연결된다.

[0125] 박막 트랜지스터는 반도체 층(220), 게이트 전극(240), 및 제어 및/또는 접촉 소스/드레인 전극 층들(260/270)로부터 형성된다. 그러나, TFT의 구성은 전술된 예시적인 실시형태에 한정되지 않고, 전문가에 의해 용이하게 구현될 수 있는 다른 많은 구성들을 가질 수도 있다.

[0126] TFT 구조 위에는 평탄화 층(280)이 배치될 수도 있으며, 특히, 예를 들어 OLED 층들(미도시)과 같은, 추가 발광 층들이 TFT 위에 배치되는 경우에 그려하다. 평탄화 층(280)은, 예를 들어, 폴리아크릴레이트 수지, 에폭시 수지, 페놀 수지, 폴리아미드 수지, 폴리아미드 수지, 불포화 폴리에스테르 수지, 폴리페닐렌-에테르 수지, 폴리페닐렌-설파이드 수지, 또는 벤조사이클로부텐(BCB)을 포함할 수 있다. 평탄화 층(280)에는 제어 및/또는 접촉 드레인 전극 층(270)을 액세스 가능하게 하는 관통 홀이 제공된다.

[0127] 도 10에는 픽셀 전극 층(290)이 또한 예로서 도시되어 있으며, 이는 평탄화 층(280) 위에 적용되어 있고, 관통 홀을 통해 제어 및/또는 접촉 드레인 전극 층(270)에 전기 전도성으로 연결되어 있다. LTPS-OLED 디스플레이 스크린의 경우, 픽셀 전극 층(290)은 발광 구조체의 제1 전극(일반적으로 상향으로 방출하는 구조체의 음극)을 형성한다. 픽셀 전극 층(290)이 광학적으로 투명한 층으로서 형성되는 경우, 예를 들어, ITO(indium-tin oxide), IZO(indium-zinc oxide), ZnO(zinc oxide), 또는 AZO(aluminium-zinc oxide)를 포함할 수 있다.

[0128] 픽셀 전극 층(290)이 광학적으로 반사층으로서 형성되는 경우, Al, Ag, Mg, Pt, Pd, Au, Nd, Ni, Ir로 제조된 반사층, 그리고 또한 ITO(indium-tin oxide), IZO(indium-zinc oxide), ZnO(zinc oxide), 또는 AZO(aluminium-zinc oxide)를 포함하는 층을 포함할 수 있다.

[0129] 조사된 층들의 기계적 특성들은 여전히 더 최적화될 수 있는 것으로 추정된다. 이에 따라, 표적화된 열처리를 통해, 몰리브덴에 기초한 증착 층들의 미세구조 및 내부 응력 상태는 더 최적화될 수 있는 가능성성이 있다. 층들의 성장은 증착 조건들의 표적화된 설정을 통해 의도적으로 영향을 받을 수도 있고, 연성의 추가 증가가 달성될 수 있을 가능성이 매우 많다.

### 부호의 설명

[0130] R 층들의 전기 저항

$R_0$  측정 초기에서의 전기 저항

$R_0$  비표면 저항

$\varepsilon$  최대 신장

|                    |                             |

|--------------------|-----------------------------|

| $\varepsilon_k$    | 임계 신장                       |

| $L_{\text{const}}$ | 안에서는 신장이 일어나지 않는 고정 클램핑된 길이 |

| $\rho$             | 충 저항                        |

| 1                  | 디스플레이 유닛                    |

| 2a/b               | 데이터 드라이버 회로(열 드라이버)         |

| 3                  | 게이트 드라이버 구조(행 드라이버)         |

| 4                  | DC-DC 변환기 회로                |

| 5                  | 전기 회로                       |

| 6                  | 타이밍 제어기 회로(TCon)            |

| 7                  | 디지털-아날로그 변환기 회로             |

| 8                  | 방전 스테이지                     |

| 9                  | 버퍼 회로                       |

| 10                 | 접촉 영역("pad contacts")       |

| 20                 | 전기 도체 트랙들                   |

| 21                 | 전기 도체 트랙들                   |

| 100                | 가요성 기판                      |

| 110                | 버퍼 충                        |

| 120                | 게이트 전극                      |

| 140                | 전기 절연 층(게이트 절연체, 게이트 유전체)   |

| 150                | 반도체 층                       |

| 170a               | 소스 전극                       |

| 170b               | 드레인 전극                      |

| 180                | 전기 절연 패시베이션 층               |

| 190                | 픽셀 전극 층                     |

| 200                | 가요성 기판                      |

| 210                | 버퍼 층                        |

| 220                | 반도체 층                       |

| 221                | 도핑된 반도체 영역(소스 전극)           |

| 222                | 도핑된 반도체 영역(드레인 전극)          |

| 230                | 게이트 절연체 층                   |

| 240                | 게이트 전극                      |

| 250                | 절연 층                        |

| 260                | 제어 및/또는 접촉 소스 전극 층          |

| 270                | 제어 및/또는 접촉 드레인 전극 층         |

| 280                | 평탄화 층                       |

## 도면

## 도면1

## 도면2

## 도면3

## 도면4

## 도면5

도면6

도면7

도면8

도면9

도면10

도면11

도면12