(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6919133号

(P6919133)

(45) 発行日 令和3年8月18日(2021.8.18)

(24) 登録日 令和3年7月28日(2021.7.28)

|                         |                      |

|-------------------------|----------------------|

| (51) Int.Cl.            | F 1                  |

| HO 1 L 29/78 (2006.01)  | HO 1 L 29/78 6 5 2 K |

| HO 1 L 21/336 (2006.01) | HO 1 L 29/78 6 5 3 C |

| HO 1 L 21/283 (2006.01) | HO 1 L 29/78 6 5 8 F |

| HO 1 L 29/41 (2006.01)  | HO 1 L 21/283 B      |

|                         | HO 1 L 29/44 Y       |

請求項の数 14 (全 28 頁)

|                    |                               |

|--------------------|-------------------------------|

| (21) 出願番号          | 特願2017-558391 (P2017-558391)  |

| (86) (22) 出願日      | 平成28年5月9日(2016.5.9)           |

| (65) 公表番号          | 特表2018-515927 (P2018-515927A) |

| (43) 公表日           | 平成30年6月14日(2018.6.14)         |

| (86) 国際出願番号        | PCT/US2016/031517             |

| (87) 国際公開番号        | W02016/179598                 |

| (87) 国際公開日         | 平成28年11月10日(2016.11.10)       |

| 審査請求日              | 平成31年4月24日(2019.4.24)         |

| (31) 優先権主張番号       | 14/706, 927                   |

| (32) 優先日           | 平成27年5月7日(2015.5.7)           |

| (33) 優先権主張国・地域又は機関 | 米国(US)                        |

|           |                                                                                                                       |

|-----------|-----------------------------------------------------------------------------------------------------------------------|

| (73) 特許権者 | 507107291<br>テキサス インスツルメンツ インコーポ<br>レイテッド<br>アメリカ合衆国 テキサス州 75265<br>-5474 ダラス メイル ステイショ<br>ン 3999 ピーオーボックス 655<br>474 |

| (74) 代理人  | 100098497<br>弁理士 片寄 恒三                                                                                                |

| (72) 発明者  | 河原 秀明<br>アメリカ合衆国 75093 テキサス州<br>ブレイノ, エイビーティー 2121<br>, チャールズ ブレース 4701                                               |

最終頁に続く

(54) 【発明の名称】複数遮蔽トレンチゲートFET

## (57) 【特許請求の範囲】

## 【請求項 1】

半導体デバイスを形成する方法であって、

半導体材料を含む基板を提供することと、

前記基板において縦型MOSトランジスタのドレイン領域を形成することと、

前記ドレイン領域の上方の前記半導体材料において前記縦型MOSトランジスタの縦型

ドリフト領域を形成することと、

前記縦型ドリフト領域においてトレンチを形成することと、

前記基板に接する前記トレンチにおいて誘電体ライナーを形成することと、

前記誘電体ライナー上の前記トレンチにおいて下部フィールドプレートセグメントを形

成することと、

前記下部フィールドプレートセグメントの上方の前記誘電体ライナーの少なくとも一部

を除去することと、

前記下部フィールドプレートセグメントの上方の前記トレンチにおいて上部フィールド

プレートセグメントを形成することであって、前記上部フィールドプレートセグメントと

前記基板との間の誘電体材料が、前記上部フィールドプレートセグメントと前記基板との

間に前記誘電体ライナーを提供し、前記下部フィールドプレートセグメントと前記基板との

間の前記トレンチの側壁上に配置される前記誘電体ライナーが、前記上部フィールドプレ

ートセグメントと前記基板との間の前記トレンチの前記側壁上に配置される前記誘電体

ライナーより厚い、前記上部フィールドプレートセグメントを形成することと、

前記上部フィールドプレートセグメントの上方の前記トレンチから前記誘電体ライナーを除去することと、

前記上部フィールドプレートセグメントの上方の前記トレンチにおいて前記基板に接する、前記縦型MOSトランジスタのゲート誘電体層であって、前記上部フィールドプレートセグメントと前記基板との間の前記誘電体ライナーより薄い、前記ゲート誘電体層を形成することと、

前記ゲート誘電体層に接触する前記トレンチにおいて前記縦型MOSトランジスタのトレンチゲートを形成することと、

前記縦型ドリフト領域の上方の前記ゲート誘電体層に接する前記基板において前記縦型MOSトランジスタのボディを形成することと、

前記上部フィールドプレートセグメントに電気的に結合されて前記上部フィールドプレートセグメントにバイアス電圧を印加するためのフィールドプレートコンタクトを前記基板上に形成することと、

を含む、方法。

【請求項2】

請求項1に記載の方法であって、

前記トレンチにおいて誘電体ライナーを形成することが、前記基板に接する前記トレンチにおいて熱酸化物層を形成することと、前記下部フィールドプレートセグメントが第1の堆積2酸化ケイ素層上にあるように、前記トレンチにおいて前記熱酸化物層上に前記第1の堆積2酸化ケイ素層を形成することとを含む、方法。

【請求項3】

請求項2に記載の方法であって、

前記下部フィールドプレートセグメントの上方の前記誘電体ライナーの少なくとも一部を除去することが、前記下部フィールドプレートセグメントの上方の適所において前記熱酸化物層の大部分を残して、前記下部フィールドプレートセグメントの上方の前記第1の堆積2酸化ケイ素層の少なくとも一部を除去すること含み、

前記上部フィールドプレートセグメントと前記基板との間の残余熱酸化物層が、前記上部フィールドプレートセグメントと前記基板との間の前記トレンチの前記側壁上に前記誘電体ライナーの少なくとも一部を提供する、方法。

【請求項4】

請求項3に記載の方法であって、

前記基板から前記上部フィールドプレートセグメントを分離する前記トレンチの前記側壁上の前記誘電体ライナーが、第2の堆積2酸化ケイ素層を含むように、前記第1の堆積2酸化ケイ素層を除去した後で、前記上部フィールドプレートセグメントを形成する前に、前記下部フィールドプレートセグメントの上方の前記残余熱酸化物層上に前記第2の堆積2酸化ケイ素層を形成することを更に含む、方法。

【請求項5】

請求項4に記載の方法であって、

前記上部フィールドプレートセグメントが前記下部フィールドプレートセグメントに接觸するように、前記上部フィールドプレートセグメントを形成する前に、前記下部フィールドプレートセグメント上の前記第2の堆積2酸化ケイ素層を除去することを更に含む、方法。

【請求項6】

請求項4に記載の方法であって、

前記上部フィールドプレートセグメントが前記下部フィールドプレートセグメントから電気的に隔離されるように、前記上部フィールドプレートセグメントが、前記下部フィールドプレートセグメント上の前記第2の堆積2酸化ケイ素層の一部上に形成される、方法。

【請求項7】

請求項3に記載の方法であって、

10

20

30

40

50

前記下部フィールドプレートセグメントの上方の前記残余熱酸化物層が、前記基板から前記上部フィールドプレートセグメントを分離する前記トレンチの前記側壁上に前記誘電体ライナーを提供するように、前記上部フィールドプレートセグメントが、前記下部フィールドプレートセグメントの上方の前記残余熱酸化物層上に形成される、方法。

【請求項 8】

請求項1に記載の方法であって、

前記下部フィールドプレートセグメントの上方の前記誘電体ライナーの少なくとも一部を除去することが、前記下部フィールドプレートセグメントの上方の前記誘電体ライナーの実質的に全てを除去することを含み、

前記方法が、

熱酸化物層が、前記上部フィールドプレートセグメントと前記基板との間の前記トレンチの前記側壁上の前記誘電体ライナーの少なくとも一部を提供するように、前記下部フィールドプレートセグメントを形成した後に前記下部フィールドプレートセグメントの上方の前記基板に接する前記トレンチにおいて前記熱酸化物層を形成することを更に含む、方法。

【請求項 9】

請求項1に記載の方法であって、

前記上部フィールドプレートセグメントが前記下部フィールドプレートセグメントから電気的に隔離されるように、前記上部フィールドプレートセグメントが、前記下部フィールドプレートセグメント上の誘電体材料の上に形成される、方法。

【請求項 10】

請求項1に記載の方法であって、

前記トレンチゲートが前記上部フィールドプレートセグメントから電気的に隔離されるように、前記トレンチゲートが、前記上部フィールドプレートセグメント上の前記ゲート誘電体層の一部上に形成される、方法。

【請求項 11】

請求項1に記載の方法であって、

前記下部フィールドプレートセグメントを形成することが、

前記トレンチ内と前記基板の頂部表面の上とにポリシリコンの層を形成することと、

前記下部フィールドプレートセグメントを提供するように前記トレンチにおいて前記ポリシリコンの層の一部を残して、前記基板の前記頂部表面の上と前記トレンチの一部とから、前記ポリシリコンの層を除去することと、

を含む、方法。

【請求項 12】

半導体デバイスを形成する方法であって、

半導体材料を含む基板を提供することと、

前記基板において縦型MOSトランジスタのドレイン領域を形成することと、

前記ドレイン領域の上方の前記半導体材料において前記縦型MOSトランジスタの縦型ドリフト領域を形成することと、

前記縦型ドリフト領域においてトレンチを形成することと、

前記基板に接する前記トレンチにおいて誘電体ライナーを形成することと、

前記誘電体ライナー上の前記トレンチにおいて下部フィールドプレートセグメントを形成することと、

前記下部フィールドプレートセグメントの上方の前記誘電体ライナーの少なくとも一部を除去することと、

前記下部フィールドプレートセグメントの上方の前記トレンチにおいて上部フィールドプレートセグメントを形成することであって、前記上部フィールドプレートセグメントと前記基板との間の誘電体材料が、前記上部フィールドプレートセグメントと前記基板との間に前記誘電体ライナーを提供し、前記下部フィールドプレートセグメントと前記基板との間の前記トレンチの側壁上に配置される前記誘電体ライナーが、前記上部フィールドブ

10

20

30

40

50

レートセグメントと前記基板との間の前記トレンチの前記側壁上に配置される前記誘電体ライナーより厚い、前記上部フィールドプレートセグメントを形成することと、

前記上部フィールドプレートセグメントの上方の前記トレンチから前記誘電体ライナーを除去することと、

前記上部フィールドプレートセグメントの上方の前記トレンチにおいて前記基板に接する、前記縦型MOSトランジスタのゲート誘電体層であって、前記上部フィールドプレートセグメントと前記基板との間の前記誘電体ライナーより薄い、前記ゲート誘電体層を形成することと、

前記ゲート誘電体層に接触する前記トレンチにおいて前記縦型MOSトランジスタのトレンチゲートを形成することと、

前記縦型ドリフト領域の上方の前記ゲート誘電体層に接する前記基板において前記縦型MOSトランジスタのボディを形成することと、

を含み、

前記上部フィールドプレートセグメントが前記下部フィールドプレートセグメントに接觸するように、前記上部フィールドプレートセグメントを形成する前に、前記下部フィールドプレートセグメント上の誘電体材料を除去することを更に含む、方法。

【請求項13】

半導体デバイスを形成する方法であって、

半導体材料を含む基板を提供することと、

前記基板において縦型MOSトランジスタのドレイン領域を形成することと、

前記ドレイン領域の上方の前記半導体材料において前記縦型MOSトランジスタの縦型ドリフト領域を形成することと、

前記縦型ドリフト領域においてトレンチを形成することと、

前記基板に接する前記トレンチにおいて誘電体ライナーを形成することと、

前記誘電体ライナー上の前記トレンチにおいて下部フィールドプレートセグメントを形成することと、

前記下部フィールドプレートセグメントの上方の前記誘電体ライナーの少なくとも一部を除去することと、

前記下部フィールドプレートセグメントの上方の前記トレンチにおいて上部フィールドプレートセグメントを形成することであって、前記上部フィールドプレートセグメントと前記基板との間の誘電体材料が、前記上部フィールドプレートセグメントと前記基板との間に前記誘電体ライナーを提供し、前記下部フィールドプレートセグメントと前記基板との間の前記トレンチの側壁上に配置される前記誘電体ライナーが、前記上部フィールドプレートセグメントと前記基板との間の前記トレンチの前記側壁上に配置される前記誘電体ライナーより厚い、前記上部フィールドプレートセグメントを形成することと、

前記上部フィールドプレートセグメントの上方の前記トレンチから前記誘電体ライナーを除去することと、

前記上部フィールドプレートセグメントの上方の前記トレンチにおいて前記基板に接する、前記縦型MOSトランジスタのゲート誘電体層であって、前記上部フィールドプレートセグメントと前記基板との間の前記誘電体ライナーより薄い、前記ゲート誘電体層を形成することと、

前記ゲート誘電体層に接触する前記トレンチにおいて前記縦型MOSトランジスタのトレンチゲートを形成することと、

前記縦型ドリフト領域の上方の前記ゲート誘電体層に接する前記基板において前記縦型MOSトランジスタのボディを形成することと、

を含み、

前記トレンチゲートが前記上部フィールドプレートセグメントに接觸するように、前記トレンチゲートを形成する前に、前記上部フィールドプレートセグメント上の前記ゲート誘電体層を除去することを更に含む、方法。

【請求項14】

10

20

30

40

50

半導体デバイスを形成する方法であって、

半導体材料を含む基板を提供することと、

前記基板において縦型MOSトランジスタのドレイン領域を形成することと、

前記ドレイン領域の上方の前記半導体材料において前記縦型MOSトランジスタの縦型

ドリフト領域を形成することと、

前記縦型ドリフト領域においてトレンチを形成することと、

前記基板に接する前記トレンチにおいて熱酸化物層を形成することと、

前記熱酸化物層上の前記トレンチにおいて第1の堆積2酸化ケイ素層を形成することと、

、

前記トレンチにおいて前記第1の堆積2酸化ケイ素層上に下部フィールドプレートセグメントを形成することであって、前記熱酸化物層と前記第1の堆積2酸化ケイ素層との組合せが、前記基板から前記下部フィールドプレートセグメントを分離する前記トレンチの側壁上の誘電体ライナーを提供する、前記下部フィールドプレートセグメントを形成することと、

前記下部フィールドプレートセグメントの上方の適所における前記熱酸化物層の大部分を残して、前記下部フィールドプレートセグメントの上方の前記第1の堆積2酸化ケイ素層の少なくとも一部を除去することと、

前記下部フィールドプレートセグメントの上方の前記トレンチにおいて上部フィールドプレートセグメントを形成することであって、前記上部フィールドプレートセグメントと前記基板との間の残余熱酸化物層が、前記上部フィールドプレートセグメントと前記基板との間の前記トレンチの前記側壁上の前記誘電体ライナーの少なくとも一部を提供し、前記下部フィールドプレートセグメントと前記基板との間の前記トレンチの前記側壁上に配置される前記誘電体ライナーが、前記上部フィールドプレートセグメントと前記基板との間の前記トレンチの前記側壁上に配置される前記誘電体ライナーより厚い、前記上部フィールドプレートセグメントを形成することと、

前記上部フィールドプレートセグメントの上方の前記トレンチから前記熱酸化物層を除去することと、

前記上部フィールドプレートセグメントの上方の前記トレンチにおいて前記基板に接する前記縦型MOSトランジスタのゲート誘電体層を形成することであって、前記上部フィールドプレートセグメントと前記基板との間の前記トレンチの前記側壁上の前記誘電体ライナーより薄い前記ゲート誘電体層を形成することと、

前記ゲート誘電体層に接触する前記トレンチにおいて前記縦型MOSトランジスタのトレンチゲートを形成することと、

前記縦型ドリフト領域の上方の記ゲート誘電体層に接する前記基板において前記縦型MOSトランジスタのボディを形成することと、

前記上部フィールドプレートセグメントに電気的に結合されて前記上部フィールドプレートセグメントにバイアス電圧を印加するためのフィールドプレートコンタクトを前記基板上に形成することと、

を含む、方法。

【発明の詳細な説明】

40

【技術分野】

【0001】

本願は一般に半導体デバイスに関し、より詳細には、半導体デバイスにおける垂直MOSトランジスタに関する。

【背景技術】

【0002】

トレンチにおいてトレンチゲートを備える垂直金属酸化物半導体(MOS)トランジスタは、ゲート誘電体層と、ボディを超えてトレンチの下方に延在し、ボディの下の垂直ドリフト領域に接するゲートとを有する。ゲート誘電体層がドリフト領域における高い電界に対応できないので、トレンチは、所望の動作電圧に対応するため、所望されるよりも深

50

くなければならない。ゲート誘電体層の厚さが増加されると、オン状態におけるチャネル領域の抵抗が望ましくなく増加する。

【発明の概要】

【0003】

述べられる例において、半導体デバイスが、トレンチにおいてトレンチゲートを有する垂直MOSトランジスタを含む。トレンチは、垂直MOSトランジスタのボディを超えて、および、ボディの下の垂直MOSトランジスタのドリフト領域に接して、半導体デバイスの基板内へ延在する。トレンチは、ゲートの下にフィールドプレートを有する。フィールドプレートは、ドリフト領域の近隣にあり、複数のセグメントを有する。ドリフト領域からフィールドプレートを分離する、トレンチにおける誘電体ライナーが、ゲートとボディとの間のゲート誘電体層より大きな厚さを有する。誘電体ライナーは、トレンチの底部においてフィールドプレートの下部セグメント上で、ゲートの真下の上部セグメントより厚い。

10

【図面の簡単な説明】

【0004】

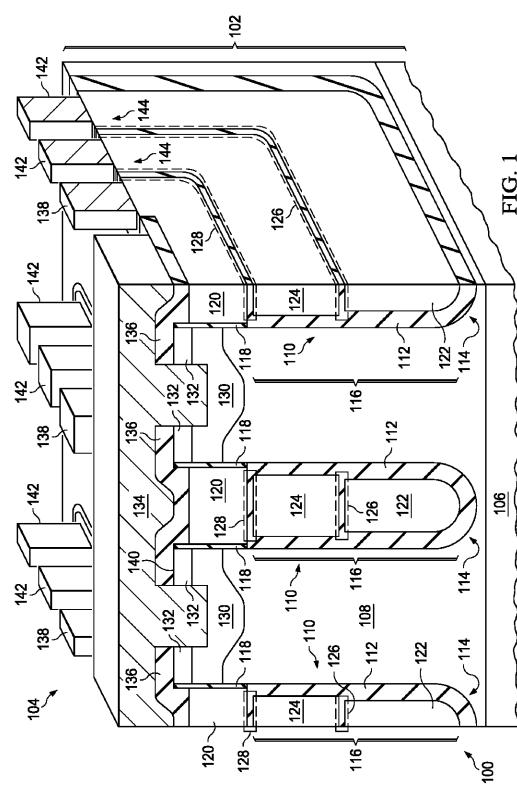

【図1】垂直nチャネルMOSトランジスタを含む例示的な半導体デバイスの断面図である。

20

【0005】

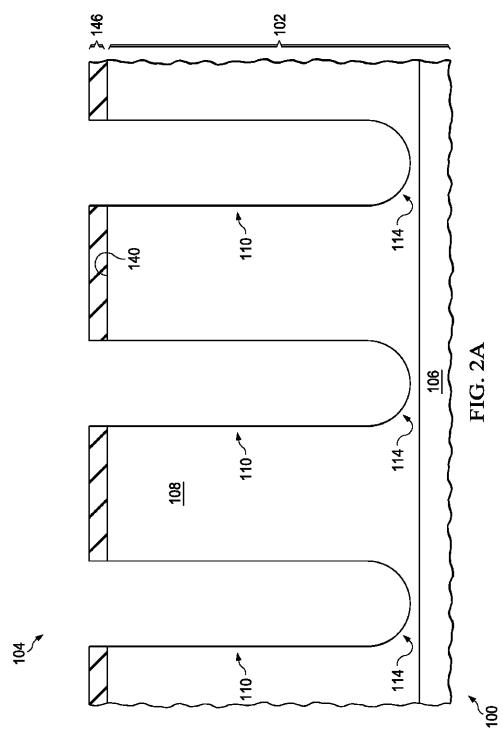

【図2A】製造の連続的な段階において描写される、図1の半導体デバイスの断面図である。

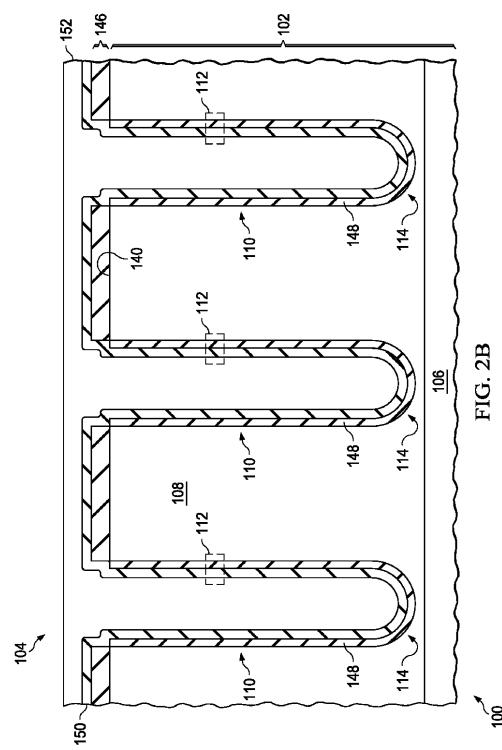

【図2B】製造の連続的な段階において描写される、図1の半導体デバイスの断面図である。

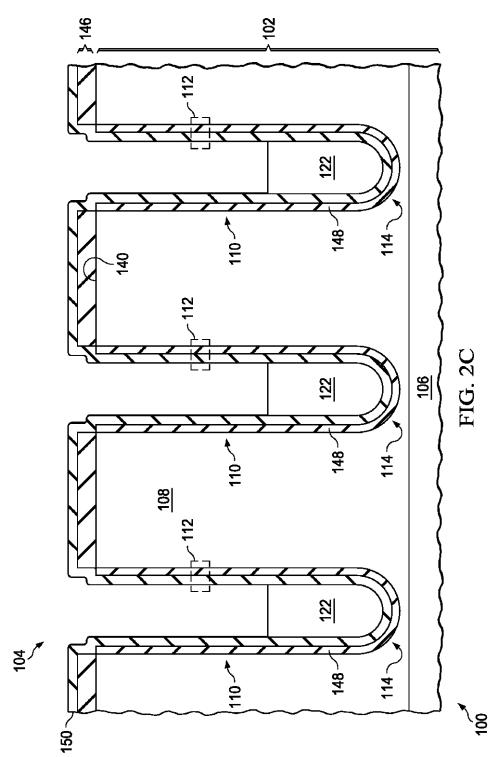

【図2C】製造の連続的な段階において描写される、図1の半導体デバイスの断面図である。

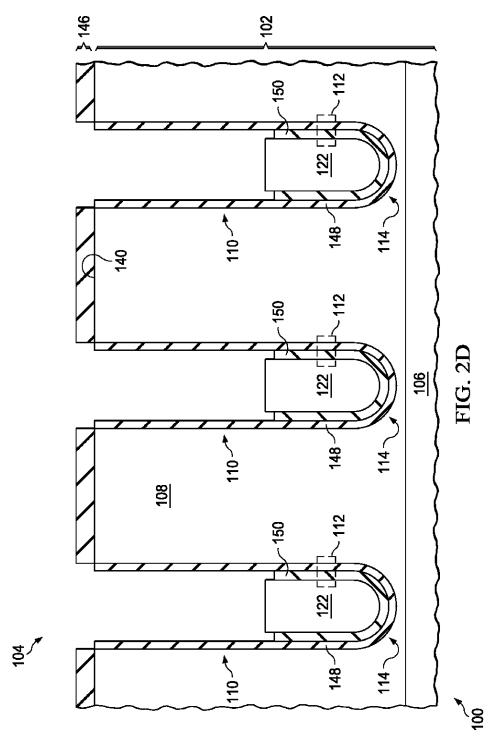

【図2D】製造の連続的な段階において描写される、図1の半導体デバイスの断面図である。

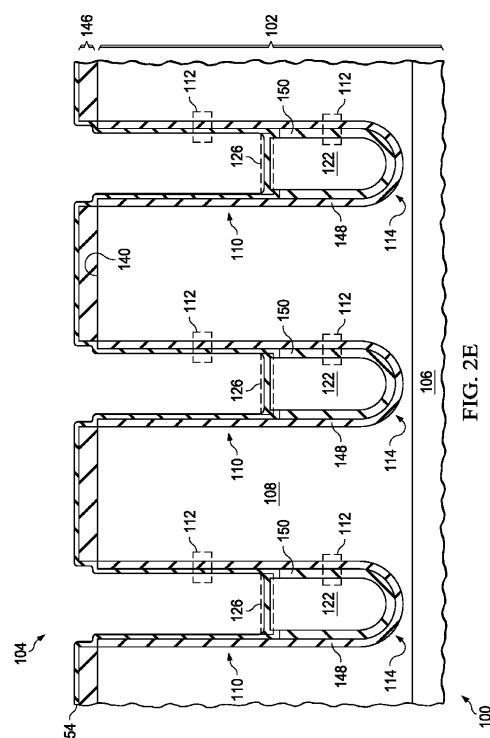

【図2E】製造の連続的な段階において描写される、図1の半導体デバイスの断面図である。

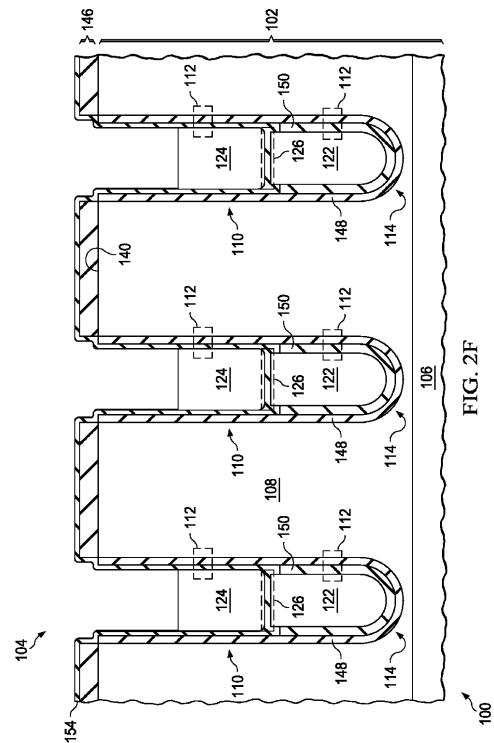

【図2F】製造の連続的な段階において描写される、図1の半導体デバイスの断面図である。

30

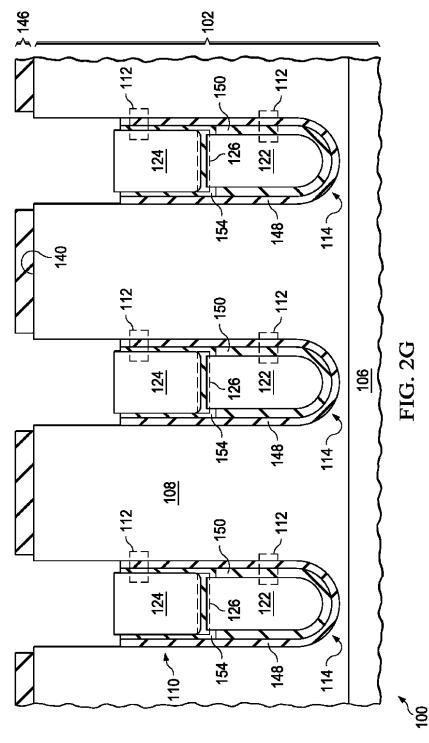

【図2G】製造の連続的な段階において描写される、図1の半導体デバイスの断面図である。

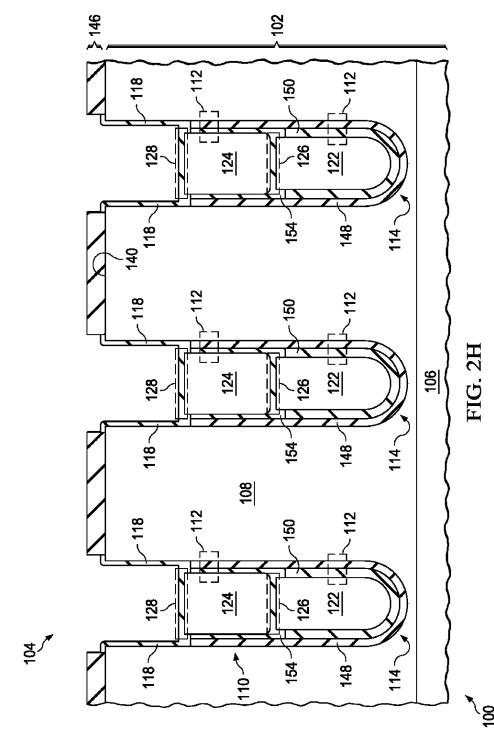

【図2H】製造の連続的な段階において描写される、図1の半導体デバイスの断面図である。

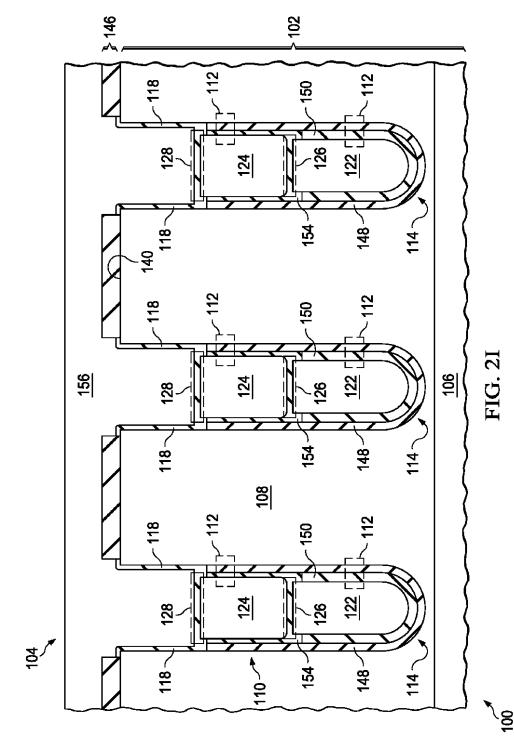

【図2I】製造の連続的な段階において描写される、図1の半導体デバイスの断面図である。

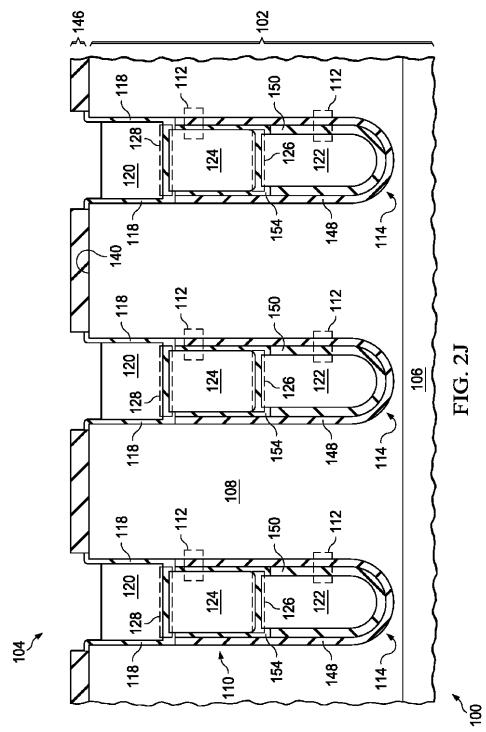

【図2J】製造の連続的な段階において描写される、図1の半導体デバイスの断面図である。

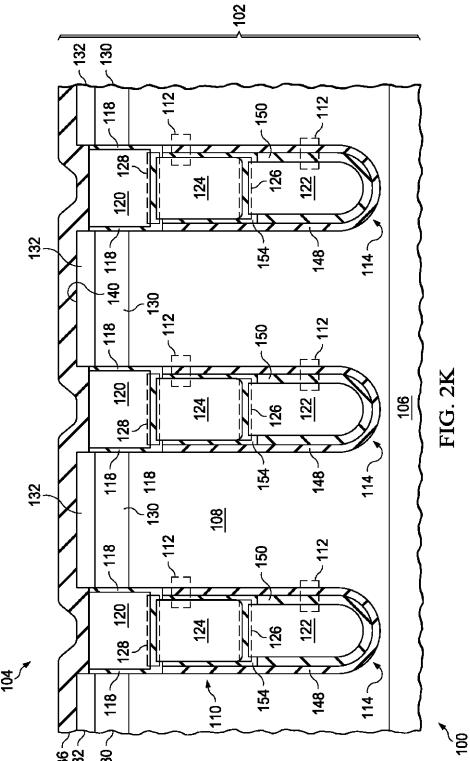

【図2K】製造の連続的な段階において描写される、図1の半導体デバイスの断面図である。

40

【0006】

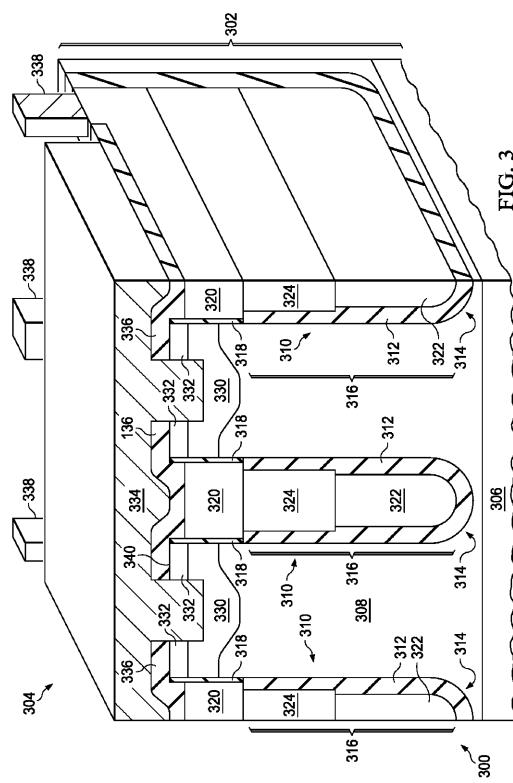

【図3】垂直nチャネルMOSトランジスタを含む別の例示的な半導体デバイスの断面図である。

【0007】

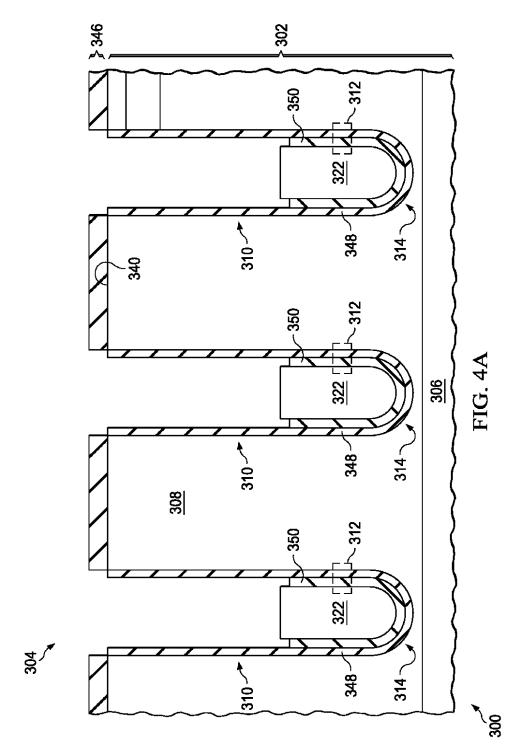

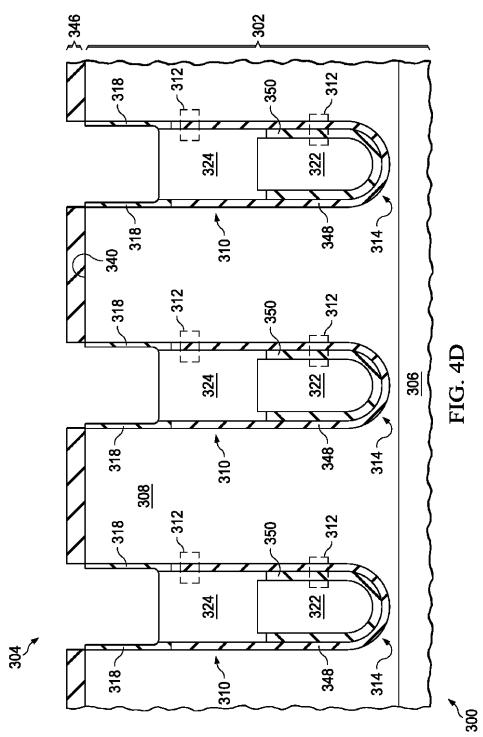

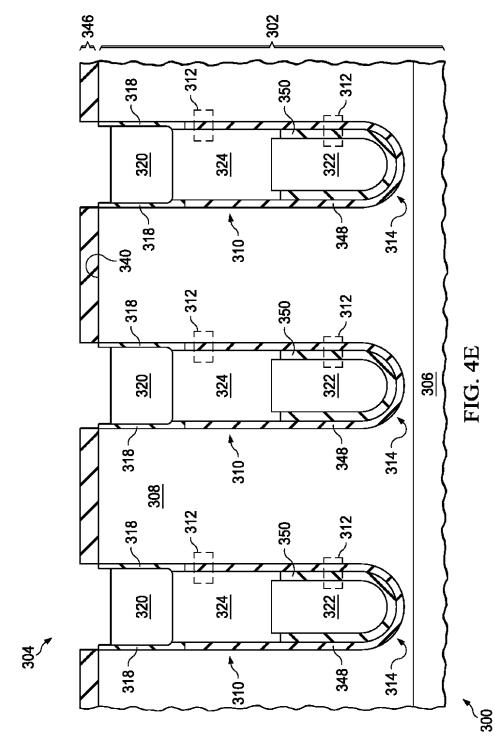

【図4A】製造の連続的な段階において描写される、図3の半導体デバイスの断面図である。

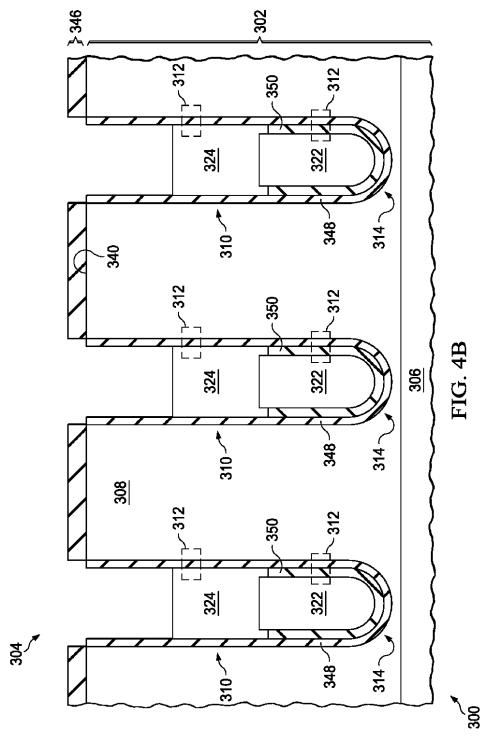

【図4B】製造の連続的な段階において描写される、図3の半導体デバイスの断面図である。

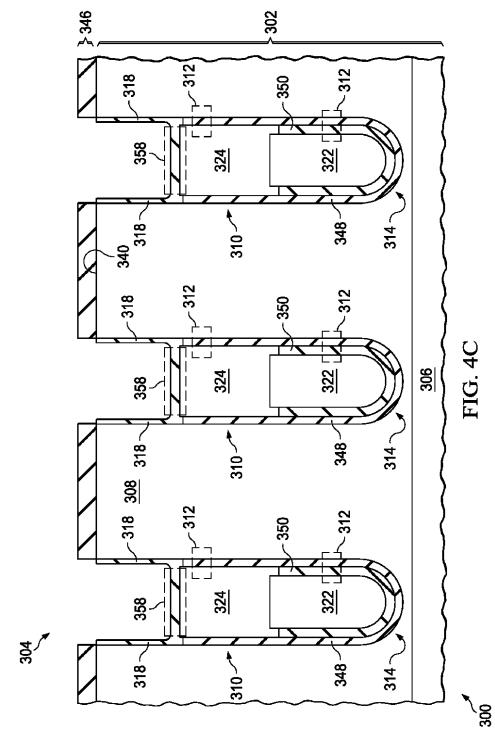

【図4C】製造の連続的な段階において描写される、図3の半導体デバイスの断面図である。

50

【図4D】製造の連続的な段階において描写される、図3の半導体デバイスの断面図である。

【図4E】製造の連続的な段階において描写される、図3の半導体デバイスの断面図である。

【0008】

【図5】垂直pチャネルMOSトランジスタを含む例示的な半導体デバイスの断面図である。

【0009】

【図6A】製造の連続的な段階において描写される、図5の半導体デバイスの断面図である。

10

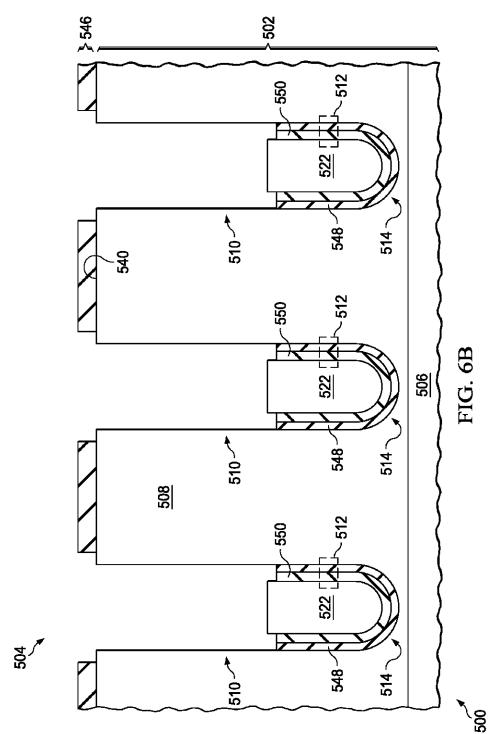

【図6B】製造の連続的な段階において描写される、図5の半導体デバイスの断面図である。

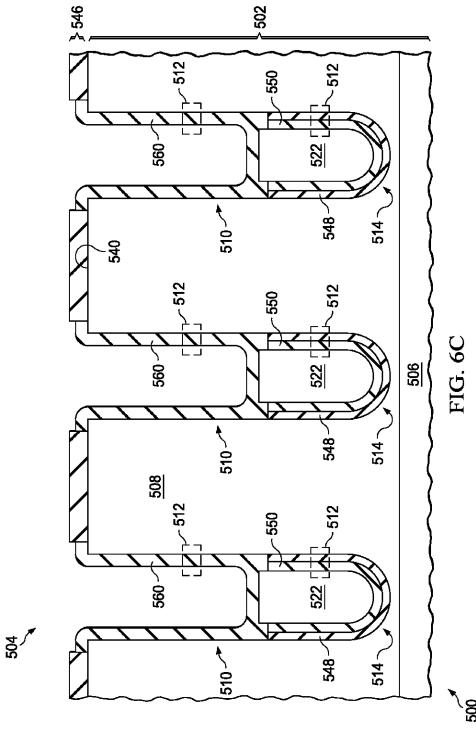

【図6C】製造の連続的な段階において描写される、図5の半導体デバイスの断面図である。

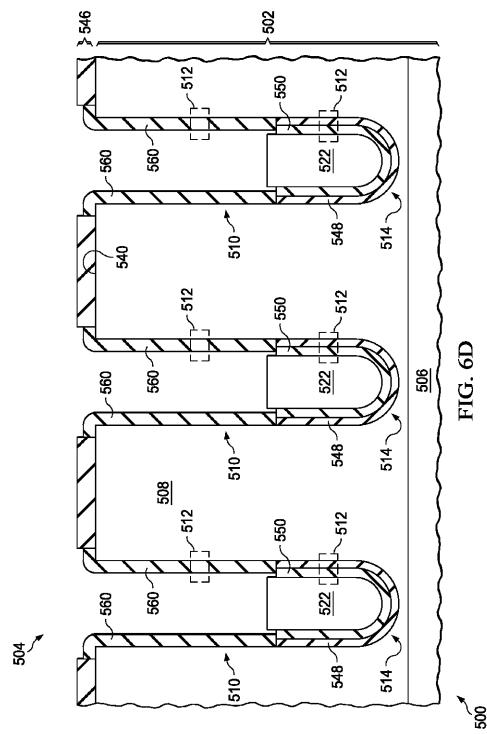

【図6D】製造の連続的な段階において描写される、図5の半導体デバイスの断面図である。

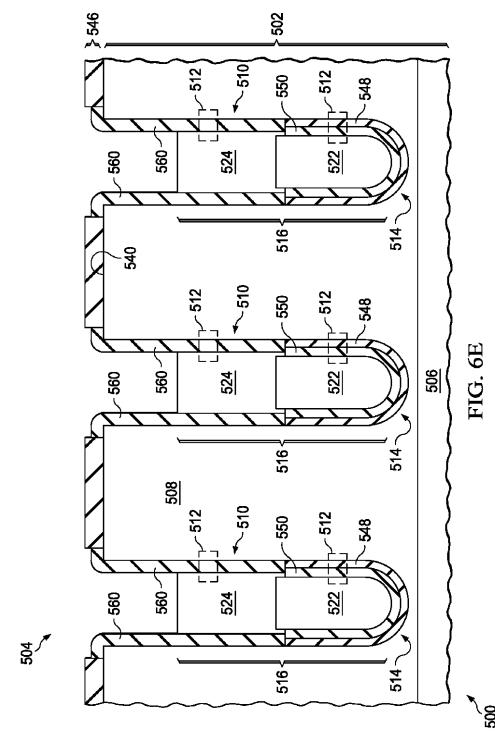

【図6E】製造の連続的な段階において描写される、図5の半導体デバイスの断面図である。

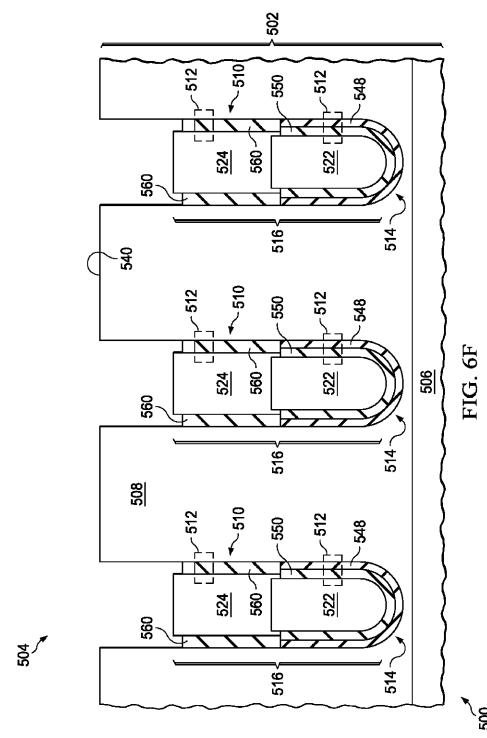

【図6F】製造の連続的な段階において描写される、図5の半導体デバイスの断面図である。

20

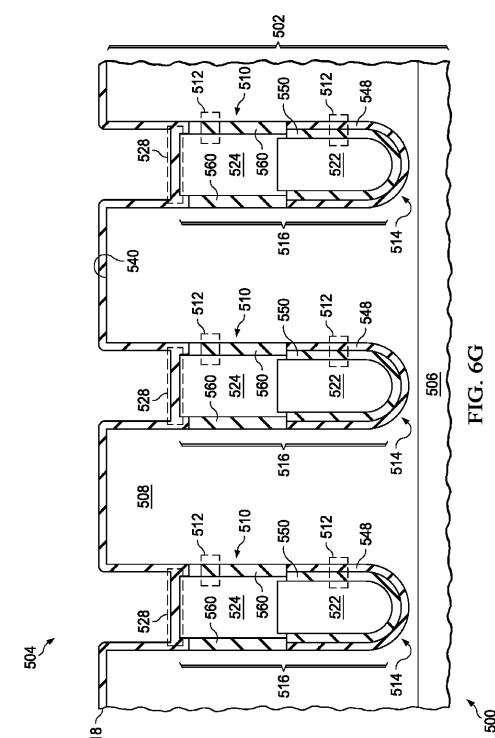

【図6G】製造の連続的な段階において描写される、図5の半導体デバイスの断面図である。

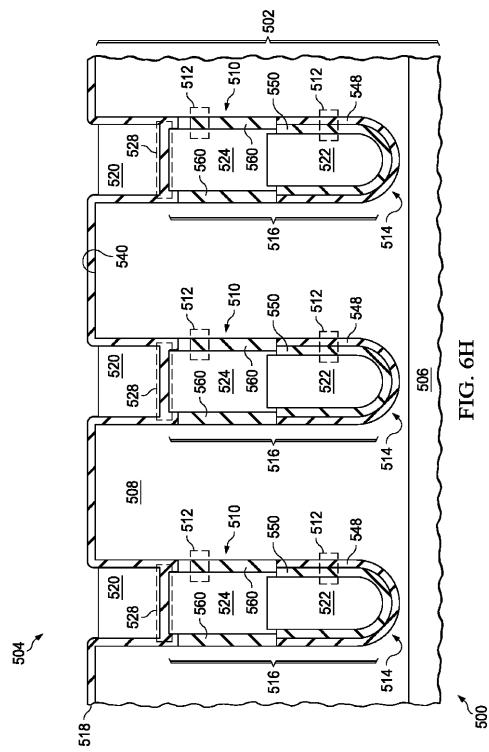

【図6H】製造の連続的な段階において描写される、図5の半導体デバイスの断面図である。

【0010】

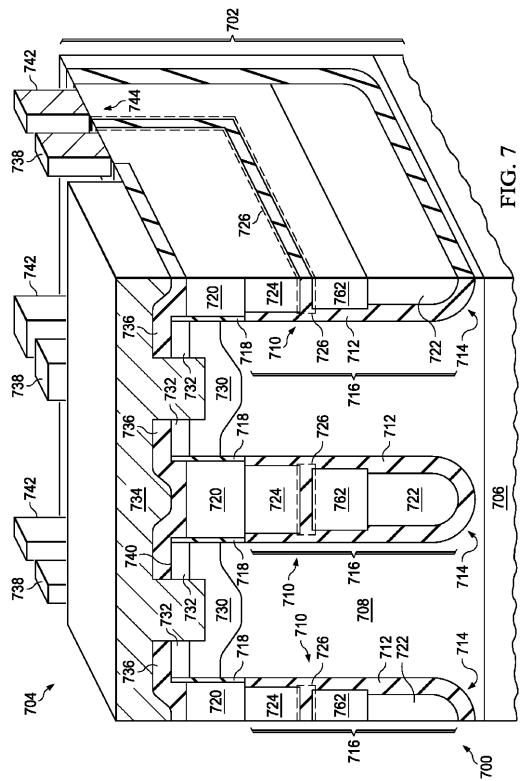

【図7】垂直nチャネルMOSトランジスタを含む別の例示的な半導体デバイスの断面図である。

【発明を実施するための形態】

【0011】

図面は一定の縮尺で描かれていらない。幾つかの行為は、異なる順序で、および／または、他の行為または事象と同時に成され得る。図示される行為または事象全てが、例示的な実施形態に従って方法論を実施するために必要とされるとは限らない。

30

【0012】

半導体デバイスが、半導体デバイスの基板内へ延在するトレンチを有する垂直MOSトランジスタを含む。垂直MOSトランジスタのドレイン領域が、トレンチの底部における、またはトレンチの底部の下の、基板に配置される。ドリフト領域が、ドレイン領域の上方およびトレンチ間の基板に配置される。垂直MOSトランジスタのボディが、ドリフト領域の上方に、および、トレンチに接して、基板に配置される。垂直MOSトランジスタのソースが、ボディの上方に配置される。垂直MOSトランジスタのゲートが、ボディの近隣のトレンチに配置され、ゲート誘電体層によってボディから分離される。複数のセグメントを備えるフィールドプレートが、ゲートの下でトレンチに配置され、トレンチの側壁上の誘電体ライナーによってドリフト領域から分離される。誘電体ライナーは、トレンチの底部における、フィールドプレートの下部セグメント上で、ゲートの真下の上部セグメントより厚い。フィールドプレートセグメントは、互いに接続され得、または、互いから電気的に絶縁され得る。上部フィールドプレートセグメントは、ゲートに接続され得、または、ゲートから電気的に絶縁され得る。垂直MOSトランジスタは、nチャネルMOSトランジスタまたはpチャネルMOSトランジスタであり得る。

40

【0013】

この説明の目的のために、「RESURF」という用語は、近隣の半導体領域における電界を減少させる材料を指す。例えば、RESURF領域は、近隣の半導体領域とは反対

50

の導電型を有する半導体領域であり得る。RESURF構造は、Appelsらの「薄層高電圧デバイス」Philips J, Res. 35 1 13, 1980において述べられる。

【非特許文献1】Appels, et al. "Thin layer High Voltage Device" Philips J, Res. 35 1 13, 1980

【0014】

図1は、垂直nチャネルMOSトランジスタを含む例示的な半導体デバイスの断面図である。半導体デバイス100は、半導体材料を含む基板102上に形成される。本明細書においてトランジスタ104と呼ばれるnチャネル垂直MOSトランジスタ104は、半導体デバイス100の唯一の能動素子であり得、または、半導体デバイス100における複数の能動デバイスの一つであり得る。トランジスタ104は、n型垂直ドリフト領域108の下の基板102において配置されるn型ドレイン領域106を含む。

【0015】

半導体デバイス100はトレンチ110を含み、トレンチ110は、図1において描寫されるように、ドレイン領域106に近接した垂直ドリフト領域108を介して垂直に、または、場合によりドレイン領域106内へ、延在する。トレンチ110は、トレンチ110の底部114まで延在し、基板102に接する、トレンチ110の側壁上の誘電体ライナー112と、誘電体ライナー112上の複数のフィールドプレートセグメント116とを含む。トレンチ110はさらに、基板102に接する誘電体ライナー112の上方のゲート誘電体層118と、ゲート誘電体層118に接触する、トランジスタ104のトレンチゲート120とを含む。この例において、フィールドプレートセグメント116は、トレンチ110の底部114におけるそれぞれの誘電体ライナー112上のそれぞれの下部フィールドプレートセグメント122と、それぞれの下部フィールドプレートセグメント122の上方に配置されるそれぞれの上部フィールドプレートセグメント124とを含む。フィールドプレートセグメント116およびトレンチゲート120は、ポリシリコンと呼ばれる、主に多結晶シリコンを含み得る。誘電体ライナー112は、主に二酸化ケイ素を含み得る。誘電体ライナー112は、下部フィールドプレートセグメント122および上部フィールドプレートセグメント124を基板102から分離する。下部フィールドプレートセグメント122と基板102との間の、トレンチ110の側壁上に配置される誘電体ライナー112は、上部フィールドプレートセグメント124と基板102との間の、トレンチ110の側壁上に配置される誘電体ライナー112より厚い。上部フィールドプレートセグメント124と基板102との間の、トレンチ110の側壁上に配置される誘電体ライナー112は、トレンチゲート120と基板102との間の、トレンチ110の側壁上に配置されるゲート誘電体層118より厚い。例えば、トランジスタ104が最大250ボルトで動作するように設計されるこの例の或るバージョンにおいて、下部フィールドプレートセグメント122と基板102との間の、トレンチ110の側壁上に配置される誘電体ライナー112は、900ナノメートル～1000ナノメートルの厚さであり得、上部フィールドプレートセグメント124と基板102との間の、トレンチ110の側壁上に配置される誘電体ライナー112は、300ナノメートル～400ナノメートルの厚さであり得る。

【0016】

この例において、下部フィールドプレートセグメント122は、下部フィールドプレートセグメント122と上部フィールドプレートセグメント124との間に配置される第1の絶縁層126によって、上部フィールドプレートセグメント124から電気的に絶縁される。また、この例において、上部フィールドプレートセグメント124は、上部フィールドプレートセグメント124とトレンチゲート120との間に配置される第2の絶縁層128によって、トレンチゲート120から電気的に絶縁される。第1の絶縁層126および第2の絶縁層128は、二酸化ケイ素などの誘電体材料を含み、誘電体ライナー112と同様の組成物を有し得る。

【0017】

10

20

30

40

50

トランジスタ 104 は、ゲート誘電体層 118 に接する、垂直ドリフト領域 108 の上方の基板 102 における p 型ボディ 130 を含む。トランジスタ 104 はさらに、ボディ 130 の上方に、ゲート誘電体層 118 に接する n 型ソース 132 を含む。トレンチゲート 120 は、垂直ドリフト領域 108 およびソース 132 と部分的に同じ広がりを持つ。ソース電極 134 が基板 102 の上に配置され、ソース 132 およびボディ 130 への電気的接続を成す。ソース電極 134 は、トレンチゲート 120 の上の誘電体キャップ層 136 によってトレンチゲート 120 から電気的に絶縁される。

#### 【0018】

トランジスタ 104 が最大 250 ボルトで動作するように設計されるこの例の或るバージョンにおいて、トレンチ 110 は、13 ミクロン～17 ミクロンの深さ、および 2.5 ミクロン～2.8 ミクロンの幅であり得る。垂直ドリフト領域 108、すなわち、近隣トレンチ 110 間は、0.5 ミクロン～3 ミクロンの幅であり得、 $1.4 \times 10^{-16} \text{ cm}^{-3} \sim 1.6 \times 10^{-16} \text{ cm}^{-3}$  の平均ドーピング密度を有し得る。

10

#### 【0019】

トレンチゲート 120 への電気接続は、基板 102 の頂部表面 140 におけるゲートの露出されたエリア上のゲートコンタクト 138 を介して成され得る。フィールドプレートセグメント 116 への電気接続は、フィールドプレートセグメント 116 から最大で基板 102 の頂部表面 140 まで延在するフィールドプレートライザ 144 上のフィールドプレートコンタクト 142 を介して成され得る。フィールドプレートセグメント 116 への電気接続を成すためのその他の構造もこの例の範囲内にある。

20

#### 【0020】

半導体デバイス 100 の動作の間、トレンチ 110 に配置されるトレンチゲート 120 は、有利に、平坦なゲートを備える同様の垂直MOSトランジスタと比較して、トランジスタ 104 によって占有される頂部表面 140 のエリアにおいて一層高いオン状態電流を提供する。上部フィールドプレートセグメント 124 および下部フィールドプレートセグメント 122 の組合せが、単一のフィールドプレートを備える同様の垂直MOSトランジスタと比較して、垂直ドリフト領域 108 における一層高いドーピング密度で、垂直ドリフト領域 108 における電界を所望の値に維持するように RESURF 構成を提供する。従って、上部フィールドプレートセグメント 124 および下部フィールドプレートセグメント 122 の組合せを備える垂直MOSトランジスタ 104 を形成することによって、トランジスタ 104 は、単一のフィールドプレートを備える同様の垂直MOSトランジスタより浅いトレンチ 110 を有することが可能とされ、有利に半導体デバイス 100 の製造コストを削減する。互いから電気的に絶縁される下部フィールドプレートセグメント 122、上部フィールドプレートセグメント 124、および、トレンチゲート 120 を形成することは、有利に、トランジスタ 104 における電流密度を増加させるために、下部フィールドプレートセグメント 122 および上部フィールドプレートセグメント 124 を独立してバイアスすることを可能にし得る。

30

#### 【0021】

図 2A～図 2K は、製造の連続的な段階において描写される、図 1 の半導体デバイスの断面図である。図 2A を参照すると、半導体デバイス 100 は、頂部表面 140 まで延在するエピタキシャル層を備えるバルクシリコンウエハまたはシリコンウエハなどの基板 102 上に形成される。基板 102 におけるその他の半導体材料もこの例の範囲内にある。ドレイン領域 106 は、 $1 \times 10^{-2} \text{ cm}^{-3}$  より高いドーピング密度を有するように基板 102 において形成される。例えば、ドレイン領域 106 は、アンチモンや、場合によりヒ素などの n 型ドーパントを基板 102 に注入することによって形成され得、その後、注入された n 型ドーパントの上の n 型半導体材料のアニールおよびエピタキシャル成長が続き、その結果、エピタキシャル層は、垂直ドリフト領域 108 を提供する。垂直ドリフト領域 108 におけるリンなどの N 型ドーパントが、エピタキシャル成長の間に混合され得、または、後に注入され得、その後、注入されたドーパントを拡散および活性化させるため熱駆動が続く。

40

50

## 【0022】

基板102の上にハードマスク146が形成され、ハードマスク146はトレント110のためのエリアを露出させる。ハードマスク146は、数百ナノメートルの二酸化ケイ素であり得、フォトレジストマスクを介してエッチングすることによりパターニングされ得る。トレント110は、ハードマスク146によって露出されたエリアにおける基板102から材料を除去することによって形成される。この材料は、トレント110の所望の深さを得るため、時限の反応性イオンエッチング(RIE)プロセスによって基板102から除去され得る。

## 【0023】

図2Bを参照すると、図1の下部フィールドプレートセグメント122に接する誘電体ライナー112は、熱酸化物層148および第1の堆積二酸化ケイ素層150の組合せ層として形成され得る。熱酸化物層148は、トレント110の側壁および底部114に形成される。熱酸化物層148は、50ナノメートル～200ナノメートルの厚さであり得る。第1の堆積二酸化ケイ素層150は、熱酸化物層148上に形成される。第1の堆積二酸化ケイ素層150は、200ナノメートル～400ナノメートルの厚さであり得、ジクロロシランおよび酸素を用いる準大気圧化学気相成長(SACVD)プロセスによって形成され得る。或いは、第1の堆積二酸化ケイ素層150は、テトラエトキシシランまたはTEOSとしても知られる、テトラエチルオルソシリケートを用いるプラズマエンハンスト化学気相成長(PECVD)プロセスによって形成され得る。第1の堆積二酸化ケイ素層150は、アニール工程においてその後高密度化され得る。誘電体ライナー112のためのその他の層構造およびその他のプロセスも、この例の範囲内にある。

## 【0024】

第1のポリシリコン層152が、誘電体ライナー112上に、基板102の頂部表面140の上に延在して形成される。例えば、第1のポリシリコン層152は、頂部表面140の上で500ナノメートル～700ナノメートルの厚さであり得る。また、例えば、第1のポリシリコン層152は、 $1 \times 10^{18} \text{ cm}^{-3} \sim 5 \times 10^{18} \text{ cm}^{-3}$ の平均ドーピング密度を有するための形成の間、リンでドープされ得る。或いは、第1のポリシリコン層152は、 $1 \times 10^{14} \text{ cm}^{-2} \sim 5 \times 10^{15} \text{ cm}^{-2}$ のドーズ量で、リンなどのイオン注入ドーパントによってドープされ、その後、10分～60分間900～1000でアニールされ得る。

## 【0025】

図2Cを参照すると、プランケットエッチバックプロセスが、下部フィールドプレートセグメント122を形成するためにトレント110の下部部分におけるポリシリコンを残して、頂部表面140の上およびトレント110における図2Bの第1のポリシリコン層152からポリシリコンを除去する。例えば、プランケットエッチバックは、フッ素ラジカルを含む時限のプラズマエッチング、および/または、コリン、水酸化アンモニウム、もしくは、水酸化テトラメチルアンモニウムを用いる時限のウェットエッチングを用いて実施され得る。プランケットエッチバックは、一つまたは複数のエッチング工程において実施され得る。この例の一つのバージョンにおいて、プランケットエッチバックは、著しい量の誘電体ライナー112を除去しない。

## 【0026】

図2Dを参照すると、第1のプランケット酸化物エッチバックプロセスが、第1の堆積二酸化ケイ素層150の少なくとも一部および場合により全部を、基板102の頂部表面140の上から、および、下部フィールドプレートセグメント122の上方のトレント110から除去する。下部フィールドプレートセグメント122は、下部フィールドプレートセグメント122の頂部より下のトレント110からの、第1の堆積二酸化ケイ素層150の除去を防止する。第1のプランケット酸化物エッチバックプロセスが完了した後、熱酸化物層148の大部分および場合により全てがトレント110の側壁上に残る。例えば、第1のプランケット酸化物エッチバックプロセスは、緩衝フッ酸溶液を用いる時限のウェットエッチングを含み得る。例示的な緩衝フッ酸溶液は、脱イオン水において10倍

10

20

30

40

50

の40パーセントフッ化アンモニウム、および、脱イオン水において1倍の49パーセントフッ化水素酸であり、この緩衝フッ化水素酸は、熱酸化物のエッティングレートの2倍以上である、高密度化されたSACVD二酸化ケイ素のエッティングレートを示す。

【0027】

図2Eを参照すると、第2の堆積二酸化ケイ素層154が、トレンチ110における熱酸化物層148の上、および下部フィールドプレートセグメント122の上に形成される。例えば、第2の堆積二酸化ケイ素層154は、160ナノメートル～280ナノメートルの厚さであり得、SACVDプロセスまたはPECVDプロセスによって形成され得る。第2の堆積二酸化ケイ素層154は、その後、アニール工程において高密度化され得る。熱酸化物層148と組み合わされた第2の堆積二酸化ケイ素層154は、図1の上部フィールドプレートセグメント124に接する誘電体ライナー112を提供する。下部フィールドプレートセグメント122上の第2の堆積二酸化ケイ素層154の一部が、第1の絶縁層126を提供する。

【0028】

図2Fを参照すると、第2のポリシリコン層が、図2Bに関連して述べたように、トレンチ110における誘電体ライナー112上および基板102の頂部表面140の上に形成される。その後のエッチバックプロセスが、上部フィールドプレートセグメント124を形成するための第2の堆積二酸化ケイ素層154上のポリシリコンを残して、頂部表面140の上から、および、トレンチ110の頂部部分からポリシリコンを除去する。エッチバックプロセスは、図2Cに関連して述べたように、时限のプラズマエッティングおよび/または时限のウェットエッティングであり得る。この例において、上部フィールドプレートセグメント124は、第2の堆積二酸化ケイ素層154によって、下部フィールドプレートセグメント122から電気的に絶縁される。

【0029】

図2Gを参照すると、第2のプランケット酸化物エッチバックプロセスが、基板102の頂部表面140の上から、および、上部フィールドプレートセグメント124の上方のトレンチ110から、第2の堆積二酸化ケイ素層154および熱酸化物層148を除去する。上部フィールドプレートセグメント124は、上部フィールドプレートセグメント124の頂部より下のトレンチ110からの、第2の堆積二酸化ケイ素層154の除去を防止する。ハードマスク146の一部が、図2Gにおいて描写されるように、第2のプランケット酸化物エッチバックプロセスによって除去され得る。第2のプランケット酸化物エッチバックプロセスは、半導体材料が基板102から実質的に除去されないように実施され得る。

【0030】

図2Hを参照すると、ゲート誘電体層118は、上部フィールドプレートセグメント124の上方のトレンチ110の側壁上に形成され、同時に、第2の絶縁層128は、上部フィールドプレートセグメント124上に形成される。ゲート誘電体層118および第2の絶縁層128は、熱酸化、または、熱酸化および誘電体材料の堆積の組合せによって形成され得る。トレンチ110の側壁を露出させるように熱酸化物層148を除去することは、ゲート誘電体層118の厚さのプロセス制御を有利に改善する。

【0031】

図2Iを参照すると、ポリシリコン156の第3の層が、ゲート誘電体層118に接触して、および、基板102の頂部表面140の上に形成される。ポリシリコン156の第3の層は、形成の間、n型ドーパントでドープされ得、または、その後、n型ドーパントが注入され得、その後、アニールが続き得る。

【0032】

図2Jを参照すると、トランジスタ104のトレンチゲート120を形成するため、ポリシリコンをゲート誘電体層118に接触したままにするように、プランケットエッチバックプロセスが、基板102の頂部表面140の上から、図2Iのポリシリコン156の第3の層からのポリシリコンを除去する。この例において、トレンチゲート120は、第

2の絶縁層128によって上部フィールドプレートセグメント124から電気的に絶縁される。

【0033】

図2Kを参照すると、ボディ130は、垂直ドリフト領域108の上方の基板102内へ、ホウ素などのp型ドーパントを注入することによって形成される。トレンチゲート120は、トレンチゲート120を逆ドープするのを防止するために、p型ドーパントが注入される間インプラントマスクによって任意選択で覆われ得る。ソース132は、ボディ130の上方の基板102に、リンやヒ素などのn型ドーパントを注入することによって形成される。基板102はその後、注入されたドーパントを活性化するためにアニールされる。ボディ130およびソース132は、近隣トレンチ110間の基板102にわたって延在する。ボディ130およびソース132が形成された後、キャップ層136は、二酸化ケイ素および任意選択で窒化ケイ素の副層の堆積によって形成される。キャップ層136は、TEOSを用いるPECVDプロセスによって形成され得る。キャップ層136が形成された後、ソースコントラクト開口が、キャップ層136を介しておよびソース132を介して、ボディ130内へ形成される。付加的なp型ドーパントが、ソースコントラクト開口によって露出された箇所におけるボディ130内に注入され得、図1において描写されたボディにおける下向きの隆起を提供する。図1のソース電極134はその後形成され、さらなる製造が図1の構造を提供する。

【0034】

図3は、垂直nチャネルMOSトランジスタを含む別の例示的な半導体デバイスの断面図である。半導体デバイス300は基板302上に形成され、基板302は半導体材料を含む。本明細書においてトランジスタ304と呼ばれる、nチャネル垂直MOSトランジスタ304は、n型垂直ドリフト領域308の下方の基板302において配置されるn型ドレイン領域306を含む。

【0035】

半導体デバイス300はトレンチ310を含み、トレンチ310は、ドレイン領域306に近接する垂直ドリフト領域308を介して垂直に、または、場合によりドレイン領域306内へ延在する。トレンチ310は、トレンチ310の底部314まで延在し、基板302に接する、誘電体ライナー312と、誘電体ライナー312上の複数のフィールドプレートセグメント316とを含む。トレンチ310はさらに、基板302に接する誘電体ライナー312の上方のゲート誘電体層318と、ゲート誘電体層318に接触する、トランジスタ304のトレンチゲート320とを含む。この例において、フィールドプレートセグメント316は、トレンチ310の底部314におけるそれぞれの誘電体ライナー312上のそれらの下部フィールドプレートセグメント322と、それぞれの下部フィールドプレートセグメント322の上方に配置されるそれぞれの上部フィールドプレートセグメント324とを含む。フィールドプレートセグメント316およびトレンチゲート320は、主にn型ポリシリコンを含み得る。誘電体ライナー312は、主に二酸化ケイ素を含み得る。誘電体ライナー312は、下部フィールドプレートセグメント322および上部フィールドプレートセグメント324を基板302から分離する。基板302から下部フィールドプレートセグメント322を分離する誘電体ライナー312は、基板302から上部フィールドプレートセグメント324を分離する誘電体ライナー312より厚い。上部フィールドプレートセグメント324と基板302との間の、トレンチの側壁310上に配置される誘電体ライナー312は、トレンチゲート320と基板302との間の、トレンチ310の側壁上に配置されるゲート誘電体層318より厚い。例えば、トランジスタ304が最大40ボルトで動作するように設計されるこの例の或るバージョンにおいて、下部フィールドプレートセグメント322と基板302との間の、トレンチ310の側壁上に配置される誘電体ライナー312は、100ナノメートル～150ナノメートルの厚さであり得、上部フィールドプレートセグメント324と基板302との間の、トレンチ310の側壁上に配置される誘電体ライナー312は、50ナノメートル～80ナノメートルの厚さであり得る。

10

20

30

40

50

## 【0036】

この例において、下部フィールドプレートセグメント322は、トレンチ310において上部フィールドプレートセグメント324に接触している。上部フィールドプレートセグメント324は、トレンチ310においてトレンチゲート320に接触している。また、この例においてトレンチゲート320に印加されるバイアス電圧が、上部フィールドプレートセグメント324および下部フィールドプレートセグメント322と同じバイアス電圧にバイアスする。

## 【0037】

トランジスタ304は、ゲート誘電体層318に接する、垂直ドリフト領域308の上方の基板302におけるp型ボディ330を含む。トランジスタ304はさらに、ボディ330の上方に、および、ゲート誘電体層318に接する、n型ソース332を含む。トレンチゲート320は、垂直ドリフト領域308およびソース332と部分的に同じ広がりを持つ。ソース電極334が基板302の上に配置され、ソース332およびボディ330への電気的接続を成す。ソース電極334は、トレンチゲート320の上の誘電体キャップ層336によってトレンチゲート320から電気的に絶縁される。ソース332およびボディ330に関するソース電極334のその他の構成も、この例の範囲内にある。

10

## 【0038】

トランジスタ304が最大40ボルトで動作するように設計されるこの例の一つのバージョンにおいて、トレンチ310は、2.2ミクロン～2.8ミクロンの深さ、および、600ナノメートル～700ナノメートルの幅であり得る。垂直ドリフト領域308、すなわち、近隣トレンチ310間は、500ナノメートル～1.5ミクロンの幅であり得、 $1.8 \times 10^{16} \text{ cm}^{-3} \sim 2.0 \times 10^{16} \text{ cm}^{-3}$ の平均ドーピング密度を有し得る。

20

## 【0039】

トレンチゲート320への電気接続は、基板302の頂部表面340におけるゲートの露出されたエリア上でゲートコンタクト338を介して成され得る。トレンチゲート320に電気接続するためのその他の構造も、この例の範囲内にある。上部フィールドプレートセグメント324および下部フィールドプレートセグメント322への電気接続が、ゲートコンタクト338を介して成され得るように、トレンチ310においてトレンチゲート320に接触するように上部フィールドプレートセグメント324を形成すること、および、トレンチ310において上部フィールドプレートセグメント324に接触するように下部フィールドプレートセグメント322を形成することが、有利に、半導体デバイス300の複雑さおよび製造コストを削減し得る。

30

## 【0040】

半導体デバイス300の動作の間、トレンチゲート320は、有利に、図1に関連して説明したような一層高い電流密度を提供する。フィールドプレートセグメント316は、図1に関連して説明したように、垂直ドリフト領域308における電界を所望の値に維持するようにRESURF構成を提供する。従って、上部フィールドプレートセグメント324および下部フィールドプレートセグメント322の組合せを備える垂直MOSトランジスタ304を形成することによって、トランジスタ304は、単一のフィールドプレートを備える同様の垂直MOSトランジスタより浅いトレンチ310を有することが可能となり、有利に、半導体デバイス300の製造コストを削減する。

40

## 【0041】

図4A～図4Eは、製造の連続的な段階において描写される、図3の半導体デバイスの断面図である。図4Aを参照すると、半導体デバイス300は、基板302上に形成される。ドレイン領域306は、 $1 \times 10^{20} \text{ cm}^{-3}$ より高いドーピング密度を有するように、基板302において形成される。垂直ドリフト領域308におけるリンなどのN型ドーパントは、エピタキシャル成長の間に混合され得、または、後に注入され得る。ハードマスク346が基板302の上に形成され、ハードマスク346はトレンチ310のためのエリアを露出させる。トレンチ310は、ハードマスク346により露出されたエリア

50

における基板 302 から材料を除去することによって形成される。ドレイン領域 306、ハードマスク 346、および、トレンチ 310 は、図 2A に関連して述べたように形成され得る。

【0042】

熱酸化物層 348 が、トレンチ 310 の側壁および底部 314 に形成される。この例において、熱酸化物層 348 は、図 3 の上部フィールドプレートセグメント 324 と基板 302 との間の、トレンチ 310 の側壁上に配置される完全な誘電体ライナー 312 を提供するように、40 ボルトの動作電圧のための 70 ナノメートル～80 ナノメートルの厚さなど、十分な厚さである。堆積二酸化ケイ素層 350 が、熱酸化物層 348 上に形成される。堆積二酸化ケイ素層 350 は、130 ナノメートル～170 ナノメートルの厚さであり得、SACVD プロセスまたはPECVD プロセスによって形成され得る。

10

【0043】

下部フィールドプレートセグメント 322 が、図 2B および図 2C に関連して述べたように、堆積二酸化ケイ素層 350 上のトレンチ 310 に形成される。堆積二酸化ケイ素層 350 と組み合わされた熱酸化物層 348 は、下部フィールドプレートセグメント 322 を基板 302 から分離する誘電体ライナー 312 を提供する。

【0044】

第 1 のプランケット酸化物エッチバックプロセスが、下部フィールドプレートセグメント 322 の上方のトレンチ 310 から、堆積二酸化ケイ素層 350 の少なくとも一部および場合により全てを除去する。下部フィールドプレートセグメント 322 は、下部フィールドプレートセグメント 322 の頂部より下のトレンチ 310 からの、堆積二酸化ケイ素層 350 の除去を防止する。この例において、第 1 のプランケット酸化物エッチバックプロセスが完了した後、熱酸化物層 348 の実質的に全てが、トレンチ 310 の側壁上に残る。第 1 のプランケット酸化物エッチバックプロセスは、下部フィールドプレートセグメント 322 の頂部を露出させる。

20

【0045】

図 4B を参照すると、上部フィールドプレートセグメント 324 が、図 2F に関連して述べたように、熱酸化物層 348 上、およびトレンチ 310 における下部フィールドプレートセグメント 322 上に形成される。この例において、熱酸化物層 348 は、基板 302 から上部フィールドプレートセグメント 324 を分離する誘電体ライナー 312 を提供し、これは、有利に、半導体デバイス 300 の製造の複雑性およびコストを削減する。

30

【0046】

図 4C を参照すると、第 2 のプランケット酸化物エッチバックプロセスが、上部フィールドプレートセグメント 324 の上方のトレンチ 310 から熱酸化物層 348 を除去する。上部フィールドプレートセグメント 324 は、上部フィールドプレートセグメント 324 頂部より下のトレンチ 310 からの、熱酸化物層 348 の除去を防止する。第 2 のプランケット酸化物エッチバックプロセスは、実質的に半導体材料が基板 302 から除去されないように実施され得る。

【0047】

ゲート誘電体層 318 は、上部フィールドプレートセグメント 324 の上方のトレンチ 310 の側壁上に形成され、誘電体材料 358 が、同時に、上部フィールドプレートセグメント 324 上に形成される。ゲート誘電体層 318 は、熱酸化、または、熱酸化および誘電体材料の堆積の組合せによって形成され得る。トレンチ 310 の側壁を露出させるために熱酸化物層 348 を除去することは、ゲート誘電体層 318 の厚さのプロセス制御を有利に改善する。上部フィールドプレートセグメント 324 上の誘電体材料 358 は、結晶シリコンと比較した、ポリシリコン上の一層高い熱酸化成長率に起因して、ゲート誘電体層 318 より厚くし得る。

40

【0048】

図 4D を参照すると、RIE プロセスなどの異方性エッティングプロセスが、ゲート誘電体層 318 を著しく劣化させることなく、上部フィールドプレートセグメント 324 の頂

50

部から、図 4 C の誘電体材料 358 を除去する。この例の一つのバージョンにおいて、ゲート誘電体層 318 は、ポリシリコンまたは窒化ケイ素の犠牲層によって保護され得、他方、誘電体材料 358 が除去された後、犠牲層は、ゲート誘電体層 318 を著しく劣化させることなく除去される。

【0049】

図 4 E を参照すると、トレンチゲート 320 は、ゲート誘電体層 318 および上部フィールドプレートセグメント 324 に接触して形成される。トレンチゲート 320 は、図 2 I および図 2 J に関連して述べたように形成され得る。この例において、上部フィールドプレートセグメント 324 の頂部から、図 4 C の誘電体材料 358 を除去することにより、トレンチゲート 320 が、上部フィールドプレートセグメント 324 との電気的接続を成すことが可能となる。さらなる製造が図 3 の構造を提供する。 10

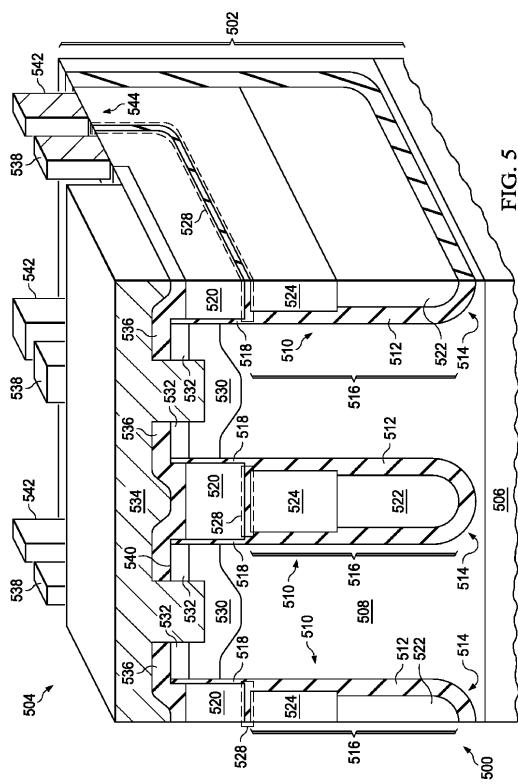

【0050】

図 5 は、垂直 p チャネル MOS トランジスタを含む例示的な半導体デバイスの断面図である。半導体デバイス 500 は基板 502 上に形成され、基板 502 は半導体材料を含む。本明細書においてトランジスタ 504 と呼ばれる p チャネル垂直 MOS トランジスタ 504 は、p 型垂直ドリフト領域 508 の下方の基板 502 において配置される p 型ドレイン領域 506 を含む。

【0051】

半導体デバイス 500 はトレンチ 510 を含み、トレンチ 510 は、ドレイン領域 506 に近接する垂直ドリフト領域 508 を介して垂直に、または、場合によりドレイン領域 506 内へ延在する。トレンチ 510 は、トレンチ 510 の底部 514 まで延在し、基板 502 に接する、誘電体ライナー 512 と、誘電体ライナー 512 上の複数のフィールドプレートセグメント 516 とを含む。トレンチ 510 はさらに、基板 502 に接する誘電体ライナー 512 の上方のゲート誘電体層 518 と、ゲート誘電体層 518 に接触する、トランジスタ 504 のトレンチゲート 520 とを含む。この例において、フィールドプレートセグメント 516 は、トレンチ 510 の底部 514 におけるそれぞれの誘電体ライナー 512 上のそれぞれの下部フィールドプレートセグメント 522 と、それぞれの下部フィールドプレートセグメント 522 の上方に配置されるそれぞれの上部フィールドプレートセグメント 524 とを含む。フィールドプレートセグメント 516 およびトレンチゲート 520 は、主に p 型ポリシリコンを含み得る。誘電体ライナー 512 は、主に二酸化ケイ素を含み得る。誘電体ライナー 512 は、下部フィールドプレートセグメント 522 および上部フィールドプレートセグメント 524 を基板 502 から分離する。下部フィールドプレートセグメント 522 を基板 502 から分離する誘電体ライナー 512 は、上部フィールドプレートセグメント 524 を基板 502 から分離する誘電体ライナー 512 より厚い。上部フィールドプレートセグメント 524 と基板 502 との間の、トレンチ 510 の側壁上に配置される誘電体ライナー 512 は、トレンチゲート 520 と基板 502 との間の、トレンチ 510 の側壁上に配置されるゲート誘電体層 518 より厚い。例えば、トランジスタ 504 が最大 100 ボルトで動作するように設計されるこの例の或るバージョンにおいて、下部フィールドプレートセグメント 522 と基板 502 との間の、トレンチ 510 の側壁上に配置される誘電体ライナー 512 は、400 ナノメートル～500 ナノメートルの厚さであり得、上部フィールドプレートセグメント 524 と基板 502 との間の、トレンチ 510 の側壁上に配置される誘電体ライナー 512 は、150 ナノメートル～200 ナノメートルの厚さであり得る。 30 40

【0052】

この例において、下部フィールドプレートセグメント 522 は、トレンチ 510 において上部フィールドプレートセグメント 524 に接触している。上部フィールドプレートセグメント 524 は、上部フィールドプレートセグメント 524 とトレンチゲート 520 との間に配置される絶縁層 528 によってトレンチゲート 520 から絶縁される。また、この例において上部フィールドプレートセグメント 524 に印加されるバイアス電圧が、下部フィールドプレートセグメント 522 を同じバイアス電圧までバイアスする。 50

## 【0053】

トランジスタ504は、ゲート誘電体層518に接する、垂直ドリフト領域508の上方の基板502におけるn型ボディ530を含む。トランジスタ504はさらに、ボディ530の上方の、および、ゲート誘電体層518に接する、p型ソース532を含む。トレンチゲート520は、垂直ドリフト領域508およびソース532と部分的に同じ広がりを持つ。ソース電極534が基板502の上に配置されて、ソース532およびボディ530への電気的接続を成す。ソース電極534は、トレンチゲート520の上の誘電体キャップ層536によってトレンチゲート520から電気的に絶縁される。ソース532およびボディ530に関するソース電極534のその他の構成も、この例の範囲内にある。

10

## 【0054】

トランジスタ504が最大100ボルトで動作するように設計されるこの例の一つのバージョンにおいて、トレンチ510は、6ミクロン～7ミクロンの深さ、および1.2ミクロン～1.4ミクロンの幅であり得る。垂直ドリフト領域508、すなわち、近隣トレンチ510間は、0.5ミクロン～2.0ミクロンの幅であり得、 $1.8 \times 10^{16} \text{ cm}^{-3} \sim 2.0 \times 10^{16} \text{ cm}^{-3}$ の平均ドーピング密度を有し得る。

## 【0055】

トレンチゲート520への電気接続は、基板502の頂部表面540におけるゲートの露出されたエリア上のゲートコンタクト538を介して成され得る。フィールドプレートセグメント516への電気接続は、フィールドプレートセグメント516から最大で基板502の頂部表面540まで延在するフィールドプレートライザ544上の組み合わされたフィールドプレートコンタクト542を介して成され得る。トレンチゲート520およびフィールドプレートセグメント516に電気接続するためのその他の構造も、この例の範囲内にある。トレンチゲート520から絶縁されるように上部フィールドプレートセグメント524を形成することは、有利に、トランジスタ504における電流密度を増加させるために、フィールドプレートセグメント516を独立してバイアスすることを可能にし得、他方、上部フィールドプレートセグメント524および下部フィールドプレートセグメント522への電気接続が、組み合わされたフィールドプレートコンタクト542を介して成され得るように、トレンチ510における上部フィールドプレートセグメント524に接触するように下部フィールドプレートセグメント522を形成することが、有利に半導体デバイス500の複雑さおよび製造コストを削減し得る。

20

## 【0056】

半導体デバイス500の動作の間、トレンチゲート520は、有利に、図1に関連して説明したような一層高い電流密度を提供する。フィールドプレートセグメント516は、図1に関連して説明したように、垂直ドリフト領域508における電界を所望の値に維持するようにRESURF構成を提供する。従って、上部フィールドプレートセグメント524および下部フィールドプレートセグメント522の組合せを備える垂直MOSトランジスタ504を形成することによって、トランジスタ504が、単一のフィールドプレートを備える同様の垂直MOSトランジスタより浅いトレンチ510を有することが可能とされ、有利に半導体デバイス500の製造コストを削減する。

30

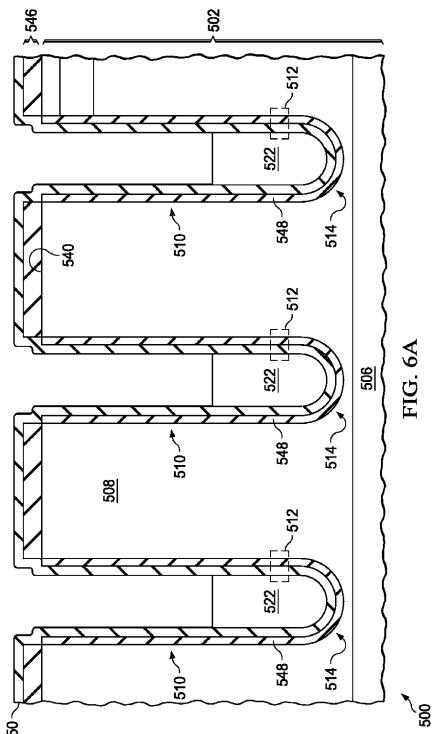

## 【0057】

図6A～図6Hは、製造の連続的な段階において描写される、図5の半導体デバイスの断面図である。図6Aを参照すると、半導体デバイス500は基板502上に形成される。ドレイン領域506は、 $1 \times 10^{20} \text{ cm}^{-3}$ より高いドーピング密度を有するように基板502において形成される。垂直ドリフト領域508におけるホウ素などのP型ドーパントが、エピタキシャル成長の間に混合され得、または、後に注入され得る。ハードマスク546が基板502の上に形成され、ハードマスク546はトレンチ510のためのエリアを露出する。トレンチ510は、ハードマスク546によって露出されたエリアにおける基板502から材料を除去することによって形成される。ドレイン領域506、ハードマスク546、および、トレンチ510は、図2Aに関連して述べたように形成され

40

50

得る。

【0058】

第1の熱酸化物層548が、トレンチ510の側壁および底部514に形成される。堆積二酸化ケイ素層550が、SACVDプロセスまたはPECVDプロセスによって、第1の熱酸化物層548上に形成される。下部フィールドプレートセグメント522が、図2Bおよび図2Cに関連して述べたように、堆積二酸化ケイ素層550上のトレンチ510において形成される。この例において、下部フィールドプレートセグメント522は、垂直ドリフト領域508のRESURF構造において効果的な荷電平衡を提供するため、p型ポリシリコンであり得る。堆積二酸化ケイ素層550と組み合わされた第1の熱酸化物層548は、下部フィールドプレートセグメント522を基板502から分離する誘電体ライナー512を提供する。例えば、この例において、第1の熱酸化物層548は、70ナノメートル～80ナノメートルの厚さであり得、堆積二酸化ケイ素層550は、100ボルトの動作電圧のため、330ナノメートル～420ナノメートルの厚さであり得る。

。

【0059】

図6Bを参照すると、第1のプランケット酸化物エッチバックプロセスが、下部フィールドプレートセグメント522の上方のトレンチ510から、誘電体ライナー512の実質的に全て、すなわち、第1の熱酸化物層548と堆積二酸化ケイ素層550との両方、を除去する。下部フィールドプレートセグメント522は、下部フィールドプレートセグメント522の頂部より下のトレンチ510からの、誘電体ライナー512の除去を防止する。例えば、第1のプランケット酸化物エッチバックプロセスは、緩衝フッ酸溶液を用いる時限のウェットエッティングを含み得る。

。

【0060】

図6Cを参照すると、第2の熱酸化物層560が、下部フィールドプレートセグメント522の上方のトレンチ510の側壁において、および、下部フィールドプレートセグメント522の頂部表面上に形成される。この例において、第2の熱酸化物層560は、図5の上部フィールドプレートセグメント524と基板502との間の誘電体ライナー512を提供する。第2の熱酸化物層560は、トランジスタ504のための100ボルト動作を提供するため、150ナノメートル～200ナノメートルの厚さであり得る。

。

【0061】

図6Dを参照すると、RIEプロセスなどの異方性エッティングプロセスが、下部フィールドプレートセグメント522の頂部表面を露出するため、下部フィールドプレートセグメント522の頂部表面から第2の熱酸化物層560を除去する。異方性エッティングプロセスは、トレンチ510の側壁上の第2の熱酸化物層560を実質的に劣化させることを防ぐために実施される。異方性エッティングプロセスは、トレンチ510の側壁上の第2の熱酸化物層560上に保護ポリマーを形成し得、保護ポリマーは、その後、下部フィールドプレートセグメント522の頂部表面が露出された後、除去される。

。

【0062】

図6Eを参照すると、上部フィールドプレートセグメント524が、図2Fに関連して述べたように、トレンチ510における第2の熱酸化物層560上および下部フィールドプレートセグメント522上に形成される。この例において、上部フィールドプレートセグメント524は、図6Eに関連して説明されるように、p型ポリシリコンであり得る。この例において、第2の熱酸化物層560は、基板502から上部フィールドプレートセグメント524を分離する誘電体ライナー512を提供し、これは、基板502から上部フィールドプレートセグメント524を分離する誘電体ライナー512における第2の誘電体層を形成する必要をなくすことにより、半導体デバイス500の製造の複雑さおよびコストを有利に削減し得る。

。

【0063】

図6Fを参照すると、第2のプランケット酸化物エッチバックプロセスが、上部フィールドプレートセグメント524の上方のトレンチ510から第2の熱酸化物層560を除

。

去する。上部フィールドプレートセグメント 524 は、上部フィールドプレートセグメント 524 の頂部より下のトレンチ 510 からの、第 2 の熱酸化物層 560 の除去を防止する。第 2 のプランケット酸化物エッチバックプロセスは、実質的に半導体材料が基板 502 から除去されないように実施され得る。図 6E のハードマスク 546 は、図 6F において描写されるように、基板 502 の頂部表面 540 を露出するために、第 2 のプランケットエッチバックによって除去され得る。

【0064】

図 6G を参照すると、ゲート誘電体層 518 は、トレンチ 510 の側壁上に形成され、同時に、絶縁層 528 は、上部フィールドプレートセグメント 524 の頂部表面上に形成される。この例において、基板 502 の頂部表面 540 が、図 6F に関連して論じた第 2 のプランケットエッチバックによって露出される場合、ゲート誘電体層 518 も、図 6G において描写されたように、頂部表面 540 上に形成され得る。ゲート誘電体層 518 および絶縁層 528 は、熱酸化、または、熱酸化および誘電体材料の堆積の組合せによって形成され得る。絶縁層 528 における熱酸化は、結晶シリコンと比較したポリシリコン上の 1 層高い熱酸化成長率に起因して、ゲート誘電体層 518 における熱酸化より厚くし得る。

10

【0065】

図 6H を参照すると、トレンチゲート 520 は、ゲート誘電体層 518 および絶縁層 528 に接触して形成される。トレンチゲート 520 は、図 2I および図 2J に関連して述べたように形成され得る。この例において、上部フィールドプレートセグメント 524 の頂部上の絶縁層 528 は、トレンチゲート 520 からフィールドプレートセグメント 516 を電気的に絶縁し、トレンチゲート 520 に対するフィールドプレートセグメント 516 の独立したバイアスを可能にする。さらなる製造が図 5 の構造を提供する。

20

【0066】

図 7 は、垂直 n チャネル MOS トランジスタを含む別の例示的な半導体デバイスの断面図である。半導体デバイス 700 は、基板 702 上に形成され、基板 702 は半導体材料を含む。本明細書においてトランジスタ 704 と呼ばれる n チャネル垂直 MOS トランジスタ 704 は、n 型垂直ドリフト領域 708 の下方の基板 702 において配置される n 型ドレイン領域 706 を含む。

30

【0067】

半導体デバイス 700 はトレンチ 710 を含み、トレンチ 710 は、ドレイン領域 706 に近接する垂直ドリフト領域 708 を介して垂直に、または場合により、ドレイン領域 706 内へ延在する。トレンチ 710 は、トレンチ 710 の底部 714 まで延在し、基板 702 に接する、誘電体ライナー 712 と、誘電体ライナー 712 上の複数のフィールドプレートセグメント 716 とを含む。トレンチ 710 はさらに、基板 702 に接する誘電体ライナー 712 の上方のゲート誘電体層 718 と、ゲート誘電体層 718 に接触する、トランジスタ 704 のトレンチゲート 720 とを含む。この例において、フィールドプレートセグメント 716 は、トレンチ 710 の底部 714 におけるそれぞれの誘電体ライナー 712 上の下部フィールドプレートセグメント 722 と、それぞれの下部フィールドプレートセグメント 722 の上方に配置される、それの中間フィールドプレートセグメント 762 と、それの中間フィールドプレートセグメント 762 の上方およびそれの中間トレンチゲート 720 の下方に配置される、それの中間フィールドプレートセグメント 724 を含む。フィールドプレートセグメント 716 およびトレンチゲート 720 は、主に n 型ポリシリコンを含み得る。誘電体ライナー 712 は、主に二酸化ケイ素を含み得る。誘電体ライナー 712 は、下部フィールドプレートセグメント 722 、中間フィールドプレートセグメント 762 、および、上部フィールドプレートセグメント 724 を基板 702 から分離する。基板 702 から下部フィールドプレートセグメント 722 を分離する誘電体ライナー 712 は、基板 702 から中間フィールドプレートセグメント 762 を分離する誘電体ライナー 712 より厚く、基板 702 から中間フィールドプレートセグメント 762 を分離する誘電体ライナー 712 は、基板 702 から上部フィ

40

50

ールドプレートセグメント 724 を分離する誘電体ライナー 712 より厚い。上部フィールドプレートセグメント 724 と基板 702 との間の、トレンチ 710 の側壁上に配置される誘電体ライナー 712 は、トレンチゲート 720 と基板 702 との間の、トレンチ 710 の側壁上に配置されるゲート誘電体層 718 より厚い。

【0068】

この例において、下部フィールドプレートセグメント 722 は、トレンチ 710 における中間フィールドプレートセグメント 762 に接触し、上部フィールドプレートセグメント 724 は、トレンチ 710 におけるトレンチゲート 720 に接触し、中間フィールドプレートセグメント 762 は、上部フィールドプレートセグメント 724 と中間フィールドプレートセグメント 762 との間に配置される絶縁層 726 によって上部フィールドプレートセグメント 724 から分離される。それゆえ、トレンチゲート 720 に印加されるバイアス電圧が、この例において上部フィールドプレートセグメント 724 にも印加され、中間フィールドプレートセグメント 762 に印加される独立したバイアス電圧も、下部フィールドプレートセグメント 722 を同じ独立したバイアス電圧にバイアスする。

【0069】

トランジスタ 704 は、ゲート誘電体層 718 に接する、垂直ドリフト領域 708 の上方の基板 702 における p 型ボディ 730 を含む。トランジスタ 704 はさらに、ボディ 730 の上方の、ゲート誘電体層 718 に接する、n 型ソース 732 を含む。トレンチゲート 720 は、垂直ドリフト領域 708 およびソース 732 と部分的に同じ広がりを持つ。ソース電極 734 が基板 702 の上に配置され、ソース 732 およびボディ 730 への電気接続を成す。ソース電極 734 は、トレンチゲート 720 の上の誘電体キャップ層 736 によってトレンチゲート 720 から電気的に絶縁される。ソース 732 およびボディ 730 に関するソース電極 734 のためのその他の構成も、この例の範囲内にある。

【0070】

トレンチゲート 720 および上部フィールドプレートセグメント 724 への電気接続は、基板 702 の頂部表面 740 における露出されたエリア上のゲートコンタクト 738 を介して成され得る。中間フィールドプレートセグメント 762 および下部フィールドプレートセグメント 722 への電気接続は、フィールドプレートライザ 744 上の組み合わされたフィールドプレートコンタクト 742 を介して成され得、フィールドプレートライザ 744 は、中間フィールドプレートセグメント 762 から、最大で基板 702 の頂部表面 740 まで延在する。トレンチゲート 720 および中間フィールドプレートセグメント 762 への電気接続を成すためのその他の構造も、この例の範囲内にある。中間フィールドプレートセグメント 762 および下部フィールドプレートセグメント 722 から絶縁されるように、トレンチゲート 720 および上部フィールドプレートセグメント 724 を形成することは、有利に、図 1 に関連して論じたような、トレンチゲート 720 およびフィールドプレートセグメント 716 のための独立したバイアスの利点と、図 3 に関連して論じたような、組み合わされたフィールドプレートコンタクト 742 の利点とのバランスを可能にし得る。

【0071】

半導体デバイス 700 の動作の間、トレンチゲート 720 は、有利に、図 1 に関連して説明したような一層高い電流密度を提供する。フィールドプレートセグメント 716 は、図 1 に関連して説明したように、垂直ドリフト領域 708 における電界を所望の値に維持するように RESURF 構成を提供する。従って、上部フィールドプレートセグメント 724 および下部フィールドプレートセグメント 722 の組合せを備える垂直MOSトランジスタ 704 を形成することによって、トランジスタ 704 が、単一のフィールドプレートを備える同様の垂直MOSトランジスタより浅いトレンチ 710 を有することが可能とされ、有利に、半導体デバイス 700 の製造コストを削減する。

【0072】

特許請求の範囲内で、述べられた実施形態において改変が可能であり、その他の実施形態が可能である。

10

20

30

40

50

【図1】

FIG. 1

【図2A】

FIG. 2A

【図2B】

FIG. 2B

【図2C】

FIG. 2C

【図2D】

FIG. 2D

【図2E】

FIG. 2E

【図2F】

## 【図2G】

FIG. 2F

FIG. 2G

## 【図2H】

FIG. 2H

FIG. 21

## 【図21】

## 【図2】

FIG. 2J

【図2K】

FIG. 2K

【図3】

FIG. 3

【図4A】

FIG. 4A

【図4B】

FIG. 4B

【図4C】

FIG. 4C

【図4D】

FIG. 4D

【図4E】

FIG. 4E

【 5 】

### 【図 6 A】

【図 6 B】

【 図 6 C 】

【図 6 D】

FIG. 6D

【図 6 E】

FIG. 6E

【図 6 F】

FIG. 6F

【図 6 G】

FIG. 6G

【図6H】

FIG. 6H

【図7】

FIG. 7

---

フロントページの続き

(72)発明者 シーサラマン スリダール

アメリカ合衆国 75082 テキサス州 リチャードソン, シーダー エルム サークル 4

424

(72)発明者 クリストファー ボウガスロウ ココン

アメリカ合衆国 18707 ペンシルベニア州 マウンテン トップ, ウィルドウッド レー

ン 5

(72)発明者 シモン ジョン モロイ

アメリカ合衆国 18104 ペンシルベニア州 アレンタウン, ウエスト ユニオン ストリ

ート 2331

(72)発明者 ホン ヤン

アメリカ合衆国 75082 テキサス州 リチャードソン, ブレッキンリッジ ブールバード

4616

審査官 西出 隆二

(56)参考文献 特開2003-017696 (JP, A)

特開2007-116189 (JP, A)

特開2014-078741 (JP, A)

特開2012-109580 (JP, A)

特開2010-129973 (JP, A)

特開2002-299619 (JP, A)

特表2010-537428 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 29/78

H01L 21/283

H01L 21/336

H01L 29/41