(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4310847号

(P4310847)

(45) 発行日 平成21年8月12日(2009.8.12)

(24) 登録日 平成21年5月22日(2009.5.22)

(51) Int.Cl.

HO4N 7/01 (2006.01)

F 1

HO4N 7/01

Z

請求項の数 4 (全 15 頁)

(21) 出願番号 特願平11-127294

(22) 出願日 平成11年5月7日(1999.5.7)

(65) 公開番号 特開2000-324497 (P2000-324497A)

(43) 公開日 平成12年11月24日(2000.11.24)

審査請求日 平成18年2月16日(2006.2.16)

(73) 特許権者 000002185

ソニー株式会社

東京都港区港南1丁目7番1号

(74) 代理人 100082762

弁理士 杉浦 正知

(72) 発明者 近藤 哲二郎

東京都品川区北品川6丁目7番35号 ソ

ニー株式会社内

(72) 発明者 立平 靖

東京都品川区北品川6丁目7番35号 ソ

ニー株式会社内

(72) 発明者 内田 真史

東京都品川区北品川6丁目7番35号 ソ

ニー株式会社内

最終頁に続く

(54) 【発明の名称】 画像情報変換装置および変換方法

## (57) 【特許請求の範囲】

## 【請求項 1】

インターレース走査方式の入力ディジタル画像信号のフィールド間に新たなフィールドを生成することによって上記入力ディジタル画像信号のフィールド数より多いフィールド数のインターレース走査方式の出力ディジタル画像信号を形成する画像情報変換装置において、

上記入力ディジタル画像信号から処理対象の注目画素の周辺の複数の画像データを切り出す第1の画像切り出し手段と、

上記第1の画像切り出し手段によって切り出される上記複数の画像データの各々のレベル分布を検出し、検出したレベル分布から上記注目画素が属するクラスを決定し、決定したクラスを表現するクラス検出情報を出力するクラス検出手段と、

上記入力ディジタル画像信号から上記注目画素の周辺の複数の画像データを切り出す第2の画像切り出し手段と、

上記クラスのそれぞれに対応して予め決定され、上記出力ディジタル画像信号を推定するための予測係数を記憶し、記憶した予測係数の内から、上記クラス検出手段からの上記クラス検出情報に対応する予測係数を出力する係数記憶手段と、

上記第2の画像切り出し手段によって切り出される上記複数の画像データと、上記係数記憶手段から供給される予測係数との積和演算を行い、上記出力ディジタル画像信号の画像データの予測値を生成する演算処理手段とを有し、

上記予測係数は、上記クラス毎に予め学習によって求められて上記係数記憶手段に記憶

され、

上記学習は、

上記入力ディジタル画像信号の画素位置に対して、上記入力ディジタル画像信号のフィールドと時間方向に一致するフィールドを含み、且つ上記入力ディジタル画像信号と垂直方向の画素位置が一致する第1の位置関係の出力ディジタル画像信号と、上記入力ディジタル画像信号のフィールドと時間方向に一致するフィールドを含み、且つ上記入力ディジタル画像信号の画素位置を中心として画素位置が垂直方向に対称となる第2の位置関係の出力ディジタル画像信号と、上記入力ディジタル画像信号のフィールドを中心としてフィールドが時間方向に対称となり、且つ上記入力ディジタル画像信号と垂直方向の画素位置が一致する第3の位置関係の出力ディジタル画像信号と、上記入力ディジタル画像信号のフィールドを中心としてフィールドが時間方向に対称となり、且つ上記入力ディジタル画像信号の画素位置を中心として画素位置が垂直方向に対称となる第4の位置関係の出力ディジタル画像信号とからなり、

上記第1、第2、第3、および第4の位置関係の出力ディジタル画像信号の内から1つの位置関係の出力ディジタル画像信号を選択し、上記選択された出力ディジタル画像信号と同一の信号形式の教師画像信号の画素を、上記入力ディジタル画像信号の画素位置へ変換し、

上記変換された出力ディジタル画像信号の単位時間当たりのフィールド数を、上記入力ディジタル画像信号と同一となるように変換したディジタル画像信号を生成し、

上記積和演算によって、上記生成されたディジタル画像信号から上記選択された出力ディジタル画像信号の画素値を生成する時に、生成される画素値と上記教師画像信号の対応する位置の画素の真値との誤差を最小にするように、上記予測係数を求める処理である画像情報変換装置。

#### 【請求項2】

上記演算処理手段は、

単位時間当たりのフィールド数が上記入力ディジタル画像信号の2倍となるような上記出力ディジタル画像信号を生成する請求項1に記載の画像情報変換装置。

#### 【請求項3】

上記学習では、

上記出力ディジタル画像信号の画素に対して垂直位相のずれを生じさせ、上記入力ディジタル画像信号の画素位置へ変換する垂直位相シフト手段を有する請求項1に記載の画像情報変換装置。

#### 【請求項4】

インターレース走査方式の入力ディジタル画像信号のフィールド間に新たなフィールドを生成することによって上記入力ディジタル画像信号のフィールド数より多いフィールド数のインターレース走査方式の出力ディジタル画像信号を形成する画像情報変換方法において、

上記入力ディジタル画像信号から処理対象の注目画素の周辺の複数の画像データを切り出す第1の画像切り出しステップと、

上記第1の画像切り出しステップによって切り出される上記複数の画像データの各々のレベル分布を検出し、検出したレベル分布から上記注目画素が属するクラスを決定し、決定したクラスを表現するクラス検出情報を出力するクラス検出ステップと、

上記入力ディジタル画像信号から上記注目画素の周辺の複数の画像データを切り出す第2の画像切り出しステップと、

上記クラスのそれぞれに対応して予め決定され、上記出力ディジタル画像信号を推定するための予測係数を記憶し、記憶した予測係数の内から、上記クラス検出ステップからの上記クラス検出情報を対応する予測係数を出力する係数記憶ステップと、

上記第2の画像切り出しステップによって切り出される上記複数の画像データと、上記係数記憶ステップから供給される予測係数との積和演算を行い、上記出力ディジタル画像信号の画像データの予測値を生成する演算処理ステップとを有し、

10

20

30

40

50

上記予測係数は、上記クラス毎に予め学習によって求められて記憶され、

上記学習は、

上記入力ディジタル画像信号の画素位置に対して、上記入力ディジタル画像信号のフィールドと時間方向に一致するフィールドを含み、且つ上記入力ディジタル画像信号と垂直方向の画素位置が一致する第1の位置関係の出力ディジタル画像信号と、上記入力ディジタル画像信号のフィールドと時間方向に一致するフィールドを含み、且つ上記入力ディジタル画像信号の画素位置を中心として画素位置が垂直方向に対称となる第2の位置関係の出力ディジタル画像信号と、上記入力ディジタル画像信号のフィールドを中心としてフィールドが時間方向に対称となり、且つ上記入力ディジタル画像信号と垂直方向の画素位置が一致する第3の位置関係の出力ディジタル画像信号と、上記入力ディジタル画像信号のフィールドを中心としてフィールドが時間方向に対称となり、且つ上記入力ディジタル画像信号の画素位置を中心として画素位置が垂直方向に対称となる第4の位置関係の出力ディジタル画像信号とからなり、

上記第1、第2、第3、および第4の位置関係の出力ディジタル画像信号の内から1つの位置関係の出力ディジタル画像信号を選択し、上記選択された出力ディジタル画像信号と同一の信号形式の教師画像信号の画素を、上記入力ディジタル画像信号の画素位置へ変換し、

上記変換された出力ディジタル画像信号の単位時間当たりのフィールド数を、上記入力ディジタル画像信号と同一となるように変換したディジタル画像信号を生成し、

上記積和演算によって、上記生成されたディジタル画像信号から上記選択された出力ディジタル画像信号の画素値を生成する時に、生成される画素値と上記教師画像信号の対応する位置の画素の真値との誤差を最小にするように、上記予測係数を求める処理である画像情報変換方法。

#### 【発明の詳細な説明】

##### 【0001】

##### 【発明の属する技術分野】

この発明は、入力するディジタル画像信号を、より画素数の大きいディジタル画像信号に変換する画像情報変換装置および変換方法に関する。

##### 【0002】

##### 【従来の技術】

テレビジョン受像器の走査方式としては、従来から、水平走査線（ライン）を1本おきに飛び越して走査するインターレース走査方式が最も広く採用されている。インターレース走査方式では、奇数番目のラインを走査してなる奇数フィールドと偶数番目のラインを走査してなる偶数フィールドとの2枚のフィールドによって1枚のフレームが形成される。

##### 【0003】

インターレース走査方式は、世界各国のテレビジョン標準方式として採用されている。例えば欧州のテレビジョン放送では、フィールド周波数が50Hzのインターレース走査方式が用いられている。

##### 【0004】

##### 【発明が解決しようとする課題】

フィールド周波数が50Hzのインターレース走査方式を用いたテレビジョン受像機では、面フリッカと称されるちらつきが表示画面の広い範囲に渡って発生するという問題があった。面フリッカは、インターレース走査方式において奇数フィールドから偶数フィールドに切り替わるまでに所定の時間を要するため、各ラインが所定時間間隔毎に表示されることに起因して生じる。

##### 【0005】

このような問題に対処する方法として、入力する例えば50HzのSD(Standard Definition)画像に基づいて、メディアンフィルタによって補間フィールドを生成することにより、例えば100Hzの画像信号を生成するフィールド倍速処理が知られている。この方法は、補間画素を含むフィールド内、および補間画素を含むフィールドの1フィールド前

10

20

30

40

50

のフィールド内で当該補間画素に近接する例えは 3 個の画素の内で、中間の画素値を補間画素の画素値とするものである。

【 0 0 0 6 】

しかしながら、このような方法では、補間処理の対象とされる SD 画像が静止画像の場合に、垂直解像度の高い画像領域において不自然な歪みが発生する。また、補間処理の対象とされる SD 画像が動画像の場合に、1 フィールド前の画素の画素値が補間画素の画素値として選択されることがあり、このような選択がなされる場合には不自然な動きが発生するという問題があった。

【 0 0 0 7 】

このような問題点を解消すべく、本願出願人は、クラス分類適応処理を行うことによって 10

入力画像をフィールド倍速画像に変換する方法を提案している。但し、かかる方法では、生成すべき画像内の画素と SD 画像内の画素との位置関係によって変換性能に部分的なばらつきが生じ、その結果としてフィールド倍速画像全体における画質の向上が妨げられるおそれがあった。

【 0 0 0 8 】

従って、この発明の目的は、生成すべき画像内の画素と SD 画像内の画素との間で複数種類の画素位置関係を前提とする処理を行うことにより、例えばフィールド倍速画像等の画像情報変換の結果として生成される画像における画質を向上させることが可能な、画像情報変換装置および変換方法を提供することにある。

【 0 0 0 9 】

【課題を解決するための手段】

請求項 1 の発明は、インターレース走査方式の入力ディジタル画像信号のフィールド間に新たなフィールドを生成することによって入力ディジタル画像信号のフィールド数より 20

多いフィールド数のインターレース走査方式の出力ディジタル画像信号を形成する画像情報変換装置において、入力ディジタル画像信号から処理対象の注目画素の周辺の複数の画像データを切り出す第 1 の画像切り出し手段と、第 1 の画像切り出し手段によって切り出される複数の画像データの各々のレベル分布を検出し、検出したレベル分布から注目画素が属するクラスを決定し、決定したクラスを表現するクラス検出情報を出力するクラス検出手段と、入力ディジタル画像信号から注目画素の周辺の複数の画像データを切り出す第 2 の画像切り出し手段と、クラスのそれぞれに対応して予め決定され、出力ディジタル画像信号を推定するための予測係数を記憶し、記憶した予測係数の内から、クラス検出手段からのクラス検出情報に対応する予測係数を出力する係数記憶手段と、第 2 の画像切り出し手段によって切り出される複数の画像データと、係数記憶手段から供給される予測係数との積和演算を行い、出力ディジタル画像信号の画像データの予測値を生成する演算処理手段とを有し、予測係数は、クラス毎に予め学習によって求められて係数記憶手段に記憶され、学習は、入力ディジタル画像信号の画素位置に對して、入力ディジタル画像信号のフィールドと時間方向に一致するフィールドを含み、且つ入力ディジタル画像信号と垂直方向の画素位置が一致する第 1 の位置関係の出力ディジタル画像信号と、入力ディジタル画像信号のフィールドと時間方向に一致するフィールドを含み、且つ入力ディジタル画像信号の画素位置を中心として画素位置が垂直方向に對称となる第 2 の位置関係の出力ディジタル画像信号と、入力ディジタル画像信号のフィールドを中心としてフィールドが時間方向に對称となり、且つ入力ディジタル画像信号と垂直方向の画素位置が一致する第 3 の位置関係の出力ディジタル画像信号と、入力ディジタル画像信号のフィールドを中心としてフィールドが時間方向に對称となり、且つ入力ディジタル画像信号の画素位置を中心として画素位置が垂直方向に對称となる第 4 の位置関係の出力ディジタル画像信号とからなり、第 1 、第 2 、第 3 、および第 4 の位置関係の出力ディジタル画像信号の内から 1 つの位置関係の出力ディジタル画像信号を選択し、選択された出力ディジタル画像信号と同一の信号形式の教師画像信号の画素を、入力ディジタル画像信号の画素位置へ変換し、変換された出力ディジタル画像信号の単位時間当たりのフィールド数を、入力ディジタル画像信号と同一となるように変換したディジタル画像信号を生成し、積和演算によって、生成 40

50

されたディジタル画像信号から選択された出力ディジタル画像信号の画素値を生成する時に、生成される画素値と教師画像信号の対応する位置の画素の真値との誤差を最小にするように、予測係数を求める処理である画像情報変換装置である。

【0010】

請求項4の発明は、インターレース走査方式の入力ディジタル画像信号のフィールド間に新たなフィールドを生成することによって入力ディジタル画像信号のフィールド数より多いフィールド数のインターレース走査方式の出力ディジタル画像信号を形成する画像情報変換方法において、入力ディジタル画像信号から処理対象の注目画素の周辺の複数の画像データを切り出す第1の画像切り出しステップと、第1の画像切り出しステップによって切り出される複数の画像データの各々のレベル分布を検出し、検出したレベル分布から注目画素が属するクラスを決定し、決定したクラスを表現するクラス検出情報を出力するクラス検出ステップと、入力ディジタル画像信号から注目画素の周辺の複数の画像データを切り出す第2の画像切り出しステップと、クラスのそれぞれに対応して予め決定され、出力ディジタル画像信号を推定するための予測係数を記憶し、記憶した予測係数の内から、クラス検出ステップからのクラス検出情報に対応する予測係数を出力する係数記憶ステップと、第2の画像切り出しステップによって切り出される複数の画像データと、係数記憶ステップから供給される予測係数との積和演算を行い、出力ディジタル画像信号の画像データの予測値を生成する演算処理ステップとを有し、予測係数は、クラス毎に予め学習によって求められて記憶され、学習は、入力ディジタル画像信号の画素位置に対して、入力ディジタル画像信号のフィールドと時間方向に一致するフィールドを含み、且つ入力ディジタル画像信号と垂直方向の画素位置が一致する第1の位置関係の出力ディジタル画像信号と、入力ディジタル画像信号のフィールドと時間方向に一致するフィールドを含み、且つ入力ディジタル画像信号の画素位置を中心として画素位置が垂直方向に対称となる第2の位置関係の出力ディジタル画像信号と、入力ディジタル画像信号のフィールドを中心としてフィールドが時間方向に対称となり、且つ入力ディジタル画像信号と垂直方向の画素位置が一致する第3の位置関係の出力ディジタル画像信号と、入力ディジタル画像信号のフィールドを中心として画素位置が垂直方向に対称となり、且つ入力ディジタル画像信号の画素位置を中心として画素位置が垂直方向に対称となる第4の位置関係の出力ディジタル画像信号とからなり、第1、第2、第3、および第4の位置関係の出力ディジタル画像信号の内から1つの位置関係の出力ディジタル画像信号を選択し、選択された出力ディジタル画像信号と同一の信号形式の教師画像信号の画素を、入力ディジタル画像信号の画素位置へ変換し、変換された出力ディジタル画像信号の単位時間当たりのフィールド数を、入力ディジタル画像信号と同一となるように変換したディジタル画像信号を生成し、積和演算によって、生成されたディジタル画像信号から選択された出力ディジタル画像信号の画素値を生成する時に、生成される画素値と教師画像信号の対応する位置の画素の真値との誤差を最小にするように、予測係数を求める処理である画像情報変換方法である。

【0011】

以上のような発明によれば、生徒画像信号と教師画像信号との複数種類の組合せの内、所望の画像情報変換に対してより好適な組合せを用いて予測係数を生成することができる。

【0012】

【発明の実施の形態】

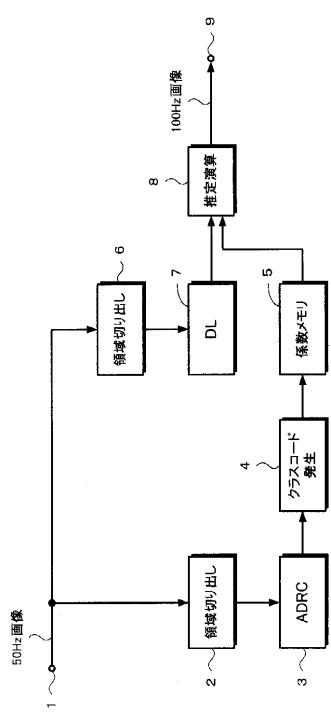

以下、この発明の一実施形態について図面を参照して説明する。図1に、この発明の一実施形態における画像情報変換に係る構成の一例を示す。入力端子1を介して、PAL方式における50Hzインターレース画像がデジタル化されてなる画像信号がSD画像データとして領域切り出し回路2および6に供給される。領域切り出し回路2は、供給されるSD画像データから所定の画素領域をクラスタップとして切り出し、切り出したクラスタップのデータをADC(Adaptive Dynamic Range Coding)回路3に供給する。ADC回路3は供給されるデータにADC処理を施し、これによって生成したコード値をクラスコード発生回路4に供給する。

10

20

30

40

50

## 【0013】

クラスコード発生回路4は、供給されるコード値に基づいて、時空間におけるパターンに応じたクラスを示すクラスコードを発生する。発生したクラスコードは係数メモリ5に供給される。係数メモリ5には、後述するようにして予め決定された、予測係数セットがクラスコードに対応して記憶されている。

## 【0014】

一方、領域切り出し回路6は、供給される50Hzインターレース画像から所定の画素領域を予測タップとして切り出し、切り出した予測タップのデータを遅延回路7に供給する。遅延回路7は、供給されるデータを一旦保持し、保持したデータを適切なタイミングで推定演算回路8に供給する。これにより、予測タップのデータが推定演算回路8に供給されるタイミングと、予測係数が係数メモリ5から推定演算回路8に供給されるタイミングとが合わされる。推定演算回路8は、遅延回路7の出力と、係数メモリ5の出力とに基づく演算を行うことにより、フィールド倍速画像としての100Hz画像を生成する。生成される100Hz画像は、出力端子9を介して図示しないテレビジョン受像機等の表示装置等に供給される。

10

## 【0015】

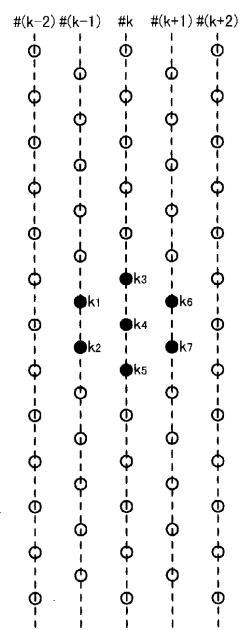

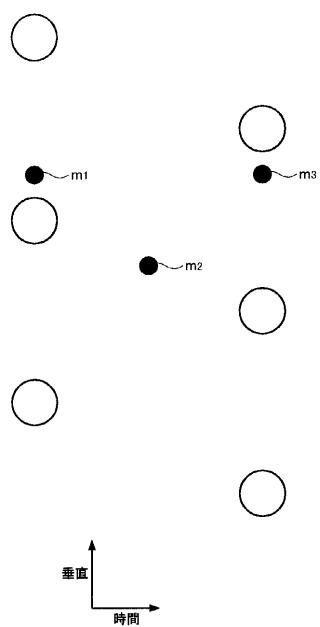

以下、各構成要素による処理について詳細に説明する。領域切り出し回路2が切り出すクラスタップのタップ構造の一般的な例を図2に示す。ここで、水平方向は時間の推移を示す。すなわち、#(k-2), #(k-1), ..., #(k+2)は、それぞれ、時点 k-2, k-1, ..., k+2 におけるフィールドを示している。また、垂直方向は各フィールドにおける垂直方向を示す。50Hzインターレース画像では隣接するフィールド間で走査線位相がずれている。この例では、k1 ~ k7 の7個の画素がクラスタップとされる。

20

## 【0016】

ADC回路3は、1画素当たり例えば8ビットからなるクラスタップの画素データを、例えば2ビットの再量子化コード値に変換する。このようにして生成される再量子化コード値により、クラスタップのデータにおけるレベル分布のパターンがより少ない情報量によって表現される。すなわち、ADC回路3の出力は、パターン圧縮データとして用いられる。ADCは、本来、VTR(Video Tape Recorder)用の高能率符号化のために開発された適応的再量子化法であるが、信号レベルの局所的なパターンを短い語調で効率的に表現できるという特徴を有する。このため、クラス分類のコードを発生するための、画像信号の時空間内でのパターンに使用することができる。ADC回路3では、以下の式(1)により、クラスタップとして切り出される領域内の最大値MAXと最小値MINとの間を指定されたビット数で均等に分割して、クラスタップとして切り出されたデータを再量子化する。

30

## 【0017】

$$DR = MAX - MIN + 1$$

$$Q = [ (L - MIN + 0.5) \times 2^n / DR ] \quad (1)$$

ここで、DRは領域内のダイナミックレンジである。また、nはビット割り当て数であり、例えばn=2とすることができます。また、Lは領域内画素のデータレベルであり、Qが再量子化コードである。但し、大かっこ([ ])は切り捨て処理を意味する。

40

## 【0018】

図2に示すようなk1 ~ k7の7画素からなるクラスタップのタップ構造を用いる場合、上述したような処理により、各画素に対応する7個の再量子化コードq1 ~ q7がADC回路3の出力とされる。かかる出力に基づいてクラスコード発生回路4が発生するクラスコードclassは、次の式(2)のようなものである。

## 【0019】

## 【数1】

$$class = \sum_{i=1}^n q_i (2^p)^i \quad (2)$$

## 【0020】

ここで、 $n$  はクラスタップ中の画素数であり、図 2 に示すようなクラスタップのタップ構造においては  $n = 7$  である。また、 $p$  の値としては、例えば  $p = 2$  とすることができます。

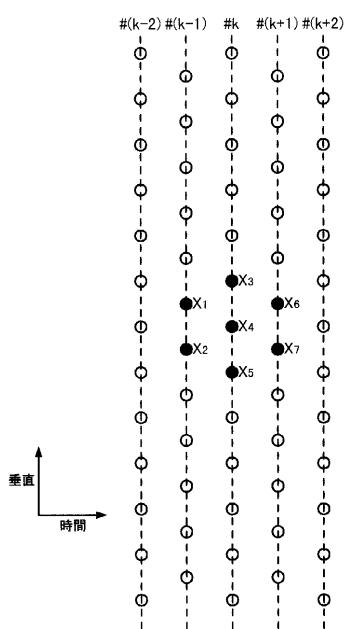

## 【0021】

また、領域切り出し回路 6 が切り出す予測タップのタップ構造の一般的な例を図 3 に示す。ここで、水平方向は時間の推移を示す。すなわち、#(k-2), #(k-1), #(k+2) は、それぞれ、時点  $k-2, k-1, \dots, k+2$  におけるフィールドを示している。また、垂直方向は各フィールドにおける垂直方向を示す。この例では、 $k_1 \sim k_7$  の 7 個の画素が予測タップとされる。

## 【0022】

$$h d' = w_1 \times x_1 + w_2 \times x_2 + \dots + w_n \times x_n \quad (3)$$

ここで、 $x_1, \dots, x_n$  が各予測タップの画素データであり、 $w_1, \dots, w_n$  が各予測係数である。

## 【0023】

$$h d' = w_1 \times x_1 + w_2 \times x_2 + \dots + w_n \times x_n \quad (3)$$

ここで、 $x_1, \dots, x_n$  が各予測タップの画素データであり、 $w_1, \dots, w_n$  が各予測係数である。

## 【0024】

上述したようにしてクラス分類適応処理によってフィールド倍速画像を生成する場合には、SD 画像データを単に補間処理する場合に比べ、より精度良くフィールド倍速画像を生成することができる。なお、予測係数は、SD 画像データ内の画素位置と、生成されるべきフィールド倍速画像内の画素位置との関係に応じて、後述するような処理によって決定される。

## 【0025】

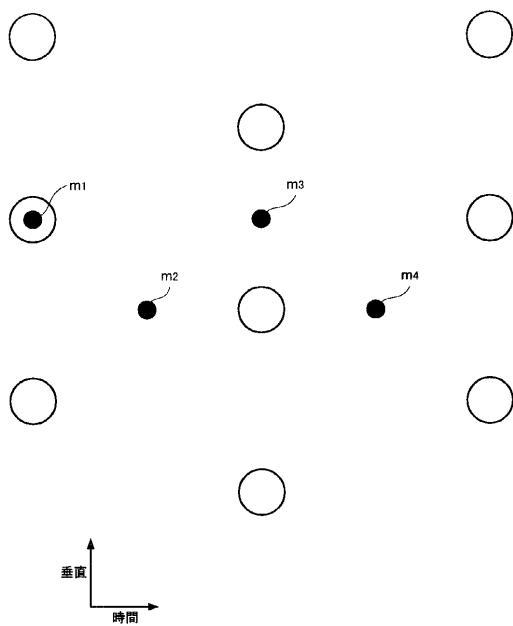

次に、SD 画像としての 50 Hz 画像内の画素位置とフィールド倍速画像としての 100 Hz 画像内の画素位置との位置関係に応じた変換性能について説明する。まず、本願出願人によるフィールド倍速処理に係る先の提案 (9800237506 参照) における、創造すべきフィールドの画素位置と予測タップの画素位置との関係の例を図 4 に示す。この場合、創造される 100 Hz 画素  $m_1, m_2, m_3, m_4$  の内、 $m_1$  は時間的空間的に 50 Hz 画素と一致した位置にあるため、 $m_1$  の創造に係る変換性能は極めて良好となる。

## 【0026】

これに対し、 $m_2$  および  $m_4$  は、50 Hz 画素との時間的な隔たりが大きいので、 $m_2$  および  $m_4$  の創造に係る変換性能は特に動画像において  $m_1$  の創造に係る変換性能に比べて劣るという問題があった。一般に、画像全体についての画質の良否は、当該画像全体の中で最も劣化した部分に強く影響される傾向がある。このため、画像全体についての画質の向上を図る上で、画素の位置関係によって変換性能が大きく異なることは好ましくない。

## 【0027】

また、100 Hz 画素  $m_2$  および  $m_4$  は、時間的な対称性を利用すると互いに同一の予測係数を使用することによって創造することができる。これに対して、100 Hz 画素  $m_1$  および  $m_3$  を創造するためにはそれぞれ別個の予測係数を使用する必要がある。すなわち、図 4 に示した例においては 3 種類の予測係数が必要となる。このため、ハードウェアの規模が大きくなるので、特にハードウェアの規模が制約される場合において問題となることがある。

## 【0028】

そこで、この発明は、SD 画像内の画素とフィールド倍速画像内の画素との画素位置関係

10

20

30

40

50

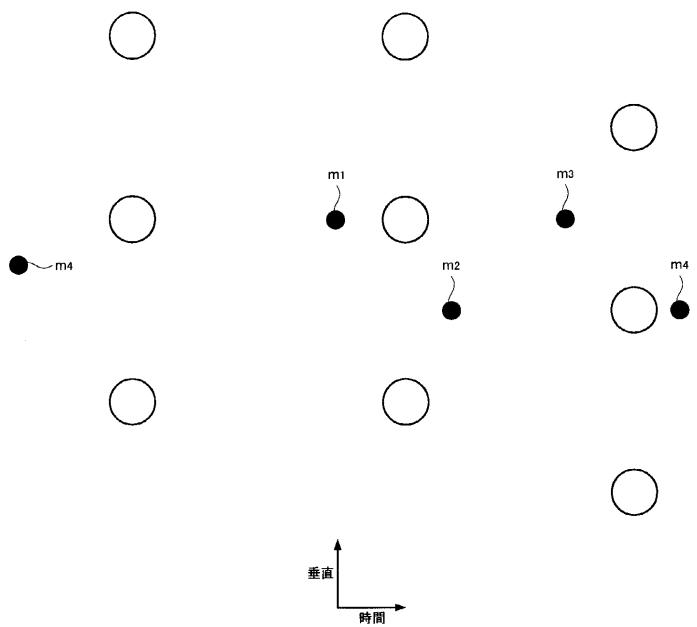

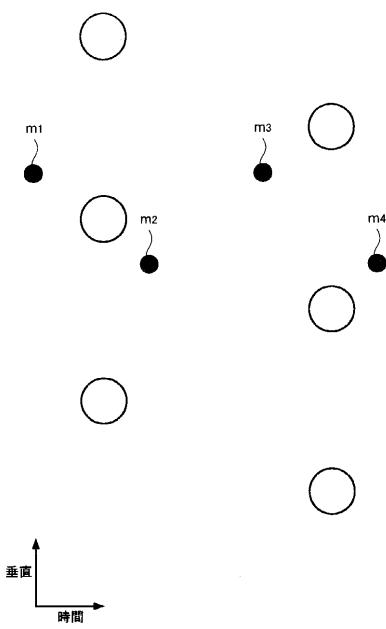

としてより適切なものを選択できるようにしたものである。以下、図4に示した例と共に、図5、図6、図7にそれぞれ示す、この発明の一実施形態において用いることが可能な画素位置関係の一例、他の例、さらに他の例について順次説明する。

【0029】

図4に示した画素位置関係の例を用いてフィールド倍速変換を行う場合には、 $m_1$  の予測精度が最も高く、 $m_3$  の予測精度がそれに次いで高く、 $m_2$  および $m_4$  の予測精度が最も低い。そして、変換によって得られる画像全体の画質は、 $m_2$  および $m_4$  の予測精度に大きく影響される。また、上述したように、全部で3種類の予測係数が必要とされる。また、この画素位置関係においては、ラインフリッカが強調されることはない。

【0030】

図6に示す画素位置関係の他の例を用いてフィールド倍速変換を行う場合には、 $m_1$ 、 $m_2$ 、 $m_3$ 、 $m_4$  の4種類の画素の各々について予測精度が異なる。但し、図4に示した例と比較するとばらつきは小さく、ばらつきの程度は図5に示した一例と略同等となる。また、 $m_1$  および $m_3$  を創造するに際しては、時間方向の対称性を利用することによって予測係数の共通化を行うことができる。さらに、 $m_2$  および $m_4$  を創造するに際しては、空間（垂直）方向の対称性を利用することによって予測係数の共通化を行うことができる。従って、創造すべき4種類の画素について全部で2種類の予測係数が必要となる。また、この場合にはラインフリッカが強調されることはない。

【0031】

図6に示す画素位置関係の他の例を用いてフィールド倍速変換を行う場合には、 $m_1$ 、 $m_2$ 、 $m_3$ 、 $m_4$  の4種類の画素の各々について予測精度が異なる。但し、図4に示した例と比較するとばらつきは小さく、ばらつきの程度は図5に示した一例と略同等となる。また、 $m_1$  および $m_3$  を創造するに際しては、時間方向の対称性を利用することによって予測係数の共通化を行うことができる。さらに、 $m_2$  および $m_4$  を創造するに際しては、空間（垂直）方向の対称性を利用することによって予測係数の共通化を行うことができる。従って、創造すべき4種類の画素について全部で2種類の予測係数が必要となる。また、この場合にはラインフリッカが強調されることはない。

【0032】

図7に示す画素位置関係のさらに他の例を用いてフィールド倍速変換を行う場合には、 $m_1$ 、 $m_2$ 、 $m_3$ 、 $m_4$  の4種類の画素の各々について予測精度が同一となり、予測精度の画素位置によるばらつきは無い。また、時間方向の対称性／空間（垂直）方向の対称性を利用することによって $m_1$ ～ $m_4$  の全ての予測係数の共通化を行うことができる。従って、創造すべき4種類の画素の全てを、1種類の予測係数の下で創造することができる。また、この場合にはラインフリッカが強調されるおそれがある。

【0033】

上述したような画素位置関係の各例についての特徴を考慮して、予測係数を保持するためのメモリ容量等のハードウェア的な制約、ラインフリッカが許容されるか否か等の用途等に係る条件等に応じて最も好適な画素位置関係を選ぶことにより、総合的な変換性能を向上させることができる。

【0034】

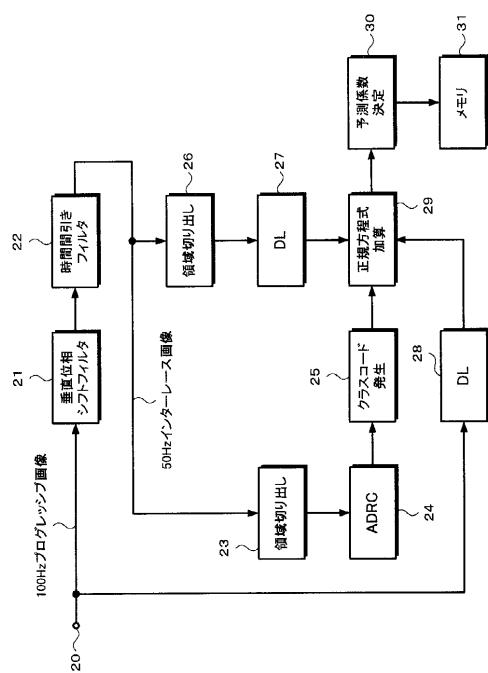

次に、この発明の一実施形態における学習、すなわち予測係数を決定する処理について図8を参照して説明する。入力端子20を介して、画像情報変換の結果として生成されるべき画像と同一の信号形式を有する画像（教師画像と称される）内の画素を全て含む画像が供給される。この発明の一実施形態は、50Hz画像を100Hz画像に変換するものなので、100Hzプログレッシブ画像が入力端子20を介して垂直位相シフトフィルタ21および遅延回路28に供給される。垂直位相シフトフィルタ21は、図4～図7を参照して上述したような画素位置関係の何れを前提として学習を行うかに応じた処理を行う（これについては後述する）。

【0035】

垂直位相シフトフィルタ21の出力が時間間引きフィルタ22に供給される。時間間引き

10

20

30

40

50

フィルタ22は、垂直位相シフトフィルタ21の出力に対して、時間方向に平滑化する処理を施すことにより、50Hzインターレース画素位置に画素を生成する。このようにして、SD画像と同一の信号形式（すなわち50Hzインターレース画像）を生成することができる。かかる画像は生徒画像と称される。生徒画像が領域切り出し回路23、26に供給される。

【0036】

領域切り出し回路23は、図1中の領域切り出し回路2と同一の処理を行う。すなわち、領域切り出し回路23は、供給される生徒画像から、領域切り出し回路2によって切り出されるものと同一の画素領域をクラスタップとして切り出し、切り出したクラスタップのデータをADRC回路24に供給する。ADRC回路24は、供給されるデータに図1中のADRC回路3と同一の処理を施す。すなわち、上述の式(1)に示したような演算を行うことにより、例えば8ビットを単位とするデータから2ビットを単位とする再量子化コードを形成する。形成された再量子化コードがパターン圧縮データとしてクラスコード発生回路25に供給する。

10

【0037】

クラスコード発生回路25は、図1中のクラスコード発生回路3と同一の処理を行う。すなわち、クラスコード発生回路25は、ADRC回路24の出力に基づいて上述の式(2)に示したような演算を行うことにより、クラスコードを発生する。クラスコード発生回路25の出力は、正規方程式加算回路29に供給される。一方、領域切り出し回路26は、図1中の領域切り出し回路6と同一の処理を行う。すなわち、領域切り出し回路26は、供給される画像信号から、領域切り出し回路6によって切り出されるものと同一の画素領域を予測タップとして切り出し、切り出した予測タップのデータを遅延回路27に供給する。遅延回路27は、供給されるデータを一旦保持し、その後、正規方程式加算回路29に供給する。

20

【0038】

また、遅延回路28は、供給される100Hzプログレッシブ画像を一旦保持し、その後、正規方程式加算回路29に供給する。遅延回路28および29により、算処理を行ために好適なタイミングで、正規方程式加算回路29が領域切り出し回路26の出力および100Hzプログレッシブ画像を供給されることが担保される。

30

【0039】

正規方程式加算回路29は、遅延回路27から供給されるクラスタップのデータ、遅延回路25から供給されるクラスコード、および遅延回路28から供給される100Hzプログレッシブ画像に基づいて、後述するような正規方程式のデータを算出する。ここで、正規方程式加算回路29は、100Hzプログレッシブ画像から教師画像を構成するデータを抽出し、抽出したデータに基づく演算処理を行う。算出されるデータは、予測係数決定回路30に供給される。予測係数決定回路30は、供給されるデータに基づいて正規方程式を解くための演算を行う。かかる演算の結果として算出された予測係数はメモリ31に供給される。図1を参照して上述した構成による処理を行うに先立ち、メモリ31の記憶内容が係数メモリ5にロードされる。

40

【0040】

予測係数を算出するための演算処理について説明する。以下の説明では、予測タップとして切り出される画素数を一般化してnとする。すなわち、 $x_1, x_2, \dots, x_n$ を予測タップとする場合、フィールド倍速画像中の画素レベルyが次の式(4)に従って計算されるとする。

【0041】

$$y = w_1 \times x_1 + w_2 \times x_2 + \dots + w_n \times x_n \quad (4)$$

学習前は、予測係数 $w_1, \dots, w_n$ が未定係数である。学習は、クラス毎に複数の画像データについて行う。画像データの種類数をmと表記する場合、式(4)から、以下の式(5)が設定される。

【0042】

50

$$y_k = w_1 \times x_{k1} + w_2 \times x_{k2} + \dots + w_n \times x_{kn} \quad (5)$$

( $k = 1, 2, \dots, m$ )

$m > n$  の場合には、 $w_1, \dots, w_n$  は一意に決まらないので、誤差ベクトル  $e$  の要素  $e_k$  を以下の式 (6) で定義して、式 (7) によって定義される誤差ベクトル  $e$  を最小とするように予測係数を定めるようにする。すなわち、いわゆる最小 2 乗法によって予測係数を一意に定める。

【0043】

$$e_k = y_k - \{ w_1 \times x_{k1} + w_2 \times x_{k2} + \dots + w_n \times x_{kn} \} \quad (6)$$

( $k = 1, 2, \dots, m$ )

【0044】

【数2】

10

$$e^2 = \sum_{k=0}^m e_k^2 \quad (7)$$

【0045】

式 (7) の  $e^2$  を最小とする予測係数を求めるための実際的な計算方法としては、 $e^2$  を予測係数  $w_i$  ( $i=1, 2, \dots, n$ ) で偏微分し (式 (8))、 $i$  の各値について偏微分値が 0 となるように各予測係数  $w_i$  を決定すれば良い。

20

【0046】

【数3】

$$\frac{\partial e^2}{\partial w_i} = \sum_{k=0}^m 2 \left( \frac{\partial e_k}{\partial w_i} \right) e_k = \sum_{k=0}^m 2 x_{ki} \cdot e_k \quad (8)$$

【0047】

30

式 (8) から各予測係数  $w_i$  を決定する具体的な手順について説明する。式 (9)、(10) のように  $X_{ji}$ 、 $Y_i$  を定義すると、式 (8) は、式 (11) の行列式の形に書くことができる。

【0048】

【数4】

$$X_{ji} = \sum_{p=0}^m x_{pi} \cdot x_{pj} \quad (9)$$

40

【0049】

【数5】

$$Y_i = \sum_{k=0}^m x_{ki} \cdot y_k \quad (10)$$

【0050】

50

## 【数6】

$$\begin{bmatrix} X_{11} & X_{12} & \dots & X_{1n} \\ X_{21} & X_{22} & \dots & X_{2n} \\ \dots & \dots & \dots & \dots \\ X_{m1} & X_{m2} & \dots & X_{mn} \end{bmatrix} \begin{bmatrix} W_1 \\ W_2 \\ \dots \\ W_n \end{bmatrix} = \begin{bmatrix} Y_1 \\ Y_2 \\ \dots \\ Y_m \end{bmatrix} \quad (11)$$

## 【0051】

式(11)が一般に正規方程式と呼ばれるものである。正規方程式加算回路29は、供給されるデータに基づいて式(9)、(10)に示すような演算を行うことにより、 $X_{ji}$ 、 $Y_i$  ( $i = 1, 2, \dots, n$ )をそれぞれ計算する。予測係数決定回路30は、掃き出し法等の一般的な行列解法に従って正規方程式(11)を解くことにより、予測係数 $w_i$  ( $i = 1, 2, \dots, n$ )を算出する。以上のような処理の結果として、統計的に最も真値に近い推定値を各クラス毎のフィールド倍速データ $y$ として推定するための予測係数が算出される。

## 【0052】

この発明は、上述したような学習を、複数の画素位置関係の各々について選択的に行うようにしたものである。この発明の一実施形態では、図4～図7を参照して上述した4種類の画素位置関係の何れに対しても、対応する予測係数を計算できるように構成されている。まず、図5および図7を参照して上述したような画素位置関係においては、入力する50Hz画像内の画素と、創造すべき100Hz画像内の画素との垂直方向の画素位置がずれている。かかる位置関係に対応した学習を行う際には、垂直間位相シフトフィルタ21は、供給される100Hzプログレッシブ画像に対して垂直方向の位相シフトを行う。

## 【0053】

一方、図4および図6を参照して上述したような画素位置関係においては、入力する50Hz画像内の画素と、創造すべき100Hz画像内の画素との垂直方向の画素位置が一致している。かかる位置関係に対応した学習を行う際には、垂直間引きフィルタ21は、位相シフトは行わず、供給される100Hzプログレッシブ画像をそのまま出力する。

## 【0054】

上述したようにして、画像情報変換の対象および結果である、50Hz画像および100Hz画像の間の複数種類の画素位置関係の内で、画像情報変換の結果として生成されるべき100Hz画像のとしてより高品質の画像が生成されるような学習を行うことが可能となる。

## 【0055】

また、予測係数を保持するためのメモリ容量等のハードウェア的な制約、ラインフリッカが許容されるか否か等の用途等に係る条件等に関連して最も好適な画素位置関係に対応する学習を選択的に行うことができる。これにより、より好適な画素位置関係を前提とするクラス分類適応処理を適用してフィールド倍速変換等の画像情報変換を行うことが可能となるので、総合的な変換性能を向上させることができる。

## 【0056】

上述したこの発明の一実施形態は、50Hz画像を100Hz画像に変換するフィールド倍速変換を行うものである。これに対して、学習時に、例えば垂直方向の位相シフト等を必要に応じて行うことによって教師画像、或いは生徒画像を生成することにより、インターレース画像をプログレッシブ画像に変換する、或いはSD画像をHD(High Definition)画像に変換する等の画像情報変換を行う場合等においても、この発明を適用することができる。すなわち、この発明は、ディジタル画像を、より画素数の多いディジタル画像に変換する画像情報変換全般において有効である。

## 【0057】

また、この発明の一実施形態は、100Hzのプログレッシブ画像と50Hzのインター

10

20

30

40

50

レース画像との間で学習を行うものであるが、学習に係る画像の組み合わせはこれに限定されるものではない。例えば、50Hzのプログレッシブ画像と25Hzのインターレース画像との間で学習を行うようにしても良いし、60Hzのプログレッシブ画像と30Hzのインターレース画像との間で学習を行うようにしても良い。

【0058】

また、上述したこの発明の一実施形態では、50Hz画像等の入力画像の空間波形を少ないビット数でパターン化するためにADRCを行うようにしている。これに対して、時空間内における画像パターンを少ないクラスで表現することに資するような情報圧縮方法であれば、ADRC以外の方法を用いるようにしても良い。例えば、DPCM(Differential Pulse Code Modulation)や、VQ(Vector Quantization)等の方法を用いるようにしても良い。

10

【0059】

この発明は、上述したこの発明の一実施形態に限定されるものでは無く、この発明の主旨を逸脱しない範囲内で様々な変形や応用が可能である。

【0060】

【発明の効果】

この発明によれば、生徒画像と教師画像との複数種類の組み合わせの内から何れかの組み合わせを選択し、選択した組み合わせの下で学習を行うことによって決定される予測係数を使用して予測演算を行うことができる。

【0061】

20

このため、画像情報変換の結果としてより高品質の画像が生成されるような学習を行うことが可能となる。

【0062】

また、予測係数を保持するためのメモリ容量等のハードウェア的な制約、ラインフリッカが許容されるか否か等の用途等に係る条件等に関連して最も好適な画素位置関係に対応する学習を行うことが可能となる。

【0063】

また、生徒画像と教師画像との組み合わせによって時間方向或いは空間方向の対称性が異なることに起因して、予測係数の種類数も異なるので、予測係数として記憶されるべきデータ量は、選択される生徒画像と教師画像との組み合わせによって異なる。このため、この発明を適用することにより、装置の仕様等において許容される予測係数用のメモリの容量等の条件により適合する画像情報変換を行うことができる。

30

【図面の簡単な説明】

【図1】この発明の一実施形態における画像情報変換に係る構成の一例を示すブロック図である。

【図2】クラスタップのタップ構造の一例を示す略線図である。

【図3】予測タップのタップ構造の一例を示す略線図である。

【図4】本願出願人の先の提案に係る画像情報変換における画素位置関係について説明するための略線図である。

【図5】この発明の一実施形態において用いることができる画素位置関係の一例について説明するための略線図である。

40

【図6】この発明の一実施形態において用いることができる画素位置関係の他の例について説明するための略線図である。

【図7】この発明の一実施形態において用いることができる画素位置関係のさらに他の一例について説明するための略線図である。

【図8】この発明の一実施形態における学習について説明するためのブロック図である。

【符号の説明】

21・・・垂直位相シフトフィルタ

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

---

フロントページの続き

(72)発明者 服部 正明

東京都品川区北品川6丁目7番35号 ソニー株式会社内

(72)発明者 宮井 岳志

東京都品川区北品川6丁目7番35号 ソニー株式会社内

審査官 菅原 道晴

(56)参考文献 特開平07-099635 (JP, A)

特開平08-275118 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H04N 7/00-7/01