(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6510637号

(P6510637)

(45) 発行日 令和1年5月8日(2019.5.8)

(24) 登録日 平成31年4月12日(2019.4.12)

(51) Int.Cl.

H02M 3/155 (2006.01)

H05B 37/02 (2006.01)

F 1

H02M 3/155

H02M 3/155

H05B 37/02E

P

J

請求項の数 12 (全 14 頁)

(21) 出願番号 特願2017-514258 (P2017-514258)

(86) (22) 出願日 平成27年3月12日 (2015.3.12)

(65) 公表番号 特表2017-521995 (P2017-521995A)

(43) 公表日 平成29年8月3日 (2017.8.3)

(86) 國際出願番号 PCT/US2015/020057

(87) 國際公開番号 WO2015/179006

(87) 國際公開日 平成27年11月26日 (2015.11.26)

審査請求日 平成29年10月19日 (2017.10.19)

(31) 優先権主張番号 62/002,417

(32) 優先日 平成26年5月23日 (2014.5.23)

(33) 優先権主張国 米国(US)

(31) 優先権主張番号 14/620,656

(32) 優先日 平成27年2月12日 (2015.2.12)

(33) 優先権主張国 米国(US)

(73) 特許権者 501105602

アレグロ・マイクロシステムズ・エルエル

シー

アメリカ合衆国ニューハンプシャー州03

103-3353, マンチェスター, ペリ

メーター・ロード955番

(74) 代理人 100140109

弁理士 小野 新次郎

(74) 代理人 100075270

弁理士 小林 泰

(74) 代理人 100101373

弁理士 竹内 茂雄

(74) 代理人 100118902

弁理士 山本 修

最終頁に続く

(54) 【発明の名称】スイッチングレギュレータ制御回路

## (57) 【特許請求の範囲】

## 【請求項 1】

安定化出力が L E D 負荷に提供される出力へ入力源からのエネルギーを移送するように導通するスイッチを備えたスイッチングレギュレータを制御するためのスイッチングレギュレータ制御回路であって、

前記スイッチの導通を制御するための制御信号を生成するように構成されており、基準信号に応答する第1の入力と、前記安定化出力に比例するフィードバック信号に応答する第2の入力と、前記制御信号が提供される出力とを有する回路であって、前記基準信号は前記安定化出力の変化率を制御するようにランプされる、回路と、

前記回路の前記出力において前記制御信号を受け取るように結合され、前記 L E D 負荷を調光するために PWM 信号に応答して前記制御信号を前記スイッチに選択的に結合するよう構成された論理回路であって、前記基準信号は前記 PWM 信号のエッジに応答してランプされ、前記安定化出力は電流であり、前記基準信号は前記安定化出力の減少率を制御するようにランプダウンされ、前記 PWM 信号は外部デジタル信号の遅延バージョンである、論理回路と、

を備えるスイッチングレギュレータ制御回路。

## 【請求項 2】

前記基準信号は、部分的にキャパシタによって確立されたレートでランプされる、請求項 1 に記載のスイッチングレギュレータ制御回路。

## 【請求項 3】

10

20

前記基準信号は、ユーザがプログラム可能なレートでランプされる、請求項1に記載のスイッチングレギュレータ制御回路。

**【請求項4】**

前記基準信号は、ユーザが選択したキャパシタンスに従ってランプされる、請求項3に記載のスイッチングレギュレータ制御回路。

**【請求項5】**

前記基準信号に、第1のソフトスタート時間間隔の間に第1の電流源によって確立された第1の増加率と、第2の時間間隔の間に第2の電流源によって確立された第2のより高速な増加率とが提供される、請求項1に記載のスイッチングレギュレータ制御回路。

**【請求項6】**

LEDを駆動するためのLED電流を提供するように構成され、スイッチを備えるスイッチングレギュレータにおいて、前記LEDを調光する方法であって、

基準信号とLED電流に比例するフィードバック信号とに応答して前記スイッチの導通を制御するための制御信号を生成するステップと、

PWM信号の立ち上がりエッジと立ち下がりエッジとのうちの関連する一方に応答して前記スイッチをオンに切り替え、前記PWM信号の前記立ち上がりエッジと前記立ち下がりエッジとのうちの他方に応答して前記スイッチをオフに切り替えるために、外部デジタル信号の遅延バージョンの形式のPWM信号に応答して前記制御信号を前記スイッチに選択的に結合するステップと、

前記LED電流の減少率を制御するように、前記基準信号をランプダウンさせるステップと、

を含む方法。

**【請求項7】**

前記LEDと直列に結合された第2のスイッチをリニアレギュレータとして動作させるために第2の制御信号を前記第2のスイッチに提供するステップをさらに含む、請求項6に記載の方法。

**【請求項8】**

前記LED電流は、ユーザがプログラム可能なレートでランプダウンされる、請求項6に記載の方法。

**【請求項9】**

前記LED電流がダンプダウンされる前記レートは、キャパシタンスの選択に従って選択可能である、請求項8に記載の方法。

**【請求項10】**

タイムアウト条件に応答して、前記LED電流のランプダウンを停止させるステップをさらに含む、請求項6に記載の方法。

**【請求項11】**

前記タイムアウト条件は、基準信号が所定の電圧レベル未満に下降することを含む、請求項10に記載の方法。

**【請求項12】**

安定化出力がLED負荷に提供される出力へ入力源からのエネルギーを移送するよう導通するスイッチを備えたスイッチングレギュレータを制御するためのスイッチングレギュレータ制御回路であって、

前記スイッチの導通を制御するための制御信号を生成するように構成されており、基準信号に応答する第1の入力と、前記安定化出力に比例するフィードバック信号に応答する第2の入力と、前記制御信号が提供される出力とを有する回路であって、前記基準信号は電流源及び電流シンクに結合され、前記基準信号は前記安定化出力の変化率を制御するようにランプされる、回路と、

前記回路の前記出力において前記制御信号を受け取るように結合され、前記LED負荷を調光するためにPWM信号に応答して前記制御信号を前記スイッチに選択的に結合するように構成された論理回路であって、前記電流源及び前記電流シンクは前記PWM信号に

10

20

30

40

50

よって制御され、前記安定化出力は電流であり、前記基準信号は前記安定化出力の減少率を制御するようにランプダウンされ、前記P W M信号は外部デジタル信号の遅延バージョンである、論理回路と、

を備えるスイッチングレギュレータ制御回路。

**【発明の詳細な説明】**

**【技術分野】**

**【0 0 0 1】**

[0001]本開示は、一般は、スイッチングレギュレータに関し、より詳しくは、スイッチングレギュレータ制御回路に関する。

**【背景技術】**

**【0 0 0 2】**

[0002]電力スイッチと称されることもあるスイッチを含み、A C又はD Cの電圧源又は電流源などの入力からのエネルギーを安定化出力( r e g u l a t e d o u t p u t )に移送するためのレギュレータ又はコンバータが広く知られている。スイッチングレギュレータと称されることもある一部のレギュレータにおいては、スイッチがオンオフして出力を調節する。リニアレギュレータと称されることもある他のレギュレータにおいては、スイッチは、その活性領域又は飽和領域で動作する。

**【0 0 0 3】**

[0003]一般的なスイッチングレギュレータ構成は、いくつかの例を挙げると、バック、ブースト、バックブースト、フライバック、S E P I C、C u k、ハーフブリッジ、及びフルブリッジを含む。やはり周知であるように、パルス幅変調(P W M)とパルス周波数変調(P F M)とを含む、電力スイッチの導通を制御するための様々な制御方法をスイッチングレギュレータに適用することが可能であり、これらの制御方法のそれぞれに対し、電圧モード制御と電流モード制御とを含む、様々なフィードバック及びフィードフォード技法が可能である。

**【0 0 0 4】**

[0004]スイッチングレギュレータは、直列及び/又は並列に結合された1つ又は複数のL E Dを含み得るL E D負荷を駆動するための安定化電流を提供するのに用いられることが多い。そのようなスイッチングレギュレータは、L E Dを選択的に調光することによって、L E Dの強度又は輝度を制御する。アナログ調光と称されることもある、あるタイプのL E Dの調光では、安定化L E D電流を調節することによって、L E Dの強度が調節される。アナログ調光は、基準信号とレギュレータ出力に比例するフィードバック信号とに応答して誤差信号を生成する誤差増幅器を利用することができ得る。そして、誤差信号は、スイッチの導通と、その結果生じる安定化電流とを制御するためのスイッチ制御信号を生成するのに用いられる。たとえば、誤差信号は、L E D電流を所望のレベルに安定化させるのに適したデューティサイクルでスイッチ制御信号を生成するために、ランプ(r a m p)信号と比較され得る。

**【0 0 0 5】**

[0005]P W M調光と称されることもある別のタイプのL E D調光では、L E Dの強度は、D C電流及び周波数(典型的には、1 0 0 H zから1 K H z)が固定されている可変デューティサイクルのP W M信号に応答してL E Dをオンオフさせることによって、調節される。P W M信号は、外部から提供されるか、又は、内部で生成され得る。

**【0 0 0 6】**

[0006]L E Dについては、多くの場合、アナログ調光よりもP W M調光が好まれるが、その理由は、P W M調光が、アナログ調光を用いるときに生じる可能性があるカラーシフトを最小化するからである。他方で、アナログ調光はP W M調光に比べて実装が複雑化しないことが可能であり、またP W M調光はL E D電流をパルス化し、それが、可視フリッカ、可聴ノイズ、又はE M I問題を生じさせ得る。

**【0 0 0 7】**

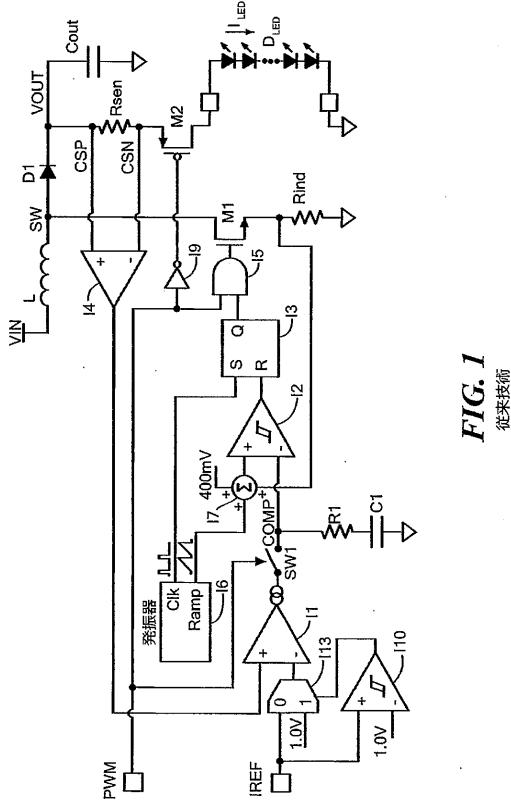

[0007]図1は、P W M調光とアナログ調光との両方を許容する電流モード制御を用いて

10

20

30

40

50

L E D 負荷を駆動する、ブーストレギュレータを図解している。アナログ調光は、外部ピン上の電圧に従って誤差増幅器（I 1）の基準を調節することにより達成される。図1に図解されているように、I R E F ピンは、電圧が1 . 0 V未満であるときに誤差増幅器の基準を制御するのに用いられる外部入力である。I R E F ピンが1 . 0 Vを超えるときには、コンパレータ1 1 0が、アナログマルチプレクサ（「m u x」）1 1 3の状態を変更し、誤差増幅器を、I R E F ピンに供給される電圧よりも正確であり得る内部基準で動作させる。この機能は、外部信号が内部基準未満であるときに、内部基準を無効にする追加的な正の入力を誤差増幅器（I 1）に加えることによって、実装されることがある。

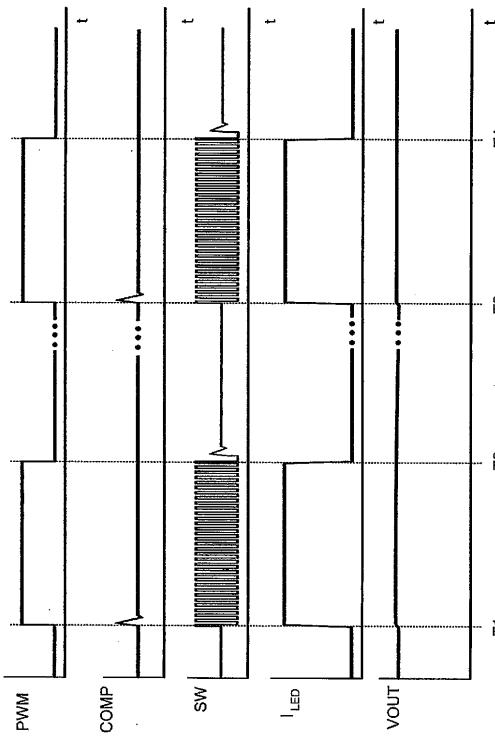

#### 【0 0 0 8】

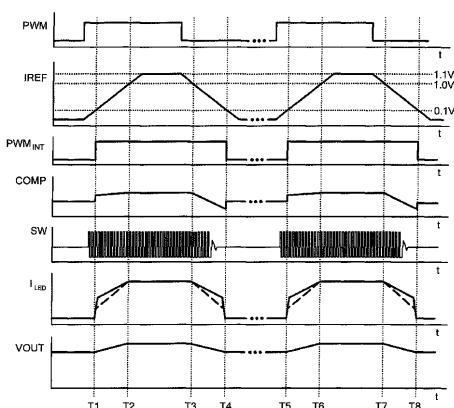

[0008] P W M 調光のためには、ユーザは、デジタルP W M 信号を図1のP W M ピンに供給することによって、L E D の強度を制御する。言及したように、いくつかのL E D レギュレータは、チップ上でのP W M 信号の生成を含む場合があり得るが、その場合は、ユーザが、P W M デューティサイクルに変換されるアナログ信号を供給する。図2の例示的な波形も参照すると、P W M 信号がローのときには、S W ノードは、A N D ゲート1 5がL E D 電流をディセーブルさせるトライステートである。さらに、多くのL E D レギュレータは、スイッチS W 1を導入することによって、C O M P ノードもトライステートにする。この技法によると、レギュレータがP W M 入力の立ち上がりエッジで再びイネーブルされると、制御ループが迅速に回復することが可能になる。スイッチS W 1が存在しない場合には、誤差増幅器（I 1）は、動作を再開するために、C O M P ノードをスルー（s l e w）させなければならないはずである。

10

20

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0 0 0 9】

[0009] L E D をさらに高速にオンオフさせるために、いくつかのレギュレータでは、図1のM 2によって図解されているように、L E D と直列でありP W M 入力によって駆動されるスイッチを導入する。M 2がない場合には、L E D 電流のターンオフ特性は指数関数的になるが、その理由は、L E D における動的抵抗がL E D のダイオード素子をオフにするのに十分なほど出力キャパシタ（C o u t）を放電するまで、C o u tがL E D に電流を供給し続けるからである。L E D における動的抵抗は、よりゆっくりと出力キャパシタを放電させるが、この結果として、ソフトなターンオフ特性と出力キャパシタの両端の小さな電圧リップルとが生じる。このソフトなターンオフ特性のために、低いデューティサイクルの場合は特に、P W M ピンのデューティサイクルとL E D の強度との間の関係が非線形になる。他方で、瞬間にL E D 電流をオンオフさせると、いくつかのシステムではE M I 問題が生じ得るが、その理由は、高速のエッジが、減衰させるのが困難である可能性がある高調波ノイズを、さらに高い周波数領域で生じさせるからである。この問題は、L E D ドライバとL E D との間に、図1に示されているように有線が存在するときに特に悪化するが、その理由は、その有線がE M I 放射のためのアンテナとして作用するからである。

30

#### 【課題を解決するための手段】

#### 【0 0 1 0】

40

[0010] スイッチングレギュレータ制御回路が、レギュレータの安定化出力の変化（すなわち、増加及び／又は減少）率を制御するようにランプされている基準信号に応答してレギュレータスイッチの導通を制御するための制御信号を生成するように構成された回路を含み、制御信号は、P W M 信号に応答してゲートされる。この構成を用いると、安定化出力がL E D 負荷を駆動するための安定化電流である適用例では、L E D は、P W M 信号に応答して、しかし、基準信号に応答したL E D 電流のランプ制御と共に、調光される。説明されている回路と技法を用いると、スイッチを瞬間にオンオフすることによって生じるE M I 及びその他の問題は、L E D をオンにするときにはL E D 電流をゆっくりとランプアップし、L E D をオフにするときにはL E D をゆっくりとランプダウンすることによって、十分に制御された態様で緩和される。たとえば、説明されている構成は、調光され

50

た後で L E D が再びオンにされるときに、制御ループのオーバーシュートを減少させる。説明されている回路と方法とは、優れた低いデューティサイクル性能を可能にしながら、E M I を減少させる。

#### 【 0 0 1 1 】

[0011] 機能は、以下のうちの 1 つ又は複数を含み得る。P W M 信号は、外部デジタル信号の遅延バージョンであり得る。安定化出力は、電流であり、基準信号は、安定化出力の減少率を制御するためにランプダウンされ得る。基準信号は、部分的にキャパシタによって確立されたレートで、及び / 又は、ユーザがプログラム可能なレートで、ランプされ得る。基準信号には、第 1 のソフトスタート時間間隔の間に第 1 の電流源によって確立された第 1 の増加率と、第 2 の時間間隔の間に第 2 の電流源によって確立された第 2 のより高速の増加率とが提供され得る。10

#### 【 0 0 1 2 】

L E D を調光する方法であって、P W M 信号の立ち上がりエッジと立ち下がりエッジとのうちの関連する一方に応答してスイッチをオンに切り替え、P W M 信号の立ち上がりエッジと立ち下がりエッジとのうちの他方に応答してスイッチをオフに切り替えるために、P W M 信号をスイッチに提供するステップを含む方法もまた説明される。L E D 電流は、スイッチをオフにすることに関連する立ち上がりエッジもしくは立ち下がりエッジの一方又は P W M 信号に応答して、ランプダウンされる。L E D 電流は、P W M 信号の遷移の後でスイッチのオフへの切り替えを遅延させることによって、ランプダウンされ得る。遅延は、基準信号と所定の閾値との交差に基づいて、確立され得る。基準信号は、部分的にキャパシタによって確立されたレートで、及び / 又は、ユーザがプログラム可能なレートで、ランプされ得る。ソフトスタート機能が、実装され得る。基準信号のランピングは、タイムアウト機能に従う。L E D 負荷と直列に結合された第 2 のスイッチは、基準信号に応答して、リニアレギュレータによって制御され得る。20

#### 【 0 0 1 3 】

[0012] 本開示自体に加え、以上の本開示の機能については、下記の図面に関する以下の詳細な説明から、より十分な理解を得ることができる。

#### 【 図面の簡単な説明 】

#### 【 0 0 1 4 】

【 図 1 】 [0013] 従来型のスイッチングレギュレータの回路図である。30

【 図 2 】 [0014] 図 1 のレギュレータと関連するいくつかの例示的な波形図である。

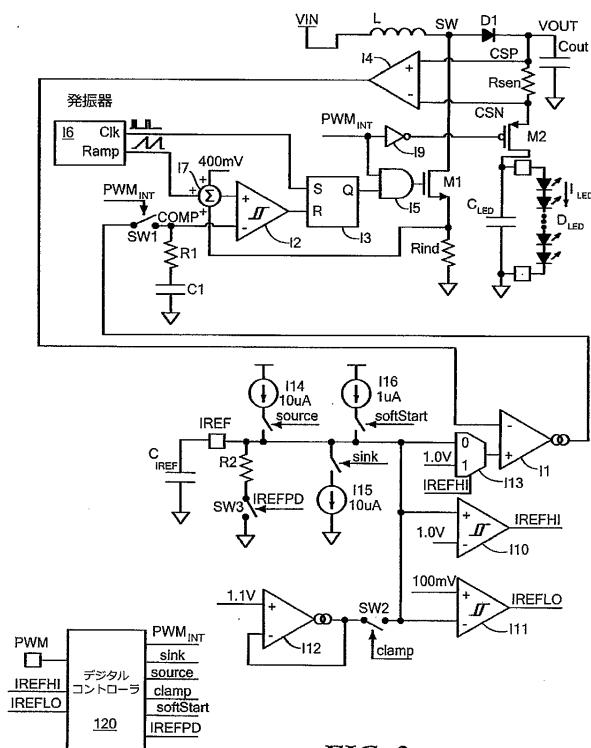

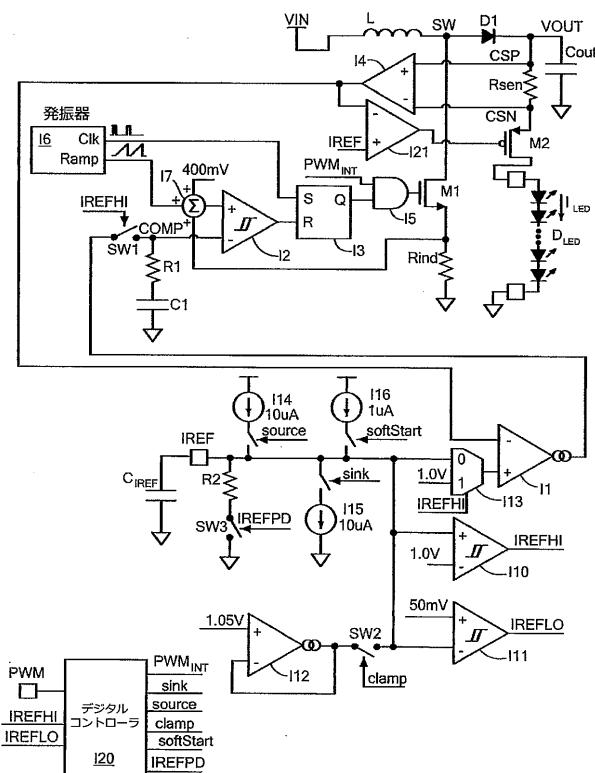

【 図 3 】 [0015] ランプ制御機能を備えた制御回路を有するスイッチングレギュレータの回路図である。

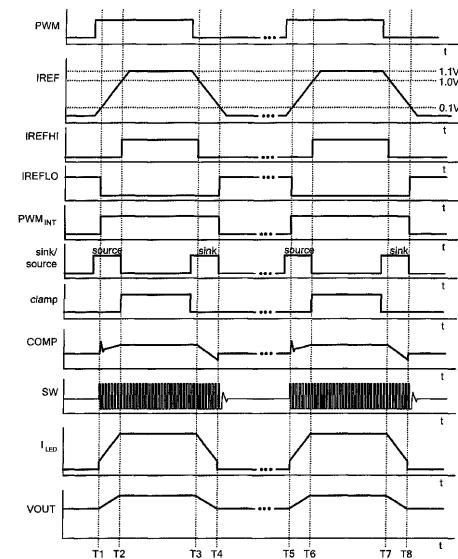

【 図 4 】 [0016] 図 3 のレギュレータと関連するいくつかの例示的な波形図である。

【 図 5 】 [0017] 図 3 のレギュレータと関連するいくつかの追加的な例示的な波形図である。

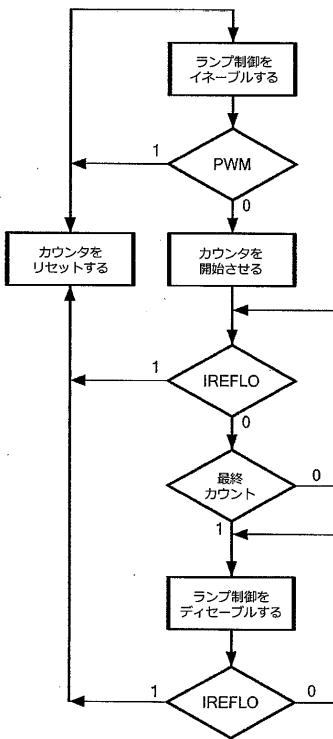

【 図 6 】 [0018] 図 3 のランプ制御機能のタイムアウトのための例示的なプロセスを示す流れ図である。

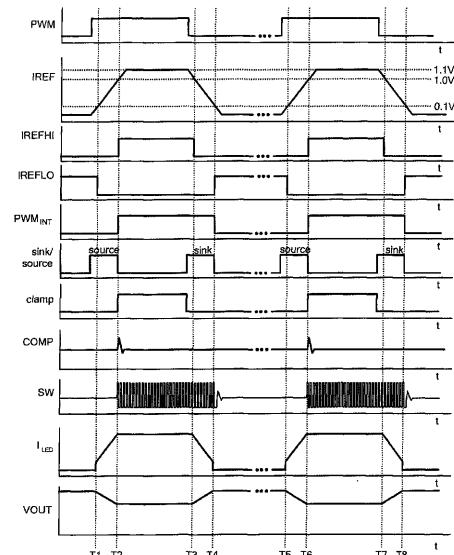

【 図 7 】 [0019] 別のランプ制御機能を含む制御回路を有するスイッチングレギュレータの回路図である。40

【 図 8 】 [0020] 図 7 のレギュレータと関連するいくつかの例示的な波形図である。

#### 【 発明を実施するための形態 】

#### 【 0 0 1 5 】

[0021] 図 3 を参照すると、入力源 V I N からのエネルギーを安定化出力が提供される出力へ移送するように導通するスイッチ M 1 を含むスイッチングレギュレータは、スイッチ M 1 の導通を制御するための制御信号を生成するように構成された回路であって、基準信号（たとえば、I R E F において提供される）に応答する第 1 の入力と、安定化出力（たとえば、I 4 によって提供される）に比例するフィードバック信号に応答する第 2 の入力と、制御信号が提供される出力とを有する回路を、さらに含む。I R E F 基準信号は、ランプ制御機能を実装するために、安定化出力 (I L E D ) の変化（すなわち、増加及び / 50

又は減少)率を制御するようにランプされる。レギュレータ制御回路は、この回路自体の出力に結合されており PWM<sub>INT</sub>信号に応答して制御信号をゲートする論理回路 I 5 を、さらに含む。

#### 【0016】

[0022]より詳しくは、レギュレータ制御回路は、IREF電圧をゆっくりとランプさせるための外部キャップ(C<sub>IREF</sub>)と共にIREFピンに結合された電流源(I14)と電流シンク(I15)とを含む。LED電流I<sub>LED</sub>は、後述されるように、電流源(I14、I16)又は電流シンク(I15)によって確立されたレートとキャパシタC<sub>IR</sub><sub>E</sub><sub>F</sub>の値とで、IREF電圧と共にゆっくりとランプすることになる。外部キャップC<sub>IREF</sub>を用いることにより、ユーザが、ランプレートを、典型的には10μから100μsのオーダーでプログラムすることが可能になる。IREFピンのシンク及びソース電流に加えて、レギュレータは、また、ランプ制御機能を形成するために、10%のIREF LOコンパレータ(I11)と、110%の高インピーダンスドライバ(I12)と、IREFプルダウン(SW3)と、デジタルコントローラI20とを含む。10

#### 【0017】

[0023]図3と関連する例示的な波形を示す図4も参照すると、ランプ制御機能は、PWM入力の立ち上がり及び立ち下がりエッジの後でのみ、アクティブである。PWM入力がローからハイになると、IREFピンは、0Vから始まり、IREFキャパシタンスとソースI14のソース電流(T1からT2)とによって決定されるレートで、内部基準(ここでは、1.0V)を超えてランプアップする。示されているように、LED電流I<sub>LED</sub>は、IREFピンの電圧をトラッキングして、IREF電圧と、共にゆっくりとランプアップする。20

#### 【0018】

[0024]IREFピンが1.0Vの内部基準を超えると、コンパレータI10がトリップして(すなわち、IREFHI=1)、マルチプレクサ113をトグルさせて、IREFピンから1.0Vの内部基準へとハンドオフ制御させる。デジタルコントローラを通じて、IREFHI信号は、また、ソース信号を用いてソース電流I14をディセーブルし、110%のドライバ(I12)をクランプ信号を用いてオンにする。これにより、IREFが1.0V基準より下まで低下しないことを保証しながら、1.0V基準をはるかに超えて十分に充電することが防止される。ドライバ(I12)は、10μAのオーダーのソース及びシンク能力だけを有する1.1V基準にバッファとして接続されたOTAを用いて、実装され得る。この高インピーダンスの駆動により、ユーザがドライバを容易に無効にして、アンテナ調光基準を設定するために基準IREFを1.0V未満にプルすることが可能になる。IREFピンがIREFHIコンパレータI10より下までプルされると、110%のドライバI12はスイッチSW2を用いてディセーブルされることに注意されたい。このシステムは、動作のアナログ調光モードを検出し、よりよい精度を提供するために、ソース及びシンク電流(I14及びI15)をディセーブルするようにも、設計され得る。30

#### 【0019】

[0025]図3及び図4に示されているように、PWM<sub>INT</sub>信号は、PWM<sub>INT</sub>の立ち上がりエッジで、SW動作を再開させ、LEDスイッチを閉じ(M2)、COMPスイッチ(SW1)を閉じる。しかし、ランプ制御機能の追加により、LEDスイッチが閉じられると(M2)、後でより詳細に説明される放電特性のために、LED電流は10%レベルにジャンプするだけである。図解されているように、時間T1で、SW、COMP、及びLEDの動作が再開され、ランプ制御機能が、IREFピンをゆっくりとランプアップさせ始め、その結果、LED電流(I<sub>LED</sub>)、LED電圧(V<sub>OUT</sub>)、及びCOMP電圧をゆっくりとランプアップさせる。40

#### 【0020】

[0026]PWM入力がハイからローになると、図4に示されているように、クランプがディセーブルされ、1.1Vの基準で始まるシンク電流(I15)でIREFピンが放電さ50

れ、次に、LED電流  $I_{LED}$  が、1.0VのハンドオフでREF電圧をトラッキングしながら、ランプダウンし始める。従来技術では、LEDスイッチ(M2)は、PWMの立ち下がりエッジで直ちにオフになるが、ランプ制御機能があると、LEDスイッチM2は、LED電流  $I_{LED}$  がランプダウンされている間、閉じられなければならない。この遅延は、 $PWM_{INT}$  信号を経由して、デジタルコントローラ(120)によって実装される。PWM入力の立ち下がりエッジの後では、 $PWM_{INT}$  信号は、REFピンの電圧が10%の閾値に達するまで(すなわち、REFLO信号が時間T4に遷移するまで)、ハイのままである。よって、 $PWM_{INT}$  信号がPWM入力における信号の遅延バージョンであることが明らかであり、遅延は、REFピンにおける電圧がPWM信号の立ち下がりエッジで(コンパレータI11によって確立された)10%の閾値に下がるのに要する時間に対応する、及び/又は、遅延は、REFピンにおける電圧がPWM信号の立ち上がりエッジで10%の閾値を超えるのに要する時間に対応する。 $PWM_{INT}$  の立ち下がりエッジ(T4)では、LEDスイッチ(M2)が開かれ、SW動作が停止され、COMPノードがスイッチSW1を用いてトライステートになる。COMPノードが、出力がアクティブでない間は制御ループ動作点を保存するためにトライステートになることにより、動作が再開すると、制御ループは非常に迅速に安定化を再開する。この場合、動作点は10%のレベルにあったので、動作もまた10%のレベルで再開する。

#### 【0021】

[0027]図4で論じられ図解されるように、ランプダウンの安定化(すなわち、REF電圧を経由した、LED電流  $I_{LED}$  の減少率の制御)は、REFピンがコンパレータI11によって確立された10%の閾値未満であるときには、停止される。この非ゼロの閾値が選択される理由は、LED電流がダンプダウンしているときには、出力キャパシタ(Cout)を放電させるために、システムがLED列に依存しているからである。電流がより減少するにつれて、LEDが出力キャパシタンスを放電させる能力は低下し、これにより、LED電流は、REFピンによって設定された基準よりも高いままになり得る。換言すると、図3のレギュレータはダイオードD1に起因して電流シンク能力をまったく有しておらず、したがって、LEDが放電され得る最速のレートは、CoutとLEDのV-I特性( $D_{LED}$ )とによって設定される。LEDの指数関数的なV-I特性のために、Coutが放電するレートは、電流と共に低下する。したがって、10%のターンオフ閾値は、LEDがREF電圧を近似的にトラッキングするために十分なシンク能力を依然として有するように、選択される。

#### 【0022】

[0028]レギュレータは、DCM(不連続導通モード)動作とSWノードの最小デューティサイクル限度とのために、極端に低いレベルまではLED電流を安定化できないため、10%での遮断は、PWM入力の立ち上がりエッジに対しても有益である。その理由により、10%は、また、制御ループがLED電流を容易に維持できる点としても選択される。図4に示されているように、制御は、ディセーブルされたのと同じレベル(10%)で再開されることが望ましい。これは、LED電圧(VOUT)がそのレベルまで放電され、COMPノードがそのレベルに設定されているからである。補償ネットワーク内でR1によって導入されたゼロのために、COMPノードは、 $PWM_{INT}$  の立ち上がり及び立ち下がりエッジにおいてステップ応答を有する、ということに注意されたい。COMPはスルーしているので、SW1が開くと消滅させられるR1の両端の間に電圧が生じる。コントローラが再びイネーブルされると、インダクタ電流を正しいレベルまでスルーするために、COMPノードは、いくらかのオーバーシュートを生じる。

#### 【0023】

[0029]制御ループがREFピンにおける低い電圧で安定化を維持できることを保証するために、レギュレータに軽い負荷の制御技法を含めることが望ましいことがあり得る。軽い負荷の制御技法のひとつとして、図3のI7における400mVのノードで示されているように、電流センス信号においてオフセットを導入することによって実装可能なパルススキッピングがある。したがって、SWノードは、COMP電圧が400mVの基準未

10

20

30

40

50

満まで低下すると、スイッチングを停止し、COMP電圧が400mVの台よりも上まで上昇すると、再開する。この技法は、パルス周波数変調やコンスタントオンタイムなど、他の軽い負荷制御技法と共に、当業者には広く理解されている。

#### 【0024】

[0030]図4に図解されているように、10%のIREFL0閾値の結果として、LEDスイッチ(M2)が開閉されると、LED電流に小さな10%のステップが生じる。このステップの大きさが小さいことにより、深刻なEMI問題を生じさせないはずである。しかし、LEDと並列に小さなキャパシタ(CLED)を追加することで、エッジレートを縮小させることが可能になる。このキャパシタ(CLED)は、Coutのキャパシタよりも、大きさが少なくとも1桁から数桁小さくなければならない。10

#### 【0025】

[0031]LEDドライバでは、PWM入力がLEDのPWM調光に直接的に対応することが重要であり、PWM調光は、光の強度の一次関数である。ほとんどの場合には、IREFランプは、より高いデューティサイクルでのLEDのオン時間と比較して僅かであるが、デューティサイクルが低い場合には、LEDのオン時間と比較して誤差項がはるかに深刻であるために、この要件を満たすことは特に困難かつ重要になる。ランプ制御機能を用いてこの要件を満たすために、制御回路は、ランプアップしている時の曲線の下の面積とランプダウンしている時の面積とを加算した面積を、制御機能が存在していない場合と同じ面積にするように設計されている。これを達成するためには、IREFピンのソース及びシンク電流(I14及びI15)は同一であってよく、相対的によい精度で実装され得る。10%のIREFL0機能によって導入された遅延をキャンセルするために、IREFドライバ(I12)基準は、基準ハンドオフ点(1.0V)よりも10%高くなるように選択される。この方法は、IREFドライバ(I12)が1.0Vの内部基準に対して正確であることに依存している。20

#### 【0026】

[0032]補償ネットワークによってCOMPピンに設定されるクロスオーバ周波数によっては、LED電流が、IREFピンを厳密にトラッキングしないことがあり得る。これは、高速のLED電流スルーレートが望ましいとき、又は、大きな出力キャパシタ(Cout)もしくは補償キャパシタ(C1)が用いられるときに、特に当てはまる。誤差増幅器の電流シンク及びソース能力もまた、IREF電圧をトラッキングする制御ループの能力に影響を与える。LED電流がIREFのランプレートに遅れる状況では、IREFピンのスルーレートは、所望のLED電流のランプレートが達成されるまで、調整されるべきである。図5は、システムが、高速のLED電流のスルーレートでどのように動作するかを図解しており、この図では、LED電流は、IREFピンを厳密にトラッキングしていない(予測されるLED電流が破線で示されている)。図解されているように、より高速のランプ及び/又はより低速の制御ループは、結果的に、PWM<sub>INT</sub>の立ち上がりエッジ及び立ち下がりエッジでのLED電流により大きなステップを生じさせる。30

#### 【0027】

[0033]高速のIREFピンのランプレートを用いてLED電流のトラッキングを改善するために、IREFH1=0の間に誤差増幅器の相互コンダクタンスを上昇させることによって達成され得るCOMPピンのより高速なスルーリングを提供するように、誤差増幅器が変更されることが可能であり、これによって、制御ループのクロスオーバ周波数を上昇させることになる。さらに、誤差増幅器のソース及びシンク能力が、変更され得る。フィードバック入力とIREF入力との差が大きくなりすぎると、COMPピンをスルーするために、大信号制御技法も用いられ得る。このアプローチと類似のものとして、開ループの態様でCOMPピンを単純にランプすることもあり得る。これらの方法は、デジタル制御ループを使用する場合にはさらに拡張され得る。40

#### 【0028】

[0034]ランプ制御機能が故障に対して堅牢でありアナログ調光又はPWM調光機能に悪影響を与えないことを保証するために、ランプ制御タイムアウト機能や他の類似の機能が50

実装され得る。タイムアウト機能は、IREFがランプダウンしているときに特に重要であり得るが、その理由は、ランプ制御機能は、IREFがIREFL0閾値を超えるまで、SWノードのトライステート化(M1の強制的なオフ)とLEDスイッチ(M2)の開放とを遅延させるからである。この遅延の結果、アナログ調光のためにDC信号を用いてIREF入力が駆動されるときに、PWM入力が無視されることになる。タイムアウトにより、PWM調光の間に、IREFピンを1.0V基準を超えるように駆動することによって、ユーザがランプ制御機能をディセーブルすることも可能になる。IREFピンを浮遊状態にしてもIREFピンの寄生キャパシタンスのためにランプ制御の影響は完全には消去できないため、ランプ制御機能が望ましくない場合に、これは有益である。

## 【0029】

10

[0035]図6は、例示的なランプ制御タイムアウト機能の動作の詳細を示している。ランプ制御タイムアウトは、PWMの立ち下がりエッジのみにおいてモニタされ、タイムアウトタイマは、PWM入力がローになると始動する。IREFがIREFL0閾値(IREFL0=1)と交差すると、タイマがリセットされ、ランプ制御動作は通常通りに継続する。そうではなく、IREFL0=1となる前にタイマが最終カウントに到達する場合には、ランプ制御機能がディセーブルされる。この機能は、IREF信号がIREFL0閾値よりも低く駆動されるまで、ディセーブルされたままである。IREFピンがもはや外部から駆動されなくなると、当然にランプ制御動作が再開するが、これは、PWM信号がローになると、シンク電流がIREFピンをランプするからである。

## 【0030】

20

[0036]ランプ制御機能をディセーブルするためには他の回路及び技法も用いられ得ることが認識されるであろう。たとえば、モードピンや、さらにはシリアルインターフェースなどの、他のピンが、ランプ制御機能を直接にディセーブルするために用いられることがあり得る。

## 【0031】

[0037]スタートアップ及びフォールト条件の間は、IREFピンは、スタートアップ状態に初期化される。これは、図3では、IREFピンをプルダウンするために、SW3とデジタルコントローラI20から来るIREFPD信号とを用いて、行われる。

## 【0032】

30

[0038]ランプ制御アーキテクチャは、図3に示されている実装例などのソフトスタート機能を含むのに適している。基準信号IREFには、第1のソフトスタート時間間隔の間にソフトスタート機能を実装するために、電流源I16によって確立された第1の増加率(すなわち、第1のレートでのランプアップ)が提供され、第2の時間間隔の間にランプ制御機能を実装するために電流源I14によって確立された第2のより高速の増加率が提供される。それぞれの電流源制御信号(ソース及びソフトスタート)は、示されているように、デジタルコントローラによって提供される。

## 【0033】

[0039]この例示的な実施形態では、ランプ制御機能は、10μAのシンク及びソース電流(I14及びI15)を用いて実装され、他方で、ソフトスタートランプは、1μAの電流源(I16)を用いて実装される。この結果、ランプ制御レートよりも10倍遅いソフトスタートランプが生じる。他のレートが用いられることもあり得る。スタートアップの際、第1の時間間隔の間、UVLO(under voltage lock out)故障が解消した後、又は任意の他の故障の後で、IREFプルダウン(SW3)がリリースされ、1μAのソフトスタート電流(I16)が、ランプ制御電流源(I14及びI15)がディセーブルされた状態で、IREFピンを充電するのに用いられる事になる。IREFピンがIREFHI閾値と交差した後に開始する第2の時間間隔の間には、ソフトスタート機能がディセーブルされ、ランプ制御ドライバと電流源とが、上述されたように、再び関わることになる。

## 【0034】

[0040]図3は、誤差増幅器I1の基準を単にランプすることによって、ソフトスタート

40

50

機能を実装する。その両端に数Vの電位差が存在しない限りLEDは電流を導通させないという事実のために、電流センス電圧(CSP-CSN)は、VOUTが数Vに達するまで、ゼロのままである。結果的に、0Vの電流センス電圧(CSP-CSN)はソフトスタートランプをトラッキングしていないので、誤差増幅器は、COMPピンを可能な限り強く駆動することになる。この結果として、LEDが最終的に導通を開始すると、いくつかのオーバーシュートが生じ得る。幸運なことに、このオーバーシュートは、非常に小さなLED電流で生じ、その時点で、LED電流は、ソフトスタートランプのトラッキングを開始する。他のソフトスタート回路及び技法もまた可能である。一例は、LEDが導通を開始するまで、誤差増幅器のフィードバック信号を、電流センス増幅器I4からVOUTの両端の抵抗分割器に変更するものである。

10

### 【0035】

[0041]ランプ制御機能は、提示されている回路及び技法に加えて、もしくは、提示されている回路及び技法の代わりに、他の回路並びに/又は技法を用いても、実装され得る。追加的な一技法が図7に図解されており、この技法によると、PMOSであるLEDスイッチ(M2)が、増幅器I21の追加により、リニアレギュレータとなる。リニアレギュレータ(I21及びM2)の基準は、IREF信号である。このリニアレギュレータ技法は、先に説明されたLEDストリングが出力キャパシタ(Cout)を放電するという制約を受けないが、その理由は、M2が、Coutの両端の間の電圧とは独立にLED電流を制御することができるからである。したがって、図7では、IREFL0の閾値は、より高性能であるこの技法を利用するため、5%(50mV)に変更されている。さらに、ドライバI12のための基準は、遅延を適切に消去するために、105%(1.05V)に変更されている。回路における誤差に寛容であるように非ゼロのIREFL0閾値を用い、リニアレギュレータの設計要件を緩和することは依然として有益であることに注意されたい。

20

### 【0036】

[0042]図7においてなされているように、LED電流を安定化させるために追加的な制御ループを加えるときには、複数のループが否定的に相互作用しないことが重要である。この場合に、スイッチングレギュレータは、リニアレギュレータI21の電流の必要性をサポートするため、端的に、十分な電流を供給しなければならない。図7及び図8に示されているように、この要件は、IREFHI信号を用いてCOMPピンをトライステートにすることによって満たされ、それにより、あたかもLEDが十分な安定化電流をシンクし続けているように、スイッチングレギュレータが動作し続けることになる。結果的に、LED電流をダンプダウンするときには、図8に図解されているように、出力キャパシタが過剰電流を用いて充電されるにつれて、出力電圧(VOUT)が上昇する。次に、LED電流がランプアップされると、図8に示されているように、PWMINT信号をシフトすることによってスイッチングレギュレータがディセーブルされ、それにより、LED電流がランプアップされているため、出力キャパシタ(Cout)における過剰充電が使い尽くされる(deplete)。IREF電圧が1.0Vのハンドオフポイントを超えると、リニアレギュレータは、自然に、LEDスイッチ(M2)をトライオード領域に駆動するが、その理由は、スイッチングレギュレータが、リニアレギュレータによって要求されるよりも少ない電流を供給することによって、安定化を引き受けるからである。

30

### 【0037】

[0043]設計が誤差に対して堅牢であることを保証するために、スイッチングレギュレータがすべての場合に対して十分な電流を提供することが保証されるように、誤差増幅器(I1)の基準とリニアレギュレータとの間にオフセットを追加することが有益であり得る。スイッチングレギュレータがリニアレギュレータに十分な電流を提供することを保証するためには、電流センス増幅器(I4)から、レギュレータへの出力電圧VOUTが安定化ポイントよりも上のレベルにあることをモニタする抵抗分割器への誤差増幅器フィードバックを多重化するなど、他の技法も用いられ得る。

40

### 【0038】

50

[0044]本明細書で引用されているすべての参考文献は、参照により、それらの全体が本明細書に組み込まれる。

[0045]本発明の好ましい実施形態について述べてきたが、当業者には、これらの概念を組み込む他の実施形態を用いることができるようになる。提案されるランプ制御回路及び技法は、これらに限定されないが、バック、ブースト、バックブースト、S E P I C、C u k、ハーフブリッジ、フルブリッジ、及びリニアレギュレータを含む、任意のリニア又はスイッチングレギュレータのトポロジに適用され得ることが認識されるであろう。さらに、説明されている回路及び技法は、混合信号システムに限定されることはなく、デジタルアナログコンバータや、I R E F ピンにおける電流源と外部キャパシタとを置き換える充電ポンプなど、デジタル、アナログ、又はソフトウェアによる方法を用いて適用され得る。I R E F ピンのレートは、入力電圧、出力電圧、光の強度、又は任意の他の固定もしくは可変パラメータなど、他のパラメータによって定義され得る。ランプアップ及びランプダウン特性は、線形であることを必要とせず、たとえば、指数関数的な特性や、又は、所望の場合には形状に不連続性さえも有することがあり得る。説明されている回路及び技法は、電流モード制御（論じられ例示されたような）、電圧モード制御、コンスタントオンタイム制御、コンスタントオフタイム制御、又は任意の他のアナログ及び／もしくはデジタル制御方式を含む任意の制御ループを用いて、実装され得る。さらに、提案されている回路及び技法は、電流を安定させるレギュレータにおける適用に限定されることではなく、電圧、電力、又は他のパラメータを代わりに安定させるレギュレータにも適用され得る。さらに、本明細書で説明されているタイプのレギュレータは、ランプ制御機能を用いる本明細書で説明されている調光と共に、及び／又はそのような調光に加えて、他の調光モードでも動作し得ることが認識されるだろう。10

20

#### 【 0 0 3 9 】

[0046]したがって、これらの実施形態は、開示されている実施形態に限定されるべきでなく、むしろ、添付の特許請求の範囲の精神及び範囲によってのみ限定されるべきである。

【図1】

FIG. 1

従来技術

【図2】

FIG. 2

従来技術

【図3】

FIG. 3

【図4】

FIG. 4

【図5】

FIG. 5

【図6】

FIG. 6

【図7】

FIG. 7

【図8】

FIG. 8

---

フロントページの続き

(74)代理人 100147991

弁理士 鳥居 健一

(72)発明者 ウィッパン, ジョジュア

アメリカ合衆国ミネソタ州55112, ニュー・ブライトン, エイティーンス・アベニュー, ノースウェスト 1782

(72)発明者 キンバー, カート

アメリカ合衆国ミネソタ州55417, ミネアポリス, サーティフィフス・アベニュー・サウス 4811

(72)発明者 トッド, ピーター

イギリス国 エдинバラ, ローティアン イーエイチ15・1エヌワイ, ダーラム・ロード 1

9

審査官 宮本 秀一

(56)参考文献 特開2013-132107(JP, A)

特開2011-243787(JP, A)

特開2011-233260(JP, A)

(58)調査した分野(Int.Cl., DB名)

H02M3/00 - 3/44

H05B37/00 - 39/10