# (19) 대한민국특허청(KR) (12) 특허공보(B1)

(51) Int. CI.<sup>5</sup> H03L 7/00 (45) 공고일자 1992년09월21일

(11) 공고번호 특1992-0008049

| (21) 출원번호<br>(22) 출원일자 | 특 1984-0003310<br>1984년 06월 13일                 | (65) 공개번호<br>(43) 공개일자 | 특 1985-0000155<br>1985년02월25일 |

|------------------------|-------------------------------------------------|------------------------|-------------------------------|

| (30) 우선권주장<br>(71) 출원인 | 83-106257 1983년06월14일<br>소니 가부시끼가이샤 오요          |                        |                               |

|                        | 일본국 도오꾜도 시나가와꾸                                  | 기다시나가와 6쬬메 7번          | 발 35고<br>-                    |

| (72) 발명자               | 오다까 겐따로<br>일본국 도오꾜도 시나가와꾸<br>끼가이샤 나이<br>후까미 다다시 | 기다시나가와 6죠메 7번          | 반 35고 소니 가부시                  |

일본국 도오꾜도 시나가와꾸 기다시나가와 6죠메 7반 35고 소니 가부시

끼가이샤 나이 오자끼 신야

일본국 도오꾜도 시나가와꾸 기다시니가와 6죠메 7반 35고 소니 가부시

끼가이샤 나이

(74) 대리인 이병호

심사관 : 이택수 (책자공보 제2954호)

## <u>(54) 동기회로</u>

## 요약

내용 없음.

## 叫丑도

### 명세서

[발명의 명칭]

동기회로

[도면의 간단한 설명]

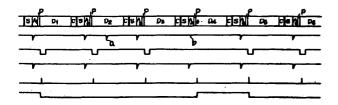

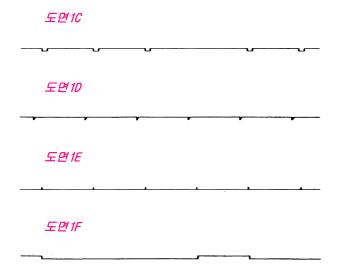

제1a도 내지 제1f도는 본 발명의 설명도.

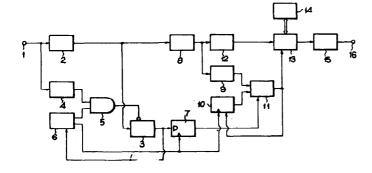

제2도는 본 발명 일예의 블럭도.

\* 도면의 주요부분에 대한 부호의 설명

1 : 입력단자 2 : 복조회로

3 : 어드레스신호 및 에러검출신호 검출회로 4 : 동기신호 검출회로

6 : 타이밍신호 발생수단 9 : 어드레스신호 검출회로

10 : 내삽 어드레스신호 발생회로 11 : 절환회로

[발명의 상세한 설명]

본 발명은, 예를 들면 PCM 복조장치에 사용하는데 적합한 동기회로에 관한 것이다.

예를 들면, 헬리컬 스캔형의 회전헤드를 사용하여, 이 회전헤드 드럼의 90도에 테이프를 감고, 음성 신호의 PCM 데이타를 시간축 압축하여, 헤드가 90도 범위의 테이프에 대접하는 기간마다 기록하도록 한 장치가 제한되어 있다.

그런데 이와 같은 장치의 경우에, 신호의 시간축이 압축되로, 재생때, 간헐적으로 인추되도록 되어 있으므로 정확한 동기를 취하는 것이 매우 곤란하다.

한편 변속 재생등의 특수 재생 때에는, 데이타도 간헐적으로 되기 때문에, 동기를 취한다는 것은 더욱 곤란하게 된다.

그래서 데이타신호의 소정 비트수의 블럭마다 동기신호와 함께 어드레스신호를 부가하는 것을 생각하게 되었다. 이것에 의하면, 재생때 어드레스신호를 검출하여 정확한 동기를 취할 수가 있다.

그런데 이 경우에 어드레스신호도 데이타신호와 동일하게 에러 정정 등의 대책을 행할 필요가 있다. 그 경우에 종래는 어드레스신호와 데이타신호를 함께하여 에러 정정 코드를 부가하고 있었다.

그렇지만 이 방법에서는, 어드레스신호 및 데이타신호의 전체에 에러 정정 코드가 걸려있기 때문에, 데이타신호만을 인터리브하여 정정 능력을 높일 수가 없다. 혹은 인터리블 행하기 위해서는 어드레 스신호도 함께 기억하지 않으면 안되고, 메모리가 대용량 필요하게 되어 버린다.

또 어드레스신호의 정확성 여부를 판단하기 위하여 1블럭의 전체를 보지 않으면 안되고, 이것 때문에 이때만이 1 블럭분의 메모리가 필요하게 된다. 더우기 PCM 데이타 부분이 정확하여도, 어드레스부분이 잘못된 경우에 1 블럭 전체가 잘못되버리는 등의 문제가 있었다.

본 발명은 이와 같은 점을 비추어보아, 간단한 구성으로 정확한 동기가 취할 수 있도록 하는 것이다.

본 발명은, 데이타신호가 소정의 비트마다 분할되고, 이 분할마다 동기 신호와 임의의 어드레스신호 와 이 어드레스신호의 에러검출 비트가 부가된 신호를 전송하고, 재생시, 상기 동기신호를 검출함과 동시에 상기 어드레스신호의 에러를 검출하고, 상기 어드레스신호가 정확할 때 내삽 동기신호원을 구동하고, 상기 검출된 동기신호와 상기 내삽 동기신호에 의하여 상기 어드레스신호의 에러검출회로 를 구동하고, 상기 내삽 동기신호에서 내삽 어드레스신호 발생회로를 구동하고, 상기 어드레스신호 의 정확성 여부에 따라서 상기 어드레스신호의 재생신호와 상기 내삽 어드레스신호를 절환하여 꺼내 어지게 되도록 한 동기회로이고, 이것에 의하면 간단한 구성으로 정확한 동기를 취할 수가 있다.

제1a도는 전송되는 신호를 도시하고, S는 동기신호이며, 이 동기신호(S)후에 어드레스신호(A), 어드레스신호(A)의 에러검출 비트(P), 데이타신호(D), 데이타신호(D)의 에러 정정 코드(C)가 계속되어 일련의 신호로 되고, 이 신호가 순차 전송된다. 그리고 동기신호에는, 본래 데이타신호중에 존재치 않은 금지 패턴등이 사용된다.

다음에 제2도는 동기회로를 포함하는 재생장치의 블럭도이고, 입력단자 (1)에 상기의 신호가 예를 들면 NRZ 변조된 RF신호로 공급된다. 이 신호가 복조회로(2)에 공급되어서 "1""0"의 코드신호로된다. 이 코드신호가 어드레스신호의 에러 검출회로(3)에 공급된다.

또 입력단자(1)로부터 RF신호가 동기신호의 검출회로(4)에 공급된다. 여기서 상기의 금지 패턴등을 사용함에 의하여, 동기신호(S)는 RF신호로부터 예를 들면 제1b도에 도시하는 바 같이 직접 검출된다 이 동기신호(S)가 앤드회로(5)를 통하여 검출회로(3)의 리세트 단자에 공급된다. 그리고 이 검출회로(3)에서, 어드레스신호(A) 및 에러검출 비트(P)를 사용하여 어드레스신호의 정확성이 판별되고, 제1c도에 도시하는 것과 같은 정확할때 로우 레벨로 되는 신호가 형성된다.

이 신호가 내삽 동기신호원(6)으로 공급되어서, 제1d도에 도시하는 바 같은 동기신호가 형성되고, 이 신호가 앤드회로(5)에 공급된다. 또 이 내삽 동기신호원(6)에서 제1e도에 도시하는 바 같이 검출비트(P) 직후의 타이밍으로서 클럭신호가 형성된다.

다시 검출회로(3)로부터의 신호가 D 플립플롭(7)의 D단자에 공급되고, 신호원(6)으로부터의 클럭신호가 클럭단자에 공급되어서, 제1f도에 도시하는 바 같은 신호가 형성된다.

한편 복조회로(2)로부터의 코드신호가 직병렬 변환회로(8)에 공급되고, 변환된 신호의 어드레스신호 (A)부분이 어드레스 검출회로(9)에 공급된다. 또 신호원(6)으로부터의 클럭신호가 내삽 어드레스신호 발생회로(10)에 공급되어서 내삽 어드레스신호가 형성된다. 이 검출된 어드레스신호와 내삽 어드레스신호가 절환회로(11)에 공급되고, 플립플롭(7)으로부터의 신호에서 로우일때 검출회로(9)로부터의 어드레스신호, 이하일때 발생회로(10)로부터의 내삽 어드레스신호가 꺼내어진다. 이 꺼내어진 어드레스신호가 내십 어드레스 발생회로(10)에 공급된다.

또 직병렬 변화회로(8)로부터의 신호의 데이타신호(D) 및 에러 정정 코드(C)의 부분이 데이타 검출회로(12)에 공급된다. 이 데이타신호(D) 및 에러 정정 코드(C)의 부분이 데이타 검출회로(12)에 공급된다. 이 데이타신호(D) 및 에러 정정 코드(C)가 RAM(13)에 공급됨과 함께, 상기의 전환회로(11)로부터의 어드레스신호가 메모리(13)에 공급되고, 이 어드레스신호에 따라서 기록이 행하여진다. 이메모리(13)에 기록된 신호가 에러 정정회로(14)에서 오차가 정정되고, 소정의 타이밍으로 판독되고, DA 변환회로(15)로 아날로그화 되어서 출력단자(16)에 인출된다.

이렇게 하여 재생이 행하여지는 것이지만, 이 장치에 의하면 동기신호(S)의 직후에 어드레스신호(A)와 에러검출 비트(P)가 설치되고, 이 정확성이 검출되기 때문에, 예를 들면 제1a도에 도시한 바같이 데이타신호(D)의 오차 등에 의하여 동기신호가 잘못 검출되어도, 어드레스신호에 대응하는 부분이 에어라데 의하여 배제된다. 또 내삽 동기 신호원(6)이 설치되어 있기 때문에 제1b도에 도시하는 바와 같이 동기신호(S)가 에러등에 의하여 검출되지 않았던 경우에 이것이 내삽되고, 다시 내삽 어드레스신호 발생회로(10)가 설치됨에 의하여 이 어드레스신호(A)가 내삽되어서, 동기신호(S) 및 어드레스신호(A)만이 잘못되었을 경우에도 데이타신호(D)를 활용할 수가 있다. 즉 동기신호(S)를 매

우 정확하게 검출할 수가 있다.

또 이 경우에 어드레스신호(A)의 직후에 에러검출 비트(P)가 설치되어 있기 때문에, 에러검출을 위한 메모리는 매우 소용량으로서 족하다.

그리고 종래의 어드레스신호의 에러검출이 행하여지지 않았을 경우에는, 틀린 어드레스에 의하여 부정한 어드레스에 데이타가 기록되고, 정확한 데이타가 파괴되는 일때문에, 에러율이 2배로 악화하는

그런 그런 이 예상되었으나, 이 장치에 의하면, n비트의 검출 비트를 설치됨에 의하여, 에러율을  $2^{n}-1$ 의 악화로 멈추게 할 수 있고, 예를 들면 n=4로 하여서 악화는 7%이하로 할 수가 있다.

또 변속 재생때, 내삽 어드레스 발생회로(10)에서 속도에 맞춘 연산을 행하든가, 기록 정지신호를 형성함에 의하여, 변속 재생때의 오동작의 방지를 할 수도 있다.

본 발명에 의하면, 간단한 구성으로 정확한 동기를 취할 수가 있게 되었다.

#### (57) 청구의 범위

### 청구항 1

전송 매체를 경유하여 전송되도록 각기 동기신호, 어드레스신호 및 상기 어드레스신호를 위한 에러 검출신호를 포함하는 신호 블럭으로 소정 비트수마다 분할되는 데이타신호를 재생하기 위한 동기회로에 있어서, 상기 전송된 데이타를 수신하기 위한 입력단자(1)와, 상기 전송된 데이타로부터 동기신호를 검출해내는 수단(4)과, 상기 전송된 데이타로부터 어드레스신호 및 에러검출신호를 검출해내는 수단(3)과, 상기 에러검출신호를 사용하므로써 상기 어드레스신호의 에러를 검출하고 상기 어드레스신호가 정확한 것으로 판정될때 검출신호를 발생시키는 수단(3)과, 상기 검출수단(3)으로부터 상기 검출신호와 동기하여 타이밍신호를 발생시키는 수단(6), 및 상기 발생수단(6)에 대해 상기 타이밍신호와 동기하여 상기 데이타신호를 처리하는 수단(7.9,10.11.13)을 포함하는 동기회로.

#### 청구항 2

제1항에 있어서, 상기 데이타신호 처리수단(7,9,10,11,13)이 상기 데이타신호를 기억시키는 메모리수단(13) 및 상기 메모리수단(13)을 액세스하기 위한 어드레스신호를 발생시키는 수단(9,10,11)을 포함하는 것을 특징으로 하는 동기회로.

#### 청구항 3

제2항에 있어서, 상기 어드레스신호 발생수단(9,10,11)이 상기 전송된 데이타로부터 상기 어드레스 신호를 검출하는 수단(9), 내삽 어드레스신호를 발생시키는 수단(10) 및 상기 검출신호가 상기 어드 레스신호의 에러 상태를 나타내는지 여부에 따라 상기 메모리수단(13)에 의해 상기 어드레스신호 및 상기 내삽 어드레스신호를 선택적으로 제공하는 수단(11)을 포함하는 것을 특징으로 하는 동기회로.

#### 청구항 4

제1항에 있어서, 상기 타이밍신호 발생수단(6)이 상기 검출신호와 동기하여 내삽 동기화신호를 발생 시키고 상기 검출수단(3)이 동기신호 및 내삽 동기신호에 의해 리셋트되는 것을 특징으로 하는 동기 회로.

## 청구항 5

제1항에 있어서, 상기 데이타신호가 펄스 코드 변조 오디오신호인 것을 특징으로 하는 동기회로.

#### 청구항 6

제1항에 있어서, 상기 데이타신호가 헬리컬 스캔형의 회전헤드에 의해 기록되고 재생되는 것을 특징으로 하는 동기회로.

#### 청구항 7

제1항에 있어서, 상기 데이타신호가 시간축 압축되고, 간헐적으로 기록 및 재생되는 것을 특징으로 하는 동기회로.

## 도면

#### 도면1A

##

## **도면1**8

# 도면2