(19)

Bundesrepublik Deutschland

Deutsches Patent- und Markenamt

(10) DE 698 37 722 T2 2008.01.10

(12)

## Übersetzung der europäischen Patentschrift

(97) EP 1 038 360 B1

(21) Deutsches Aktenzeichen: 698 37 722.2

(86) PCT-Aktenzeichen: PCT/US98/26053

(96) Europäisches Aktenzeichen: 98 960 824.5

(87) PCT-Veröffentlichungs-Nr.: WO 1999/030427

(86) PCT-Anmeldetag: 08.12.1998

(87) Veröffentlichungstag

der PCT-Anmeldung: 17.06.1999

(97) Erstveröffentlichung durch das EPA: 27.09.2000

(97) Veröffentlichungstag

der Patenterteilung beim EPA: 02.05.2007

(47) Veröffentlichungstag im Patentblatt: 10.01.2008

(51) Int Cl.<sup>8</sup>: H04B 1/10 (2006.01)

H03M 1/18 (2006.01)

(30) Unionspriorität:

987853 09.12.1997 US

(84) Benannte Vertragsstaaten:

DE, ES, GB, IT, SE

(73) Patentinhaber:

Qualcomm Inc., San Diego, Calif., US

(72) Erfinder:

YOUNIS, Saed G., San Diego, CA 92130, US;

BAZARJANI, Seyfollah S., San Diego, CA 92130,

US; CICCARELLI, Steven C., Encinitas, CA 92024,

US

(74) Vertreter:

WAGNER & GEYER Partnerschaft Patent- und

Rechtsanwälte, 80538 München

(54) Bezeichnung: EMPFÄNGER MIT PROGRAMMIERBAREN DYNAMIKBEREICH

Anmerkung: Innerhalb von neun Monaten nach der Bekanntmachung des Hinweises auf die Erteilung des europäischen Patents kann jedermann beim Europäischen Patentamt gegen das erteilte europäische Patent Einspruch einlegen. Der Einspruch ist schriftlich einzureichen und zu begründen. Er gilt erst als eingelebt, wenn die Einspruchsgebühr entrichtet worden ist (Art. 99 (1) Europäisches Patentübereinkommen).

Die Übersetzung ist gemäß Artikel II § 3 Abs. 1 IntPatÜG 1991 vom Patentinhaber eingereicht worden. Sie wurde vom Deutschen Patent- und Markenamt inhaltlich nicht geprüft.

**Beschreibung**

## Hintergrund der Erfindung

## I. Gebiet der Erfindung

**[0001]** Die vorliegende Erfindung bezieht sich auf Kommunikationen. Genauer bezieht sich die vorliegende Erfindung auf einen neuartigen und verbesserten programmierbaren Empfänger mit dynamischem Bereich.

## II. Beschreibung des Standes der Technik

**[0002]** Der Entwurf eines Empfängers mit großer Performance ist eine Herausforderung aufgrund mehrerer Entwurfseinschränkungen. Erstens erfordern viele Anwendungen eine große Performance. Eine große Performance kann beschrieben werden durch die Linearität der aktiven Geräte (Verstärker, Mischer etc.) und durch den Rauschfaktor des Empfängers. Zweitens ist der Energieverbrauch für einige Anwendungen wie in einem zellularen Kommunikationssystem eine wichtige Betrachtung wegen der tragbaren Natur des Empfängers. Im allgemeinen sind eine große Performance und eine große Effizienz konkurrierende Betrachtungen des Entwurfs.

**[0003]** Ein aktives Gerät hat die folgende Transferfunktion:

$$y(x) = a_1 \cdot x + a_2 \cdot x^2 + a_3 \cdot x^3 + \text{higher order terms} \quad (1)$$

wobei x das Eingabesignal, y(x) das Ausgabesignal und  $a_1$ ,  $a_2$  und  $a_3$  Koeffizienten sind, die die Linearität des aktiven Gerätes definieren. Der Einfachheit halber werden Terme höherer Ordnung (z.B. Terme über dritter Ordnung) ignoriert. Für ein ideales aktives Gerät sind die Koeffizienten  $a_2$  und  $a_3$  0,0 und das Ausgabesignal ist einfach das Eingabesignal, das mit  $a_1$  skaliert ist. Alle aktiven Geräte jedoch erfahren einem gewissen Betrag an Nichtlinearität, die durch die Koeffizienten  $a_2$  und  $a_3$  quantifiziert wird. Der Koeffizient  $a_2$  definiert den Betrag der Nichtlinearität zweiter Ordnung und der Koeffizient  $a_3$  definiert den Betrag der Nichtlinearität dritter Ordnung.

**[0004]** Die meisten Kommunikationssysteme sind Schmalbandsysteme, die auf einem Eingabe-HF-Signal arbeiten, das eine vorbestimmte Bandbreite und eine Mittenfrequenz bzw. zentrale Frequenz besitzt. Das Eingabe-HF-Signal umfasst typischerweise andere Störsignale, die über das gesamte Frequenzspektrum angeordnet sind. Die Nichtlinearität innerhalb des aktiven Gerätes verursacht die Intermodulation der Störsignale, was darin resultiert, dass deren Produkte in das Signalband fallen können.

**[0005]** Die Wirkung der Nichtlinearität zweiter Ordnung (z.B. verursacht durch den  $x^2$ -Term) kann gewöhnlich durch eine vorsichtige Entwurfsmethodik verhindert oder eliminiert werden. Die Nichtlinearität zweiter Ordnung erzeugt Produkte bei den Summen- und Differenzfrequenzen. Typischerweise befinden sich die Störsignale, die In-Band-Produkte zweiter Ordnung erzeugen können, weit entfernt von dem Signalband und können leicht herausgefiltert werden. Nichtlinearität dritter Ordnung ist jedoch problematischer. Für Nichtlinearität dritter Ordnung erzeugen Störsignale  $x = g_1 \cdot \cos(w_1 t) + g_2 \cdot \cos(w_2 t)$  Produkte bei den Frequenzen  $(2w_1 - w_2)$  und  $(2w_2 - w_1)$ . Somit können Nahband-Störsignale ("die schwierig sind herauszufiltern") Intermodulationsprodukte dritter Ordnung erzeugen, die in das Band fallen, was zu einer Verschlechterung des Empfangssignals führt. Dieses Problem wird dadurch verstärkt, dass die Amplitude der Produkte dritter Ordnung skaliert werden durch  $g_1 \cdot g_2^2$  und durch  $g_1^2 \cdot g_2$ . Somit erzeugt jede Verdopplung der Amplitude der Störsignale einen achtfachen Anstieg der Amplitude der Produkte dritter Ordnung. Auf andere Weise betrachtet, resultiert jede Erhöhung des Eingabe-HF-Signals um 1 dB in einer Erhöhung des Ausgabe-HF-Signals um 1 dB aber zu einem Anstieg der Produkte dritter Ordnung um 3 dB.

**[0006]** Die Linearität eines Empfängers (oder eines aktiven Gerätes) kann durch den eingabebezogenen Schnittpunkt dritter Ordnung (IIP3 = third order intercept point) charakterisiert werden. Das Ausgabe-HF-Signal und die Intermodulationsprodukte dritter Ordnung werden typischerweise gegen das Eingabe-HF-Signal aufgetragen. Wenn das Eingabe-HF-Signal vergrößert wird, ist der IIP3 ein theoretischer Punkt, wo die Amplitude des gewünschten Ausgabe-HF-Signals und der Produkte dritter Ordnung gleich groß werden. Der IIP3 ist ein extrapoliertes Wert, da das aktive Gerät in Kompression übergeht, bevor der IIP3-Punkt erreicht wird.

**[0007]** Für einen Empfänger, der mehrere aktive Geräte umfasst, die kaskadenförmig verbunden sind, kann der IIP3 des Empfängers von der ersten Stufe aktiver Geräte bis zur n-ten Stufe folgendermaßen errechnet

werden:

$$IIP3_n = -10 \cdot \log_{10} \left[ 10^{-IIP3_{n-1}/10} + 10^{(Av_n - IIP3_{dn})/10} \right], \quad (2)$$

, wobei  $IIP3_n$  der eingabebezogene Schnittpunkt dritter Ordnung von der ersten Stufe aktiver Geräte bis zur  $n$ -ten Stufe,  $IIP3_{n-1}$  der eingabebezogene Schnittpunkt dritter Ordnung von der ersten Stufe bis zu der  $(n-1)$ -ten Stufe,  $Av_n$  die Verstärkung der  $n$ -ten Stufe,  $IIP3_{dn}$  der eingabebezogene Schnittpunkt dritter Ordnung der  $n$ -ten Stufe ist und alle Terme in Dezibel (dB) angegeben sind. Die Berechnung in Gleichung (2) kann in sequenzieller Ordnung für aufeinanderfolgende Stufen innerhalb des Empfängers ausgeführt werden.

**[0008]** Aus der Gleichung (2) ist ersichtlich, dass eine Möglichkeit der Verbesserung des abgestuften IIP3 darin besteht, die Verstärkung vor dem ersten nichtlinearen aktiven Gerät zu verringern. Jedes aktive Gerät erzeugt jedoch auch thermisches Rauschen, das die Signalqualität verschlechtert. Da der Rauschpegel auf einem konstanten Pegel gehalten wird, verschlechtert sich die Signalqualität, wenn die Verstärkung und die Signalamplitude verringert werden. Der Betrag der Verschlechterung kann durch den Rauschfaktor (NF = noise figure) des aktiven Gerätes wie folgt bemessen werden:

$$NF_d = SNR_{in} - SNR_{out} \quad (3)$$

, wobei  $NF_d$  der Rauschfaktor des aktiven Gerätes,  $SNR_{in}$  das Signal-zu-Rauschen-Verhältnis des Eingabe-HF-Signals in das aktive Gerät hinein,  $SNR_{out}$  das Signal-zu-Rauschen-Verhältnis des Ausgabe-HF-Signals von dem aktiven Gerät ist und  $NF_d$ ,  $SNR_{in}$  und  $SNR_{out}$  alle in Dezibel (dB) angegeben sind. Für einen Empfänger, der mehrere aktiven Geräte umfasst, die kaskadenförmig verbunden sind, kann der Rauschfaktor des Empfängers von der ersten Stufe aktiver Geräte bis zur  $n$ -ten Stufe folgendermaßen errechnet werden:

$$NF_n = 10 \cdot \log_{10} \left[ 10^{(NF_{n-1}/10)} + \frac{10^{(NF_{dn}/10)} - 1}{10^{(G_{n-1}/10)}} \right], \quad (4)$$

wobei  $NF_n$  der Rauschfaktor von der ersten Stufe bis zu der  $n$ -ten Stufe,  $NF_{n-1}$  der Rauschfaktor der ersten Stufe bis zu der  $(n-1)$ -ten Stufe,  $NF_{dn}$  der Rauschfaktor der  $n$ -ten Stufe und  $G_{n-1}$  die akkumulierte Verstärkung der ersten Stufe bis zu der  $(n-1)$ -ten Stufe in Dezibel ist. Wie in Gleichung (4) gezeigt, kann die Verstärkung des aktiven Gerätes den Rauschfaktor der nachfolgenden Stufen beeinflussen. Ähnlich wie die Berechnung des IIP3 in Gleichung (2) kann die Berechnung des Rauschfaktors in Gleichung (4) in sequenzieller Ordnung für aufeinanderfolgende Stufen des Empfängers durchgeführt werden.

**[0009]** Empfänger werden für viele Kommunikationsanwendungen verwendet, wie zum Beispiel zellulare Kommunikationssysteme und Fernsehen mit hoher Auflösung (HDTV = high definition television). Beispielhafte zellulare Kommunikationssysteme beinhalten Codemultiplexvielfachzugriff- (CDMA = code division multiple access) Kommunikationssysteme, Zeitmultiplexvielfachzugriff- (TDMA = time division multiple access) Kommunikationssysteme und analoge FM-Kommunikationssysteme. Die Verwendung von CDMA-Techniken in einem Vielfachzugriff-Kommunikationssystem wird in dem US Patent mit der Nummer 4,901,307 mit dem Titel "Spread Spectrum Multiple Access Communication System Using Satellite or Terrestrial Repeaters" und dem US Patent mit der Nummer 5,103,459 mit dem Titel "System and Method For Generating Waveforms in a CDMA Cellular Telephone System" offenbart, wobei beide Patente dem Rechtsnachfolger der vorliegenden Erfindung zugewiesen und hier als Referenz enthalten sind. Ein beispielhaftes HDTV-System wird in dem US Patent mit der Nummer 5,452,104, in dem US Patent mit der Nummer 5,107,345 und in dem US Patent mit der Nummer 5,021,891 offenbart, wobei alle drei Patente den Titel tragen "Adaptive Block Size Image Compression Method And System", ebenfalls offenbart in dem US Patent Nummer 5,576,767 mit dem Titel "Interframe Video Encoding And Decoding System", wobei alle vier Patente dem Rechtsnachfolger der vorliegenden Erfindung zugewiesen und hier als Referenz enthalten sind.

**[0010]** In zellularen Anwendungen ist es üblich, dass sich mehr als ein Kommunikationssystem innerhalb des selben geographischen Abdeckungsgebietes befindet. Weiterhin können diese Systeme auf demselben oder in der Nähe desselben Frequenzbandes arbeiten. Wenn dies auftritt, kann das Senden von einem System die Verschlechterung des Empfangssignals eines anderen Systems verursachen. CDMA ist ein Spreizspektrum-kommunikationssystem, welches die Sendeleistung auf jeden Benutzer über die gesamte 1,2288 MHz-Signalbandbreite spreizt. Die spektrale Antwort einer Übertragung, die auf FM basiert, kann auf die zentrale Frequenz konzentriert werden. Deshalb kann die FM-basierte Übertragung verursachen, dass innerhalb des zugewiesene-

nen CDMA-Bandes und sehr nahe an dem empfangenen CDMA-Signal Störsender auftreten. Weiterhin kann die Amplitude dieser Störsender um viele Male größer als die Amplitude des CDMA-Signals sein. Diese Störsender können Intermodulationsprodukte dritter Ordnung verursachen, die die Performance des CDMA-Systems verschlechtern können.

**[0011]** Typischerweise wird der Empfänger so entworfen, dass er einen hohen IIP3 besitzt, um die Verschlechterung aufgrund der Intermodulationsprodukte zu minimieren, die von den Störsendern verursacht werden. Der Entwurf eines Empfängers mit einem hohen IIP3 erfordert es, dass diese aktiven Geräte innerhalb des Empfängers mit einem hohen Gleichstrom vorgespannt sind und dabei große Energiemengen verbrauchen. Dieser Entwurfsansatz ist besonders für zelluläre Anwendungen, wobei der Empfänger eine tragbare Einheit darstellt und Energie begrenzt ist, unerwünscht.

**[0012]** Mehrere Techniken wurden nach dem vorangehenden Stand der Technik verwendet, um dem Bedürfnis nach einem hohen IIP3 Rechnung zu tragen. Eine solche Technik, die ebenfalls versucht, den Energieverbrauch zu vermindern, ist es, die Verstärkerstufe mit einer Vielzahl von Verstärkern zu implementieren, die parallel zueinander verbunden sind, und die Verstärker selektiv zu aktivieren, wenn ein höherer IIP3 benötigt wird. Diese Technik wird im Detail offenbart in der US-Patentanmeldung mit der Seriennummer 08/843,904 mit dem Titel "Dual Mode Amplifier With High Efficiency And High Linearity", wobei diese am 17.4.1997 eingereicht wurde und dem Rechtsnachfolger der vorliegenden Erfindung zugewiesen und hier als Referenz enthalten ist. Eine andere Technik ist es, die empfangene HF-Signalleistung zu messen und die Verstärkung der Verstärker basierend auf der Amplitude der HF-Signalleistung anzupassen. Die Technik wird im Detail offenbart in der US-Patentanmeldung mit der Seriennummer 08/723,491 mit dem Titel "Method and Apparatus For Increasing Receiver Power Immunity To Interference", wobei diese am 30. September 1996 eingereicht wurde und dem Rechtsnachfolger der vorliegenden Erfindung zugewiesen und hier als Referenz enthalten ist. Diese Techniken verbessern die IIP3-Performance, haben aber weder den Energieverbrauch wesentlich gesenkt noch die Schaltungskomplexität verringert.

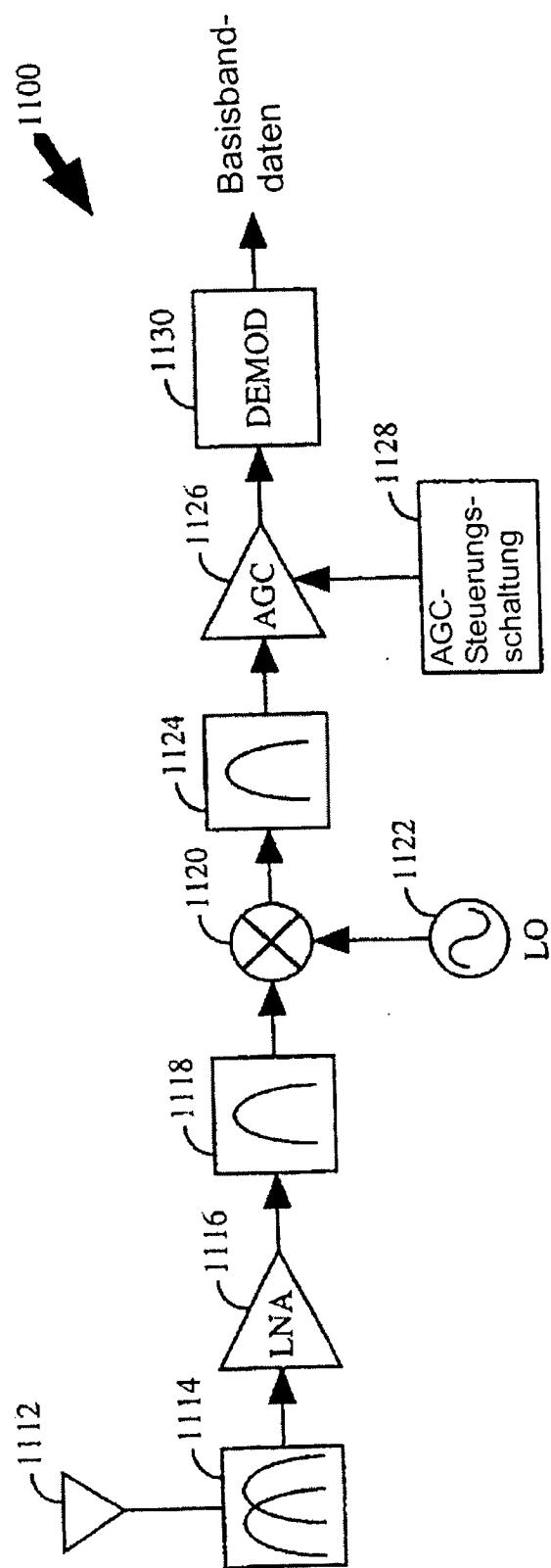

**[0013]** Ein beispielhaftes Blockdiagramm einer Empfängerarchitektur nach dem vorangehenden Stand der Technik wird in [Fig. 1](#) gezeigt. Innerhalb des Empfängers **1100** wird das gesendete HF-Signal von der Antenne **1112** empfangen, durch den Duplexer **1114** geleitet und an den Verstärker mit geringem Rauschen (LNA = low noise amplifier) **1116** geliefert. Der LNA **1116** verstärkt das HF-Signal und liefert das Signal an den Bandpassfilter **1118**. Der Bandpassfilter **1118** filtert das Signal, um einige der Störsignale zu entfernen, die Intermodulationsprodukte in den nachfolgenden Stufen verursachen können. Das gefilterte Signal wird an den Mischers **1120** geliefert, der das Signal auf eine Zwischenfrequenz (ZF bzw. IF = intermediate frequency) mit der Sinusform von dem lokalen Oszillator **1122** herabkonvertiert. Das ZF-Signal wird an den Bandpassfilter **1124** geliefert, der Störsignale und Produkte der Herabkonvertierung vor den nachfolgenden Herabkonvertierungsstufen herausfiltert. Das gefilterte ZF-Signal wird an den Verstärker mit automatischer Verstärkungssteuerung (AGC = automatic-gain-control) **1126** geliefert, der das Signal mit einer variablen Verstärkung verstärkt, um ein ZF-Signal bei der erforderlichen Amplitude vorzusehen. Die Verstärkung wird von einem Steuerungssignal von der AGC-steuerungsschaltung **1128** gesteuert. Das ZF-Signal wird an den Demodulator **1130** geliefert, der das Signal gemäß dem Modulationsformat, das bei dem Sender verwendet wird, demoduliert. Für digitale Übertragung wie zum Beispiel binäre Phasenverschiebungsverschlüsselung (BPSK = binary Phase shift keying), quartäre Phasenverschiebungsverschlüsselung (QPSK = quaternary Phase shift keying), quartäre Offset-Phasen Verschiebungsverschlüsselung (OQPSK = Offset quaternary Phase shift keying) und Quadraturamplitudenmodulation (QAM = quadrature amplitude modulation) wird ein digitaler Demodulator verwendet, um die digitalisierten Basisbanddaten vorzusehen. Für eine FM-Übertragung wird ein FM-Demodulator verwendet, um das analoge Signal vorzusehen.

**[0014]** Der Empfänger **1100** umfasst die grundlegenden Funktionalitäten, die von den meisten Empfängern benötigt werden. Der Ort der Verstärker **1116** und **1126**, der Bandpassfilter **1118** und **1124** und des Mischers **1120** kann jedoch neu festgelegt werden, um die Performance des Empfängers für eine bestimmte Anwendung zu optimieren. In dieser Empfängerarchitektur wird ein hoher IIP3 vorgesehen, indem die aktiven Geräte mit einem hohen Vorspannungsgleichstrom vorgespannt werden und/oder die Verstärkung des Verstärkers **1126** gesteuert wird.

**[0015]** Diese Empfängerarchitektur besitzt mehrere Nachteile. Erstens sind die aktiven Geräte typischerweise mit einem hohen Gleichstrom vorgespannt, um den höchsten erforderlichen IIP3 vorzusehen. Dies bewirkt, dass der Empfänger **1100** zu jedem Zeitpunkt bei dem hohen IIP3-Arbeitspunkt betrieben wird, auch wenn ein hoher IIP3 die meiste Zeit nicht benötigt wird. Zweitens kann der hohe IIP3 verbessert werden, indem die Verstärkung des AGC-Verstärkers **1126** angepasst wird, wie in dem bereits erwähnten US-Patent mit der Nummer

5,009,204 offenbart wird. Die Verringerung der Verstärkung des Verstärkers **1126** kann jedoch den Rauschfaktor des Empfängers **1100** verschlechtern.

**[0016]** Das Dokument US 5619536 offenbart einen digitalen Empfänger mit Überlagerung mit verbesserter Genauigkeit, der frei von Drift ist und die Anpassungsfähigkeit besitzt, seine Charakteristiken gemäß verschiedener Bedürfnisse anzupassen, zum Beispiel die Anpassung an verschiedene Modulationstypen oder verschiedene Bandbreiten, um einen Verwürfleiter zu eliminieren oder eine Vorfilterung oder eine anpassungsfähige Filterung für eine Entzerrung bzw. Angleichung (equalization) anzuwenden.

(5,009,204 offenbart wird. Die Verringerung der Verstärkung des Verstärkers **1126** kann jedoch den Rauschfaktor des Empfängers **1100** verschlechtern.)

#### Zusammenfassung der Erfindung

**[0017]** Die vorliegende Erfindung wird in den anhängenden Ansprüchen definiert und ist ein neuartiger und verbesserter programmierbaren Empfänger mit dynamischem Bereich, der das nötige Niveau an Performance mit verminderter Energieverbrauch vorsieht. In einem beispielhaften Ausführungsbeispiel umfasst der Empfänger einen Frontend, einen  $\Sigma\Delta$ -ADC, einen digitalen Signalprozessor, einen Leistungsdetektor und eine AGC-Steuerungsschaltung. In einem beispielhaften Ausführungsbeispiel wird das Eingabe-HF-Signal konditioniert und in ein ZF-Signal durch den Frontend herabkonvertiert. Das ZF-Signal wird durch den  $\Sigma\Delta$ -ADC quantisiert, um ZF-Abtastungen zu erzeugen, die durch den digitalen Signalprozessor verarbeitet werden, um das gewünschte Signal zu erhalten. Der Leistungsdetektor misst die Amplitude des Signals in dem  $\Sigma\Delta$ -ADC. In dem beispielhaften Ausführungsbeispiel wird der benötigte dynamische Bereich aus der Messung der Amplitude des gewünschten Signals und des Signals in dem  $\Sigma\Delta$ -ADC errechnet. In dem alternativen Ausführungsbeispiel wird der gewünschte dynamische Bereich basierend auf dem Modus des Empfängers bestimmt.

**[0018]** Es ist eine Aufgabe der vorliegenden Erfindung, einen programmierbaren Empfänger mit dynamischem Bereich vorzusehen, der den Energieverbrauch minimiert, indem er eine oder mehrere Schleifen innerhalb des  $\Sigma\Delta$ -ADCs aktiviert oder sperrt. In einem beispielhaften Ausführungsbeispiel ist der  $\Sigma\Delta$ -ADC mit einer oder mehreren Schleifen implementiert. Jede Schleife sieht eine Performance des vorbestimmte dynamischen Bereichs vor. Einen oder mehrere Schleifen innerhalb des  $\Sigma\Delta$ -ADC können aktiviert oder gesperrt werden, wenn der erforderliche dynamische Bereich einen Satz von Dynamikbereichsschwellen überschreitet oder unter diesen fällt. Die Dynamikbereichsschwellen können basierend auf zahlreichen Betrachtungen ausgewählt werden, wie zum Beispiel den Statistiken des Eingabe-HF-Signals und der Performance des  $\Sigma\Delta$ -ADC. Weiterhin können die Dynamikbereichsschwellen mit einer Hysterese implementiert werden, um eine Fluktuation bzw. Hin- und Herschalten der Schleifen zwischen den aktivierte und gesperrten Zuständen zu verhindern.

**[0019]** Es ist eine weitere Aufgabe der vorliegenden Erfindung, einen programmierbaren Empfänger mit dynamischem Bereich vorzusehen, der den Energieverbrauch minimiert, indem der Vorspannstrom angepasst wird. In einem beispielhaften Ausführungsbeispiel ist der  $\Sigma\Delta$ -ADC mit einem anpassbaren Vorspannstrom entworfen. Der dynamische Bereich des  $\Sigma\Delta$ -ADC verändert sich ungefähr proportional zu dem Vorspannstrom. Durch Anpassung des Vorspannstroms kann der erforderliche dynamische Bereich durch den  $\Sigma\Delta$ -ADC mit einem minimalen Energieverbrauch vorgesehen werden. Der Vorspannstrom kann in diskreten Schritten oder auf kontinuierliche Weise angepasst werden.

**[0020]** Eine weitere Aufgabe der vorliegenden Erfindung ist es ebenfalls, einen programmierbaren Empfänger mit dynamischem Bereich vorzusehen, der den Energieverbrauch minimiert, indem er eine Referenzspannung angelegt an den  $\Sigma\Delta$ -ADC angepasst. Der dynamische Bereich des  $\Sigma\Delta$ -ADC wird durch den maximalen Eingabesignalspitzenwert und das Rauschen von dem  $\Sigma\Delta$ -ADC bestimmt, das das Schaltungsräuschen und das Quantisierungsräuschen beinhaltet. Wenn der erforderliche dynamische Bereich sinkt, kann die Referenzspannung gesenkt werden, während ungefähr derselbe Rauschpegel aufrechterhalten wird. Dies trifft besonders dann zu, wenn eine Schleife ausgeschaltet wird und sich das Quantisierungsräuschen so erhöht, dass es viel größer als das Schaltungsräuschen ist. Durch Absenken der Referenzspannung, so dass das Quantisierungsräuschen ungefähr gleich dem Schaltungsräuschen ist, wird das gewünschte Performanceniveau vorgesehen, während der Signalpegel auf einem geringen Pegel gehalten wird. Es ist ein zusätzlicher Vorteil, dass der Verstärker, der den  $\Sigma\Delta$ -ADC treibt, einen geringeren maximalen Signalspitzenwert besitzt und mit einem geringeren Strom vorgespannt werden kann.

**[0021]** Eine weitere Aufgabe der vorliegenden Erfindung ist es ebenfalls, einen programmierbaren Empfänger mit dynamischem Bereich vorzusehen, der den Energieverbrauch minimiert, indem die Abtastungsfrequenz des  $\Sigma\Delta$ -ADC angepasst wird. Der dynamische Bereich des  $\Sigma\Delta$ -ADC ist eine Funktion des Überabtastungver-

hältnisses (= oversampling ratio), das proportional zu der Abtastungsfrequenz ist, weil die Bandbreite des Signals in den  $\Sigma\Delta$ -ADC konstant ist. Ein hoher dynamischer Bereich erfordert ein hohes Überabtastungsverhältnis. Der Energieverbrauch der Schaltungen, die verwendet werden, um den  $\Sigma\Delta$ -ADC zu implementieren, kann von der Abtastungsfrequenz abhängen. In der vorliegenden Erfindung kann die Abtastungsfrequenz verringert werden, um den Energieverbrauch zu minimieren, wenn ein hoher dynamischer Bereich nicht erforderlich ist.

**[0022]** Es ist ebenfalls eine weitere Aufgabe der vorliegenden Erfindung, einen programmierbaren Empfänger mit dynamischem Bereich vorzusehen, der den Energieverbrauch minimiert, indem der geeignete  $\Sigma\Delta$ -ADC basierend auf der erforderlichen Performance eingeschaltet wird. In diesem Ausführungsbeispiel kann der Empfänger mit einem oder mehreren  $\Sigma\Delta$ -ADCs ausgestattet sein, die die Abtastungsfunktion für zwei oder mehrere Arbeitsmodi vorsehen. Zum Beispiel kann ein Empfänger mit zwei  $\Sigma\Delta$ -ADCs ausgestattet sein, einen für den CDMA-Modus und einen für den FM-Modus. Der  $\Sigma\Delta$ -ADC für den FM-Modus kann so entworfen werden, dass er wegen der geringeren Signalbandbreite und des geringeren erforderlichen dynamischen Bereichs deutlich weniger Energie verbraucht. Der geeignete  $\Sigma\Delta$ -ADC kann eingeschaltet werden abhängig davon, ob der Empfänger in dem CDMA- oder FM-Modus arbeitet.

**[0023]** Die oben beschriebenen Merkmale können je nach Eignung miteinander kombiniert werden, um das erforderliche Performanceniveau vorzusehen, während die Energieeinsparung maximiert wird.

#### Kurze Beschreibung der Zeichnungen

**[0024]** Die Merkmale, Aufgaben und Vorteile der vorliegenden Erfindung werden aus der folgenden detaillierten Beschreibung in Verbindung mit den Zeichnungen, in denen jeweils gleiche Bezugszeichen durchgehend gleiches kennzeichnen, deutlicher hervorgehen, wobei

**[0025]** [Fig. 1](#) ein Blockdiagramm eines beispielhaften Empfängers nach dem vorangehenden Stand der Technik ist;

**[0026]** [Fig. 2](#) ein Blockdiagramm eines beispielhaften programmierbaren linearen Empfängers der vorliegenden Erfindung ist;

**[0027]** [Fig. 3](#) ein Blockdiagramm eines beispielhaften programmierbaren linearen Dualband-Empfängers der vorliegenden Erfindung ist;

**[0028]** [Fig. 4](#) ein Blockdiagramm eines beispielhaften QPSK-Demodulators ist, der innerhalb der Empfänger der vorliegenden Erfindung verwendet wird;

**[0029]** [Fig. 5A](#)-[Fig. 5B](#) jeweils schematische Diagramme eines beispielhaften diskreten Entwurfs eines Verstärkers mit geringem Rauschen (LNA = low-noise-amplifier) und einer Stromquelle sind, die in den Empfängern der vorliegenden Erfindung verwendet werden;

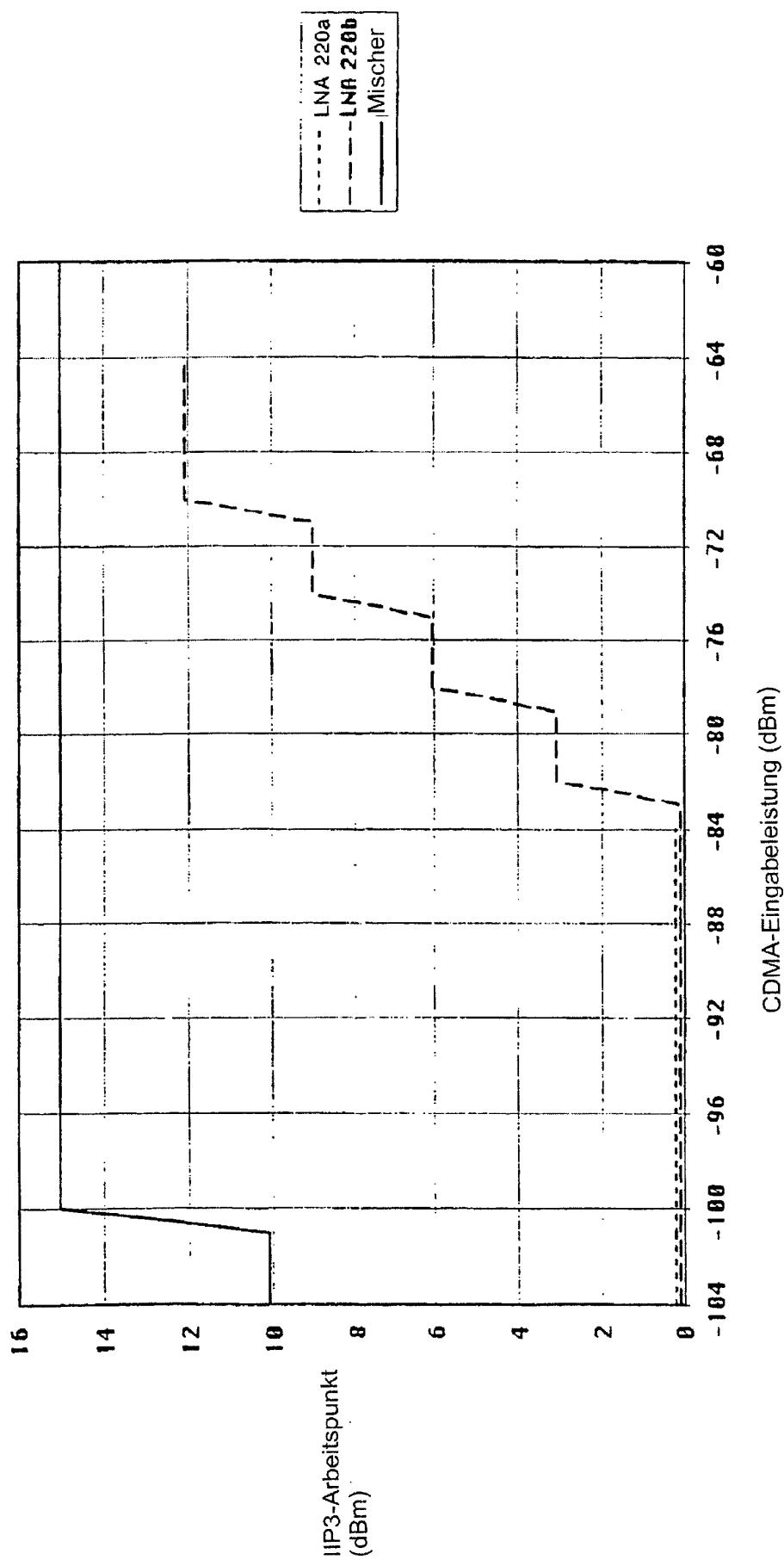

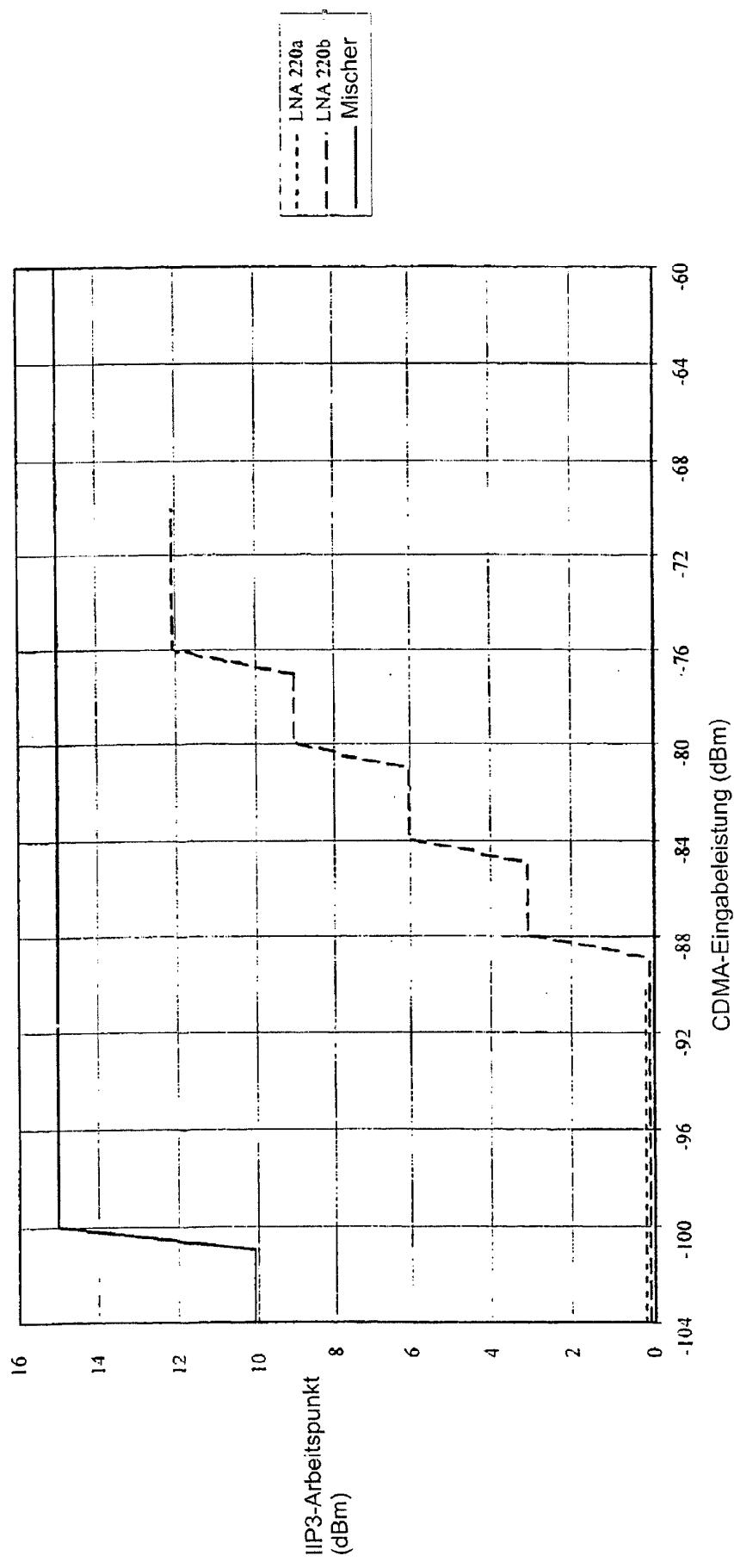

**[0030]** [Fig. 6A](#)-[Fig. 6B](#) jeweils Diagramme der IIP3-Performance in Abhängigkeit des Vorspannstroms des Transistors sind, die in dem LNA und den Performancekurven des LNA verwendet werden;

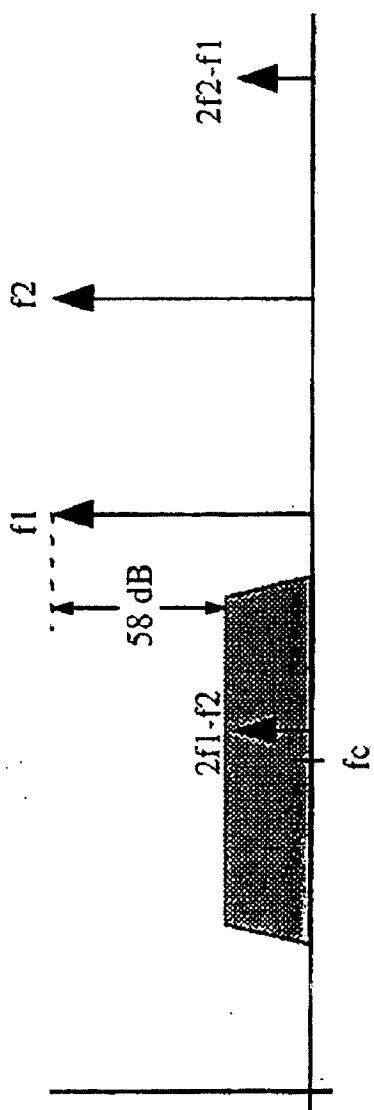

**[0031]** [Fig. 7A](#)-[Fig. 7B](#) jeweils Diagramme der Zweitton- und Einfachtonstörsender-Spezifikationen für ein CDMA-Signal sind, das durch den IS-98-A definiert ist;

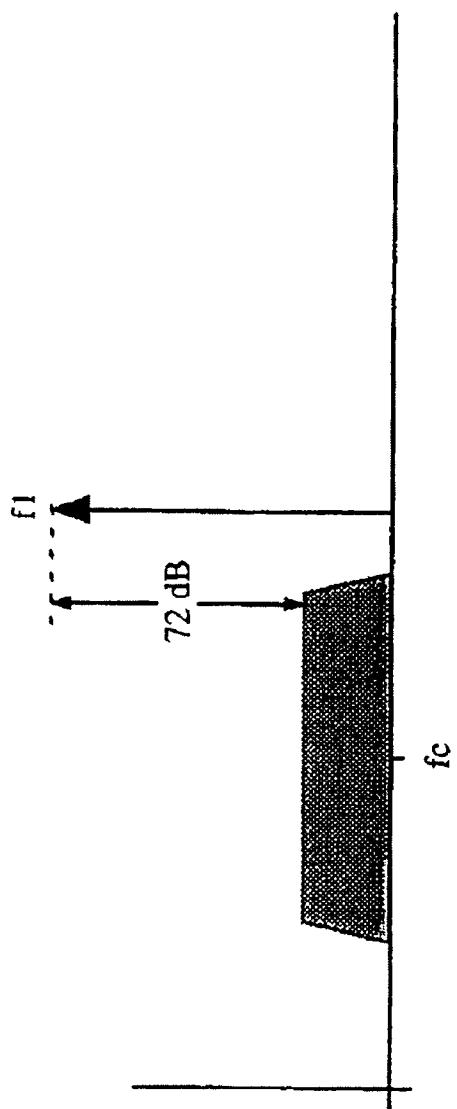

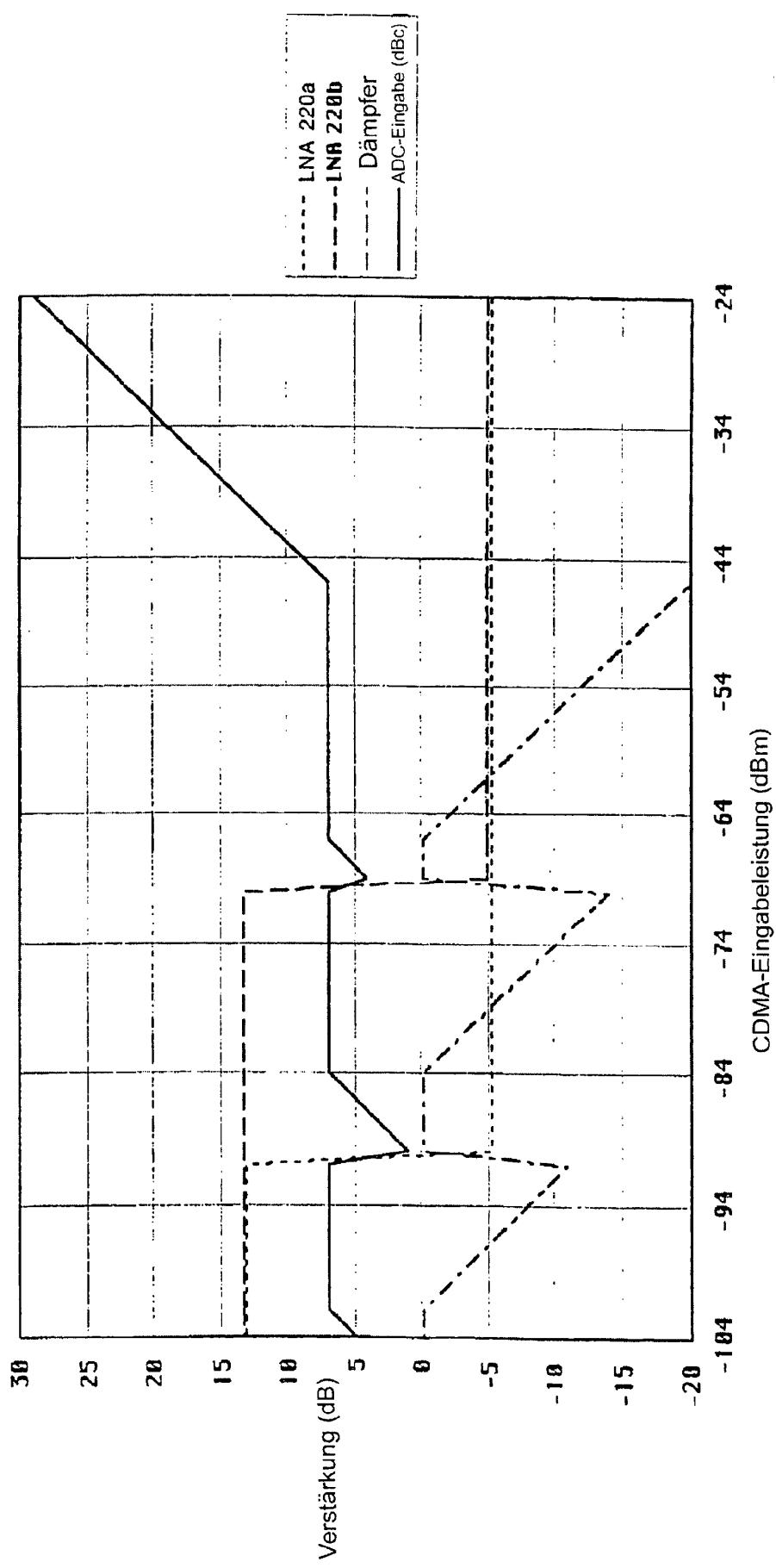

**[0032]** [Fig. 8A](#)-[Fig. 8B](#) jeweils Diagramme des AGC-Steuerungsbereichs für ansteigende und absinkende CDMA-Eingabeleistung sind;

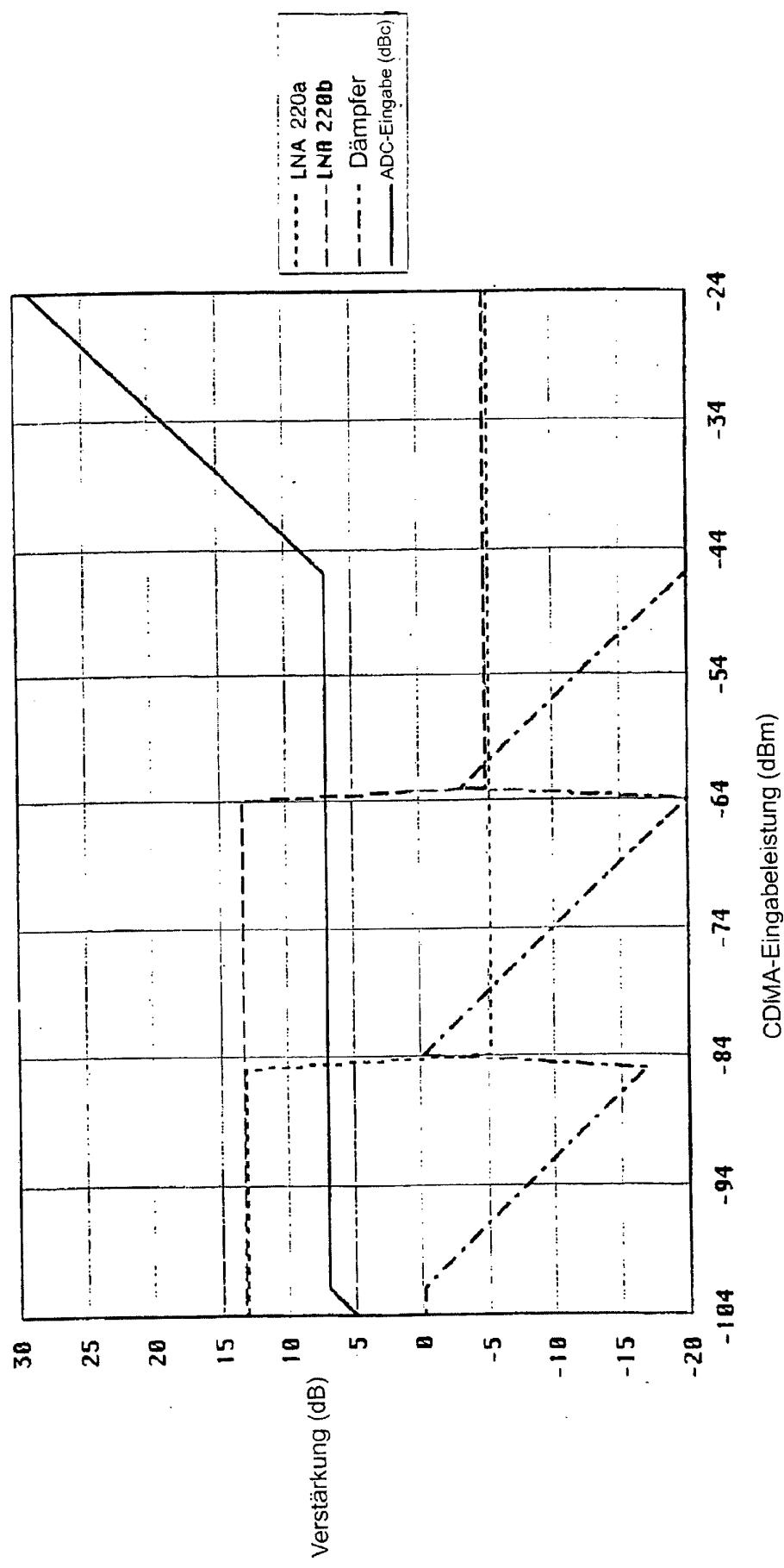

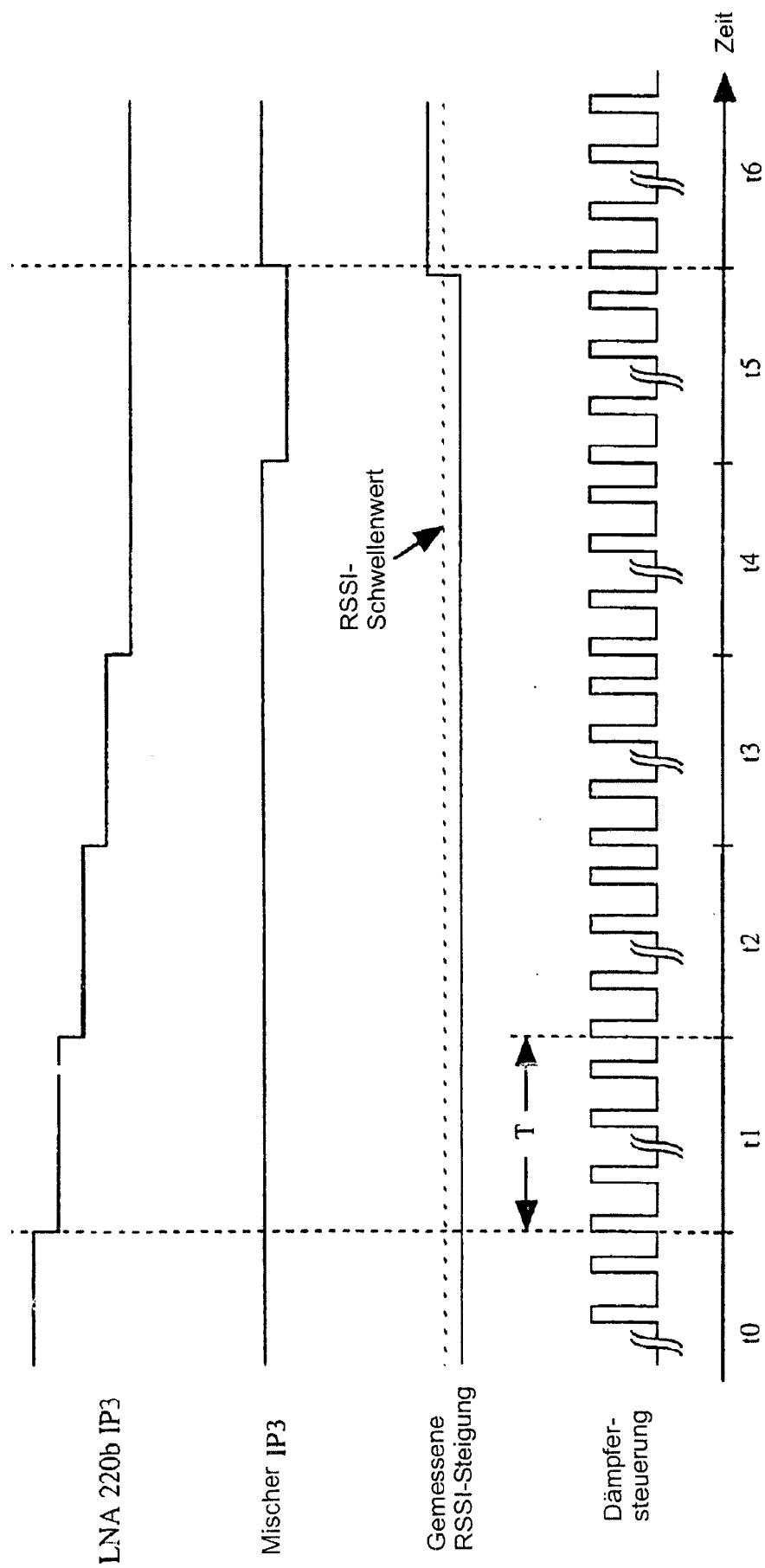

**[0033]** [Fig. 9](#) ein Diagramm eines beispielhaften IIP3-Vorspannungssteuerungsmechanismus der vorliegenden Erfindung ist;

**[0034]** [Fig. 10A](#)-[Fig. 10B](#) jeweils Diagramme für die IIP3-Vorspannungssteuerung für ansteigende oder absinkende CDMA-Eingabeleistung sind; und

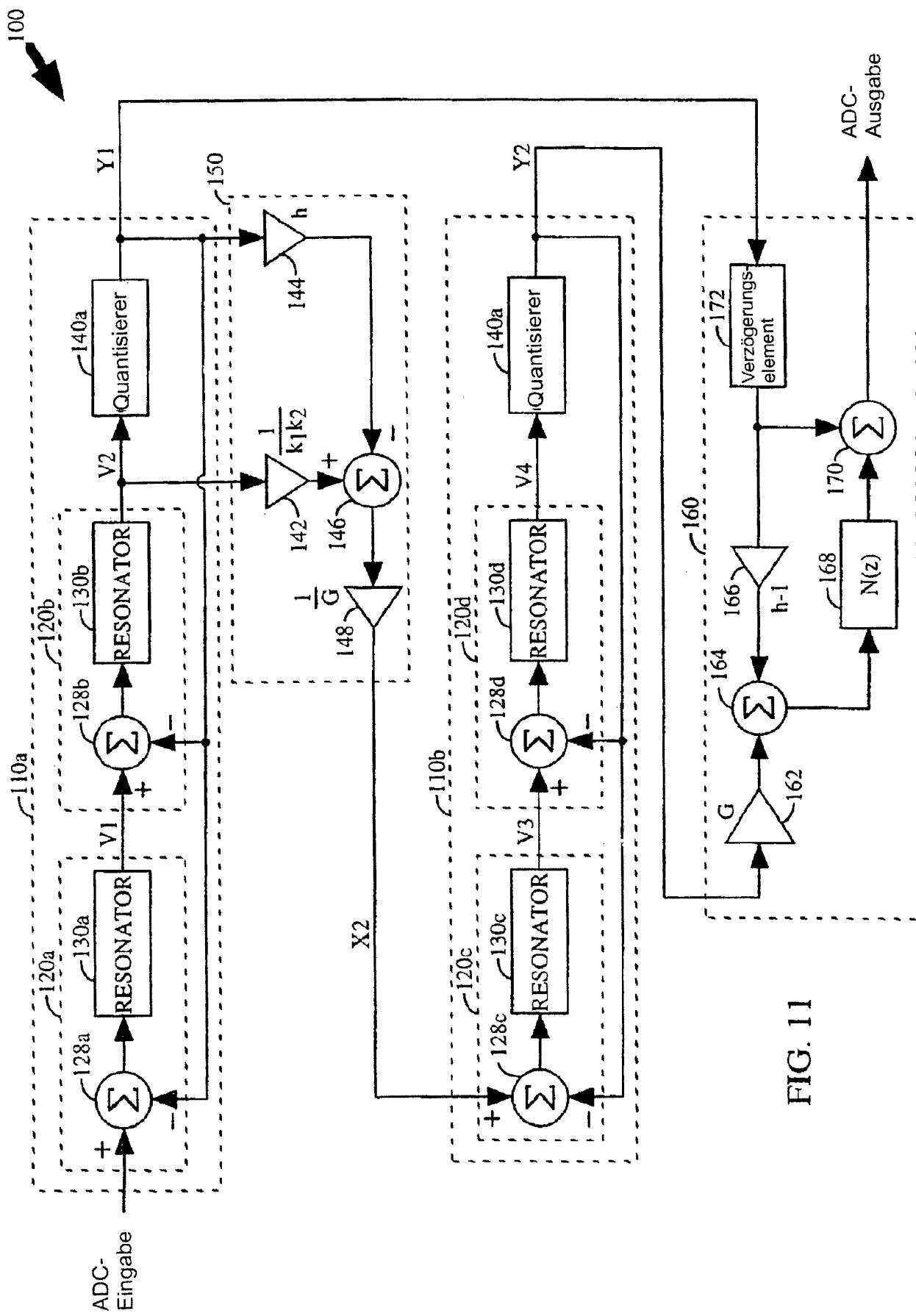

**[0035]** [Fig. 11](#) ein Blockdiagramm eines beispielhaften Zwei-Schleifen-Bandpass-MASH- $\Sigma\Delta$ -Analog-Zu-Digital-Wandlers ist.

## Detaillierte Beschreibung der bevorzugten Ausführungsbeispiele

**[0036]** Der Empfänger der vorliegenden Erfindung sieht ein erforderliches Niveau der Systemperformance vor und minimiert den Energieverbrauch, indem er den Gleichspannung-Bias bzw. das Gleichspannungssignal der Vorspannung der aktiven Geräte steuert. Die vorliegende Erfindung kann ausgeübt werden, indem eines der drei im Folgenden beschriebenen Ausführungsbeispiele verwendet wird. In dem ersten Ausführungsbeispiel wird der Betrag an Nichtlinearität bei der Ausgabe des Empfängers gemessen und dazu verwendet, den IIP3-Arbeitspunkt der aktiven Geräte innerhalb des Empfängers wie die Verstärker und den Mischer einzustellen. In dem zweiten Ausführungsbeispiel wird der IIP3-Arbeitspunkt der aktiven Geräte gemäß dem erwarteten Pegel des Empfangssignals basierend auf dem Modus des Empfängers eingestellt. Und in dem dritten Ausführungsbeispiel wird der IIP3-Arbeitspunkt der aktiven Geräte gemäß dem gemessenen Signalpegel bei verschiedenen Stufen innerhalb des Empfängers eingestellt.

**[0037]** In der vorliegenden Erfindung ist die AGC-Funktion mit einer AGC-Steuerungsschaltung vorgesehen, die mit einer Vorspannungssteuerungsschaltung zusammenarbeitet. Der IIP3-Arbeitspunkt der aktiven Geräte wird gemäß dem gemessenen Betrag an Nichtlinearität eingestellt, der von der Amplitude des Signals abhängt. Die Signalamplitude wiederum hängt von den Verstärkungseinstellungen des Empfängers ab. In der vorliegenden Erfindung werden der AGC und die Vorspannungssteuerung auf integrierte Weise betrieben, um den erforderlichen Grad an Linearität über einen spezifizierten AGC-Bereich vorzusehen, während der Energieverbrauch minimiert wird.

## I. Empfängerarchitektur

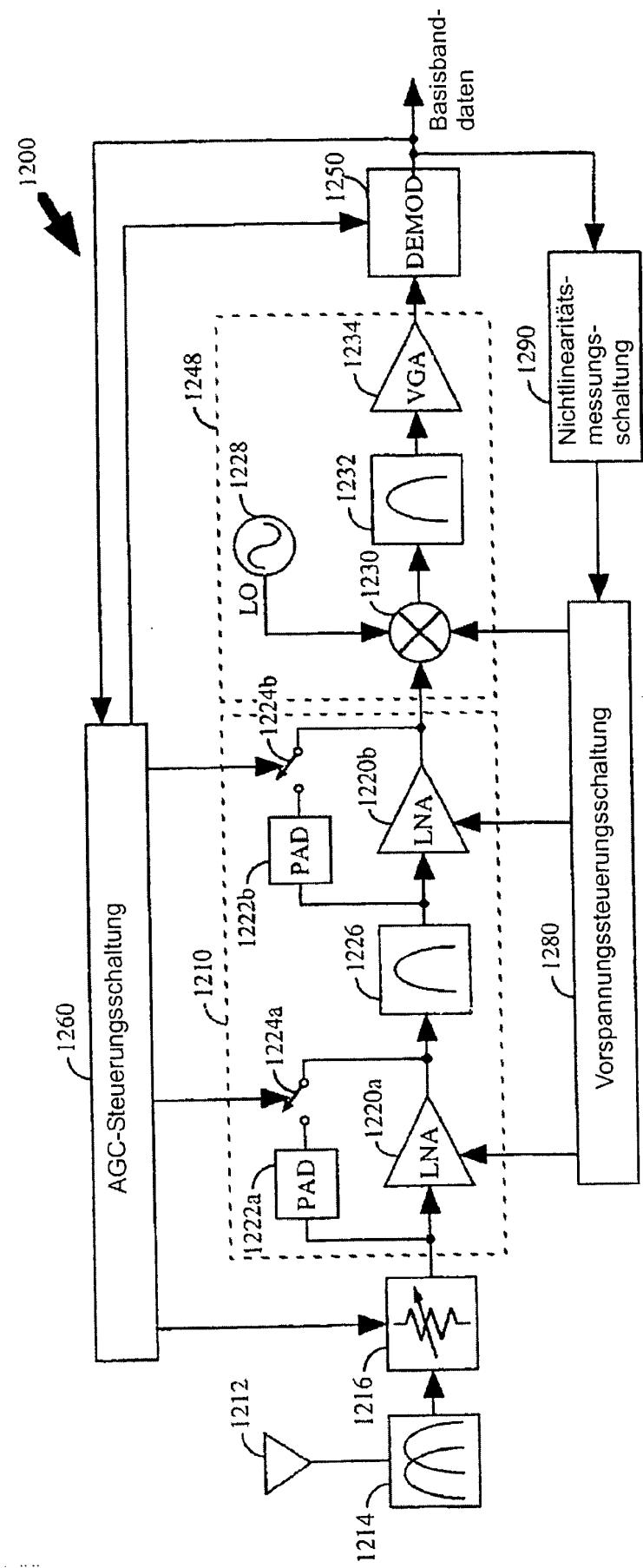

**[0038]** Ein Blockdiagramm einer beispielhaften Empfängerarchitektur der vorliegenden Erfindung wird in [Fig. 2](#) gezeigt. Innerhalb des Empfängers **1200** wird das gesendete HF-Signal von der Antenne **1212** empfangen, durch den Duplexer **1214** geleitet und an den Dämpfer **1216** geliefert. Der Dämpfer **1216** dämpft das HF-Signal ab, um ein Signal mit der erforderlichen Amplitude vorzusehen und liefert das gedämpfte Signal an den HF-Prozessor **1210**. Innerhalb des HF-Prozessors **1210** wird das gedämpfte Signal an das Dämpfungsglied bzw. Pad **1222a** und an den Verstärker mit geringem Rauschen (LNA) **1220a** geliefert. Der LNA **1220a** verstärkt das HF-Signal und liefert das verstärkte Signal an den Bandpassfilter **1226**. Das Dämpfungsglied **1222a** sieht einen vorbestimmten Dämpfungspegel vor und ist in Reihe verbunden mit dem Schalter **1224a**. Der Schalter **1224a** sieht eine Umgehung um den LNA **1220a** vor, wenn die Verstärkung des LNA **1220a** nicht benötigt wird. Der Bandpassfilter **1226** filtert das Signal, um Störsignale zu entfernen, die Intermodulationsprodukte in den nachfolgenden Signalverarbeitungsstufen verursachen können. Das gefilterte Signal wird an das Dämpfungsglied **1222b** und an den Verstärker mit geringem Rauschen (LNA) **1220b** geliefert. Der LNA **1220b** verstärkt das gefilterte Signal und liefert das Signal an den HF/ZF-Prozessor **1248**. Das Dämpfungsglied **1222b** sieht einen vorbestimmten Dämpfungspegel vor und ist in Reihe verbunden mit dem Schalter **1224b**. Der Schalter **1224b** sieht eine Umgehung um den LNA **1220b** vor, wenn die Verstärkung des LNA **1220b** nicht benötigt wird. Innerhalb des HF/ZF-Prozessors **1248** konvertiert der Mischer **1230** das Signal mit der Sinusform von dem lokalen Oszillatoren (LO = local oscillator) **1228** auf eine Zwischenfrequenz (IF = intermediate frequency) herab. Das ZF-Signal wird an den Bandpassfilter **1232** geliefert, der Störsignale und Produkte der Herabkonvertierung, die außerhalb des Bandes liegen, herausfiltert. In dem bevorzugten Ausführungsbeispiel wird das gefilterte ZF-Signal an den Spannungssteuerungsverstärker (VGA = voltage control amplifier) **1134** geliefert, der das Signal mit einer variablen Verstärkung verstärkt, die durch ein Verstärkungssteuerungssignal angepasst wird. Der Verstärker **1234** kann auch, von den Erfordernissen des Systems abhängig, als ein Verstärker mit fester Verstärkung implementiert werden und auch dies gehört zu dem Umfang der vorliegenden Erfindung. Das verstärkte ZF-Signal wird an den Demodulator **1250** geliefert, der das Signal gemäß dem Modulationsformat demoduliert, das von dem Sender verwendet wird (nicht gezeigt). Der HF-Prozessor **1210** und der HF/ZF-Prozessor **1248** werden insgesamt als ein Frontend bezeichnet.

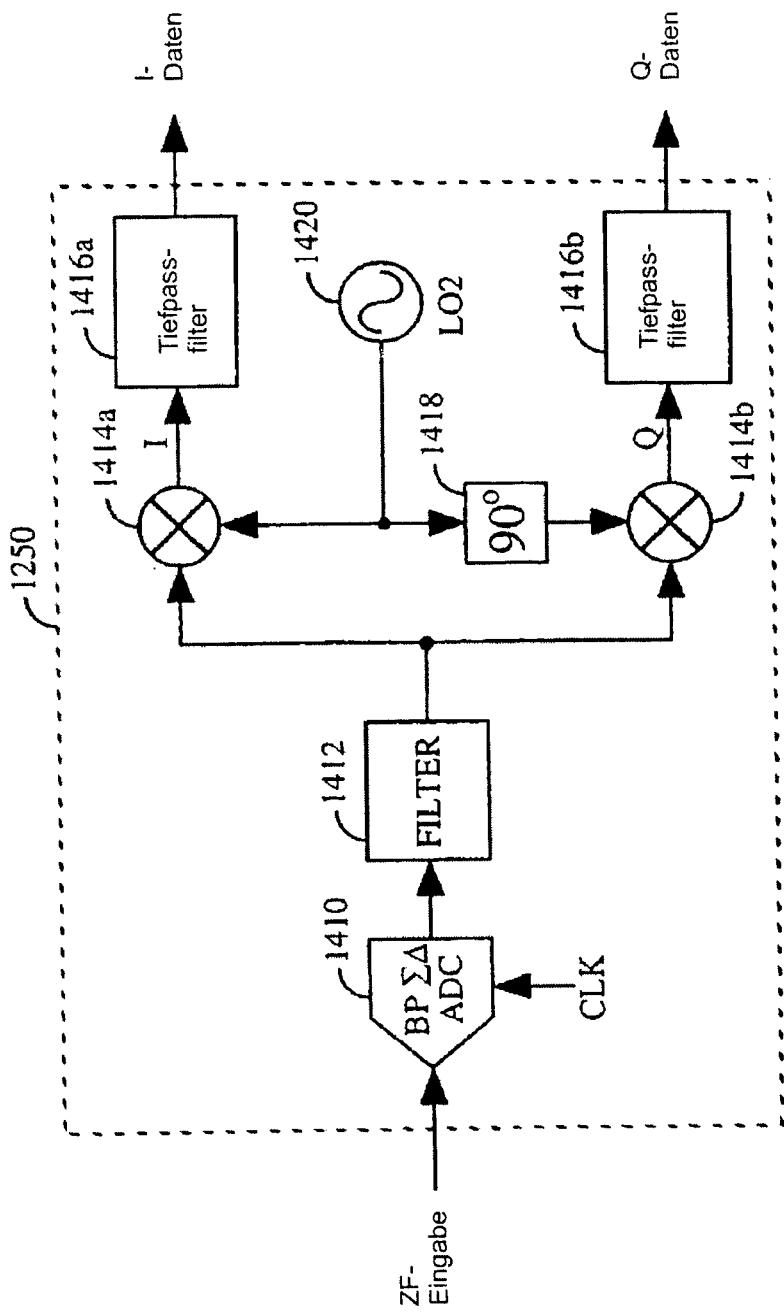

**[0039]** In [Fig. 4](#) wird ein Blockdiagramm eines beispielhaften Demodulators **1250** dargestellt, der zur Demodulation der quadraturmodulierten Signale (z.B. QPSK, OQPSK und QAM) verwendet wird. In dem beispielhaften Ausführungsbeispiel ist der Demodulator **1250** als ein Subabtastungsbandpass-Demodulator bzw. subsampling bandpass demodulator implementiert. Das ZF-Signal wird an den Bandpass-SigmaDelta-Analog-zu-Digital-Wandler ( $\Sigma\Delta$ -ADC) **1410** geliefert, die das Signal bei einer hohen Abtastfrequenz quantisiert, die durch das CLK-Signal bestimmt wird. Ein beispielhafter Entwurf eines  $\Sigma\Delta$ -ADCs wird im Detail beschrieben in der US-Anmeldung mit der Seriennummer 08/928,874, die den Titel trägt "Sigma-Delta Analog-to-Digital Converter", erteilt am 12.9.1997 und dem Rechtsnachfolger der vorliegenden Erfindung zugewiesen. Die Verwendung eines  $\Sigma\Delta$ -ADCs innerhalb eines Empfängers wird offenbart in der anhängenden US-Patentanmeldung mit der Seriennummer 08/987,306, die den Titel trägt "Receiver With Sigma-Delta Ana-

log-to-Digital Converter", erteilt am 9.12.1997, wobei diese dem Rechtsnachfolger der vorliegenden Erfindung zugewiesen und hier als Referenz enthalten ist. Das quantisierte Signal wird an Filter **1412** geliefert, der das Signal filtert und dezimiert. Das gefilterte Signal wird an die Multiplizierer **1414a** und **1414b** geliefert, die das Signal auf das Basisband mit den In-Phasen- und Quadratur-Sinusformen von jeweils dem lokalen Oszillatoren (LO2) **1420** und dem Phasenverschieber **1418** herabkonvertieren. Der Phasenverschieber **1418** sieht eine Phasenverschiebung um 90° für die Quadratur-Sinusform vor. Die I- und Q-Signale des Basisbands werden jeweils an die Tiefpassfilter **1416a** und **1416b** geliefert, die das Signal filtern, um die I- und Q-Daten vorzusehen. Die Basisbanddaten in [Fig. 2](#) umfassen die I- und Q-Daten in [Fig. 4](#). In dem beispielhaften Ausführungsbeispiel sehen der Filter **1412** und/oder die Tiefpassfilter **1416** auch eine Skalierung des Signals vor, um es dem Demodulator **1250** zu ermöglichen, Basisbanddaten bei mehreren Amplituden vorzusehen. Andere Implementierungen des Demodulators **1250** können entworfen werden, um die Demodulation der QPSK-modulierten Wellenform durchzuführen und befinden sich innerhalb des Umfangs der vorliegenden Erfindung.

**[0040]** Nochmals bezugnehmend auf [Fig. 2](#), umfasst der Empfänger **1200** die grundlegenden Funktionen, die von den meisten Empfängern benötigt werden. Die Anordnung des Dämpfers **1216**, der LNAs **1220a** und **1220b**, der Bandpassfilter **1226** und **1232** und des Mischers **1230** kann neu geordnet werden, um die Performance des Empfängers **1200** für bestimmte Anwendungen zu optimieren. Zum Beispiel kann der Dämpfer **1216** sich zwischen dem LNA **1220a** und dem Bandpassfilter **1226** befinden, um die Rauschfaktor-Performance zu verbessern. Weiterhin kann vor dem LNA **1220a** ein Bandpassfilter eingesetzt werden, um unerwünschte Störsignale vor der ersten Verstärkerstufe zu entfernen. Es können verschiedene Anordnungen der Funktionen, die hier gezeigt werden, betrachtet werden und diese befinden sich innerhalb des Umfangs der vorliegenden Erfindung. Weiterhin können andere Anordnungen der hier gezeigten Funktionalitäten in Kombination mit anderen Empfängerfunktionalitäten nach dem Stand der Technik auch betrachtet werden und befinden sich innerhalb des Umfangs der vorliegenden Erfindung.

**[0041]** In der vorliegenden Erfindung werden der Dämpfer **1216**, die Schalter **1224a** und **1224b** und der Demodulator **1250** von der AGC-Steuerungsschaltung **1260** so gesteuert, dass sich das ZF-Signal von dem Verstärker **1234** bei der erforderlichen Amplitude befindet. Die AGC-Funktion wird im folgenden im Detail beschrieben. In dem beispielhaften Ausführungsbeispiel sind die LNAs **1220a** und **1220b** Verstärker mit fester Verstärkung. Die LNAs **1220a** und **1220b** und der Mischer **1230** werden von der Vorspannungssteuerungsschaltung **1280** gesteuert, um den Vorspannungsgleichstrom und/oder die Spannungen dieser aktiven Geräte so anzupassen, dass die erforderliche Linearitäts-Performance mit minimalem Energieverbrauch erreicht wird. Der variable IIP3-Vorspannungssteuerungsmechanismus wird im folgenden im Detail beschrieben.

**[0042]** Die Empfängerarchitektur der vorliegenden Erfindung kann für die Verwendung in zahlreichen Anwendungen übernommen werden, einschließlich zellularer Telefone und HDTV-Anwendungen. In dem zellularen Telefon kann der Empfänger **1200** für die Verwendung in CDMA-Kommunikationssystemen übernommen werden, die auf dem Individualkommunikationssystem- (PCS = personal communication system) Band oder dem zellularen Band arbeiten.

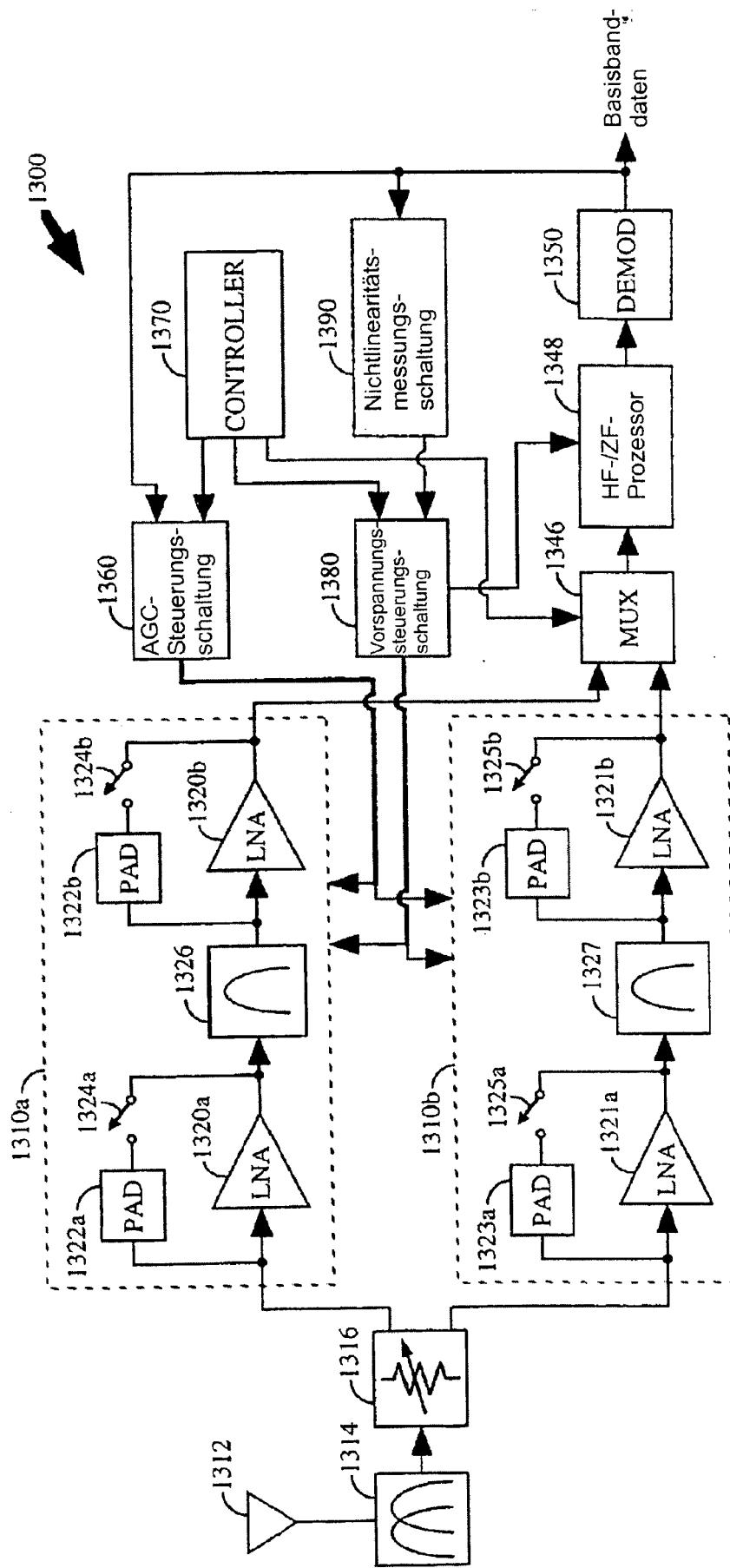

**[0043]** In [Fig. 3](#) wird ein Blockdiagramm eines beispielhaften Empfängers gezeigt, der Dualband (PCS und zellular) und Dualmodus (CDMA und AMPS) unterstützt. Das PCS-Band hat eine Bandbreite von 60 MHz und eine Mittenfrequenz von 1900 MHz. Das zellulare Band hat eine Bandbreite von 25 MHz und eine Mittenfrequenz von 900 MHz. Jedes Band benötigt einen eigenen HF-Bandpassfilter. Deshalb werden für die beiden Bänder zwei HF-Prozessoren verwendet.

**[0044]** Der Empfänger **1300** umfasst viele Komponenten, die denen in dem Empfänger **1200** gleichen (siehe [Fig. 2](#)). Die Antenne **1312**, der Duplexer **1314** und der Dämpfer **1316** sind identisch mit der Antenne **1212**, dem Duplexer **1214** und dem Dämpfer **1216** in dem Empfänger **1200**. Das gedämpfte Signal von dem Dämpfer **1316** wird an die HF-Prozessoren **1310a** und **1310b** geliefert. Der HF-Prozessor **1310a** ist dafür entworfen, auf dem zellularen Band zu arbeiten und der HF-Prozessor **1310b** ist dafür entworfen, auf dem PCS-Band zu arbeiten. Der HF-Prozessor **1310a** und der HF-Prozessor **1210** in dem Empfänger **1200** sind identisch. Der HF-Prozessor **1310a** umfasst zwei Stufen des Verstärkers mit geringem Rauschen (LNA = low-noise amplifier) **1320a** und **1320b**, die in Reihe mit dem Bandpassfilter **1326** verbunden sind, der sich zwischen den beiden Stufen befindet. Jeder LNA **1320** hat einen parallelen Signalpfad, der das Dämpfungsglied **1322** und den Schalter **1324** umfasst. Der HF-Prozessor **1310a** und der HF-Prozessor **1301b** sind ähnlich bis auf den Sachverhalt, dass die LNAs **1321a** und **1321b** und der Bandpassfilter **1327** dafür entworfen sind, auf dem PCS-Band zu arbeiten. Die Ausgabe der HF-Prozessoren **1310a** und **1310b** werden an den Multiplexer (MUX = multiplexer) **1346** weitergegeben, der das gewünschte Signal gemäß einem Steuerungssignal von dem Controller **1370** (in [Fig. 3](#) aus Gründen der Übersichtlichkeit nicht gezeigt) auswählt. Das HF-Signal von MUX **1346**

wird an den HF/ZF-Prozessor **1348** weitergegeben, der mit dem HF/ZF-Prozessor **1248** in [Fig. 2](#) identisch ist. Das ZF-Signal von dem Prozessor **1348** wird an den Demodulator (DEMOD = demodulator) **1350** geliefert, der das Signal gemäß dem Modulationsformat, das bei dem entfernten Sender (nicht gezeigt) verwendet wird, demoduliert. Der Demodulator **1350**, die AGC-Steuerungsschaltung **1360**, die Vorspannsteuerungsschaltung **1380** und die Nichtlinearitäts-Messungsschaltung **1390** in [Fig. 3](#) sind jeweils identisch mit dem Demodulator **1250**, der AGC-Steuerungsschaltung **1260**, der Vorspannsteuerungsschaltung **1280** und der Nichtlinearitäts-Messungsschaltung **1290** in [Fig. 2](#).

**[0045]** Der Controller **1370** ist mit der AGC-Steuerungsschaltung **1360**, der Vorspannsteuerungsschaltung **1380** und dem MUX **1346** verbunden und steuert den Betrieb dieser Schaltungen. Der Controller **1370** kann als ein Mikroprozessor, ein Mikrocontroller oder ein digitaler Signalprozessor implementiert werden, der dafür programmiert ist, die hier beschriebenen Funktionen auszuführen. Der Controller **1370** kann auch ein Speicherlement (memory storage element) umfassen, das die Arbeitsmodi des Empfängers **1300** und die zugehörigen Steuerungssignale speichert.

**[0046]** Gemäß [Fig. 2](#) wird ein beispielhafter Entwurf eines Empfängers **1200** im folgenden im Detail beschrieben, der speziell an zelluläre Telefonanwendungen angepasst ist. In dem beispielhaften Ausführungsbeispiel hat der Dämpfer **1216** einen Dämpfungsbereich von 20 dB und sieht eine Dämpfung von 0,2 dB bis -20 dB vor. Der Dämpfer **1216** kann mit einem Diodenpaar oder durch Feldeffekttransistoren (FETs = field effect transistors) entworfen werden, wobei die Implementierungen nach dem Stand der Technik bekannt sind. In dem beispielhaften Ausführungsbeispiel haben die LNAs **1220a** und **1220b** feste Verstärkungen von jeweils 13 dB. Die LNAs **1220a** und **1220b** können handelsübliche, monolithische HF-Verstärker oder Verstärker sein, die dafür entworfen wurden, diskrete Komponenten zu verwenden. Ein beispielhafter diskreter Entwurf von LNA **1220** wird im folgenden im Detail beschrieben. In dem beispielhaften Ausführungsbeispiel sehen die Dämpfungsglieder **1222a** und **1222b** 5 dB Dämpfung vor und können mit Widerständen nach dem Stand der Technik implementiert werden. In dem beispielhaften Ausführungsbeispiel ist der Bandpassfilter **1226** ein Filter für akustische Oberflächenwellen (SAW = surface acoustic wave), der eine Bandbreite von 25 MHz besitzt, der gesamten Bandbreite des zellularen Bandes, und ist auf etwa 900 MHz zentriert.

**[0047]** In dem beispielhaften Ausführungsbeispiel ist der Bandpassfilter **1232** auch ein SAW-Filter, der eine Bandbreite von 1,2288 MHz besitzt, der Bandbreite eines CDMA-Systems, und ist auf ungefähr 116,5 MHz zentriert. Der Mischer **1230** ist ein aktiver Mischer, der ein handelsüblicher Mischer sein kann wie zum Beispiel der Motorola MC13143 oder ein anderer aktiver Mischer, der nach dem Stand der Technik entworfen wurde. Der Mischer **1230** kann ebenfalls mit passiven Komponenten implementiert werden wie zum Beispiel einem doppelt ausbalancierten Diodenmischer. Der Verstärker **1234** kann ein monolithischer Verstärker oder einen Verstärker sein, der mit diskreten Komponenten entworfen wurde. In dem beispielhaften Ausführungsbeispiel ist der Verstärker **1234** dazu entworfen, eine Verstärkung von 40 dB vorzusehen.

**[0048]** In dem beispielhaften Ausführungsbeispiel ist der gesamte Verstärkungsbereich des Empfängers **1200** ausschließlich des Demodulators **1250** +51 dB bis -5 dB. Dieser Verstärkungsbereich besteht unter der Annahme eines beispielhaften Eingabeverlustes von -3 dB für den Bandpassfilter **1226**, einer Verstärkung von +1 dB für den Mischer **1230** und eines Eingabeverlustes von -13 dB für den Bandpassfilter **1232**. Für CDMA-Anwendungen wird typischerweise ein AGC-Bereich von 80 dB benötigt, um Pfadverlust, Fading-Verhältnisse und Störsender angemessen zu behandeln. In dem beispielhaften Ausführungsbeispiel ist der AGC-Bereich, der durch den Dämpfer **1216**, die LNAs **1220a** und **1220b** und die Dämpfungsglieder **1222a** und **1222b** vorgesehen wird, 56 dB. In dem beispielhaften Ausführungsbeispiel werden die verbleibenden 24 dB des AGC-Bereichs von dem Demodulator **1250** und/oder dem Verstärker **1234** vorgesehen. Innerhalb des Demodulators **1250** (siehe [Fig. 4](#)) quantisiert der ADC **1410** die analoge Wellenform und liefert die digitalisierten Werte an die nachfolgenden digitalen Signalverarbeitungsblöcke. In dem beispielhaften Ausführungsbeispiel ist die erforderliche Auflösung für den ADC **1410** vier Bits. In dem beispielhaften Ausführungsbeispiel sieht eine zusätzliche Auflösung von sechs Bits Spitzenbereich bzw. Spielraum für die noch ungefilterten Störsender vor. Der ADC **1410** kann so entworfen werden, dass er mehr als 10 Bits Auflösung vorsieht. Jedes zusätzliche Bit, das über 10 Bit hinausgeht, kann dazu verwendet werden, eine Verstärkungssteuerung von 6 dB vorzusehen. Glücklicherweise reichen die Pegel der Störsender außerhalb des Bandes bei hohen CDMA-Signalpegeln nicht über +72 dB über das CDMA-Signal hinaus. Deshalb benötigen die Störsendern, wenn das CDMA-Signal stark ist, eine geringere Auflösung als 6 Bits für den Spitzenbereich der Störsender. In dem beispielhaften Ausführungsbeispiel ist die AGC-Funktion, die in dem Demodulator **1250** durchgeführt wird, nur aktiv, wenn das CDMA-Signal stark ist, zum Beispiel am oberen Ende des CDMA-Steuerungsbereichs. Somit werden jetzt die zusätzlichen Bits an Auflösung, die zu Beginn für den Spitzenbereich der Störsender reserviert werden, aufgrund des starken CDMA-Signalpegels für die AGC-Funktion verwendet. Der Entwurf eines Subabtastungs-

bandpass- $\Sigma\Delta$ -ADC, der die Performance vorsieht, die für den Empfänger **1200** erforderlich ist, wird in der bereits erwähnten, anhängenden US-Patentanmeldung mit der Seriennummer 08/987,306 offenbart.

## II. Verstärkerentwurf

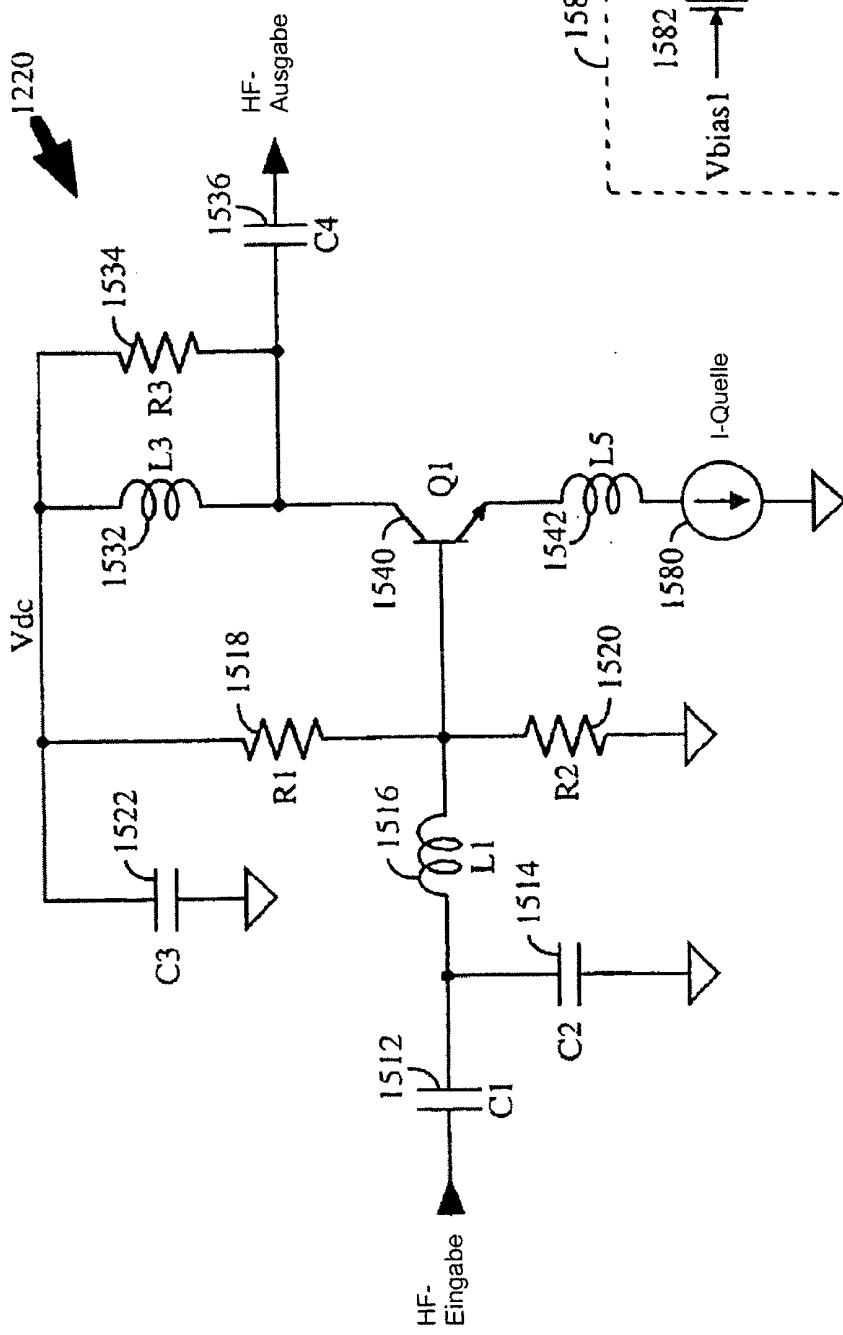

**[0049]** In [Fig. 5A](#) wird ein schematisches Diagramm eines beispielhaften diskreten LNA-Entwurfs gezeigt. Innerhalb des LNA **1220** wird die HF-Eingabe an ein Ende des Wechselspannungs- (AC) Kopplungskondensators **1514** und der Spule **1516** geliefert. Das andere Ende des Kondensators **1514** ist mit dem analogen Nullpotential verbunden und das andere Ende der Spule **1516** ist mit einem Ende der Widerstände **1518** und **1520** und der Basis des Transistors **1540** verbunden. Das andere Ende des Widerstands **1518** ist mit der Stromversorgung Vdc verbunden und das andere Ende des Widerstands **1520** ist mit dem analogen Nullpotential verbunden. Der Überbrückungskondensator **1522** ist mit Vdc und dem analogen Nullpotential verbunden. In dem beispielhaften Ausführungsbeispiel ist der Transistor **1540** ein HF-Transistor mit geringem Rauschen wie zum Beispiel der Siemens BFP420, der gewöhnlich nach dem Stand der Technik verwendet wird. Der Emitter des Transistors **1540** ist mit einem Ende der Spule **1542** verbunden. Das andere Ende der Spule **1542** ist mit der Stromquelle **1580** verbunden, die auch mit dem analogen Nullpotential verbunden ist. Der Kollektor des Transistors **1540** ist mit einem Ende der Spule **1532**, des Widerstands **1534** und des Kondensators **1536** verbunden. Das andere Ende der Spule **1532** und des Widerstands **1534** ist mit Vdc verbunden. Das andere Ende des Kondensators **1536** umfasst die HF-Ausgabe.

**[0050]** Innerhalb des LNA **1220**, sehen die Kondensatoren **1512** und **1536** jeweils eine Wechselstromkopplung der HF-Eingabe- und Ausgabesignale vor. Der Kondensator **1514** und die Spule **1516** sehen eine Rauschanpassung vor. Die Spule **1516** und **1532** sehen ebenfalls jeweils eine Anpassung der LNA-Eingabe und -Ausgabe vor. Die Spule **1532** sieht auch einen Gleichspannungs- (DC) Pfad für den Vorspannstrom des Transistors **1540** vor. Die Spule **1542** sieht eine Verringerung bzw. Degenerierung der Emitterimpedanz vor, um die Linearität zu verbessern. Die Widerstände **1518** und **1520** stellen das Gleichspannungs-Vorspannungspotenzial bzw. DC-Biasspannung bei der Basis des Transistors **1540** ein. Der Widerstand **1534** bestimmt die Verstärkung des LNA **1220** und die Ausgabeimpedanz. Die Stromquelle **1580** steuert den Vorspannstrom des Transistors **1540**, der den IIP3 des LNA **1220** bestimmt.

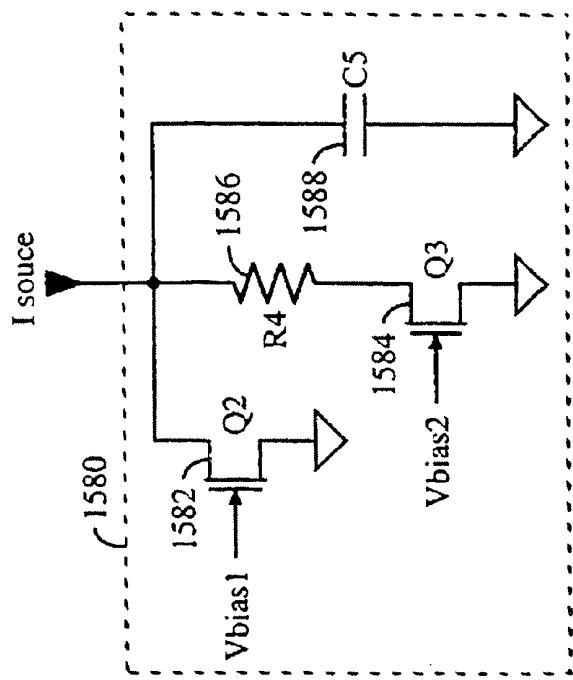

**[0051]** In [Fig. 5B](#) wird ein schematisches Diagramm einer beispielhaften Stromquelle **1580** gezeigt. Die Source-Kontakte der n-Kanal MOSFETs **1582** und **1584** sind mit dem analogen Nullpotential verbunden. Der Drain-Kontakt des MOSFET **1584** ist mit einem Ende des Widerstands **1586** verbunden. Das andere Ende des Widerstands **1586** ist mit dem Drain-Kontakt des MOSFET **1582** verbunden und umfasst die Ausgabe der Stromquelle **1580**. Der Überbrückungskondensator **1588** ist über die Ausgabe der Stromquelle **1580** und mit dem analogen Nullpotential verbunden. Das Gatter des MOSFET **1582** ist mit Vbias1 und das Gatter des MOSFET **1584** ist mit Vbias2 verbunden.

**[0052]** Die MOSFETs **1582** und **1584** liefern den Kollektorschaltstrom Icc zu dem Transistor **1540**, der wiederum den IIP3-Arbeitspunkt des LNA **1220** bestimmt. Die Gatter der MOSFETs **1582** und **1584** sind jeweils mit einer Steuerungsspannung Vbias1 beziehungsweise Vbias2 verbunden. Wenn Vbias1 niedrig ist (z.B. 0 Volt) wird der MOSFET **1582** ausgeschaltet und sieht keinen Kollektorschaltstrom Icc für den Transistor **1540** vor. Wenn Vbias1 hoch ist, (z.B. sich Vdc annähert) wird der MOSFET **1582** eingeschaltet und sieht den maximalen Kollektorschaltstrom für den Transistor **1540** vor. Somit bestimmt Vbias1 den Betrag des Kollektorschaltstroms Icc, der von dem MOSFET **1582** vorgesehen wird. In ähnlicher Weise bestimmt Vbias2 den Betrag des Kollektorschaltstroms, der vom MOSFET **1584** vorgesehen wird. Die Spannung an der Basis des Transistors **1540** und der Betrag des Widerstands **1586** begrenzen den maximalen Kollektorschaltstrom, der von dem MOSFET **1584** vorgesehen wird.

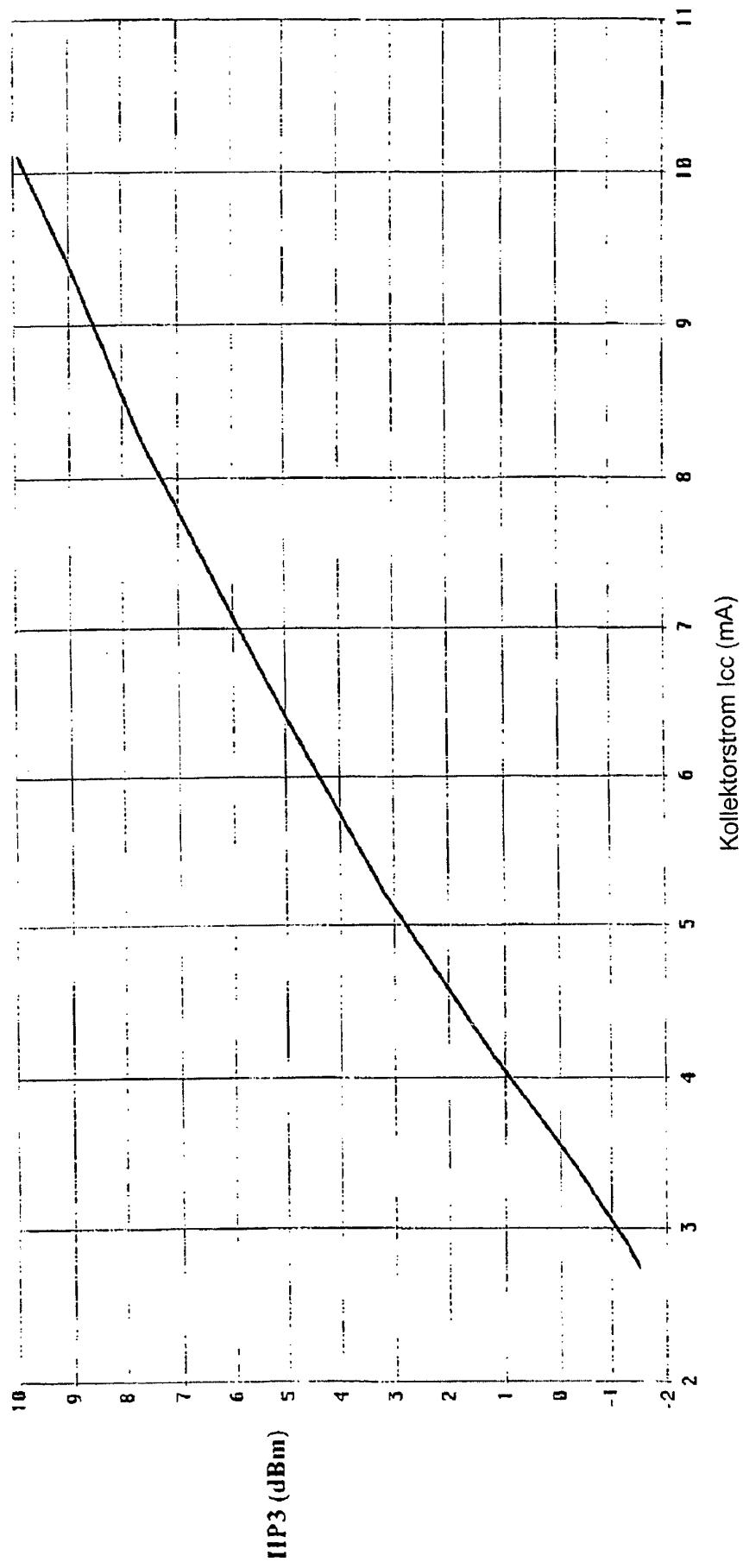

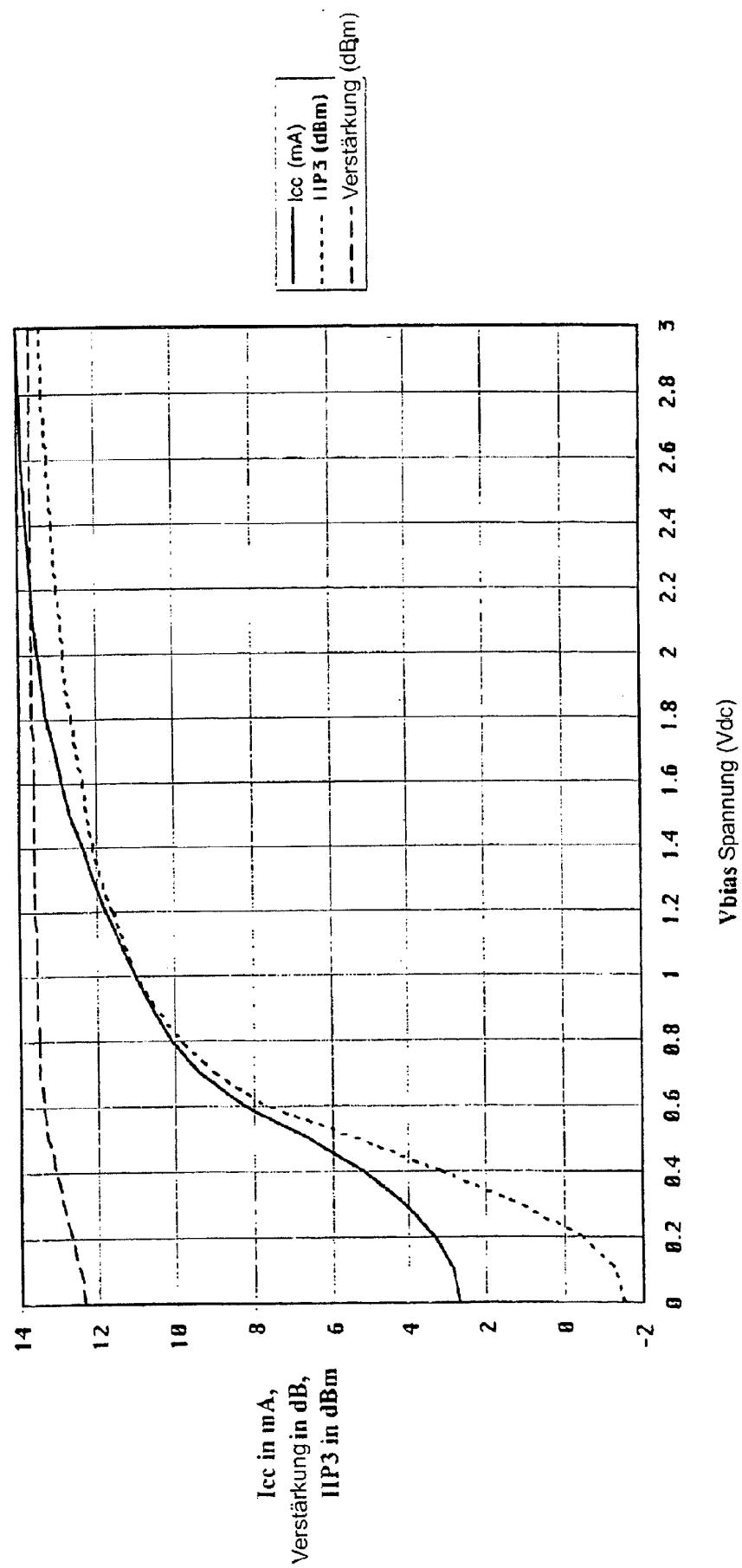

**[0053]** In [Fig. 6](#) ist die IIP3-Performance des LNA **1220** in Abhängigkeit des Kollektorschaltstroms Icc dargestellt. Man beachte, dass der IIP3 um ungefähr 6 dB ansteigt, wenn sich der Kollektorschaltstrom um eine Oktave erhöht (oder sich verdoppelt). In [Fig. 6B](#) sind der Kollektorschaltstrom des Transistors **1540**, die Verstärkung des LNA **1220** und der IIP3 des LNA **1220** in Abhängigkeit der Steuerungsspannung Vbias1 dargestellt. Man beachte, dass die Verstärkung näherungsweise konstant ist (z.B. Verstärkungsvariation von ungefähr 1 dB für alle Vbias1-Spannungen). Ebenfalls beachte man, dass der IIP3 in ähnlicher Weise in Abhängigkeit von dem Kollektorschaltstrom Icc variiert. Somit kann, wenn ein hoher IIP3 nicht erforderlich ist, der Kollektorschaltstrom mit einer minimalen Wirkung auf die Verstärkung des LNA **1220** vermindert werden.

**[0054]** [Fig. 5A](#) und [Fig. 5B](#) stellen jeweils einen beispielhaften Entwurf des LNA **1220** und einer Stromquelle

**1580** dar. Der LNA **1220** kann entworfen werden, indem andere Topologien verwendet werden, um die notwendige Performance (z.B. größere Verstärkung, besserer Rauschfaktor, bessere Anpassung bzw. matching) vorzusehen. Der LNA **1220** kann mit anderen aktiven Geräten entworfen werden wie Bipolartransistoren (BJT = bipolar-junction transistors), Heterojunction-Bipolartransistoren (HBT), Metalloxidhalbleiter-Feldeffekttransistor (MOSFET = metal-oxide-semiconductor field effect transistor), GaAs-Feldeffekttransistor (GaAsFET = gallium arsenide field effect transistor) oder andere aktive Geräte. Der LNA **1220** kann auch als monolithischer Verstärker nach dem Stand der Technik implementiert werden. In ähnlicher Weise kann die Stromquelle **1580** nach anderen Ansätzen gemäß dem Stand der Technik entworfen und implementiert werden. Die verschiedenen Implementierungen des LNA **1220** und der Stromquelle **1580** befinden sich innerhalb des Umfangs der vorliegenden Erfindung.

### III. Variable IIP3-Vorspannungssteuerung

**[0055]** Wie bereits beschrieben, können In-Band-Intermodulationsprodukte durch Störsignale erzeugt werden, die nichtlineare Geräte durchlaufen. Eine An-Wendung, die eine herausfordernde Linearitätsanforderung besitzt, ist ein CDMA-Kommunikationssystem, das mit anderen zellularen Telefonensystemen wie dem erweiterten Mobiltelefonsystem (AMPS = Advanced Mobile Phone System) kolokalisiert ist. Die anderen zellularen Telefonensysteme können Störsignale (oder Störsender) bei einer hohen Leistung in der Nähe des Betriebsbandes des CDMA-Systems senden, wodurch hohe IIP3-Anforderungen an den CDMA-Empfänger notwendig sind.

**[0056]** Die Anforderung an die Ablehnung von Störsignalen für einen CDMA-System wird in zwei Spezifikationen definiert, einem Zweitton-Test und einem Einfachton-Test in dem "TIA/EIA/IS-98-A Intermodulation Spurious Response Attenuation" im folgenden der IS-98-A-Standard. Der Zweitton-Test wird in [Fig. 7](#) dargestellt. Die zwei Töne sind von der zentralen Frequenz der CDMA-Wellenform aus bei  $f_1 = +900$  KHz und  $f_2 = +1700$  KHz lokalisiert. Die zwei Töne besitzen dieselbe Amplitude, die um 58 dB größer ist als die Amplitude des CDMA-Signals. Dieser Test simuliert ein FM-moduliertes Signal, das über den benachbarten Kanal gesendet wird, wie zum Beispiel das Signal von einem AMPS-System. Das FM-modulierte Signal beinhaltet den Großteil der Leistung in dem Träger, während die Leistung in der CDMA-Wellenform über die 1,2288 MHz-Bandbreite ausgetragen ist. Das CDMA-Signal ist bezüglich dem Zustand des Kanals stabiler und wird bei einem geringeren Leistungspegel durch eine Leistungssteuerungsschleife aufrechterhalten. In der Tat wird das CDMA-Signal bei dem minimalen Leistungspegel aufrechterhalten, der für ein erforderliches Performanceniveau nötig ist, um die Interferenz zu vermindern und die Kapazität zu erhöhen.

**[0057]** Der Einfachton-Test wird in [Fig. 7B](#) dargestellt. Der Einfachton befindet sich von der zentralen Frequenz der CDMA-Wellenform aus bei  $f_1 = +900$  KHz und hat eine Amplitude, die um +72 dBc größer ist als die Amplitude des CDMA-Signals.

**[0058]** Gemäß IS-98-A ist die Linearität des Empfängers bei dem CDMA-Eingabeleistungspegel festgelegt auf  $-101$  dBm,  $-90$  dBm und  $-79$  dBm. Für den Zweitton-Test befinden sich die Störsender bei  $-43$  dBm,  $-32$  dBm und  $-21$  dBm (+58 dBc) und das äquivalente In-Band-Signal des Intermodulationsprodukts befindet sich für den jeweiligen Eingabeleistungspegel von  $-101$  dBm,  $-90$  dBm und  $-79$  dBm bei jeweils  $-104$  dBm,  $-93$  dBm und  $-82$  dBm.

**[0059]** Wie in [Fig. 7A](#) dargestellt, erzeugen die Störtöne (oder Störsender) bei  $f_1 = +900$  KHz und  $f_2 = +1700$  KHz Intermodulationsprodukte dritter Ordnung bei  $(2f_1 - f_2) = +100$  KHz und  $(2f_2 - f_1) = +2500$  KHz. Das Produkt bei +2500 KHz kann durch die nachfolgenden Bandpassfilter **1226** und **1232** einfach gefiltert werden (siehe [Fig. 2](#)). Das Produkt bei +100 kHz jedoch befindet sich innerhalb der CDMA-Wellenform und verschlechtert das CDMA-Signal.

**[0060]** Um die Verschlechterung der Performance des Empfängers **1200** zu minimieren, wird der IIP3 der aktiven Geräte innerhalb des Empfängers **1200** gemäß dem Betrag an Nichtlinearität in dem empfangenen Signal angepasst. Der Empfänger **1200** ist so entworfen, dass er die Zweitton-Intermodulationsspezifikation erfüllt. In der Praxis jedoch sind die Störsender nur für einen Teil der Betriebszeit des Empfängers **1200** vorhanden. Deshalb wird die Amplitude der Störsender selten den festgelegten Pegel von +58 dB erreichen. Deshalb ist eine Auslegung für den Fall der schlimmsten Störsender und der Betrieb des Empfängers **1200** in dem hohen IIP3-Modus in Erwartung der schlimmsten Störsender eine Verschwendungen der Batterieleistung.

**[0061]** In der vorliegenden Erfindung wird der IIP3 der aktiven Geräte, im besonderen des LNA **1220b** und des Mischers **1230**, gemäß der gemessenen Nichtlinearität in dem Ausgabesignal von dem Empfänger **1200** angepasst. In dem beispielhaften Ausführungsbeispiel wird die Nichtlinearität über die RSSI-Steigungsmetho-

de gemessen. Die Messung der RSSI-Steigung wird im Detail in dem US-Patent mit der Nummer 5,107,225 beschrieben, mit dem Titel "High Dynamic Range Closed Loop Automatic Gain Control Circuit" erteilt am 21.4.1992, dem Rechtsnachfolger der vorliegenden Erfindung zugewiesen und hier als Referenz enthalten. Bezugnehmend auf [Fig. 2](#) hat der Bandpassfilter **1232** eine Bandbreite von 1,228 MHz und unterdrückt die meisten Störsender und Intermodulationsprodukte außerhalb des Bandes. Die Intermodulationsprodukte, die innerhalb des Bandes fallen, können nicht unterdrückt werden und werden zu der CDMA-Wellenform addiert. Das ZF-Signal von dem Verstärker **1234** wird an den Demodulator **1250** geliefert, der das ZF-Signal verarbeitet und die digitalisierten Basisbanddaten vorsieht, die die I- und Q-Daten umfassen. Die Basisbanddaten werden an die Nichtlinearitätsschaltung **1290** geliefert. In dem beispielhaften Ausführungsbeispiel errechnet die Nichtlinearitätsschaltung **1290** die Leistung des Signals gemäß der folgenden Gleichung:

$$P = (I^2 + Q^2), \quad (5)$$

wobei P die Leistung der Basisbandssignale und I und Q jeweils die Amplitude der I- und Q-Signale sind. Die Leistungsmessung wird an die Vorspannungssteuerungsschaltung **1280** geliefert.

**[0062]** Die Leistungsmessung beinhaltet die Leistung der gewünschten Basisband-I- und Q-Signale sowie die Leistung der Intermodulationsprodukte. Wie oben beschrieben, erhöhen sich die Intermodulationsprodukte für Nichtlinearität zweiter Ordnung für jeden Anstieg des Eingabesignalpegels von einem Dezibel um 2 dB. Für Nichtlinearität dritter Ordnung erhöhen sich die Intermodulationsprodukte für jede Erhöhung des Eingabesignalpegels von 1 dB um 3 dB. Somit kann der Betrag an Intermodulation abgeschätzt werden, indem man die RSSI-Steigung misst, die definiert ist als die Änderung des Ausgabesignalpegels in Abhängigkeit der Änderung des Eingabesignalpegels. Die Änderung des Eingabesignalpegels kann auf eine vorbestimmte Schrittweite (z.B. 0,5 dB) eingestellt werden. Für den Empfänger **1200** entspricht für den Betrieb in dem linearen Bereich eine 0,5 dB-Erhöhung des Eingabesignalpegels einer 0,5 dB-Erhöhung des Ausgabesignalpegels und einer RSSI-Steigung von 1,0. Wenn jedoch ein oder mehrere aktiven Geräte in den nichtlinearen Betriebsbereich übergehen, vergrößert sich die RSSI-Steigung. Eine höhere RSSI-Steigung entspricht einem größeren Pegel an Nichtlinearität. Eine RSSI-Steigung von 3,0 entspricht dem Betrieb des Empfängers **1200** in vollständiger Kompression (zum Beispiel kein Anstieg des gewünschten Ausgabesignalpegels, wenn sich die Eingabe erhöht) und bedeutet, dass die Ausgabe durch Intermodulationsprodukte dritter Ordnung dominiert wird.

**[0063]** In der vorliegenden Erfindung kann die RSSI-Steigung mit einem vorbestimmten RSSI-Schwellenwert verglichen werden. Wenn die RSSI-Steigung den Schwellenwert übersteigt, wird der IIP3 des richtigen aktiven Gerätes erhöht. Im anderen Fall, wenn die RSSI-Steigung sich unterhalb des RSSI-Schwellenwerts befindet, wird der IIP3 vermindert. Der RSSI-Schwellenwert kann während des Betriebs des Empfängers **1200** basierend auf der erforderlichen Bit-zu-Fehler-Rate (BER = bit-error-rate) oder Rahmen-zu-Fehler-Rate (FER = frame-error-rate) -Performance angepasst werden. Ein höherer RSSI-Schwellenwert gestattet einen höheren Pegel der Intermodulationsprodukte, bevor der IIP3 erhöht wird, wobei dadurch der Energieverbrauch auf Kosten der BER- oder FER-Performance minimiert wird. Der RSSI-Schwellenwert kann ebenfalls durch eine Steuerungsschleife angepasst werden, die den Schwellenwert für einen erforderlichen Performancepegel (zum Beispiel 1% FER) einstellt. In dem beispielhaften Ausführungsbeispiel wird eine RSSI-Steigung von 1,2 ausgewählt. Die Verwendung anderer RSSI-Schwellenwerte befindet sich jedoch innerhalb des Umfangs der vorliegenden Erfindung.

**[0064]** In der vorliegenden Erfindung ist es nicht kritisch, die Amplitude der Störsender direkt zu messen. Es ist wichtiger, die unerwünschte Wirkung der Störsender auf das gewünschte Signal hinsichtlich eines höheren Pegels an Intermodulationsprodukten zu messen. Die RSSI-Steigung ist ein Verfahren, um den Nichtlinearitätspegel zu messen. Der Nichtlinearitätspegel kann auch gemessen werden, indem die Änderung des Energie-pro-Chip-zu-Rauschen-Verhältnisses (Echo) des Ausgabesignals für eine kleine Änderung der Amplitude des Eingabesignals errechnet wird. Die Intermodulationsprodukte erhöhen sich um den Faktor eins bis drei, wenn der Empfänger **1200** sich in Kompression befindet und das Ausgabesignal durch Intermodulationsprodukte dritter Ordnung dominiert wird. Wie mit der RSSI-Steigungsmethode kann der Nichtlinearitätspegel durch die Änderung des Echo in Abhängigkeit der Änderung des Eingabesignalpegels abgeschätzt werden. Andere Methoden, die Nichtlinearitätspegel zu messen, sind vorstellbar und innerhalb des Umfangs der vorliegenden Erfindung.

**[0065]** In dem beispielhaften Ausführungsbeispiel wird der IIP3 der aktiven Geräte gemäß dem Betrag an Nichtlinearität angepasst (zum Beispiel über die Messung der RSSI-Steigung), der von jedem aktiven Gerät erfahren wird, um die Performance zu maximieren. Die LNAs **1220a** und **1220b** sehen eine feste Verstärkung vor. Somit erfährt der Mischer **1230** den größten Signalpegel, der LNA **1220b** erfährt den nächstgrößeren Si-

gnalpegel und der LNA **1220a** erfährt den kleinsten Signalpegel (dies setzt die Annahme voraus, dass die Verstärkung des LNA **1220a** größer als der Eingabeverlust des Bandpassfilters **1226** ist). Aufgrund dieser Annahmen wird der IIP3-Arbeitspunkt des Mischers **1230** zuerst erhöht, wenn ein Störsender erfasst wird (z.B. über die Messung einer hohen RSSI-Steigung). Sobald der IIP3 des Mischers **1230** vollständig angepasst ist (z.B. an den höchsten IIP3-Arbeitspunkt) wird der IIP3 des LNA **1220b** erhöht. Sobald der IIP3 des LNA **1220b** vollständig angepasst ist, kann zuletzt der IIP3 des LNA **1220a** erhöht werden. In dem beispielhaften Ausführungsbeispiel wird der LNA **1220a** bei einem vorbestimmten IIP3-Arbeitspunkt gehalten, um die Performance des Empfängers **1200** zu optimieren. Entsprechend kann der IIP3 des LNA **1220b** zuerst vermindert werden, wenn keine Störsender erfasst werden. Sobald der IIP3 des LNA **1220b** vollständig angepasst ist (zum Beispiel auf dem geringsten IIP3-Arbeitspunkt), wird der IIP3 des Mischers **1230** vermindert.

**[0066]** Der IIP3 des LNA **1220b** und der Mischer **1230** können auf kontinuierliche Weise (zum Beispiel indem kontinuierliche Vbias1- und Vbias2-Steuerungsspannungen vorgesehen werden) oder in diskreten Schritten angepasst werden. Die vorliegende Erfindung ist ausgerichtet auf die Verwendung von kontinuierlichen, diskreten Schritten oder anderen Verfahren, um den IIP3 der aktiven Geräte zu steuern.

**[0067]** Die oben beschriebene Reihenfolge der IIP3-Anpassung setzt die Annahme voraus, dass nur der IIP3 in Betracht gezogen wird. Verschiedene Anwendungen können jedoch verschiedenen Eingabeverhältnissen ausgesetzt sein und besitzen verschiedene Performanceansprüche. Die Reihenfolge der IIP3-Anpassung kann neu geordnet werden, um diesen Ansprüchen gerecht zu werden. Weiterhin kann die Reihenfolge der IIP3-Anpassung bezüglich der oben beschriebenen Reihenfolge umgekehrt werden (zum Beispiel Verminde rung des IIP3 für einen steigenden Eingabesignalpegel), um die Performance des Empfängers **1200** für eine bestimmte Betriebsbedingung zu optimieren. Eine unterschiedliche Reihenfolge der IIP3-Anpassung und eine unterschiedliche Richtung der IIP3-Anpassung befinden sich innerhalb des Umfangs der vorliegenden Erfindung.

#### IV. Verstärkungssteuerung

**[0068]** Die meisten Empfänger sind so entworfen, dass sie einen breiten Bereich von Eingabesignalpegeln zulassen. Für CDMA-Empfänger ist der erforderliche AGC-Bereich nominell 80 dB. In dem beispielhaften Ausführungsbeispiel der vorliegenden Erfindung (siehe [Fig. 2](#)) wird der AGC-Bereich von dem Dämpfer **1216**, den LNAs **1220a** und **1220b**, den Dämpfungsgliedern **1222a** und **1222b**, den Demodulator **1250** und möglicherweise dem Verstärker **1234** vorgesehen. In dem beispielhaften Ausführungsbeispiel sieht der Dämpfer **1216** einen AGC-Bereich von 20 dB vor, das Dämpfungsglied **1222a** und **1222b** sieht jeweils einen AGC-Bereich von 5 dB vor, der LNA **1220a** und **1220b** sieht jeweils einen AGC-Bereich von 13 dB vor und der Verstärker **1234** und/oder der Demodulator **1250** sieht einen AGC-Bereich von 24 dB vor. Der AGC-Bereich einer oder mehrerer dieser Komponenten kann angepasst werden und befindet sich innerhalb des Umfangs der vorliegenden Erfindung. Weiterhin kann der Verstärker **1234** so entworfen werden, um einen AGC-Bereich vorzusehen, um die AGC-Bereiche der anderen Komponenten zu ergänzen. Zum Beispiel kann der AGC-Bereich der Dämpfungsglieder **1222** auf jeweils 2 dB vermindert werden und der Verstärker **1234** kann mit einem AGC-Bereich von 6 dB entworfen werden.

**[0069]** In dem beispielhaften Ausführungsbeispiel werden die ersten 2 dB des AGC-Bereichs von dem Demodulator **1250** vorgesehen. Der Demodulator **1250** umfasst den Bandpass-Subabtastungs- $\Sigma\Delta$ -ADC **1410**, der zusätzliche Auflösungsbits vorsieht, die für die AGC-Steuerung verwendet werden können. Die nächsten 20 dB des AGC-Bereichs werden von dem Dämpfer **1216** und/oder dem Verstärker **1234** vorgesehen. Die nächsten 18 dB des AGC-Bereichs werden von den LNAs **1220a** und dem Dämpfungsglied **1222a** vorgesehen. Die nächsten 18 dB des AGC-Bereichs werden von den LNAs **1220b** und dem Dämpfungsglied **1222b** vorgesehen. Und die verbleibenden 22 dB des AGC-Bereichs werden von dem Verstärker **1234** und/oder dem Demodulator **1250** vorgesehen.

**[0070]** In [Fig. 8A](#) wird ein beispielhaftes Diagramm gezeigt, dass den AGC-Steuerungsbetrieb des Empfängers **1200** der vorliegenden Erfindung für steigende CDMA-Eingabesignalleistung darstellt. In diesem Beispiel ist der Verstärker **1234** aus Gründen der Einfachheit als ein Verstärker mit fester Verstärkung implementiert. Der CDMA-Eingabe Leistungspegel kann sich zwischen -104 dBm und -24 dBm befinden. Zwischen -104 dBm und -102 dBm sind die LNAs **1220a** und **1220b** eingeschaltet, die Schalter **1224a** und **1124b** sind ausgeschaltet, und der AGC wird von dem Demodulator **1053** vorgesehen. Zwischen -102 dBm und -85 dBm wird der AGC von dem Dämpfer **1216** vorgesehen. Zwischen -84 dBm und -62 dBm ist der LNA **1220a** ausgeschaltet, der Schalter **1224a** eingeschaltet, der LNA **1220b** bleibt eingeschaltet, der Schalter **1224b** bleibt ausgeschaltet und der AGC wird von dem Dämpfer **1216** vorgesehen. Und der AGC wird von dem Dämpfer **1216**

vorgesehen. Zwischen –63 dBm und –46 dBm sind die LNAs **1220a** und **1220b** ausgeschaltet, der ZF-Signalpegel in den Demodulator **1250** hinein erhöht sich um 1 dB für einen Anstieg des Eingabe-HF-Signalpegels um 1 dB und der AGC wird nach dem ADC **1410** durch den Demodulator **1250** vorgesehen.

**[0071]** In [Fig. 8B](#) wird ein beispielhaftes Diagramm gezeigt, das den AGC-Steuerungsbetrieb des Empfängers **1200** für eine abnehmende CDMA-Signalleistung darstellt. In diesem Beispiel wird ebenfalls aus Gründen der Einfachheit der Verstärker **1234** als ein Verstärker mit fester Verstärkung implementiert. Zwischen –24 dBm und –46 dBm sind die LNAs **1220a** und **1220b** ausgeschaltet, die Schalter **1124a** und **1124b** sind eingeschaltet und der AGC wird nach dem ADC **1410** durch den Demodulator **1250** vorgesehen. Zwischen –46 dBm und –66 dBm wird der AGC von dem Dämpfer **1216** vorgesehen. Zwischen –66 dBm und –69 dBm befindet sich der Dämpfer **1216** in dem minimalen Dämpfungszustand und der AGC wird von dem Demodulator **1250** vorgesehen. Bei –70 dBm ist der LNA **1220b** eingeschaltet und der Schalter **1224b** ausgeschaltet. Zwischen –70 dBm und –84 dBm wird der AGC von dem Dämpfer **1216** vorgesehen. Zwischen –84 dBm und –90 dBm wird der AGC von den Demodulator **1250** vorgesehen. Bei –91 dBm ist der LNA **1220a** eingeschaltet und der Schalter **1124a** ist ausgeschaltet. Zwischen –91 dBm und –102 dBm wird der AGC von dem Dämpfer **1216** vorgesehen. Und zwischen –102 dBm und –104 dBm wird der AGC von den Demodulator **1250** vorgesehen.

**[0072]** [Fig. 8A](#)-[Fig. 8B](#) stellen die Eingabe-HF-Signalpegel dar, wobei die LNAs **1220a** und **1220b** eingeschaltet und ausgeschaltet sind. Der LNA **1220a** wird ausgeschaltet, wenn der Eingabesignalpegel –85 dBm übersteigt (siehe [Fig. 8A](#)), wird aber nicht wieder eingeschaltet, bis der Signalpegel unterhalb von –91 dBm sinkt. Die Hysterese von 6 dB hindert den LNA **1220a**, zwischen dem eingeschalteten und ausgeschalteten Zustand zu fluktuieren. Der LNA **1220b** ist aus demselben Grund auch mit einer Hysterese von 6 dB vorgesehen. Verschiedene Hysteresebeträge können verwendet werden, um die Systemperformance zu optimieren und befinden sich innerhalb des Umfangs der vorliegenden Erfindung.

**[0073]** Die obige Beschreibung stellt eine beispielhafte Implementierung der benötigten AGC-Steuerung dar. Die AGC-Steuerung kann auch mit AGC-Verstärkern implementiert werden, die anpassbare Verstärkungen besitzen. Weiterhin ist die Anordnung des Dämpfers **1216** und der LNAs **1220a** und **1220b**, wie dargestellt in [Fig. 2](#), nur eine Implementierung, die die CDMA-Spezifikation erfüllt. Andere Implementierungen der AGC-Funktionalitäten, die die hier beschriebenen Elemente verwenden, und andere Implementierungen, die diese Elemente in Kombination mit anderen Elementen oder Schaltungen verwenden, die nach dem Stand der Technik bekannt sind, gehören zum Umfang der vorliegenden Erfindung.

#### V. Empfängereinstellung gemäß der gemessenen Nichtlinearität

**[0074]** In dem ersten Ausführungsbeispiel der vorliegenden Erfindung werden die IIP3 der aktiven Geräte gemäß den gemessenen Nichtlinearitätspegel eingestellt, der von dem Empfänger **1200** erzeugt wird. Der Nichtlinearitätspegel kann mit der RSSI-Steigung oder mit der Ec/Io-Messung abgeschätzt werden. In [Fig. 9](#) wird das Timing-Diagramm einer beispielhaften Implementierung einer RSSI-Steigungsmessung dargestellt. In dem beispielhaften Ausführungsbeispiel wird der Eingabe-HF-Signalpegel verändert, indem die Dämpfung des Dämpfers **1316** in schmalen Pulsen verändert wird. Jeder Puls wird als ein sogenannter "Wiggle" bezeichnet. Die RSSI-Steigung wird für jeden Puls gemessen und die Messungen werden über eine vorbestimmte Periode T gemittelt, um die Genauigkeit der RSSI-Steigungsmessung zu verbessern. Am Ende der Periode T wird die gemessene RSSI-Steigung mit dem RSSI-Schwellenwert verglichen und das Ergebnis wird dazu verwendet, um den IIP3 der aktiven Geräte auf die oben beschriebene Weise anzupassen.

**[0075]** Wie in [Fig. 9](#) gezeigt wird, ist die RSSI-Steigungsmessung bei  $T_0$  kleiner als der RSSI-Schwellenwert, was anzeigt, dass der Empfänger **1200** innerhalb der linearen Grenzen arbeitet. Somit wird der IIP3 des LNA **1220b** vermindert, um Energie zu sparen. In ähnlicher Weise ist am Ende der Zeitspannen  $T_1$ ,  $T_2$ , und  $T_3$  die gemessene RSSI-Steigung kleiner als der RSSI-Schwellenwert und der IIP3 des LNA **1220b** wird weiterhin vermindert. Am Ende der Zeitspanne  $T_4$  ist die gemessene RSSI-Steigung immer noch geringer als der RSSI-Schwellenwert und der IIP3 des Mischers **1230** wird vermindert, weil der IIP3 des LNA **1220b** vollständig auf dem minimalen IIP3-Arbeitspunkt angepasst wurde. Am Ende der Zeitspanne  $T_5$  ist die gemessene RSSI-Steigung größer als der RSSI-Schwellenwert, was anzeigt, dass die Intermodulationsprodukte auf einen unakzeptablen Pegel angestiegen sind. Der IIP3 des Mischers **1230** wird daraufhin erhöht, um die Linearität zu verbessern.

**[0076]** In dem beispielhaften Ausführungsbeispiel besitzt jeder Puls eine Länge von 200  $\mu$ s, die Zeitspanne T ist 5 ms lang und die Anzahl der Pulse innerhalb einer Zeitspanne T ist neun. Unter Verwendung dieser Werte beträgt der Arbeitszyklus 36%. In dem bevorzugten Ausführungsbeispiel sollte der Arbeitszyklus der Pulse ge-

ring genug sein, so dass der Echo des gewünschten Signals durch die periodische Störung der Signalamplitude minimal verschlechtert wird. Die Pulsbreite wird so ausgewählt, dass sie kurz andauert, um die Störung der AGC-Steuerungsschaltung **1280** zu minimieren. Typischerweise ist die AGC-Steuerungsschleife langsam und kann den Änderungen des Signalpegels, die durch die kurzen Dämpfungspulse verursacht werden, nicht folgen. Dieses besonders wichtig, weil die Veränderung der Amplitude des Ausgabesignals die Veränderungen der Amplitude des Eingabesignals und der Intermodulationsprodukte genau wiedergeben sollte und nicht die Veränderungen, die von der AGC-Steuerungsschaltung **1280** verursacht werden. Eine kurze Pulsbreite jedoch resultiert in einer weniger genauen Messung der Ausgabesignalleistung. Die vorliegende Erfindung ist ausgerichtet auf die Verwendung von Pulsen mit verschiedenen Breiten und verschiedene Arbeitszyklen für die hier beschriebenen Funktionen.

**[0077]** Die Amplitude der Störung in dem Eingabe-HF-Signalpegel wird so ausgewählt, dass sie klein ist, um die Verschlechterung des Ausgabesignals zu minimieren sowie die Wirkung auf den IIP3 des gesamten Empfängers **1200** zu minimieren. In dem beispielhaften Ausführungsbeispiel beträgt der Dämpfungsschritt für die RSSI-Steigungsmessung 0,5 dB. Für den Dämpfungsschritt können andere Werte verwendet werden, wobei diese zu dem Umfang der vorliegenden Erfindung gehören.

**[0078]** In dem beispielhaften Ausführungsbeispiel wird ein RSSI-Schwellenwert von 1,2 ausgewählt. Die Verwendung eines RSSI-Schwellenwerts kann dazu führen dass die IIP3-Arbeitspunkte zwischen aufeinander folgenden Zeitspannen T fluktuieren. Um dies zu verhindern können zwei RSSI-Schwellenwerte verwendet werden, um Hysterese vorzusehen. Der IIP3 wird nicht erhöht, es sei denn, die gemessene RSSI-Steigung übersteigt den ersten RSSI-Schwellenwert und der IIP3 wird nicht vermindert, es sei denn, die gemessene RSSI-Steigung befindet sich unterhalb des zweiten RSSI-Schwellenwerts. Die Verwendung eines einzelnen Schwellenwerts oder mehrere Schwellenwerte gehört zu dem Umfang der vorliegenden Erfindung.

**[0079]** In [Fig. 10A](#) wird ein Diagramm gezeigt, das den IIP3-Vorspannungssteuerungsbetrieb des Empfängers **1200** der vorliegenden Erfindung für einen zunehmenden HF-Leistungspegel darstellt. Das Eingabe-HF-Signal umfasst ein CDMA-Signal und Zweitton-Störsender, die sich +58 dBc oberhalb des CDMA-Signals befinden. Wenn sich die CDMA-Signalleistung zwischen –104 dBm und –101 dBm befindet, wird der IIP3 des Mischers **1230** auf +10 dBm eingestellt und der IIP3 der LNAs **1220a** und **1220b** wird auf 0 dBm eingestellt. Wenn das CDMA-Signal unterhalb von –101 dBm fällt, übersteigt die gemessene RSSI-Steigung den RSSI-Schwellenwert und der IIP3 des Mischers **1230** wird auf +15 dBm erhöht, um den Nichtlinearitätspegel zu minimieren. Der Dämpfer **1216** sieht eine Dämpfung des Eingabe-HF-Signals vor, die zwischen –104 dBm und –84 dBm liegt. Bei –84 dBm wird der LNA **1220a** überbrückt und der Dämpfer **1216** stellt sich auf seinen Zustand mit niedriger Dämpfung zurück. Wenn sich die CDMA-Signalleistung bei –83 dBm, –79 dBm, –75 dBm und –71 dBm befindet, wird der IIP3 des LNA **1220b** erhöht, um die Intermodulationsprodukte zu minimieren. Bei ungefähr –64 dBm wird der LNA **1220b** überbrückt und der Dämpfer **1216** stellt sich erneut auf seinen Zustand mit geringer Dämpfung zurück.

**[0080]** In [Fig. 10B](#) wird ein Diagramm gezeigt, dass den IIP3-Vorspannungssteuerungsbetrieb des Empfängers **1200** für abnehmenden Eingabe-HF-Leistungspegel darstellt. Wieder umfasst das Eingabe-HF-Signal ein CDMA-Signal und Zweitton-Störsender, die sich +58 dBc oberhalb des CDMA-Signals befinden. Wenn sich zu Beginn die CDMA-Signalleistung bei –60 dBm befindet, werden die LNAs **1220a** und **1220b** überbrückt. Wenn die CDMA-Signalleistung auf –70 dBm fällt, wird der LNA **1220b** eingeschaltet, um die nötige Verstärkung vorzusehen. Bei ungefähr –76 dBm, –80 dBm, –84 dBm und –88 dBm Wert der IIP3 des LNA **1220b** vermindert, um den Energieverbrauch zu minimieren. Bei –90 dBm erreicht der Dämpfer **1216** seinen oberen Dämpfungsbereich und der LNA **1220a** wird eingeschaltet. Bei –100 dBm wird der IIP3 des Mischers **1230** vermindert, um Energie zu sparen, weil der Eingabe-HF-Signalpegel klein ist.

**[0081]** Wie oben beschrieben, wird der Eingabe-HF-Leistungspegel dort von der gemessenen RSSI-Steigung bestimmt, wo der IIP3 des Mischers **1230** und der LNAs **1220a** und **1220b** angepasst wird. Wie in [Fig. 10A](#) und [Fig. 10B](#) gezeigt, kann die RSSI-Steigungsmessung zu IIP3-Vorspannungsschaltungspunkten führen, die keinen linearen Abstand besitzen. Weiterhin können die schrittweisen Schaltungspunkte durch eine kontinuierlich anpassbare Vorspannungssteuerung ersetzt werden.

## VI. Empfängereinstellungen gemäß dem Betriebsmodus

**[0082]** In dem zweiten Ausführungsbeispiel der vorliegenden Erfindung wird der IIP3 der aktiven Geräte gemäß dem Betriebsmodus des Empfängers eingestellt. Wie oben dargestellt, kann der Empfänger **1300** (siehe [Fig. 3](#)) in einem zellularen Telefon verwendet werden, welches den Betrieb in entweder einem PCS- oder zel-

lularen Band erfordert. Jedes Band kann entweder digitale und/oder analoge Plattformen unterstützen. Jede Plattform kann weiterhin eine Vielzahl von Betriebsmodi umfassen. Die verschiedenen Betriebsmodi werden dazu verwendet, um die Performance zu verbessern und Batterieenergie zu sparen. Verschiedene Betriebsmodi werden zum Beispiel verwendet, um die folgenden Merkmale eines zellularen Telefons zu unterstützen: (1) geschlitztes Modus-Paging für eine längere Stand-by-Zeit, (2) Verstärkungsschritt für dynamische Bereichsvergrößerung, (3) punktierte Senderausgabe für längere Gesprächszeit, (4) Frequenzbandwahl für Dual-Band-Telefone (PCS und zellular), (5) Vielfachzugriffsschalten zwischen Systemen (CDMA, AMPS, GSM etc.) und (6) Mittel zur Schaltungsvorspannungssteuerung in Anwesenheit von Störsendern.

**[0083]** Die Betriebsmodi des zellularen Telefons besitzen verschiedene Performanceanforderungen. In dem beispielhaften Ausführungsbeispiel wird jeder Betriebsmodus einem einzigen Identifizierer zugeordnet, der N Modusbits umfasst. Die Modusbits definieren bestimmte Charakteristiken des Betriebsmodus. Zum Beispiel kann ein Modusbit dazu verwendet werden, um zwischen dem PCS- und dem zellularen Band auszuwählen und ein anderes Modusbit kann dazu verwendet werden, um zwischen digitalen (CDMA) oder analogen (FM) Modus auszuwählen. Die N Modusbits werden an eine logische Schaltungseinheit innerhalb des Kontrollers **1370** geliefert, die die N Modusbits in einen Steuerungsbustbus decodiert, der bis zu  $2^N$  Steuerungsbits umfasst. Der Steuerungsbustbus wird an Schaltungen innerhalb des Empfängers **1300** weitergeleitet, die Steuerung benötigen. Zum Beispiel kann der Steuerungsbustbus folgendes anweisen: (1) Einstellung des IIP3 des Mischers innerhalb des HF/ZF-Prozessors **1348** und der LNAs innerhalb der HF-Prozessoren **1310a** und **1310b**, (2) Einstellung der Verstärkung des Empfängers **1300**, (3) Einstellung der Vorspannungsgleichspannungen und/oder -stroms auf eine andere HF- und ZF-Schaltungseinheit innerhalb des Empfängers **1300**, (4) Auswahl des gewünschten Signalbands und (5) Einstellen der Oszillatoren auf die richtige Frequenzen.

**[0084]** In der Tabelle 1 und 2 wird eine beispielhafte Implementierung der IIP3-Steuerung für den Empfänger **1300** basierend auf dem Betriebsmodus dargestellt. Der Empfänger **1300** unterstützt Dualband (PCS und zellular) und Dualmodus (CDMA und FM). In dem beispielhaften Ausführungsbeispiel unterstützt das PCS-Band nur CDMA-Übertragung, während das zellulare Band sowohl CDMA- als auch FM-Übertragungen unterstützt (die FM-Übertragung kann aus dem AMPS-System erfolgen). In dem beispielhaften Ausführungsbeispiel werden vier Modusbits verwendet. Die vier Modusbits sind die BAND\_SELECT-, IDLE/-, FM/- und LNA\_RANGE-Bits. Das BAND\_SELECT-Bit bestimmt das Betriebsband und ist definiert als 1 = PCS und 0 = zellular. Das IDLE-/Bit (0 = Leerlauf) schaltet den Empfänger **1300** in den Leerlaufmodus (zum Beispiel Betrieb bei geringerem IIP3), während das zellulare Telefon inaktiv ist. Das FM-/Bit (0 = FM) stellt den Empfänger **1300** so ein, dass er ein FM-Signal verarbeitet. Und das LNA\_RANGE-/Bit (1 = Überbrückung) stellt die Verstärkung des Empfängers **1300** ein. Wenn das LNA\_RANGE-/Bit auf hohen Wert eingestellt ist, wird der Überbrückungsmodus auszeichnet, werden Vbias1 und Vbias2 des ersten LNA **1320a** oder **1321a** auf niedrigen Wert eingestellt und der LNA wird ausgeschaltet.