## (19) World Intellectual Property Organization

International Bureau

#

#### (43) International Publication Date 17 April 2008 (17.04.2008)

### (10) International Publication Number WO 2008/045887 A1

(51) International Patent Classification: H01L 21/78 (2006.01)

(21) International Application Number:

PCT/US2007/080838

(22) International Filing Date: 9 October 2007 (09.10.2007)

(25) Filing Language: English

(26) Publication Language: English

(30) Priority Data:

11/548.647 11 October 2006 (11.10.2006)

(71) Applicant (for all designated States except US): SEMI-PHOTONICS CO., LTD. [CN/CN]; 7F, No.13 Ke Jung Rd., Chu-Nan Site, Hsinchu Science Park, Miao-Li County, Chu-nan, 350 (TW).

(72) Inventors; and

(75) Inventors/Applicants (for US only): CHU, Chen-fu [CN/CN]; No. 19, Alley 2, Lane 239, Minsheng Rd., Hsinchu City, 300 (TW). DOAN, Trung Tri [US/CN]; No. 2, Lane 38, Songcui Road, Baoshan Township (TW). TRAN, Chuong Anh [US/CN]; Lane 81, No. 1, Songcuei Rd., Hsinchu County 308, Baoshan Township, 308 (TW). CHENG, Chao-chen [CN/CN]; 4F, No. 20, Lane 23, Jianjhong 1st Rd., Hsinchu City, 300 (TW). CHU, Jiunn-yi [CN/CN]; 3F-2, No. 340, Guangming 5th St., Hsinchu County, Chubei City, 302 (TW). LIU, Wen-huang [CN/CN]; No. 13-1. 11 Neighborhood, Hsinchu County, 306, Bei-shan Village, Guan-xi Town, 306 (TW). CHENG, Hao-chun [CN/CN]; No. 16, Lane 185, Jhongjheng Rd., Pingtung County 928, Donggang Township, 928 (TW). FAN, Feng-hsu [CN/CN]; 3F, No. 6-2, Alley 2, Lane 31, Minli St., Taipei County 235, Jhonghe City, 235 (TW). YEN, Jui-kang [CN/CN]; 8 F, No. 362, Sec. 4, Chengde Rd., Shihlin District, Taipei City, 111 (TW).

- (74) Agents: PATTERSON, B. Todd et al.; Patterson & Sheridan, L.L.P., 3040 Post Oak Blvd., Suite 1500, Houston, TX 77056-6582 (US).

- (81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AT, AU, AZ, BA, BB, BG, BH, BR, BW, BY, BZ, CA, CH, CN, CO, CR, CU, CZ, DE, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IS, JP, KE, KG, KM, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LT, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PG, PH, PL,

[Continued on next page]

(54) Title: DIE SEPARATION

(57) Abstract: Techniques for dicing wafer assemblies containing multiple metal device dies, such as vertical light-emitting diode (VLED), power device, laser diode, and vertical cavity surface emitting laser device dies, are provided. Devices produced accordingly may benefit from greater yields and enhanced performance over conventional metal devices, such as higher brightness of the light-emitting diode and increased thermal conductivity. Moreover, such techniques are applicable to GaN-based electronic devices in cases where there is a high heat dissipation rate of the metal devices that have an original non- (or low) thermally conductive and/or non- (or low) electrically conductive carrier substrate that has been removed.

## WO 2008/045887 A1

PT, RO, RS, RU, SC, SD, SE, SG, SK, SL, SM, SV, SY, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

(84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LS, MW, MZ, NA, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European (AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI,

FR, GB, GR, HU, IE, IS, IT, LT, LU, LV, MC, MT, NL, PL, PT, RO, SE, SI, SK, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

#### Published:

- with international search report

- before the expiration of the time limit for amending the claims and to be republished in the event of receipt of amendments

SEMI/0039PCT

#### **DIE SEPARATION**

#### **TECHNICAL FIELD**

[0001] Embodiments of the present invention generally relate to a metal device, such as a light emitting diode (LED), a power device, a laser diode, and a vertical cavity surface emitting device, and methods for fabricating the same.

#### **BACKGROUND**

[0002] Microelectronic devices, such as metal devices, are playing an increasingly important role in our daily life. For instance, LEDs have become ubiquitous in many applications, such as mobile phones, appliances, and other electronic devices. Recently, the demand for nitride-based semiconductor materials (e.g., having gallium nitride or GaN) for opto-electronics has increased dramatically for applications ranging from video displays and optical storage to lighting and medical instruments.

[0003] Conventional blue LEDs are formed using compound semiconductor materials with nitride, such as GaN, AlGaN, InGaN, and AlInGaN. Most of the semiconductor layers of these light-emitting devices are epitaxially formed on electrically non-conductive sapphire substrates.

#### SUMMARY OF THE INVENTION

[0004] One embodiment of the invention is a method of dicing a wafer assembly comprising a plurality of semiconductor dies disposed on a metal substrate. The method generally includes applying a laser between a first and a second die to cut through at least a portion of the wafer assembly and applying a physical force to fully separate the first die from the second die.

[0005] Another embodiment of the invention is a method of separating a plurality of vertical light-emitting diode (VLED) dies disposed on a metal substrate. The method generally includes applying a laser between adjacent VLED dies of the plurality to cut through any

1

SEMI/0039PCT

semiconductor material between the adjacent VLED dies and at least a portion of the metal substrate and physically forcing the adjacent VLED dies apart.

#### BRIEF DESCRIPTION OF THE DRAWINGS

[0006] Figs. 1a-c illustrate dicing a wafer assembly into individual semiconductor dies in accordance with embodiments of the invention; and

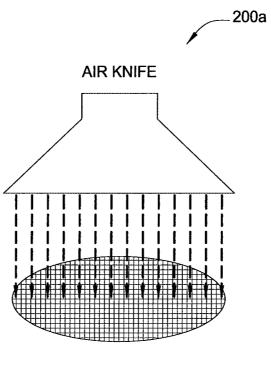

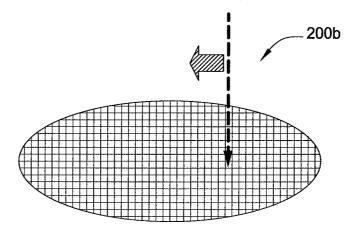

[0007] Figs. 2a-b illustrate dicing the wafer assembly with an air knife or a water jet with a chemical solution in accordance with embodiments of the invention.

### **DETAILED DESCRIPTION**

[0008] Embodiments of the invention provide improvements in the art of fabricating light-emitting diodes (LEDs), including higher yield and better performance, such as higher brightness of the LED and better thermal conductivity. Moreover, the description discloses embodiments in the fabrication arts that are applicable to GaN-based electronic devices such as vertical light-emitting diodes (VLEDs), power devices, laser diodes, and vertical cavity surface emitting laser devices in cases where there is a high heat dissipation rate of the metal devices that have an original non- (or low) thermally conductivity and/or non- (or low) electrically conductive substrate that has been removed.

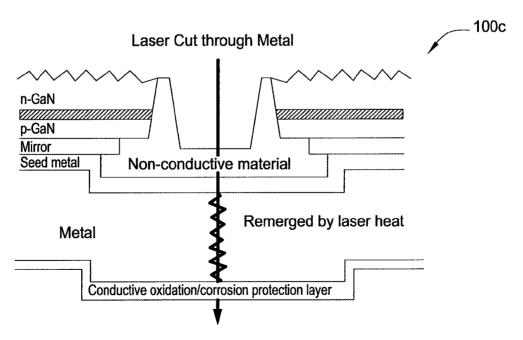

[0009] Fig. 1a depicts an example of a wafer assembly 100a having multiple n-GaN-up vertical light diode emitting (VLED) structures, where the light passes through the n-GaN to the environment outside the VLED structure, that need to be separated into individual semiconductor dies. A multilayer epitaxial structure (EPI) may be formed with an n-type GaN layer, one or more quantum wells with InGaN/GaN layers, and a p-type AlGaN/GaN layer. Although the n-type layer and the p-type layer may comprise various compound semiconductor materials, such as GaN, AlGaN, InGaN, and AlInGaN, n-GaN and p-GaN layers will be described henceforth. Various methods known to those skilled in the art may have been employed to define the distinct VLED structures.

[0010] For some VLED structures before die separation, a mirror may be disposed below the p-GaN to act as the reflector for photons. The mirror, by way of example, may be

SEMI/0039PCT

composed of multiple layers, such as Ni/Ag/Ni/Au, Ag/Ni/Au, Ti/Ag/Ni/Au, Ag/Pt or Ag/Pd or Ag/Cr, using an alloy containing Ag, Au, Cr, Pt, Pd, or Al.

[0011] One or more electrically non-conductive layers, which may also be thermally conductive layers, (hereinafter referred to as the "non-conductive material") may have been used to fill the street, the area between the defined devices. The non-conductive material that fills the street may also cover at least a portion of the lateral surfaces of the p-GaN in an effort to further protect the multiple quantum well (MQW) active area.

[0012] A deposition of one or more metal layers may have been made on top of the mirror and the non-conductive material before the carrier substrate was removed in an effort to create one thick metal plate, for instance, labeled as "metal." In Fig. 1a, the wafer assembly 100a has already been inverted after removal of the carrier substrate, so the metal is shown below the mirror and epitaxial structures. The one or more deposited metal layers may have been formed by electrochemical deposition (ECD) or electroless chemical deposition (ElessCD), CVD, plasma enhanced chemical vapor deposition (PECVD), physical vapor deposition (PVD), evaporation, or plasma spray. The metal layer may be single or multi-layered. In cases where the metal layer is a multi-layered structure, a plurality of metal layers with different composition (*e.g.*, Cu, Ni, Ag, Au, Co, Cu-Co, Cu-Mo, Ni/Cu, Ni/Cu-Mo, and their alloys) may have been formed, and these layers may have been formed using different techniques. For some embodiments, the thickest metal layer may have been deposited using ECD or ElessCD, where the thickest metal layer can be any layer within the multiple layers of metal. The thickness of each metal layer may be about 10~400 μm.

[0013] Before depositing the metal layer(s) using electrochemical or electroless chemical deposition techniques, a seed metal that is preferably electrically conductive may have been formed as seen in Figs. 1a-c. The seed metal may be composed of copper, nickel, or tungsten that may have been deposited as one or more layers by first using evaporation, sputtering, chemical vapor deposition (CVD), or metal organic chemical vapor deposition (MOCVD) of the tungsten before using ECD to form the copper and the nickel. In the case of ECD or ElessCD for the metal layer, a deposit of conductive

SEMI/0039PCT

materials may have been made so as to form a seed metal. The seed metal may have assisted the growth of a single metal layer or of multiple metal layers via electroplating or an electroless plating process. In such cases, the seed metal may have a structure such as Ta/Cu, Ta/TaN/Cu, Ta/TaN/Cu, Ti/TaN/Cu, Ta/TiN/Cu, Ti/TiN/Cu, Ti/TiN/Cu, Cr/Au, Cr/Au/Ti/Ni/Au, Cr/Au/Ti/Ni/Au, Ti/Au, or Ti/Ni/Au.

[0014] One or more additional metal layers may have been formed above the original metal layer in an effort to protect the underlying metal layers (labeled as "Conductive oxidation/corrosion protection layer" in Figs. 1a-c). Such additional protective metal layers may comprise, for example, Cr/Au, Ni, or Ni/Au.

[0015] After separating the carrier substrate from the epitaxial wafer assembly and, in some cases, inverting the wafer assembly as shown in Fig. 1a, the wafer assembly may be diced (*i.e.*, dicing into individual semiconductor dies) using various steps. In these steps, methods to separate the dies include using a breaker, an air knife, or a water jet with a chemical solution (for coating the anti-oxidizing material on the cut edge of copper).

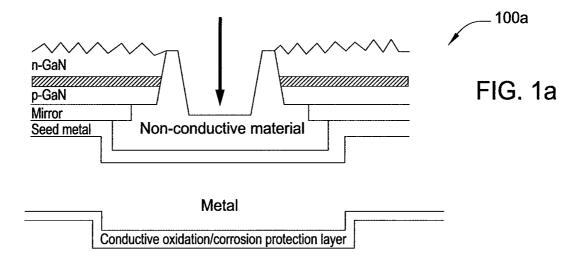

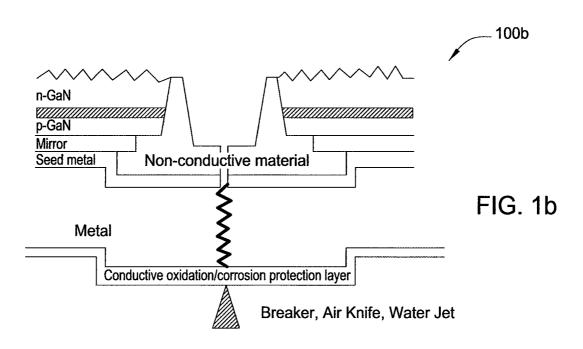

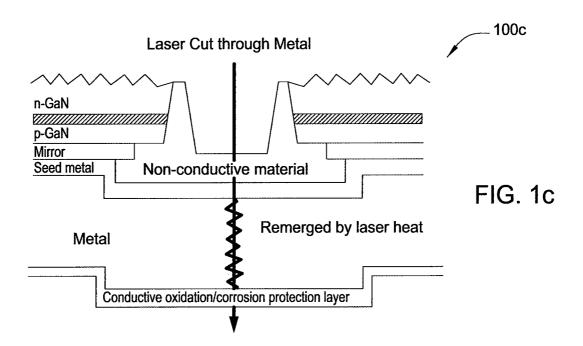

[0016] For some embodiments, a wafer assembly having dies disposed thereon may be separated by laser cut, saw cut, or water jet processes. This is represented by a downward force seen in wafer assembly 100a in Fig. 1a. After a laser has been used to cut the metal substrate, the metal may remerge together from the laser heating, as seen in wafer assembly 100b in Fig. 1b. Then, the dies may be fully separated by the application of a light force such as by using a breaker, a knife, an air knife, or a water jet, as shown regarding wafer assembly 100c in Fig. 1c.

[0017] In that the force of the breaker may be too strong and cause damage to the electrical devices, the dies may be separated by using an air knife to carefully control the dicing of the wafer, as shown regarding wafer assembly 200a in Fig. 2a.

[0018] For the case of laser cutting, it may be advantageous to protect the devices with a removable protecting coating (e.g., a polymer coating) before cutting in order to protect the devices from the debris that can be formed during the laser cutting process. It may

SEMI/0039PCT

also be advantageous to cut the devices in an oxygen-containing environment for manufacturing and junction properties.

[0019] After the laser cutting process, the devices may be cleaned in a liquid and/or a solvent in an effort to effectively remove the debris, to remove the protective coating if one is used, and to clean/passivate the junction. The liquid may be a base or an acid solution with or without an oxidizer (e.g., H2SO4:H2O2, HNO3, HNO3/HCI, NH4OH:H2O2, KOH:H2O2, and H3PO4). The solutions may be heated or may be used at room temperature. Any solvent may be used to clean the devices in an effort to remove the removable protective coating on the surface of the wafer. The solvent may be used with or without a surfactant and may be a water solution. The solvent may be used first, followed by the liquid. Alternatively, the liquid may be used first, followed by the solvent. For some embodiments, only the liquid may be used to clean the devices, or only the solvent may be used to clean the devices. It may be preferred, however, to remove the protecting coating first with the solvent, and then clean/passivate the junction with the liquid.

[0020] For the dicing, especially after a laser cutting operation, an anti-oxidizing passivation may be applied to the edges of the dies, such as by the use of a chemical water jet solution, as shown in Fig. 2b. The chemical solution may be, for example, a Cu, Pd, Ni, or Au plating solution.

[0021] Embodiments disclosed herein may also be applied to the fabrication of GaN-based electronic devices such as power devices, laser diodes, and vertical cavity surface emitting laser device due to its high heat dissipation rate of its metal substrate. Relative to conventional LEDs, the above teaching can improve yield, brightness, and thermal conductivity.

[0022] While the foregoing is directed to embodiments of the present invention, other and further embodiments of the invention may be devised without departing from the basic scope thereof, and the scope thereof is determined by the claims that follow.

5

SEMI/0039PCT

#### What is claimed is:

1. A method of dicing a wafer assembly comprising a plurality of semiconductor dies disposed on a metal substrate, the method comprising:

- (a) applying a laser between a first and a second die to cut through at least a portion of the wafer assembly; and

- (b) applying a physical force to fully separate the first die from the second die.

- 2. The method of claim 1, further comprising repeating step (a) for all of the plurality of semiconductor dies.

- 3. The method of claim 2, further comprising repeating step (b) for all of the plurality of semiconductor dies.

- 4. The method of claim 1, wherein the at least a portion of the wafer assembly comprises any semiconductor material between the first and second dies and at least a portion of the metal substrate.

- 5. The method of claim 4, wherein the at least a portion of the metal substrate remerges after applying the laser.

- 6. The method of claim 1, wherein applying the physical force comprises applying at least one of a breaker, a knife, an air knife, or a water jet.

- 7. The method of claim 6, wherein the water jet comprises only water.

- 8. The method of claim 1, wherein applying the physical force comprises applying a water jet with a chemical solution.

- 9. The method of claim 8, wherein the chemical solution is an acid or a base.

- 10. The method of claim 9, wherein the chemical solution comprises at least one of H2SO4:H2O2, HNO3, HNO3/HCI, NH4OH:H2O2, KOH:H2O2, or H3PO4.

- 11. The method of claim 8, wherein the chemical solution is at least one of a Cu, Pd, Ni, or Au plating solution.

#### SEMI/0039PCT

12. The method of claim 8, wherein applying the water jet with the chemical solution leaves an anti-oxidizing passivation layer on edges of the first and second dies.

- 13. The method of claim 1, wherein the metal substrate comprises at least one of Cu, Ni, Au, Aq, Co, or alloys thereof.

- 14. The method of claim 1, wherein the metal substrate comprises a seed metal layer and a thick metal layer.

- 15. The method of claim 14, wherein the seed metal layer comprises at least one of Cu, Ni, W, Ta/Cu, Ta/TaN/Cu, TaN/Cu, Ti/TaN/Cu, Ta/TiN/Cu, Ti/Cu, Ti/TiN/Cu, TiN/Cu, Cr/Au, Cr/Au/Ni/Au, Ti/Au, or Ti/Ni/Au.

- 16. The method of claim 1, wherein the semiconductor dies are light-emitting diode (LED) dies, power device dies, laser diode dies, or vertical cavity surface emitting device dies.

- 17. A method of separating a plurality of vertical light-emitting diode (VLED) dies disposed on a metal substrate, the method comprising:

- (a) applying a laser between adjacent VLED dies of the plurality to cut through any semiconductor material between the adjacent VLED dies and at least a portion of the metal substrate; and

- (b) physically forcing the adjacent VLED dies apart.

- 18. The method of claim 17, wherein physically forcing the adjacent VLED dies apart comprises breaking a remerged portion of the metal substrate between the adjacent VLED dies.

- 19. The method of claim 17, wherein physically forcing the adjacent VLED dies apart comprises applying at least one of a breaker, a knife, an air knife, or a water jet.

- 20. The method of claim 17, wherein physically forcing the adjacent VLED dies apart comprises applying a water jet with a chemical solution.

#### SEMI/0039PCT

21. The method of claim 20, wherein the chemical solution is at least one of a Cu, Pd, Ni, or Au plating solution.

- 22. The method of claim 20, wherein applying the water jet with the chemical solution leaves an anti-oxidizing passivation layer on edges of the first and second dies.

- 23. The method of claim 17, wherein the VLED dies comprise at least one of GaN, AlGaN, InGaN, or AlInGaN.

1/3

2/3

3/3

FIG. 2a

## WATER JET WITH CHEMICAL SOLUTION

FIG. 2b

# INTERNATIONAL SEARCH REPORT PCT/US2097/08083

PCT/US 07/80838

CLASSIFICATION OF SUBJECT MATTER IPC(8) - H01L 21/78 (2008.01) USPC - 438/460; 438/463 According to International Patent Classification (IPC) or to both national classification and IPC FIELDS SEARCHED Minimum documentation searched (classification system followed by classification symbols) IPC(8)-H01L 21/00 (2008.01) USPC- 438/460; 438/463 Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched Electronic data base consulted during the international search (name of data base and, where practicable, search terms used) PubWest (USPT, PG, PB, EPAB, JPAB); DialogPRO (Engineering); Google Scholar Search Terms Used: wafer assembly, first die, second die, metal substrate, laser DOCUMENTS CONSIDERED TO BE RELEVANT Citation of document, with indication, where appropriate, of the relevant passages Relevant to claim No. Category\* US 2006/0040472 A1 (Tamura et al.) 23 February 2006 (23.02.2006), para [0034], [0035]; х 1-6 [0040], [0024], [0023], [0036], [0033], [0050] Υ 7-23 US 2005/0031822 A1 (Aihara et al.) 10 February 2005 (10.02.2005), para [0059], [0082], [0089], 7-15 and 20-22 [0091], [0169], [0214] US 2005/0186783 A1 (Hon et al.) 25 August 2005 (25.08.2005), para [0011], [0014] 16-23 Υ 1-23 US 2005/0191791 A1 (Hartwell et al.) 01 September 2005 (01.09.2005), para [0030], [0033], [0038], [0043] Further documents are listed in the continuation of Box C. Special categories of cited documents: later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention document defining the general state of the art which is not considered to be of particular relevance earlier application or patent but published on or after the international document of particular relevance; the claimed invention cannot be filing date considered novel or cannot be considered to involve an inventive document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other step when the document is taken alone document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art special reason (as specified) document referring to an oral disclosure, use, exhibition or other document published prior to the international filing date but later than "&" document member of the same patent family the priority date claimed Date of mailing of the international search report Date of the actual completion of the international search 03 MAR 2008 26 December 2007 (26.12.2007) Name and mailing address of the ISA/US Authorized officer:  $\theta$ Lee W. Young Mail Stop PCT, Attn: ISA/US, Commissioner for Patents P.O. Box 1450, Alexandria, Virginia 22313-1450 PCT Helpdesk: 571-272-4300 Facsimile No. 571-273-3201 PCT OSP: 571-272-7774