(19)

Bundesrepublik Deutschland

Deutsches Patent- und Markenamt

(10) **DE 600 21 939 T2 2006.03.30**

(12)

## Übersetzung der europäischen Patentschrift

(97) **EP 1 037 213 B1**

(21) Deutsches Aktenzeichen: **600 21 939.9**

(96) Europäisches Aktenzeichen: **00 300 946.1**

(96) Europäischer Anmeldetag: **07.02.2000**

(97) Erstveröffentlichung durch das EPA: **20.09.2000**

(97) Veröffentlichungstag

der Patenterteilung beim EPA: **17.08.2005**

(47) Veröffentlichungstag im Patentblatt: **30.03.2006**

(51) Int Cl.<sup>8</sup>: **G11C 11/22 (2006.01)**

**G11C 14/00 (2006.01)**

**G11C 7/20 (2006.01)**

(30) Unionspriorität:

**7263999 17.03.1999 JP**

(84) Benannte Vertragsstaaten:

**DE, FR, GB**

(73) Patentinhaber:

**Fujitsu Ltd., Kawasaki, Kanagawa, JP**

(72) Erfinder:

**Kato, Tatsuo, Kawasaki-shi, Kanagawa 211-8588, JP**

(74) Vertreter:

**W. Seeger und Kollegen, 81369 München**

(54) Bezeichnung: **Ferroelektrische Speicheranordnung die Festwertdaten festhält**

Anmerkung: Innerhalb von neun Monaten nach der Bekanntmachung des Hinweises auf die Erteilung des europäischen Patents kann jedermann beim Europäischen Patentamt gegen das erteilte europäische Patent Einspruch einlegen. Der Einspruch ist schriftlich einzureichen und zu begründen. Er gilt erst als eingelebt, wenn die Einspruchsgebühr entrichtet worden ist (Art. 99 (1) Europäisches Patentübereinkommen).

Die Übersetzung ist gemäß Artikel II § 3 Abs. 1 IntPatÜG 1991 vom Patentinhaber eingereicht worden. Sie wurde vom Deutschen Patent- und Markenamt inhaltlich nicht geprüft.

## Beschreibung

**[0001]** Die vorliegende Erfindung betrifft eine ferroelektrische Speichervorrichtung, in der ferroelektrische Kondensatoren verwendet werden.

**[0002]** In den letzten Jahren ist eine ferroelektrische Speichervorrichtung, in der ferroelektrische Kondensatoren verwendet werden, als nichtflüchtiger Speicher vorgeschlagen worden. Die ferroelektrische Speichervorrichtung speichert und liest Daten unter Verwendung ihrer Hysteresekarakteristik und Restpolarisationswirkung, die in einem ferroelektrischen Film des ferroelektrischen Kondensators enthalten ist. Durch das Anwenden eines elektrischen Feldes auf den ferroelektrischen Kondensator in einer Richtung nimmt der ferroelektrische Kondensator einen polarisierten Zustand in einer Richtung ein. Durch das Anwenden eines elektrischen Feldes auf den ferroelektrischen Kondensator in der anderen Richtung nimmt der ferroelektrische Kondensator alternativ einen polarisierten Zustand in der umgekehrten Richtung an. Solch ein polarisierter Zustand kann als Restpolarisation auch dann gehalten werden, nachdem ein elektrisches Feld erloschen ist, das auf den ferroelektrischen Kondensator angewendet wird. Deshalb wird die ferroelektrische Speichervorrichtung als nichtflüchtiger Speicher verwendet, worin Daten auch dann gehalten werden können, wenn die Energie AUS ist.

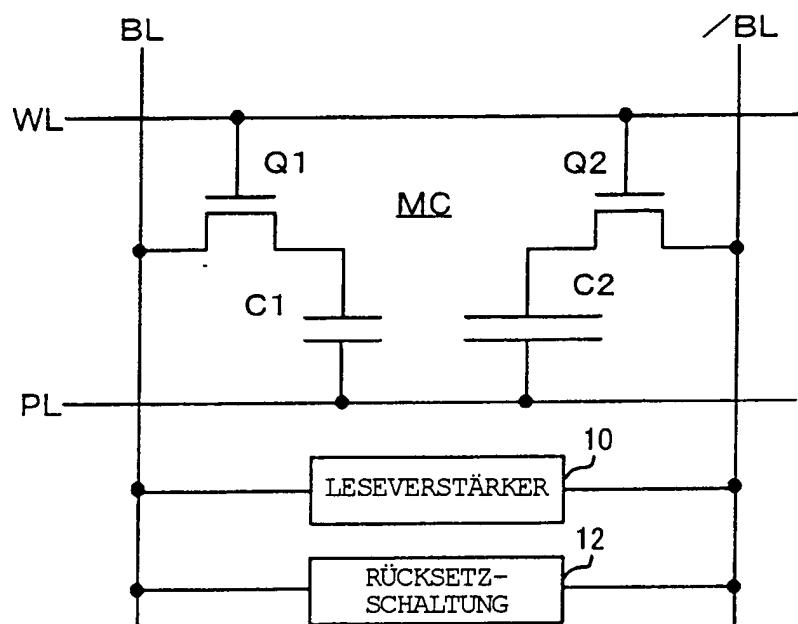

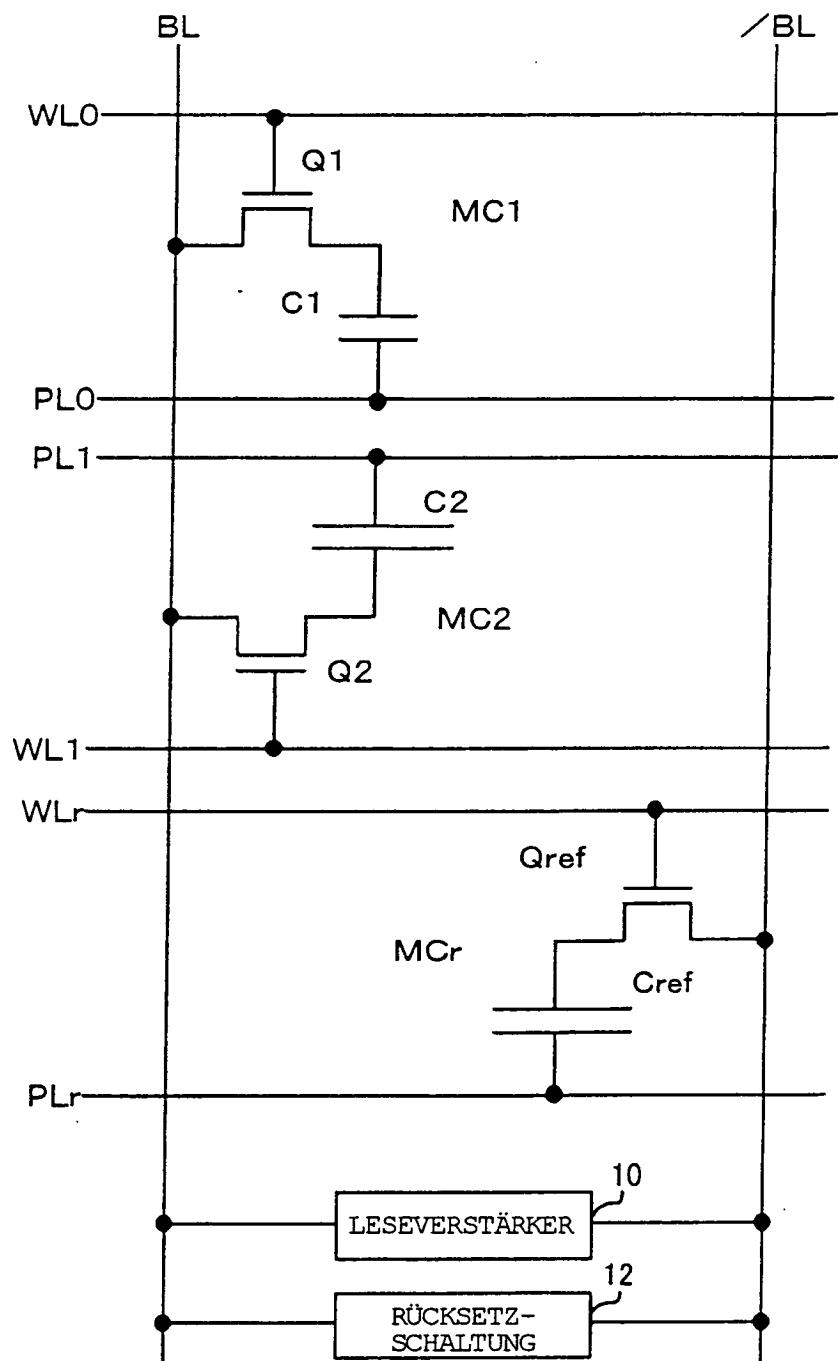

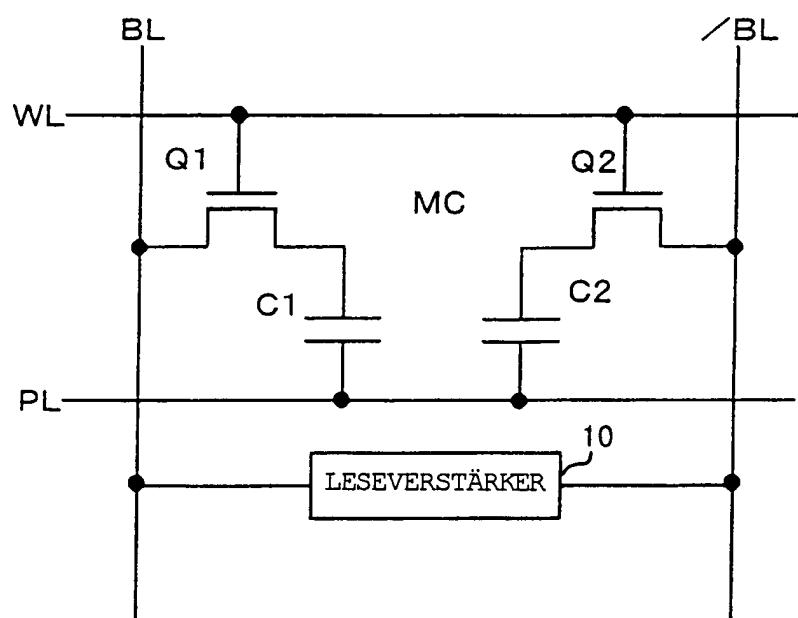

**[0003]** [Fig. 9](#) ist ein Schaltungsdiagramm einer ferroelektrischen Speicherzelle nach Stand der Technik. Die Struktur einer Speicherzelle MC von [Fig. 9](#) wird als 2T2C-Struktur bezeichnet, in der ein Paar von Transistoren Q1, Q2 und ein Paar von ferroelektrischen Kondensatoren C1, C2, die mit jedem der Transistoren verbunden sind, enthalten sind. Jeder der Transistoren Q1, Q2 hat ein Gate, das mit einer Wortleitung WL verbunden ist, und eine Source- oder Drain-Elektrode, mit der jeweils eine von dem Bitleitungspaar BL, /BL verbunden ist. Zusätzlich sind die ferroelektrischen Kondensatoren C1, C2 mit einer Plattenleitung PL verbunden. Ein Leseverstärker **10** ist mit einem Bitleitungspaar BL, /BL verbunden.

**[0004]** Daten werden durch das Polarisieren eines Kondensatorpaars C1, C2 der Speicherzelle MC aufgezeichnet, die in [Fig. 9](#) gezeigt ist, und die aufgezeichneten Daten werden bei dem später erläuterten Verfahren ausgelesen.

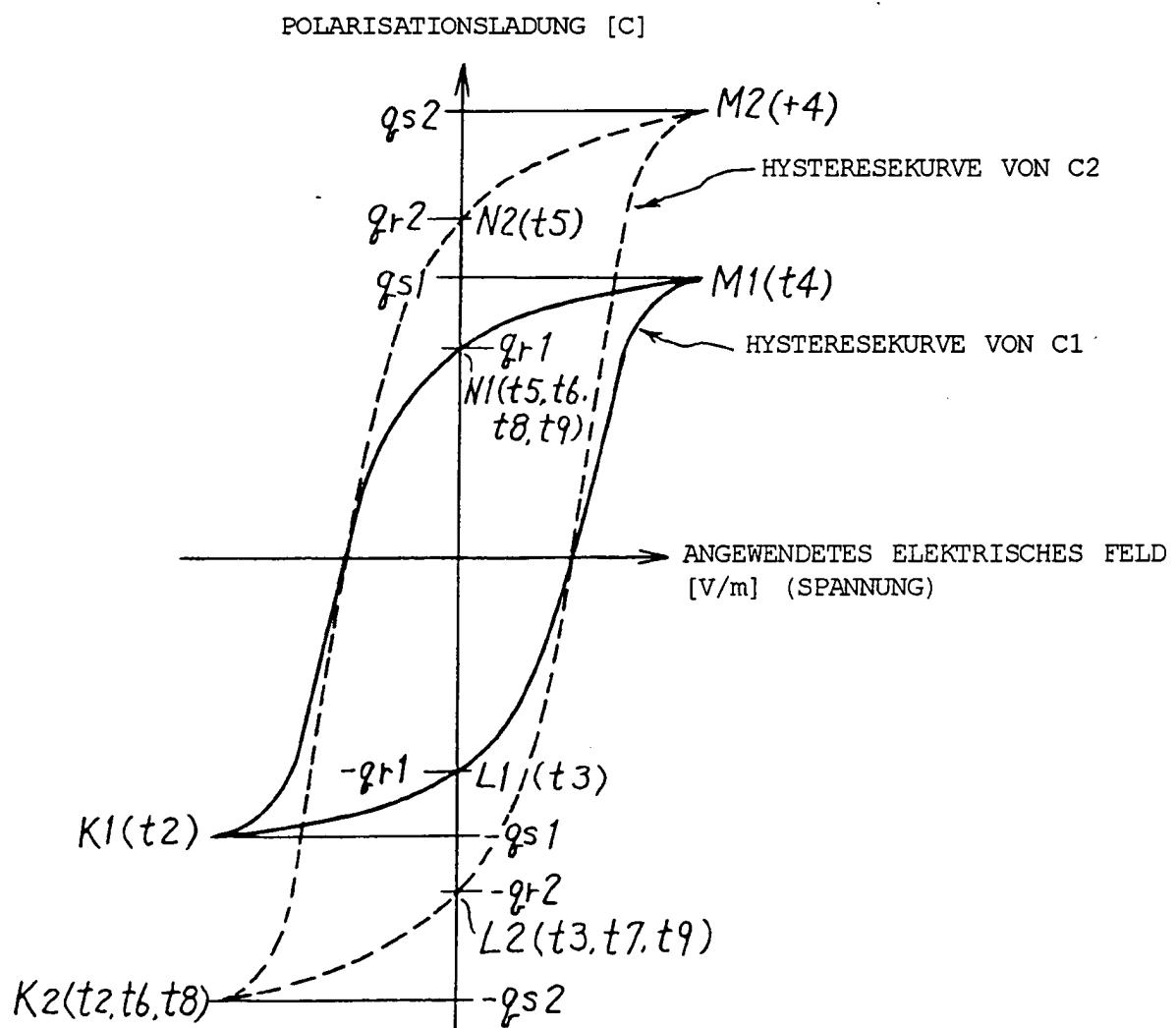

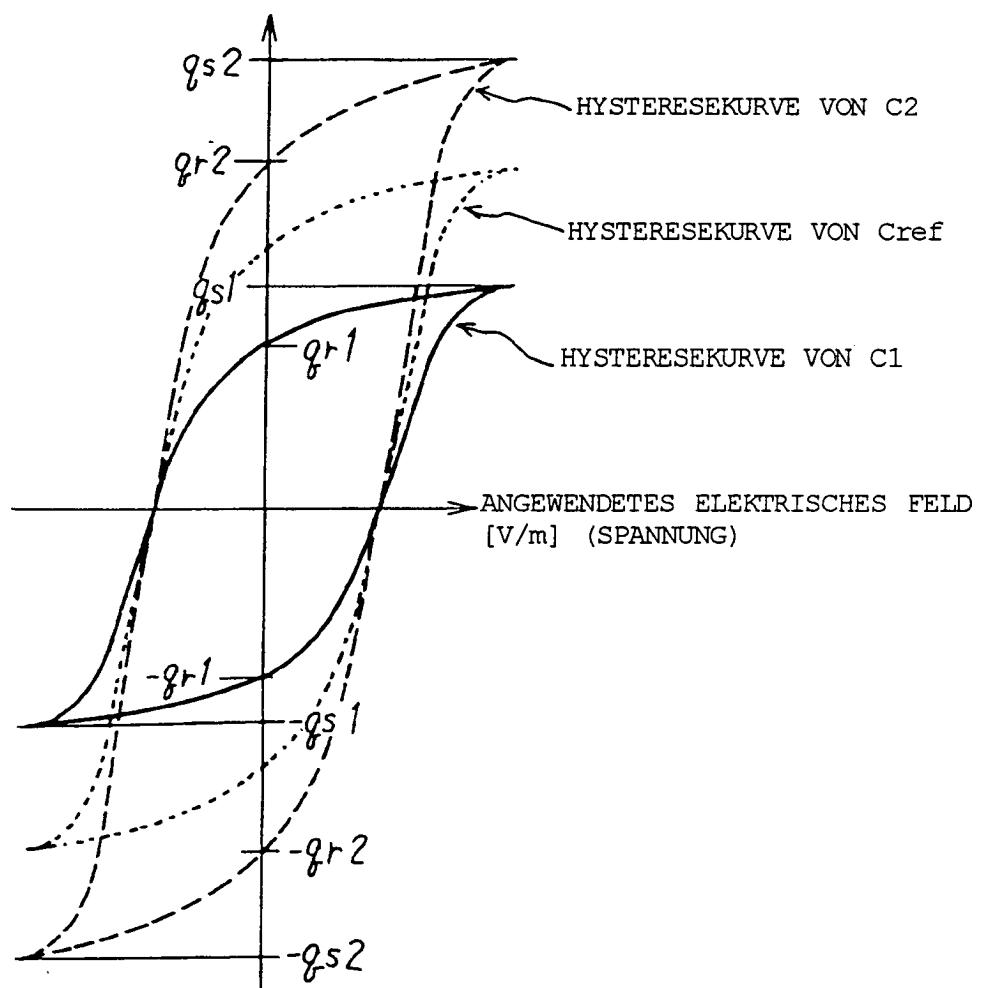

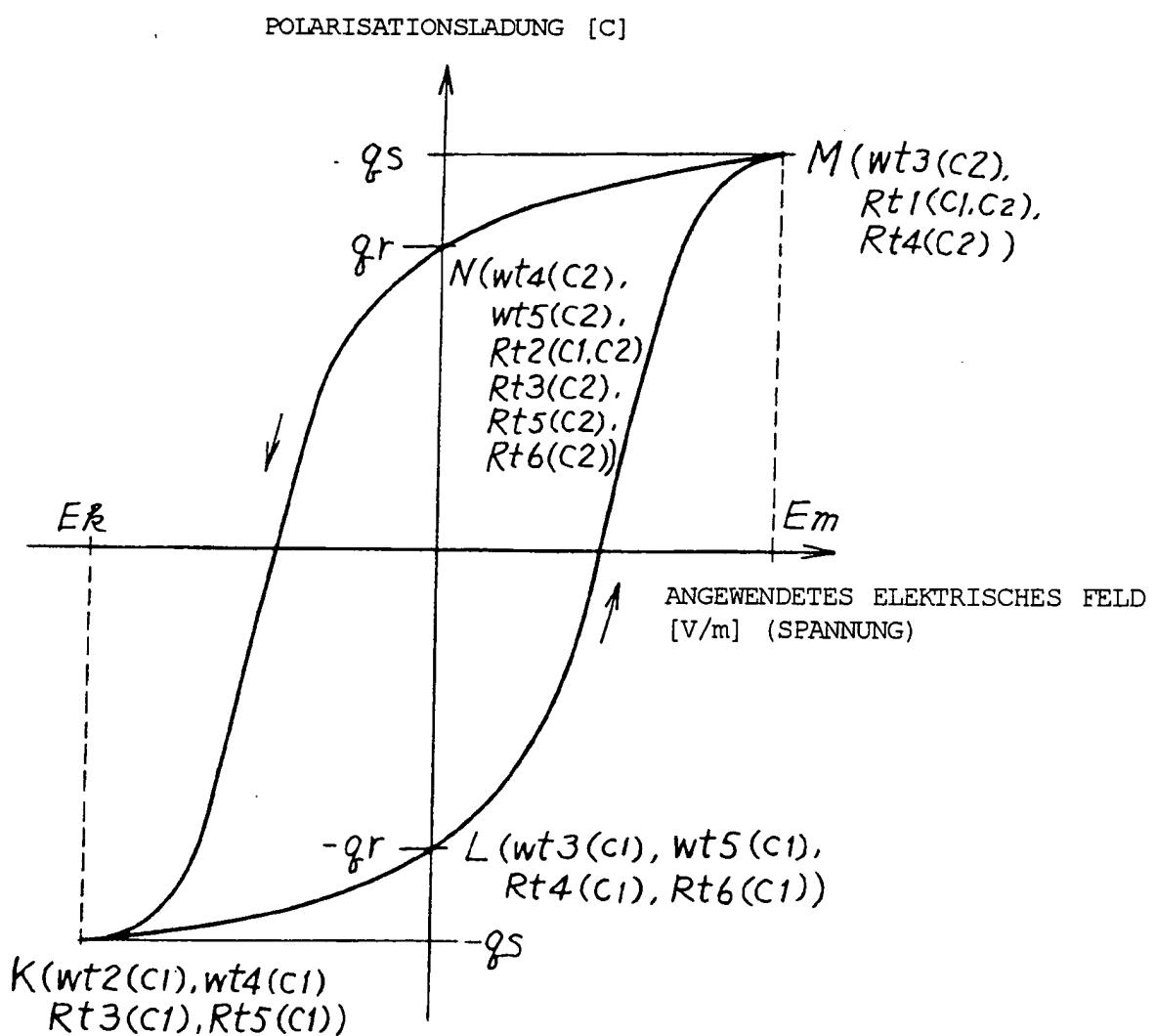

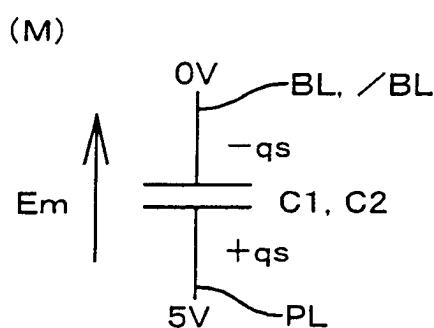

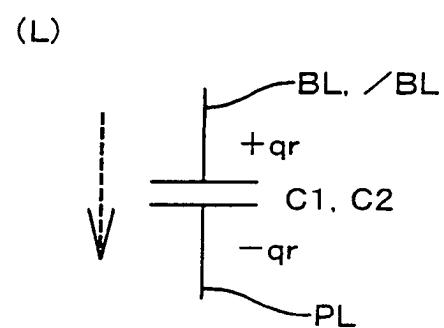

**[0005]** [Fig. 10](#) zeigt eine Hysteresekurve des ferroelektrischen Films. [Fig. 10](#) zeigt ein angewandtes elektrisches Feld oder die Spannung an der Abszissenachse und eine Polarisationsladung an der Ordinatenachse. In der Hysteresekurve verändert sich der Polarisationszustand des ferroelektrischen Films zum Beispiel von einem Punkt K und kehrt über die Punkte L, M, N zu dem Punkt K zurück.

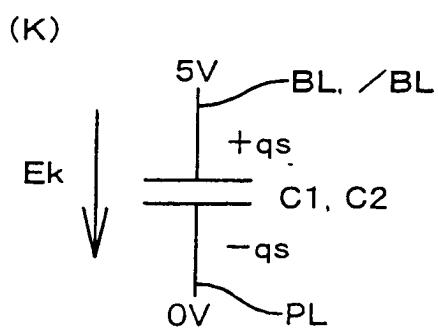

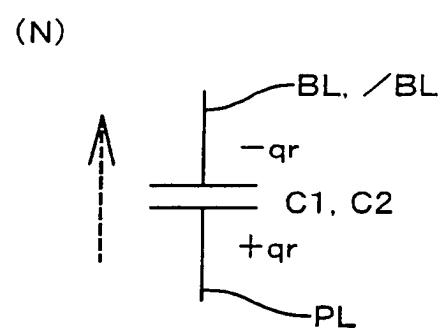

**[0006]** [Fig. 11](#) dient in dieser Beschreibung zum Definieren der Polarisationsrichtung des ferroelektrischen Kondensators. In [Fig. 11](#) sind die polarisierten Zustände K, L, M, N von [Fig. 10](#) gezeigt. Eine Hysteresekarakteristik des ferroelektrischen Films wird nun gemäß [Fig. 10](#) und [Fig. 11](#) erläutert.

**[0007]** Wenn ein abwärtiges elektrisches Feld  $E_k$  auf die ferroelektrischen Kondensatoren C1, C2 angewendet wird, wie in [Fig. 11](#) gezeigt, indem eine Spannung von beispielsweise 5 V angewendet wird, wird eine abwärtige Polarisationsladung  $-qs$  von [Fig. 11](#) auf den Kondensatoren C1, C2 erzeugt. Wenn die Spannung, die zwischen den Kondensatoren C1, C2 angewendet wird, ab diesem Zustand K entfernt wird, wird danach der Zustand zu dem Zustand L verschoben, und die Polarisationsladung  $-qs$  verbleibt auf den Kondensatoren C1, C2. Wenn andererseits eine Spannung von 5 V auf die ferroelektrischen Kondensatoren C1, C2 in der aufwärtigen Richtung von [Fig. 11](#) angewendet wird, wird das aufwärtige elektrische Feld  $E_m$  angewendet, und der Zustand erreicht einen polarisierten Zustand M mit der Polarisationsladung  $+qs$ . Auch wenn die Spannungsanwendung auf den Kondensator ab diesem Zustand M entfernt wird, kann der polarisierte (im folgenden der "Polarisations-") Ladungszustand  $+qs$  auf den Kondensatoren als Zustand N gehalten werden.

**[0008]** Deshalb ist in dieser Beschreibung der Zustand K oder M, wenn das elektrische Feld oder die Spannung auf die Kondensatoren angewendet wird, durch eine durchgehende Pfeillinie dargestellt, und der Zustand L oder N der Restpolarisation, wenn keine Potentialdifferenz in dem Kondensator vorhanden ist und das elektrische Feld nicht angewendet wird, ist durch eine gestrichelte Pfeillinie dargestellt. Die Richtung des Pfeils gibt jede Polarisationsrichtung an.

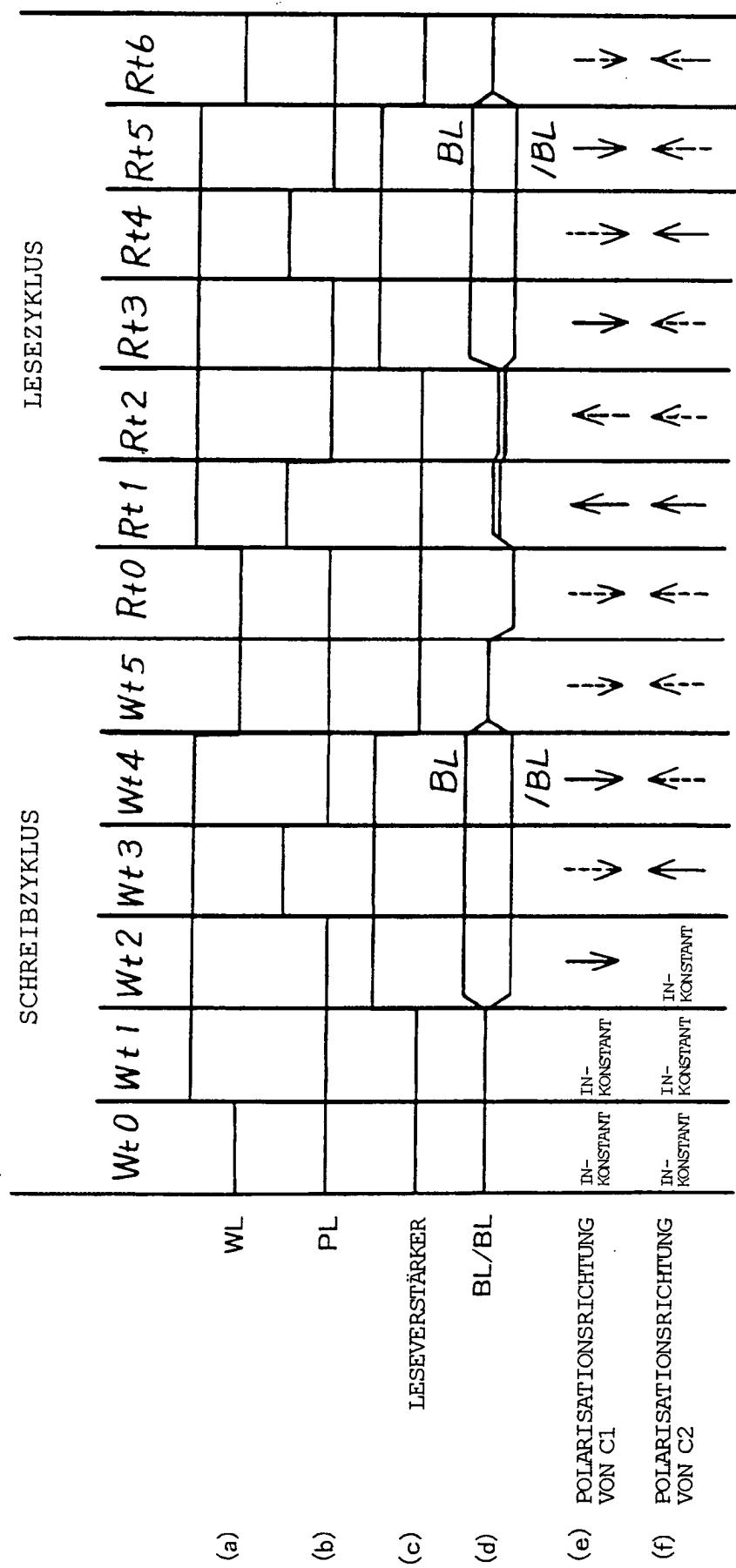

**[0009]** [Fig. 12](#) ist ein Zeitlagendiagramm zum Schreiben und Lesen von Daten für die Speicherzelle, die eine 2T2C-Struktur hat, nach Stand der Technik. In diesem Zeitlagendiagramm sind eine Wortleitung WL, eine Plattenleitung PL, eine Leseverstärkeroperation, ein Bitleitungspaar BL, /BL und jede Polarisationsrichtung der Kondensatoren C1, C2 gezeigt. [Fig. 12](#) gibt an der Abszisse die Zeit an.

**[0010]** Datenschreib- und -leseoperationsmodi für die Speicherzelle von [Fig. 9](#) werden unter Bezugnahme auf [Fig. 10](#) und [Fig. 12](#) erläutert. Zuerst wird angenommen, daß Daten, die in die ferroelektrische Speicherzelle geschrieben sind, zu der Zeit  $Wt_0$  eines Schreibzyklus unbestimmt sind. Das Bitleitungspaar BL, /BL wird auf ein Zwischenpotential zwischen den Pegeln H und L zurückgesetzt, und die Wortleitung WL und die Plattenleitung PL werden auf den L-Pegel gesetzt. Wenn die Wortleitung WL zu der Zeit  $Wt_1$  auf den H-Pegel gesteuert wird, werden die

Transistoren Q1, Q2 der Speicherzelle leitend, und ein Kondensatorpaar C1, C2 wird jeweils mit dem Bitleitungspaar BL, /BL verbunden. Zu der Zeit Wt2 wird dann der Leseverstärker **10** gemäß den geschriebenen Daten aktiviert, um die Bitleitungen BL und /BL auf den H- bzw. L-Pegel zu setzen. Als Resultat wird das abwärtige elektrische Feld auf den ferroelektrischen Kondensator C1 angewendet, und der Zustand erreicht den Zustand K, der der abwärtige Polarisationszustand ist. Dann wird kein elektrisches Feld auf den anderen ferroelektrischen Kondensator C2 angewendet, so daß die Polarisationsrichtung nicht verändert wird.

**[0011]** Wenn die Plattenleitung PL zu der Zeit Wt3 auf den H-Pegel gesteuert wird, wird der Kondensator C2, der mit der Bitleitung /BL mit dem L-Pegel verbunden ist, in der anderen Richtung polarisiert, die zu dem Kondensator C1 entgegengesetzt ist. Mit anderen Worten, der Kondensator C2 erreicht den Zustand M, und der Kondensator C1 erreicht den Zustand L. Nachdem die Plattenleitung PL auf den L-Pegel zurückgekehrt ist und der Kondensator C1 wieder polarisiert wird, wird dann die Wortleitung WL zu der Zeit Wt5 auf den L-Pegel zurückgeführt, und die Zelltransistoren Q1, Q2 sind AUS. Aus diesem Grund erreicht der Kondensator C1 den abwärtigen Polarisationszustand L, und der Kondensator C2 erreicht den aufwärtigen Polarisationszustand N. Die Polarisationszustände bleiben so und werden auch dann gehalten, wenn die Energie AUS ist.

**[0012]** Im Leseoperationsmodus wird das Bitleitungspaar BL, /BL zu der Zeit Rt0 auf 0 V vorgeladen. Wenn die Wortleitung WL zu der Zeit Rt1 auf den H-Pegel gesteuert wird und die Plattenleitung PL auf den H-Pegel gesteuert wird, wird dann der Zustand des Kondensators C1 von dem Zustand L zu dem Zustand M verschoben, und seine Polarisierung wird umgekehrt. Andererseits wird der Zustand des Kondensators C2 von dem Zustand N zu dem Zustand M verschoben. Als Resultat emittiert der ferroelektrische Kondensator C1, dessen Polarisierung umgekehrt wird, mehr Ladung als der ferroelektrische Kondensator C2, dessen Polarisierung nicht umgekehrt wird, zu jeder Bitleitung, wodurch eine vorbestimmte Potentialdifferenz zwischen dem Bitleitungspaar BL, /BL erzeugt wird.

**[0013]** Zu der Zeit Rt2 wird die Plattenleitung PL auf den L-Pegel gesetzt. Als Resultat kann dann, obwohl das Potential des Bitleitungspaares BL, /BL leicht herabgezogen wird, die oben beschriebene Potentialdifferenz gehalten werden. Zu der Zeit Rt3 kann die Potentialdifferenz zwischen dem Bitleitungspaar BL und /BL durch das Aktivieren des Leseverstärkers **10** detektiert und verstärkt werden. Als Resultat können die in dem ferroelektrischen Kondensator gespeicherten Daten durch jede Bitleitung ausgelesen werden.

**[0014]** Da beide Kondensatoren C1, C2 zu der Zeit Rt1 in dem aufwärtigen Polarisationszustand sind, werden die gespeicherten Daten zerbrochen. Deshalb wird das Resultat der Verstärkung des Leseverstärkers **10** den ferroelektrischen Kondensatoren C1, C2 zugeführt, und Daten werden neu geschrieben, indem die Plattenleitung PL zu den jeweiligen Zeiten Rt4 und Rt5 auf den H- bzw. L-Pegel gesteuert wird. Wenn die Wortleitung WL zu der Zeit Rt6 auf den L-Pegel gesetzt wird, kann dann ein Restpolarisationszustand gemäß den gespeicherten Daten in den Kondensatoren der Speicherzelle gehalten werden.

**[0015]** Die oben beschriebene ferroelektrische Speichervorrichtung wird durch den Einbau in einen Mikrocontroller verwendet und wird zum Beispiel als wiederbeschreibbarer ROM genutzt. Es gibt einige Fälle mit einem Programm, in das eine Prozedur zum Aktivieren des Mikrocontrollers geschrieben wird, da die ferroelektrische Speichervorrichtung nicht flüchtig ist. Eine CPU, die in den Mikrocontroller eingebaut ist, führt erforderliche Operationen gemäß dem Programm aus, das in den ferroelektrischen Speicher geschrieben ist.

**[0016]** Wenn jedoch die ferroelektrische Speichervorrichtung anstelle des in den herkömmlichen Mikrocontroller eingebauten ROM verwendet wird, ergibt sich folgende Schwierigkeit.

**[0017]** Unmittelbar nach Abschluß eines Herstellungsprozesses werden Daten in einem Speicher in einer ferroelektrischen Speichervorrichtung unbestimmt. Deshalb sollten Daten in einigen Arten von Verfahren in einen Speicher geschrieben werden. Obwohl eine Nur-Schreib-Vorrichtung bei diesem Schreibverfahren verwendet werden kann, sollte in einem Mikrocontroller eine spezielle Schaltung derart vorgesehen sein, daß die Daten, die von der Nur-Schreib-Vorrichtung übertragen werden, in dem ferroelektrischen Speicher gespeichert werden. Deshalb wird verlangt, daß gewünschte Daten bei dem Herstellungsprozeß wie bei dem herkömmlichen ROM vorher aufgezeichnet werden können.

**[0018]** Andererseits können, sobald gewünschte Daten bei dem Herstellungsprozeß in den herkömmlichen ROM geschrieben sind, die Daten danach nicht neu geschrieben werden. Deshalb kann, wenn ein Programm in einem ROM eines Mikrocontrollers aufgezeichnet wird, das Programm danach nicht verändert werden. Da die gespeicherten Daten in der ferroelektrischen Speichervorrichtung jedoch frei verändert werden können, macht es die Verwendung der ferroelektrischen Speichervorrichtung anstelle des herkömmlichen ROM möglich, das Programm zu verändern. Umgekehrt bedeutet das freie Verändern eines Programms, daß Daten, die bei dem Herstellungsprozeß gespeichert wurden, verlorengehen können, und deshalb ist es auch erforderlich, daß die

verlorengegangenen Daten wiederhergestellt oder zurückgewonnen werden können.

**[0019]** US 5 991 189 offenbart eine ferroelektrische Speichervorrichtung mit wahlfreiem Zugriff, die Daten in einem Bitpaar von ferroelektrischen Kondensatoren in Form von Remanenz speichert, die längs einer Hystereseschleife variiert. Ein Leseverstärker wird verwendet, um einen defekten Kondensator zu detektieren, der eine andere Hysteresekarakteristik als ein normaler Kondensator hat, so daß der defekte Kondensator ausgesondert werden kann.

**[0020]** EP-A-0 920 032, die unter Art. 54(3) fällt und der obengenannten US 5 991 189 entspricht, offenbart eine ferroelektrische Speichervorrichtung gemäß der Präambel von Anspruch 1. In dieser Vorrichtung leiden die ferroelektrischen Kondensatoren während des Gebrauchs unter Ermüdung, wodurch sich ihre Restpolarisationen ändern.

**[0021]** Es ist wünschenswert, eine ferroelektrische Speichervorrichtung vorzusehen, in der gewünschte Daten bei einem Herstellungsprozeß aufgezeichnet werden können.

**[0022]** Es ist auch wünschenswert, eine ferroelektrische Speichervorrichtung vorzusehen, in der auch dann, wenn die Daten, die bei dem Herstellungsprozeß gespeichert wurden, danach verändert werden, die Anfangsdaten bei Bedarf wiederhergestellt oder zurückgewonnen werden können.

**[0023]** Ausführungsformen der vorliegenden Erfindung sehen eine ferroelektrische Speichervorrichtung vor, die Speicherzellen umfaßt, die jeweilige ferroelektrische Kondensatoren enthalten, die jeweils eine verschiedene Hysteresekarakteristik haben. Die verschiedenen Hysteresekarakteristiken der Kondensatoren werden als ROM-Daten bei dem Herstellungsprozeß gebildet. Dann wird die Differenz der Hysteresekarakteristiken genutzt, um die Original-ROM-Daten wiederherzustellen, die bei dem Herstellungsprozeß geschrieben wurden, und die Daten in einer Polarisationsrichtung aufzuzeichnen. Ferner können die aufgezeichneten Daten durch ein normales Schreibverfahren frei verändert werden, und die aufgezeichneten Daten können auch dann gehalten werden, nachdem die Energie AUS ist. Auch nachdem erste ROM-Daten verändert werden, können die Original-ROM-Daten unter Verwendung der oben beschriebenen Hysteresekarakteristiken wiederhergestellt oder zurückgewonnen werden.

**[0024]** Gemäß der vorliegenden Erfindung ist eine ferroelektrische Speichervorrichtung vorgesehen, die umfaßt: eine Vielzahl von Speicherzellen, die an Schnittpunkten zwischen einer Vielzahl von Bitleitungen und einer Vielzahl von Wortleitungen angeordnet sind, bei der jede von der Vielzahl von Speicherzellen

eine erste Speicherzelle enthält, die einen ferroelektrischen Kondensator umfaßt, der eine erste Hysteresekarakteristik hat, und eine zweite Speicherzelle, die einen ferroelektrischen Kondensator umfaßt, der eine zweite Hysteresekarakteristik hat, die sich von der ersten Hysteresekarakteristik unterscheidet, erste Daten in den Speicherzellen in Abhängigkeit von den ersten und zweiten Hysteresekarakteristiken gespeichert sind und gemäß den ersten und zweiten Hysteresekarakteristiken ausgelesen werden und zweite Daten in den Speicherzellen in Abhängigkeit von ersten und zweiten Polarisationszuständen gespeichert werden; dadurch gekennzeichnet, daß die ferroelektrischen Kondensatoren mit den verschiedenen Hysteresekarakteristiken bei einem Herstellungsprozeß gebildet werden.

**[0025]** Vorzugsweise ist die Kapazität des ferroelektrischen Kondensators mit der ersten Hysteresekarakteristik kleiner als die des ferroelektrischen Kondensators mit der zweiten Hysteresekarakteristik. Hinsichtlich einer konkreteren Struktur hat der ferroelektrische Kondensator mit der ersten Hysteresekarakteristik eine kleinere Dimension und eine größere Filmdicke als der ferroelektrische Kondensator mit der zweiten Hysteresekarakteristik.

**[0026]** Durch die vorliegende Erfindung können ROM-Daten durch das Bilden von ferroelektrischen Kondensatoren mit jeweils verschiedenen Hysteresekarakteristiken bei einem Herstellungsprozeß gemäß Anfangsdaten (ROM-Daten) geschrieben werden. Die Differenz der Hysteresekarakteristiken kann unter Verwendung des Betrages der Veränderung der Polarisationsladungen der Kondensatoren wiederhergestellt werden, die auftritt, wenn die erste Spannung oder das erste elektrische Feld in die zweite Spannung oder das zweite elektrische Feld in dem ferroelektrischen Kondensator verändert wird. Eine Speicherzelle mit 1T1C-Struktur oder 2T2C-Struktur kann auf die vorliegende Erfindung angewendet werden.

**[0027]** Beispielhaft wird Bezug auf die beiliegenden Zeichnungen genommen, in denen:

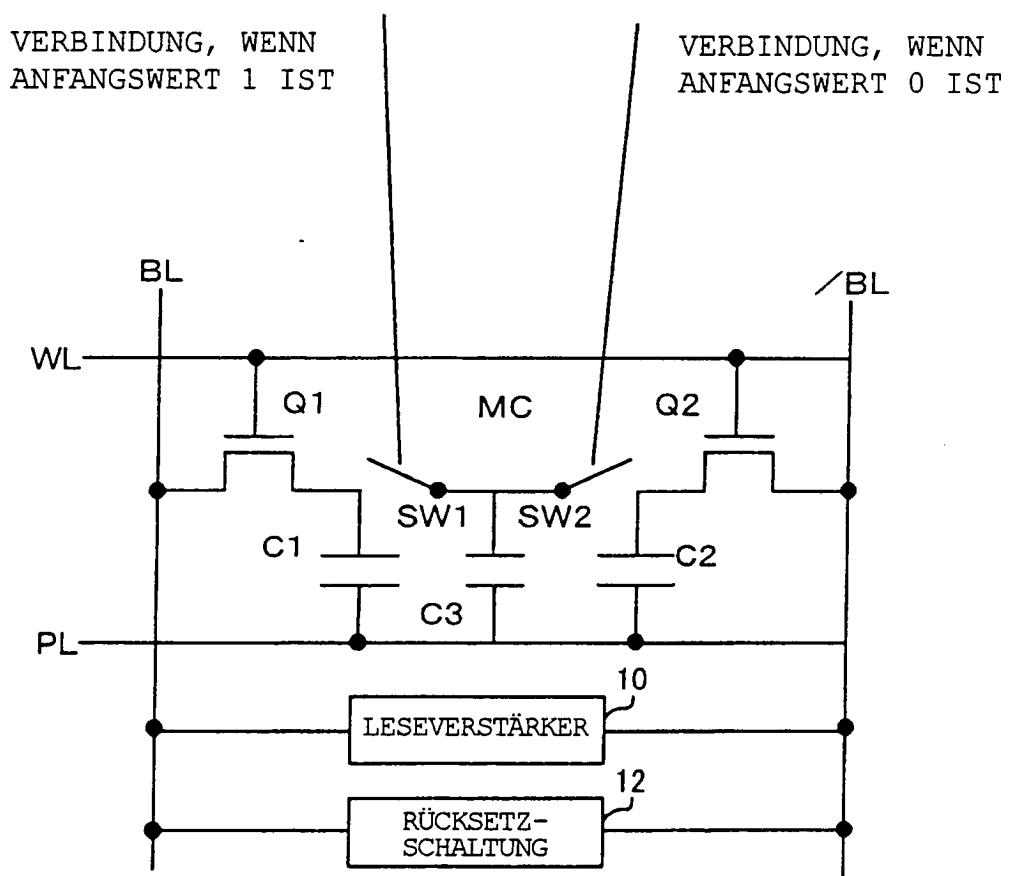

**[0028]** [Fig. 1](#) eine ferroelektrische Speicherzelle mit 2T2C-Struktur in einer Ausführungsform der Erfindung zeigt;

**[0029]** [Fig. 2](#) ein Diagramm ist, das eine Hysteresekurve von Kondensatoren mit unterschiedlicher Dimension zeigt;

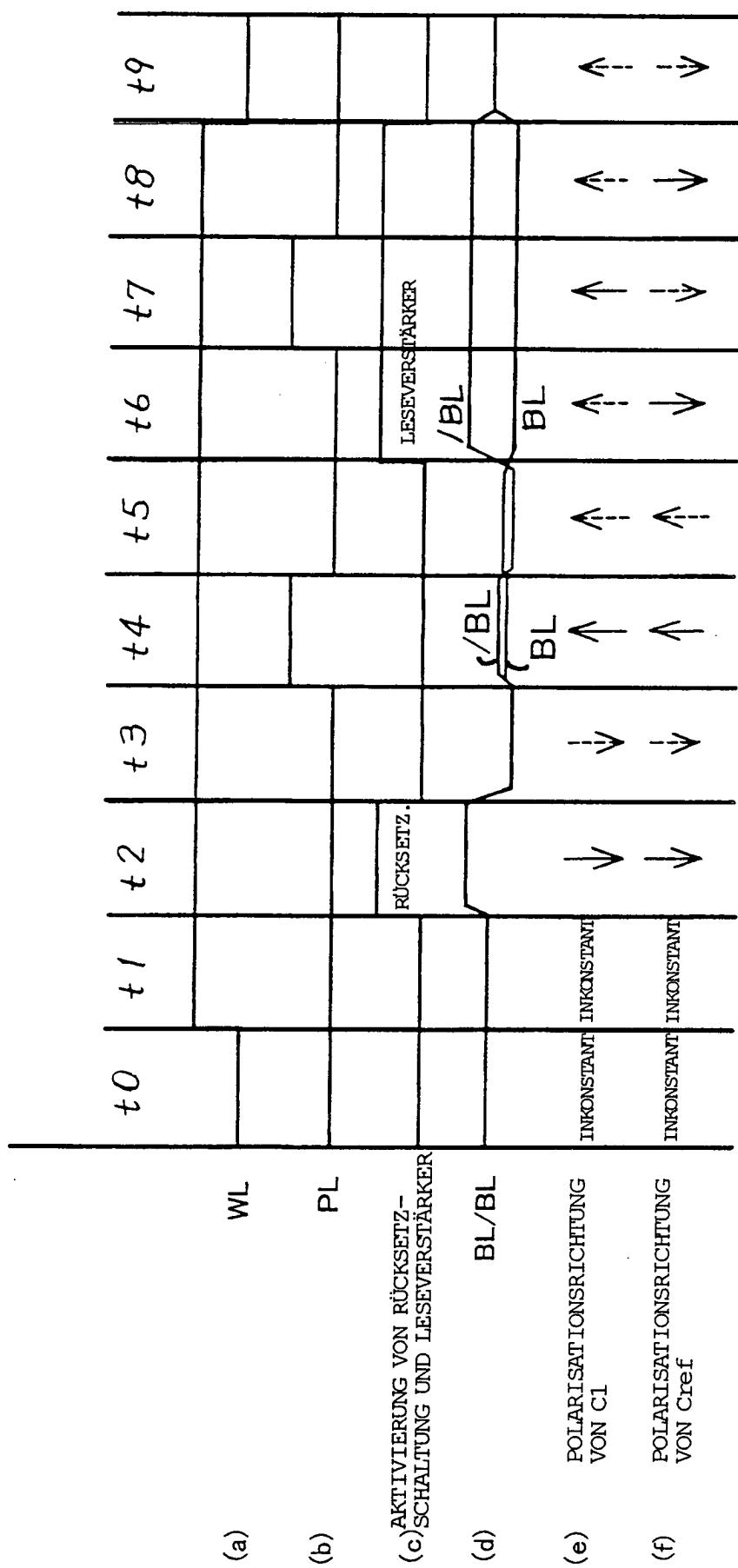

**[0030]** [Fig. 3](#) ein Zeitlagendiagramm eines Prozesses zum Wiederherstellen von Anfangsdaten (ROM-Daten) einer Zelle in 2T2C-Form gemäß [Fig. 1](#) ist;

**[0031]** [Fig. 4](#) ein Schaltungsdiagramm einer Spei-

cherzelle mit 1T1C-Struktur (die einen Transistor und einen Kondensator hat) in einer anderen Ausführungsform der Erfindung ist;

[0032] [Fig. 5](#) ein Diagramm ist, das eine Hysteresekurve von Kondensatoren mit unterschiedlicher Dimension zeigt;

[0033] [Fig. 6](#) ein Zeitlagendiagramm eines Prozesses zum Wiederherstellen von Anfangsdaten in einer Zelle in 1T1C-Form gemäß [Fig. 4](#) ist;

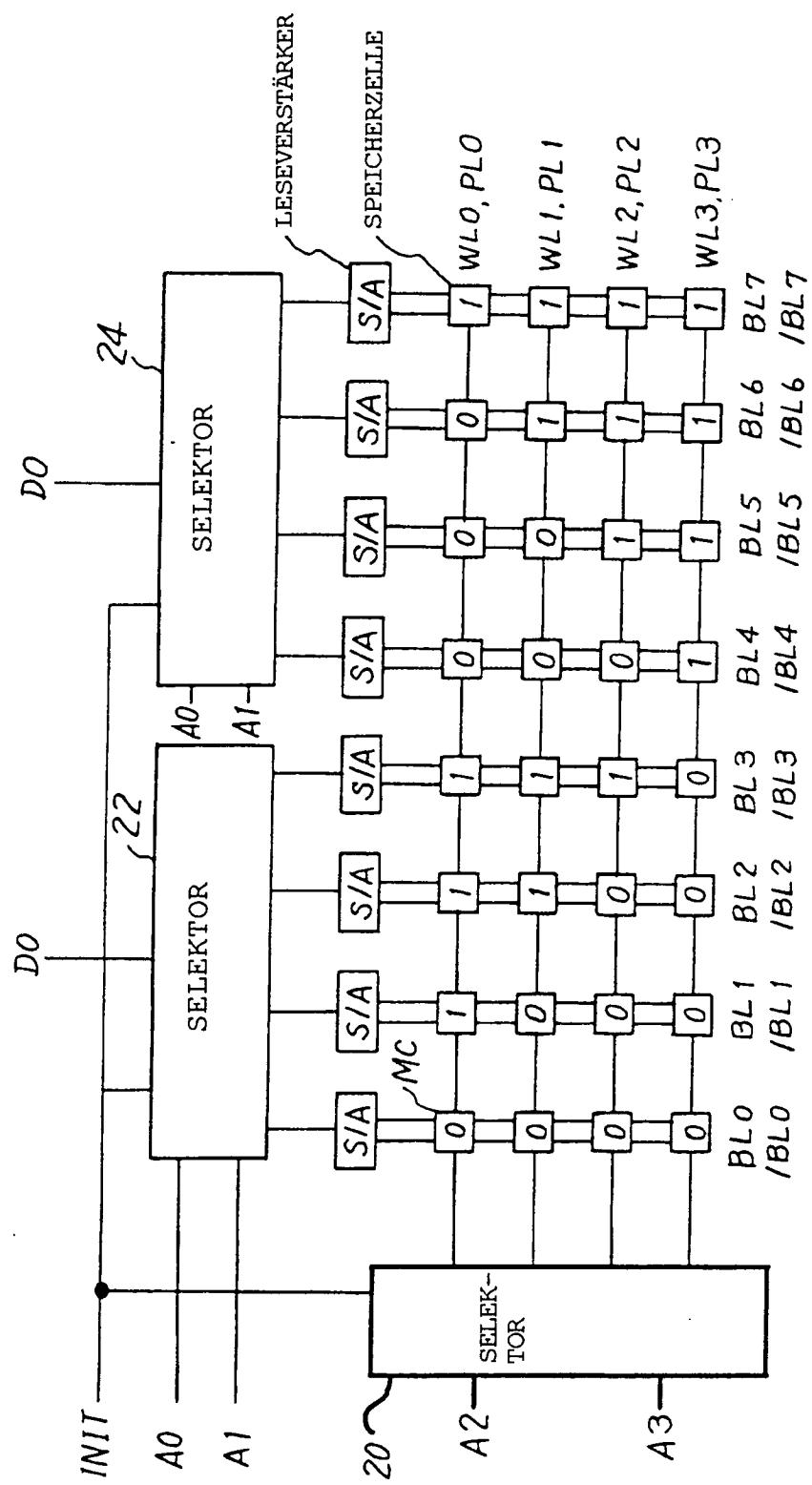

[0034] [Fig. 7](#) eine Gesamtstruktur einer ferroelektrischen Speichervorrichtung zeigt, die die vorliegende Erfindung verkörpert;

[0035] [Fig. 8](#) ein erläuterndes Diagramm zum Schreiben von Anfangsdaten der Speicherzelle in 2T2C-Form ist, die die vorliegende Erfindung verkörpert;

[0036] [Fig. 9](#) ein Schaltungsdiagramm einer ferroelektrischen Speicherzelle nach Stand der Technik ist;

[0037] [Fig. 10](#) ein Diagramm ist, das eine Hysteresekurve des ferroelektrischen Films zeigt;

[0038] [Fig. 11](#) ein Diagramm ist, das eine Definition einer Polarisationsrichtung des ferroelektrischen Kondensators in dieser Beschreibung zeigt;

[0039] [Fig. 12](#) ein Zeitlagendiagramm zum Schreiben und Lesen von Daten in einer Speicherzelle in 2T2C-Form nach Stand der Technik ist.

[0040] Im folgenden werden unter Bezugnahme auf die Zeichnungen bevorzugte Ausführungsformen der vorliegenden Erfindung beschrieben. Der technische Umfang der vorliegenden Erfindung ist jedoch nicht auf diese Ausführungsformen begrenzt.

[0041] [Fig. 1](#) ist eine ferroelektrische Speicherzelle mit 2T2C-Struktur in einer Ausführungsform der Erfindung. Ähnlich wie nach Stand der Technik, der in [Fig. 9](#) gezeigt ist, ist ein Bitleitungspaar BL, /BL vorgesehen, und eine Wortleitung WL und eine Plattenleitung PL, die dieses kreuzen; und eine Speicherzelle MC, die ein Transistorpaar Q1, Q2 und ein ferroelektrisches Kondensatorpaar C1, C2 enthält, ist an dem Schnittpunkt des Bitleitungspaares BL, /BL, der Wortleitung WL und der Plattenleitung PL angeordnet. In dieser Ausführungsform wird der ferroelektrische Kondensator C2 bei dem Herstellungsprozeß so dimensioniert, um größer als der Kondensator C1 zu sein, und die Kapazität des Kondensators C2 wird gebildet, um größer als jene des Kondensators C1 zu sein. Ein Leseverstärker **10** und eine Rücksetzschaltung **12** sind mit dem Bitleitungspaar BL, /BL verbunden. Der Leseverstärker **10** steuert das Bitleitungspaar gemäß den geschriebenen Daten zu der Daten-

schreibzeit und detektiert und verstärkt eine sehr kleine Potentialdifferenz, die auf dem Bitleitungspaar gebildet wird, zu der Datenlesezeit, ähnlich wie nach Stand der Technik. Ferner setzt die Rücksetzschaltung **12** das Bitleitungspaar jeweils zurück auf den H-Pegel, um die Anfangsdaten zu lesen, die bei dem Herstellungsprozeß aufgezeichnet wurden.

[0042] [Fig. 2](#) ist ein Diagramm, das Hysteresekurven von Kondensatoren zeigt, die jeweils eine verschiedene Dimension haben. Die Dimension des ferroelektrischen Kondensators C1 ist größer als jene des anderen ferroelektrischen Kondensators C2, wie in [Fig. 1](#) gezeigt. Auf diese Weise bedeutet der Zustand, wenn die Dimension des Kondensators C2 größer als jene des Kondensators C1 ist, ROM-Daten (Anfangsdaten) "0". Deshalb bedeutet der Fall, wenn die Dimension des Kondensators C1 größer als jene des Kondensators C2 ist, ROM-Daten "1".

[0043] Die Hysteresekurve des Kondensators C1 mit einer kleineren Dimension weist eine kleinere Veränderung der Polarisationsladung als Antwort auf eine Veränderung eines konstanten elektrischen Feldes oder einer Spannung auf, wie durch eine durchgehende Linie in [Fig. 2](#) gezeigt. Zusätzlich weist die Hysteresekurve des Kondensators **2**, der eine größere Dimension hat, eine größere Veränderung der Polarisationsladung als Reaktion auf die Veränderung des konstanten elektrischen Feldes oder der Spannung auf, wie durch eine gestrichelte Linie in [Fig. 2](#) gezeigt. In dieser Ausführungsform können ROM-Daten, die bei dem Herstellungsprozeß gespeichert wurden, ausgelesen und wiedergegeben und wieder in die Speicherzelle geschrieben werden, indem Differenzen zwischen Hysteresekurven genutzt werden. Deshalb ist es nicht notwendig, eine spezielle Schreibschaltung in einem Mikrocontroller vorzusehen, wie es beim Stand der Technik beschrieben ist.

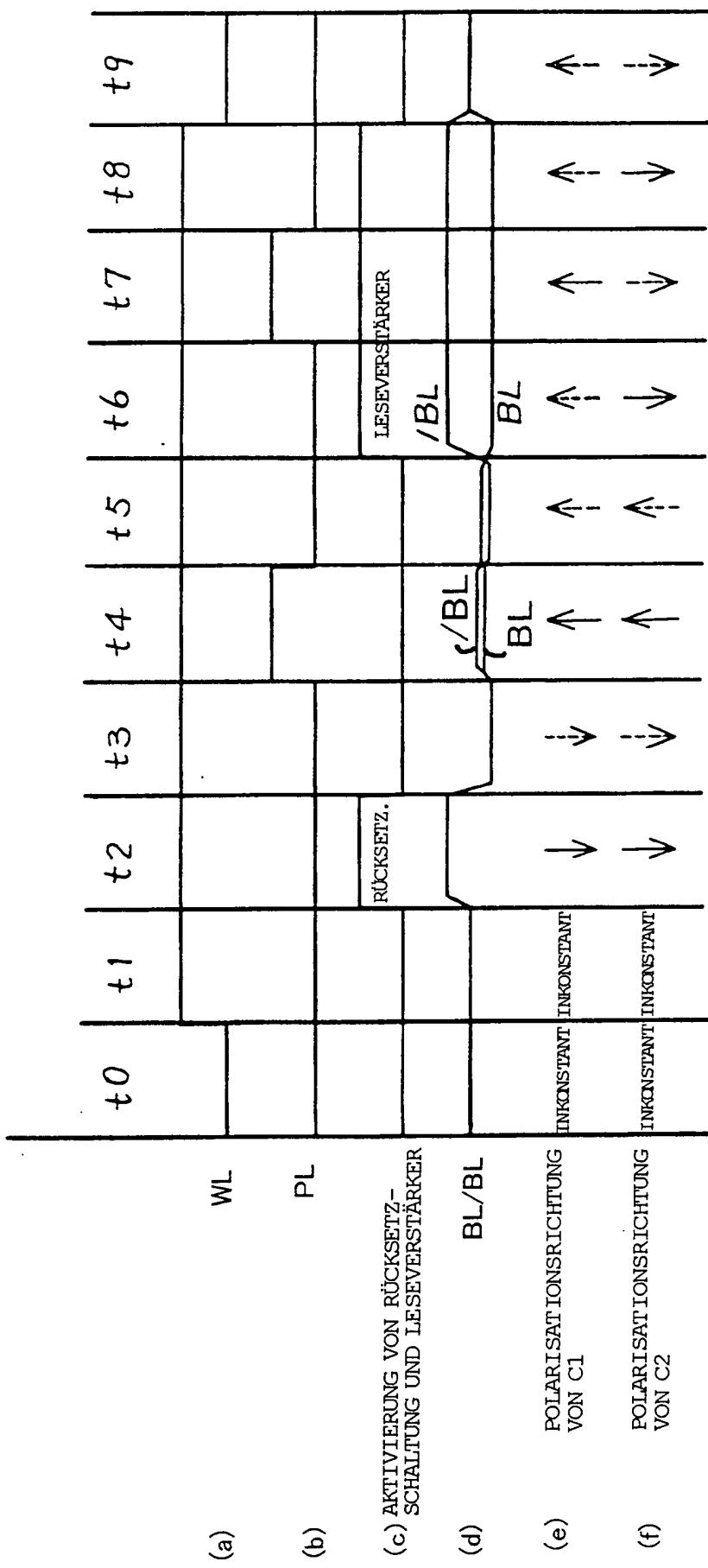

[0044] [Fig. 3](#) ist ein Zeitlagendiagramm eines Prozesses zum Wiederherstellen von Anfangsdaten (ROM-Daten) einer Zelle in 2T2C-Form in dieser Ausführungsform.

[0045] Jede Zeit t0 bis t9, die in [Fig. 3](#) gezeigt ist, ist in jedem der Zustände K, L, M, N von [Fig. 2](#) dargestellt. Der Prozeß zum Wiederherstellen von ROM-Daten wird nun unter Bezugnahme auf [Fig. 2](#) und [Fig. 3](#) erläutert.

[0046] Die Polarisationsrichtungen von ferroelektrischen Kondensatoren C1, C2 sind zu der Zeit t0, unmittelbar nachdem der Herstellungsprozeß beendet worden ist, unbestimmt. Das Bitleitungspaar BL, /BL wird auf ein vorbestimmtes Zwischenpotential gesetzt, und die Plattenleitung PL wird zu der Zeit t0 auf den L-Pegel zurückgesetzt. Dann wird die Wortleitung WL auf den H-Pegel gesteuert, so daß das Bit-

leitungs paar BL, /BL zu der Zeit t1 mit jeweiligen ferroelektrischen Kondensatoren C1, C2 verbunden wird.

**[0047]** Die Rücksetzung 12 wird gesteuert, um das Bitleitungs paar BL, /BL zu der Zeit t2 auf den H-Pegel zu steuern. Als Resultat wird ein elektrisches Feld oder eine Spannung in der Plattenleitungsrichtung (abwärtige Richtung) auf die beiden Kondensatoren C1, C2 angewendet, und dann erreichen die beiden Kondensatoren C1, C2 den abwärtigen Polarisationszustand. Das heißt, die Kondensatoren erreichen den Zustand K1 bzw. K2 von [Fig. 2](#). Die Rücksetzung 12 lädt das Bitleitungs paar BL, /BL zu der Zeit t3 auf den L-Pegel vor. Obwohl die Potentialdifferenz zwischen beiden Kondensatoren entfernt wird, wird dann ein Restpolarisationszustand gehalten, wie es durch einen abwärtigen gestrichelten Pfeil von [Fig. 3](#) gezeigt ist. Mit anderen Worten, die beiden Kondensatoren nehmen die Zustände L1 und L2 von [Fig. 2](#) an.

**[0048]** Wenn die Plattenleitung PL zu der Zeit t4 auf den H-Pegel gesteuert wird, tritt dann bei den Kondensatoren C1 und C2 eine Polaritätsumkehr auf. Speziell verändert sich der Zustand des Kondensators C1 von dem Zustand L1 in den Zustand M1, und der Zustand des Kondensators C2 verändert sich von dem Zustand L2 in den Zustand M2 in [Fig. 2](#). Als Resultat entlädt der Kondensator C2, dessen Hysteresekurve größer ist, mehr Ladungen als der Kondensator C1, dessen Hysteresekurve kleiner ist, auf die Bitleitungen. Deshalb wird das Potential der Bitleitung /BL höher als jenes der Bitleitung BL, wie zu der Zeit t4 von [Fig. 3](#) gezeigt.

**[0049]** Wenn die Plattenleitung PL zu der Zeit t5 auf den L-Pegel zurückgesetzt wird, wird das Potential des Bitleitungs paares leicht verringert, aber die Beziehung der Potentialdifferenz wird gehalten. In diesem Fall nehmen die Kondensatoren jeweilig die Zustände N1 und N2 von [Fig. 2](#) an. Wenn der Leseverstärker 10 aktiviert wird, um eine winzige Potentialdifferenz zu detektieren und zu verstärken, die auf dem Bitleitungs paar auftrat, wird die Bitleitung /BL dann auf den H-Pegel gesteuert und wird die Bitleitung BL auf den L-Pegel gesteuert.

**[0050]** In diesem Zustand werden gemäß dem H-Pegel der Plattenleitung PL zu der Zeit t7 und dem L-Pegel der Plattenleitung PL zu der Zeit t8 die Daten, die auf dem Bitleitungs paar erzeugt wurden, zu den ferroelektrischen Kondensatoren C1 und C2 der Speicherzelle übertragen, und die Anfangsdaten (ROM-Daten) werden durch ein normales Neuschreibprinzip, ähnlich wie nach Stand der Technik, in den Kondensator der Speicherzelle geschrieben. Selbst wenn die Wortleitung WL zu der Zeit t9 auf den L-Pegel zurückgesetzt wird, kann der Polarisationszustand der Kondensatoren, für die die Daten ge-

schrieben wurden, gehalten werden.

**[0051]** Wie aus der obigen Erläuterung hervorgeht, werden ROM-Daten, die jeder Dimensionsgröße der Kondensatoren entsprechen, in die die Daten bei dem Herstellungsprozeß geschrieben werden, ab der Zeit t1 bis zu der Zeit t6 zu dem Bitleitungs paar ausgelesen. Die ROM-Daten werden von dem Bitleitungs paar durch Operationen ab der Zeit t6 bis zu der Zeit t9 in die Speicherzelle geschrieben. Auf diese Weise können gewünschte Daten neu geschrieben werden, ähnlich wie bei dem herkömmlich verwendeten ROM, indem die Hysteresekurve des Kondensators in der Speicherzelle bei dem Herstellungsprozeß verändert wird. Zusätzlich können die geschriebenen ROM-Daten durch die Operationen, die ab der Zeit t0 bis zu der Zeit t6 angegeben sind, ausgelesen werden, und die Daten werden ab der Zeit t6 bis zu der Zeit t9 in die Speicherzelle geschrieben. Deshalb ist es nicht notwendig, eine spezielle Schreibvorrichtung zu verwenden, und die ROM-Daten (Anfangsdaten), die bei dem Herstellungsprozeß geschrieben wurden, können als Polarisationszustand in die ferroelektrische Speicherzelle geschrieben werden.

**[0052]** In der in [Fig. 1](#) gezeigten Speicherzelle MC steuert der Leseverstärker 10 das Bitleitungs paar gemäß geschriebenen Daten, so daß beliebige Schreibdaten geschrieben werden können und durch eine normale Leseoperation ausgelesen werden können. Mit anderen Worten, gewisse Daten, die sich von den Anfangs-ROM-Daten unterscheiden, die bei dem Herstellungsprozeß aufgezeichnet wurden, können später in die Speicherzelle geschrieben werden. Zusätzlich können die Anfangs-ROM-Daten, die bei dem Herstellungsprozeß geschrieben wurden, in der Speicherzelle wiederhergestellt werden, indem der Anfangsdatenwiederherstellungsprozeß wieder ausgeführt wird, der in [Fig. 3](#) gezeigt ist.

**[0053]** Wenn die Anfangs-ROM-Daten wiederhergestellt werden, wie oben beschrieben, kann dann, da der Betrag der Polarisationsladung ( $qs_2+qr_2$ ), der durch den Kondensator C2 gegeben ist, dessen Hysteresekurve größer ist, größer als der Betrag der Polarisationsladung ( $qs_1+qr_1$ ) wird, der durch den Kondensator C1 gegeben ist, dessen Hysteresekurve kleiner ist, eine sehr kleine Potentialdifferenz zwischen dem Bitleitungs paar erzeugt werden. Zusätzlich erfordert es eine normale Leseoperation, daß der Betrag der Polarisationsladung ( $qs_1+qr_1$ ), wenn sich der Kondensator C1 von dem Zustand L1 in den Zustand M1 verändert, größer als der Betrag der Polarisationsladung ( $qs_2-qr_2$ ) ist, wenn sich der umgekehrte Polarisationszustand des Kondensators C2 von dem Zustand N2 in M2 verändert. Anfangsdaten werden während der Herstellung geschrieben, um eine Hysteresekurve zu bilden, die die obige Bedingung erfüllt.

**[0054]** Die gewünschten Daten können bei dem Herstellungsprozeß geschrieben werden, ähnlich wie bei dem herkömmlichen Programm-ROM, dadurch, daß der ferroelektrische Speicher als Programmaufzeichnungsspeicher in einen Mikrocontroller eingebaut wird, und die Daten können neu geschrieben werden, nachdem der Herstellungsprozeß beendet worden ist. Somit kann dann, wenn der Speicher ein Programm-ROM ist, der in einen Mikrocontroller eingebaut wird, das Programm korrigiert und verändert werden, und die Original-Anfangsdaten können einfach wiederhergestellt werden, wenn das Programm aus Versehen verändert wird.

**[0055]** [Fig. 4](#) ist ein Schaltungsdiagramm der Speicherzelle, die aus einem Transistor und einem Kondensator gebildet ist (die also die 1T1C-Struktur hat), gemäß einer anderen Ausführungsform. In [Fig. 4](#) kreuzen sich drei Sätze von Wort- und Plattenleitungen mit dem Bitleitungs paar BL, /BL. WL0, WL1 sind normale Wortleitungen, und WLr ist eine Wortleitung zur Referenz. Ähnlich sind PL0, PL1 normale Plattenleitungen, und PLr ist eine Plattenleitung zur Referenz. In [Fig. 4](#) sind normale Speicherzellen MC1, MC2 jeweils mit der Seite der einen Bitleitung BL verbunden. Demgegenüber ist eine Speicherzelle MCr zur Referenz mit der Seite der anderen Bitleitung /BL verbunden. Ein Transistor Q und ein ferroelektrischer Kondensator C sind für jede Speicherzelle vorgesehen.

**[0056]** In dieser Ausführungsform ist die Dimension des ferroelektrischen Kondensators C1 der Speicherzelle MC1 kleiner als jene des ferroelektrischen Kondensators C2 der Speicherzelle MC2. Zusätzlich hat der ferroelektrische Kondensator Cref der Speicherzelle MCr zur Referenz die Dimension, die zwischen jenen der Kondensatoren C1, C2 liegt. Genauer gesagt, die Dimension wird in der Ordnung der Kondensatoren C1, Cref und C2 größer, und die Kapazität des Kondensators wird auch in jener Ordnung größer.

**[0057]** [Fig. 5](#) ist ein Diagramm, das Hysteresekurven von Kondensatoren zeigt, die jeweils eine verschiedene Dimension haben. Die Dimension wird in der Ordnung der Kondensatoren C1, Cref und C2 größer, wie oben in [Fig. 4](#) beschrieben, so daß jede Hysteresekurve eines Kondensators in derselben Ordnung größer wird.

**[0058]** Wenn die Speicherzelle MC1 in einem Speicherzellenarray mit der 1T1C-Struktur von [Fig. 4](#) gelesen wird, wird die Speicherzelle MCr zur Referenz eingesetzt. Wenn die Speicherzelle MC2 gelesen wird, wird ähnlich die Speicherzelle MCr zur Referenz verwendet. Speziell ist, wenn das 1T1C-Speicherzellenarray zum Einsatz kommt, jede Speicherzelle aus einem Transistor und einem ferroelektrischen Kondensator gebildet, und eine Speicherzelle MCr zur

Referenz, die mit der anderen Bitleitung /BL verbunden ist, wird durch viele Speicherzellen, die mit der selben Bitleitung BL verbunden sind, gemeinsam genutzt. Deshalb können die Anzahlen von Elementen von einer Speicherzelle verringert werden und kann die Kapazität des Speichers erhöht werden.

**[0059]** Aus dem oben beschriebenen Prinzip geht hervor, daß dann, wenn Anfangsdaten (ROM-Daten) in der Speicherzelle MC1 wiederhergestellt und aus ihr ausgelesen werden, die Hysteresekurven der Kondensatoren C1 und Cref, die in [Fig. 5](#) gezeigt sind, genutzt werden. Diese Formation ist dieselbe wie im Fall der Speicherzelle in 2T2C-Form, die in [Fig. 1](#) gezeigt ist. Andererseits werden, wenn Anfangsdaten (ROM-Daten) in der Speicherzelle MC2 wiederhergestellt oder aus ihr gelesen werden, die Hysteresekurven der Kondensatoren Cref und C2 von [Fig. 5](#) genutzt, ähnlich wie im Fall von [Fig. 2](#).

**[0060]** [Fig. 6](#) ist ein Zeitlagendiagramm eines Anfangsdatenwiederherstellungsprozesses in dem 1T1C-Speicherzellenarray gemäß der vorliegenden Ausführungsform. Dieses Zeitlagendiagramm zeigt den Fall, wenn Anfangsdaten in der Speicherzelle MC1 wiederhergestellt werden. Das Zeitlagendiagramm von [Fig. 6](#) ist ungefähr dasselbe wie jenes von [Fig. 3](#). Der unterschiedliche Punkt ist der, daß Polarisationsrichtungen von Kondensatoren C1 und Cref gezeigt sind und auch Wort- und Plattenleitungen WL0 und PL0 für die Speicherzelle MC1 und Wort- und Plattenleitungen WLr und PLr zur Referenz gezeigt sind. Die anderen Teile sind dieselben wie jene des Zeitlagendiagramms von [Fig. 3](#).

**[0061]** Speziell werden, wenn die 1T1C-Speicherzelle eingesetzt wird, Anfangsdaten ab der Zeit t0 bis zu der Zeit t6 ausgelesen, und die von der Zeit t0 bis zu der Zeit t6 ausgelesenen Anfangsdaten werden in der Speicherzelle als Polarisationszustand aufgezeichnet. Ähnlich wie im Fall von [Fig. 3](#) wird die Wortleitung zu der Zeit t1 auf den H-Pegel gesteuert, und die Rücksetschaltung 12 steuert zu der Zeit t2 das Bitleitungs paar BL, /BL auf den H-Pegel. Als Resultat tritt die abwärtige Polarisierung auf den Kondensatoren C1, Cref auf. Nachdem die Rücksetschaltung 12 das Bitleitungs paar zu der Zeit t3 auf den L-Pegel vorlädt, werden die Plattenleitungen PLO und PLr zu der Zeit t4 auf den H-Pegel gesteuert. Dann fließen die verschiedenen Ladungsbeträge zu dem Bitleitungs paar, und zwar gemäß den verschiedenen Größen der Hysteresekurven von beiden Kondensatoren. Bei dem Beispiel von [Fig. 6](#) fließt mehr Ladung zu der Bitleitung /BL und fließt weniger Ladung zu der Bitleitung BL, wodurch eine winzige Potentialdifferenz auf dem Bitleitungs paar auftritt.

**[0062]** Die winzige Potentialdifferenz des Bitleitungs paares, die auf diese Weise auftritt, wird durch Aktivieren des Leseverstärkers 10 zu der Zeit t6 de-

tektiert und verstärkt. Als Resultat wird das Bitleitungs paar /BL und BL auf den H-Pegel bzw. L-Pegel gesteuert, und dann werden die Anfangsdaten auf das Bitleitungs paar ausgelesen. Danach wird jede Plattenleitung zu der Zeit t7 jeweils auf den H-Pegel gesteuert, und ein aufwärtiger Polarisationszustand wird auf dem Kondensator C1 erzeugt. Die Plattenleitungen werden zu der Zeit t8 jeweils auf den L-Pegel gesteuert, und ein abwärtiger Polarisationszustand wird auf dem Kondensator Cref zur Referenz erzeugt. Dann wird die Wortleitung zu der Zeit t9 auf den L-Pegel zurückgesetzt, und die Restpolarisationszustände werden in den Speicherzellen aufgezeichnet.

**[0063]** Da nur der Kondensator C1 in der Speicherzelle MC1 vorgesehen ist, wenn die in [Fig. 4](#) gezeigte 1T1C-Speicherzelle zum Einsatz kommt, ist die Erzeugung einer Polarisation für den Kondensator Cref zur Referenz zu der Zeit t8 nicht erforderlich.

**[0064]** Anfangsdaten (ROM-Daten), die bei dem Herstellungsprozeß aufgezeichnet wurden, können, wie oben erläutert, auch unter Verwendung der Speicherzellenstruktur wiederhergestellt werden, die einen Transistor und einen ferroelektrischen Kondensator hat; Daten, die in der Speicherzelle gespeichert sind, können bei Bedarf später umgeschrieben werden, und die Anfangsdaten (ROM-Daten) können wiederhergestellt werden, wenn die Daten aus Versehen überschrieben werden.

**[0065]** [Fig. 7](#) zeigt eine Gesamtstruktur der ferroelektrischen Speichervorrichtung gemäß der vorliegenden Ausführungsform. Die Speichervorrichtung hat Speicherzellen MC in jeweils vier Reihen und acht Spalten, mit denen Wort- und Plattenleitungen WL und PL und ein Bitleitungs paar BL, /BL verbunden sind. Ein Leseverstärker S/A ist jeweils mit einem Bitleitungs paar verbunden. Adresssignale A0, A1 werden jeweils Spaltenselektoren **22**, **24** zugeführt, und Adresssignale A2, A3 werden einem Reihenselektor **20** zugeführt. Anfangsdaten (ROM-Daten) "0" und "1", die in [Fig. 7](#) gezeigt sind, werden bei dem Herstellungsprozeß in jede Speicherzelle geschrieben.

**[0066]** Nun wird ein Fall zum Wiederherstellen der oben beschriebenen Anfangsdaten in der ferroelektrischen Speichervorrichtung erläutert, die in [Fig. 7](#) gezeigt ist. Zuerst folgt die Erläuterung unter Bezugnahme auf das Intervall zwischen der Zeit t0 und t9 des in [Fig. 3](#) und [Fig. 6](#) gezeigten Zeitlagendiagramms. Der Reihenselektor **20** steuert die Wortleitung WL0 und die Plattenleitung PLO in der ersten Reihe, indem die Adressen A2, A3 jeweils auf 0 gesetzt werden. Als Resultat können alle Anfangsdaten für acht Speicherzellen MC in der ersten Reihe wiederhergestellt werden. Als nächstes können alle Anfangsdaten für acht Speicherzellen in der zweiten Reihe wiederhergestellt werden, indem die Adressen A2, A3 verändert werden. Auf dieselbe Weise können

alle Anfangsdaten für die Speicherzellen in den dritten und vierten Reihen wiederhergestellt werden. Deshalb wird klar, daß die Anfangsdaten (ROM-Daten), die bei dem Herstellungsprozeß geschrieben wurden, bei all den vielen Speicherzellen in derselben Reihe durch das Steuern der Wort- und Plattenleitungen wiederhergestellt werden können, so daß wenig Zeit benötigt wird, um einen Prozeß zum Wiederherstellen der Anfangsdaten auszuführen.

**[0067]** [Fig. 8](#) ist ein erläuterndes Diagramm zum Schreiben von Anfangsdaten der Speicherzelle in 2T2C-Form gemäß der vorliegenden Ausführungsform. Die Größe der Kondensatoren C1 oder C2 kann größer oder kleiner gemacht werden, indem ein Schalter SW1 oder SW2 bei dem Herstellungsprozeß verbunden oder getrennt wird. Die Anfangsdaten können in bezug auf die Schalter SW1, SW2 unter Verwendung von Maskendaten geschrieben werden, die zum Beispiel zeigen, ob ein Durchgangsloch gebildet ist oder nicht. Alternativ werden die Schalter SW1 und SW2 aus Schmelzelementen gebildet, um die Anfangsdaten durch das Trennen von einem Schmelzelement zu schreiben.

**[0068]** Wenn ein Transistor und ein Kondensator die Speicherzelle bilden, können die Anfangsdaten geschrieben werden, indem ein zusätzlicher Kondensator parallel verbunden wird oder nicht verbunden wird.

**[0069]** In den oben beschriebenen Ausführungsformen können die Anfangsdaten (ROM-Daten) geschrieben werden, indem die Dimension von jedem Kondensator einer Speicherzelle verändert wird, um eine verschiedene Hysteresekarakteristik zu ergeben. Die vorliegende Erfindung ist nicht darauf begrenzt, und eine größere Hysteresekarakteristik kann sich ergeben, indem die Dicke des ferroelektrischen Kondensators der Speicherzelle verringert wird, um dessen Kapazität anzuheben. Alternativ wird das Material des ferroelektrischen Kondensators verändert, um die Hysteresekurve größer oder kleiner zu machen, um die Anfangsdaten (ROM-Daten) aufzuzeichnen.

**[0070]** Gemäß der vorliegenden Erfindung können die Anfangsdaten (ROM-Daten) bei dem Herstellungsprozeß geschrieben werden, wie oben erläutert. Dann können die Anfangsdaten wiederhergestellt werden, um die Anfangsdaten in die Speicherzelle zu schreiben. Ferner können die Daten nach der Herstellung durch eine normale Schreiboperation in beliebige Daten verändert werden, und die Anfangsdaten können auch wiederhergestellt werden.

**[0071]** Somit kann die vorliegende Erfindung eine ferroelektrische Speichervorrichtung vorsehen, in der ROM-Daten gehalten werden können, die während der Herstellung gespeichert wurden. Die ferroelektrische

sche Speichervorrichtung gemäß der vorliegenden Erfindung ist besonders als nichtflüchtiger Speicher geeignet, der zum Beispiel in einem Mikrocontroller vorgesehen wird.

### Patentansprüche

1. Ferroelektrische Speichervorrichtung mit: einer Vielzahl von Speicherzellen (MC), die an Schnittpunkten zwischen einer Vielzahl von Bitleitungen (BL, /BL) und einer Vielzahl von Wortleitungen (WL) angeordnet sind, bei der jede von der Vielzahl von Speicherzellen eine erste Speicherzelle (C1, Q1) enthält, die einen ferroelektrischen Kondensator (C1) umfaßt, der eine erste Hysteresekarakteristik hat, und eine zweite Speicherzelle (C2, Q2), die einen ferroelektrischen Kondensator (C2) umfaßt, der eine zweite Hysteresekarakteristik hat, die sich von der ersten Hysteresekarakteristik unterscheidet, erste Daten in den Speicherzellen in Abhängigkeit von den ersten und zweiten Hysteresekarakteristiken gespeichert sind und gemäß den ersten und zweiten Hysteresekarakteristiken ausgelesen werden und zweite Daten in den Speicherzellen in Abhängigkeit von ersten und zweiten Polarisationszuständen gespeichert werden; **dadurch gekennzeichnet**, daß die ferroelektrischen Kondensatoren (C1, C2) mit den verschiedenen Hysteresekarakteristiken bei einem Herstellungsprozeß gebildet werden.

2. Ferroelektrische Speichervorrichtung nach Anspruch 1, bei der die erste Hysteresekarakteristik eine erste Polarisationsveränderung als Antwort auf eine Veränderung einer vorbestimmten Spannung oder eines elektrischen Feldes enthält, die auf den ferroelektrischen Kondensator angewendet werden, und die zweite Hysteresekarakteristik eine zweite Polarisationsveränderung, die größer als die erste Polarisationsveränderung ist, als Antwort auf die Veränderung der vorbestimmten Spannung oder des elektrischen Feldes enthält.

3. Ferroelektrische Speichervorrichtung nach Anspruch 1 oder 2, bei der der ferroelektrische Kondensator (C1), der die erste Hysteresekarakteristik hat, eine kleinere Kapazität als der ferroelektrische Kondensator (C2) hat, der die zweite Hysteresekarakteristik hat.

4. Ferroelektrische Speichervorrichtung nach Anspruch 1, bei der der ferroelektrische Kondensator (C1), der die erste Hysteresekarakteristik hat, eine kleinere Größe oder größere Dicke als der ferroelektrische Kondensator (C2) hat, der die zweite Hysteresekarakteristik hat.

5. Ferroelektrische Speichervorrichtung nach ir-

gendeinem der Ansprüche 1 bis 4, bei der die Speicherzelle einen Zelltransistor (Q1, Q2) hat, der zwischen der Bitleitung (BL, /BL) und dem ferroelektrischen Kondensator (C1, C2) angeordnet ist und dessen Leitfähigkeit durch die Wortleitung (WL) gesteuert wird, und die ersten Daten vorbestimmte aufgezeichnete Daten sind und ausgelesen werden können, indem der ferroelektrische Kondensator (C1, C2) in einen ersten Polarisationszustand gemäß der Hysteresekarakteristik durch Anwenden einer ersten Spannung oder eines ersten elektrischen Feldes auf den ferroelektrischen Kondensator versetzt wird und der ferroelektrische Kondensator in den zweiten Polarisationszustand gemäß der Hysteresekarakteristik durch Verändern der ersten Spannung oder des ersten elektrischen Feldes in eine zweite Spannung oder ein zweites elektrisches Feld versetzt wird, während der ferroelektrische Kondensator mit der Bitleitung (BL, /BL) verbunden ist, so daß sich das Potential der Bitleitung gemäß der Veränderung von dem ersten Polarisationszustand in den zweiten Polarisationszustand verändert.

6. Ferroelektrische Speichervorrichtung nach Anspruch 5, bei der der ferroelektrische Kondensator (C1, C2) gemäß einem Potential der Bitleitung (BL, /BL) in den entsprechenden Polarisationszustand versetzt wird, wenn die ersten Daten ausgelesen sind, so daß die ersten Daten als die zweiten Daten in die Speicherzelle geschrieben werden.

7. Ferroelektrische Speichervorrichtung nach Anspruch 5, ferner mit: einer Rücksetschaltung (12) zum Steuern des Bitleitungspaares (BL, /BL) auf ein vorbestimmtes Potential, um die erste Spannung oder das erste elektrische Feld auf den ferroelektrischen Kondensator (C1, C2) anzuwenden, bevor die ersten Daten auf das Bitleitungspaar (BL, /BL) ausgelesen werden; und einem Leseverstärker (10) zum Detektieren der Veränderung des Potentials der Bitleitung (BL, /BL), während der erste Polarisationszustand in den zweiten Polarisationszustand verändert wird, wodurch die ersten Daten ausgelesen werden.

8. Ferroelektrische Speichervorrichtung nach irgendeinem der Ansprüche 1 bis 7, bei der jede Bitleitung ein Paar von Bitleitungen (BL, /BL) umfaßt, jede Speicherzelle ein Paar von Zelltransistoren (Q1, Q2) enthält, die mit dem Bitleitungspaar verbunden sind, wobei das Paar der ferroelektrischen Kondensatoren (C1, C2) mit dem Paar der Zelltransistoren verbunden ist.

9. Ferroelektrische Speichervorrichtung nach irgendeinem der Ansprüche 1 bis 7, bei der jede erste und zweite Speicherzelle einen Zelltransistor enthält, der mit einer Bitleitung verbunden ist, und der

ferroelektrische Kondensator mit dem Zellentransistor verbunden ist.

Es folgen 12 Blatt Zeichnungen

FIG. 1

2T2C-ZELLE

GEMÄSS DER VORLIEGENDEN ERFINDUNG

FIG. 2

HYSTERESEKURVEN VON KONDENSATOREN

JEWEILS MIT UNTERSCHIEDLICHER DIMENSION

$$q_{s2} + q_{r2} > q_{s1} + q_{r1} > q_{s2} - q_{r2}$$

FIG. 3

ZEITLAGENDIAGRAMM EINES PROZESSES ZUM WIEDERHERSTELLEN VON

ANFANGSDATEN EINER 2T2C-ZELLE

FIG. 4

1T1C-ZELLE

GEMÄSS DER VORLIEGENDEN ERFINDUNG

FIG. 5

HYSEREEKURVEN VON KONDENSATOREN

JEWEILS MIT UNTERSCHIEDLICHER DIMENSION

POLARISATIONSLADUNG [C]

FIG. 6

ZEITLAGENDIAGRAMM EINES PROZESSES ZUM WIEDERHERSTELLEN VON

ANFANGSDATEN EINER 1T1C-ZELLE

(IN BEZUG AUF C1)

GESAMTSTRUKTUR DER FERROELEKTRISCHEN SPEICHERVORRICHTUNG

FIG. 7

FIG. 8

2T2C-ZELLE

FIG. 9

2T2C-ZELLE

NACH STAND DER TECHNIK

FIG. 10

HYSTERESEKURVE VON FERROELEKTRISCHEM FILM

FIG. 11

DEFINITION DER POLARISATIONSRICHTUNG

WENN EINE SPANNUNG ZWISCHEN DEN KONDENSATOREN ANGEWENDET WIRD

WENN KEINE SPANNUNG ZWISCHEN DEN KONDENSATOREN ANGEWENDET WIRD

**FIG. 12**

ZEITLAGENDIAGRAMM EINER DATENSCHREIB- UND -LESEOPERATION EINER

2T2C-ZELLE NACH STAND DER TECHNIK