(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2004-7615

(P2004-7615A)

(43) 公開日 平成16年1月8日(2004.1.8)

(51) Int.CI.<sup>7</sup>H04N 3/18

G09G 1/00

F 1

H04N 3/18

G09G 1/00

G09G 1/00

テーマコード(参考)

5C068

W

X

審査請求 未請求 請求項の数 10 O L (全 10 頁)

(21) 出願番号 特願2003-119623 (P2003-119623)

(22) 出願日 平成15年4月24日 (2003.4.24)

(31) 優先権主張番号 02009136.9

(32) 優先日 平成14年4月24日 (2002.4.24)

(33) 優先権主張国 欧州特許庁 (EP)

(71) 出願人 501263810

トムソン ライセンシング ソシエテ ア

ノニム

Thomson Licensing S

. A.

フランス国、エフ-92100 ブロー

ニュ ビヤンクール、ケ アルフォンス

ル ガロ、46番地

(74) 代理人 100061815

弁理士 矢野 敏雄

(74) 代理人 100094798

弁理士 山崎 利臣

(74) 代理人 100099483

弁理士 久野 琢也

最終頁に続く

(54) 【発明の名称】過剰に高い電圧を発生しないようにする方法

## (57) 【要約】

【課題】大きな許容範囲の問題点、環境の影響の受け易さとエージングを回避するという問題点を克服して、製造中の調節及び調整を簡単にして、X線を発生する高電圧を安全に確実に遮断するCRTディスプレイX線防護方法を提供すること。

【解決手段】高電圧回路が過剰に高い電圧を発生しないようにする方法において、メモリ内に記憶された複数の作動モードの1つに関連した基準値のデジタル表現を読み出し、基準値の表現の保全性を検査し、高電圧回路の出力電圧を示す検知信号を供給し、検知信号を基準値と比較し、この比較が過剰高電圧を示す場合、高電圧出力の発生を抑制する。

【選択図】 図2

**【特許請求の範囲】****【請求項 1】**

高電圧回路が過剰に高い電圧を発生しないようにする方法において、

a ) メモリ内に記憶された複数の作動モードの 1 つに関連した基準値のデジタル表現を読み出すステップ、

b ) 前記基準値の前記表現の保全性 (integrity) を検査するステップ、

c ) 高電圧回路の出力電圧を示す検知信号を供給するステップ、

d ) 前記検知信号を前記基準値と比較するステップ、

e ) ステップ (d) での比較が過剰高電圧を示す場合、高電圧出力の発生を抑制することを特徴とする方法。

10

**【請求項 2】**

異なった作動モード用の異なった基準値の各デジタル表現を読む請求項 1 記載の方法。

**【請求項 3】**

チェックサムアルゴリズムを用いることによって、基準値表現の保全性を検査する請求項 1 記載の方法。

**【請求項 4】**

チェックサムアルゴリズムを、記憶された基準値全ての各表現に適用する請求項 3 記載の方法。

**【請求項 5】**

基準値の表現の保全性を検査するために、前記基準値の異なった少なくとも 2 つの表現を読む請求項 1 記載の方法。

**【請求項 6】**

記憶上限のある基準値を含むことによって、前記基準値の表現の保全性を検査する請求項 1 記載の方法。

**【請求項 7】**

記憶下限のある基準値を含むことによって、前記基準値の表現の保全性を検査する請求項 1 記載の方法。

**【請求項 8】**

基準値の変化した表現を検出することによって、エラー指示信号を形成する請求項 1 から 7 及びの何れか 1 記載の方法。

30

**【請求項 9】**

基準値の変化した表現を、同じ基準値の変化していない他の表現から再構成する請求項 1 から 8 及びの何れか 1 記載の方法。

**【請求項 10】**

基準値の変化した表現を、同じ基準値の変化していない複数の表現から再構成する請求項 9 記載の方法。

**【発明の詳細な説明】****【0001】****【発明の属する技術分野】**

本発明は、高電圧回路が過剰に高い電圧を発生しないようにする方法及び装置に関する。

40

**【0002】****【従来の技術】**

CRT が組み込まれたテレビ製品又はコンピュータディスプレイは、X 線放射に関する厳格な法規制下に置かれている。

**【0003】**

CRT は、電子で面プレート上の蛍光体をたたいて、電子の運動エネルギーを光、熱及び他の形式のエネルギー、例えば、X 線に変換することによって、可視光を放射する。光子放射の周波数スペクトルは、蛍光材料の属性である。ターゲット材料のタイプの他に、X 線周波数の光子の放射の確率は、加速電位（アノード電圧）に依存し、蛍光物質をたたく電子の個数は、時間（「アノード電流」又は「ビーム電流」）の単位である。

50

## 【0004】

高効率テレビ受像機及びコンピュータディスプレイでは、知覚される光出力は、ビーム電流総量と高電圧電力の関数である。そのようなレシーバ及びモニタでは、作動点をできる限り高く設定するのが望ましく、X線防護規則に厳格に従う必要がある。コンポーネントの許容偏差が考慮される場合には、保護回路がいつも受容可能レベルでエラーを生じるが、通常動作で作動するためには、高電圧作動点を、所望値よりも低くしなければならない。

## 【0005】

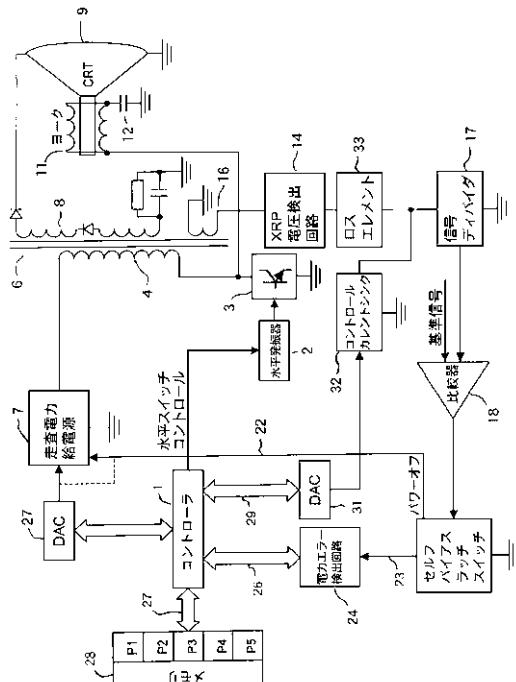

CRTの各モデルは、個別の最大加速電圧、及び、最大許容X線放射に相応するビーム電流を有している。多くのテレビジョンレシーバ及びコンピュータディスプレイでは、「ノーマル作動」のアノード電流は、常に最大値、つまり、最悪の場合の電流以下となるように調整され、最大許容X線放射に関する法規制に違反しないようにされる。何れかの可能な作動点、及び、何れかの可能なエラー状態下で、テレビジョン又はコンピュータディスプレイ機器により、X線が、公表されている限界値を超過しないようにされ、CRTを使うテレビジョンレシーバ及びコンピュータディスプレイの多くは、「エックス線防護回路」 "X-ray protection circuit" 乃至XRP回路を含む。図1には、テレビジョンレシーバモデルの最大許容加速電圧曲線1が、ビーム電流の関数として示されている。テレビジョンレシーバは、2.5kVの高電圧回路許容偏差を有しており、2.3kVのX線保護回路許容偏差が示されている。曲線2は、XRP回路の定格トリップ電圧、曲線3は、上側トリップ電圧、及び曲線4は、XRP回路の下側トリップ電圧を示しており、曲線5は、高電圧トランスの定格電圧、曲線6は、高電圧トランスの上側電圧、曲線7は、各コンポーネントの許容偏差から生じる高電圧トランスの下側電圧を示している。法的要件に従うために、定格作動高電圧は、最大値以下のほぼ9.5kVに設定される。高電圧回路の許容偏差は、精度コンポーネントを選択することによって低減される。高電圧の許容偏差は、高電圧を測定して、高電圧調整のためにフィードバックループを設けることによって殆ど除去することができる。これらの方法は、高価で量産に適していないけれども、テレビジョンレシーバ及びビデオモニタ設計で使われている。

## 【0006】

あるタイプのXRP回路では、エラーが検出された場合に、テレビジョン画像が「見えなくなる("not viewable")」。これを解決するための1つの方法は、水平走査周波数を高くすることであり、それにより、ローリングする画像となる。この方法の欠点は、テレビジョンレシーバが、エラーがあっても作動し続けるという点にある。

## 【0007】

もっと最新タイプの別のXRP回路は、水平偏向を遮断する。高電圧トランスが偏向ヨーク走査電流の整数部であるテレビジョン及びモニタでは、水平偏向をターンオフすると、既述のように、電子ビーム用の加速電位である高電圧を発生しなくなる。最新のテレビジョンレシーバでは、ビデオ、カラープロセッシング、オーディオ、同期分離器、水平及び垂直偏向用のタイミング信号の各回路は、一般に集積回路、又は、チップセット内に含まれている。そのような所謂「ワンチップ」は、「X線防護」ピンを有していることが屡々であり、このピンは、作動された場合に、水平偏向用のドライブを取り外す。水平偏向を停止すると、電界源を取り外すことにより、電子ビームを加速することができるという利点が得られるが、実際には、実行するのが難しい。レシーバとモニタを大きくし、且つ、光出力を多くするために、水平走査回路は、ワイドレンジの負荷条件の下で作動する必要がある。一層効率的に水平走査を駆動する1方法は、負荷に関して水平駆動部にフィードバックする回路を設けることである。この「プロポーショナルドライブ」の技術概念により、負荷電流が増大した場合に、水平出力スイッチへのベースドライブが増大される。しかし、水平走査回路は、もともと共振回路であり、駆動レベルが非常に低くても発振し続けようとする。水平偏向を停止する「X線防護」が明確には実施されていない場合には、エラー時に、水平駆動を完全に取り外すのは難しいことがある。

## 【0008】

10

20

30

40

50

過剰 X 線放射の場合に作動するために、多くの X R P 回路は、アノード電圧の「イメージ」をモニタする。典型的には、高電圧トランスの付加的な巻線により、このイメージが発生され、それにより、磁気結合のために、巻線数によって決定される固定比で、C R T のアノードの高電圧が形成される。付加的又は「X 線防護」巻線電圧は、整流されてから、エラーが発生しているかいないか決定するために基準値と比較される。「X R P 電圧」が基準レベル以下である場合、テレビジョン機器は正常作動であるとされる。アノード電圧を示す「イメージ電圧」が、設定基準レベルを超過した場合、つまり、許容可能な高電圧を超過していることを示しているか、又は、C R T によって放射された X 線のレートを示している場合、X 線防護回路は、機器が「正常作動」を停止するようにする必要がある。

## 【0009】

10

上述の X R P 回路の許容偏差を補償するための 1 方法は、可変抵抗又はポテンシオメータを付加すること、X R P 回路への基準電圧か、又は、付加巻線で発生した「イメージ電圧」のどちらかを調整することである。生産時の調整中、X R P 回路作動用の目標高電圧に達する迄、走査線供給が増大される。それから、ポテンシオメータにより、X R P 出力の状態が変わり、エラーが発生したことを示す迄調整される。しかし、ポテンシオメータを用いると多くの問題が生じることがある。機械的な装置として、汚染、振動、熱膨張及び収縮、及びエージングにさらされる。変化分を減らすために、調整が変えられて、粘着性又は防護性のケースが使われるのが屢々である。

## 【0010】

20

回路許容偏差の影響を低減するための他の方法は、米国特許第 6 0 5 7 6 8 7 号明細書 (Cheng 他) (Mag Technology Co., Ltd., Taipei, Taiwan に登録) に開示されている。この明細書に記載の方法は、付加的な巻線で発生された整流「イメージ電圧」のサンプリング及び変換を使用する。マイクロプロセッサは、アナログ・デジタルコンバータからの高電圧に相応する電圧のデジタル化値を周期的にポーリングして、その結果を、高及び低の限界値と比較し、メモリ内に記憶し、このメモリは、生産時調整中較正されている。上側又は下側限界値のどれかを超過すると、マイクロプロセッサは信号を送出し、高電圧トランスへの電力給電を遮断する。

## 【0011】

30

生産時調節中の高電圧許容偏差を低減する「オープンループ」方法は、電力給電源のフィードバックを調整することができ、所望の高電圧目標値が達成される迄高電圧の 1 次巻線に電力給電される。しかし、この調整方法は、他の回路用の他の 2 次給電での許容偏差が大きくなることがある。

## 【0012】

30

## 【発明が解決しようとする課題】

本発明の課題は、大きな許容範囲の問題点、環境の影響の受け易さとエージングを回避するという問題点を克服して、製造中の調節及び調整を簡単にして、X 線を発生する高電圧を安全に確実に遮断する C R T ディスプレイ X 線防護方法を提供することにある。

## 【0013】

40

## 【課題を解決するための手段】

課題を解決するため、本発明は、高電圧回路が過剰に高い電圧を発生しないようにする方法において、

- a ) メモリ内に記憶された複数の作動モードの 1 つに関連した基準値のデジタル表現を読み出すステップ、

- b ) 基準値の表現の保全性を検査するステップ、

- c ) 高電圧回路の出力電圧を示す検知信号を供給するステップ、

- d ) 検知信号を基準値と比較するステップ、

- e ) ステップ (d) での比較が過剰高電圧を示す場合、高電圧出力の発生を抑制することを提案するものである。

## 【0014】

50

## 【発明の実施の形態】

従属請求項記載の手段によって、本発明の方法の有利な実施例及び改善が可能である。利点は以下の通り：回路許容偏差のインパクトが低減され、環境からの影響が低減され、サポートされた各作動周波数毎に別個に調節することができ、調節エラーを検出することができる。

#### 【0015】

別の利点は、以下の説明から分かる。

#### 【0016】

#### 【実施例】

以下、図示の実施例を用いて、本発明について詳細に説明する。

#### 【0017】

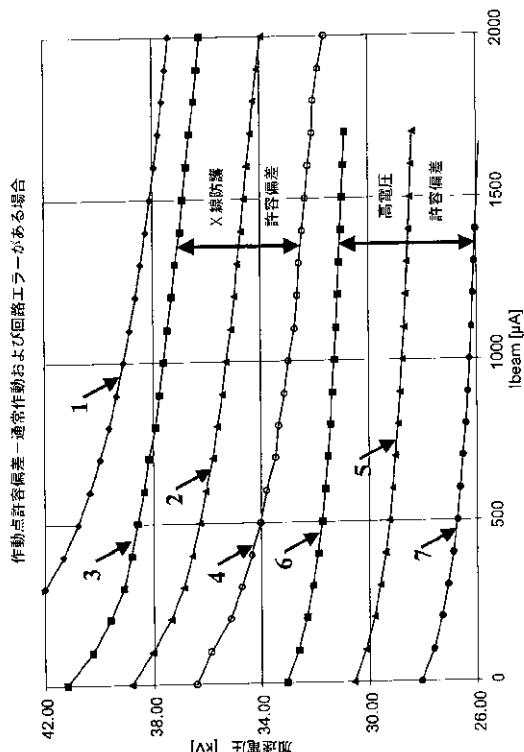

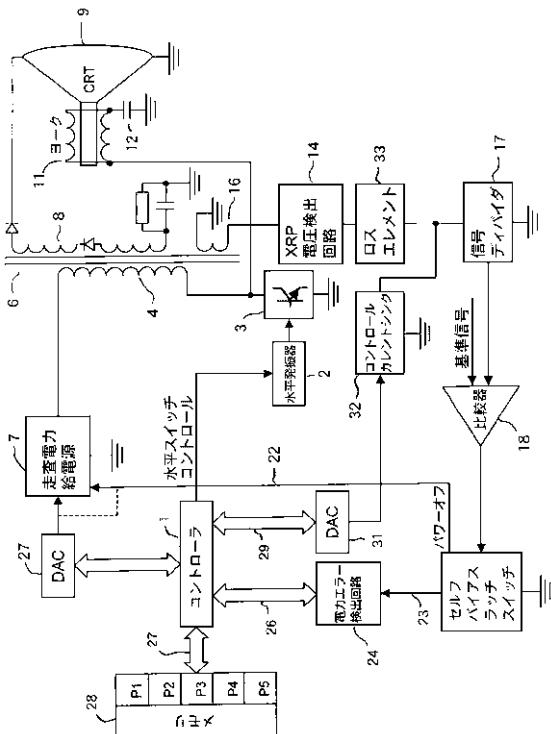

図2には、CRTを有するTVモニタ又はコンピュータモニタの簡単なダイアグラムが示されている。コントローラ1は、水平走査スイッチ3用の駆動信号を発生するための水平発振器2を制御する。水平走査スイッチ3は、高電圧トランス6の1次巻線4の一端に接続されている。1次巻線4の他端は、走査電力給電源7に接続されている。水平走査スイッチ3をスイッチングすることによって、高電圧トランス6の2次巻線8内に高電圧が発生される。CRT(図示していない)のアノード電極によって送出された電子ビームの加速電位を供給するために、高電圧が陰極管(CRT)9に接続されている。電子ビームは、ヨーク11によって発生されて水平スイッチ3によって制御された磁場を通過し、その際、ラスタスキャニング方法で偏向される。ヨーク11は、一端が帰線キャパシタ12に接続されており、他端が水平走査スイッチ3に接続されている。電圧検出回路14は、トランス6の3次巻線16及び信号ディバイダ17に接続されており、この信号ディバイダの出力側には、信号比較器18の一方の入力側に供給される信号が送出される。基準信号19は、比較器18の第2の入力側に供給される。比較器18の出力信号は、セルフバイアスラッチスイッチ21への入力である。高電圧トランス6の3次巻線16には、2次巻線と3次巻線との比に比例する高電圧が形成されるものとする。従って、3次巻線の両端電圧を検出することによって、2次巻線8の高電圧についての情報が導出される。基準信号は、高電圧トランス6の3次巻線16の高電圧を示す信号と比較される。基準値の超過により、信号比較器の出力側の信号は、その状態が変わり、従って、セルフバイアスラッチスイッチ21が作動される。セルフバイアスラッチスイッチ21は、第1のポイントで、電力源に接続されたオンオフ制御線22に接続されており、従って、制御線にラッチ信号が供給されることによって電力源の作動が直ぐに抑制される。水平走査スイッチ3用の駆動信号を発生するための水平発振器2は、スイッチ3を作動状態にし続け、それにより、電力源7内に蓄積されたエネルギー、及び、トランス6の2次巻線8及び関連の各コンポーネントからの高電圧が放電される。セルフバイアスラッチスイッチ21の第2の接続部23は、ラッチ信号を、エラー状態をシグナリングする電力エラー検出回路24に送出する。コントローラ1は、バス接続26を介して、電力エラー検出回路の状態を周期的にポーリングし、従って、エラー状態が検出されると、所定時間経過後、駆動信号を発生するための手段2を制御することによって、水平走査スイッチ3の作動が抑制される。WRPエラーに続くシーケンスで、コントローラ1は、セルフバイアスラッチスイッチへの電力を遮断し、スイッチをリセットし、他のコンポーネント全てをリセットし、リスタートするために電力給電する。XRPエラーが直ぐに再発した場合には、コントローラは、ディスプレイデバイスが更に作動するのを抑制する。ディスプレイデバイスをリスタートするために、コントローラ1は、電力源及び回路内の他のコンポーネントをリセットし、電力オンオフ制御線22をローにし、従って、セルフバイアス電流をラッチスイッチ21から切り離す。

#### 【0018】

既述の高電圧回路を、1タイプのCRTの異なった作動モード又は異なったタイプのCRTに適合可能にするために、コントローラ1は、ディバイダ17から比較器18に供給される信号を処理する。

#### 【0019】

10

20

30

40

50

コントローラ1は、メモリ28からの動作モードに関連した制御データをバスライン27を介して読む。メモリ28内には、1セットの基準値の多種の例が異なった格納位置（ページとして言及されることが屡々ある）内に記憶されている（メモリ28のP1...P5として図示されている）。メモリ28の何らかのセルに物理的なエラーがある場合でも、メモリからのデータを安全に回復するために、ページメモリは、メモリ28内の異なった物理領域内に配置するとよい。

#### 【0020】

コントローラ1は、制御データをバスライン29を介してデジタル／アナログ変換器31に転送する。DAC31のアナログ出力信号は、カレントシンク32を制御し、カレントシンク32は、ロスエレメント33と共に働いて、ディバイダ17の入力信号レベルを決める。このようにして、基準信号が変えられないままで、比較器の異なったスイッチングレベルが選択可能である。10

#### 【0021】

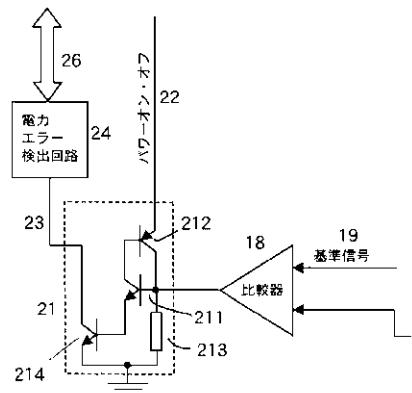

図3には、図2の本発明回路の有利な実施例の部分拡大図が示されている。この実施例では、過剰高電圧の場合に、比較器18は、トランジスタ211のベース-エミッタダイオードを順方向バイアスするのに十分な電圧の信号を送出して、トランジスタ211のコレクタ電極からエミッタ電極への導電路を形成する。その際、電流路が形成されて、順方向バイアストランジスタ211に制御電流が流れる。この結果、次に、トランジスタ212のエミッタ電極からコレクタ電極に電流が流れ、オンオフ制御線22からの電流が電力源7から引き込まれ、それにより、電力給電が抑制される。通電により、抵抗213の両端に電圧が形成され、この電圧は、比較器18からの信号がなくても、トランジスタ211を導通状態にし続けるのに十分である。トランジスタ212のベース-エミッタダイオード、及び、トランジスタ211のコレクタ-エミッタ路を流れる電流により、トランジスタ214が導通状態にスイッチングされる。この結果、次に、電力エラー検出回路24への接続部26が接地される。コントローラ1は、電力エラー検出回路24の状態について周期的にポーリングし、高電圧トランス6の2次巻線8からの高電圧を制御して遮断した後、駆動信号発生器2を相応に制御して、水平走査スイッチ3を抑制する。20

#### 【0022】

他の有利な実施例では、電力源が専用のオンオフコントロール入力を特徴としない場合、電力オンオフライン22は、例えば、DAC28からの電圧制御信号27を、図2及び3に破線で示されているように、ローに駆動するために使うとよく、それにより、電力源7が作動停止される。30

#### 【0023】

既述の回路と共に、メモリ28から読み出されるデータはノイズの影響があることがあるという点について考慮することは大切である。そのような場合に、何らかの危険な事象を回避するために、メモリ28から読み出されたデータの保全性が検査される。電子的に整列することによって、記憶装置内にランダムにエラーが生じるか、又は、全ての格納位置がずっとエラー状態であることがある。本発明の方法の1実施例によると、チェックサムアルゴリズムがデータに適用される。孤立したランダムなエラーの場合には、チェックサムアルゴリズムにより、1エラーの最小値をいつも検出することができるようになる。多種のエラーの性質に依存して、アルゴリズムは多種のエラーを十分に検出する。40

#### 【0024】

記憶装置内の全ての格納位置にエラーがある場合、全ての格納位置が同じ値を有している結果、それらは同じようにエラーが生じている。アドレッシングされる必要がある2つの特別な場合がある。記憶装置は、記憶装置全体がエラー状態であるために、又は、初めから装置のプログラミングにエラーがあるために、全てゼロか、又は、全て1を有していることがある。チェックサムアルゴリズムにより、常に個別調節の各値とは異なったチェックサムが形成される。従って、全ての調節格納位置がチェックサムと同じ値を有しているかどうかエラーが検出される。このような、調節の特性により、装置がプログラミングされていないことが保証され、又は、全ての格納位置内に同じ値（典型的にはゼロ又は1）50

が記憶されているようなエラー状態のある装置が検出され、X線が放射されていないことが保証されるようになる。

#### 【0025】

調節値の保全性を確実にするために付加的に測定される。調節格納位置は、一度書き込まれたら、リードオンリーであり、それにより、格納位置が不正に書き込まれるのが阻止される。調節値は、隣接格納位置には記憶されていない。こうすることにより、エラー検出の際に有利となり、記憶装置に1メモリブロックしかエラーがないかどうか、調節データ又はチェックサム保全性が維持されているかどうか、エラーがランダムとなるように現れているか、アルゴリズムによって容易に検出されるような孤立したエラーであるか検出される。結局、調節データの限界範囲が分かると、使う前に、各個別調節を検証することができるようになる。従って、計算されたチェックサムが記憶されたチェックサムと等しいような多種のエラーが生じている場合、個別調節格納位置の内容が妥当でないので、エラー状態が未だ検出される。10

#### 【0026】

本発明の方法の別の実施例では、同じデータの幾つかの例が読み出されて、データの保全性が検証される。D A C出力値ブロックは、5つの異なったページを用いて、メモリ28の5つの格納位置に記憶されている。單一ブロックへのリードアクセスが常に2回繰り返され、両方のリードがエラーなしに同じ値を戻した場合に限ってしか、その値は妥当でない。20

#### 【0027】

ブロックは以下の構造である：

ビット 7 6 5 4 3 2 1 0

バイト1 P P D D D D D D pは偶数パリティであり、2回記憶される。

#### 【0028】

バイト2 D D D D D D P P DはD A Cレジスタの6ビット値である。

#### 【0029】

バイト3 p p d d d d d d pは奇数パリティであり、2回記憶される。

#### 【0030】

バイト4 d d d d d d p p dは6ビット値の補数である。

#### 【0031】

6ビット値が、ブロック内に4回異なったビット位置で記憶される。各回毎に、残りの2ビットがパリティビットで充填される。1つ又は複数のパリティビットが間違っているか、又は、復号された4つのD A C値が全て同一とはかぎらない場合、ブロックは汚染されているものと定義される。30

#### 【0032】

(全部で5つのブロックのうち)1つ又は2つの汚染ブロックが検出された場合、残りの4つ又は3つの正しいブロックは、エラーを含む単数又は複数のブロックを補正するために使われる。偏向開始前にチェックされる。

#### 【0033】

2つ以上のブロックが汚染されている場合、T Vはスタンバイモードにされ続け、エラーコードを記憶して、エラーコードを点滅して指示する。レジスタD A C出力のN V M値は、00Hにリセットされる必要がある。従って、D A C値00Hにより、水平駆動開始後直ぐに常にアクティブであるので、もはや偏向開始できない。40

#### 【0034】

#### 【発明の効果】

本発明の利点は、汚染されたデータにより、特にX線防護に関して何らかの危険な状況が生じることはない点にある。

#### 【0035】

本発明によると、ルーチンとして定期的に、記憶されたX線防護データが妥当であることが検証されるという顕著な効果を奏することができる。本発明によると、回路許容偏差の50

インパクトを低減することができ、環境の影響を低減することができ、サポートされた各作動周波数に対して個別に調節可能であり、調節エラーを検出することができる。

【図面の簡単な説明】

【図1】従来技術により構成された高電圧回路の例での高電圧発生器及びX線防護回路の作動点許容偏差を、CRTの例示モデル用の最大許容可能加速電圧に沿って示す図

【図2】CRT及び本発明の高電圧回路が組み込まれているディスプレイのブロックダイアグラムを示す図

【図3】図2の本発明回路の一部分の詳細図

【符号の説明】

|     |                         |    |

|-----|-------------------------|----|

| 1   | コントローラ                  | 10 |

| 2   | 水平発振器                   |    |

| 3   | 水平走査スイッチ                |    |

| 4   | 1次巻線                    |    |

| 6   | 高電圧トランス                 |    |

| 7   | 走査電力給電源                 |    |

| 8   | 2次巻線                    |    |

| 9   | 陰極管(CRT)                |    |

| 11  | ヨーク                     |    |

| 12  | 帰線キャパシタ                 |    |

| 14  | 電圧検出回路                  | 20 |

| 16  | トランス6の3次巻線              |    |

| 17  | 信号ディバイダ                 |    |

| 18  | 信号比較器                   |    |

| 19  | 基準信号                    |    |

| 21  | セルフバイアスラッチスイッチ          |    |

| 22  | オンオフ制御線                 |    |

| 23  | セルフバイアスラッチスイッチ21の第2の接続部 |    |

| 24  | 電力エラー検出回路               |    |

| 26  | バス接続                    |    |

| 28  | メモリ                     | 30 |

| 29  | バスライン                   |    |

| 31  | デジタル/アナログ変換器            |    |

| 32  | カレントシンク                 |    |

| 33  | ロスエレメント                 |    |

| 211 | 順方向バイアストランジスタ           |    |

| 212 | トランジスタ                  |    |

| 213 | 抵抗                      |    |

| 214 | トランジスタ                  |    |

【図1】

【図2】

【図3】

---

フロントページの続き

(74)代理人 100114890

弁理士 アインゼル・フェリックス=ラインハルト

(72)発明者 デイヴィッド ロス ジャクソン

アメリカ合衆国 インディアナ - マリオン インディアナポリス アビイ クリーク レーン 4

422

(72)発明者 アンジェラ レネ バーネット

アメリカ合衆国 インディアナ - マリオン インディアナポリス ブレトン ウッド ドライヴ

6821

(72)発明者 ミヒヤエル マイオラノ

ドイツ連邦共和国 ファウエス - シュヴェニンゲン シュトゥルムビュールシュトラーセ 198

(72)発明者 チャールズ ハーディング

ドイツ連邦共和国 ファウエス - リートハイム プファッフェンヴァイラー シュトラーセ 5

Fターム(参考) 5C068 AA14 CB01 CC01 CC11