(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2010-267341

(P2010-267341A)

(43) 公開日 平成22年11月25日(2010.11.25)

| (51) Int.Cl.             | F 1          | テーマコード (参考)       |

|--------------------------|--------------|-------------------|

| G 11 C 16/02 (2006.01)   | G 11 C 17/00 | 6 1 4 5 B 1 2 5   |

| H 01 L 27/115 (2006.01)  | G 11 C 17/00 | 6 1 2 B 5 F 0 8 3 |

| H 01 L 21/8247 (2006.01) | H 01 L 27/10 | 4 3 4 5 F 1 0 1   |

| H 01 L 27/10 (2006.01)   | H 01 L 27/10 | 4 8 1             |

| H 01 L 29/788 (2006.01)  | H 01 L 29/78 | 3 7 1             |

審査請求 未請求 請求項の数 18 O L (全 77 頁) 最終頁に続く

|           |                              |          |                                                |

|-----------|------------------------------|----------|------------------------------------------------|

| (21) 出願番号 | 特願2009-119016 (P2009-119016) | (71) 出願人 | 302062931 ルネサスエレクトロニクス株式会社 神奈川県川崎市中原区下沼部1753番地 |

| (22) 出願日  | 平成21年5月15日 (2009.5.15)       | (74) 代理人 | 100064746 弁理士 深見 久郎                            |

|           |                              | (74) 代理人 | 100085132 弁理士 森田 俊雄                            |

|           |                              | (74) 代理人 | 100083703 弁理士 仲村 義平                            |

|           |                              | (74) 代理人 | 100096781 弁理士 堀井 豊                             |

|           |                              | (74) 代理人 | 100109162 弁理士 酒井 将行                            |

|           |                              | (74) 代理人 | 100111246 弁理士 荒川 伸夫                            |

|           |                              |          | 最終頁に続く                                         |

(54) 【発明の名称】半導体装置

## (57) 【要約】

【課題】消去時間の短縮を行なうとともにデータアクセスを効率的に実行することのできる不揮発性メモリ機能を有する半導体装置を提供する。

【解決手段】コマンドレジスタ／制御回路(24)の制御のもとに、メモリセル境界領域に配置される埋込消去ゲート配線(4)に対して消去電圧を印加し、フローティングゲート(FG)と埋込消去ゲートEGの間で電荷を移動させて消去動作を行なうとき、消去電圧印加中にメモリゲート線(MGL)およびアシストゲート線(AGL)に読み出選択電圧を印加してデータの読み出を実行する。

【選択図】図9

**【特許請求の範囲】**

**【請求項 1】**

行列状に配列され、各々が基板領域上に形成されるフローティングゲートと、前記フローティングゲート上に配置されるメモリゲートとを有するメモリトランジスタと、前記フローティングゲートおよびメモリゲートに隣接して配置されるアシストゲートとを有し、前記メモリトランジスタと直列に接続されるアシストゲートトランジスタと、前記基板領域表面に形成される素子分離領域表面に形成される埋込消去ゲートとを有し、該フローティングゲートの蓄積電荷量に応じて不揮発的にデータを記憶する複数のメモリセル、

各前記メモリセル行に対応して配置され、各々が対応の行のメモリセルのメモリゲートに結合される複数のメモリゲート線、

各前記メモリセル行に対応して配置され、各々が対応の行のアシストゲートに結合される複数のアシストゲート線、

各前記メモリセル列に対応して配置され、各々が対応の列の埋込消去ゲートに結合される複数の埋込消去ゲート配線、

各前記メモリセル列に対応して配置され、各々が対応の列のメモリセルのメモリトランジスタの第1の導通ノードに結合される複数のソース線、

各前記メモリセル列に対応して配置され、各々が対応の列のメモリセルのアシストゲートトランジスタの第2の導通ノードに結合される複数のビット線、および

動作モード指示とアドレス信号とに従って指定されたメモリセルに対して指定された動作を制御する制御回路を備え、前記制御回路は、消去動作が指定されたとき、選択メモリセルに対するソース線、メモリゲート線および埋込消去ゲート配線それぞれに供給される電圧を指定するとともに消去動作を制御する消去制御部と、前記選択メモリセルに対するアシストゲート線およびビット線に対して供給される読出に必要な電圧を指定するとともに読出動作を制御する読出制御部とを含み、前記消去制御部および前記読出制御部は、並行して動作可能であり、

前記消去制御部および読出制御部からの電圧選択信号に従って指定された電圧を発生する電圧発生回路、

前記電圧発生回路からの消去電圧を選択されたメモリセルの埋込消去ゲート配線に伝達する消去回路、および

前記電圧発生回路からの読出電圧を選択されたメモリセルへ供給して前記選択メモリセルの記憶データを読出す読出回路を備え、前記読出回路は前記消去回路の消去電圧印加中に前記記憶データの読出を行うように前記制御回路により動作制御される、半導体装置。半導体装置。

**【請求項 2】**

前記読出回路は、前記消去動作を行なうために選択されたメモリセルの消去状態を検証するためのデータ読出を行う、請求項1記載の半導体装置。

**【請求項 3】**

前記読出制御部は、前記選択メモリセルが接続するビット線と異なるビット線に接続される非選択メモリセルに対する記憶データの読出を制御する、請求項1記載の半導体装置。

**【請求項 4】**

前記制御回路は、前記消去動作を行なうために選択されたメモリセルの消去状態を検証するベリファイ読出動作を制御する消去ベリファイ制御回路をさらに備え、

前記読出制御部は、前記動作モード指示が消去動作を指示しているときに前記動作モード指示に従って読出動作が指定されると前記選択メモリセルのアシストゲート線に接続される非選択メモリセルに対する記憶データの読出を制御する、請求項1記載の半導体装置。

**【請求項 5】**

前記複数のメモリセルは、複数の消去単位に分割され、前記ビット線は前記複数の消去単位に対して共通に配置され、

10

20

30

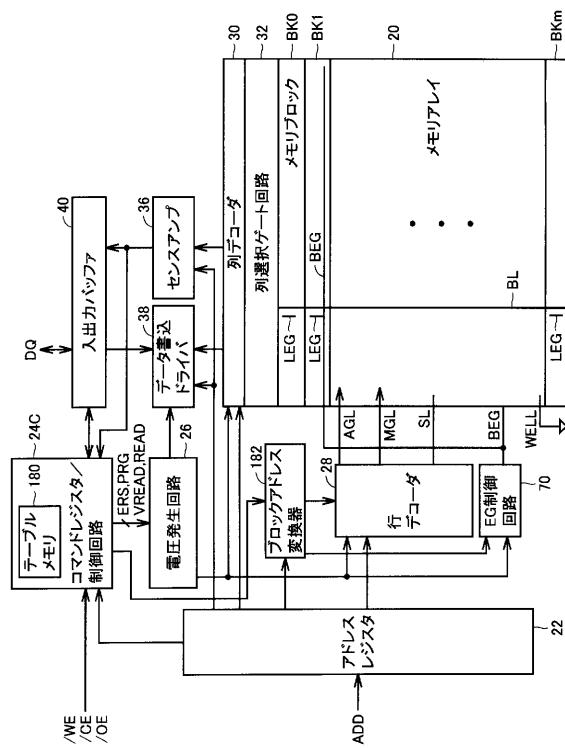

40

50

前記埋込消去ゲート配線は、各前記消去単位に分割され、

前記制御回路は、動作モード指示とアドレス信号とに応答して前記消去のために選択されたメモリセルが含まれる消去単位と異なる消去単位の非選択メモリセルに対して、前記消去制御部による前記消去のために選択されたメモリセルへの消去電圧の印加と並行して書きを行なうように前記書き回路を制御する書き制御部をさらに備える、請求項1記載の半導体装置。

#### 【請求項6】

前記消去電圧の印加中に読出すとき、前記読み出し制御部は、読み出電圧を、前記消去のための消去電圧パルス印加期間よりも短い期間印加するとともに前記消去パルス印加期間よりも短い間隔で前記読み出電圧を印加するように前記読み出回路を制御する、請求項1記載の半導体装置。 10

#### 【請求項7】

行列状に配列され、各々がデータを記憶する電荷蓄積層とデータを消去する消去ゲートとを少なくとも備える複数の不揮発性メモリセルを有し、かつ複数のブロックに分割されるメモリアレイ、

前記複数のブロックに対して共通に設けられ、消去モード指示に応答して前記メモリアレイの選択ブロックに対して消去電圧を少なくとも前記消去ゲートに印加して該選択ブロックの不揮発性メモリセルの記憶データの消去を行なう動作を制御する消去制御回路、および

前記複数のブロックに対して共通に設けられ、アクセス指示に応答して、前記選択ブロックへの消去電圧印加期間中に前記選択ブロックと異なるブロックの不揮発性メモリセルに対してデータアクセスを行なう動作を制御するデータアクセス制御回路を備える、半導体装置。 20

#### 【請求項8】

前記消去制御回路は、消去ベリファイ動作を実行時、該消去ベリファイを示す信号を外部へ出力し、

前記データアクセス制御回路は、内部でのデータアクセスを示す信号を外部へ出力する、請求項7記載の半導体装置。

#### 【請求項9】

前記消去制御回路は、消去時に前記選択ブロックのメモリセルが消去状態にあるかを検証する動作を制御する消去ベリファイ制御部を備え、 30

前記データアクセス制御回路は、外部からのデータアクセス要求時、前記消去ベリファイ制御部が消去ベリファイ制御を実行中のときには前記ベリファイ制御部の消去ベリファイ動作を停止させて前記データアクセス要求に応じたアクセス動作を実行するように動作制御し、前記データアクセス要求に応じたアクセス動作完了後、前記消去ベリファイ部の制御動作停止を解除して消去ベリファイ動作を継続させる、請求項7記載の半導体装置。

#### 【請求項10】

前記メモリアレイの消去対象を特定するブロックを指定する消去アドレスを順次格納するファーストインファーストアウトレジスタをさらに備え、

前記消去制御回路は、前記ファーストインファーストアウトレジスタに格納された消去アドレスに従って消去対象のブロックに対する消去動作制御を順次実行する、請求項7記載の半導体装置。 40

#### 【請求項11】

各々が前記メモリアレイの消去対象のブロックを指定する消去アドレスを格納するとともに格納内容を並列に出力する複数のレジスタと、

消去期間を規定する時間をカウントするタイマとをさらに備え、

前記消去制御回路は、前記複数のレジスタに格納された消去アドレスに従って消去対象のブロックに対する消去動作を並行して実行し、該消去動作の最長期間は前記タイマのカウント値により規定される、請求項7記載の半導体装置。

#### 【請求項12】

前記消去制御回路は、前記レジスタへの消去アドレスの格納時に前記タイマを初期値にリセットして該初期値からカウント動作を行わせる、請求項11記載の半導体装置。

#### 【請求項13】

前記複数のブロックは、2つのブロックが対をなすように配置され、

前記消去制御回路および前記データアクセス制御回路は、外部からのデータ書込指示に応答して前記選択ブロックと対をなすように予め定められたブロックを並行して選択して前記選択ブロックに対する消去と前記予め定められたブロックに対して書込を並行して実行するように制御するとともに、前記対をなすブロックにおいては書込および消去を行うブロックが交互に切換えられる、請求項7記載の半導体装置。

#### 【請求項14】

前記不揮発性メモリセルは、

単層選択ゲートを有し、選択信号に応答して選択的に導通する選択トランジスタと、

前記選択トランジスタと直列に接続され、電荷を蓄積するフローティング状態の電荷蓄積層とを有する単層ゲート構造のメモリトランジスタと、

メモリセル境界領域に配置されて隣接メモリセルを分離する素子分離膜上に形成され、消去動作時、前記電荷蓄積層との間で電荷を移動させる消去ゲートとを備える、請求項7記載の半導体装置。

#### 【請求項15】

前記不揮発性メモリセルは、

互いに積層されるとともに電気的に短絡される第1および第2の選択ゲート層を有し、選択信号に応答して選択的に導通する選択トランジスタと、

前記選択トランジスタと直列に接続され、電荷を蓄積するフローティング状態の電荷蓄積層と、前記電荷蓄積層上に形成され、前記電荷蓄積層への電荷の移動を制御する制御ゲートを有する積層ゲート構造のメモリトランジスタと、

メモリセル境界領域に配置されて隣接メモリセルを分離する絶縁膜上に形成され、消去動作時、前記電荷蓄積層との間で電荷を移動させる消去ゲートとを備える、請求項7記載の半導体装置。

#### 【請求項16】

各前記不揮発性メモリセルは、

基板領域上に形成され、電荷を蓄積するフローティング状態の電荷蓄積層と、

少なくともデータ読出時に該不揮発性メモリセルを選択する信号が印加される選択ゲートと、

前記基板領域上に前記選択ゲートと平行に配置され、消去時に前記電荷蓄積層との間で電荷を移動させる消去ゲートとを備える、請求項7記載の半導体装置。

#### 【請求項17】

行列状に配列され、各々が情報を不揮発的に記憶する複数の不揮発性メモリセルを有するメモリアレイを備え、各前記不揮発性メモリセルは、単層選択ゲートを有し、選択信号に応答して選択的に導通する選択トランジスタと、前記選択トランジスタと直列に接続され、電荷を蓄積するフローティング状態の電荷蓄積層と、ソース線に結合される第1の不純物領域とを有する単層ゲート構造のメモリトランジスタと、隣接メモリセルを分離する分離膜表面に配置され、消去動作時、前記電荷蓄積層との間で電荷を移動させる消去ゲートとを備え、

各前記メモリセル行に対応して配置され、各々に対応の行の不揮発性メモリセルの選択ゲートが接続される複数のワード線、および

各前記メモリセル列に対応して配置され、各々に対応の列のメモリセルの選択トランジスタの第2の不純物領域が接続される複数のビット線を備える、半導体装置。

#### 【請求項18】

行列状に配列され、各々が情報を不揮発的に記憶する複数の不揮発性メモリセルを有するメモリアレイを備え、各前記不揮発性メモリセルは、互いに積層されるとともに電気的に短絡される第1および第2の選択ゲート層を有し選択信号に応答して選択的に導通する

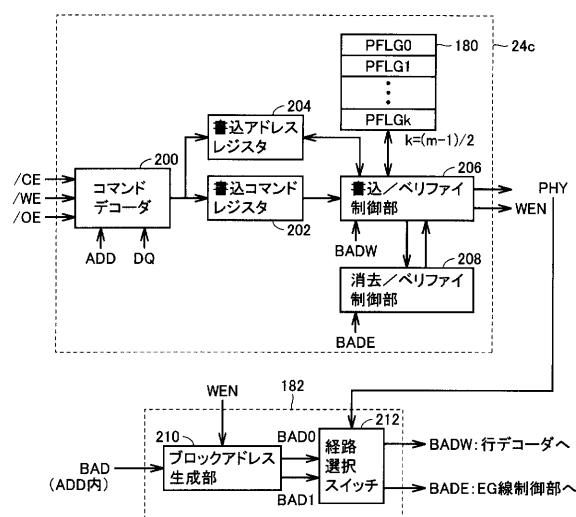

10

20

30

40

50

選択トランジスタと、前記選択トランジスタと直列に接続され、電荷を蓄積するフローティング状態の電荷蓄積層と、前記電荷蓄積層上に形成されて前記電荷蓄積層への電荷の移動を制御する制御ゲートとを有する積層ゲート構造のメモリトランジスタと、隣接メモリセルを分離する分離膜表面に形成され、消去動作時、前記電荷蓄積層との間で電荷を移動させる消去ゲートとを備え、

各前記メモリセル行に対応して配置され、各々が対応の行のメモリセルの選択トランジスタの選択ゲートに接続される複数のワード線、および

各前記メモリセル列に対応して配置され、各々が対応の列のメモリセルの選択トランジスタの不純物領域に接続される複数のビット線とを備える、半導体装置。

【発明の詳細な説明】

10

【技術分野】

【0001】

この発明は、情報を不揮発的に記憶する機能を有する半導体装置に関し、特に、フローティングゲートなどの電荷蓄積層に蓄積される電荷量に応じて情報を不揮発的に記憶する不揮発性メモリセルを有する半導体装置に関する。より特定的には、この発明は、消去動作モード時に並行してデータアクセスを行なうための構成に関する。

【背景技術】

【0002】

フラッシュメモリは、情報を不揮発的に格納するメモリであり、プロセッサに対するポート用プログラム情報の格納および携帯機器におけるダウンロードデータなどのアプリケーションデータ／プログラムを格納するためなど広く用いられている。

20

【0003】

通常、マイクロコンピュータに内蔵される混載フラッシュメモリは、メモリサイズが、数KB（Kバイト）から数百KBである。通常のNOR型フラッシュメモリセルにおいて消去動作を行なう場合、コントロールゲートに-10V、基板領域へ10Vを印加する必要がある。この基板消去電圧が、メモリセルトランジスタのソースおよびドレイン領域を介してソース線およびビット線に伝達される。したがって、メモリセルの消去状態を確認するベリファイ動作は、各領域を初期状態に復帰させてベリファイ読出を行なう必要があり、消去電圧の供給を停止してから所定時間経過後に消去ベリファイを行なっている。このため、消去動作が長くなるという問題が生じる。

30

【0004】

また、フラッシュメモリにおいては、1つのメモリバンクに対して消去動作を行っている間に別のメモリバンクに対してデータ読出アクセスを行うバックグラウンドオペレーションモード（BGOモード）がサポートされているメモリがある。しかしながら、BGOモード搭載のフラッシュメモリにおいては、複数のバンクが必要となり、マイクロコンピュータに内蔵される混載フラッシュメモリのような小規模のメモリにおいては、複数バンク構成により面積が増大し、応じて、マイクロコンピュータの面積が増大するという問題が生じる。

【0005】

また、消去モード時のアクセス効率を改善するために、サスペンドモードを備えるフラッシュメモリがある。このサスペンドモードにおいては、消去動作を一旦停止してデータの読出（外部アクセス）を行なう。この読出動作完了後、再び停止された消去動作を再開する。このため、消去動作を一時停止させるための制御回路が必要となり、制御回路の面積が増大するという問題が生じる。また、消去動作を停止させるため、消去時間が長くなるという問題が生じる。

40

【0006】

また、消去ゲートをワード線（メモリセル行）方向に延在させて各ブロックごとに分離し、ブロック単位で消去を行なう構成が、特許文献1（特開平1-91395号公報）に示されている。この特許文献1に示される不揮発性メモリセルにおいては、消去動作時、消去ゲートにたとえば27Vの正の高電圧を印加し、ビット線、ソース線およびコントロ

50

ールゲートを0Vにする。これにより、フローティングゲートから消去ゲートに電子が引抜かれ、フローティングゲートを正に帯電させる。データ書込時においては、コントロールゲートにたとえば21Vの正の高電圧、ドレインを10V、ソースを0V、消去ゲートをたとえば5Vに設定する。これにより、ドレイン近傍においてホットエレクトロンを発生させ、このホットエレクトロンのインパクトアイオナイゼーション(impact ionization)により発生した高エネルギー電子をフローティングゲート中に注入する。消去ゲート線は、ブロック内で消去線に共通に結合され、ブロック単位での消去を行なうことができる。これにより、特許文献1は消去時間の短縮を実現することを図る。

#### 【0007】

また、消去ゲートを不純物層で形成してメモリセルのサイズを低減することを図る構成が、特許文献2（特開2008-270708号公報）に示されている。この特許文献2に示される構成においては、第1の方向に第1のプログラム線、第1の消去線および第1のワード線を配置する。第1のプログラム線は、メモリセルのプログラムゲート（不純物領域）に接続し、第1の消去線はメモリセルの消去ゲート（不純物領域）に接続され、第1のワード線がメモリセルのワード線ノード（コントロールゲート）に接続される。この特許文献2においては、消去ゲートを構成する不純物層を、プログラムゲート線を構成する不純物領域とビット線に接続する不純物領域の間に配置する。消去ゲート線およびプログラム線を同一方向に配置することにより、同一行の隣接メモリセルに消去ゲート不純物領域を共有させてメモリセルサイズを低減することを図る。また、消去線とプログラム線を同一方向に配置することにより、プログラム動作および消去動作を、1つのページ（ワード線）に制限し、他のページに対してプログラム障害（ディスタークション）が発生するのを抑制することを図る。

10

20

30

40

#### 【先行技術文献】

#### 【特許文献】

#### 【0008】

【特許文献1】特開平1-91395号公報

【特許文献2】特開2008-270708号公報

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0009】

上述の特許文献1に示されるように消去ゲート線をワード線方向に配置し、コントロールゲートおよび消去ゲートを分離して配置することにより、消去電圧を印加する消去ゲート線と書込および読出に必要なメモリゲート線、ビット線およびソース線を分離することができる。しかしながら、この特許文献1の構成においては、消去電圧が基板領域上に形成されており、消去電圧を印加した状態でデータの読出または書込を行なうことができない。消去動作のみを単独で行なうことが考慮されており、BGOモードまたはサスPENDモードのような消去動作と並行して書込または読出を行なう構成については何ら考慮されていない。また、消去ゲート線にたとえば27Vの高電圧を印加しており、消去ベリファイを行なう場合、消去ゲート線の電圧が十分に低下した後にデータの読出を行なう必要がある。このため、消去時間を短縮することが困難となるという問題が生じる。

#### 【0010】

また、特許文献2に示される構成においては、不純物層をプログラムゲートおよび消去ゲートとしてメモリトランジスタのソース／ドレイン不純物領域と別に平行に配置している。したがって、隣接メモリセル間で消去ゲート領域を共有して、メモリセルサイズを低減することができる。しかしながら、この特許文献2の構成の場合、プログラムゲートを構成する不純物領域および消去ゲートを構成する不純物領域が1つのメモリセル領域内にメモリトランジスタのソースおよびドレイン不純物領域と並列に配置されており、メモリセルサイズを低減するのが困難となるという問題が生じる。

#### 【0011】

また、この特許文献2は、消去ゲート領域およびプログラムゲート領域をワード線と同

50

一方向に延在させて、ページ単位で消去を行なうことを開示しているものの、ページ単位での消去モード時、他のページまたは他ブロックでデータアクセスを行なう構成については何ら考察していない。

#### 【0012】

それゆえ、この発明の目的は、メモリセルサイズを増大させることなく、消去動作時にデータアクセスを消去動作に悪影響を及ぼすことなく実行することのできる半導体装置およびメモリセル構造を提供することである。

#### 【0013】

この発明の他の目的は、シングルバンク構成においても、BGOモードまたはサスペンドモードでデータアクセスを行なうことのできる半導体装置およびメモリセル構造を提供することである。

10

#### 【課題を解決するための手段】

#### 【0014】

この発明に係る半導体装置の一実施の形態においては、複数のメモリセルを有する。各メモリセルは、基板領域上に形成されるフローティングゲートと、このフローティングゲート上に配置されるメモリゲートとを有するメモリトランジスタと、フローティングゲートおよびメモリゲートに隣接して配置されるアシストゲートを有し、メモリトランジスタと直列に接続されるアシストゲートトランジスタと、基板領域表面に形成される埋込消去ゲートとを有する。メモリセルは、フローティングゲートの蓄積電荷量に応じて不揮発性データを記憶する。

20

#### 【0015】

この発明に係る半導体装置は、一実施形態においてさらに、各メモリセル行に対応して配置され、各々が対応の行のメモリセルのメモリゲートに結合される複数のメモリゲート線と、各メモリセル行に対して配置され、各々が対応の行のメモリセルのアシストゲートに結合される複数のアシストゲート線と、各メモリセル列に対応して基板領域表面に配置され、各々が対応の列の埋込消去ゲートに結合される埋込消去ゲート配線と、メモリセル列に対応して配置され、各々が対応の列のメモリセルのメモリトランジスタの第1導通ノードに結合される複数のソース線と、各メモリセル列に対応して配置され、各々が対応の列のメモリセルのアシストゲートトランジスタの第2の不純物領域に結合される複数のビット線と、動作モード指示とアドレス信号とに従って指定されたメモリセルに対して指定された動作を行なうための制御信号を生成する制御回路とを備える。この制御回路は、消去動作が指定されたとき、選択メモリセルに対するソース線、メモリゲート線および埋込消去ゲート配線に各々供給される電圧を指定するとともに消去動作を制御する消去制御部と、選択メモリセルに対するアシストゲート線およびビット線に対して供給される読出に必要な電圧を指定するとともに読出動作を制御する読出制御部とを含む。

30

#### 【0016】

この一実施の形態において、半導体装置は、さらに、消去制御部および読出制御部から指定された電圧を発生する電圧発生回路と、電圧発生回路からの消去電圧を選択皿たメモリセルの埋込消去ゲート配線に伝達する消去回路と、電圧発生回路からの読出電圧を選択メモリセルへ供給して該選択メモリセルの記憶データを読出ス読出回路を備える。読出回路は、消去回路の消去電圧印加中に記憶データの読出を行なうように動作制御される。

40

#### 【0017】

この発明に係る半導体装置は、別の実施の形態においては、メモリアレイと、消去制御回路と、データアクセス制御回路とを含む。メモリアレイは、行列状に配列され、各々が少なくともデータを記憶する電荷蓄積層と、データを消去する消去ゲートを少なくとも備える複数の不揮発性メモリセルを有し、また複数のブロックに分割される。

#### 【0018】

消去制御回路は、複数のブロックに対して共通に設けられ、メモリアレイの選択ブロックに対して消去電圧を少なくとも消去ゲートに印加して選択ブロックの不揮発性メモリセルの記憶データの消去を行なう動作を制御する。

50

## 【0019】

データアクセス制御回路は、複数のブロックに対して共通に設けられ、選択ブロックへの消去電圧印加期間中に、この選択ブロックと異なるブロックの不揮発性メモリセルに対してデータアクセスを行なう動作を制御する。

## 【0020】

この発明に係る半導体装置は、さらに別の実施の形態においては、複数の不揮発性メモリセルを有するメモリアレイを有する。各不揮発性メモリセルは、単層選択ゲートを有し選択信号に応答して選択的に導通する選択トランジスタと、この選択トランジスタと直列に接続され、電荷を蓄積するフローティング状態の電荷蓄積層と、ソース線に結合される第1の不純物領域とを有する単層ゲート構造のメモリトランジスタと、メモリセル境界領域に配置され、隣接メモリセルを分離する分離膜表面に形成され、消去動作時、電荷蓄積層との間で電荷を移動させる消去ゲートとを備える。10

## 【0021】

この半導体装置はさらに、各メモリセル行に対応して配置され、各々に対応の行の不揮発性メモリセルの選択ゲートが接続される複数のワード線と、各メモリセル列に対応して配置され、各々に対応の列のメモリセルの選択トランジスタの第2の不純物領域が接続される複数のビット線を備える。

## 【0022】

この発明に係る半導体装置は、さらに他の実施の形態において、複数の不揮発性メモリセルを有するメモリアレイを含む。この不揮発性メモリセルは、互いに積層されるとともに、電気的に短絡される第1および第2の選択ゲート層を有し、選択信号に応答して選択的に導通する選択トランジスタと、この選択トランジスタと直列に接続され、電荷を蓄積するフローティング状態の電荷蓄積層と、この電荷蓄積層上に形成され、電荷蓄積層への電荷の移動を制御する制御機能を有する積層ゲート構造のメモリトランジスタと、メモリセル境界領域において隣接メモリセルを分離する絶縁膜上に形成され、消去動作時、電荷蓄積層との間で電荷を移動させる消去ゲートとを備える。20

## 【0023】

この半導体装置は、さらに、各メモリセル行に対応して配置され、各々が対応の行のメモリセルの選択トランジスタの選択ゲートに接続される複数のワード線と、各メモリセル列に対応して配置され、各々が対応の列のメモリセルの選択トランジスタの不純物領域に接続される複数のビット線とを備える。30

## 【発明の効果】

## 【0024】

不揮発性メモリセルにおいて消去ゲートを設け、この消去ゲートと電荷蓄積層との間で電荷を移動させる。この消去電圧印加と並行して、データの読出／書込を行なう。したがって、シングルバンク構成においても、消去動作のバックグラウンドでデータアクセスを行なうことができ、アクセス効率が改善される。

## 【0025】

また、メモリセル構造としては、セル間の素子分離領域上に消去ゲートを配置することにより、メモリセルのレイアウト面積の増大は抑制される。40

## 【図面の簡単な説明】

## 【0026】

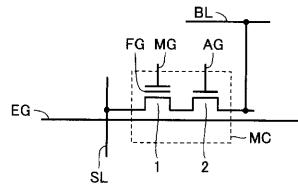

【図1】この発明の実施の形態1に従う半導体装置のメモリセルの典型的等価回路を示す図である。

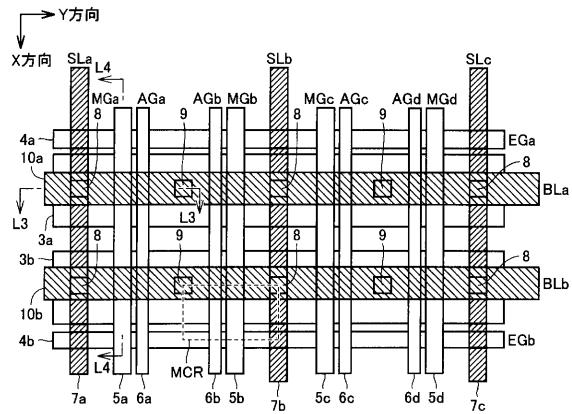

【図2】この発明の実施の形態1に従う半導体装置のメモリセルの平面レイアウトを概略的に示す図である。

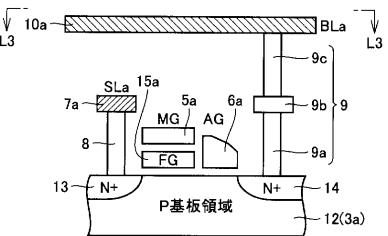

【図3】図2に示す線L3-L3に沿った断面構造を概略的に示す図である。

【図4】図2に示す線L4-L4に沿った断面構造を概略的に示す図である。

【図5】図1に示すメモリセルの各動作モードにおける印加電圧を一覧にして示す図である。

10

20

30

40

50

【図 6】図 1 に示すメモリセルの書き込み時の印加電圧および電子の流れを模式的に示す図である。

【図 7】図 1 に示すメモリセルの消去時の印加電圧および電子の流れを示す図である。

【図 8】図 1 に示すメモリセルのデータ読み出時の印加電圧および電流の流れを示す図である。

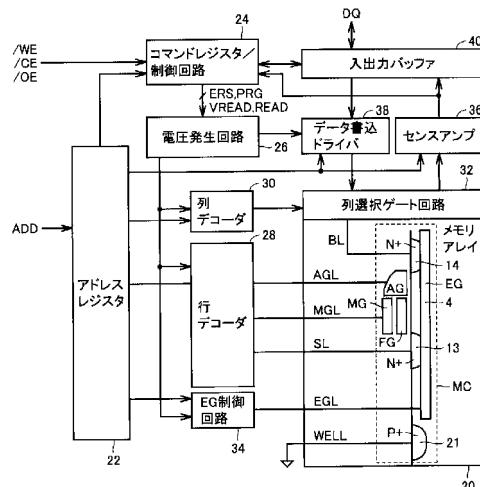

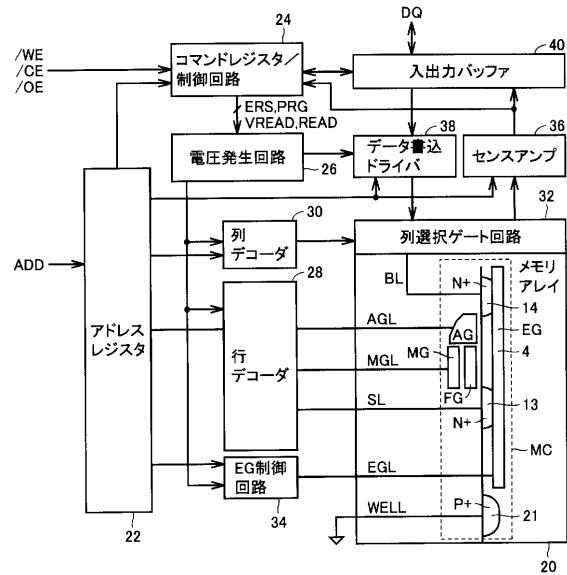

【図 9】この発明の実施の形態 1 に従う半導体装置の全体の構成を概略的に示す図である。

【図 10】この発明の実施の形態 1 に従う半導体装置の消去時の動作を示すフロー図である。

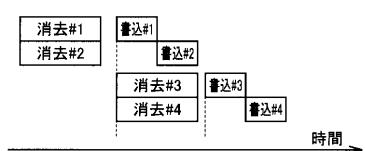

【図 11】図 10 に示す消去時の動作を示すタイミング図である。

【図 12】この発明の実施の形態 1 に従う半導体装置の消去動作に関連する部分の構成を概略的に示す図である。

【図 13】図 1 に示すメモリセルの消去および書き込み状態時の電流特性を示す図である。

【図 14】この発明の実施の形態 2 に従う半導体装置の全体の構成を概略的に示す図である。

【図 15】図 14 に示す列選択ゲート回路の構成を概略的に示す図である。

【図 16】図 14 に示す半導体装置の消去時の動作を示すタイミング図である。

【図 17】この発明の実施の形態 2 に従う半導体装置の変更例のアレイ構成を概略的に示す図である。

【図 18】この発明の実施の形態 2 に従う半導体装置のコマンドレジスタ / 制御回路の構成を概略的に示す図である。

【図 19】図 14 に示す行デコーダ、列デコーダおよび E G 制御回路の構成を概略的に示す図である。

【図 20】消去および読み出時のフローティングゲートの寄生容量の分布を概略的に示す図である。

【図 21】この発明の実施の形態 3 のデータ読み出および消去シーケンスを示すタイミング図である。

【図 22】この発明の実施の形態 3 に従う半導体装置のコマンドレジスタ / 制御回路の構成を概略的に示す図である。

【図 23】この発明の実施の形態 4 に従う半導体装置の全体の構成を概略的に示す図である。

【図 24】図 23 に示すメモリアレイの構成をより具体的に示す図である。

【図 25】この発明の実施の形態 4 に従う半導体装置における各メモリブロックの印加電圧を概略的に示す図である。

【図 26】この発明の実施の形態 4 に従う半導体装置の消去およびデータアクセス動作を説明するタイミング図である。

【図 27】この発明の実施の形態 4 に従う半導体装置の書き込みおよび読み出動作シーケンスを示す図である。

【図 28】図 23 に示すコマンドレジスタ / 制御回路の構成を概略的に示す図である。

【図 29】図 23 に示す E G 制御回路の構成を概略的に示す図である。

【図 30】この発明の実施の形態 5 に従う半導体装置の全体の構成を概略的に示す図である。

【図 31】図 30 に示す半導体装置の消去時の動作シーケンスを示す図である。

【図 32】図 30 に示す半導体装置の消去および書き込み動作様式を示す図である。

【図 33】図 30 に示すコマンドレジスタ / 制御回路の構成を概略的に示す図である。

【図 34】この発明の実施の形態 6 に従う半導体装置の消去および読み出動作シーケンスを示す図である。

【図 35】この発明の実施の形態 6 に従う半導体装置のコマンドレジスタ / 制御回路の構成を概略的に示す図である。

【図 36】この発明の実施の形態 7 に従う半導体装置の全体の構成を概略的に示す図であ

10

20

30

40

50

る。

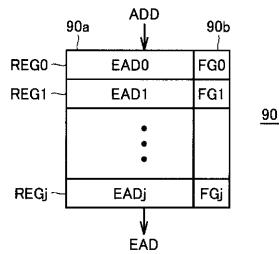

【図37】図36に示す消去アドレスレジスタファイルの構成を概略的に示す図である。

【図38】図36に示す半導体装置の消去対象のメモリブロックを示す図である。

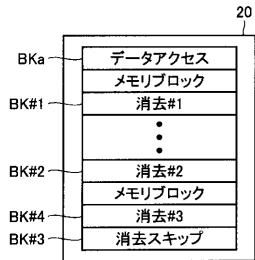

【図39】図36に示す半導体装置の消去および読出動作シーケンスを示す図である。

【図40】図36に示すコマンドレジスタ／制御回路の構成を概略的に示す図である。

【図41】図40に示すコマンドレジスタ／制御回路のレジスタファイル制御動作を示すフロー図である。

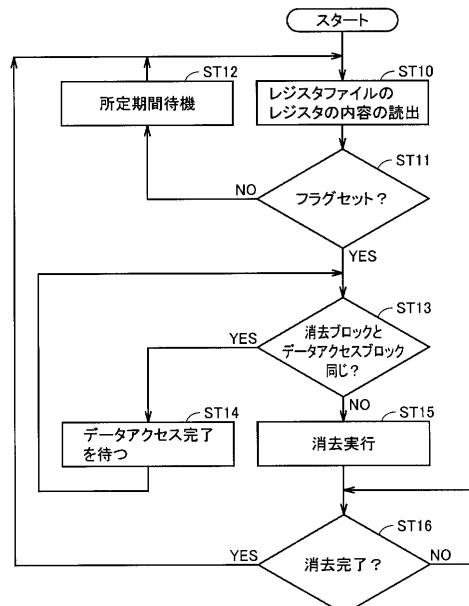

【図42】図40に示すコマンドレジスタ／制御回路の消去動作を示すフロー図である。

【図43】図40に示すコマンドレジスタ／制御回路の電源遮断時の動作制御を示すフロー図である。

【図44】この発明の実施の形態8に従う半導体装置の要部の構成を概略的に示す図である。

【図45】この発明の実施の形態8に従う半導体装置のEG制御回路の構成を概略的に示す図である。

【図46】この発明の実施の形態8に従う半導体装置のレジスタ制御様式を示す図である。

【図47】この発明の実施の形態8に従う半導体装置の動作シーケンスを示す図である。

【図48】この発明の実施の形態8に従う半導体装置の消去時の動作を示すフロー図である。

【図49】この発明の実施の形態9に従う半導体装置のメモリアレイの構成を概略的に示す図である。

【図50】この発明の実施の形態9に従う半導体装置の書き込みおよび消去動作シーケンスを示す図である。

【図51】この発明の実施の形態9に従う半導体装置のコマンドレジスタ／制御回路の構成を概略的に示す図である。

【図52】この発明の実施の形態9に従う半導体装置の制御時の動作シーケンスを示す図である。

【図53】この発明の実施の形態9に従う半導体装置の消去時の動作シーケンスの変更例を示す図である。

【図54】この発明の実施の形態10に従う半導体装置のメモリアレイのブロック構成を概略的に示す図である。

【図55】図54に示すメモリブロックへのアクセスシーケンスを示す図である。

【図56】この発明の実施の形態10に従う半導体装置の全体の構成を概略的に示す図である。

【図57】図56に示す半導体装置のコマンドレジスタ／制御回路およびクロックアドレス変換器の構成を概略的に示す図である。

【図58】図56に示す半導体装置の動作を示すフロー図である。

【図59】この発明の実施の形態11に従う半導体装置の全体の構成を概略的に示す図である。

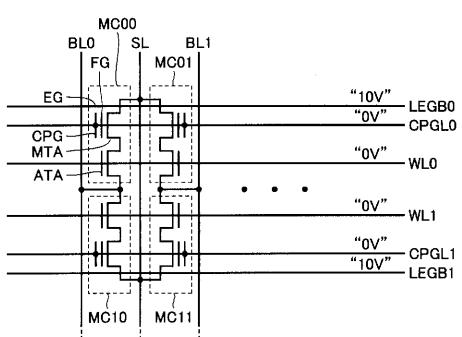

【図60】図59に示す半導体装置のメモリアレイのメモリセルの配置を示す図である。

【図61】図60に示すメモリセルの平面レイアウトを概略的に示す図である。

【図62】図62に示す線L62-L62に沿った断面構造を概略的に示す図である。

【図63】図61に示す線L63-L63に沿った断面構造を概略的に示す図である。

【図64】図60に示すメモリアレイへのデータ書き込み時の印加電圧を示す図である。

【図65】図62に示すメモリアレイへの消去時の印加電圧を示す図である。

【図66】図62に示すメモリアレイへの読出時の印加電圧を示す図である。

【図67】この発明の実施の形態12に従う半導体装置の全体の構成を概略的に示す図である。

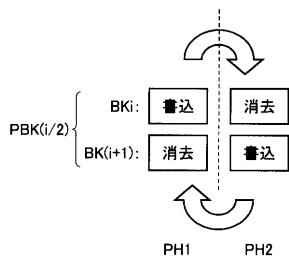

【図68】図67に示す半導体装置のメモリアレイの構成を概略的に示す図である。

【図69】図68に示すメモリセルの平面レイアウトを概略的に示す図である。

10

20

30

40

50

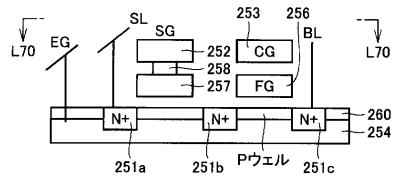

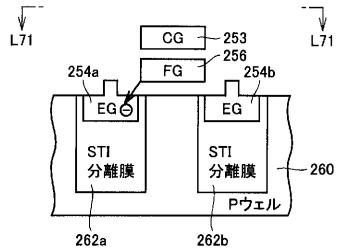

【図 7 0】図 6 9 に示す線 L 7 0 - L 7 0 に沿った断面構造を概略的に示す図である。

【図 7 1】図 6 9 に示す線 L 7 1 - L 7 1 に沿った断面構造を概略的に示す図である。

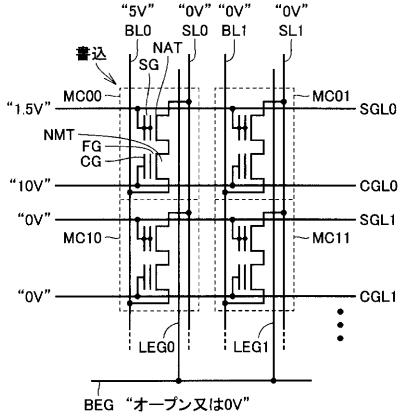

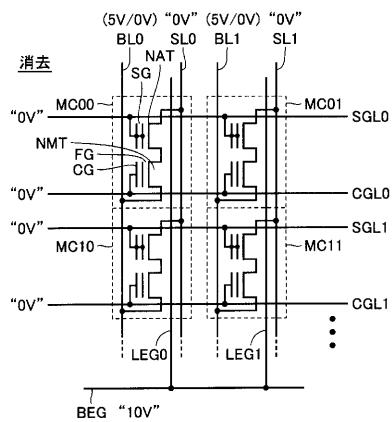

【図 7 2】図 6 8 に示すメモリアレイの書き時の印加電圧を示す図である。

【図 7 3】図 6 8 に示すメモリアレイの消去時の印加電圧の一例を示す図である。

【図 7 4】図 6 8 に示すメモリアレイの読み出時の印加電圧の一例を示す図である。

【図 7 5】この発明の実施の形態 13 に従う半導体装置の全体の構成を概略的に示す図である。

【図 7 6】この発明の実施の形態 13 に従う半導体装置のメモリセルの平面レイアウトを概略的に示す図である。

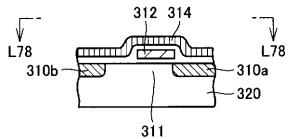

【図 7 7】図 7 6 に示す線 L 7 7 - L 7 7 に沿った断面構造を概略的に示す図である。

【図 7 8】図 7 6 に示す線 L 7 8 - L 7 8 に沿った断面構造を概略的に示す図である。

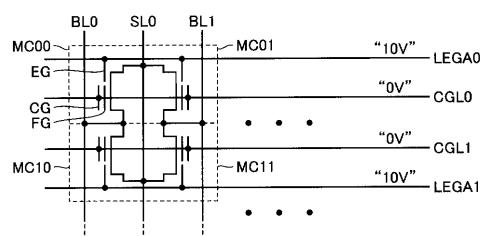

【図 7 9】図 7 5 に示すメモリアレイのメモリセルの配置の一例を示す図である。

【図 8 0】この発明の実施の形態 13 の変更例のメモリセルの断面構造を概略的に示す図である。

【図 8 1】図 8 0 に示すメモリセルのアレイ部の配置の一例を示す図である。

【発明を実施するための形態】

【0 0 2 7】

#### [実施の形態 1]

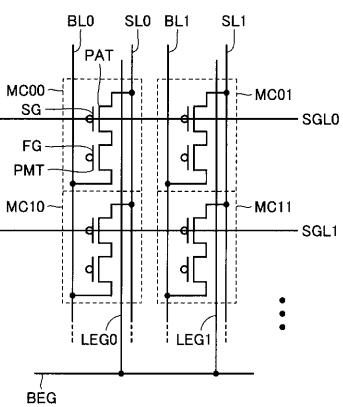

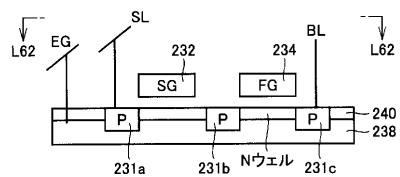

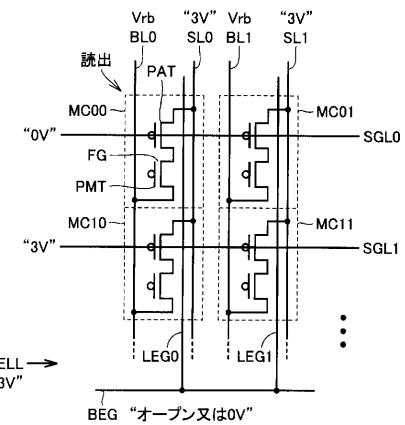

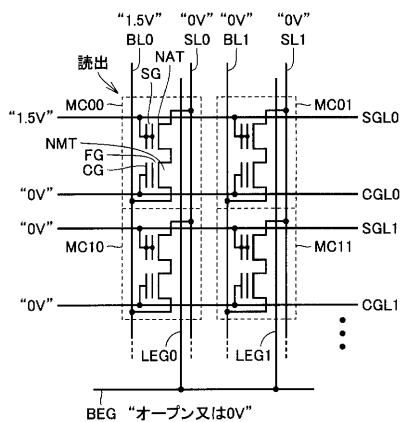

図 1 は、この発明の実施の形態 1 において用いられる半導体装置のメモリセルの電気的等価回路を概略的に示す図である。図 1 において、メモリセル MC は、フローティングゲート FG を有するメモリトランジスタ 1 と、メモリトランジスタ 1 と直列に接続されるアシストゲートトランジスタ（選択トランジスタ）2 を含む。メモリトランジスタ 1 は、フローティングゲート FG とその上層に形成されるメモリゲート MG との積層ゲート構造を有する N チャネル MOS トランジスタ（絶縁ゲート型電界効果トランジスタ）であり、そのソース不純物領域がソース線 SL に結合される。アシストゲートトランジスタ 2 は、アシストゲート AG を有する単層ゲート構造の N チャネル MOS トランジスタであり、ビット線 BL にその不純物領域が接続される。これらのアシストゲートトランジスタ 2 およびメモリゲートトランジスタ 1 の間には不純物領域は形成されない。

【0 0 2 8】

メモリセル MC は、さらに消去ゲート EG を有する。この消去ゲート EG は、メモリセルを分離する素子分離領域（STI（シャロー・トレーナ・アイソレーション）膜）表面に、列方向（ビット線延在方向）に沿って連続的に延在するように形成される。この消去ゲート EG とフローティングゲート FG の間で電荷を移動させ、フローティングゲート FG から電子を消去ゲート線 EG に引抜くことにより、消去動作を行なう。このメモリセル MC の境界領域にビット線 BL と平行に消去ゲート EG を埋込配線で配設することにより、メモリセル MC のレイアウト面積の増大を抑制する。

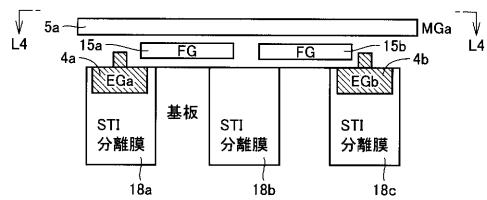

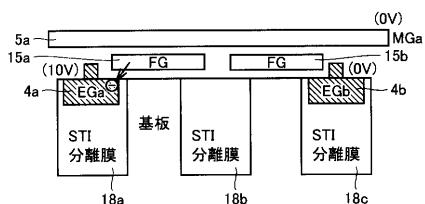

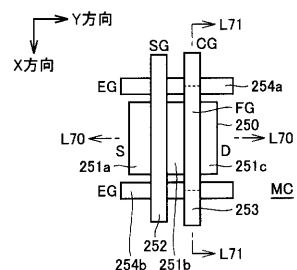

【0 0 2 9】

図 2 は、メモリセルの平面レイアウトを概略的に示す図である。図 2 において、Y 方向（列方向）に沿って互いに間をおいてかつ各々 Y 方向に沿って連続的に延在するように活性領域 3 a および 3 b が配置される。活性領域 3 a および 3 b 各々においては、図 1 に示すメモリトランジスタ 1 およびアクセストランジスタ 2 が形成される。

【0 0 3 0】

活性領域 3 a および 3 b と直交する方向に、すなわち X 方向（行方向）に連続的に延在してメモリゲート配線 5 a - 5 d およびアシストゲート配線 6 a - 6 d がそれぞれ隣接して配置される。メモリゲート配線 5 a - 5 d がメモリゲート MG a - MG d を構成し、アシストゲート配線 6 a - 6 d がアシストゲート AG a - AG d を構成する。

【0 0 3 1】

メモリゲート配線 5 a - 5 d の間に、ソース線 SL a - SL c をそれぞれ形成するメタル配線 7 a - 7 c が X 方向に連続的に延在してかつ互いに間をおいて配置される。ソースメタル配線 7 a - 7 c は、それぞれソースコンタクト 8 により、下層の活性領域に形成さ

10

20

30

40

50

れる不純物領域に電気的に接続される。

【0032】

活性領域3aおよび3b上にY方向に連続的に延在してビット線BLaおよびBLbをそれぞれ形成するメタル配線10aおよび10bがそれぞれ配設される。このビット線メタル配線10aおよび10bはそれぞれ、アシストゲートを構成するゲート配線6aおよび6bの間のビット線コンタクト9を介して活性領域3aおよび3bに形成される不純物領域に接続される。

【0033】

また、活性領域3aおよび3bの間の素子分離領域には、後に説明するようにシャロー・トレンチ・アイソレーション膜が形成されており、このシャロー・トレンチ・アイソレーション膜上に、埋込消去ゲート配線層4aおよび4bがY方向に沿って連続的に延在して形成され、それぞれ消去ゲートEGaおよびEGbとして用いられる。活性領域3aおよび3bの間には、埋込消去ゲート配線層は設けられていない。2行のメモリセルに共通に消去ゲート線が共有される。

10

【0034】

図2に示す平面レイアウトにおいて、図2において破線ブロックで示すメモリセル領域MCRは、ビット線コンタクト9、アシストゲートAG、メモリゲートMG、ソース線コンタクト8および消去ゲートEGを含む。Y方向において隣接するメモリセルにおいてビット線コンタクト9およびソース線コンタクト8が共有され、メモリセルレイアウト面積を低減する。また、2行に配設されるメモリセルに共通に消去ゲート線を設けることにより、最小消去単位を2行のメモリセルに設定することができる。

20

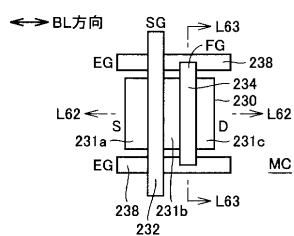

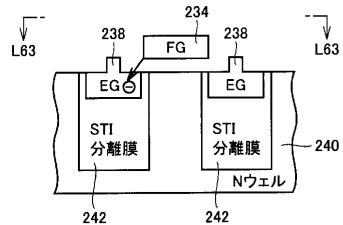

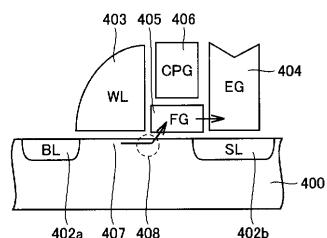

【0035】

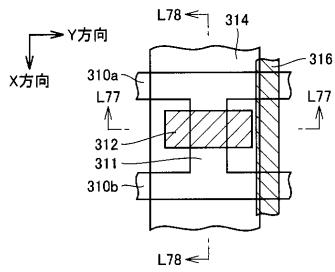

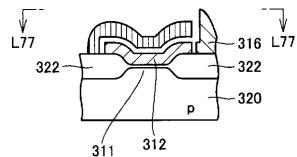

図3は、図2に示す線L3-L3に沿った断面構造を概略的に示す図である。図3において、P型半導体基板領域12表面に、互いに間をおいてN型不純物領域13および14が形成される。このP型半導体基板領域12は、図2に示す活性領域3aに対応する。

20

【0036】

不純物領域13は、ソース線コンタクト8を介してソース線SLaを形成するメタル配線7aに電気的に接続される。一方、不純物領域14は、ビット線コンタクト9を介してビット線BLaを形成するメタル配線10aに電気的に接続される。ビット線コンタクト9は、プラグ9aおよび9cと、これらのプラグ9aおよび9cの間の中間配線9bを含む。

30

【0037】

不純物領域13および14の間の基板領域上に、フローティングゲートFGを構成する電荷蓄積層15とメモリゲートMGを形成するゲート配線5aが互いに整列してかつ積層して配置される。フローティングゲートFGおよびメモリゲートMGに隣接してアシストゲートAGを形成するゲート配線6aが配置される。アシストゲートAGは単に、下層の基板領域12表面に選択的にチャネルを形成する。

【0038】

図4は、図2に示す線L4-L4に沿った断面構造を概略的に示す図である。線L4-L4に沿った領域においては、メモリゲートMGaが、メタルゲート配線5aにより形成されており、その下部の基板領域表面には、チャネル領域が存在し、不純物領域は設けられていない。各活性領域(3a、3b)は、STI(シャロー・トレンチ・アイソレーション)分離膜18a、18bおよび18cにより互いに分離される。

40

【0039】

活性領域(明確に示さず；正確にはメモリトランジスタのチャネル形成領域)表面上にフローティングゲートFGを構成する電荷蓄積層15aおよび15bが配置される。STI分離膜18aおよび18c表面に、上部に突出部を有する埋込配線層4aおよび4bが形成され、フローティングゲートを構成する電荷蓄積層15aおよび15bに、この突出部が隣接する。図4においては、中央のSTI分離膜18bにおいては、消去ゲートEGを構成する埋込配線層は形成されないが、形成されていてもよい。

50

### 【0040】

図5は、各動作モード時におけるメモリゲートMG、ソース線SL、アシストゲートAGおよびビット線BL、および、消去ゲートEGへの各動作モード時の印加電圧を一覧にして示す図である。以下、図5に示す印加電圧を参照して、各動作モードについて説明する。

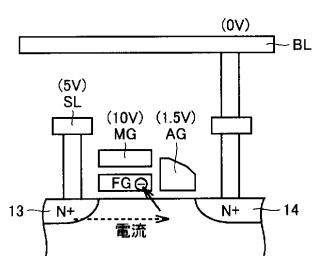

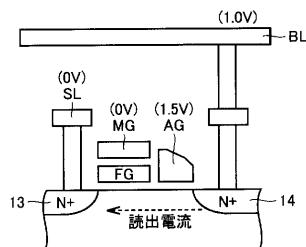

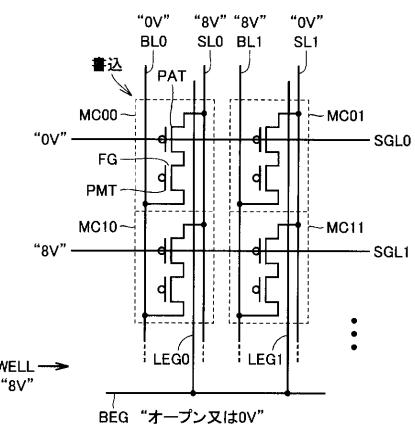

### 【0041】

図6は、メモリセルMCへのデータ書込時の選択メモリセルへの印加電圧を示す図である。この場合、図5に示すように、選択メモリセルMCのメモリゲートMGへ10Vが印加され、ソース線SLには5Vが印加される。アシストゲートAGには1.5Vが印加され、ビット線BLは、0Vに設定される。図6においては示さない埋込消去ゲートEGはオープン状態または接地電圧(0V)に設定される。10

### 【0042】

この状態においては、アシストゲートAGには1.5V程度の低い電圧が印加され、その下層の基板表面に比較的高抵抗のチャネルを形成する。ソース線SLから不純物領域13および14を介してビット線BLに電流が流れる。アシストゲートAG下部には、比較的高抵抗のチャネルが形成されており、この高抵抗のチャネル境界領域において高電界が発生し、この高電界により電子がエネルギーを得てホットエレクトロンとなる。メモリゲートMGの高電圧により、この生成された電子(ホットエレクトロン)がフローティングゲートFGに注入される。これにより、メモリトランジスタのしきい値電圧が高くなる。

### 【0043】

非選択メモリセルに対しては、メモリゲートMG、ソース線SL、アシストゲートAGは0Vに設定され、ビット線BLが1.5Vに設定される。非選択メモリゲートMGおよび非選択アシストゲートAGが0Vであり、チャネルは形成されず、電流は流れない。20

### 【0044】

ビット線BLを、非選択セルに対して1.5Vに設定するのは以下の理由による。すなわち、図2に示すように、アシストゲートAGを構成するアシストゲート配線とビット線BLとは直交する方向に配置される。したがって、選択行かつ非選択列のメモリセルにおいては、アシストゲートAGが選択状態の1.5Vである。ビット線BLを1.5Vに設定することにより、非選択メモリセルにおいてアシストゲートトランジスタのゲートおよびソース(アシストゲートAGおよび不純物領域14)の電位が等しくなり、チャネルは、アシストゲートAG下部に形成されず、不純物領域13および14間に電流は流れない。これにより、半選択状態のメモリセルに対するデータの書き込みを防止する。30

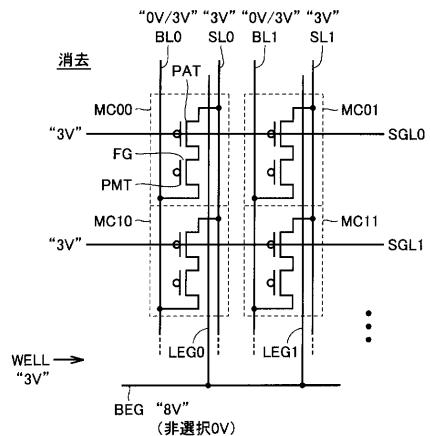

### 【0045】

図7は、消去時のメモリセルへの印加電圧をその断面構造とともに示す図である。図5および図7に示すように、消去時においては、選択メモリセルおよび非選択メモリセルに関わらず、メモリゲートMG、ソース線SLは接地電圧(0V)に設定され、アシストゲートAGおよびビット線BLは開放状態(オープン状態)に設定される。選択メモリセルに対して埋込消去ゲートEGaに10Vを印加し、非選択メモリセルの消去ゲートEGbには0Vを印加する。この場合、図7に示すように、電荷蓄積層15aと埋込消去ゲートEGaの間に大きな電界が印加され、フローティングゲート15aから埋込消去ゲート配線4aにファウラーノルドハイム電流により電子が流出し、電荷蓄積層15aの蓄積電荷量が低減し、メモリトランジスタのしきい値電圧が小さくなる。一方、埋込消去ゲートEGbには0Vが印加され、フローティングゲートFGb(電荷蓄積層15b)と埋込ゲートEGbの間には、高電界は印加されず、電荷の移動は生じない。40

### 【0046】

この消去動作において、基板領域に正の消去高電圧を印加してフローティングゲートFGから電子を基板領域へと放出する場合、ソースおよびドレイン不純物領域により、基板領域からの高電圧が、同様、印加され、フローティングゲートFGと基板領域の間の結合容量が大きくなり、効率的に電荷(電子)を引抜けない。一方、埋込消去ゲートEGを利用する場合、単にSTI分離膜18aおよび18c表面に形成される埋込消去ゲート配線

10

20

30

40

50

4 a および 4 b の基板領域上部の突出部と対応のフローティングゲート F G との間で電界が発生するだけであり、カップリングを小さくでき、低電圧で消去を行なうことができる。また、埋込消去ゲート E G は、S T I 分離膜 1 8 a および 1 8 c 表面に形成されており、基板領域、ソース線およびビット線には、消去時の高電圧は印加されず、消費電力を低減することができる。また、後に説明するように、埋込消去ゲートは、ビット線、ソース線およびメモリゲート線と分離されており、埋込消去ゲートに消去電圧を印加した状態で、メモリセルに対してデータアクセスを行なうことができる。

#### 【 0 0 4 7 】

図 8 は、メモリセルのデータ読出時の印加電圧および電流の流れる経路を概略的に示す図である。図 5 に示すように、メモリセルが選択セルの場合、ビット線 B L に読出電圧 1 . 0 V が印加され、アシストゲート A G に 1 . 5 V が印加される。メモリゲート M G およびソース線 S L は、0 V に設定される。通常の読出時においては、埋込消去ゲート E G はオープン状態または接地電圧 (0 V) に設定される。

10

#### 【 0 0 4 8 】

メモリセルのフローティングゲート F G が消去状態のときには、メモリトランジスタはデプレッション状態であり、下部にチャネルが形成され、ビット線 B L からソース線 S L に電流が流れる（アシストゲート A G 下部にはチャネルが形成されている）。

#### 【 0 0 4 9 】

一方、フローティングゲート F G が書込状態（プログラム状態）の場合、しきい値電圧は大きく、メモリトランジスタ（メモリゲート下部）の基板領域表面にはチャネルは、形成されない。この場合、ビット線 B L からソース線 S L へは、ほとんど電流が流れない。この消去状態を論理 “1” および書込状態を論理 “0” に対応付けると、ビット線 B L を流れる電流を図示しないセンスアンプで検出することにより、メモリセルの記憶データを検出することができる。

20

#### 【 0 0 5 0 】

非選択メモリセルにおいては、アシストゲート A G およびビット線 B L が 0 V に設定される。選択行かつ非選択列のメモリセルにおいても、ビット線 B L およびソース線 S L は同一電位であり、電流は流れず、データの読出は行なわれない。

#### 【 0 0 5 1 】

この埋込消去ゲートを用いて、フローティングゲートと埋込消去ゲートの間で電荷を移動させて消去を行なうメモリセルの構成の場合、書込電流は小さい（ソースサイド注入を行なっており、効率的に低消費電流（10 μA 程度）で書込を行なうことができる）。また、書込時に、電圧 5 V、10 V、消去時に 10 V の電圧が必要とされ、合計 2 種類の電源電圧を生成する電源回路が必要とされるだけである。また、消去および書込時の電流消費は小さく、消去および書込高電圧を生成する回路（チャージポンプ回路）のサイズを低減でき、応じて、レイアウト面積を低減することができる。

30

#### 【 0 0 5 2 】

本発明においては、この埋込消去ゲートを有するメモリセル構造を利用して、消去と並行して同一メモリブロック内でデータアクセスを行なう。

40

#### 【 0 0 5 3 】

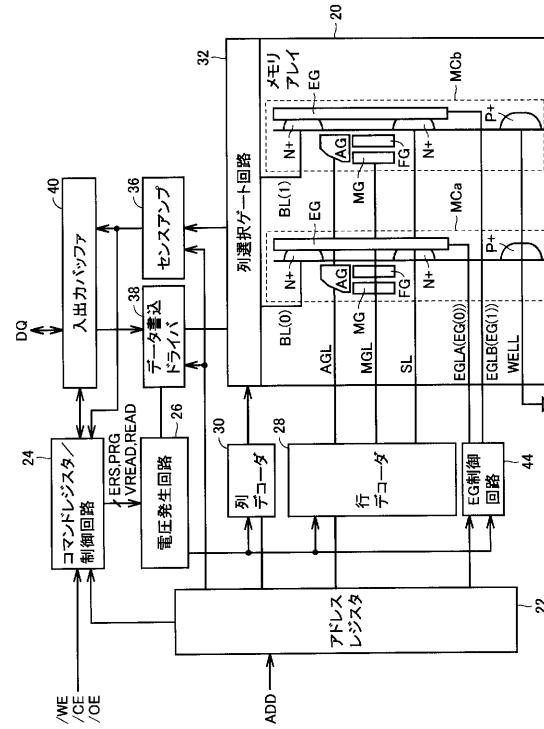

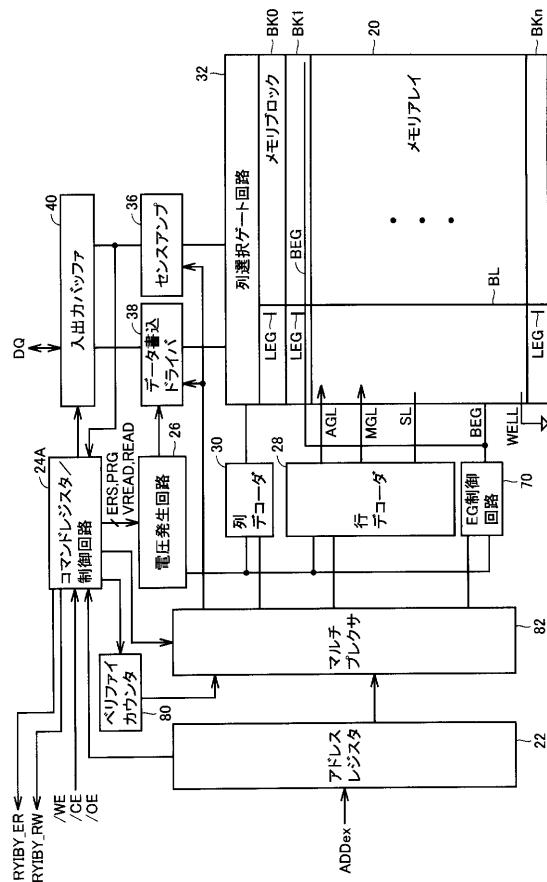

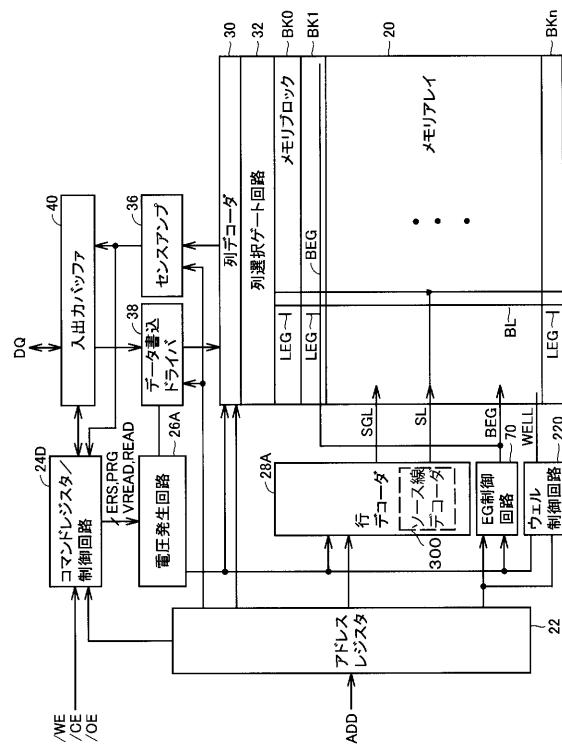

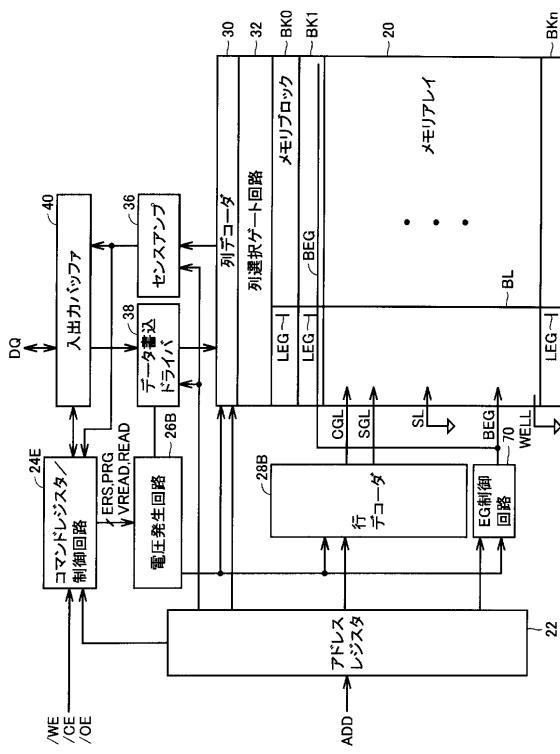

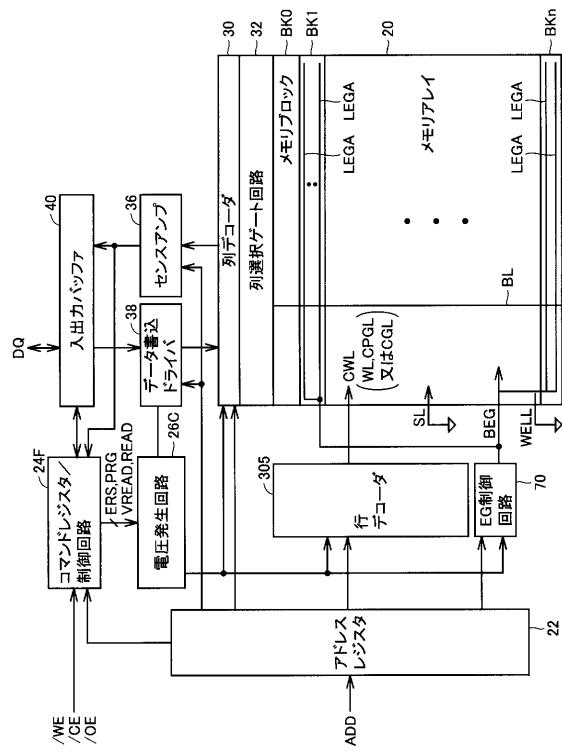

図 9 は、この発明の実施の形態 1 に従う半導体装置の全体の構成を概略的に示す図である。図 9 において、半導体装置は、メモリセル M C が行列状に配列されるメモリアレイ 2 0 を含む。この図 9 において、メモリアレイ 2 0 内において 1 つのメモリセル M C を代表的に示す。メモリセル M C は、ソース不純物領域 1 3 、ドレイン不純物領域 1 4 、埋込消去ゲート E G を構成する埋込消去ゲート配線 4 と、ウェル領域にウェル電圧 W E L L を印加する P 型不純物領域 2 1 を含む。このウェル電圧 W E L L は、図 9 に示す構成においては接地電圧レベルに固定される。

#### 【 0 0 5 4 】

このメモリセル M C の基板領域上に、アシストゲート A G 、フローティングゲート F G およびメモリゲート M G が形成される。1 行のメモリセルのアシストゲート A G はアシス

50

トゲート線 A G L に接続され、1行のメモリセルのメモリゲート M G がメモリゲート線 M G L に接続される。またソース線 S L が不純物領域 1 3 に接続される。このソース線 S L は、書込モード時に 5 V の電圧が印加されるため、その電圧レベルが後に説明する行デコーダ 2 8 により設定される。1列のメモリセルの不純物領域 1 4 に共通にピット線 B L が設けられる。

#### 【 0 0 5 5 】

この半導体装置は、さらに、外部からのアドレス ADD を受けるアドレスレジスタ 2 2 と、アドレスレジスタ 2 2 からのアドレスおよび外部からの制御信号 / W E 、 / C E および / O E を受けて、指定された動作モードを識別し、指定された動作に必要な動作制御を行なうコマンドレジスタ / 制御回路 2 4 と、コマンドレジスタ / 制御回路 2 4 からの動作モード指示に従って動作モードに応じた電圧を発生する電圧発生回路 2 6 を含む。

10

#### 【 0 0 5 6 】

制御信号 / W E は、ライトイネーブル信号であり、制御信号 / C E は、チップイネーブル信号でありこの半導体装置が選択されたことを示す。制御信号 / O E は出力イネーブルであり、データ読出タイミングを与える。通常、これらの制御信号 / W E および / C E の変化に応じて、動作モードを指定するコマンドおよびアクセス対象のメモリセルを指定するアドレスを取り込むタイミングが規定される。このコマンドは、アドレス入力ノードおよびデータ入力ノードを介して与えられる。

#### 【 0 0 5 7 】

電圧発生回路 2 6 は、消去モード時には消去動作に必要な電圧 (10 V) を生成し、書込モード時においては、5 V および 10 V および 1.5 V の電圧を生成する。読出時においては、アシストゲートへの電圧 1.5 V およびピット線 B L に印加される 1.0 V の電圧を生成する。

20

#### 【 0 0 5 8 】

半導体装置はさらに、行選択を行う行デコーダ 2 8 、列選択を行う列デコーダ 3 0 および列選択ゲート回路 3 2 と消去ゲート電圧を設定する E G 制御回路 3 4 とを含む。行デコーダ 2 8 は、アドレスレジスタ 2 2 からのアドレス信号に従ってメモリセルアレイ 2 4 の選択行に対応するアシストゲート線 A G L およびメモリゲート線 M G L へ、電圧発生回路 2 6 から与えられた電圧を伝達する。この行デコーダ 2 8 は、ソース線デコーダ 2 8 を含み、データ書込時選択列の書込対象のソース線に 5 V の書込電圧を伝達する。

30

#### 【 0 0 5 9 】

列デコーダ 3 0 は、アドレスレジスタ 2 2 からの列アドレス信号をデコードし、メモリアレイ 2 0 の列を対応するピット線を選択する列選択信号を生成するとともに、電圧発生回路 2 6 からの電圧レベルの列選択信号を生成する。列選択ゲート回路 3 2 は、列デコーダ 3 0 からの列選択信号に従って選択列のピット線を選択する。

#### 【 0 0 6 0 】

E G 制御回路 3 4 は、消去動作時、アドレスレジスタ 2 2 からのアドレス信号に従って消去対象の消去ゲート線 E G L へ、電圧発生回路 2 6 からの消去電圧を伝達する。

#### 【 0 0 6 1 】

この E G 制御回路 3 4 は、消去時、電圧発生回路 2 6 からの消去電圧を伝達された書込消去ゲート線 E G L 上に供給する。行デコーダ 2 8 および列デコーダ 3 0 は、E G 制御回路 3 4 からの消去高電圧印加期間中に、並行してメモリセル選択を行ない、消去ペリファイのためのメモリセルデータ読出を実行する。

40

#### 【 0 0 6 2 】

この半導体装置は、さらに、メモリセルのデータを読出すセンスアンプ 3 6 と、選択メモリセルにデータの書込を行なうデータ書込ドライバ 3 8 と、外部との間でデータ D Q を送受する入出力バッファ 4 0 を含む。データ書込ドライバ 3 8 およびセンスアンプ 3 6 へは、アドレスレジスタ 2 2 からのアドレスが与えられ、複数の列 (1 I / Oあたり) のうち 1 つの列を選択してデータの書込および読出を実行する。データ書込ドライバ 3 8 へは、また、電圧発生回路 2 6 からの書込電圧が与えられ、データ書込ドライバ 3 8 により、

50

ビット線書込電圧を選択列へ伝達する。

【0063】

データ書込ドライバ38により、“0”データの書込を行なう場合、ビット線BLの電圧が0Vに設定され、データ“0”が書込まれる。一方、データ“1”を格納する場合には、ビット線BLに1.5Vの電圧が印加され、選択メモリセルは、消去状態の低しきい値電圧状態に維持される。

【0064】

出入力バッファ40は、データ書込時には、外部からのデータDQから内部書込データを生成してデータ書込ドライバ38へ伝達し、データ読出時には、センスアンプ36からの内部読出データをバッファ処理して外部出力データDQを生成する。データ出力タイミングが制御信号/OEにより決定される。10

【0065】

このコマンドレジスタ／制御回路20および電圧発生回路26を用いて各動作モードに応じた内部電圧を生成するとともに、内部動作を制御する。コマンドレジスタ／制御回路24は、たとえばシーケンスコントローラで構成され、消去、書き込みおよび読出に必要な内部動作をシーケンスコントローラに設定されたシーケンスに従って順次制御する。

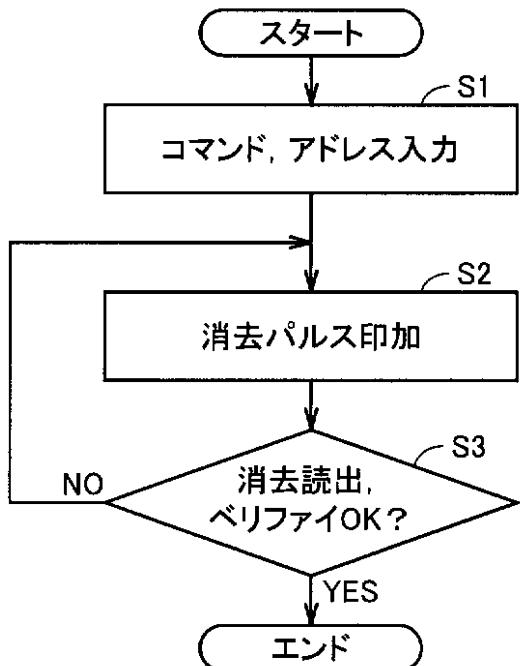

【0066】

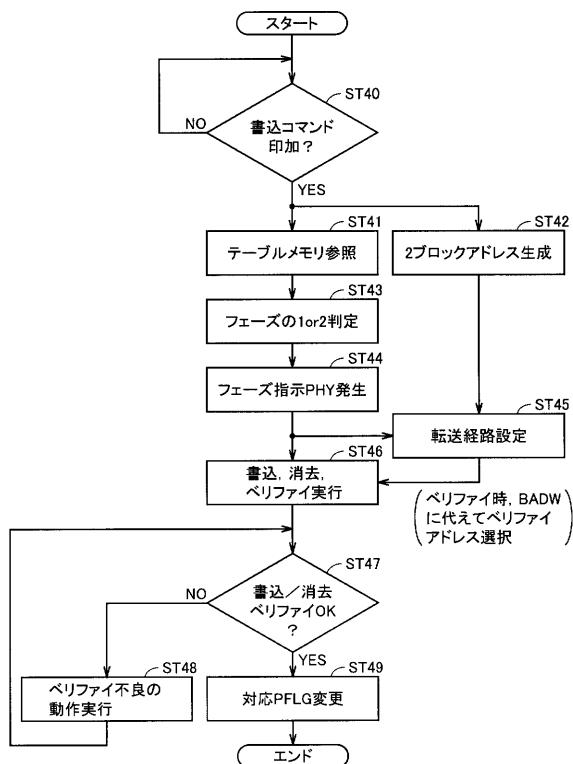

図10は、図9に示す半導体装置の消去時の動作を示すフロー図である。以下、図10を参照して、図9に示す半導体装置の消去動作について説明する。

【0067】

まず、外部から消去動作を指示するコマンドおよび消去対象のメモリセル領域を示すアドレスが与えられる(ステップS1)。このコマンドおよびアドレスに従って図9に示すコマンドレジスタ／制御回路24は、電圧発生回路26に、消去モード指示ERSを与え、電圧発生回路26に消去動作に必要な電圧を発生させる。20

【0068】

行デコーダ28は、消去モード時においては、アシストゲート線AGLおよびメモリゲート線MGLを、それぞれ、オープン状態(または0V)および0Vに設定する。列デコーダ30の出力信号は全て非選択状態であり、列選択ゲート回路32は、ビット線BLを全て、オープン状態に維持する。

【0069】

この状態で、選択されたメモリセルの消去ゲート線EGLに消去高電圧(消去パルス)を印加する(ステップS2)。すなわち、図9に示すEG制御回路34は、電圧発生回路26からの消去高電圧を、選択メモリセルに対して配置された埋込消去ゲート線EGLへ伝達する。30

【0070】

この消去パルスを印加した状態で、次いで消去対象のメモリセルのデータの読出を行い、メモリセルが消去状態、すなわち低しきい値電圧状態にあるかを識別する(ステップS3)。この消去ベリファイにおいて非消去状態のメモリセルが存在する場合、再びステップS2からの消去パルス印加ステップを実行する。一方、ステップS3において、消去対象のメモリセル全てが、消去状態と判定されると、消去動作が完了する。40

【0071】

通常、消去高電圧はたとえば10Vの電圧レベルである。この消去電圧は、電圧発生回路26においてチャージポンプ回路を用いて発生されるのが一般的である。したがって、消去高電圧の消去開始時の所定レベルへの立上げおよび消去停止時の所定レベルへの立下げに、数100μs程度の時間が必要である。この立下げ時間を利用してメモリセルデータの読出を行なって消去ベリファイを行なうことができ、消去時間を短くすることができる。特に、消去ゲート線EGLを選択状態のHレベルに維持した状態でも消去ベリファイを実行することができ、消去時間を短くすることができる。この場合、選択トランジスタ(アシストゲートAG)が存在するため、メモリトランジスタは、過消去状態(デプレッシュン状態)にあっても特に問題は生じず、消去パルス印加時にメモリセルのデータの読

10

20

30

40

50

出を行なって、通常よりも長い期間消去パルスが印加される状態が生じても特に問題は生じない。

#### 【0072】

なお、1回目の消去での消去ベリファイ時に、1ビットでも非消去状態のメモリセルが存在すると、消去対象のメモリセルに対して再度、2回目の消去パルス（消去高電圧）が印加される。

#### 【0073】

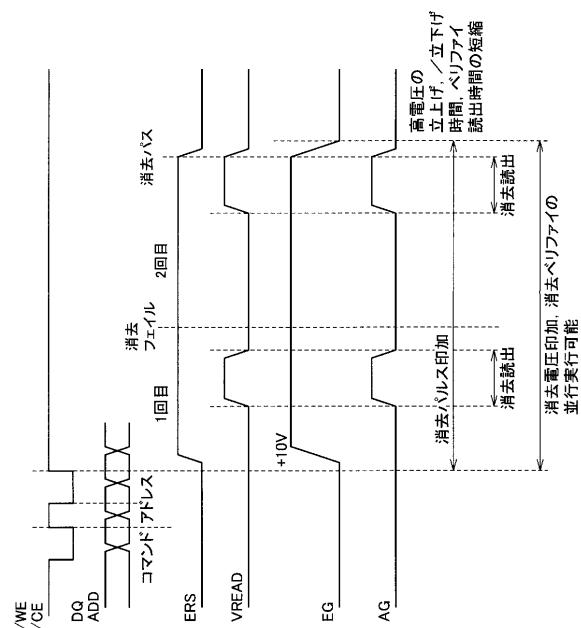

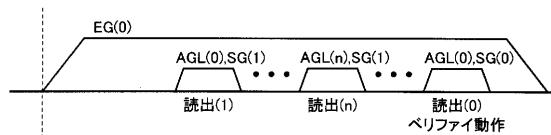

図11は、図10に示す消去動作を具体的に示すタイミング図である。以下、図11を参照して、図9に示す半導体装置の消去動作について説明する。

#### 【0074】

図11において、外部からの制御信号／WEおよび／CEをともに一旦立下げるから立上げると、データ端子DQおよびアドレス端子ADDから与えられた信号が、コマンドとして内部へ取込まれ、コマンドレジスタ／制御回路24により取込んだコマンドに従って動作モード（消去モード）の識別が行なわれる。

#### 【0075】

次に、制御信号／WEおよび／CEの立上がりから次の立下りに従って、アドレスADDがアドレスレジスタ22に取込まれて消去対象のメモリセルが指定される。この後、制御信号／WEおよび／CEをHレベルに立上げると、消去モードが開始される。すなわち、コマンドレジスタ／制御回路24は、制御信号／WEおよび／CEが2回立上げられると、コマンドにより指定された動作モードに入る。この場合、電圧発生回路26に消去モード指示ERSをイネーブルして与え、消去に必要な電圧（消去高電圧）を発生させる。消去モードにおいては、EG制御回路34により、消去対象として指定されたメモリセルの埋込消去ゲート線EGLへは、消去高電圧（+10V）の消去パルスが印加される。この消去パルスが印加され所定期間が経過すると、内部で消去ベリファイ読出を行なう。すなわち、所定時間経過後、所定の時間間隔で、消去ベリファイ読出指示VReadが、イネーブルされ、行デコーダ28および列デコーダ30および列選択ゲート回路32を用いて、埋込消去ゲート線EGLに消去電圧を与えた状態で、メモリゲート線MGLおよびビット線BLに読出電圧を供給する。ビット線電流に従って選択メモリセルのデータをセンスアンプ36で読出し、コマンドレジスタ／制御回路24において、読出したメモリセルが消去状態にあるかの識別を行なう。このベリファイ動作を、各メモリセルに対して順次実行する。

#### 【0076】

この1回目の消去に対するベリファイ（VR）により、消去不良（消去フェイル）と判断されると、引き続き、消去パルスを所定期間印加した後、再度消去ベリファイを実行する（消去高電圧を印加した状態で）この2回目の消去に対するベリファイにおいて全ビット消去完了と判定されると（消去パスと判定されると）、消去モードERSをディスエーブルし、EG制御回路34から消去ゲート線EGLへの消去高電圧の印加を停止する。この消去パルスの印加および消去ベリファイは、消去ベリファイにおいて消去パスと判定されるまで、繰返し実行される。

#### 【0077】

消去パルスの印加期間の間に、複数の消去対象のメモリセルの逐次ベリファイ読出を行なうことができる。したがって、この消去パルスが完全に接地電圧レベルに低下するまでの期間を待つ必要なく、ベリファイ動作を開始することができ、消去時間を短縮することができる。この場合、1回目の消去ベリファイ読出を行なうまでの期間として、消去に必要な時間が確保されればよい。消去ベリファイ時においては、少なくとも1ビットの未消去状態のメモリセルが存在する場合、消去対象のメモリセルに対し引き続き消去パルスを印加する。したがって、最初の消去ベリファイを消去パルス印加中に行なうメモリセルの消去パルス印加期間が仮に不十分であっても、消去ベリファイ期間において消去パルスが印加される。したがって、次の消去パルス印加後、この最初の消去ベリファイ時に未消去状態と識別されるメモリセルでも、確実に、消去状態に設定することは可能であり、全体と

して消去時間の増大は、十分に抑制することができる。

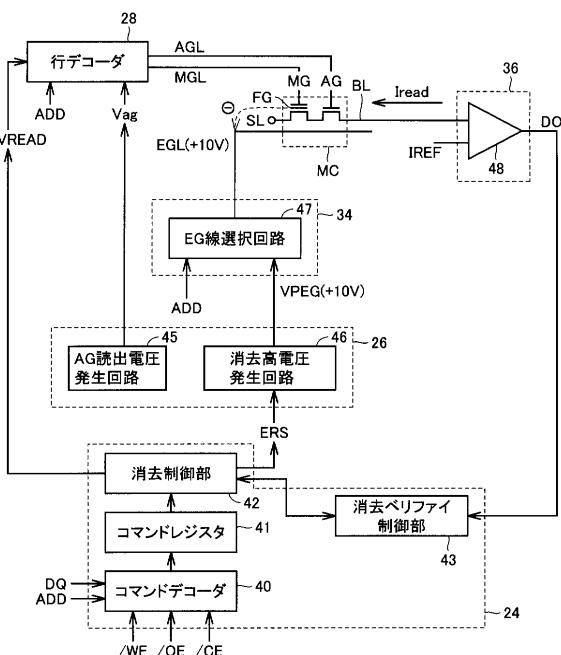

#### 【0078】

図12は、メモリセルMCの消去および消去ベリファイ読出に関連する部分の構成を概略的に示す図である。コマンドレジスタ／制御回路24は、コマンドをデコードするコマンドデコーダ40と、コマンドデコーダ40のデコードしたコマンドを格納するコマンドレジスタ41と、コマンドレジスタ41に格納される消去コマンドに従って消去動作を制御する消去制御部42と、消去ベリファイを行なう消去ベリファイブ43を含む。

#### 【0079】

コマンドデコーダ40は、外部からの制御信号／WEおよび／CEおよび／OEに従つて、アドレスADDおよびデータDQをコマンドとして受けてデコードする。

10

#### 【0080】

消去制御部42は、コマンドレジスタ41に格納された消去コマンドに従って消去指示ERSをイネーブルして消去動作モードを指示するとともに消去ベリファイ時には所定の間隔で消去読出指示VREADをアサート（活性化）し、消去動作および消去ベリファイ読出動作の制御および消去ベリファイ制御部43のベリファイ動作を制御する。この消去制御部42は、たとえば消去制御シーケンスコントローラで構成され、消去コマンドに従って所定のシーケンスで消去指示ERSおよび消去ベリファイ読出指示VREADを所定のタイミングでイネーブルする。

#### 【0081】

消去ベリファイ制御部43は、消去制御部42により動作制御され、センスアンプ36に含まれるセンスアンプ回路48からのベリファイ読出データDOを受け、このベリファイ読出データDOが消去状態を示す論理値であるかを判別する。

20

#### 【0082】

電圧発生回路26は、消去高電圧発生回路46と、AG読出電圧発生回路45とを含む。消去高電圧発生回路46は、消去制御部42からの消去動作指示ERSの活性化時（アサート時）、消去高電圧VPEG（+10V）を生成する。一方、消去読出および消去ベリファイおよび書込時において、1.5Vまたは0Vの電圧がアシストゲートAGに印加されるだけであり、AG読出電圧発生回路45は、たとえば1.5Vのアシストゲート電圧Vagを常時生成する。

#### 【0083】

EG制御回路34は、EG線選択回路47を含む。このEG線選択回路47は、消去動作時消去制御部42によりイネーブルされ、アドレス信号ADDに従って消去対象のメモリセルの埋込消去ゲート線EGLを選択し、該選択された埋込消去ゲート線EGLに、消去高電圧発生回路46からの消去高電圧VPEGを伝達する。

30

#### 【0084】

消去動作時、行デコーダ28は、消去ベリファイ読出指示VREADがアサートされると、アドレス信号ADDに従って消去対象のメモリセルに対して配置されるアシストゲート線AGLにアシストゲート電圧Vagを伝達する。このとき、メモリゲート線MGLは、0Vに設定される。行デコーダ28により選択された1行のメモリセルのうち、図9に示す列選択ゲート回路32が列デコーダ30からの列選択信号に従って選択メモリセルのビット線BLをセンスアンプ36に結合する。センスアンプ36は、センスアンプ回路48を含み、読出電流Ireadを選択列のビット線BLに伝達し、参照電流REFとの間で大小比較を行なってベリファイ読出データDOを生成し、消去ベリファイ制御部43へ与える。

40

#### 【0085】

消去ベリファイ制御部43は、センスアンプ36からの内部読出データDOが消去状態の論理値“1”であるかの判別を行い、消去不良ビットが存在すると、消去不良ビットの存在を消去制御部42に伝達する。全ビットが消去状態のときには、消去完了を消去制御部42に通知する。この消去ベリファイ制御部43からの消去結果通知に従って、消去動作の継続および完了（消去パルスの継続印加および印加停止）を実行する。

50

## 【0086】

消去ベリファイ動作時、消去高電圧を埋込消去ゲート線 E G L に与えた場合、メモリセル M C において、フローティングゲート F G と埋込消去ゲート線 E G L の間で電子が、ファウラーノルドハイム電流の形態で引抜かれる。このフローティングゲート F G および埋込消去ゲート線 E G L は、ソース線 S L、メモリゲート M G およびアシストゲート A G およびビット線 B L とすべて電気的に分離されている。したがって、この状態で、アシストゲート A G にベリファイ読出電圧 V a g を印加してビット線 B L とソース線 S L の間に、メモリセル M C の記憶データに応じた電流を流しても、何ら消去動作には影響を及ぼさず、正確にメモリセル M C のメモリトランジスタのしきい値電圧に応じた電流を流すことができる。

10

## 【0087】

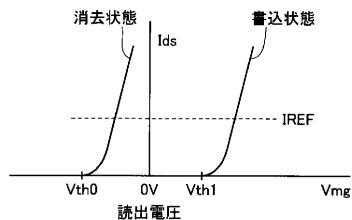

図 13 は、このメモリトランジスタのしきい値電圧とメモリセルを流れる電流の対応を概略的に示す図である。消去状態においては、メモリトランジスタはしきい値電圧 V t h 0 を有し、メモリゲート M G に印加される電圧 V m g が 0 V であっても、メモリトランジスタにはチャネルが形成される。一方、メモリトランジスタが書込状態のときには、このメモリトランジスタは、しきい値電圧 V t h 1 を有し、メモリゲート電圧 V m g が 0 V の場合、電流は流れない。直列に接続されるアシストゲート A G を選択することにより、メモリトランジスタのしきい値電圧の状態に応じた読出電流がビット線 B L ソース線 S L との間に流れ、センスアンプ 3 6において、ビット線電流と参照電流 I r e f との大小に応じて、消去状態および書込状態を識別することができる。

20

## 【0088】

また、消去状態においては、メモリトランジスタは、デプレッション状態にある。しかしながら、アシストゲートトランジスタ（選択トランジスタ）により、メモリセルの選択／非選択がデータ書込／読出時に行なわれるため、この消去状態、すなわちデプレッション状態にメモリトランジスタがあっても特に、問題は生じず、また、消去の制御が容易となる（デプレッション状態が許容されるため）。

20

## 【0089】

以上のように、この発明の実施の形態 1 に従えば、埋込消去ゲート線を用いて消去を行なっており、この消去ゲートは、ビット線、ソース線、ウェルおよびメモリゲートと分離されており、消去電圧印加と並行して消去ベリファイ読出を行なうことができる。これにより、消去に要する時間を短縮することができる。

30

## 【0090】

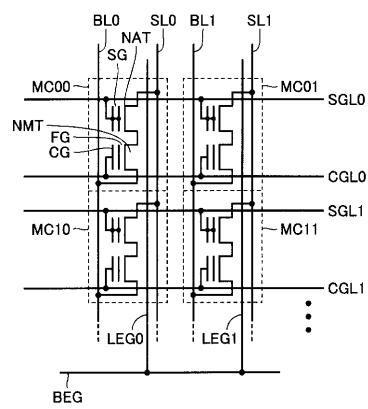

## [実施の形態 2]

図 14 は、この発明の実施の形態 2 に従う半導体装置の全体の構成を概略的に示す図である。図 14 に示す半導体装置は、以下の点で、図 9 に示す半導体装置とその構成が異なる。すなわち、メモリアレイ 2 0 において、複数の埋込消去ゲート線 E G L A および E G L B により、メモリアレイ 2 0 は複数の列ブロックに分割される。埋込消去ゲート線 E G L A ( E G ( 0 ) ) がメモリセル M C a の埋込消去ゲート E G に結合され、埋込消去ゲート線 E G L B ( E G ( 1 ) ) が、メモリセル M C b の埋込消去ゲート E G に結合される。メモリセル M C a および M C b は、それぞれビット線 B L ( 0 ) および B L ( 1 ) に結合される。

40

## 【0091】

メモリアレイ 2 0 は、単一バンク構造であり、ある行のメモリセルに対するデータアクセス（読出または書込）時、別の行のメモリセルに対して並行してデータアクセスはできない。

## 【0092】

E G 制御回路 4 4 は、埋込消去ゲート線単位で、メモリアレイ 2 0 における消去を実行する。ここで、メモリアレイ 2 0 が、列ブロックに分割されているのは、埋込消去ゲート線は、ビット線と平行に配設されているためである。したがって、消去対象のメモリセル M C a が消去実行状態のとき、この消去対象のメモリセル M C a と同一行のメモリセル M

50

C<sub>b</sub>は埋込消去ゲート線は非選択状態であり、一方、アシストゲート線A<sub>GL</sub>はオープン状態である。メモリゲート線M<sub>GL</sub>およびソース線S<sub>L</sub>は接地電圧レベルであり、ビット線B<sub>L</sub>(0)はフローティング状態である。このとき、アシストゲート線A<sub>GL</sub>を選択状態へ駆動して、この消去非対象のメモリセルMC<sub>b</sub>に対するデータの読出を実行する。この図14に示す半導体装置の他の構成は、図9に示す半導体装置の構成と同じであり、対応する部分には同一参照番号を付し、その詳細説明は省略する。

#### 【0093】

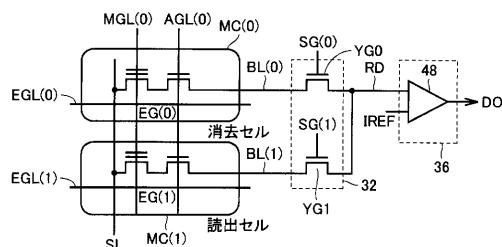

図15は、図14に示す列選択ゲート回路32の構成を、関連するメモリセルMC(0)およびMC(1)の接続様とともに示す図である。メモリセルMC(0)は、埋込消去ゲート線E<sub>GL</sub>(0)に接続される消去ゲートEG(0)を有し、メモリセルMC(1)は、埋込消去ゲート線E<sub>GL</sub>(1)に接続される消去ゲートEG(1)を有する。メモリセルMC(0)およびMC(1)に共通に、メモリゲート線M<sub>GL</sub>(0)およびアシストゲート線A<sub>GL</sub>(0)が設けられる。メモリセルMC(0)はビット線B<sub>L</sub>(0)を介して列選択ゲート回路32に含まれるY選択ゲートYG0に結合され、メモリセルMC(1)は、ビット線B<sub>L</sub>(1)を介してY選択ゲートYG1に結合される。これらのY選択ゲートYG0およびYG1は、それぞれ、列選択信号SG(0)およびSG(1)に応答して選択的に導通し、導通時、対応のビット線B<sub>L</sub>(0)およびB<sub>L</sub>(1)を内部読出データ線RDに結合する。この内部読出データ線RDはセンスアンプ36に含まれるセンスアンプ回路48に結合される。このセンスアンプ回路48は、図12に示すセンスアンプ回路48と同じであり、内部読出データ線RDを流れる電流と参照電流REFとを差動増幅して内部読出データDOを生成する。

10

20

30

#### 【0094】

今、図15においてメモリセルMC(0)が消去対象のメモリセルであり、メモリセルMC(1)が読出対象のメモリセルであるとする。ここで、読出対象のメモリセルは、外部からデータアクセスが要求されたメモリセルである。

#### 【0095】

図16は、図14および図15に示す半導体装置の消去動作および読出動作を並行して実行するときの動作タイミングを示す図である。以下、図16を参照して、図14および図15に示す半導体装置の消去時のデータ読出動作について説明する。

#### 【0096】

消去時においては、メモリゲート線M<sub>GL</sub>(0)およびアシストゲート線A<sub>GL</sub>(0)はともにオープン状態である。この状態で、埋込消去ゲート線E<sub>GL</sub>(0)に消去高電圧が印加され、消去対象のメモリセルMC(0)の埋込消去ゲートEG(0)の電圧レベルが10Vの高電圧レベルに設定されて、メモリセルMC(0)における消去が実行される。このとき、埋込消去ゲート線E<sub>GL</sub>(1)は非選択状態またはオープン状態の接地電圧レベルであり、メモリセルMC(1)に対しては何ら消去は行なわれない。消去電圧を埋込消去ゲートAG(0)に印加した状態で、埋込消去ゲート線E<sub>GL</sub>(1)に接続されるメモリセルMC(1)等のメモリセルの読出を実行する。

#### 【0097】

すなわち、アシストゲート線A<sub>GL</sub>(0)およびY選択信号SG(1)を選択状態に駆動し、メモリセルMC(1)のデータの読出を実行する。所定の間隔で、アシストゲート線A<sub>GL</sub>(i)を最終のアシストゲート線A<sub>GL</sub>(n)まで、順次選択する。このときまた、Y選択ゲートYG1を列選択信号SG(1)に従って選択状態に駆動する。これにより、埋込消去ゲート線E<sub>GL</sub>(1)に対応して配置されるメモリセルのデータを、順次読出ることができる。埋込消去ゲート線E<sub>GL</sub>(1)に対するメモリセルのデータの読出完了後、次いで、アシストゲート線A<sub>GL</sub>(0)を選択状態へ駆動するとともに、Y選択信号SG(0)を選択し、消去対象のメモリセルMC(0)、…のベリファイ読出を順次、消去高電圧を立ち下げる前に、開始する。

40

#### 【0098】

したがって、消去高電圧を印加した状態で、データアクセス（外部読出）を行なうこと

50

ができる、通常のフラッシュメモリのサスPENDモード動作のように、一旦、消去高電圧の印加を停止してビット線等の内部電圧が安定した後に外部からデータアクセスを行なう必要がない。これにより、高速のデータアクセスを行なうことができる、また、実施の形態1と同様、ベリファイと消去を並行して実行することが可能であり、消去に要する時間も短縮することができる。

#### 【0099】

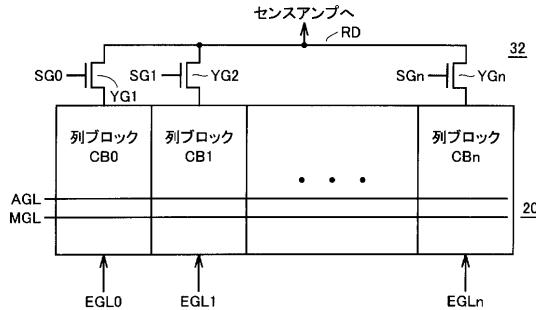

図17は、この発明の実施の形態2における半導体装置のメモリアレイ20の一般的構成を概略的に示す図である。図17においてメモリアレイ20は、複数の列ブロックCB0-CBnに分割される。これらの列ブロックCB0-CBnそれぞれに対応して埋込消去ゲート線EGL0、EGL1、…EGLnが設けられる。消去は、列ブロック単位で実行される。これらの列ブロックCB0-CBnに共通にアシストゲート線AGLおよびメモリゲート線MGLが配設される。列ブロックCB0-CBnそれぞれに、Y選択ゲートYGL1、YGL2、…YGLnが設けられる。これらのYゲートYGL1-YGLnは、それぞれブロック選択信号SG0、SG1、…SGnに従って対応の列ブロックの選択列を内部読出データ線RDを介してセンスアンプへ結合する。

10

#### 【0100】

この図17に示すアレイ構成においては、1つの列ブロックCBiにおいて消去が埋込消去ゲート線EGLiの印加電圧に従って実行されているとき、他の列ブロックにおいてデータの読出を行ない、また、消去ブロックにおいて消去動作と並行してベリファイ動作を行なうことができる。

20

#### 【0101】

なお、列ブロックCB0-CBnそれぞれにおいて、複数列にわたってビット線が配設される。この場合、ビット線各々に対して列選択ゲートが配置され、列選択信号に従ってビット線が選択され、この選択列のビット線がブロック選択信号SG0-SGnに従って対応のY選択ゲートにより選択されて内部読出データ線RDに結合される。

30

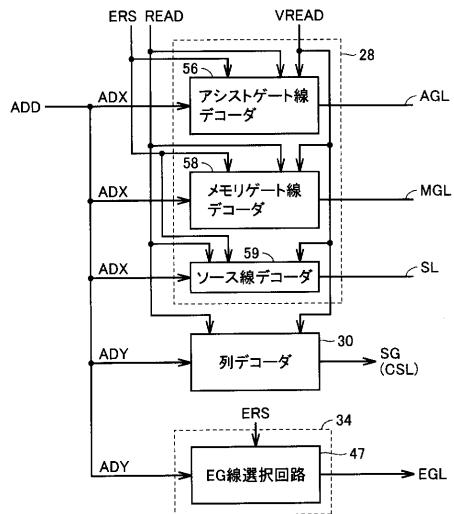

#### 【0102】

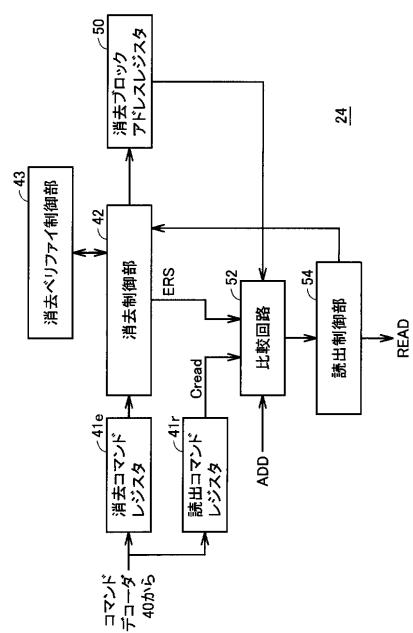

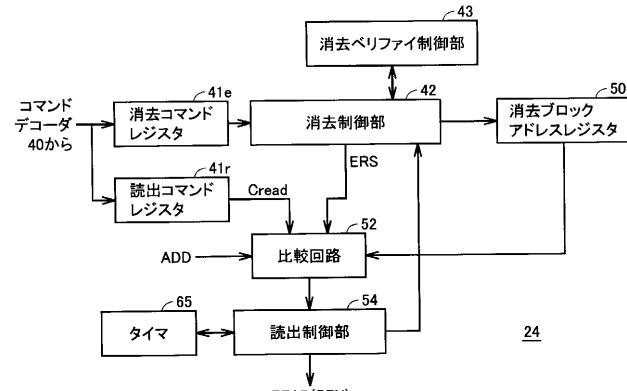

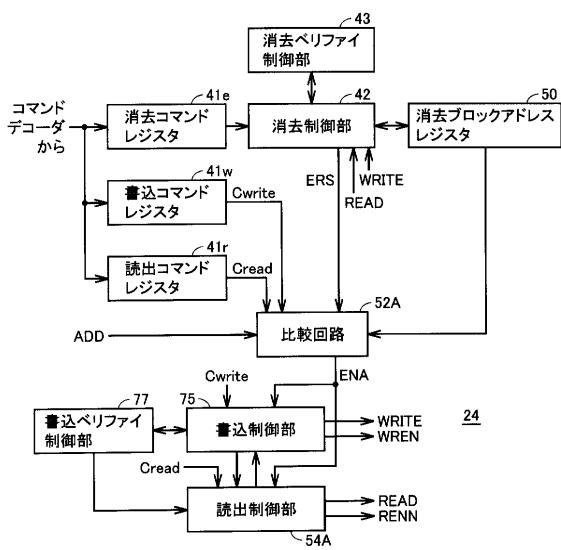

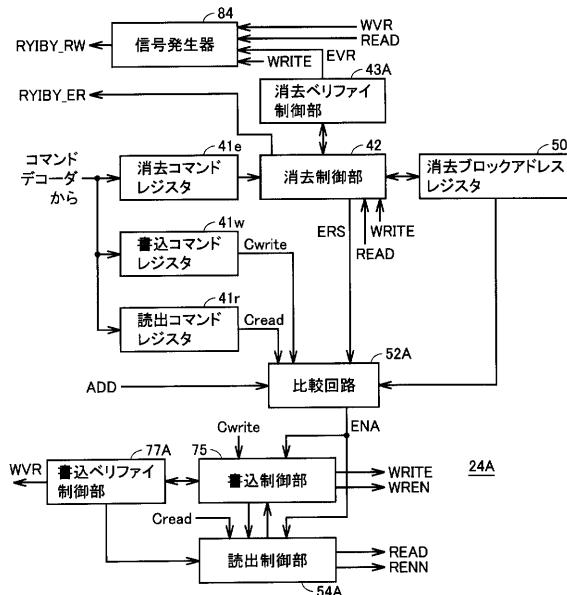

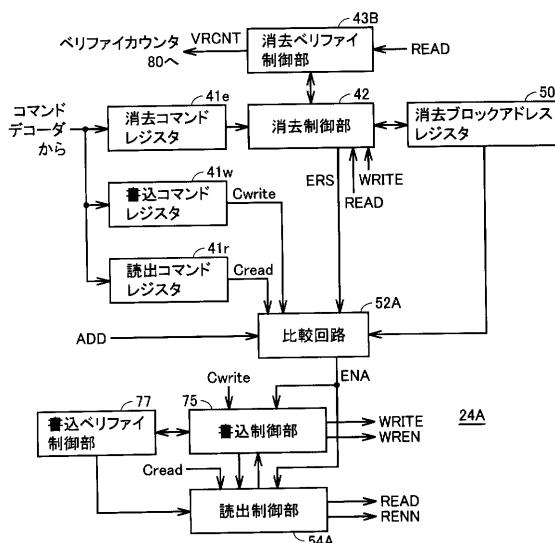

図18は、図14に示すコマンドレジスタ／制御回路24の構成を概略的に示す図である。図18に示すコマンドレジスタ／制御回路24において、コマンドレジスタとして、消去コマンドを格納する消去コマンドレジスタ41eと読出コマンドを格納する読出コマンドレジスタ41rとが設けられる。消去コマンドレジスタ41eからの消去コマンド（消去指示）が消去制御部42へ与えられる。また、消去対象の列ブロックを指定する消去ブロックアドレスを格納する消去ブロックアドレスレジスタ50が設けられる。

40

#### 【0103】

消去制御部42は、消去モードが指定されたとき、消去列ブロックを特定する列ブロックアドレスを消去ブロックアドレスレジスタ50に格納する。

#### 【0104】

消去制御部42は、また、消去ベリファイ動作を制御する消去ベリファイ制御部43の動作を制御する。このコマンドレジスタ／制御回路24において、また、比較回路52および読出制御部54が設けられる。比較回路52は、読出コマンドレジスタ41rに読出コマンドが格納され、この読出コマンドレジスタ41rからデコードされた読出コマンドとして読出指示Creadが与えられ、かつ消去制御部42からの消去モード指示ERSが与えられると、消去ブロックアドレスレジスタ50の格納ブロックアドレスと外部からのアドレス信号ADDのブロックアドレスとを比較する。

40

#### 【0105】

読出制御部54は、この比較回路52の出力信号が不一致を示すとき、読出モードイネーブル信号READをイネーブルする。読出制御部54からの読出モードイネーブル信号READは、消去制御部42へ与えられ、消去制御部42は、この読出モードイネーブル信号READのアサート時（活性化時）、ベリファイ動作を禁止状態に設定して、消去動作を継続的に実行する。

#### 【0106】

50

比較回路 5 2 がアドレスの一致を検出した場合には、この読出動作は消去ブロックに対して実行されるため、データの外部読出は停止され、読出動作モードイネーブル信号 R E A D は非活性状態に維持される。これにより、消去ブロックと別のブロックに対し外部からデータの読出アクセスを行なうことができる。

#### 【 0 1 0 7 】

なお、このデータ読出時、外部からのアドレスをアドレスレジスタ 2 2 に格納し、このアドレスレジスタ 2 2 に格納されたアドレスを先頭アドレスとして、順次内部アドレスを生成して、選択ブロックの行（アシストゲート線）が順次選択されてもよい。このとき、列選択信号は、選択ブロックにおいて、同じ列を選択するように固定されてもよい。

#### 【 0 1 0 8 】

図 1 9 は、図 1 4 に示す行デコーダ 2 8 、列デコーダ 3 0 および E G 制御回路 3 4 の構成をより具体的に示す図である。図 1 9 において、行デコーダ 2 8 は、アシストゲート線デコーダ 5 6 、メモリゲート線デコーダ 5 8 、およびソース線デコーダ 5 9 を含む。アシストゲート線デコーダ 5 6 は、読出モードイネーブル信号 R E A D 、消去モード指示 E R S およびベリファイ読出モード指示 V R E A D に従って、データ読出モードにおいては、アドレス信号 A D D に含まれる X アドレス信号 A D X をデコードし、選択行のアシストゲート線 A G L へ所定の電圧（V a g ）を伝達する。

#### 【 0 1 0 9 】

消去モード時においては、このアシストゲート線デコーダ 5 6 はディスエーブルされ、アシストゲート線 A G L を開放状態または接地電圧（0 V ）レベルに設定する。アシストゲート線デコーダ 5 6 のアシストゲート線ドライバは、アシストゲート線を開放状態に設定する構成の場合、3 値ドライバで構成され、消去モード時、非選択アシストゲート線ドライバは、出力ハイインピーダンス状態に設定される。

#### 【 0 1 1 0 】

メモリゲート線デコーダ 5 8 も同様、消去モード指示 E R S 、読出モードイネーブル信号 R E A D 、およびベリファイ読出モードイネーブル信号 V R E A D に従ってアドレス信号 A D X をデコードし、メモリゲート線 M G L に所定の電圧を印加する。このメモリゲート線デコーダ 5 8 は、消去動作モード時には、メモリゲート線 M G L を開放状態（オープン状態）または接地電圧（0 V ）に設定し、ベリファイ読出およびデータアクセス読出時においては、メモリゲート線 M G L を接地電圧レベルに維持する。メモリゲート線デコーダ 5 8 は、データ書込時において、選択行のメモリゲート線 M G L に書込高電圧を印加する。

#### 【 0 1 1 1 】

ソース線デコーダ 5 9 は、消去モード指示 E R S 、読出モードイネーブル信号 R E A D 、およびベリファイ読出モードイネーブル信号 V R E A D に従ってアドレス信号 A D X をデコードし、書込モード時、選択行のソース線 S L へ書込高電圧（5 V ）を伝達し、それ以外の動作モード時には、ソース線 S L を接地電圧レベルに維持する。

#### 【 0 1 1 2 】

列デコーダ 3 0 は、この読出モードイネーブル信号 R E A D 、ベリファイ読出イネーブル信号 V R E A D のアサート時イネーブルされ、アドレス信号 A D D に含まれる Y アドレス信号 A D Y をデコードし、列選択信号 S G を生成する。この列選択信号 S G は、列ブロックを特定するブロック選択信号およびこの特定された列ブロック内の列を指定する列選択信号 C S L 両者を含んでもよい。また、この列選択信号は、列ブロック選択信号と列選択信号との合成信号であってもよい。

#### 【 0 1 1 3 】

E G 制御回路 3 4 に含まれる E G 線選択回路 4 7 は、消去モード指示 E R S の活性化時、アドレス信号 A D Y をデコードし、選択列の埋込消去ゲート線 E G L を選択状態に駆動し、所定の消去高電圧を印加する。読出モード時およびベリファイ読出モード時においては、E G 線選択回路 4 7 は、埋込消去ゲート線をオープン状態または接地電圧レベルに維持する。

10

20

30

40

50

**【 0 1 1 4 】**

この図19に示す構成を利用することにより、消去対象の列ブロックに対し消去を行なう動作と並行して外部からのデータアクセスをおよびベリファイ読出を別の列ブロックにおいて実行することができる。

**【 0 1 1 5 】**

なお、アドレス信号ADDは、外部からのデータアクセスが行なわれる場合には、外部からのアドレス信号ADDであり、ページモード動作が可能な場合には、このアドレス信号ADDが順次内部のアドレスレジスタに格納されたアドレスをカウントアップして内部アドレスを生成する。消去ベリファイ読出時においては、このアドレス信号ADDは、図示しないベリファイカウンタから生成されるベリファイ読出アドレス信号である。

10

**【 0 1 1 6 】**

以上のように、この発明の実施の形態2に従えば、単バンク構成のメモリアレイを複数の列ブロックに分割し、列ブロック単位で消去を行なうように構成している。これにより、消去列ブロックと別の列ブロックに対し外部からデータアクセスを行なうことができ、実施の形態1と同様の効果に加えて、データアクセスが効率的に行なうことができ、外部の処理装置のデータ待ち時間をなくすことができる。また、実施の形態1と同様の効果を得ることができる。

**【 0 1 1 7 】****[ 実施の形態3 ]**

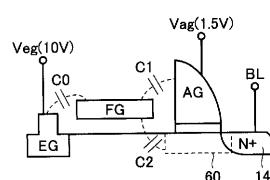

図20は、消去および読出を並行して行なう際のメモリセルの印加電圧を概略的に示す図である。図20において、消去時においては、埋込消去ゲートEGに消去高電圧Veg (= 10V)が印加される。読出時においては、アシストゲートAGに読出電圧Vag (= 1.5V)が印加される。読出時、ビット線BLは、読出電圧(1.0V)が印加される。この状態において、読出時においては、アシストゲートAG上の電圧Vagにより、ドレイン不純物領域14に隣接する基板領域表面に、チャネル60が形成される。この状態においては、埋込消去ゲートEGとフローティングゲートFGの間に、寄生容量C0が存在し、フローティングゲートFGとアシストゲートAGの間に寄生容量C1が存在し、フローティングゲートFGとチャネル60の間にも、寄生容量C2が存在する。

20

**【 0 1 1 8 】**

通常の従来と同様の消去動作においては、アシストゲートAGおよびビット線BLはオーブン状態または0V(接地電圧)であり、埋込消去ゲートEGに対してのみ消去高電圧が印加される。したがって、消去電圧印加と読出動作を並行して実行する場合、寄生容量C1およびC2により、埋込消去ゲートEGとフローティングゲートFGの間の寄生容量C0による結合の効果が低下する。このため、効率的なカップリングを埋込消去ゲートEGとフローティングゲートFGの間に実現することができなくなり、埋込消去ゲートEGとフローティングゲートFGの間に十分な電圧を印加することができず、消去効率が低下することが考えられる。

30

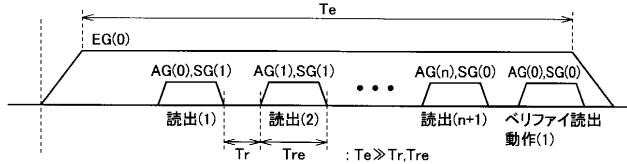

**【 0 1 1 9 】**

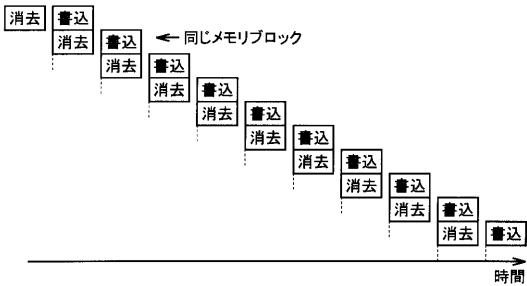

図21は、この発明の実施の形態3における消去および読出を行なう際の動作シーケンスを示すタイミング図である。メモリセルのアレイおよび読出部の構成は、先の図14および図15に示す実施の形態2に従う半導体装置の構成と同じである。消去時、埋込消去ゲートEG(0)に消去高電圧を印加する。続いて、消去非対称のアシストゲートAGを順次選択し、同一列のブロック列選択信号(またはブロック選択信号)SG(1)を選択状態に駆動し、データ読出を行なう。図21に示すシーケンスにおいては、AG(0)からAG(n)を順次選択して、(n+1)回のデータ読出を行なう。この読出の間の待機期間Trおよび読出期間Treは、消去パルス印加期間Teよりも十分に小さくする。

40

**【 0 1 2 0 】**

すなわち、消去パルス印加時においては、データ読出は連続的ではなく所定の間隔Trにおいて行ない、読出間隔Trよりも十分長い期間、消去高電圧を印加する。最後に外部データ読出を行なった後、ベリファイ読出動作が実行される。図21に示すシーケンスに

50

おいては、列選択信号（またはブロック選択信号）SG(0)に従ってアシストゲート線AG(0)、…を順次選択して実行される。この消去電圧印加中にベリファイ読出を開始し、ベリファイ読出モードでデータを内部読出しし、消去ベリファイ結果が消去パスを示せば、消去高電圧を所定のレベルに低下させる。

#### 【0121】

したがって、このアシストゲートに印加される読出パルス印加期間Treは、消去高電圧を印加する期間Teに比べて十分短くされ、埋込消去ゲートEGとフローティングゲートFGのカップリングが低下する影響を低減することができ、正確に消去を行なうことができる。

#### 【0122】

図22は、この発明の実施の形態3に従う半導体装置のコマンドレジスタ／制御回路24の構成を概略的に示す図である。この図22に示すコマンドレジスタ／制御回路24は、以下の点で、図18に示すコマンドレジスタ／制御回路24の構成と、その構成が異なる。すなわち、図22に示すコマンドレジスタ／制御回路24においては、読出制御部54に対しタイマ65が設けられる。この図22に示すコマンドレジスタ／制御回路24の他の構成は、図18に示す構成と同じであり、対応する部分には同一参照番号を付し、その詳細説明は省略する。

10

#### 【0123】

この図22に示すコマンドレジスタ／制御回路24の構成においては、読出制御部54は、データ読出を行なうとき、読出モードイネーブル信号READをタイマ65からのカウント値に従って所定間隔でイネーブルする。この読出モードイネーブル信号READの活性化期間により、データ読出期間が指定される。この場合、読出制御部54は、読出モードとして、バーストモードのように連続的にデータの読出を行なうモードが指定されたとき、読出モードイネーブル信号READを、この読出動作期間中イネーブル状態に設定し、各読出期間を規定する読出活性化信号RENを、タイマ65のカウント値に従って選択的に所定の間隔で、所定期間イネーブル状態とする構成が用いられてもよい。

20

#### 【0124】

消去制御部42は、読出制御部54からの読出動作完了指示に従って消去ベリファイ制御部43を制御し、ベリファイ読出を消去ベリファイ制御部43の制御の下に実行する。

#### 【0125】

列デコーダおよび行デコーダの構成は、先の図19に示す構成と同様の構成を利用する。読出モードイネーブル信号READの活性化期間中、アドレス信号ADDのデコード動作が実行されて、行および列の選択が実行される。

30

#### 【0126】

電圧発生回路(26)は、各動作モードに応じて必要な電圧、すなわち消去高電圧、読出電圧およびベリファイ読出電圧を、各制御部42, 43および54の制御の基に生成する。

#### 【0127】

なお、バーストモードが許容される場合、また、アドレス信号ADDは、タイマ65のカウント値に従って、順次、アドレスカウンタ（図示せず）からアドレスレジスタの格納アドレスを出発アドレスとして生成する構成が用いられてもよい。

40

#### 【0128】

以上のように、この発明の実施の形態3に従えば、消去電圧印加中のデータ読出時、消去電圧印加期間よりも十分短い間隔および読出期間で読出を行っており、消去電圧印加による消去動作に影響を及ぼすことなく、並行してデータ読出を行なうことができる。

#### 【0129】

##### [実施の形態4]

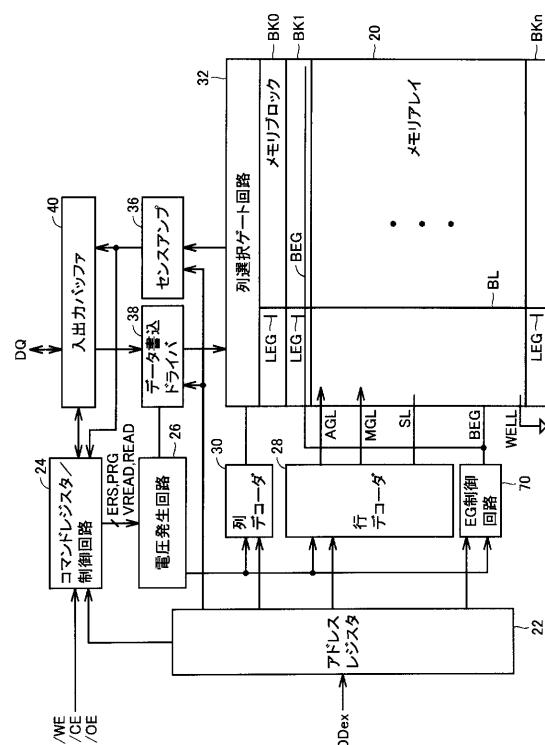

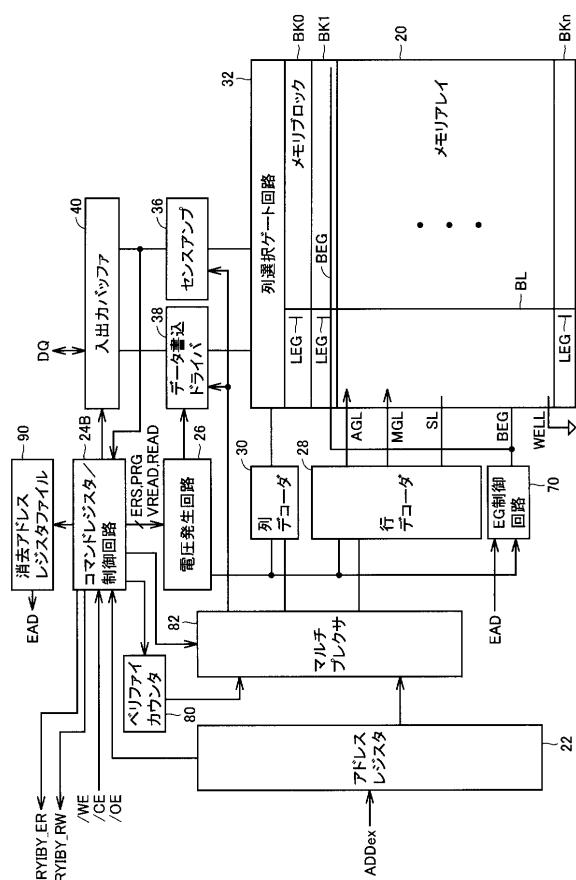

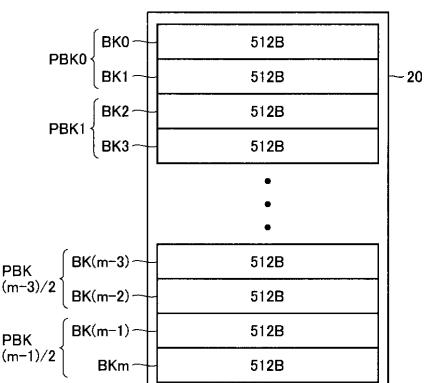

図23は、この発明の実施の形態4に従う半導体装置の全体の構成を概略的に示す図である。図23に示す半導体装置は、以下の点で、その構成が、図14に示す半導体装置と異なる。すなわち、メモリアレイ20が、複数のメモリブロックBK0-BKnに分割さ

50

れる。これらのメモリブロック B K 0 - B K n には共通に、ビット線 B L が配設され、各メモリブロックの対応の列のメモリセルがビット線 B L に接続される。

#### 【 0 1 3 0 】

メモリブロック B K 0 - B K n には、それぞれ、行方向に沿って延在するアシストゲート線 A G L およびメモリゲート線 M G L が配設される。また、メモリブロック B K 0 - B K n それぞれに対して、ブロック埋込消去ゲート線 B E G が配設される。メモリブロック B K 0 - B K n それぞれにおいてローカル埋込消去ゲート線 L E G が配設され、対応のブロック消去ゲート線 B E G に結合される。ローカル埋込消去ゲート線 L E G は、対応のメモリブロック内において各メモリセル列に沿って列方向に延在するように配置される。

#### 【 0 1 3 1 】

E G 制御回路 7 0 は、消去モード時、メモリブロック単位で、ブロック埋込消去ゲート線 B E G を選択状態へ駆動する。

#### 【 0 1 3 2 】

この図 2 3 に示す他の構成は、図 1 4 に示す半導体装置の構成と同じであり、対応する部分には同一参照番号を付し、その詳細説明は省略する。

#### 【 0 1 3 3 】

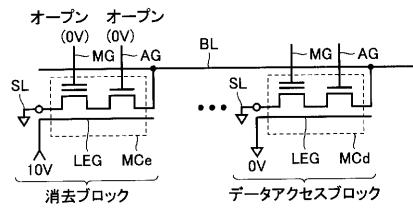

図 2 4 は、図 2 3 に示すメモリアレイ 2 0 の構成をより具体的に示す図である。図 2 4 に示す構成においては、消去単位が異なるメモリブロックが設けられているため、メモリブロック B K 0 - B K n の符号に代えて、符号 B K A および B K B を用いる。

#### 【 0 1 3 4 】

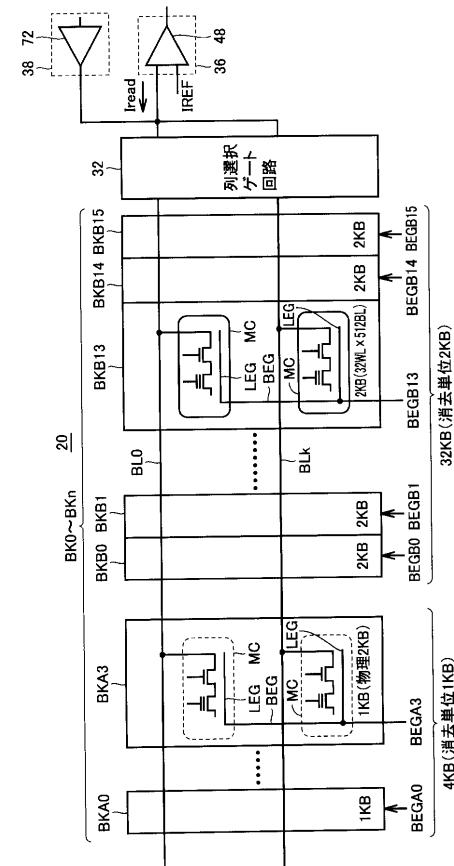

図 2 4 において、たとえば 1 K バイトの容量のメモリブロック B K A 0 - B K A 3 と、例えば 2 K バイトの容量のメモリブロック B K B 0 - B K B 1 5 が設けられる。メモリブロック B K A 0 - B K A 3 および B K B 0 - B K B 1 5 に対しては、メモリブロック単位で消去が行なわれる。したがって、合計容量 4 K B ( バイト ) のメモリブロック B K A 0 - B K A 3 においては、消去単位は 1 K バイトであり、一方、合計 3 2 K B のメモリブロック B K B 0 - B K B 1 5 においては、消去単位は 2 K バイトである。この消去単位を異ならせることにより、アプリケーションに応じてデータを、消去単位の異なるメモリブロックに格納する。例えば、頻繁に書き換えるデータを容量の小さなメモリブロック B K A 0 - B K A 3 に格納し、データ量が多いまたは書換え頻度の小さなデータを容量の大きなメモリブロック B K B 0 - B K B 1 5 に格納する。

#### 【 0 1 3 5 】

メモリブロック B K A 0 - B K A 3 および B K B 0 - B K B 1 5 に共通にビット線 B L が設けられる。図 2 4 においては、ビット線 B L 0 および B L k を代表的に示す。ビット線 B L 0 - B L k に対し、各メモリブロックにおいてメモリセル M C の選択トランジスタ ( アシストゲートトランジスタ ) が結合される。この場合、データアクセスが各メモリブロックにおいて 2 ビット単位で実行されるため、記憶容量は、物理アドレスの 1 / 2 倍となる。

#### 【 0 1 3 6 】

メモリブロック B K A 0 - B K A 3 および B K B 0 - B K B 1 5 に共通に、列選択ゲート回路 3 2 が設けられる。この列選択ゲート回路 3 2 により選択されたビット線が、内部データバスを介してセンスアンプ回路 4 8 および書込ドライブ回路 7 2 に結合される。このセンスアンプ回路 4 8 および書込ドライブ回路 7 2 は、それぞれ、図 2 3 に示すセンスアンプ 3 6 およびデータ書込ドライバ 3 8 内に設けられる。

#### 【 0 1 3 7 】

メモリブロック B K A 0 - B K A 3 に対しては、ブロック埋込消去ゲート線 B E G A 0 - B E G A 3 がそれぞれ設けられ、メモリブロック B K B 0 - B K B 1 5 には、ブロック埋込ゲート線 B E G B 0 - B E G B 1 5 がそれぞれ設けられる。

#### 【 0 1 3 8 】

図 2 5 は、図 2 4 に示すメモリブロックにおける 1 つのメモリブロックに対する消去を行なう場合の、各ブロックのゲート配線の印加電圧を概略的に示す図である。図 2 5 にお

10

20

30

40

50

いて、消去対象のブロックにおいては、メモリセルM C e のローカル埋込消去ゲート線 L E G に消去高電圧(10V)が印加される。メモリセルM C e のメモリゲートM G およびアシストゲートA G は、オープン状態または0Vであり、ソース線S L は、接地ノードに結合される。したがって、消去時、アシストゲートA G を0Vに設定すれば、消去対象のメモリセルM C e のローカル埋込消去ゲート線L E G は、ビット線B L と分離される。

#### 【0139】

この消去対象のメモリブロックと異なるメモリブロックにおいて、メモリセルM C d のローカル埋込消去ゲート線L E G は、0Vまたはオープン状態に維持される。メモリセルM C d のメモリゲートM G およびアシストゲートA G には、消去対象のメモリセルM C e のメモリゲートM G およびアシストゲートA G の印加電圧にかかわらず、別の電圧を印加することができる。したがって、ビット線B L に読み出電圧または書き込み電圧を印加することができ、また、消去非対象のメモリブロックのソース線S L には書き込み電圧を印加することができ、応じて、メモリセルM C d に対してデータアクセス(読み出/書き込み)を行なうことができる。すなわち、消去ブロックにおける消去電圧印加期間中に、並行して、別のメモリブロックに対してデータのアクセス(外部データの書き込みまたは読み出)を行なうことができる。

10

#### 【0140】

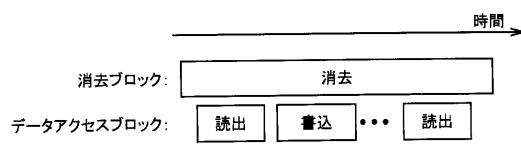

図26は、この発明の実施の形態4における消去およびデータアクセスシーケンスの一例を示す図である。図26において、消去対象ブロックにおいて消去電圧が印加される。この消去電圧印加と並行して、別のデータアクセスブロックにおいてデータの読み出または書き込みを実行することができる。これにより、読み出および書き込みの自由度が改善され、データアクセス効率が改善される。

20

#### 【0141】

消去モード時のベリファイ動作においては、単にデータアクセスブロックのデータアクセス完了時またはその間を縫って消去ベリファイ読み出が実行されればよい。

#### 【0142】

図27は、この発明の実施の形態4に従う半導体装置のデータアクセスシーケンスを示す図である。図27に示すアクセスシーケンスにおいては、書き込みおよび読み出しが交互に異なるメモリブロックに対して実行される。書き込み(プログラム)時においては、ビット線を用いて書き込み電圧が伝達されるため、書き込みおよび読み出しが並行して実行することはできない。

30

#### 【0143】

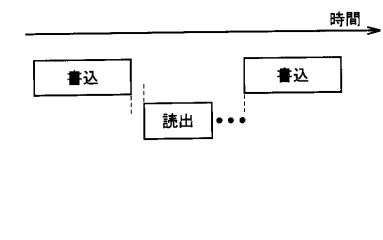

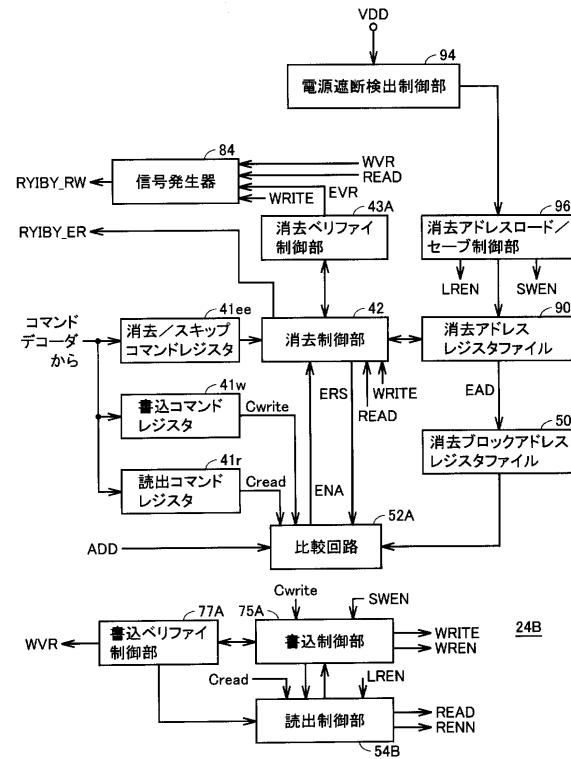

図28は、図23に示すコマンドレジスタ/制御回路24の構成を概略的に示す図である。この図28に示すコマンドレジスタ/制御回路24においては、指定された動作モードを特定するコマンドを格納するコマンドレジスタとして、消去コマンドレジスタ41e、書き込みコマンドレジスタ41w、および読み出コマンドレジスタ41rが設けられる。これらのコマンドレジスタ41e、41wおよび41rは、図示しないコマンドデコーダからのデコード後のコマンドをそれぞれ格納する。

#### 【0144】

図28に示すコマンドレジスタ/制御回路20は、先の図18に示す構成と同様、消去制御部42、消去ベリファイ制御部43および消去ブロックアドレスレジスタ50を含む。消去制御部42は、消去コマンドレジスタ41eからの消去コマンドに従って消去モード指示E R S をアサートし、消去動作と並行してまたは消去完了後消去ベリファイ制御部43を活性化して消去ベリファイ動作を実行する。消去ベリファイが完了すると消去制御部42は、消去ベリファイ制御部43からの消去ベリファイ完了指示に従って消去動作を停止する。

40

#### 【0145】

コマンドレジスタ/制御回路24においては、さらに、比較回路52A、読み出制御部54A、書き込み制御部75および書き込みベリファイ制御部77が設けられる。比較回路52Aは、書き込みコマンドレジスタ40wからの書き込みモード指示C w r i t e および読み出コマンドレジスタ41rからの読み出モード指示C r e a d の一方のアサートと消去制御部42からの

50

消去モード指示 E R S のアサートに従って、消去ロックアドレスレジスタ 50 に格納された消去ロックアドレスと与えられたアドレス信号 A D D のロックアドレスとを比較する。比較結果が一致する場合、比較回路 52A は、データアクセス活性化信号 E N A をネゲート状態に維持し、比較結果が不一致のときには、データアクセス活性化信号 E N A をアサートする。

#### 【 0 1 4 6 】

読み出制御部 54A は、書き込み制御部 75 からの書き込みモードイネーブル信号 W R I T E のネゲート（非活性化）時、読み出モード指示 C r e a d と比較回路 52A からのデータアクセス活性化指示とに従って、読み出モードイネーブル信号 R E A D および読み出動作活性化信号 R E N N を生成する。読み出モードイネーブル信号 R E A D は、読み出動作期間中イネーブル状態に設定され、読み出動作活性化信号 R E N N は、実際のデータ読み出を行なう期間を規定する。この半導体装置が、アドレス信号の変化に従って読み出動作の活性化タイミングを設定する場合、特に、読み出動作活性化信号 R E N N は生成されなくてもよい。また、読み出動作活性化信号 R E N N に従ってアシストゲート線 A G の活性化期間およびセンスアンプの活性化期間が規定される。

10

#### 【 0 1 4 7 】

読み出制御部 54A は、さらに、書き込みベリファイ制御部 77 からの書き込みベリファイ指示に従って読み出モードイネーブル信号 R E A D および読み出動作活性化信号 R E N N を活性化する。読み出制御部 54A は、また、図示しない経路により、消去ベリファイ制御部 43 からの消去ベリファイ指示に従って読み出モードイネーブル信号 R E A D および読み出動作活性化信号 R E N N を活性化する。

20

#### 【 0 1 4 8 】

書き込み制御部 75 は、比較回路 52A からのデータアクセス活性化信号 E N A のアサート時に書き込みモード指示 C w r i t e がアサートされると、書き込みモードイネーブル信号 W R I T E および書き込み動作活性化信号 W R E N を活性化する。書き込み動作モード指示信号 W R I T E は書き込み動作期間を規定し、書き込み動作活性化信号 W R E N は、メモリゲートおよびビット線に印加される書き込み電圧の印加期間を規定する。書き込み制御部 75 は、書き込み完了後、書き込みベリファイ制御部 77 を起動し、書き込みベリファイを実行する。

#### 【 0 1 4 9 】

書き込み制御部 75 は、読み出制御部 54A が読み出モードイネーブル信号 R E A D をアサートしているときには、非活性状態に維持される。

30

#### 【 0 1 5 0 】

この発明の実施の形態 4 に従う半導体装置における行デコーダの構成としては、各メモリブロックに対して、図 19 に示す構成がローカルデコーダとして設けられればよい。

#### 【 0 1 5 1 】

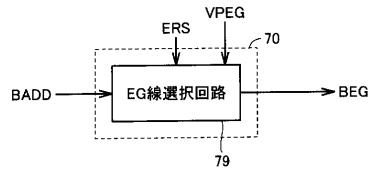

図 29 は、図 23 に示す E G 制御回路 70 の構成の一例を概略的に示す図である。図 29 に示す E G 制御回路 70 においては、E G 線選択回路 79 が設けられる。E G 線選択回路 79 は、消去モード指示 E R S のアサート時、アドレス信号 A D D に含まれるロックアドレス B A D D をデコードし、選択メモリブロックに対するロック埋込消去ゲート線 B E G に消去高電圧 V P E G を伝達する。残りの非選択メモリブロックに対しては、E G 線選択回路 79 は、ロック埋込消去ゲート線を接地電圧に維持する（またはオープン状態に維持する）。

40

#### 【 0 1 5 2 】

各動作モードに必要な電圧については、消去制御部 42、書き込み制御部 75 および読み出制御部 54A からの消去モード指示 E R S 、書き込みモードイネーブル信号 W R I T E および読み出モードイネーブル信号 R E A D に従って、それぞれ図 23 に示す電圧発生回路において消去電圧、書き込み電圧、読み出電圧および消去 / 書き込みベリファイ読み出電圧が生成され（または選択され）、行デコーダおよび列デコーダへ与えられ、各動作モードに応じた電圧が選択メモリセルへ供給される。

#### 【 0 1 5 3 】

50

以上のように、この発明の実施の形態4に従えば、消去動作と並行して別のメモリブロックにおいて読出または書込を実行可能としている。応じて、データアクセス効率がさらに改善される。また実施の形態1および2と同様の効果を得ることができる。

#### 【0154】

なお、この実施の形態4においても、実施の形態3と同様、書込または読出を行なう期間および間隔は、消去電圧印加期間よりも十分短くされ、消去動作に悪影響を及ぼさないようにされる。

#### 【0155】

##### [実施の形態5]

図30は、この発明の実施の形態5に従う半導体装置の全体の構成を概略的に示す図である。この図30に示す半導体装置は、以下の点で、図23に示す半導体装置とその構成が異なる。すなわち、コマンドレジスタ／制御回路24Aは、消去動作時には、外部に消去ステータス信号RYIBY\_ERを出力し、かつ内部でデータ読出、書込またはベリファイ動作実行中、アクセス禁止ステータス信号RYIBY\_RWを外部装置へ出力する。

10

#### 【0156】

また、ベリファイカウンタ80およびマルチプレクサ82が設けられる。ベリファイカウンタ80は、消去ベリファイ時および書込ベリファイ時、カウント動作によりベリファイ対象のメモリセルを特定するアドレスを生成する。マルチプレクサ82は、アドレスレジスタ22からの内部アドレスとベリファイカウンタ80からのベリファイアドレスの一方を選択して内部アドレスを生成して、列デコーダ30、行デコーダ28およびEG制御回路70へ与える。マルチプレクサ80からの内部アドレスは、またデータ書込ドライバ38およびセンスアンプ36へも与えられる。

20

#### 【0157】

この図30に示す半導体装置の他の構成は、図23に示す半導体装置の構成と同じであり、対応する部分には同一参照番号を付し、その詳細説明は省略する。

#### 【0158】

図30に示す半導体装置においては、コマンドレジスタ／制御回路24Aは、内部でデータの読出、書込（実際の書込動作）またはベリファイ動作を行なわれたとき、アクセス禁止ステータス信号RYIBY\_RWをアサートする。したがって、アクセス禁止ステータス信号RYIBY\_RWがアサート状態のときには、処理装置などの外部装置は、この半導体装置へのアクセスが禁止される。

30

#### 【0159】

一方、コマンドレジスタ／制御回路24Aからの消去ステータス信号RYIBY\_ERがアサート状態のときには、この半導体装置内部で消去動作が行なわれるときである（消去ベリファイ動作は行なわれていない）。したがって、この場合には、外部からのデータのアクセス（書込／読出）を許可する。内部で、ベリファイ動作が行なわれるとき、外部アクセスを禁止することによって、データの衝突を確実に防止して、高速のデータアクセスを実現することができる。

#### 【0160】

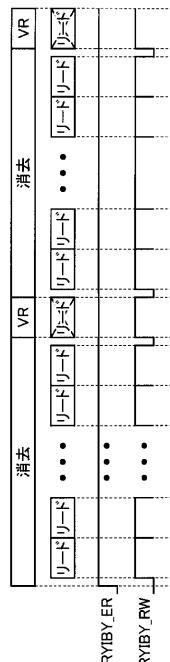

図31は、消去時の動作シーケンスの一例を示す図である。図31に示すように、メモリアレイ20における1つのメモリブロックに対する消去が行なわれる。この消去が、内部で行なわれると、コマンドレジスタ／制御回路24Aが、消去ステータス信号RYIBY\_ERをアサートする。この信号RYIBY\_ERのアサートにより、外部装置は、アクセス不可能であることを報知される。

40

#### 【0161】

外部装置が、この状態で、読出アクセス（リードアクセス）を行なうと、データアクセス禁止ステータス信号RYIBY\_RWがアサートされる。1つのリード動作が内部で完了すると、この信号RYIBY\_RWがデアサート（ネゲート）される。信号RYIBY\_RWのネゲートに従って次の読出動作が繰返し実行される。

#### 【0162】

50

メモリブロックに対する消去および消去ベリファイが完了すると、消去ステータス信号 R Y I B Y\_E R がネゲートされる。このとき、消去ベリファイ動作が実行中は（ベリファイ動作は、記号 V R で示す）、信号 R Y I B Y\_E R はアサート状態であり、さらに、信号 R Y I B Y\_R W がアサートされる。応じて、消去ベリファイ動作期間中、外部からのアクセスは禁止される。このベリファイ動作が完了し、再び消去電圧の印加が行なわれると、信号 R Y I B Y\_E R がアサートされ、外部装置に対してアクセス可能が報知される。

#### 【 0 1 6 3 】

消去ベリファイ動作完了に従って、信号 R Y I B Y\_R W はネゲートされる。したがって、消去電圧印加期間中に、読出動作が繰返し実行されると、内部の読出動作が完了するごとに、信号 R Y I B Y\_R W がネゲート状態となり、内部で読出動作が行なわれるときにアサート状態とされ、内部でデータ読出が行なわれるとき外部からのアクセスは禁止される。読出動作が完了すると、信号 R Y I B Y\_R W はネゲートされる。消去が完了すると、また、信号 R Y I B Y\_E R がネゲートされる。

10

#### 【 0 1 6 4 】

消去電圧（パルス）印加時に、信号 R Y I B Y\_E R を用いて、外部にデータアクセス可能を報知し、また、内部で読出動作が行なわれていることを外部へ信号 R Y I B Y\_R W を用いて報知することにより、消去動作時に並行して確実に外部からデータ読出アクセスを、アクセステーナとベリファイデータとの衝突を回避しつつ、行なうことができる。

20

#### 【 0 1 6 5 】

図 3 2 は、この消去パルス印加時の他の動作シーケンスの例を示す図である。図 3 2においては、消去パルス印加と並行して書込動作（ライト動作）が行なわれる。このライト動作時においては、書込ベリファイが実行される。

#### 【 0 1 6 6 】

消去パルスが印加されると、信号 R Y I B Y\_E R がアサートされ、外部に対しデータアクセス可能が報知される。応じて、外部からデータの書込アクセスが実行され、信号 R Y I B Y\_R W がアサートされる。書込動作が完了すると、書込ベリファイ動作が続いて実行される。書込ベリファイ動作（V R 動作）が実行されるため、信号 R Y I B Y\_R W は、継続してアサート状態に維持される。書込ベリファイ動作が完了すると、1つのデータ書込が完了し、信号 R Y I B Y\_R W がネゲートされる。

30

#### 【 0 1 6 7 】

消去動作時、信号 R Y I B Y\_R W のネゲートに従って、次の外部からの書込アクセスが実行される。データ書込およびベリファイ動作が完了すると、信号 R Y I B Y\_R W がネゲートされる。この信号 R Y I B Y\_R W のネゲートに従って、消去動作が完了し、信号 R Y I B Y\_E R がネゲートされる。この消去パルス印加後、消去ベリファイ動作が、消去対象のメモリセルが確実に消去されたかを識別するために実行される。このとき、信号 R Y I B Y\_E R はアサートされるものの、信号 R Y I B Y\_R W がアサート状態であり、外部からの書込アクセスは禁止される。信号 R Y I B Y\_E R および R Y I B Y\_R W を内部で利用することにより、書込ベリファイと消去ベリファイトの競合を回避することができる。

40

#### 【 0 1 6 8 】

消去ベリファイ動作により消去動作が完了すると、消去ステータス信号 R Y I B Y\_E R がネゲートされる。一方、消去ベリファイ動作により消去フェイルと判定されると、消去ステータス信号 R Y I B Y\_E R が引続きアサートされ、消去パルス印加が引続き実行される。このとき、消去ベリファイ動作完了に従って信号 R Y I B Y\_R W がネゲートされ、外部からの書込アクセスが許可される。

#### 【 0 1 6 9 】

内部で書込動作が開始されると、信号 R Y I B Y\_R W がアサートされ、データ書込が実行され、続いて、書込ベリファイが実行される。この書込および書込ベリファイが完了すると、信号 R Y I B Y\_R W がネゲートされる。また、消去パルス印加期間が完了する

50

と、信号 R Y I B Y\_E R がネゲートされる。消去ベリファイ動作が実行されるため、再び信号 R Y I B Y\_R W がアサートされ、外部からの書込アクセスは禁止される。

#### 【0170】

以上のように、内部で消去ベリファイまたは書込ベリファイを実行する場合、外部アクセスを禁止することにより、ベリファイ動作と外部からのデータアクセス動作が衝突するのを回避して消去動作に並行して外部からのデータアクセス（書込／読出）を実行することができる。特に、消去ステータス信号 R Y I B Y\_E R を、消去時の消去パルス印加時および消去ベリファイ動作中はアサート状態に維持し、アクセスステータス信号 R Y I B Y\_R W は、メモリセルへのアクセス時、すなわち、消去ベリファイ動作時、外部書込アクセス時および外部読出アクセス時にアサート状態に設定する。これにより、信号 R Y I B Y\_E R および R Y I B Y\_R W を互いに独立に制御することができ、制御が容易となる。

10

#### 【0171】

なお、図31および図32に示す構成において、各データ読出または書込ごとに、読出コマンドまたは書込コマンドが与えられるように動作を示している。しかしながら、この読出コマンドおよび書込コマンドとしてバーストアクセスモードが指定され、連続的にデータの読出または書込が実行されてもよい。この場合、信号 R Y I B Y\_R W は、このバーストアクセス期間中アサート状態に維持される。

#### 【0172】

図33は、図30に示すコマンドレジスタ／制御回路24Aの構成を概略的に示す図である。この図33に示すコマンドレジスタ／制御回路24Aの構成は、以下の点で、図28に示すコマンドレジスタ／制御回路24の構成と異なる。すなわち、書込ベリファイ制御部77Aが、書込ベリファイ指示信号WVRを生成し、消去ベリファイ制御部43Aが、消去ベリファイ指示信号EVRを生成する。この信号WVRおよびEVRのアサート時、ベリファイ動作が実行される。

20

#### 【0173】

消去制御部42は、消去電圧印加期間中および消去ベリファイ動作期間中、信号 R Y I B Y\_E R をアサートして外部へ出力する。これらの信号WVR、EVR、読出モードイネーブル信号READおよび書込モードイネーブル信号WRITEを受ける信号発生器84が、信号 R Y I B Y\_R W を生成するために設けられる。この信号発生器84は、与えられた信号WVR、READ、EVRおよびWRITEのいずれかのアサート時、信号 R Y I B Y\_R W をアサートして外部へ出力する。これにより、内部でデータの書込、読出およびベリファイが実行されている場合、信号 R Y I B Y\_R W をアサートすることができる。

30

#### 【0174】

なお、信号発生器84に対し、信号READおよびWRITEに代えて活性化信号RENおよびRENNが与えられてもよい。

#### 【0175】

消去ベリファイ制御部43Aは、消去制御部42と同様、シーケンスコントローラで構成され、消去パルス印加後、所定のシーケンスで消去ベリファイ動作を実行する。これにより、信号 R Y I B Y\_R W を利用することにより、このベリファイ動作と外部からのデータ読出アクセスとが衝突するのを防止することができる。

40

#### 【0176】

以上のように、この発明の実施の形態5に従えば、内部消去状態を示す信号と内部の読出、書込およびベリファイ動作を示す信号とを外部の装置に出力している。したがって、内部でのベリファイ動作時に、外部からの書込および読出アクセスを禁止することにより、データの外部アクセスとベリファイ動作が競合するのを防止することができる。応じて、正確かつ効率的に、消去パルス印加時においても、データアクセスを行なうことができる。

#### 【0177】

50

本実施の形態 5においては、消去電圧（パルス）印加期間中の消去ベリファイは行なわれていない。この消去パルス印加中の消去ベリファイは、以下の実施の形態において説明するように、外部アクセスとの間でタイミング調整が行われて実行されてもよい。

#### 【0178】

##### [実施の形態 6]

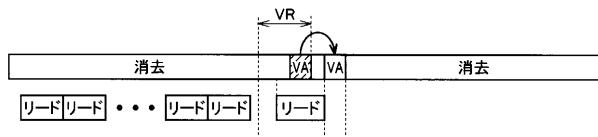

図34は、この発明の実施の形態6に従う半導体装置の消去時のデータアクセスシーケンスの一例を示す図である。図34に示す動作シーケンスにおいて、消去ベリファイ動作中に、読み出アクセス要求が発行されたとき、消去ベリファイ動作VRを停止させ、要求された読み出動作を実行する。データ読み出アクセス完了後、停止した消去ベリファイ動作を残りのベリファイアドレス領域VAについて実行する。

10

#### 【0179】

これにより、読み出データアクセス時、待ち時間を生じさせることなく、データ読み出アクセスを実行することができる。

#### 【0180】

図35は、この発明の実施の形態6に従う半導体装置のコマンドレジスタ／制御回路の構成を概略的に示す図である。半導体装置の全体の構成は、図23に示す半導体装置の構成と同じである。

#### 【0181】

図35に示すコマンドレジスタ／制御回路24Aは、以下の点で、その構成が図33に示すコマンドレジスタ／制御回路24Aと異なる。すなわち、信号発生器84は、設けられない。すなわち、内部ステータスを外部に報知する信号は、本実施の形態6においては利用されない。消去ベリファイ制御部43Bは、読み出制御部54Aからの読み出モードイネーブル信号READを受け、この読み出モードイネーブル信号READがアサートされると、実行中のベリファイ動作を停止させ、読み出制御回路54Aに対して外部読み出アクセス許可を報知する。また、カウント更新指示信号VRONTをネゲートしてベリファイカウンタ80のカウント動作を停止させる。

20

#### 【0182】

読み出制御回路54Aは、消去ブロックと異なるメモリブロックへの読み出アクセス時、この消去ベリファイ制御部43Bからの読み出アクセス許可を受けると、読み出動作活性化信号RENNをアサートしてデータの外部読み出動作を実行する。読み出アクセスが完了すると、読み出制御部54Aは、読み出モードイネーブル信号READをネゲートする。この読み出モードイネーブル信号READのネゲートに従って、カウント更新指示信号VRONTをアサートして消去ベリファイを停止したベリファイアドレスから再開する。

30

#### 【0183】

また、この消去ベリファイ制御部43Bは、消去制御部42から、消去ベリファイ開始指示が与えられた時に、読み出モードイネーブル信号READがアサートされ、外部読み出アクセスが実行されている場合には、この消去ベリファイを外部データ読み出アクセスが完了するのを待つ。消去ベリファイ制御部43Bは、この読み出モードイネーブル信号READがネゲートされると、ベリファイカウンタ80へカウント更新信号VRONTを与え、このベリファイカウンタ80からのベリファイアドレスカウントをマルチプレクサ82に選択させて、このベリファイカウンタ80からのカウント値に従って消去ベリファイ動作を実行する。

40

#### 【0184】

この図35に示すコマンドレジスタ／制御回路24Aの他の構成は、図33に示すコマンドレジスタ／制御回路24Aの構成と同様であり、その詳細説明は省略する。

#### 【0185】

以上のように、この発明の実施の形態6に従えば、消去時にベリファイ動作実行時外部からの読み出アクセス要求が与えられたとき、または、その逆に外部読み出アクセス中に消去ベリファイ指示がアサートされると、消去ベリファイ動作を停止または待ち合わせ、外部からの読み出アクセスを実行している。外部読み出アクセスに対して消去ベリファイ動作より

50

も高い優先順位を与えている。これにより、外部からの読み出しがアクセスの待ち時間を短縮することができ、高速のデータ読み出を行なうことができる。

#### 【0186】

##### [実施の形態7]

図36は、この発明の実施の形態7に従う半導体装置の全体の構成を概略的に示す図である。図36に示す半導体装置は、図30に示す半導体装置と以下の点で、その構成が異なる。すなわち、消去ブロックを特定する消去アドレスを複数個格納する消去アドレスレジスタファイル90が設けられる。消去アドレスレジスタファイル90は、コマンドレジスタ／制御回路24Bの制御の基に、格納した消去アドレスを順次読み出し、その消去ブロックアドレスEADをEG制御回路70へ与える。この図36に示す半導体装置の他の構成は、図30に示す半導体装置の構成と同じであり、対応する部分には同一参照番号を付し、その詳細説明は省略する。

10

#### 【0187】

図37は、図36に示す消去アドレスレジスタファイル90の構成の一例を概略的に示す図である。消去アドレスレジスタファイル90は、複数のレジスタを含み、各レジスタが、それぞれ消去アドレス格納領域90aおよび有効フラグ格納領域90bを含む。レジスタREG0-REGAは、シフト動作により、その記憶データを順次。 FIFO8ファーストイン・ファーストアウト) 様様で読み出す。

20

#### 【0188】

有効フラグ格納領域90bに格納されるフラグFG(FG0-FGj)が有効状態を示すとき、この対応の消去アドレス格納領域90aに含まれる消去アドレスEAD(EAD0-EADj)が消去ブロックを指定するアドレスとしてEG制御回路70へ与えられ、指定された消去ブロックに対する消去が実行される。

20

#### 【0189】

図38は、この発明の実施の形態7におけるメモリアレイ内のメモリブロックの消去シーケンスを概略的に示す図である。メモリアレイ(メモリマット)20において、複数のメモリブロックが設けられる。ここで、メモリマットは、行デコーダおよび列選択ゲート回路により囲まれるメモリアレイの部分であり、単一のバンクを構成する部分を示す。

30

#### 【0190】

図38において、メモリブロックBKaに対してデータアクセスが行なわれるとき、消去アドレスレジスタファイル90において、ブロック1、BK2、BK4を特定する消去アドレスが順次格納され、メモリブロックBK3に対しては、消去非実行を示すスキップフラグ(リセット状態とされた有効フラグ)が格納される。この場合、メモリブロックBKaに対するデータアクセス(読み出または書き込み)と並行して、メモリブロックBK1、BK2に対する消去が行なわれ、メモリブロックBK3に対しては消去はスキップされて実行されない。メモリブロックBK3に対して割当てられた消去時間の経過後、メモリブロックBK4に対する消去が実行される。

30

#### 【0191】

スキップアドレスを消去アドレスレジスタファイルにおいて格納することにより、データアクセスのバックグラウンドで消去を行なう期間を停止させる。この消去アドレスおよびスキップアドレスは、外部からのコマンドにより指定される。

40

#### 【0192】

電源遮断時においては、消去アドレスレジスタファイル90に格納された未実行の消去アドレスが、メモリアレイ20の特定の領域に格納される。

#### 【0193】

図39は、この発明の実施の形態7における消去およびデータアクセス動作シーケンスを概略的に示す図である。すなわち、メモリアレイの図38に示すメモリブロックBKaに対するデータアクセスを実行中、メモリブロックBK1に対する消去(1)が実行される。消去ベリファイ動作時には、外部からの読み出しが禁止される。このベリファイ動作が完了し、メモリブロックBK1の消去が完了すると、次のメモリブロックB

50

K<sub>2</sub>に対する消去(2)が実行される。メモリブロックBK<sub>3</sub>が特定されるとき、そのメモリブロックは消去スキップブロックであり、消去は実行されない。この間を消去停止期間とし、所定期間経過後(消去が必要な期間)、次のメモリブロックBK<sub>4</sub>に対する消去(3)が実行される。

#### 【0194】

したがって、この外部からのデータアクセス(データ読出時)時、外部に対してほぼ消去動作見えなくすることができ、アクセス効率を改善することができる。

#### 【0195】

図40は、図36に示すコマンドレジスタ／制御回路24Bの構成を概略的に示す図である。図40に示すコマンドレジスタ／制御回路24Bは、以下の点で、図33に示すコマンドレジスタ／制御回路24Aの構成とその構成が異なる。すなわち、図40において、比較回路52Aからのデータアクセス活性化信号ENAが、消去制御部42へ与えられる。消去アドレスレジスタファイル90に対するアドレスおよびフラグの書き込みが、消去制御部42の制御の下に行なわれる。消去制御部42は、消去／スキップコマンドレジスタ41eeeからのコマンドに従って消去に必要な動作を制御する。

10

#### 【0196】

消去アドレスレジスタファイル90に対し、電源遮断検出制御部94と消去アドレスロード／セーブ制御部96が設けられる。電源遮断検出制御部94は、外部からの電源VDの遮断時に、消去アドレスロード／セーブ制御部96に電源遮断検出信号を与える。消去アドレスロード／セーブ制御部96は、電源遮断検出信号のアサート時、セーブ書き込みネーブル信号SWENをアサートして書き込み制御部75へ与え、電源回復時、ロード読出イネーブル信号LRENをアサートして読出制御部54Bへ与える。すなわち、消去アドレスロード／セーブ制御部96は、電源遮断および回復時の消去アドレスレジスタファイル90に対するデータの書き込みおよび読出を制御する。

20

#### 【0197】

書き込み制御部75Aは、書き込みモード指示Cwriteのアサート時の動作制御に加えて、セーブ書き込みイネーブル信号SWENのアサート時、書き込みモードイネーブル信号WRITEおよび書き込み動作活性化信号WRENをアサートし、消去アドレスレジスタファイル90に格納される消去アドレスおよびフラグのメモリアレイの所定のメモリ領域への書き込み動作を制御する。

30

#### 【0198】

読出制御部54Bは、ロード読出イネーブル信号LRENのアサート時、また読出モードイネーブル信号READおよび読出活性化信号RENNをアサートし、このロードされた消去アドレスおよびフラグのメモリアレイの所定の領域からの読出動作を制御する。この読出されたロード消去アドレスおよびフラグは、消去アドレスロード／セーブ制御部96により、消去アドレスレジスタファイル90に順次格納される。

#### 【0199】

なお、図40において、信号発生器84は設けられず、また、信号RYIBY\_ERは発生されなくてもよい。消去は、外部データアクセスのバックグラウンドで実行されるため、外部装置に対して消去パルス印加期間を報知することは特に要求されないためである。消去コマンドとして、通常の消去モードとバックグラウンドで消去を行なうバックグラウンド消去モードが準備されている場合には、信号RYIBY\_ERが利用されてもよい。

40

#### 【0200】

この図42に示すコマンドレジスタ／制御回路24Bの他の構成は、図33に示すコマンドレジスタ／制御回路24Aの構成と同じであり、対応する部分には同一参照番号を付し、その詳細説明は省略する。

#### 【0201】

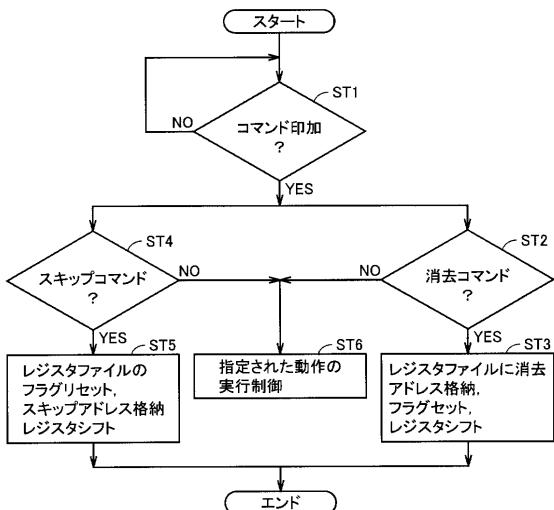

図41は、図40に示すコマンドレジスタ／制御回路24Bの消去アドレスレジスタファイル90への格納動作を示すフロー図である。以下、図41を参照して、図40に示すコマンドレジスタ／制御回路24Bの消去レジスタファイル格納動作について説明する。

50

**【0202】**

まず、コマンドレジスタ／制御回路24Bは、外部からコマンドが印加されるのを待つ（ステップS T 1）。外部からのコマンドが印加されると、消去制御部42は、この消去／スキップコマンドレジスタ41eeに格納されたコマンドが消去コマンドであるか（ステップS T 2）またはスキップコマンドであるか（S T 4）を判別する。

**【0203】**

与えられたコマンドが消去コマンドの場合（ステップS T 2）、消去制御部42は、与えられた消去アドレスを消去アドレスレジスタファイル90に格納するとともに、対応のレジスタの有効フラグFLGをセットする。消去アドレスレジスタへのアドレス格納およびフラグセット後、レジスタファイル90のレジスタのシフト動作を実行する（ステップS T 3）。

10

**【0204】**

一方、与えられたコマンドがスキップコマンドの場合（ステップS T 4）、消去制御部42は、レジスタファイル90にスキップアドレスを格納し、対応の有効フラグをリセット状態に維持する。この後、レジスタファイルのレジスタを1段シフトする。これにより、消去アドレスおよびスキップアドレス格納が完了する。このとき、単にスキップフラグのみが格納されてもよい（有効フラグをリセット状態に維持する）。次いで、レジスタを1段シフトする。

**【0205】**

与えられたコマンドが消去コマンド（バックグラウンド消去コマンドでもなく、また消去スキップコマンドでもない場合には（ステップS T 2 およびS T 4において判定結果がNOのとき）、このコマンドが指定する動作の実行を、書込コマンドレジスタ41wまたは読出コマンドレジスタ41rに格納される動作モード指示C w r i t e およびC r e a d のいずれかに従って、書込制御部75Aまたは読出制御部54Bにより、指定された動作の実行が制御される。

20

**【0206】**

消去アドレスレジスタファイル90がシフトレジスタで構成される場合、最終段のレジスタから先頭消去アドレスを読出すには、レジスタファイルのレジスタ段数コマンドが印加される必要がある。しかしながら、消去アドレスレジスタファイル90が、書込アドレスおよび読出アドレスに従ってFIFO態様でデータの書込および読出を行なう構成の場合、最初に1回格納された消去アドレスに従って消去を実行することができる。

30

**【0207】**

なお、消去コマンドとしては、外部から消去のみが指定されて通常の消去動作を行なうモードを指定する通常消去コマンドと、外部からのデータアクセスと並行してバックグラウンドモードで消去を行なうバックグラウンド消去モードを指定するコマンドがそれぞれ別々に設けられており、バックグラウンド消去コマンドが印加されたときに、消去アドレスレジスタファイル90への消去アドレスの格納動作が実行されるように構成されてもよい。

**【0208】**

図42は、図40に示すコマンドレジスタ／制御回路24Bのバックグラウンド消去モード時の動作を示すフロー図である。以下、図42を参照して、図40に示すコマンドレジスタ／制御回路24Bのバックグラウンド消去動作について説明する。

40

**【0209】**

消去制御部42は、消去アドレスレジスタファイル90から、最も古く格納されたレジスタの内容をレジスタのシフト動作により読出す（ステップS T 10）。このレジスタファイルから与えられたレジスタの内容に対して有効フラグがセット状態であるかリセット状態であるかの判定が行なわれる（ステップS T 11）。

**【0210】**

有効フラグがセット状態でなく、リセット状態の場合には、消去アドレスが指定するメモリブロックに対する消去は実行されない。所定期間の待機の後（ステップS T 12）、

50

再びステップ S T 1 0 に戻る。一方、有効フラグがセット状態の場合には、対応の消去アドレスが指定するメモリブロックに対する消去を実行する必要がある。このときには、先ず、比較回路 5 2 A において消去アドレスが示す消去対象ブロックとデータアクセスが行なわれているメモリブロックが同じであるかの判定が行なわれる（ステップ S T 1 3）。消去対象メモリブロックとデータアクセスメモリブロックとが同一の場合、この消去対象のメモリブロックに対する消去を行なうことができないため（アクセス対象のデータが変更されるため）、データアクセス（読み出または書き）が完了するのを待つ（ステップ S T 1 4）。このデータアクセス完了後、再びステップ S T 1 3 に戻る。

#### 【 0 2 1 1 】

一方、消去メモリブロックとデータアクセスメモリブロックとが異なるメモリブロックの場合には、その消去アドレスが指定するメモリブロックに対する消去を実行する（ステップ S T 1 5）。

#### 【 0 2 1 2 】

この消去が完了すると（ステップ S T 1 6）、再び、ステップ S T 1 0 に戻り、消去アドレスレジスタファイル 9 0 からのレジスタの内容のシフトアウト読み出以降の動作を実行する。これにより、データアクセスのバックグラウンドでデータアクセスメモリブロックと異なるメモリブロックに対する消去を実行することができる。

#### 【 0 2 1 3 】

また、スキップアドレスが指定するメモリブロックに対しては、有効フラグがリセット状態のとき、所定期間待機することにより、このスキップアドレスが指定するメモリブロックに対する消去期間消去を実行する必要がなく、不必要的消去を停止させて消費電流を低減する。

#### 【 0 2 1 4 】

なお、この図 4 0 に示すコマンドレジスタ／制御回路 2 4 B の構成においては、消去ベリファイ動作（V R 動作）においては、外部からのデータアクセスを停止させている。しかしながら、この場合、外部からのデータアクセスが完了するまで、消去ベリファイ動作を中断させて、データアクセス完了後、消去ベリファイを実行するように構成してもよい（実施の形態 6 参照）。

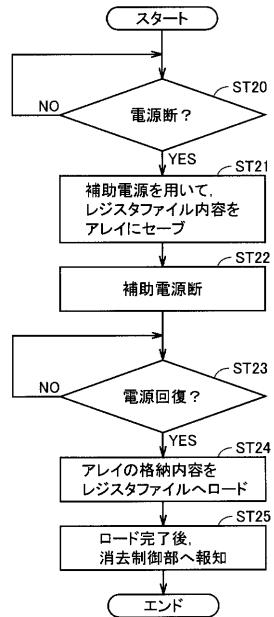

#### 【 0 2 1 5 】

図 4 3 は、図 4 0 に示すコマンドレジスタ／制御回路 2 4 B の電源遮断時の動作を示すフロー図である。以下、図 4 3 を参照して、図 4 0 に示すコマンドレジスタ／制御回路 2 4 B の電源遮断時の動作について説明する。

#### 【 0 2 1 6 】

電源遮断検出制御部 9 4 は、外部からの電源 V D D が遮断されたかを判断する（ステップ S T 2 0）。電源遮断時においては、例えば、外部の電源管理ユニットに設けられる電源切換回路により、補助電源に電源が切換えられる。この補助電源を用いて、消去アドレスロード／セーブ制御部 9 6 は、電源遮断検出制御部 9 4 からの電源遮断検出信号に従ってセーブ書き込みイネーブル信号 S W E N をアサートするとともに、消去アドレスレジスタファイル 9 0 から、各レジスタに格納された内容を読み出す。書き制御部 7 5 A が、セーブ書き込みイネーブル信号 S W E N に従ってイネーブルされ、所定のメモリアレイの領域に、消去アドレスレジスタファイル 9 0 から順次読み出されたレジスタ内容を格納する（ステップ S T 2 1）。

#### 【 0 2 1 7 】

消去アドレスロード／セーブ制御部 9 6 から、すべてのレジスタ内容のロードが完了したことが報知されると、外部の電源管理ユニットにおいて、補助電源を遮断する（ステップ S T 2 2）。次いで、この状態で、電源が回復するのを待つ（ステップ S T 2 3）。

#### 【 0 2 1 8 】

電源が回復すると、消去アドレスロード／セーブ制御部 9 6 は、電源遮断検出制御部 9 4 からの電源回復指示信号に従ってロード読み出イネーブル信号 L R E N をアサートして読み出制御部 5 4 B へ与える。読み出制御部 5 4 B は、ロード読み出イネーブル信号に従ってメモ

10

20

30

40

50

リアルイの所定領域にセーブされたレジスタ内容を読出す。この消去アドレスのセーブ／ロード時においては、特定のアドレス領域を指定するアドレスがこの消去アドレスロード／セーブ制御部96から発生されて図36に示すマルチプレクサ82を介してアドレスレジスタ22へ与えられて、特定のセーブ／ロード領域が指定される。

#### 【0219】

消去アドレスロード／セーブ制御部96は、この読み出制御部54Bの制御の下に読み出された消去アドレス、スキップアドレスおよびフラグを順次消去アドレスレジスタファイル90に格納する（ステップST24）。この消去アドレスレジスタファイル90へのレジスタ内容のロード完了後、消去アドレスロード／セーブ制御部96は、消去制御部42へ報知する（ステップST25）。この消去制御部42は、消去アドレスレジスタファイル90のロード完了指示に従って、バックグラウンドモードで、残りのアドレスが指定するメモリブロックに対する消去動作を実行する。10

#### 【0220】

なお、このバックグラウンドモードで消去を実行している際に、電源が遮断された場合、この中断された消去対象のメモリブロックは不完全な消去状態となる可能性がある。この場合、図40に示す消去ブロックアドレスレジスタファイル50に格納される消去ブロックアドレスも、併せてロード／セーブするように構成すればよい。電源回復後、再度この中断されたメモリブロックに対して消去を実行する。

#### 【0221】

以上のように、この発明の実施の形態7に従えば、データアクセス中に、バックグラウンドモードで消去をデータアクセスメモリブロックと異なるメモリブロックに対して実行している。これにより、データアクセスを中断させることなく内部で消去を実行することができる。したがって、消去時間を外部に対して隠すことができ、外部装置は、消去動作制御が不要となり、データアクセスを自由に実行することができる。20

#### 【0222】

##### [実施の形態8]

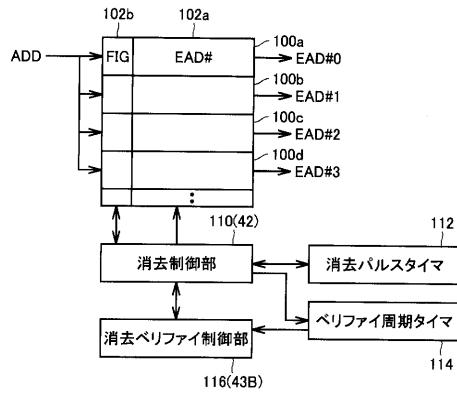

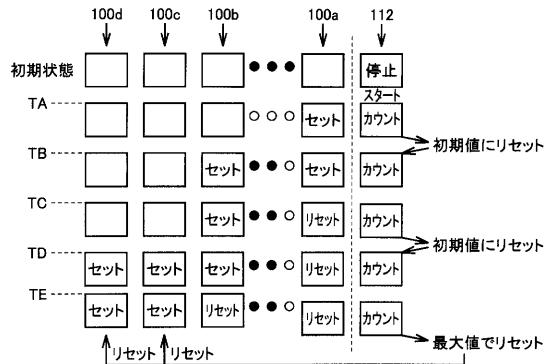

図44は、この発明の実施の形態8に従う半導体装置のコマンドレジスタ／制御回路の要部の構成を概略的に示す図である。図44において、コマンドレジスタ／制御回路は、複数の並列に設けられるレジスタ100a-100dと、消去パルスタイマ112、およびベリファイ周期タイマ114を含む。消去制御部110は、図35に示す消去制御部42に対応し、消去ベリファイ制御部116は、図35に示す消去ベリファイ制御部43Bに対応する。半導体装置全体の構成は、図36に示す半導体装置の構成と同じであり、メモリブロック単位で消去が実行され、異なるメモリブロックに対して消去およびデータアクセスを並行して実行することができる。30

#### 【0223】

レジスタ100e-100dは、各々、アドレス格納フィールド102aおよびフラグ格納フィールド102bを含む。

#### 【0224】

レジスタ100a-100dにおいては、消去用コマンドが印加されるごとに順次異なるレジスタに消去アドレスEADが格納されるとともに、有効フラグFLGがセットされる。これらのレジスタ100a-100dから並列に格納内容を読出することができる。40

#### 【0225】

消去パルスタイマ112は、消去メモリブロックに対する消去パルスの印加期間を規定し、新たな消去アドレスが与えられてフラグFLGがセットされるごとに、そのカウント値が初期値にリセットされて、この初期値から再度カウントする。

#### 【0226】

ベリファイ周期タイマ114は、この消去パルスタイマ112の最初のカウント開始からカウント動作を行ない、所定の周期でベリファイ開始を指示する。消去ベリファイ制御部116は、消去制御部110からの消去パルス電圧印加時、ベリファイ周期タイマ114からのベリファイ開始指示に従って消去ベリファイを、レジスタ100a-100dに50

格納される有効消去アドレスに対して実行する。この消去ペリファイが完了した消去メモリブロックに対しては対応のフラグ F L G がリセットされ、消去が完了したことが示される。

#### 【0227】

この消去完了指示は、また消去制御部 110 へ与えられ、このレジスタ 100a - 100d のフラグ格納フィールド 102b の対応のフラグ F L G をリセットする。消去制御部 110 は、このフラグのセット／リセットを制御するとともに、レジスタ 100a - 100d へのアドレスの格納および読出を管理する。

#### 【0228】

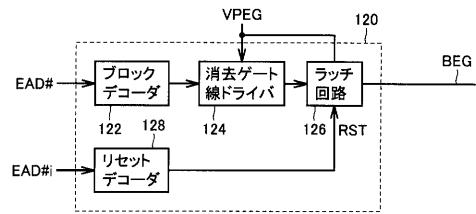

図 45 は、この発明の実施の形態 8 に従う半導体装置の E G 制御回路に含まれる消去ゲート線制御回路 120 の構成を概略的に示す図である。図 45において、消去ゲート線制御回路 120 は、ブロックデコーダ 122 と、消去ゲート線ドライバ 124 とラッチ回路 126 と、リセットデコーダ 128 とを含む。

10

#### 【0229】

ブロックデコーダ 122 は、レジスタ 100a - 100d に格納される消去アドレス E A D をデコードし、メモリブロックを指定するブロック選択信号を生成する。消去ゲート線ドライバ 124 は、消去高電圧 V P E G を受け、ブロックデコーダ 122 からのブロック選択信号に従ってブロック埋込消去ゲート線 B E G に対し、消去高電圧 V P E G を伝達する。ラッチ回路 126 は、メモリブロックそれぞれに対応して設けられ、対応のブロック埋込消去ゲート線 B E G の高電圧をラッチする。

20

#### 【0230】

リセットデコーダ 128 は、レジスタ 100a - 100d に格納される消去アドレス E A D 0 - E A D 3 のうち、消去の完了したブロックアドレス（消去アドレス）E A D i をデコードし、対応のメモリブロックに対して設けられたラッチ回路 126 に対しリセット信号 R S T を与える。ラッチ回路 126 は、リセット信号 R S T のアサートに従ってラッチ動作を停止する。したがって、このときには、ブロック埋込ゲート線 B E G は、消去ゲート線ドライバ 124 の出力信号に従ってフローティング状態または接地電圧レベルに維持される。

#### 【0231】

これにより、各メモリブロック単位で、ブロック埋込消去ゲート線 B E G を選択状態に駆動することができ、複数のメモリブロックにおいて並行して消去を実行することができる。また、リセットデコーダ 128 により、消去の完了したメモリブロックに対してのみリセット信号 R S T をアサートして、消去動作を停止させることができる。

30

#### 【0232】

図 46 は、この発明の実施の形態 8 に従う半導体装置のレジスタの格納内容と消去パルスタイミング 112 の動作の制御を概略的に示す図である。以下、図 46 を参照して、図 44 に示すコマンドレジスタ／制御回路の動作について説明する。

#### 【0233】

図 46において、初期状態では、レジスタ 100a - 100d は、すべてリセット状態にあり、また消去パルスタイミング 112 も動作停止状態にある。

40

#### 【0234】

時刻 T Aにおいて、バックグラウンド消去コマンドが印加されると、レジスタ 100a がセットされ、対応の消去アドレス（E D A ）が格納される。この時刻 T Aにおいて、最初にバックグラウンド消去モードが指示されると、消去パルスタイミング 112 がカウント動作を開始する。消去パルスタイミング 112 のカウント期間消去動作が行なわれ、消去パルス（消去高電圧）が対応のブロック埋込消去ゲート線に印加される。

#### 【0235】

時刻 T Bにおいて、再びバックグラウンド消去モードが指示され、レジスタ 100b がセットされ、対応の消去アドレスが格納される。この時刻 T Bにおける2回目のバックグラウンド消去モード指示に従って、消去パルスカウンタ 112 が初期値にリセットされ、

50

再び初期値からカウント動作を開始する。

【0236】

時刻T Cにおいて、レジスタ100aに格納される消去アドレスが指定するメモリブロックの対する消去が完了する（消去ベリファイの結果）。応じて、レジスタ100aがリセットされる（フラグFLGがリセットされる）。この時刻T Cにおいても、消去パルスタイム112はカウント動作を継続しており、レジスタ100bに格納された消去アドレスが指定するメモリブロックに対する消去が継続して実行される。

【0237】

時刻T Dにおいて、バックグラウンド消去コマンドが印加され、レジスタ100cおよび100dに消去アドレスがそれぞれ格納され、レジスタ100cおよび100dのフラグがセットされる。この時刻T Dにおけるレジスタ100cおよび100dのセットにより、再び、消去パルスタイム112がリセットされ、その初期値から再びカウント動作を開始する。

10

【0238】

時刻T Eにおいて、レジスタ100bに格納される消去アドレスが指定するメモリブロックが消去が完了し（消去ベリファイによる）、このレジスタ100bがリセットされる。このとき、まだレジスタ100cおよび100dに対する消去は行なわれており、消去パルスタイム112はカウント動作を継続する。消去パルスタイム112は、そのカウント値が予め定められた最大値に到達すると、消去パルス印加を停止し、レジスタ100cおよび100dをリセットする。

20

【0239】

以上のように、消去パルスタイム112のカウント値を、新たに消去アドレスがセットされるごとに初期値にリセットし、最長、カウント値が最大値に到達するまで消去パルスを印加する。複数のメモリブロックに対して並行して消去を行なうことができる。また、消去パルスタイム112のカウントが最大値に到達すると、消去電圧（パルス）の印加を停止させることにより、必要以上高電圧がメモリセルに印加されるのを防止することができ、消費電流が低減されるとともに絶縁膜の劣化を抑制することができる。

20

【0240】

消去高電圧が長期間にわたって印加され、メモリセルが過消去状態（メモリトランジスタがデプレッション状態）となっても、アシストゲートトランジスタ（選択トランジスタ）が存在しており、何ら問題は生じない。

30

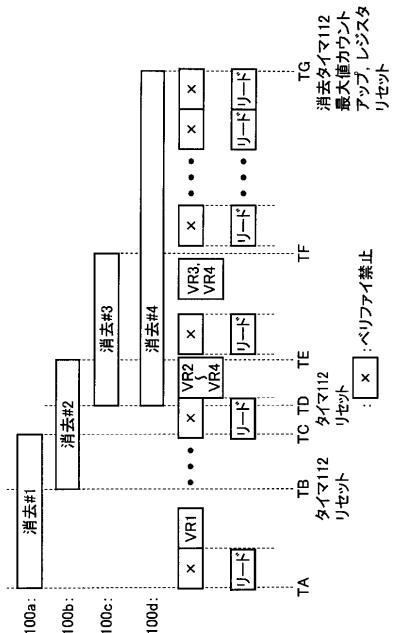

【0241】

図47は、図46に示す消去動作時に行なわれる外部アクセスの動作シーケンスの一例を示す図である。図47においては、外部からのデータアクセスとしてデータ読出を行うリード動作が一例として示される。以下、図47を参照して、この発明の実施の形態8に従う半導体装置の直列消去動作モードについて説明する。

【0242】

時刻T Aにおいて、バックグラウンド消去コマンドとともに消去アドレスが印加され、レジスタ100aに消去アドレスが格納され、このレジスタ100aに格納される消去アドレスが指定するメモリブロックに対する消去動作（1）が実行される。図44に示すタイミングマ112および114がカウント動作を開始する。このとき、外部からデータ読出アクセスが行なわれてあり、消去ベリファイ動作を実行することができない。外部データアクセス（リードアクセス）が完了すると、消去ベリファイ動作を、レジスタ100aに格納されたアドレスに従って行なうことができる。

40

【0243】

時刻T Bにおいて、新たなバックグラウンド消去コマンドが与えられ、レジスタ100bに消去アドレスが格納され、かつレジスタ100bのフラグがセットされる。この時刻T Bにおいて、消去パルスタイム112がリセットされ、再び初期値からカウント動作を実行する。レジスタ100aの消去アドレスが示すメモリブロックは、消去ベリファイ（VR1）において消去未完了と判断され、再度、消去パルスが印加される。このベリファイ

50

時においては、消去電圧印加と並行してベリファイ動作が実行されてもよい。

**【0244】**

以後、外部からのデータ読出アクセスが行なわれない期間に、図44に示すベリファイ周期タイマ114のカウント値に従って、消去ベリファイ動作が実行される。

**【0245】**

時刻TCにおいて、消去ベリファイ動作により、レジスタ100aに格納される消去アドレスが示すメモリブロックの消去が完了する。このとき、外部から読出アクセスが行なわれ、ベリファイ動作は禁止される。

**【0246】**

時刻TDにおいて、外部からのバックグラウンド消去コマンドに従って、レジスタ100cおよび100dに消去アドレスが格納され、これらのレジスタ100cおよび100dがセットされる。この時刻TDにおいて消去パルスタイマ112がリセットされ、再びタイマ112が初期値からカウント動作を継続する。

**【0247】**

外部からのデータ読出アクセスが完了すると、レジスタ100b - 100dに格納される消去アドレスに対する消去ベリファイVR2 - VR4が順次実行される。

**【0248】**

時刻TEにおいて、消去ベリファイ動作VR2により、レジスタ100bに格納される消去アドレスが示すメモリブロックに対する消去動作(2)が完了する。一方、レジスタ100cおよび100dの消去アドレスについては、消去ベリファイ動作により消去未完了と判断され、消去パルス(消去高電圧)が継続して印加される。

**【0249】**

この時刻TEの経過後、消去ベリファイ動作VR4の完了後、外部から読出アクセスが実行され、その読出アクセスの間、消去ベリファイが禁止される。外部読出アクセスが存在しなくなると、レジスタ100cおよび100dに格納される消去アドレスのメモリブロックに対する消去ベリファイ動作(VR3, VR4)が実行される。

**【0250】**

時刻TFにおいて、消去ベリファイ動作VR3により、レジスタ100cに格納される消去アドレスが示すメモリブロックの消去動作が完了する。以降、外部からのデータ読出アクセス(リード)が連続して実行され、レジスタ100dに格納される消去アドレスが指定するメモリブロックに対して継続的に消去パルス(消去高電圧)が印加され、消去ベリファイ動作は実行されない。

**【0251】**

時刻TGにおいて、消去パルスタイマ112のカウント値が最大値に到達すると、消去パルス印加が停止され、レジスタ100dのアドレスがリセットされ、消去動作が停止する。この消去の中止は、外部に対して信号で報知されてもよい。

**【0252】**

図44に示すベリファイ消去タイマ114を用いて、外部からのデータアクセスが行なわれていない期間、消去ベリファイ動作を実行する。これにより、外部からは、データアクセスを継続して行ない、外部に対し、内部で実行される消去動作を隠すことができ、データアクセスを容易に行なうことができる。

**【0253】**

制御回路の構成としては、先の図35に示す構成を用い、また、図40に示す電源遮断検出制御部(94)および消去アドレスロード/セーブ制御部(96)を利用する。これにより、電源遮断時において、レジスタ100a - 100dに格納される消去アドレスを、メモリアレイの特定の領域にセーブして、電源回復時に再びこれらのレジスタ100a - 100dにロードすることができる。

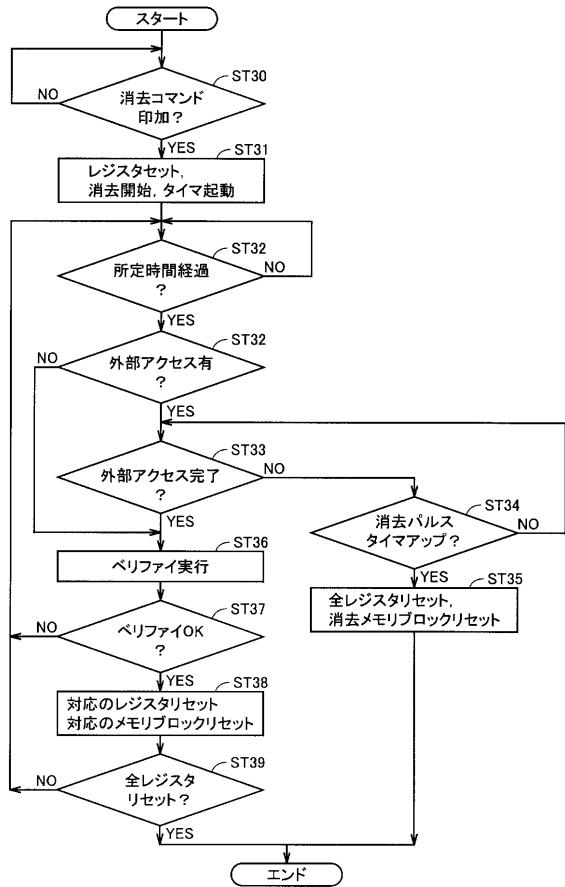

**【0254】**

図48は、図44に示すコマンドレジスタ/消去制御回路の動作を示すフロー図である。以下、図48を参照して、図44に示すコマンドレジスタ/消去制御回路の動作につい

10

20

30

40

50

て説明する。このコマンドレジスタ／消去制御回路は、コマンドレジスタ／制御回路 24B（または 24A）の消去動作制御に関連する部分を示す。

#### 【0255】

まず、消去コマンドが印加されるのを待つ（ステップ ST 30）。消去コマンドが印加されると、消去制御部 110 は、与えられたアドレスを消去レジスタに格納するとともに、フラグ F L G をセットする。また、消去コマンド印加に従って消去パルスタイミング 112 を初期値に設定して起動する。また、この消去コマンドが最初に与えられると、ベリファイ周期タイミング 114 を起動する。消去コマンドとともに与えられた消去アドレスに従って、消去制御部 110 は、図 45 に示す E G 制御回路 120 においてブロックデコーダ 122 へ消去アドレス（E A D）を与え、指定されたメモリブロックに対する消去動作を実行する（ステップ ST 31）。

10

#### 【0256】

この消去動作開始後、消去ベリファイ制御部 116 は、消去制御部 110 によりイネーブルされ、ベリファイ周期タイミング 114 のカウント値が所定値に到達するのを待つ（ステップ ST 32）。

#### 【0257】

図 44 に示すベリファイ周期タイミング 114 のカウント値が所定値に到達し、ベリファイ動作を実行する場合、まず、消去制御部 110 は、外部アクセスが存在するかを識別する（ステップ ST 32）。これは、図 35 に示す制御回路動作と同様、書き動作モード指示信号 W R I T E または読み出動作モード指示信号 R A D がアサートされているかを基に判別される。

20

#### 【0258】

外部アクセスが存在する場合、外部アクセスの完了かどうかを判別する（ステップ ST 33）。外部アクセスが完了しないで継続して実行されている場合、次いで、消去制御部 110 は、消去ベリファイ制御部 116 のベリファイ開始を待たせて、消去パルスタイミング 112 のカウント値が最大値に到達したかを識別する（ステップ ST 30）。消去パルスタイミング 112 がまだカウントアップしていない場合には、ステップ ST 33 に戻って外部アクセスが完了するのを待つ。一方、ステップ ST 34 において、消去パルスタイミング 112 がカウントアップを完了した場合には、消去制御部 110 は、レジスタ 100a - 100d をすべてリセットし、また、フラグ F L G もリセットする（ステップ ST 35）。これにより、消去動作が完了する。

30

#### 【0259】

ステップ ST 32 において外部アクセスが存在しないかまたはステップ ST 33 において外部アクセスが完了すると、消去制御部 110 が、消去ベリファイ制御部 116 をイネーブルする。レジスタ 100a - 100d に格納される有効フラグがセットされた消去アドレスが逐次読み出され、消去メモリブロックにおいてベリファイカウンタ（図 35）からのベリファイアドレスに従って、メモリブロックのメモリセルを逐次読み出して消去ベリファイ動作を実行する。このとき、電圧発生部においては、消去ベリファイに必要なベリファイ電圧が選択されて行および列デコーダ（列選択ゲート回路に含まれる列デコーダ）へ与えられてメモリセルデータの読み出しが実行される。このベリファイカウンタは、一例として、読み出された消去アドレスをブロックアドレスとして保持し、このメモリブロック内のアドレスを順次そのカウント値に従って生成する。これにより、消去メモリブロックに対するブロックアドレスおよびメモリセルアドレスを生成することができる。

40

#### 【0260】

消去ベリファイ制御部 116 は、読み出されたデータの論理値をモニタし、すべてのメモリセルの記憶データが消去状態にあるかを識別し、その識別結果に従って対応のメモリブロックが消去状態にあるかを識別する（ステップ ST 37）。対応のメモリブロックがまだすべて消去状態にない場合には、消去ベリファイ制御部 116 は、消去継続を消去制御部 110 に知らせる。消去制御部 110 は、ステップ ST 32 へ戻り、ベリファイ周期カウンタ 114 のカウント値に従って所定のベリファイ周期が完了するのを待つ。

50

**【0261】**

一方、ステップS T 3 7における消去ベリファイで、全てのメモリセルが消去状態であると識別された場合には、消去制御部110は、レジスタ100a - 100dのうちの対応のレジスタをリセットし、また、図45に示すリセットデコーダ128へ対応の消去アドレスE A D iを与える、対応のメモリブロックの消去高電圧をリセットする(ステップS T 3 9)。

**【0262】**

レジスタ100a - 100dがすべてリセット状態にある場合には(ステップS T 3 9)、消去制御部110は、消去動作を完了させる。一方、すべてのレジスタがリセット状態にない場合には、再び、ステップS T 3 2へ戻り、消去制御部110は、消去パルスターイマ112のカウント値をモニタしつつ消去高電圧を継続して生成させて、E G選択回路120へ与える。10

**【0263】**

以上のように、この図44に示すコマンドレジスタ/消去制御回路、より具体的には図35に示す制御回路および図40に示す電源遮断検出制御部および消去アドレスロード/セーブ制御部を利用することにより、複数のメモリブロックに対して並行して消去動作を行なうとともに、電源遮断時、このレジスタに格納された消去アドレスを特定のメモリ領域へ格納することができる。

**【0264】**

電源遮断時におけるレジスタ100a - 100dの内容のセーブおよびロード動作は、20図43に示すフロー図と同様の動作制御が、消去アドレスロード/セーブ制御部により実行される。

**【0265】**

以上のように、この発明の実施の形態8に従えば、複数のメモリブロックに対し並行して、消去動作を行なうように構成しており、また、外部アクセスを優先させている。したがって外部に対して内部で実行される消去動作を完全に隠すことができ、データアクセスの制御が容易となる。

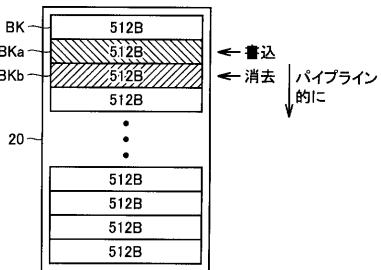

**【0266】****[実施の形態9]**

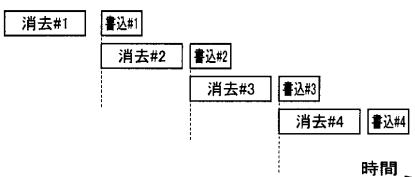

図49は、この発明の実施の形態9に従う半導体装置のメモリブロックへのアクセス様式を概略的に示す図である。図49においてメモリアレイ20には、複数のメモリブロックにおいて、パイプライン的に書き込みおよび消去を異なるメモリブロックに対して並行して実行する。30

**【0267】**

いま、メモリブロックB K bに対して消去を行なっているとき、メモリブロックB K aに並行して書き込みを実行する。このメモリブロックB K bの消去完了後、次に書き込み指示が与えられると、次のメモリブロックB K A aに対する消去動作と並行してメモリブロックB K bに対する書き込みを実行する。すなわち、書き込みは、常に消去が行なわれたメモリブロックに対して実行される。

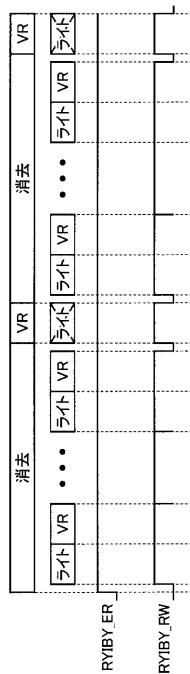

**【0268】**

図50は、この発明の実施の形態9に従う半導体装置のアクセスシーケンスの一例を示す図である。図50において、水平方向に整列して配置されるメモリブロックは同一メモリブロックを示す。40

**【0269】**

図50において、まず1つのメモリブロックにおいて消去が実行される。続いて、書き込みおよび消去を同時に行なうコマンド(または、単なる書き込みコマンド)が印加され、異なるメモリブロックに対して消去および書き込みが並行して実行される。以後、複数のメモリブロックにおいて、消去後メモリブロックに対し書き込みが実行される。

**【0270】**

書き込みおよび消去をパイプライン的に実行する。書き込みが、消去メモリブロックに対して行

10

20

30

40

50

なわれるため、高速にデータの書き込みを行なうことができる。特に、ファームウェアなどの大量のデータを一度に書き換える場合、高速に書き換えを行なうことができる。また、SRA M(スタティック・ランダム・アクセス・メモリ)からのデータのセーブを高速で行なうことができる。

#### 【0271】

なお、図50に示す動作シーケンスにおいて書き込みおよび消去時においては、ベリファイ動作が実行される。このベリファイに対しては、書きベリファイおよび消去ベリファイは、異なるタイミングで、すなわち異なる時間において実行することが要求される。

#### 【0272】

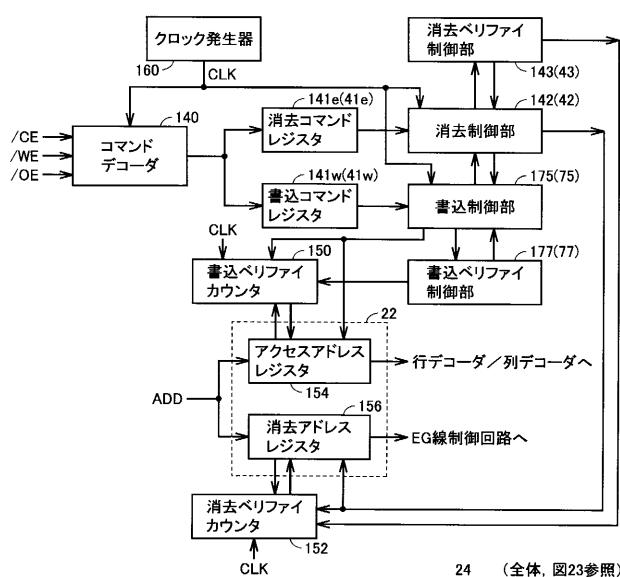

図51は、この発明の実施の形態9に従う半導体装置のコマンドレジスタ／制御回路24の構成を概略的に示す図である。この発明の実施の形態9に従う半導体装置の全体の構成は、図23に示す半導体装置の構成と同じである。10

#### 【0273】

図51において、コマンドレジスタ／制御回路24において、コマンドデコーダ140、消去コマンドレジスタ141eおよび書きコマンドレジスタ141w、消去制御部142、書き制御部175、消去ベリファイ制御部143、書きベリファイ制御部177が設けられる。

#### 【0274】

コマンドデコーダ140は、クロック発生器160からの内部クロック信号CLKに同期して外部からの制御信号/C\_E、/W\_Eおよび/O\_Eがある動作モードを指定しているとき、アドレスADDおよびデータDQから与えられたコマンドをデコードし、そのデコード結果を、デコード結果に従って、消去コマンドレジスタ141eおよび書きコマンドレジスタ141wのいずれかに与える。20

#### 【0275】

消去コマンドレジスタ141eは、図28に示す消去コマンドレジスタ41eに対応し、コマンドデコーダ140からのデコード後の消去コマンドを格納する。書きコマンドレジスタ141wは、図28に示す書きコマンドレジスタ41wに対応し、コマンドデコーダ140からのデコード後の書きコマンドを格納する。

#### 【0276】

消去制御部142は、図28に示す消去制御部42に対応し、消去コマンドレジスタ141eに格納される消去コマンドに従って消去に必要な動作を制御する。消去ベリファイ制御部143は、図28に示す消去ベリファイ制御部43に対応し、消去制御部142からの消去電圧印加時、所定のシーケンスで消去ベリファイ動作を制御し、消去ベリファイ完了時、消去制御部142に消去電圧印加動作を停止させる。30

#### 【0277】

書き制御部175は、図28に示す書き制御部75に対応し、書きコマンドレジスタ141wに格納される書きコマンドに従って書き動作を制御する。

#### 【0278】

書きベリファイ制御部177は、図28に示す書きベリファイ制御部77に対応し、書き制御部176からの書き完了指示に従ってインエーブルされて書きベリファイ動作を制御する。書きベリファイ制御部177は、書きデータを保持する書きデータレジスタを含み、書きベリファイにより正確にメモリセルに対してデータ書き込みが行なわれることを検出すると、書き制御部175に対し、書き動作を停止させる。40

#### 【0279】

この図51に示すコマンドレジスタ／制御回路24においては、さらに、書きベリファイカウンタ150、および消去ベリファイカウンタ152が設けられる。アドレスレジスタ22内において、アクセスアドレスレジスタ154および消去アドレスレジスタ156が設けられる。

#### 【0280】

アクセスアドレスレジスタ154は、書き制御部175からの制御のもとに、外部から

10

20

30

40

50

のアドレス信号 ADD をアクセスアドレスとして格納する。データ書込時、アクセスアドレスレジスタ 154 に格納された書込アドレスを先頭アドレスとしてベリファイを行うため、書込制御部 175 は、書込ベリファイカウンタ 152 の初期値として格納する。ここで、書込は連続アドレスに対して実行されるアクセスシーケンスを想定している。

#### 【0281】

書込ベリファイカウンタ 150 は、書込ベリファイ制御部 177 の制御のもとに、クロック信号 CLK に同期して書込ベリファイカウントを順次更新し、書込ベリファイアドレスを生成し、アクセスアドレスレジスタ 154 へ与える。これにより、アクセスアドレスレジスタ 154 に格納されたベリファイアドレスが、図示しない行デコーダおよび列デコーダへ与えられ、メモリセルの選択およびデータ読出が実行される。10

#### 【0282】

消去アドレスレジスタ 156 は、消去制御部 142 からの指示に従って、アドレス信号 ADD を消去アドレスとして格納するとともに、その格納した消去アドレスを消去ベリファイカウンタ 152 にカウント初期値として格納する。この消去アドレスはメモリブロックを指定しており、消去ベリファイカウンタの上位ビット位置にベリファイブロックアドレスとして格納され、カウント動作により、このメモリブロック内のメモリセルが順次指定される。

#### 【0283】

消去ベリファイカウンタ 152 は、消去制御部 142 の制御のもとに、この消去アドレスレジスタ 156 に格納されたアドレスを先頭値として格納するとともに、消去ベリファイ制御部 123 の制御のもとに、消去ベリファイ時、内部クロック信号 CLK に同期してそのカウント値を更新する。消去アドレスレジスタ 156 に格納される消去アドレスが EG 線制御回路へ与えられ、消去高電圧を印加するメモリブロックに対するロック埋込消去ゲート線 (BEG) へ消去高電圧が印加される。20

#### 【0284】

なお、この図 51 に示すコマンドレジスタ / 制御回路 24 において、図 28 に示す構成と同様、読出制御部 54 (A) が設けられ、消去ベリファイ制御部 143 および書込ベリファイ制御部 177 の制御のもとに、ベリファイカウンタのカウント値がマルチプレクサを介してデコーダへ与えられ、ベリファイ読出が実行される。

#### 【0285】

この図 51 に示すコマンドレジスタ / 制御回路 24 の構成において、書込制御部 175 および消去制御部 142 は、それぞれ消去ベリファイおよび書込ベリファイが完了するまで、次の書込および消去動作を停止させる。消去ベリファイおよび書込ベリファイが完了すると、消去制御部 142 および書込制御部 175 は、アクセスアドレスレジスタ 154 および消去アドレスレジスタ 156 に、外部から与えられるアドレスをそれぞれ格納し、クロック信号 CLK に同期して消去および書込を並行して実行する。30

#### 【0286】

なお、このパイプライン態様でのデータアクセスは、所定の消去および書込時間が規定され、外部からの装置は、その所定間隔で、消去および書込コマンドを印加するとともに、消去アドレスおよび書込アドレスを印加する。40

#### 【0287】

また、アクセスアドレスレジスタ 150 および消去アドレスレジスタ 156 が、複数のレジスタで構成され、 FIFO 態様でその格納アドレスを読出す構成とされてもよい。この場合、内部で、消去ベリファイおよび書込ベリファイがともに完了した後、アドレスレジスタ (FIFO) の格納値を更新して次のメモリブロックに対する消去および書込を実行する。

#### 【0288】

さらに、書込および消去の完了後に消去アドレスレジスタ 156 の格納するアドレスが書込アドレスレジスタ 154 に転送され、外部から書込アドレスが与えられると消去アドレスレジスタ 156 に格納されて、消去および書込が実行されてもよい。この場合、デー

10

20

30

40

50

タ書込もメモリブロック単位でブロック内の先頭アドレスから実行することが要求される。

#### 【0289】

以上のように、この発明の実施の形態9に従えば、パイプライン様で書込および消去を並行して実行しており、大量のファームウェアなどのデータを高速で書換えることができる。

#### 【0290】

また、書込時においては、消去が完了したメモリブロックに対する書込が実行されており、書込前に対応のメモリブロックの消去を行なう必要がなく、高速のデータ書込が実現される。

10

#### 【0291】

##### [変更例1]

図52は、この発明の実施の形態9に従う半導体装置のアクセスシーケンスの変更例を示す図である。この図52に示すアクセスシーケンスにおいては、2つのメモリブロックに対し並行して消去が行なわれる。その消去と並行して、消去後のメモリブロックに対してメモリブロックごとに書込が行なわれる。すなわち、図52において、メモリブロック

1および2に対し並行して消去が行なわれる。次のサイクルにおいて、メモリブロック3および4において消去が行なわれ、これと並行してメモリブロック1、2に対して順次書込が実行される。次のサイクルにおいては、消去されたメモリブロック3および4に対する書込が順次実行される。消去および書込はパイプライン的に実行される。

20

#### 【0292】