(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6528640号

(P6528640)

(45) 発行日 令和1年6月12日(2019.6.12)

(24) 登録日 令和1年5月24日(2019.5.24)

|               |              |

|---------------|--------------|

| (51) Int.Cl.  | F 1          |

| HO 1 L 29/78  | (2006.01)    |

| HO 1 L 29/12  | (2006.01)    |

| HO 1 L 21/336 | (2006.01)    |

|               | HO 1 L 29/78 |

|               | HO 1 L 29/78 |

|               | HO 1 L 29/78 |

請求項の数 5 (全 14 頁)

(21) 出願番号 特願2015-208171 (P2015-208171)

(22) 出願日 平成27年10月22日 (2015.10.22)

(65) 公開番号 特開2017-84839 (P2017-84839A)

(43) 公開日 平成29年5月18日 (2017.5.18)

審査請求日 平成30年1月22日 (2018.1.22)

(73) 特許権者 000006013

三菱電機株式会社

東京都千代田区丸の内二丁目7番3号

(74) 代理人 100082175

弁理士 高田 守

(74) 代理人 100106150

弁理士 高橋 英樹

(74) 代理人 100148057

弁理士 久野 淑己

(72) 発明者 香川 泰宏

東京都千代田区丸の内二丁目7番3号 三菱電機株式会社内

(72) 発明者 田中 梨菜

東京都千代田区丸の内二丁目7番3号 三菱電機株式会社内

最終頁に続く

(54) 【発明の名称】半導体装置及びその製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

半導体基板と、

前記半導体基板上に設けられた第1導電型のドリフト層と、

前記ドリフト層の表面側に位置する第2導電型の第1のベース領域と、

前記第1のベース領域内に位置する第1導電型のソース領域と、

前記第1のベース領域と前記ソース領域を貫通し、複数の面からなるトレンチ側壁を有し、格子状に形成されたトレンチと、

前記トレンチ内の前記トレンチ側壁に接して形成されたゲート絶縁膜と、

前記トレンチ内に前記ゲート絶縁膜を介して埋め込まれたゲート電極と、

前記トレンチの交差部における角部に接する箇所に、前記角部以外の前記トレンチ側壁に接する箇所に形成された前記第1のベース領域の不純物濃度よりも高い不純物濃度を有する、第2導電型の第2のベース領域とを備え、

前記第2のベース領域は前記トレンチ側壁から0.1 μm ~ 0.5 μmの幅を持って形成されることを特徴とする半導体装置。

## 【請求項 2】

前記第2のベース領域の第2導電型不純物濃度は、前記第1のベース領域の第2導電型不純物濃度より  $5 \times 10^{16} \text{ cm}^{-3}$  以上高いことを特徴とする請求項1に記載の半導体装置。

## 【請求項 3】

10

20

前記半導体基板が炭化珪素半導体装置であり、前記ドリフト層が炭化珪素で構成されていることを特徴とする請求項 1 又は 2 に記載の半導体装置。

【請求項 4】

半導体基板上に、第 1 導電型のドリフト層となる第 1 導電型のエピタキシャル層を成長する工程と、

前記エピタキシャル層の表層部に第 2 導電型の第 1 のベース領域を形成する工程と、

前記第 1 のベース領域の表層部に第 1 導電型のソース領域を形成する工程と、

前記ドリフト層内に第 1 のベース領域より不純物濃度が高い、第 2 導電型の第 2 のベース領域を形成する工程と、

前記第 1 のベース領域と前記ソース領域を貫通するトレンチを、格子状に、前記トレンチの交差部における角部が前記第 2 のベース領域に接するように、前記第 2 のベース領域よりも深く、エッティングにより形成する工程と、

前記トレンチ内のトレンチ側壁に接するようにゲート絶縁膜を形成する工程と、

前記トレンチ内に前記ゲート絶縁膜を介してゲート電極を埋め込む工程と、

を備え、

前記第 2 のベース領域は前記トレンチ側壁から 0.1 μm ~ 0.5 μm の幅を持って形成される半導体装置の製造方法。

【請求項 5】

前記半導体基板と前記ドリフト層が炭化珪素で構成されていることを特徴とする請求項 4 に記載の半導体装置の製造方法。

【発明の詳細な説明】

【技術分野】

【0001】

この発明は、トレンチゲート構造の絶縁ゲート型半導体装置に関するものである。

【背景技術】

【0002】

パワーエレクトロニクス分野において、モータ等の負荷への電力供給を制御するスイッチング素子として、IGBT (Insulated Gate Bipolar Transistor) やMOSFET (Metal Oxide Semiconductor Field Effect Transistor)などの半導体装置が広く使用されている。電力制御用の絶縁ゲート型半導体装置の一つに、ゲート電極が半導体層に埋め込まれて形成されたトレンチゲート型MOSFETがある。

【0003】

トレンチゲート型MOSFETでは、チャネル密度を向上させることによって低抵抗化を実現することが可能であり、特許文献 1 に記載のトレンチゲート型MOSFETではトレンチを格子状に形成し、低抵抗化を実現している。

ここで、トレンチゲート型MOSFETでは、トレンチ内にゲート絶縁膜を介して、ポリシリコン等からなるゲート電極を埋め込む構造となっており、トレンチに接するベース領域にチャネルを形成する。このトレンチゲート型MOSFETをオンさせるために、ゲート電極にベース領域が反転する電圧を印加し、ゲート電極に印加された電圧がゲート絶縁膜を介してベース領域に印加する。この電圧によって発生する電界によって、ベース領域内にチャネルが形成される。

【先行技術文献】

【特許文献】

【0004】

【特許文献 1】特表 2007 - 531246 号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

トレンチを格子状に形成したトレンチゲート型MOSFETでは、格子によって交差部

10

20

30

40

50

が発生する。交差部のチャネルには角部が存在する。ゲート電極に電圧を印加した場合、チャネルの角部には電界が集中することとなり、角部以外のゲート絶縁膜よりも大きな電界が印加される。したがって、角部のチャネルはそれ以外の箇所と比べて先にオン状態になってしまう。素子全体の閾値電圧は最も早くオン状態になった箇所で決まるため、結果として、素子全体の閾値電圧が低下してしまい、オン抵抗と閾値電圧のトレードオフの関係が悪化するとともに、低閾値電圧化によってシステムの誤動作を誘発する場合があった。

#### 【0006】

本発明は、上述のような問題を解決するためになされたもので、チャネル密度の大きな格子状のトレンチ構造を保持したまま、交差部の角部が先にオン状態となり、閾値電圧が低下するのを防ぎ、オン抵抗と閾値電圧のトレードオフの関係を改善した半導体装置を提供することを目的とする。10

#### 【課題を解決するための手段】

#### 【0007】

本発明にかかる半導体装置は、半導体基板と、半導体基板上に設けられた第1導電型のドリフト層と、ドリフト層の表面側に位置する第2導電型の第1のベース領域と、第1のベース領域内に位置する第1導電型のソース領域と、第1のベース領域とソース領域を貫通し、複数の面からなるトレンチ側壁を有し、格子状に形成されたトレンチと、トレンチ内のトレンチ側壁に接して形成されたゲート絶縁膜と、トレンチ内にゲート絶縁膜を介して埋め込まれたゲート電極と、トレンチの交差部における角部に接する箇所には、角部以外のトレンチ側壁に接する箇所に形成された第1のベース領域の不純物濃度よりも高い不純物濃度を有する、第2導電型の第2のベース領域とを備え、前記第2のベース領域は前記トレンチ側壁から $0.1\text{ }\mu\text{m} \sim 0.5\text{ }\mu\text{m}$ の幅を持って形成されることを特徴とするものである。20

#### 【発明の効果】

#### 【0008】

本発明にかかる半導体装置によれば、角部のゲート絶縁膜に接するベース領域の不純物濃度を角部以外より高くしているため、角部近傍に形成されるチャネルの部分的な閾値電圧を高くすることができ、角部が先にオン状態になるのを防ぐことができる。また、角部以外のチャネルを適切な閾値電圧に設定することができ、オン抵抗と閾値電圧のトレードオフを改善することができる。30

#### 【図面の簡単な説明】

#### 【0009】

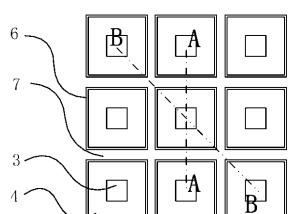

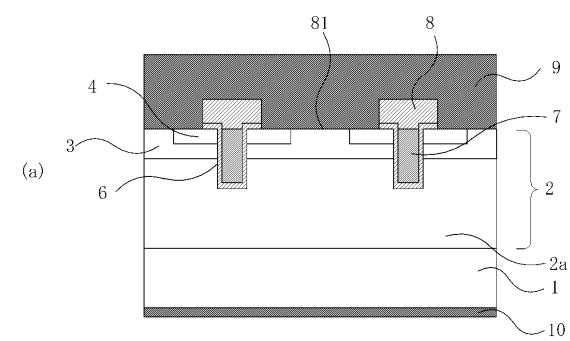

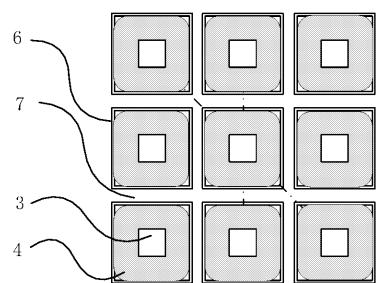

【図1】この発明の実施の形態1に係るトレンチゲート型MOSFETの活性領域の一部を示す上面図である。

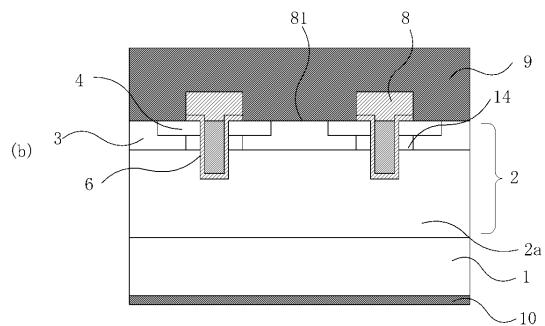

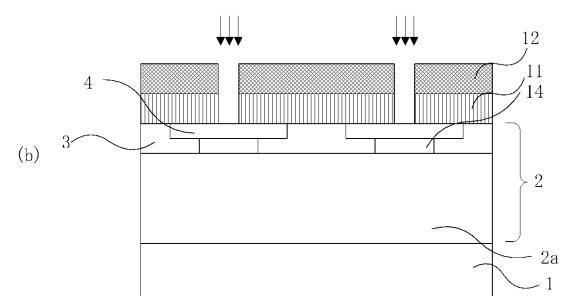

【図2】この発明の実施の形態1に係るトレンチゲート型MOSFETの活性領域の一部の断面図である。

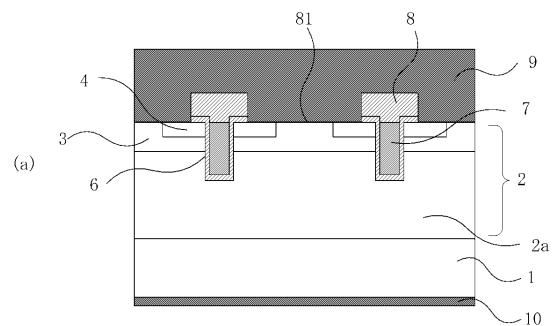

【図3】この発明の実施の形態1に係るトレンチゲート型MOSFETのオン状態における電圧電流特性を示す図である。

【図4】この発明の実施の形態1に係るトレンチゲート型MOSFETの製造方法を説明するための断面模式図である。40

【図5】この発明の実施の形態1に係るトレンチゲート型MOSFETの製造方法を説明するための断面模式図である。

【図6】この発明の実施の形態1に係るトレンチゲート型MOSFETの製造方法を説明するための断面模式図である。

【図7】この発明の実施の形態1に係るトレンチゲート型MOSFETの製造方法を説明するための断面模式図である。

【図8】この発明の実施の形態1に係るトレンチゲート型MOSFETの製造方法を説明するための断面模式図である。

【図9】この発明の実施の形態1に係るトレンチゲート型MOSFETの製造方法を説明50

するための断面模式図である。

【図10】この発明の実施の形態1に係るトレンチゲート型MOSFETの製造方法を説明するための断面模式図である。

【図11】この発明の実施の形態1に係るトレンチゲート型MOSFETの製造方法を説明するためのセル領域の一部の上面図である。

【図12】この発明の実施の形態2に係るトレンチゲート型MOSFETの活性領域の一部の断面図である。

【図13】この発明の実施の形態2に係るトレンチゲート型MOSFETの活性領域の一部の上面図である。

#### 【発明を実施するための形態】

10

#### 【0010】

##### 実施の形態1.

まず、本発明の実施の形態1にかかる半導体装置の構成を説明する。

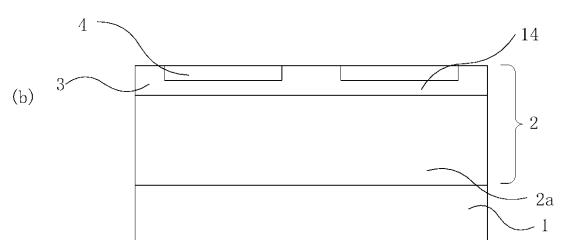

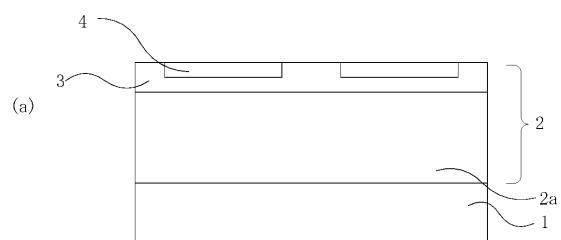

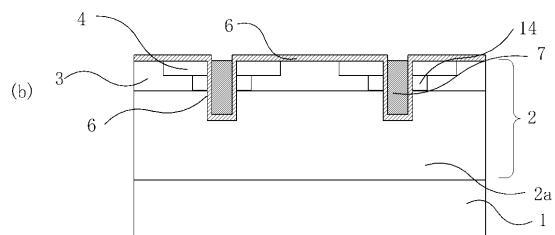

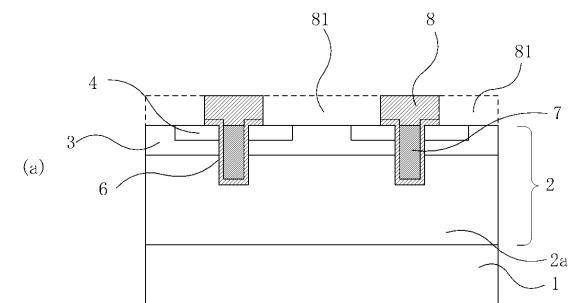

図1は、実施の形態1にかかる半導体装置であるトレンチゲート型MOSFETの活性領域の一部を模式的に示す上面図である。図1に示すように、本実施の形態のトレンチゲート型MOSFETの活性領域には、上面から見て正方形のセルが9個並んで配置されている部分がある。また、図2は、実施の形態1に係るトレンチゲート型MOSFETの活性領域の一部を模式的に示す断面図であり、図1の一点鎖線で示されるA-A断面図が図2(a)に対応し、図1の二点鎖線で示されるB-B断面図が図2(b)に対応する。ここで、B-B断面図は格子状に並ぶトレンチの交差部の特に角部を含む断面図となっている。

20

なお、図1においては、トレンチゲート型MOSFETのセルの構成が分かりやすいように、ソース電極、層間絶縁膜及びコンタクトホールは省略して示している。

#### 【0011】

本実施の形態にかかるトレンチ型MOSFETのセルの構成を、図1及び図2を参照して説明する。

本発明の実施の形態1に係る半導体装置であるトレンチ型MOSFETにおいては、低抵抗でn型の炭化珪素半導体基板1の第1の主面上に炭化珪素からなるn型のエピタキシャル層2が形成されている。エピタキシャル層2の表層部の一部には、炭化珪素からなるp型の第1のベース領域3が形成されている。エピタキシャル層2のうち、第1のベース領域3が形成されていない第1のベース領域3の下方の領域がドリフト層2aとなる。

30

#### 【0012】

第1のベース領域3の表層部の一部にはn型のソース領域4が形成されている。第1のベース領域3およびソース領域4が形成された箇所のエピタキシャル層2に、ソース領域4と第1のベース領域3を貫通するように、トレンチ5が形成されている。トレンチ5は、上面から見て縦横に交差して、格子状に形成されている。隣接するトレンチ5との間は等間隔である。トレンチ5の底部は、第1のベース領域3より下方のドリフト層2aに達している。トレンチの内部には、底部と側壁を含む内壁を覆うように内壁に接してゲート絶縁膜6が形成されている。ゲート絶縁膜6のトレンチ内壁と反対側である内側には、ゲート電極7が形成されている。

40

#### 【0013】

エピタキシャル層2の表面には、ゲート電極7を覆うように層間絶縁膜8が形成されている。層間絶縁膜8には、ソース領域4および第1のベース領域3に達するコンタクトホール81が形成されている。層間絶縁膜8上に設けられたソース電極9はこのコンタクトホール81を埋めるように形成され、ソース領域4及び第1のベース領域3に接続される。なお、上述したとおり、図1ではエピタキシャル層2上の層間絶縁膜8、ソース電極9、コンタクトホール81を省略しているので、図1ではコンタクトホール81が示されていないが、図2に断面が示されたコンタクトホール81は、上面視で矩形の空間となっている。

また、炭化珪素半導体基板1の第1の主面の反対側の面である第2の主面には、ドレイ

50

ン電極 10 が形成されている。

**【0014】**

図 1 に示すように、ゲート電極 7 は、上面視で格子状に配設されている。トレンチゲートMOSFET の活性領域内に設けられるセルでは、ゲート電極 7 で区切られた区画のそれぞれがトレンチゲート型MOSFET として機能する。

また、図示はしないが、上面から見て活性領域の外側には終端領域が設けられており、トレンチゲート型MOSFET は、活性領域と終端領域とから構成されている。

**【0015】**

ここで、本実施の形態のトレンチゲート型MOSFET では、図 2 ( b ) に示すように、格子状に形成されたトレンチの交差部に形成された角部に面して、p 型の第 2 のベース領域 14 が形成されている。角部以外のトレンチ側壁に接する箇所には第 2 のベース領域 14 は形成されず、第 1 のベース領域 3 が形成されている。第 2 のベース領域の不純物濃度は第 1 のベース領域 3 の不純物濃度よりも高く設定している。10

第 2 のベース領域 14 の幅、すなわち、トレンチ側壁からの距離は、チャネルが形成される幅以上であることが望ましく、例えば、0.1 μm 以上、0.5 μm 以下などであれば良い。

**【0016】**

次に、本実施の形態の半導体装置であるトレンチゲートMOSFET の動作について、説明する。

トレンチゲート型MOSFET において、ゲート電極 7 に電圧が印加されると、ゲート絶縁膜 6 と接するベース領域 3 に電流が流れるチャネルが形成される。チャネルが形成されると、ドレイン電流が流れだす。一般的に、ある一定のドレイン電流が流れた時のゲート電圧を閾値電圧と定義している。20

**【0017】**

図 3 は、本実施の形態のトレンチゲート型MOSFET のゲート電圧に対するドレイン電流 28 を従来構造のトレンチゲート型MOSFET のドレイン電流 29 と比較して示したものである。ここで、従来構造のトレンチゲート型MOSFET とは、トレンチの交差部に第 1 のベース領域 3 の不純物濃度よりも高い第 2 のベース領域 14 が形成されていないものということを言う。また、図 3 中、破線直線は閾値電圧を判定するドレイン電流値 30 である。30

**【0018】**

図 3 に示すように、従来構造のトレンチゲート型MOSFET では、トレンチゲート型MOSFET の格子状に形成されたトレンチ 5 の交差部における角部に印加される電界が角部以外の箇所と比較して大きくなるため、角部近傍はそれより先にオン状態となり、ドレイン電流 29 にこぶが発生してしまう。閾値電圧は、第 1 のベース領域 3 の不純物濃度にも依存し、第 1 のベース領域 3 の不純物濃度が高くなると、閾値電圧も高くなる。

**【0019】**

ここで、第 2 のベース領域 14 を形成するために注入する A1 の不純物濃度及び第 2 のベース領域 14 の幅と効果の関係について説明しておく。

第 2 のベース領域 14 の p 型（第 2 導電型）不純物濃度は、第 1 のベース領域 3 の p 型（第 2 導電型）不純物濃度より高くなる。この場合、トレンチ型MOSFET がオン状態になる際にチャネルが一定の幅を持って形成される。第 2 のベース領域 14 の幅が小さすぎると十分に閾値電圧を高くすることができず、角部のチャネルが先にオン状態となってしまうため、第 2 のベース領域 14 はチャネルによって反転する幅以上にする必要がある。さらに、第 2 のベース領域 14 の p 型（第 2 導電型）不純物濃度が低いと、角部以外の閾値電圧よりも低くなってしまうため、角部に印加される電界において、オンしない不純物濃度以上にする必要がある。40

**【0020】**

第 2 のベース領域 14 の p 型（第 2 導電型）不純物濃度と第 1 のベース領域 3 の p 型（第 2 導電型）不純物濃度との関係については、その相対関係が重要である。例えば、第 2 50

のベース領域 1 4 の p 型不純物濃度と第 1 のベース領域 3 の不純物濃度とは、その部分の M O S F E T の局所的な V t h が 0 . 5 V 以上異なればよい。そのためには、例えば、第 2 のベース領域 1 4 の第 2 導電型不純物濃度が第 1 のベース領域 3 の第 2 導電型不純物濃度より  $5 \times 10^{-6} \text{ cm}^{-3}$  以上高ければよい。このようにすれば、角部で先にチャネルがオンすることを防止できる。

#### 【 0 0 2 1 】

本実施の形態のトレンチゲート型 M O S F E T では、トレンチ 5 の交差部の角部近傍の第 2 のベース領域 1 4 の p 型（第 2 導電型）不純物の濃度を第 1 のベース領域 3 のそれより高くしている。このため、トレンチ 5 の交差部の角部で角部以外と同じゲート電圧がゲート電極 7 に印加され、角部のゲート絶縁膜 6 に印加される電界が角部以外の箇所より大きくなつた場合であつても、角部近傍の部分的な閾値電圧を高く設定できるため、角部が角部以外に対して先にオン状態となることがなく、閾値電圧の低下を防ぐことができる。したがつて、図 3 に示すように、こぶが無く高い閾値電圧のドレイン電流 - ゲート電圧特性を有するトレンチゲート型 M O S F E T を得ることができる。

#### 【 0 0 2 2 】

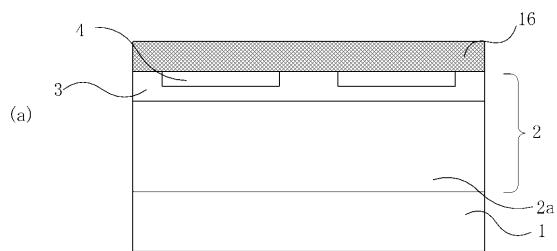

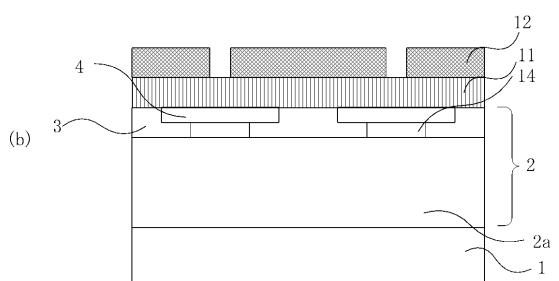

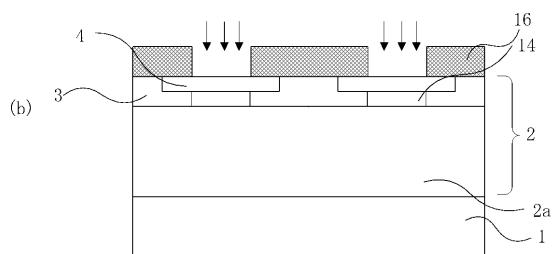

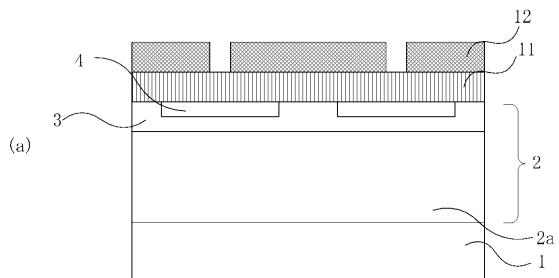

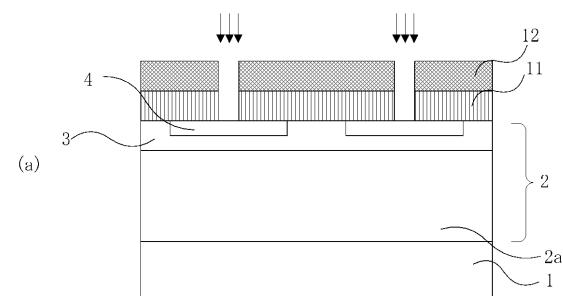

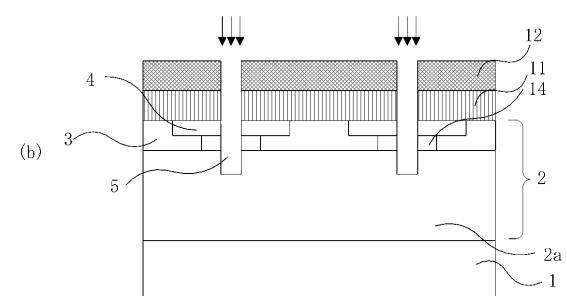

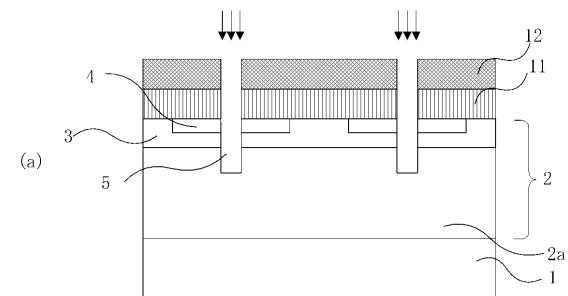

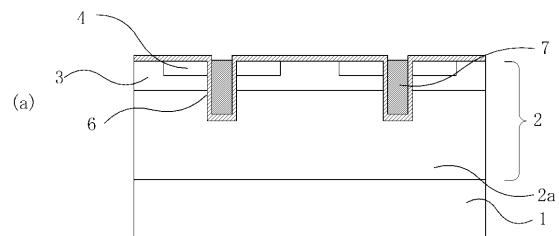

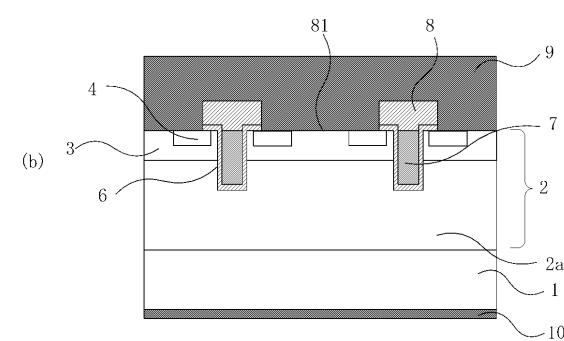

つづいて、本実施の形態のトレンチゲート型 M O S F E T の製造方法を図 4 ~ 図 1 0 を用いて順次説明する。図 4 ~ 図 1 0 は、本実施の形態のトレンチゲート型 M O S F E T の製造方法を説明するための各工程の M O S F E T の断面模式図である。また、図 1 1 は、図 5 の工程で第 2 のベース領域 1 4 を形成するためのイオン注入マスクの形状を示す平面図である。図 4 ~ 図 1 0 の各図の ( a ) および ( b ) は、それぞれ図 1 の A - A 断面及び B - B 断面に対応する断面図である。

#### 【 0 0 2 3 】

まず、図 4 に示すように、炭化珪素基板 1 上にエピタキシャル層 2 を形成する。ここでは 4 H のポリタイプを有する n 型（第 1 導電型）で低抵抗の炭化珪素基板 1 を用意し、その上に化学気相堆積（ C V D : C h e m i c a l V a p o r D e p o s i t i o n ）法により n 型（第 1 導電型）の炭化珪素エピタキシャル層 2 をエピタキシャル成長させた。エピタキシャル層 2 の n 型（第 1 導電型）不純物濃度は  $1 \times 10^{15} \text{ cm}^{-3} \sim 1 \times 10^{17} \text{ cm}^{-3}$  、厚さは 5 ~ 50  $\mu\text{m}$  とした。

#### 【 0 0 2 4 】

つづいて、エピタキシャル層 2 の表面に所定のドーパントをイオン注入することにより、p 型（第 2 導電型）の第 1 のベース領域 3 および n 型の（第 1 導電型）ソース領域 4 を形成する。ここでは、p 型（第 2 導電型）の第 1 のベース領域 3 を p 型（第 2 導電型）不純物であるアルミニウム（ A 1 ）のイオン注入により形成する。A 1 のイオン注入の深さは、エピタキシャル層 2 の厚さを超えない範囲で、0 . 5 ~ 3  $\mu\text{m}$  程度とする。注入する A 1 の不純物濃度は、エピタキシャル層 2 の n 型（第 1 導電型）不純物濃度より高くする。このとき、A 1 の注入深さよりも深いエピタキシャル層 2 の領域がドリフト層 2 a となる。つまり、p 型（第 2 導電型）の第 1 のベース領域 3 が形成されないエピタキシャル層 2 内の領域がドリフト層 2 a である。

#### 【 0 0 2 5 】

n 型（第 1 導電型）のソース領域 4 は、n 型（第 1 導電型）不純物である窒素（ N ）を第 1 のベース領域 3 の表面にイオン注入することにより形成する。ソース領域 4 は、図 1 のように、この後形成されるゲート電極 7 （トレンチ 5 ）のレイアウトに対応する格子状のパターンで形成される。従つて、ゲート電極 7 が形成されたとき、ゲート電極 7 の両側にソース領域 4 が配設される。N のイオン注入深さは、第 1 のベース領域 3 の厚さより浅くする。注入する N の不純物濃度は、第 1 のベース領域 3 の p 型（第 2 導電型）不純物濃度よりも高くし、 $1 \times 10^{18} \text{ cm}^{-3} \sim 1 \times 10^{21} \text{ cm}^{-3}$  の範囲とする。

#### 【 0 0 2 6 】

次に、図 5 に示すように、第 1 の注入マスク 1 6 を介して p 型（第 2 導電型）不純物である A 1 をエピタキシャル層 2 の表面にイオン注入することにより、ソース領域 4 の下部に p 型（第 2 導電型）の第 2 のベース領域 1 4 を形成する。第 2 のベース領域 1 4 はこの

10

20

30

40

50

後形成されるトレンチの交差部における角部近傍に形成される。

図11は、本実施の形態に係るトレンチ型MOSFETの製造方法を説明するための上面図である。本実施の形態では、図5に示されるように、角部近傍が開口した第1の注入マスク16を介してイオン注入が行われて第2のベース領域14が形成される。

#### 【0027】

第2のベース領域14は、この後形成されるトレンチ5のレイアウトに対応して、図5に示されるように、第2のベース領域14が形成される角部をまたぐように形成され、セルの配置に合わせて矩形状のパターンで形成される。また、第2のベース領域14の幅は第2のベース領域14を形成する角部のトレンチ側壁から同心円状に外側へ0.1μm以上0.5μm以下の幅を有するように形成する。

10

#### 【0028】

つづいて、図6に示すように、エピタキシャル層2の表面にシリコン酸化膜からなるエッティングマスク11を1~2μm程度の厚さで堆積し、その上にレジスト材からなるレジストマスク12を形成する。レジストマスク12は、フォトリソグラフィー技術により、トレンチ5の形成領域を開口したパターンに形成される。トレンチ5が格子状なので、レジストマスク12はそれを反転したマトリクス状のパターンとなる。

#### 【0029】

次に、図7に示すように、レジストマスク12をマスクとする反応性イオンエッティング(RIE: Reactive Ion Etching)処理により、エッティングマスク11をパターニングする。つまりレジストマスク12のパターンがシリコン酸化膜でできたエッティングマスク11に転写される。パターニングされたエッティングマスク11は次のトレンチ5を形成するエッティング工程におけるマスクとなる。

20

#### 【0030】

つづいて、図8に示すように、パターニングされたエッティングマスク11をマスクとするRIEにより、エピタキシャル層2にソース領域4および第1のベース領域3を貫通するトレンチ5を形成する。第1のベース領域3の一部には第2のベース領域14が形成されている。トレンチ5の深さは、ドリフト層2aに達するように第2のベース領域14が形成されている箇所より深くなるものとし、0.5~3μm程度とする。

#### 【0031】

次に、図8に示したレジストマスク12、および、エッティングマスク11を除去した後、熱処理装置を用いて、上記の工程でイオン注入したNおよびA1を活性化させるアニールを行う。このアニールは、アルゴン(Ar)ガスなどの不活性ガス雰囲気中で、1300~1900、30秒~1時間の条件で行なう。

30

#### 【0032】

つづいて、図9に示すように、トレンチ5の内側を含むエピタキシャル層2の全面にゲート絶縁膜6を形成した後、ゲート電極7となる低抵抗ポリシリコンを減圧CVD法により堆積し、それらをパターニングまたはエッチバックすることにより、トレンチ5内部にゲート絶縁膜6およびゲート電極7を形成する。ゲート絶縁膜6となるシリコン酸化膜は、エピタキシャル層2の表面を熱酸化法により熱酸化して形成してもよいし、エピタキシャル層2上及びトレンチ5の内側に堆積法により形成してもよい。

40

#### 【0033】

次に、図10に示すように、減圧CVD法により、エピタキシャル層2の表面全面にシリコン酸化膜からなる層間絶縁膜8を形成し、ゲート電極7を覆う。次に、層間絶縁膜8をパターニングすることで、ソース領域4および第1のベース領域3に達するコンタクトホール81を形成する。図10中、点線で囲まれた領域がコンタクトホール81に相当する。

#### 【0034】

そして、エピタキシャル層2上にA1合金等の電極材を堆積することで、層間絶縁膜8上並びにコンタクトホール81内に、ソース電極9を形成する。さらに、炭化珪素基板1の下面にA1合金等の電極材を堆積してドレイン電極10を形成することにより、図1、

50

図2に示した構成のトレンチゲート型MOSFETを得ることができる。

【0035】

本実施の形態の半導体装置によれば、角部近傍の第2のベース領域14の不純物濃度を第1のベース領域3の不純物濃度よりも高くしているため、ゲート電極7に電圧を印加した際に格子状に配列されたトレンチの交差部における角部のゲート絶縁膜6に印加される電界がそれ以外の箇所より大きくなつた場合であつても、角部近傍のチャネルの閾値電圧が角部以外のチャネルの閾値電圧より高くなるので、角部が角部以外に対して先にオン状態となることがなく、閾値電圧の低下を防ぐことができる。

【0036】

なお、本実施の形態では、エピタキシャル層2と炭化珪素基板1とが同じ第1導電型を有する構造のトレンチ型MOSFETについて説明してきたが、本発明は、エピタキシャル層2と炭化珪素基板1とが異なる導電型を有する構造のトレンチゲート型IGBTに対しても適用可能である。例えば、図1に示したエピタキシャル層2が第1導電型のn型である構成に対し、炭化珪素基板1を第2導電型のp型にすればトレンチ型IGBTの構成となる。その場合、トレンチ型MOSFETのソース領域4およびソース電極9は、それぞれトレンチゲート型IGBTのエミッタ領域およびエミッタ電極に対応し、ドレイン電極10はコレクタ電極に対応することになる。

【0037】

本実施の形態においては、炭化珪素半導体で構成された半導体装置を例として説明したが、半導体の材料は、他の材料であつても良く、また、他のワイドバンドギャップ半導体装置であつても良い。

また、本実施の形態では、第1導電型をn型、第2導電型をp型としたが、第1導電型をp型、第2導電型をn型としても良い。

【0038】

さらに、本実施の形態においては、上面から見て正方形のセルを持つ活性領域の例について説明したが、セルは他の構造であつてもよく、基本セルが長方形や六角形などであつても良い。また、セルの配置についても、縦横方向に規則正しく配置された例を用いて説明したが、隣接する列のセルがずれた配置であつて、セルの角部に第2のベース領域が形成されていれば、同様の効果を奏する。また、第1のベース領域3と第2のベース領域の境界は、急峻でなくても良く、ある幅で連続的に不純物濃度が変化するものであつてもよい。

【0039】

また、製造方法においては、第1のベース領域3をエピタキシャル成長法によって形成してもよい。その場合も第1のベース領域3の不純物濃度および厚さは、イオン注入によって形成する場合と同等であれば良い。

【0040】

実施の形態2。

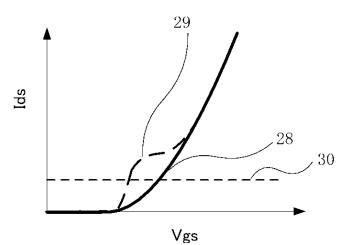

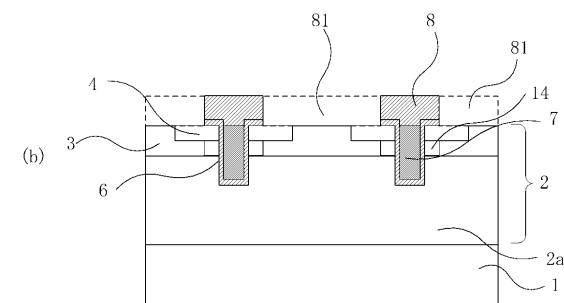

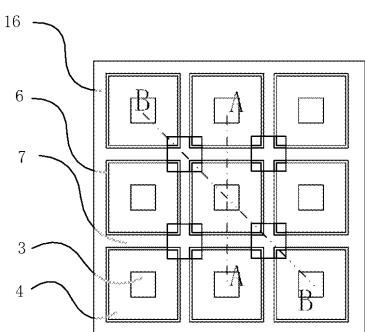

本発明の実施の形態2における炭化珪素半導体装置であるトレンチゲート型MOSFETの構成を説明する。図12と図13は、それぞれ本発明の実施の形態2に係る半導体装置であるトレンチゲート型MOSFETの活性領域の一部の上面図、活性領域の一部の断面模式図である。図12の一点鎖線で示されるA-A断面図が図13(a)に対応し、図1の二点鎖線で示されるB-B断面図が図13(b)に対応する。ここで、B-B断面図は格子状に並ぶトレンチの交差部の特に角部を含む断面図となっている。

【0041】

図12と図13に示すように、本実施の形態のトレンチゲート型MOSFETは、格子状に形成されたトレンチの交差部において、実施の形態1で説明した第2のベース領域14を設ける代わりにソース領域4をトレンチ側壁から離して形成し、交差部以外の箇所ではソース領域4をトレンチ側壁に接するように形成している。その他の点については、実施の形態1と同様であるので、詳しい説明を省略する。

【0042】

10

20

30

40

50

図12と図13に示すように、本実施の形態のトレンチゲート型MOSFETにおいては、トレンチの交差部で、ソース領域4をトレンチ側壁から離して形成しているが、その距離は、0.1μm以上などであれば良い。

#### 【0043】

本実施の形態における半導体装置によれば、角部から離れた箇所にソース領域4が形成されているため、角部近傍のチャネル長が長くなり、閾値電圧が上昇し、かつ、チャネル抵抗が上昇する。つまり、角部近傍のチャネルがオンしにくくなる。したがって、ゲート電極7に電圧を印加した際に格子状に配列されたトレンチの交差部における角部のゲート絶縁膜6に印加される電界がそれ以外の箇所より大きくなつた場合であつても、角部近傍のチャネルの部分的な閾値電圧が高くなり、チャネル抵抗が高くなるため、この部分による閾値電圧への影響を小さくなり、素子全体の閾値電圧が低下することを防ぐことができる。10

#### 【0044】

また、本実施の形態の半導体装置は、実施の形態1において第2のベース領域14を製造する工程を削除し、ソース領域4の形成領域を本実施の形態に示す形状にすれば製造できる。その他の点については、実施の形態1の半導体装置の製造方法と同様である。

#### 【0045】

本発明の実施の形態2における半導体装置の製造方法によれば、本発明の実施の形態1における第2のベース領域14を形成工程が必要無くなるため、実施の形態1と比較してイオン注入工程を削減することができ、製造コストを低減した低コストの半導体装置を得ることができる。20

#### 【符号の説明】

#### 【0046】

1 炭化珪素基板、2 エピタキシャル層、2a ドリフト層、3 第1のベース領域、4 ソース領域、5 トレンチ、6 ゲート絶縁膜、7 ゲート電極、8 層間絶縁膜、9 ソース電極、10 ドレイン電極、11 エッティングマスク、12 レジストマスク、14 第2のベース領域、81 コンタクトホール。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

---

フロントページの続き

(72)発明者 福井 裕

東京都千代田区丸の内二丁目7番3号 三菱電機株式会社内

(72)発明者 菅原 勝俊

東京都千代田区丸の内二丁目7番3号 三菱電機株式会社内

審査官 杉山 芳弘

(56)参考文献 特開2004-055976(JP,A)

特表2002-533936(JP,A)

特開2001-339064(JP,A)

特開2013-232533(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 29/12

H01L 29/78

H01L 21/336