(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2007-53346

(P2007-53346A)

(43) 公開日 平成19年3月1日(2007.3.1)

(51) Int.CI.

H01L 23/12

(2006.01)

F 1

H01L 23/12

501P

テーマコード(参考)

審査請求 未請求 請求項の数 28 O L (全 25 頁)

(21) 出願番号 特願2006-189426 (P2006-189426)

(22) 出願日 平成18年7月10日 (2006.7.10)

(31) 優先権主張番号 10-2005-0076286

(32) 優先日 平成17年8月19日 (2005.8.19)

(33) 優先権主張国 韓国 (KR)

(71) 出願人 390019839

三星電子株式会社

Samsung Electronics

Co., Ltd.

大韓民国京畿道水原市靈通区梅灘洞416

(74) 代理人 100072349

弁理士 八田 幹雄

(74) 代理人 100110995

弁理士 奈良 泰男

(74) 代理人 100114649

弁理士 宇谷 勝幸

(72) 発明者 季仁榮

大韓民国京畿道龍仁市豊徳川1洞 三星4

次アパート101棟410号

最終頁に続く

(54) 【発明の名称】半導体パッケージの配線構造物及びその製造方法、これを用いたウエハーレベルパッケージ及びその製造方法

## (57) 【要約】

【課題】製造工程を単純化した半導体パッケージの配線構造物及びその製造方法、これを用いたウエハーレベルパッケージ及びその製造方法を提供する

【解決手段】配線構造物100は、パッド110、導電パターン120、及び絶縁性フォトトレジスト構造物130を含む。パッドは、回路部105を有する本体102上に配置され回路部に信号を入力するか、又は回路部から信号を出力し、導電パターンはパッドと電気的に接続され、本体の上面上に配置される。絶縁性フォトトレジスト構造物は、導電パターンの上面の全面上に形成され、導電パターンの上面一部を露出させるコンタクトホールを有する。配線を形成するために、金属膜上に形成されたフォトトレジスト膜を2回の写真工程のみで絶縁性フォトトレジスト構造物を形成することにより、配線構造物の構造工程をより単純化させることができる。

【選択図】図1

**【特許請求の範囲】****【請求項 1】**

回路部を有する本体上に配置され、前記回路部に信号を入力するか、又は前記回路部から信号を出力するためのパッドと、

前記パッドと電気的に接続され、前記本体の上面に配置された導電パターンと、

前記導電パターンの上面の全面に形成され、前記導電パターンの前記上面の一部を露出させるコンタクトホールを有する絶縁性フォトレジスト構造物と、を含む半導体パッケージの配線構造物。

**【請求項 2】**

前記導電パターンは、 $Ti / Cu$ 、 $TiW / Ni$ 、 $Ti / Ni$ 、 $TiW / NiV$ 、 $Cr / Cu$ 、 $Cr / Ni$ 、 $Cr / NiV$ 、 $Ti / Cu / Ni$ 、 $TiW / Cu / Ni$ 、 $TiW / Cu / NiV$ 、及び $Cr / Cu / NiV$ からなる群から選択された少なくとも1つの合金を含むことを特徴とする請求項1記載の半導体パッケージの配線構造物。 10

**【請求項 3】**

前記導電パターンの厚みは、1000 ~ 7000 であることを特徴とする請求項1記載の半導体パッケージの配線構造物。

**【請求項 4】**

前記絶縁性フォトレジスト構造物は、前記導電パターンと実質的に同じ外郭形状を有することを特徴とする請求項1記載の半導体パッケージの配線構造物。

**【請求項 5】**

前記本体及び前記導電パターンの間に、前記パッドと対応する第1開口を有する保護膜パターンを更に含むことを特徴とする請求項1記載の半導体パッケージの配線構造物。 20

**【請求項 6】**

前記保護膜パターン及び前記導電パターンの間に、前記第1開口に対応する第2開口を有する第1絶縁膜パターンを更に含むことを特徴とする請求項5記載の半導体パッケージの配線構造物。

**【請求項 7】**

前記第1絶縁膜パターンの厚みは、 $1 \mu m \sim 25 \mu m$ であることを特徴とする請求項6記載の半導体パッケージの配線構造物。

**【請求項 8】**

前記絶縁性フォトレジスト構造物の上面及び露出された前記第1絶縁膜パターンに沿って配置され、前記コンタクトホールと対応する第3開口を有する第2絶縁膜パターンを更に含むことを特徴とする請求項6記載の半導体パッケージの配線構造物。 30

**【請求項 9】**

前記第2絶縁膜パターンの厚みは、 $1 \mu m \sim 25 \mu m$ であることを特徴とする請求項8記載の半導体パッケージの配線構造物。

**【請求項 10】**

回路部と電気的に接続されたパッドが形成された本体の上面に前記パッドを露出させる絶縁膜構造物を形成する段階と、

前記絶縁膜構造物上に配置され、前記パッドと電気的に連結された金属膜を形成する段階と、 40

前記金属膜上に絶縁性フォトレジスト物質を含む絶縁性フォトレジストフィルムを形成する段階と、

前記絶縁性フォトレジストフィルムを露光及び現像して、前記金属膜上に予備フォトレジスト構造物を形成する段階と、

前記予備フォトレジスト構造物をエッチングマスクとして利用して、前記金属膜をエッチングして、前記本体の上面に導電パターンを形成する段階と、

前記予備フォトレジスト構造物を部分的に露光及び現像して、前記導電パターン上に前記導電パターンを露出させるコンタクトホールを有するフォトレジスト構造物を形成する段階と、を含むことを特徴とする半導体パッケージの配線製造方法。 50

**【請求項 1 1】**

前記絶縁膜構造物を形成する段階前に、前記導電パターン及び前記本体の間に介在され、前記パッドと対応する第1開口を有する保護膜パターンを形成する段階を更に含むことを特徴とする請求項10記載の半導体パッケージの配線製造方法。

**【請求項 1 2】**

前記絶縁膜構造物を形成する段階前に、前記保護膜パターン及び前記導電パターンの間に、前記第1開口と対応する第2開口を有する第1絶縁膜パターンを形成する段階を更に含むことを特徴とする請求項11記載の半導体パッケージの配線製造方法。

**【請求項 1 3】**

前記第1絶縁膜パターンを形成する段階は、前記保護膜パターンの上面に感光性を有する第1絶縁膜を形成する段階、前記第1開口に相応する部位の前記第1絶縁膜を部分的に露光する段階、及び前記第1絶縁膜を現像して露光された部位を除去する段階を含み、前記第1絶縁膜を露光するための露光エネルギーは500mJ～2500mJであることを特徴とする請求項11記載の半導体パッケージの配線製造方法。 10

**【請求項 1 4】**

前記本体を形成する段階後に、前記フォトトレジスト構造物を覆って前記コンタクトホールと対応する第3開口を有する第2絶縁膜パターンを形成する段階を更に含むことを特徴とする請求項10記載の半導体パッケージの配線製造方法。

**【請求項 1 5】**

前記第2絶縁膜パターンを形成する段階は、前記フォトトレジスト構造物を覆うように前記本体上に感光性を有する第2絶縁膜を形成する段階、前記第3開口と対応する部位の前記第2絶縁膜を部分的に露光する段階、及び前記第2絶縁膜を現像して前記露光された部位を除去する段階を含み、前記第2絶縁膜を露光するための露光エネルギーは500mJ～2500mJであることを特徴とする請求項14記載の半導体パッケージの配線製造方法。 20

**【請求項 1 6】**

前記フォトトレジスト構造物を形成した後、前記フォトトレジスト構造物をペークする段階を更に含むことを特徴とする請求項10記載の半導体パッケージの配線製造方法。

**【請求項 1 7】**

入力信号を処理してデータ信号を出力する回路部を有する半導体チップと、

前記半導体チップ上に配置され前記回路部に電気的に接続されたパッドと、

前記パッドと電気的に接続され、前記半導体チップの上面に沿って配置された導電パターンと、

前記導電パターンの上面の全面上に形成され、前記導電パターンの上面一部を露出させるコンタクトホールを有する絶縁性フォトトレジスト構造物と、

前記コンタクトホールを埋め立てながら、前記導電パターン上に電気的に接続された導電部材と、を含むウエハーレベルパッケージ。 30

**【請求項 1 8】**

前記半導体チップ及び前記導電パターンの間に、前記パッドと対応する第1開口を有する保護膜パターンを更に含むことを特徴とする請求項17記載のウエハーレベルパッケージ。 40

**【請求項 1 9】**

前記保護膜パターン及び前記導電パターンの間に、前記第1開口に対応する第2開口を有する第1絶縁膜パターンを更に含むことを特徴とする請求項18記載のウエハーレベルパッケージ。

**【請求項 2 0】**

前記絶縁性フォトトレジスト構造物の上面及び露出された前記第1絶縁膜パターンの表面に沿って配置され、前記コンタクトホールと対応する第3開口を有する第2絶縁膜パターンを更に含むことを特徴とする請求項17記載のウエハーレベルパッケージ。

**【請求項 2 1】**

50

前記導電パターン及び前記導電部材の間に、前記導電パターン及び前記導電部材を電気的に接続するための導電性バンプを更に含むことを特徴とする請求項17記載のウエハーレベルパッケージ。

**【請求項22】**

前記導電性バンプは、前記導電パターンと接着される導電性接着パターン、前記導電性接着パターン上に配置された導電ウェッチングパターン(*conductive wetting pattern*)を含むことを特徴とする請求項21記載のウエハーレベルパッケージ。

**【請求項23】**

前記導電性バンプは、前記導電ウェッチングパターン上に形成された酸化抑制パターン 10 を更に含むことを特徴とする請求項21記載のウエハーレベルパッケージ。

**【請求項24】**

前記導電部材は、球形状を有するはんだを含むことを特徴とする請求項17記載のウエハーレベルパッケージ。

**【請求項25】**

ウエハーに形成された半導体チップに形成された回路部に電気的に連結されたパッドを露出させる第1開口が形成された保護膜パターンを形成する段階と、

前記保護膜パターン上に前記第1開口と対応する第2開口を有する第1絶縁膜パターンを形成する段階と、

前記第1絶縁膜パターン上に前記パッドと電気的に連結された金属膜及び前記金属膜上 20 に感光性フォトレジスト薄膜を順次に形成する段階と、

前記感光性フォトレジスト薄膜を露光及び現像して、前記金属膜上に予備フォトレジスト構造物を形成する段階と、

前記予備フォトレジスト構造物をエッチングマスクとして利用して、前記金属膜をエッチングして、前記第1絶縁膜パターン上に導電パターンを形成する段階と、

前記導電パターンの一部を露出させるために、前記予備フォトレジスト構造物を部分的に露光及び現像して、前記導電パターン上にコンタクトホールが形成されたフォトレジスト構造物を形成する段階と、

前記コンタクトホールを埋め立て、前記導電パターンと電気的に接続された導電部材を形成する段階と、を含むウエハーレベルパッケージの製造方法。 30

**【請求項26】**

前記導電パターンを形成する段階前に、前記コンタクトホールを通じて前記導電パターンと電気的に接続されたバンプ構造物を形成する段階を更に含むことを特徴とする請求項25記載のウエハーレベルパッケージの製造方法。

**【請求項27】**

前記半導体チップを形成する段階後に、前記フォトレジスト構造物を覆って、前記コンタクトホールと対応する第3開口を有する第2絶縁膜パターンを形成する段階を含むことを特徴とする請求項25記載のウエハーレベルパッケージの製造方法。

**【請求項28】**

前記フォトレジスト構造物を形成した後、前記フォトレジスト構造物をペークする段階 40 を更に含むことを特徴とする請求項25記載のウエハーレベルパッケージの製造方法。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、半導体パッケージの配線構造物及びその製造方法、これを用いたウエハーレベルパッケージ及びその製造方法に関する。より具体的に、本発明は、新規な配線構造を有し、単純な製造工程で製造されることができる半導体パッケージの配線構造物及びその製造方法、これを用いたウエハーレベルパッケージ及びその製造方法に関する。

**【背景技術】**

**【0002】**

最近、半導体素子の製造技術が開発されるにつれて、半導体素子の集積度が大幅向上されている。一般に、シリコン基板上に形成される半導体素子は、外部衝撃、水分、及び酸素によって容易に損傷される。従って、一般的な半導体素子はパッケージ工程を通じて衝撃、水分、及び酸素から保護される。

#### 【0003】

最近には、半導体素子の嵩に基づいて半導体素子の嵩の100%に近接した嵩を有するボールグリッドアレイパッケージ(ball grid array package)及びウエハーレベルパッケージ(wafer level package)のようなチップスケールパッケージ(chip Scale Package)が開発されたことがある。

10

#### 【0004】

チップスケールパッケージは、共通的に導電パターン及び導電ボールを含む。導電パターンは、外部信号が入力されるか、処理された信号を出力する半導体素子のパッドに電気的に接続され、導電ボールは、導電パターンの端部に形成されたランドパターンに電気的に接続される。一般的に、チップスケールパッケージの導電ボールは、半導体素子上にマトリックス形態に配置される。

#### 【0005】

このようなチップスケールパッケージ方法の例は、特許文献1及び特許文献2に開示されている。

20

#### 【0006】

導電パターン及び導電ボールを含むチップスケールパッケージの場合、導電パターンが外部に露出され他の導電体とショットされる虞がある。従って、従来チップスケールパッケージは、半導体素子のパッドに電気的に連結された導電パターンが覆われるように半導体素子の全面積にかけてフォトレジストフィルムを形成する。その後、フォトレジストフィルムを更にパターニングして導電ボールが形成される導電パターンの一部を露出させ、露出された導電パターンに導電ボールを接続させる。

#### 【0007】

従って、チップスケールパッケージの場合、導電パターンを形成するためには、導電パターンを形成するためのフォトレジストフィルムを形成する工程と、導電ボールが形成される部位を露出させるためにフォトレジストフィルムを形成する工程、即ち、2回のフォトレジストフィルムを半導体基板上に形成することになる。

30

#### 【0008】

このように複雑な工程でチップスケールパッケージを製作するためには、製造費用が多くかかり、工程時間の損失が非常に大きい。

#### 【特許文献1】米国特許第6,187,615号

#### 【特許文献2】米国特許第6,699,782号

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0009】

従って、本発明の目的は、製造工程を単純化した半導体パッケージの配線構造物を提供することにある。

40

#### 【0010】

本発明の他の目的は、前記した半導体パッケージの配線構造を製造するに最適な半導体パッケージ配線構造物の製造方法を提供することにある。

#### 【0011】

本発明の更に他の目的は、前記配線構造物を含むウエハーレベルパッケージを提供することにある。

#### 【0012】

本発明の更に他の目的は、前記配線構造物を含むウエハーレベルパッケージを製造するに適合なウエハーレベルパッケージの製造方法を提供することにある。

50

**【課題を解決するための手段】**

**【0013】**

前述した本発明の目的を達成するために、本発明の一実施形態による半導体パッケージの配線構造物は、パッド、導電パターン、及び絶縁性フォトレジスト構造物を含む。前記パッドは、回路部を有する本体上に配置され、前記回路部に信号を入力するか、又は、前記回路部から信号を出力する。前記導電パターンは、前記パッドと電気的に接続され、前記本体の上面に配置される。前記絶縁性フォトレジスト構造物は、前記導電パターンの上面の全面に形成され、前記導電パターンの上面一部を露出させるコンタクトホールを有する。

**【0014】**

前述した本発明の他の目的を具現するために、本発明の一実施形態による半導体パッケージの配線構造物の製造方法では、回路部と電気的に連結されたパッドが形成された本体の上面に前記パッドを露出させる絶縁膜構造物を形成する。絶縁膜構造物上にパッドと電気的に連結された金属膜を形成する。金属膜上に絶縁性フォトレジスト物質を含む絶縁性フォトレジストフィルムを形成し、絶縁性フォトレジストフィルムを露光及び現像して、金属膜上に感光性を有する予備フォトレジスト構造物を形成する。予備フォトレジスト構造物をエッチングマスクとして利用して、金属膜をエッチングして、本体の上面に沿って導電パターンを形成し、感光性を有する予備フォトレジスト構造物を部分的に露光及び現像して（写真工程を行って）、導電パターン上に導電パターンを露出させるコンタクトホールを有するフォトレジスト構造物を形成する。

**【0015】**

本発明の更に他の目的を具現するために、本発明の一実施形態によるウエハーレベルパッケージは、半導体チップ、パッド、導電パターン、絶縁性フォトレジスト構造物、及び導電ボールを含む。半導体チップは、入力信号を処理してデータ信号を出力する回路部を有し、パッドは、半導体チップ上に配置され回路部に電気的に接続される。導電パターンはパッドと電気的に接続され、半導体チップの上面に形成される。絶縁性フォトレジスト構造物は、前記導電パターンの上面の全面に形成され、導電パターンの上面一部を露出させるコンタクトホールを有する。導電ボールは、コンタクトホールの内部を埋め立てながら、導電パターン上に電気的に接続される。

**【0016】**

本発明の更に他の目的を具現するために、本発明によるウエハーレベルパッケージの製造方法では、ウエハーに形成された半導体チップに形成された回路部に電気的に連結されたパッドを露出させる第1開口が形成された保護膜パターンを形成し、保護膜パターン上に第1開口と対応する第2開口を有する第1絶縁膜パターンを形成する。第1絶縁膜パターン上にパッドと電気的に連結された金属膜を形成し、金属膜上に感光性フォトレジストフィルムを形成する。感光性フォトレジストフィルムを露光及び現像して（1次写真工程を行って）、金属膜上に予備フォトレジスト構造物を形成し、予備フォトレジスト構造物をエッチングマスクとして使用して、金属膜をエッチングして、第1絶縁膜パターン上に導電パターンを形成する。前記導電パターンの一部を露出させるために、予備フォトレジスト構造物を部分的に露光及び現像して（2次写真工程を行って）、導電パターン上にコンタクトホールが形成されたフォトレジスト構造物を形成する。その後、コンタクトホールを埋め立てながら、導電パターンと電気的に接続された導電ボールを形成する。

**【発明の効果】**

**【0017】**

本発明によると、配線を形成するために、金属膜上に形成されたフォトレジスト膜を2回の写真工程のみで絶縁性フォトレジスト構造物を形成することで、回路部に信号を入力又は回路部から信号を出力するパッドに連結された配線構造物を形成する工程をより短縮させることができる。

**【発明を実施するための最良の形態】**

**【0018】**

10

20

30

40

50

以下、添付図面を参照して、本発明の好ましい実施形態を詳細に説明する。

【0019】

<実施形態1>

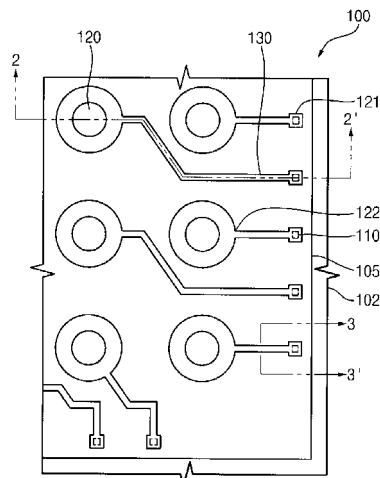

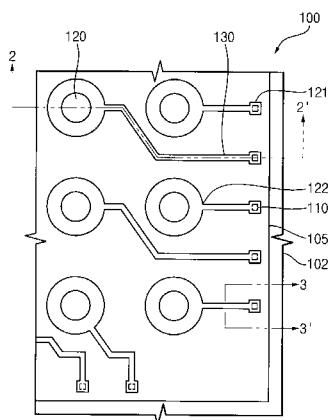

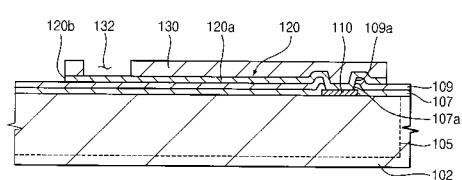

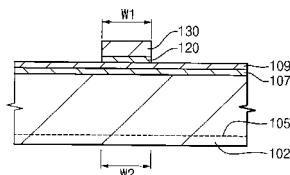

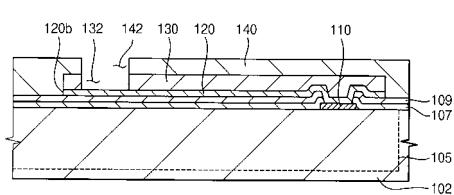

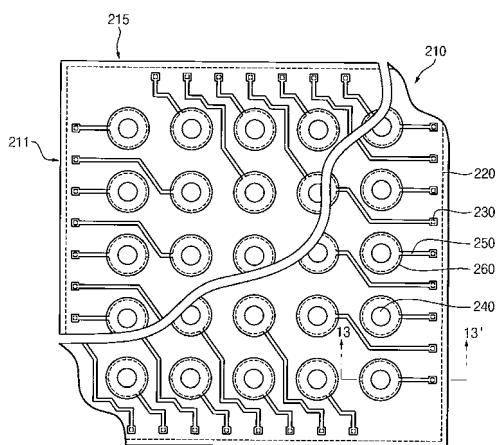

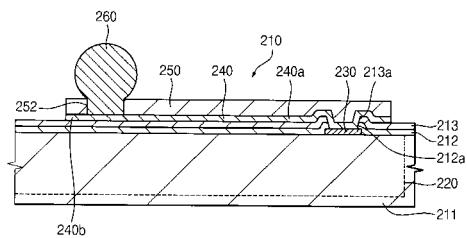

図1は、本発明の実施形態1による半導体パッケージの配線構造物を示す平面図である。図2は、図1の2-2に沿って切断した断面図である。図3は、図1の3-3に沿って切断した断面図である。

【0020】

図1乃至図3を参照すると、半導体パッケージの配線構造物100は、パッド110、導電パターン120、及び絶縁性フォトレジスト構造物130を含む。

【0021】

パッド110は、回路部105を有する本体102上に配置される。本実施形態において、本体102は、ボールグリッドアレイパッケージに使用される柔軟性ポリイミド基板又はシリコンウエハーを含むことができる。パッド110は、外部から発生された入力信号を回路部105に伝達又は回路部105で処理されたデータ信号を回路部105から外部に出力する。前記パッド110は、本体102に入力及び出力される多数の信号を多数の素子にそれぞれ伝達するために多数個形成されることができる。

【0022】

前記パッド110に使用される導電性物質の例としては、アルミニウム、アルミニウム合金、金、銀、銅等が挙げられる。これらの金属は単独又は混合して使用することができる。

【0023】

導電パターン120は前記パッド110と電気的に接続し、前記本体102の上面に形成される。図1及び図2を参照すると、導電パターン120は導電本体120a及びランド部120bを含む。

【0024】

導電本体120aはパッド110に対応して形成され、第1端部121及び第2端部122と対向する第2端部122を有するライン形状を有する。本実施形態において、導電本体120aの長さは、パッド110の位置と後述される導電部材の配置によって、他のパッド110に連結された導電本体120aとは互いに異なる長さを有することができる。本実施形態において、導電パターン120の厚みは、例えば、1000～7000の厚みを有する。

【0025】

ランド部120bは、導電本体120aの第2端部122に接続され形成される。ランド部120bは、例えば、円板形状を有し、ランド部120bは、導電本体120aと一体に形成される。

【0026】

本実施形態において、導電パターン120として使用される金属の例としては、Ti/Cu、TiW/Ni、Ti/Ni、TiW/NiV、Cr/Cu、Cr/Ni、Cr/NiV、Ti/Cu/Ni、TiW/Cu/Ni、TiW/Cu/NiV、及びCr/Cu/NiV等が挙げられる。これらの金属は、単独又は混合して使用することができる。

【0027】

図2を更に参照すると、本体102には保護膜107が形成されることがある。保護膜107は、本体102及び導電パターン120の間に介在され、保護膜107は、外部から印加された衝撃によって回路部105が損傷されることを防止する。本実施形態において、保護膜107に使用することができる物質の例としては、酸化物又は窒化物等が挙げられる。

【0028】

保護膜107には、前記パッド110に対応して前記パッド110を露出させる第1開口107aが形成されている。

【0029】

10

20

30

40

50

本体 102 上には、第 1 絶縁膜 109 が更に形成されることがある。前記第 1 絶縁膜 109 は、保護膜 107 及び導電パターン 120 の間に形成される。好ましくは、前記第 1 絶縁膜 109 は、約 1 μm ~ 25 μm の厚みを有する。

#### 【0030】

第 1 絶縁膜 109 は、外部から印加された応力を吸収して、回路部 105 の損傷を防止する。又、前記第 1 絶縁膜 109 は、回路部 105 を外部導電体から絶縁させる。第 1 絶縁膜 109 として使用される物質の例としては、感光性を有するポリイミドが挙げられる。

#### 【0031】

第 1 絶縁膜 109 は第 2 開口 109a を有する。第 2 開口 109a は、パッド 110 を露出させるために、第 1 開口 107a に対応する位置に形成される。従って、前記導電パターン 120 は、前記第 2 開口 109a と前記第 1 開口 107a を通じて前記パッド 110 に電気的に接続される。

#### 【0032】

図 2 及び図 3 を参照すると、絶縁性フォトレジスト構造物 130 は、導電パターン 120 の上面上に配置される。絶縁性フォトレジスト構造物 130 の外型 (outline) は、導電パターン 120 の外型と実質的に同じでも良い。従って、絶縁性フォトレジスト構造物 130 の幅 W1 は、導電パターン 120 の幅 W2 と実質的に同じである。絶縁性フォトレジスト構造物 130 は、導電パターン 120 のランド部 120b の一部を露出させるコンタクトホール 132 を有する。好ましくは、前記絶縁性フォトレジスト構造物 130 は、1 μm ~ 25 μm の厚みを有する。

#### 【0033】

以下、本発明の第 1 実施形態による半導体パッケージの配線の製造方法を説明する。

#### 【0034】

図 4 乃至図 7 は、図 1 乃至図 3 に図示した半導体パッケージの配線構造物の製造方法を示す断面図である。

#### 【0035】

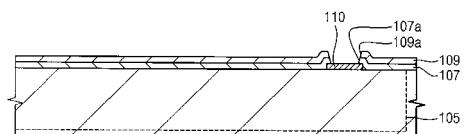

まず、図 4 は、本発明の第 1 実施形態による半導体パッケージの配線を製造するための保護膜パターン 107 及び第 1 絶縁膜パターン 109 を形成する段階を示す断面図である。

#### 【0036】

図 4 を参照すると、半導体パッケージの配線を製造するために、外部信号を処理してデータ信号を生成する回路部 105 が半導体製造工程によって本体 102 に形成される。本実施形態において、本体 102 はポールグリッドアレイパッケージに使用されるフレキシブルポリイミド基板又はシリコンウェハーでも良い。

#### 【0037】

本体 102 に回路部 105 が形成された後、本体 102 上には回路部 105 に外部信号を入力するか、回路部 105 からデータ信号を出力するためのパッド 110 が形成される。

#### 【0038】

パッド 110 を形成するために、本体 102 上にはスパッタリング工程又は化学気相蒸着工程等によってパッド金属膜（図示せず）が形成される。パッド金属膜の例としては、アルミニウム薄膜又はアルミニウム合金薄膜等が挙げられる。

#### 【0039】

パッド金属膜の上面には、スピンドルコーティング工程等によってフォトレジストフィルム（図示せず）を形成する。前記フォトレジストフィルムは、露光工程及び現像工程を含むフォト工程によってパターニングされ、パッド金属膜の上面には、パッド形成位置を覆うフォトレジストパターンが形成される。本実施形態において、フォトレジストパターンは、回路部 105 の入力端子又は出力端子と対応する位置に形成される。

#### 【0040】

10

20

30

40

50

フォトレジストパターンをエッチングマスクとして利用して、前記パッド金属膜をエッチングして、本体102上には、回路部105の出力端子又は入力端子と電気的に連結されたパッド110を形成する。その後、パッド110上に残留するフォトレジストパターンはアッシング工程等によって除去する。

#### 【0041】

回路部105の入力端子又は出力端子に電気的に連結されたパッド110を形成した後、本体102上には保護膜(図示せず)及び第1絶縁膜(図示せず)を連続的に形成する。

#### 【0042】

前記保護膜は、例えば、化学気相蒸着工程、高密度プラズマ蒸着工程等によって本体102上に形成される。本実施形態において、保護膜として使用される薄膜の例としては、酸化膜又は窒化膜等が挙げられる。10

#### 【0043】

第1絶縁膜は、保護膜の上面に約1μm～25μmの厚みに形成する。本実施形態において、第1絶縁膜として使用される薄膜の例としては、感光性ポリイミド薄膜等が挙げられる。

#### 【0044】

第1絶縁膜は、露光工程及び現像工程を含むフォト工程によってパターニングされ、保護膜の上面にパッド110と対応する位置に開口109aが形成された第1絶縁膜パターン109を形成する。第1絶縁膜パターン109は、外部から印加された衝撃を吸収して、本体102及び回路部105を衝撃から保護及び回路部105を外部導電体から絶縁させる。20

#### 【0045】

本実施形態において、第1絶縁膜は、約500mJ～約2500mJの露光エネルギーで露光してフォト工程を行う。

#### 【0046】

第1絶縁膜が酸化膜又は窒化膜等を含む場合、第1絶縁膜上にフォトレジストパターンを形成し、前記フォトレジストパターンをエッチングマスクとして利用して、第1絶縁膜をエッチングして、開口109aを有する第1絶縁膜パターン109を形成することもできる。30

#### 【0047】

第1絶縁膜パターン109を形成した後、第1絶縁膜パターン109をエッチングマスクとして利用して、露光された保護膜を部分的にエッチングして、本体102上に保護膜パターン107を形成する。保護膜パターン107は、第1絶縁膜パターン109の開口109aに対応する開口107aを有する。

#### 【0048】

図5は、図4に図示された第1絶縁膜パターン上に金属膜及び絶縁性フォトレジストフィルムを形成する段階を示す断面図である。

#### 【0049】

図4を参照すると、第1絶縁膜109上に、そして第1及び第2開口107a、109aのプロファイルに沿って金属膜119を形成する。金属膜119は、スパッタリング工程又は化学気相蒸着工程等によって形成される。本実施形態において、金属膜119として使用される物質の例としては、Ti/Cu、TiW/Ni、Ti/Ni、TiW/NiV、Cr/Cu、Cr/Ni、Cr/NiV、Ti/Cu/Ni、TiW/Cu/Ni、TiW/Cu/NiV、及びCr/Cu/NiV等が挙げられる。これらの金属は、単独又は混合して使用されることができる。本実施形態において、金属膜119の厚みは、例えば、1000～7000である。前記金属膜120の上部に第1及び第2開口107a、109aに該当する部位には、図示されたように凹部が形成される。40

#### 【0050】

金属膜119上には、前記凹部を埋め立てるようスピノコートィング工程等によって

50

絶縁性フォトレジストフィルム130を形成する。本実施形態において、絶縁性フォトレジストフィルムとして使用される物質の例としては、感光性を有するポリイミドが挙げられる。本実施形態では、ポジティブ型絶縁性フォトレジストを使用することを例として説明する。

#### 【0051】

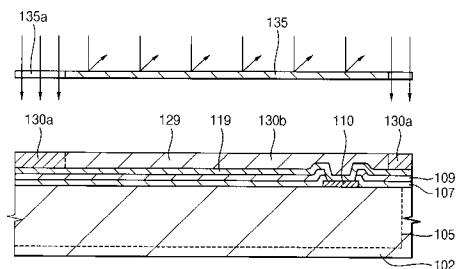

第1絶縁膜109上に金属膜119及び絶縁性フォトレジストフィルム130を順次に形成した後、絶縁性フォトレジストフィルム130の上部には、所定形状の光透過部135aを有する第1レチクル135を整列する。

#### 【0052】

第1レチクル135の光透過部135aを通過した光によって絶縁性フォトレジストフィルム130は1次に露光され、前記絶縁性フォトレジストフィルム130は、露光領域130aと非露光領域130bとに区分される。露光領域130aに存在するフォトレジストは、光反応によって現像溶液に対する溶解度が増加する。ここで、前記絶縁性フォトレジストフィルム130を1次露光するための露光エネルギーは約500mJ～約2500mJである。

#### 【0053】

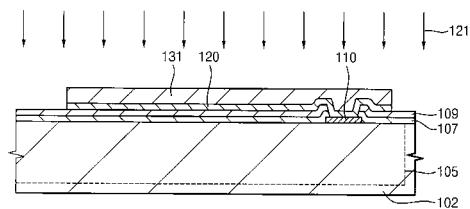

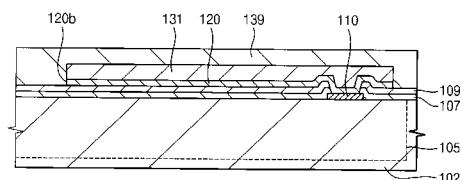

図6は、予備フォトレジスト構造物131及び導電パターン120を形成する段階を示す断面図である。

#### 【0054】

図6を参照すると、部分的に露光された絶縁性フォトレジストフィルム130は現像液によって現像され、絶縁性フォトレジストフィルム130の露光領域130aは除去される。従って、前記金属膜119上には、予備フォトレジスト構造物131が形成される。予備フォトレジスト構造物131は、平面上で見た時、図1に示すように、円板及び円板に連結されたバー( bar )形状を有する。本実施形態において、予備フォトレジスト構造物131の一部は、平面上で見た時、パッド110を覆う。

#### 【0055】

その後、前記予備フォトレジスト構造物131をエッチングマスクとして利用して、金属膜119をエッチングして、第1絶縁膜パターン109上に前記パッド102と電気的に接続された導電パターン120を形成する。前記金属膜119は、第1絶縁膜パターン109に対してエッチング選択比が高いエッチャント121を利用したエッチング工程によってエッチングする。

#### 【0056】

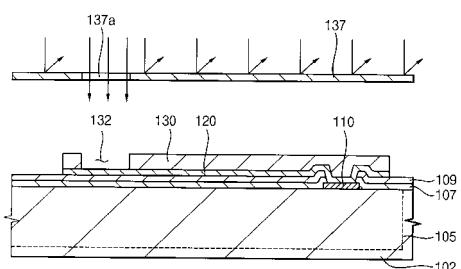

図7は、図6に図示された予備フォトレジスト構造物131をパターニングして、絶縁性フォトレジスト構造物131aを形成する段階を示す断面図である。

#### 【0057】

図7を参照すると、感光性が維持された予備フォトレジスト構造物131の上部に導電パターン120の一部とオーバーラップされる光透過部137aを有する第2レチクル137が配置される。第2レチクル137の光透過部137aを通過した光は、予備フォトレジスト構造物131の一部を2次露光する。この際、2次露光エネルギーは、例えば、500mJ～2500mJである。2次露光された予備フォトレジスト構造物130aは、現像液によって現像すると、2次に露光された部位が除去され、導電パターン120上には、導電パターン120の一部を露出させるコンタクトホール132が形成された絶縁性フォトレジスト構造物131aが形成される。コンタクトホール132が形成された絶縁性フォトレジスト構造物131aはベーク工程によって硬化され、図2に示すような半導体パッケージの配線構造物を完成する。

#### 【0058】

本実施形態によると、絶縁性フォトレジストを使用して、導電パターン120上に予備絶縁性フォトレジスト構造物131を形成した後、前記予備絶縁性フォトレジスト構造物131を更に露光及び現像して、絶縁性フォトレジスト構造物131aを形成する。従つて、従来技術のように、フォトレジストパターンをストリッピングする必要なく、簡単に

10

20

30

40

50

2回の写真工程で絶縁性フォトレジスト構造物を形成することができる。

#### 【0059】

本実施形態では、前記絶縁性フォトレジスト構造物131aは、ポジティブ型絶縁性フォトレジストを使用することを例として説明したが、ネガティブ型絶縁性フォトレジストを使用することもできる。この場合には、図5の第1レチクル135及び図7の第2レチクル137は図示したパターンと反転されたパターンを有するレチクルを使用しなければならない。

#### 【0060】

##### <実施形態2>

図8は、本発明の実施形態2による半導体パッケージの配線構造物を示す断面図である。

10 本実施形態による半導体パッケージの配線構造物は、第2絶縁膜パターンを更に形成することを除くと、前記実施形態1で説明した半導体パッケージの配線構造物と実質的に同じである。従って、同じ部材には、同じ参照符号を付与し、これについての重複説明は省略する。

#### 【0061】

図8を参照すると、図2のような配線構造物の第1絶縁膜パターン109上に第2絶縁膜パターン140が形成されている。前記第2絶縁膜パターン140は、絶縁性フォトレジスト構造物130を覆うように、前記第1絶縁膜パターン109上に形成される。本実施形態において、前記第2絶縁膜パターン140は、約1μm～30μmの厚みを有する。

20 前記第2絶縁膜パターン140として使用することができる物質の例としては、感光性を有するポリイミドが挙げられる。

#### 【0062】

第2絶縁膜パターン140は、前記絶縁性フォトレジスト構造物130のコンタクトホール132と対応する位置に形成された開口142を有する。前記開口142を通じて前記導電パターン120は部分的に露出される。前記第2絶縁膜パターン140は、導電パターン120の露出された側面を外部導電体から絶縁させる。又、前記第2絶縁膜パターン140は、外部衝撃を吸収して、導電パターン120及び回路部105の損傷を防止する。

#### 【0063】

以下、本発明の実施形態による半導体パッケージの配線の製造方法を説明する。

30

#### 【0064】

図9及び図10は、本発明の実施形態2による半導体パッケージの製造方法を説明するための断面図である。本実施形態による半導体パッケージの製造方法は、第2絶縁膜パターンを形成する段階を更に行うことを除くと、実施形態による半導体パッケージの製造方法と同じである。従って、同じ部材には同じ参照符号を付与し、同じ部材についての重複説明は省略する。

#### 【0065】

図9は、本実施形態による半導体パッケージの配線を製造するための第2絶縁膜を形成する段階を示す断面図である。

#### 【0066】

まず、実施形態1において、図4乃至図6に示すことと同じ工程を行って、図2に示すように、本体102上に予備フォトレジスト構造物131及び導電パターン120を形成する。

40

#### 【0067】

その後、図9を参照すると、本体102上に予備フォトレジスト構造物131及び導電パターン120を形成した後、予備フォトレジスト構造物130が覆われるように、スピノコーティング工程等によって本体102の全面にかけて第2絶縁膜139を形成する。本実施形態において、第2絶縁膜139に使用される物質の例としては、前記予備フォトレジスト構造物131を構成している物質と同じ感光性を有するポリイミドが挙げられる。

50

## 【0068】

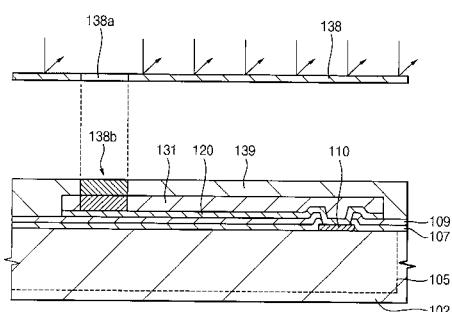

図10は、図9に図示された第2絶縁膜139を露光する段階を示す断面図である。

## 【0069】

図10を参照すると、第2絶縁膜139の上部には、光透過部138aを有する第2レチクル138が配置される。本実施形態において、光透過部138aは、導電パターン120の一部とオーバーラップされ、導電パターン120を部分的に露出させるコンタクトホール形成位置の上部に位置する。前記第2レチクル138は、実施形態1の第2レチクル137と同じものを使用することができる。

## 【0070】

第2レチクル138が本体102の上部に整列された後、前記第2レチクル138の上部から第2絶縁膜139に向かって第2絶縁膜139及び予備フォトレジスト構造物131を順次に露光するための光が走査され、第2絶縁膜139及び予備フォトレジスト構造物131は順次に露光される。その結果、第2絶縁膜139及び予備フォトレジスト構造物131は、露光領域138bで光反応が発生して、非露光領域に存在する絶縁性フォトレジストに対して溶解度が大きくなる。本実施形態において、第2絶縁膜139を露光するに必要な露光エネルギーは約500mJ～約3000mJである。

## 【0071】

その後、露光された第2絶縁膜139及び予備フォトレジスト構造物131は、現像工程によって現像されると、露光領域138bに存在する感光性フォトレジスト物質は除去され、図8に示すように、本体102上には導電パターン120を部分的に露出させる第1コンタクトホール132を有する絶縁性フォトレジスト構造物130及び第2コンタクトホール142を有する第2絶縁膜パター140が形成される。

## 【0072】

本実施形態でも実施形態1で説明したように、ポジティブ型絶縁性フォトレジストの代わりに、ネガティブ型絶縁性フォトレジストを使用することができる。

## 【0073】

## &lt;実施形態3&gt;

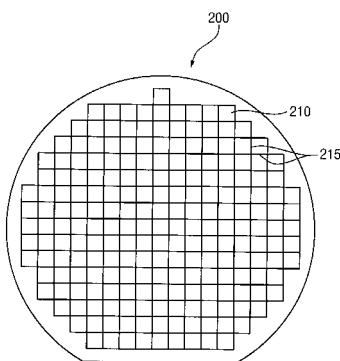

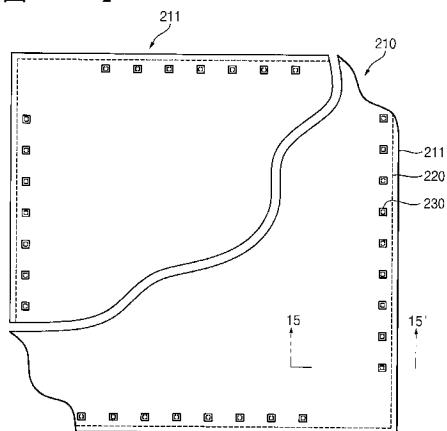

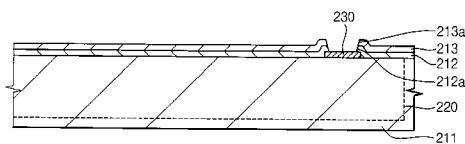

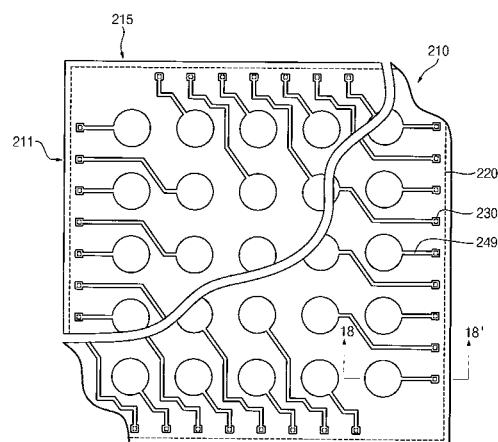

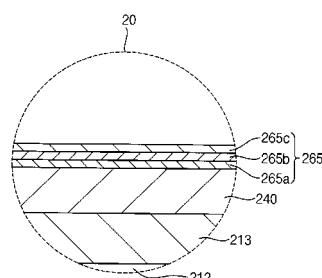

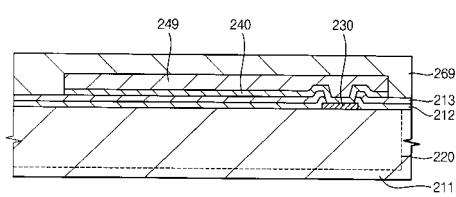

図11は、本発明の実施形態3によるウエハーレベルパッケージの半導体チップが形成されたウエハーを示す平面図である。図12は、図11に図示されたウエハーレベルパッケージAの平面図である。図13は、図12の13-13に沿って切断した断面図である。

## 【0074】

図11を参照すると、ウエハ-200は、複数個のウエハーレベルパッケージ210及びウエハーレベルパッケージ210をウエハ-200から分離するためのウエハーレベルパッケージ210の間に形成されたスクライブライン215を含む。

## 【0075】

図12及び図13を参照すると、ウエハーレベルパッケージ210は、回路部220を有する半導体チップ211、導電性パッド230、導電パターン240、絶縁性フォトレジスト構造物250、及び導電ボール260を含む。

## 【0076】

半導体チップ211の回路部220は、外部から入力された入力信号を処理し、データ信号を発生する。本実施形態において、半導体チップ211は、平面上で見た時、四角形又は矩形形状を有する。

## 【0077】

導電性パッド230は、外部入力信号を回路部220に伝達するか、回路部220から処理されたデータ信号を外部に出力するために回路部220に電気的に接続される。

## 【0078】

導電性パッド230は、半導体チップ211のエッジ部に沿って複数個が一列に配置されることができる。又は、導電性パッド230は、半導体チップ210のエッジ部に沿って複数列に配置されることができる。導電性パッド230が半導体チップ210のエッジ

10

20

30

40

50

部に沿って複数列に配置される場合、導電性パッド230は、平面上に見た時、ジグザグ形態に配置することができる。

#### 【0079】

導電性パッド230は金属のような導電物質を含み、平面上で見た時、四角プレート又は円板形状を有することができる。導電性パッド230として使用される物質の例としては、アルミニウム、アルミニウム合金、金、銀、銅等が挙げられる。これらは、単独又は混合して使用されることができる。本実施形態において、導電性パッド230はアルミニウム又はアルミニウム合金を含む。

#### 【0080】

図13を更に参照すると、導電性パッド230が形成された半導体チップ211には、10保護膜パターン212及び第1絶縁膜パターン213が順次に形成されている。

#### 【0081】

保護膜パターン212は、導電性パッド230が形成された半導体チップ211の背面上に形成される。保護膜パターン212として使用することができる薄膜の例としては、窒化膜又は酸化膜等が挙げられる。保護膜パターン212には、導電性パッド230を露出する開口212aが形成されている。保護膜パターン212は、外部から印加された衝撃から半導体チップ211に形成された回路部220の損傷を防止する。

#### 【0082】

第1絶縁膜パターン213は、保護膜パターン212上に形成されている。前記第1絶縁膜パターン213として使用することができる物質としては、例えば、感光性を有するポリイミドが挙げられる。第1絶縁膜パターン213は、前記保護膜パターン212と同様に、前記導電性パッド230を露出させる開口213aを有する。前記第1絶縁膜パターン213に形成された開口213aは、導電性パッド230を部分的に露出させるために、保護膜パターン212に形成された開口212aに対応する。前記第1絶縁膜パターン213は、外部から印加された衝撃を吸収して、半導体チップ211に形成された回路部220の損傷を防止するのみならず、前記回路部220を外部導電体から電気的に絶縁する。20

#### 【0083】

導電パターン240は、第1絶縁膜パターン213上に形成されている。導電パターン240は、導電本体240a及びランド部240bを含む。30

#### 【0084】

導電本体240aは、パッド230と電気的に接続するように形成され、第1端部及び第1端部と対向する第2端部を有するライン形状を有する。示すように、導電本体240aの長さは、パッド230の位置と導電ボールの配置によって、互いに異なる長さを有することができる。

#### 【0085】

導電パターン240の導電本体240aは、平面上で見た時、バー形状を有し、導電パターン240の一側端部は、導電性パッド230に電気的に接続され、導電パターン240の一側端部と対向する他側端部にはランド部240bが形成される。ランド部240bは、平面上で見た時、円板形状を有し、半導体チップ211の中央部に配置される。40

#### 【0086】

本実施形態において、複数個の導電性パッド230にそれぞれ電気的に接続された導電パターン240は、半導体チップ211の中央部に延長され、円板形状を有する半導体チップのランド部240bは、半導体チップ211の中央部にマトリックス形態に配置される。

#### 【0087】

絶縁性フォトレジスト構造物250は、導電パターン240上の全面に形成されている。前記絶縁性フォトレジスト構造物は、導電パターン240のランド部240bの中央部位を部分的に露出させるコンタクトホール252を有する。絶縁性フォトレジスト構造物250の外型は、コンタクトホール252を除くと、平面上で見た時、導電パターン2450

0と実質的に同じ外型を有する。本実施形態において、絶縁性フォトレジスト構造物250として使用することができる物質の例としては、感光性を有するポリイミドが挙げられる。絶縁性フォトレジスト構造物250は、導電パターン240の上面に沿って形成され導電パターン240を外部導電体(図示せず)から絶縁させる。

#### 【0088】

球形状を有する導電部材である導電ボール260は、コンタクトホール252によって露出された導電パターン240に電気的に接続される。導電ボール260として使用される物質の例としては、導電パターン240より相対的に低い溶融温度を有するはんだ等が挙げられる。導電部材は、球形状である導電ボール260以外に、橢円形状、柱形状等を有することができる。

10

#### 【0089】

以下、本実施形態によるウエハーレベルパッケージの製造方法を説明する。

#### 【0090】

図14乃至図18は、本実施形態によるウエハーレベルパッケージの製造方法を説明するための平面図及び断面図である。

#### 【0091】

図14は、ウエハーレベルパッケージの保護膜パターン212及び第1絶縁膜パターン213の形成段階を示す平面図であり、図15は、図14の15-15に沿って切断した断面図である。

20

#### 【0092】

図14及び図15を参照すると、ウエハーレベルパッケージを製造するために、まず、半導体チップ製造工程によってウエハー200上に半導体チップ211を形成する。

#### 【0093】

半導体チップ製造工程によって半導体チップ211には、外部入力信号を処理してデータ信号を発生する回路部220が形成される。その後、前記回路部220には、導電性パッド230が形成される。

30

#### 【0094】

導電性パッド230を形成するために、半導体チップ211上には、化学気相蒸着工程又はスパッタリング工程によって金属膜(図示せず)が形成される。金属膜は、回路部220に電気的に連結される。金属膜として使用される物質の例としては、アルミニウム又はアルミニウム合金、金、銀等が挙げられる。これらの金属は、単独又は混合して使用されることができる。本実施形態において、導電性パッド230はアルミニウムを含む。

30

#### 【0095】

金属膜の上面には、スピンドルコートィング工程等によってフォトレジストフィルムを形成し、フォト工程によってフォトレジストフィルムをパターニングして、半導体チップ211上にはフォトレジストパターン(図示せず)を形成する。フォトレジストパターンをエッチングマスクとして利用して、前記金属膜をエッチングして、半導体チップ211上に導電性パッド230を形成する。その後、導電性パッド230上に残留するフォトレジストパターンは、酸素プラズマを利用したアッシング工程等を通じて導電性パッド230から除去される。

40

#### 【0096】

導電性パッド230は、外部入力信号を回路部220に伝達又は回路部220から処理されたデータ信号を外部に出力する。本実施形態において、平面上で見た時、四角形形状に形成される。

#### 【0097】

図14に示すように、半導体チップ211上に形成された導電性パッド230は、半導体チップ211のエッジ部に沿って一列に配列することができる。又は、導電性パッド230は、半導体チップ211のエッジ部に沿って複数列に配列することができ、複数列に配列された導電性パッド230は、平面上で見た時、ジグザグ形態に配置することができる。

50

## 【0098】

図15を参照すると、導電性パッド230を形成した後、導電性パッド230が形成された半導体チップ211上に保護膜(図示せず)及び第1絶縁膜(図示せず)が化学気相蒸着工程やスピンドルコーティング等のような単位工程によって順次に形成される。

## 【0099】

保護膜は、半導体チップ211上に形成され、導電性パッド230を覆う。保護膜として使用される薄膜の例としては、化学気相蒸着工程又は高密度プラズマ蒸着工程等によって形成された窒化膜又は酸化膜等が挙げられる。

## 【0100】

第1絶縁膜は、スピンドルコーティング工程によって保護膜の上面に形成されることができる、第1絶縁膜として使用される物質の例としては、感光性を有するポリイミド物質が挙げられる。第1絶縁膜は、保護膜の上面に約1μm乃至25μmの厚みに形成される。

## 【0101】

第1絶縁膜は、露光工程及び現像工程を含むフォト工程によってパターニングされ、保護膜の上面にパッド230と対応する位置に開口213aが形成された第1絶縁膜パターン213を形成する。第1絶縁膜パターン213は、外部から印加された衝撃を吸収して脆性の弱い本体211及び回路部220を衝撃から保護し、回路部105を外部導電体から絶縁させる。本実施形態において、第1絶縁膜は、約500mJ～約2500mJの露光エネルギーで露光してフォト工程を行う。その後、前記絶縁膜パターン213をエッチングマスクとして使用し、前記保護膜をエッチングして、前記パッド230を露出する保護膜開口部212aを有する保護膜パターン212を形成する。

## 【0102】

第1絶縁膜が酸化膜又は窒化膜等を含む場合、第1絶縁膜上にフォトレジストパターンを形成し、前記フォトレジストパターンをエッチングマスクとして利用して、第1絶縁膜をエッチングして、開口213aを有する第1絶縁膜パターン213を形成することもできる。即ち、第1絶縁膜上にはスピンドルコーティング工程によってフォトレジストフィルムが形成され、フォトレジストフィルムは、フォト工程によってパターニングされ、第1絶縁膜上にはフォトレジストパターンが形成される。フォトレジストパターンは、導電性パッド230に対応する開口を有する。フォトレジストパターンをエッチングマスクとして利用して、第1絶縁膜及び保護膜はフォトリソグラフィ工程によってエッチングされ、半導体チップ211上には、開口212aが形成された保護膜パターン212及び開口213aが形成された第1絶縁膜パターン213が形成される。残留するフォトレジストパターンは、アッショング等の工程によって除去する。

## 【0103】

保護膜パターン212は、外部から印加された衝撃によって半導体チップ211に形成された回路部220の損傷を防止する。第1絶縁膜パターン213は、外部から印加された衝撃を吸収して、半導体チップ211に形成された回路部220の損傷を防止するのみならず、回路部220を外部導電体から絶縁する。

## 【0104】

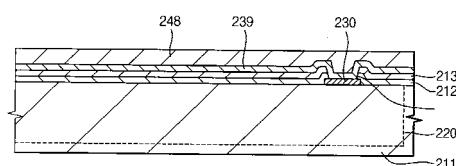

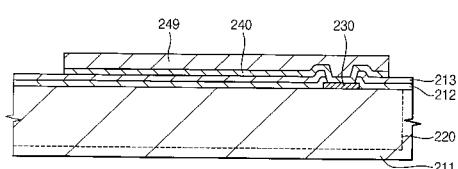

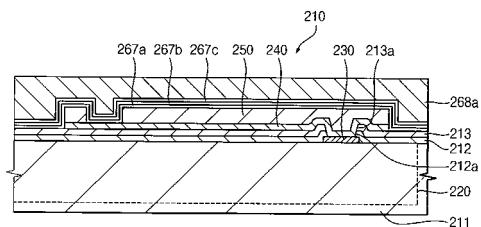

図16は、図15に図示された第1絶縁膜パターン213上に金属膜及び絶縁性フォトレジストフィルムを形成する段階を示す断面図である。

## 【0105】

図16を参照すると、第1絶縁膜パターン213上にスパッタリング工程又は化学気相蒸着工程によって全面にかけて金属膜239を形成する。

## 【0106】

その後、前記金属膜239の上面にスピンドルコーティング工程等によって絶縁性フォトレジストフィルム248を形成する。前記絶縁性フォトレジストフィルム248に使用される物質の例としては、感光性ポリイミドが挙げられる。

## 【0107】

図17は、図16に図示されたフォトレジストフィルム248をパターニングして、金

10

20

30

40

50

属膜 239 をエッティングして、予備フォトレジスト構造物 249 及び導電パターン 240 を形成する段階を示す平面図である。図 18 は、図 17 の 18 - 18 に沿って切断した断面図である。

#### 【0108】

図 17 及び図 18 を参照すると、実施形態 1 の図 5 で説明したことと同じ方法で絶縁性フォトレジストフィルム 248 の上部には、フォトレジストフィルム 248 をパターニングするための光透過部が形成された第 1 レチクル（図示せず）が整列される。第 1 レチクルがフォトレジストフィルム 248 の指定された位置に整列された後、光透過部を通じてフォトレジストフィルム 248 に提供された光によってフォトレジストフィルム 248 は、1 次露光及び現像され、金属膜 239 の上面には予備フォトレジスト構造物 249 が形成される。

#### 【0109】

その後、予備フォトレジスト構造物 249 をエッティングマスクとして利用して金属膜 239 をエッティングして、第 1 絶縁膜パターン 213 上には導電パターン 240 を形成する。

#### 【0110】

導電パターン 240 の一側端部は、半導体チップ 211 の回路部 230 に電気的に接続された導電性パッド 230 に電気的に接続され、一側端部と対向する他側端部は、第 1 絶縁膜パターン 213 の上面に沿って半導体チップ 211 の中央部に延長される。各導電性パッド 230 に電気的に連結された多数の導電パターン 240 の他側端部は、示すように、円形のランド部が連結されており、これらの円形の多数のランド部は、半導体チップ 211 の中央部にマトリックス形態に配列されるように形成される。

#### 【0111】

図 12 及び図 13 を参照すると、実施形態 1 の図 7 で説明したことと同じ方法で、感光性が維持された予備フォトレジスト構造物 249 の上部には、導電パターン 240 の一部と対応する光透過部を有する第 2 レチクル（図示せず）が配置される。第 2 レチクルの光透過部を通じて入射された光によって感光性が維持された予備フォトレジスト構造物は 2 次露光される。

#### 【0112】

2 次露光された予備フォトレジスト構造物は現像工程によって現像され、第 1 絶縁膜パターン 213 上にはコンタクトホール 252 が形成された絶縁性フォトレジスト構造物 250 が形成される。

#### 【0113】

絶縁性フォトレジスト構造物 250 の外郭形状は、平面上で見た時、コンタクトホール 252 を除くと、導電パターン 240 の外郭形状と同じである。

#### 【0114】

絶縁性フォトレジスト構造物 250 は、後にベーク工程によって硬化される。

#### 【0115】

その後、絶縁性フォトレジスト構造物 250 のコンタクトホール 252 によって露出された導電パターン 240 上に導電ボール付着工程によって球形状を有する導電部材である導電ボール 260 を付着する。前記導電ボール 260 は、例えば、赤外線リフロー炉等で溶融され、導電パターン 240 及び導電ボール 260 は、互いに電気的に接続される。その結果、図 13 に示すようなウエハーレベルパッケージが完成される。

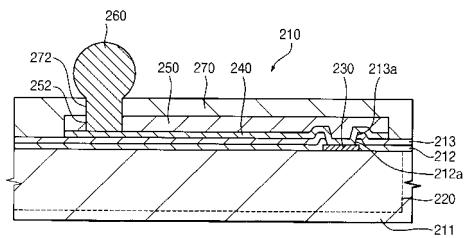

#### 【0116】

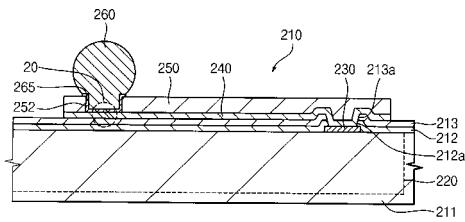

< 実施形態 4 >

図 19 は、本発明の実施形態 4 によるウエハーレベルパッケージの導電性バンプを示す断面図である。図 20 は、図 19 の「20」部分の拡大図である。本実施形態によるウエハーレベルパッケージは、導電性バンプを除くと、前述した実施形態 3 によるウエハーレベルパッケージと同じ構成を有する。従って、同じ部材には同じ参照符号を付与し、その重複説明は省略する。

10

20

30

40

50

## 【0117】

図19及び図20を参照すると、ウエハーレベルパッケージ210は、導電パターン240及び導電ボール260の間の電気的特性を大幅向上させる導電性バンプ265を更に含む。導電性バンプ265は、導電パターン240及び導電ボール260の間に配置され、導電パターン240及び導電ボール260の間の物理的接続強度と電気的特性を向上させる。

## 【0118】

導電性バンプ265は、導電性接着パターン265a、導電性ウェッチングパターン265bを含むことができる。導電性接着パターン265aは導電パターン240上に配置され、導電性ウェッチングパターン265bは、導電性接着パターン265a上に配置される。又、導電性バンプ265は酸化抑制パターン265cを更に含むことができる。10

## 【0119】

本実施形態において、導電性接着パターン265aとして使用される物質の例としては、クロム(Cr)、ニッケル(Ni)、チタニウム-タンゲステン(TiW)等が挙げられ、導電性ウェッチングパターン265bとして使用される物質の例としては、銅(Cu)、ニッケル(Ni)、ニッケル-バナジウム(NiV)等が挙げられる。

## 【0120】

本実施形態において、導電性バンプ265は、導電性接着パターン265a、導電ウェッチングパターン265b、及び酸化抑制パターン265cを含むと図示したが、導電性バンプ265は、導電性接着パターン265a、導電ウェッチングパターン265b、及び酸化抑制パターン265cのうち、いずれか一つ以上を含むことができる。20

## 【0121】

以下、本実施形態によるウエハーレベルパッケージの導電性バンプを形成する製造方法を説明する。

## 【0122】

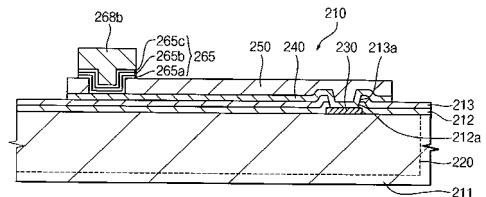

図21及び図22は、本実施形態によるウエハーレベルパッケージの導電性バンプを形成する方法を説明するための断面図である。

## 【0123】

図21は、導電性接着層、導電性ウェッチング層、及び酸化抑制層を形成する段階を示す断面図である。30

## 【0124】

図21を参照すると、導電パターン240に接続された導電性バンプ265を形成するために、半導体チップ211上には導電性接着層276a、導電性ウェッチング層267b、及び酸化抑制層267cが順次に形成される。本実施形態において、導電性接着層276a、導電性ウェッチング層267b、及び酸化抑制層267cは、スパッタリング工程又は化学気相蒸着工程等によって形成されることがある。

## 【0125】

導電性接着層267a、導電性ウェッチング層267b、及び酸化抑制層267cが順次に形成した後、酸化抑制層267c上にはスピンドルコーティング工程等によってフォトトレジストフィルム268aを形成する。40

## 【0126】

図22は、図21に形成された導電性接着層、導電性ウェッチング層、及び酸化抑制層をエッチングして、導電性バンプを形成する段階を示す断面図である。

## 【0127】

図22を参照すると、酸化抑制層267c上に形成されたフォトトレジストフィルム268aをフォト工程によってパターニングして、酸化抑制層267c上にはフォトトレジストパターン268bを形成する。前記フォトトレジストパターン268bは、絶縁性フォトトレジスト構造物250のコンタクトホール252に対応する部分に選択的に形成される。

## 【0128】

その後、フォトトレジストパターン268bをエッチングマスクとして利用して、導電性

接着層 267a、導電性ウェッティング層 267b、及び酸化抑制層 267c は順次にエッチングし、絶縁性フォトレジスト構造物 250 上には、導電性接着パターン 265a、導電性ウェッティングパターン 265b、及び酸化抑制パターン 265c で構成された導電性バンプ 265 を形成する。その後、残留するフォトレジストパターン 268b はアッティング等の方法で除去し、実施形態 4 の図 13 で説明したことと同じ方法で導電性バンプ 265 上に導電ボールを形成して、本実施形態によるウエハーレベルパッケージを完成する。

#### 【0129】

##### <実施形態 5>

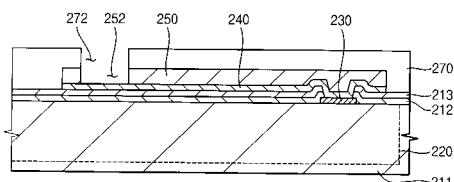

図 23 は、本発明の実施形態 5 によるウエハーレベルパッケージを示す断面図である。本実施形態によるウエハーレベルパッケージは、第 2 絶縁膜パターンを更に形成することを除くと、前記実施形態 4 で説明されたウエハーレベルパッケージと実質的に同じである。従って、同じ部材には同じ参照符号を付与し、その重複説明は省略する。

#### 【0130】

図 23 を参照すると、図 18 のような配線構造物の第 1 絶縁膜パターン 213 上には、第 2 絶縁膜パターン 270 が形成されている。前記第 2 絶縁膜パターン 270 は、絶縁性フォトレジスト構造物 250 を覆うように前記第 1 絶縁膜パターン 213 上に形成される。本実施形態において、前記第 2 絶縁膜パターン 270 は、約 1 μm ~ 30 μm の厚みを有する。前記第 2 絶縁膜パターン 270 として使用することができる物質の例としては、感光性を有するポリイミドが挙げられる。

#### 【0131】

第 2 絶縁膜パターン 270 は、前記絶縁性フォトレジスト構造物 250 のコンタクトホール 252 と対応する位置に形成された開口 272 を有する。前記開口 272 を通じて前記導電パターン 240 は部分的に露出される。前記第 2 絶縁膜パターン 270 は、導電パターン 240 の露出された側面を外部導電体から絶縁させる。又、前記第 2 絶縁膜パターン 270 は外部衝撃を吸収して、導電パターン 240 及び回路部 220 の損傷を防止する。

#### 【0132】

以下、本発明の実施形態によるウエハーレベルパッケージを製造する方法を説明する。

#### 【0133】

図 24 ~ 図 26 は、本発明の実施形態 5 によるウエハーレベルパッケージの製造方法を説明するための断面図である。本実施形態によるウエハーレベルパッケージの製造方法は、第 2 絶縁膜パターンを形成する段階を更に行うことなく、実施形態 3 によるウエハーレベルパッケージの製造方法と実質的に同じである。従って、同じ部材には同じ参照符号を付与し、その重複説明は省略する。

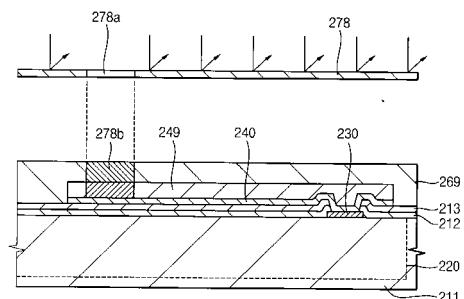

#### 【0134】

図 24 は、本実施形態によるウエハーレベルパッケージの配線を製造するための第 2 絶縁膜を形成する段階を示す断面図である。

#### 【0135】

まず、実施形態 3 で図 17 及び図 18 に示すものと同じ工程を行って半導体チップ 211 上に予備フォトレジスト構造物 249 及び導電パターン 240 を形成する。

#### 【0136】

図 24 を参照すると、半導体チップ 211 上に予備フォトレジスト構造物 249 及び導電パターン 240 を形成した後、予備フォトレジスト構造物 249 を覆うようにスピニングコーティング工程等によって半導体チップ 211 の全面積にかけて第 2 絶縁膜 269 を形成する。本実施形態において、第 2 絶縁膜 269 に使用される物質の例としては、前記予備フォトレジスト構造物 249 を構成している物質と同じ感光性を有するポリイミドが挙げられる。

#### 【0137】

図 25 は、図 24 に図示された第 2 絶縁膜 269 及び予備フォトレジスト構造物 249 を露光する段階を示す断面図である。

10

20

30

40

50

**【 0 1 3 8 】**

図25を参照すると、第2絶縁膜269の上部には、光透過部278aを有する第3レチクル278が配置される。本実施形態において、光透過部278aは、好ましく導電パターン240の一部とオーバーラップされ、導電パターン240を部分的に露出させるコンタクトホール形成の位置の上部に位置する。前記第2レチクル278は、実施形態3の第1レチクル(図示せず)と同じものを使用することができる。

**【 0 1 3 9 】**

第3レチクル278が半導体チップ211の上部に整列された後、第3レチクル278の上部から第2絶縁膜269に向かって第2絶縁膜269及び予備フォトレジスト構造物249を順次に露光するための光が走査され、第2絶縁膜269及び予備フォトレジスト構造物249は順次に露光される。その結果、第2絶縁膜269及び予備フォトレジスト構造物249は、露光領域278bで光反応が発生して、非露光領域に存在する絶縁性フォトレジストに対して溶解度が大きくなる。本実施形態において、第2絶縁膜270aを露光するのに必要な露光エネルギーは、約500mJ～約3000mJである。

**【 0 1 4 0 】**

図26は、図25に図示した第2絶縁膜269及び予備フォトレジスト構造物249を現像して、第2絶縁膜パターン270及び絶縁性フォトレジスト構造物250を形成する段階を示す断面図である。

**【 0 1 4 1 】**

露光された第2絶縁膜269及び予備フォトレジスト構造物249が現像工程によって現像されると、露光領域278bに存在する感光性フォトレジスト物質は除去され、図26に示すように、半導体チップ211上には、導電パターン240を部分的に露出させる第1コンタクトホール252を有する絶縁性フォトレジスト構造物250及び第2コンタクトホール272を有する第2絶縁膜パターン270が形成される。

**【 0 1 4 2 】**

本実施形態でも実施形態3で説明したように、ポジティブ型絶縁性フォトレジストの代わりに、ネガティブ型絶縁性フォトレジストを使用することができる。

**【 0 1 4 3 】**

図23を更に参照すると、第2絶縁膜パターン270の第1コンタクトホール252及び絶縁性フォトレジスト構造物250の第2コンタクトホール272によって露出された導電パターン240には導電ボール260を配置する。前記導電ボール260は、導電ボールアタッチ工程によって溶融され、前記第1コンタクトホール252及び前記第2コンタクトホール272を埋め立てながら、導電パターン240上に電気的に接続される。

**【 産業上の利用可能性 】****【 0 1 4 4 】**

以上で詳細に説明したように、ウエハーレベルパッケージを製造する時、パッドと連結された導電パターンを形成するために、導電パターン上に配置された予備フォトレジスト構造物を導電パターンから除去せず、感光性フォトレジストパターン上に配線を露出させるコンタクトホールを形成する。即ち、配線を形成するために、金属膜上に形成されたフォトレジスト膜を2回の写真工程のみで絶縁性フォトレジスト構造物を形成することで、配線構造物の製造工程をより単純化させることができる。

**【 0 1 4 5 】**

以上、本発明の実施形態によって詳細に説明したが、本発明はこれに限定されず、本発明が属する技術分野において通常の知識を有するものであれば本発明の思想と精神を離れることなく、本発明を修正または変更できる。

**【 図面の簡単な説明 】****【 0 1 4 6 】**

【図1】本発明の実施形態1による半導体パッケージの配線構造物を示す平面図である。

【図2】図1の2-2に沿って切断した断面図である。

【図3】図1の3-3に沿って切断した断面図である。

【図4】図1乃至図3に図示された半導体パッケージの配線構造物の製造方法を示す断面図である。

【図5】図1乃至図3に図示された半導体パッケージの配線構造物の製造方法を示す断面図である。

【図6】図1乃至図3に図示された半導体パッケージの配線構造物の製造方法を示す断面図である。

【図7】図1乃至図3に図示された半導体パッケージの配線構造物の製造方法を示す断面図である。

【図8】本発明の実施形態2による半導体パッケージの配線構造物を示す断面図である。

【図9】本発明の実施形態2による半導体パッケージの製造方法を説明するための断面図である。 10

【図10】本発明の実施形態2による半導体パッケージの製造方法を説明するための断面図である。

【図11】本発明の実施形態3によるウエハーレベルパッケージの半導体チップが形成されたウエハーを示す平面図である。

【図12】図11に図示されたウエハーレベルパッケージ(A)の平面図である。

【図13】図12の13-13に沿って切断した断面図である。

【図14】本実施形態によるウエハーレベルパッケージの製造方法を説明するための平面図及び断面図である。

【図15】本実施形態によるウエハーレベルパッケージの製造方法を説明するための平面図及び断面図である。 20

【図16】本実施形態によるウエハーレベルパッケージの製造方法を説明するための平面図及び断面図である。

【図17】本実施形態によるウエハーレベルパッケージの製造方法を説明するための平面図及び断面図である。

【図18】本実施形態によるウエハーレベルパッケージの製造方法を説明するための平面図及び断面図である。

【図19】本発明の実施形態4によるウエハーレベルパッケージの導電性バンプを示す断面図である。

【図20】図19の「20」部分の拡大図である。

【図21】本実施形態によるウエハーレベルパッケージの導電性バンプを形成する方法を説明するための断面図である。 30

【図22】本実施形態によるウエハーレベルパッケージの導電性バンプを形成する方法を説明するための断面図である。

【図23】本発明の実施形態5によるウエハーレベルパッケージを示す断面図である。

【図24】本発明の実施形態5によるウエハーレベルパッケージの製造方法を説明するための断面図である。

【図25】本発明の実施形態5によるウエハーレベルパッケージの製造方法を説明するための断面図である。

【図26】本発明の実施形態5によるウエハーレベルパッケージの製造方法を説明するための断面図である。 40

#### 【符号の説明】

##### 【0147】

- 100 配線構造物、

- 102 本体、

- 105 回路部、

- 110 パッド、

- 120 導電パターン、

- 120a 導電本体、

- 120b ランド部、

1 2 1 第 1 端部、

1 2 2 第 2 端部、

1 3 0 絶縁性フォトレジスト構造物。

【図 1】

【図 2】

【図 3】

【図 4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図11】

【図10】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図23】

【図22】

【図24】

【図25】

【図26】

---

フロントページの続き

- (72)発明者 沈 成 びん

大韓民国京畿道城南市盆唐区亭子洞 常緑マウルウソンアパート321棟503号

- (72)発明者 張 東 鉉

大韓民国京畿道水原市靈通区靈通洞 サルグゴル7団地アパート706棟904号

- (72)発明者 鄭 顯 秀

大韓民国京畿道華城市台安邑半月里868番地 新靈通現代アパート211棟

- (72)発明者 鄭 載 植

大韓民国京畿道華城市台安邑半月里 三星電子株式会社華城事業場M E 研究棟6階I P T チーム

- (72)発明者 柳 承 官

大韓民国京畿道龍仁市駒城面麻北里 三星レミアン1次アパート110棟1202号

- (72)発明者 朴 明 淵

大韓民国京畿道水原市靈通区遠泉洞 遠泉住公アパート106棟601号

- (72)発明者 尹 鐘 國

大韓民国京畿道安城市孔道邑萬井里 ブヨンアパート707 - 7番地101棟709号

- (72)発明者 崔 朱 逸

大韓民国忠清北道清州市興徳区慕忠洞440 - 14