(19) World Intellectual Property Organization

International Bureau(43) International Publication Date

25 October 2007 (25.10.2007)

PCT

(10) International Publication Number

WO 2007/120492 A1(51) International Patent Classification:

*H01L 21/336* (2006.01) *H01L 21/8242* (2006.01)

*H01L 29/06* (2006.01) *H01L 21/20* (2006.01)

*H01L 29/786* (2006.01)

(72) Inventor; and

(75) Inventor/Applicant (for US only): **FORBES, Leonard**

[US/US]; 7340 NW Mountain View Drive, Corvallis, Oregon 97330 (US).(21) International Application Number:

PCT/US2007/008123(74) Agents: **STEFFEY, Charles, E. et al.**; Schwegman, Lundberg, Woessner & Kluth PA, P. O. Box 2938, Minneapolis, MN 55402 (US).

(22) International Filing Date: 3 April 2007 (03.04.2007)

(25) Filing Language: English

(26) Publication Language: English

(30) Priority Data:

11/397,527 4 April 2006 (04.04.2006) US

11/397,430 4 April 2006 (04.04.2006) US

11/397,358 4 April 2006 (04.04.2006) US

11/397,413 4 April 2006 (04.04.2006) US

11/397,406 4 April 2006 (04.04.2006) US

(81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AT, AU, AZ, BA, BB, BG, BH, BR, BW, BY, BZ, CA, CH, CN, CO, CR, CU, CZ, DE, DK, DM, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IS, JP, KE, KG, KM, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LT, LU, LY, MA, MD, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PG, PH, PL, PT, RO, RS, RU, SC, SD, SE, SG, SK, SL, SM, SV, SY, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

(71) Applicant (for all designated States except US): **MICRON TECHNOLOGY, INC.** [US/US]; 8000 So. Federal Way, Boise, Idaho 83716-9632 (US).

(84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LS, MW, MZ, NA, SD, SL, SZ, TZ, UG, ZM,

*[Continued on next page]*

(54) Title: NANOWIRE TRANSISTOR WITH SURROUNDING GATE

**(57) Abstract:** One aspect of the present subject matter relates to a method for forming a transistor. According to an embodiment of the method, a pillar of amorphous semiconductor material is formed on a crystalline substrate, and a solid phase epitaxy process is performed to crystallize the amorphous semiconductor material using the crystalline substrate to seed the crystalline growth. The pillar has a sublithographic thickness. A transistor body is formed in the crystallized semiconductor pillar between a first source/drain region and a second source/drain region. A surrounding gate insulator is formed around the semiconductor pillar, and a surrounding gate is formed around and separated from the semiconductor pillar by the surrounding gate insulator. Other aspects are provided herein.

ZW), Eurasian (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European (AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HU, IE, IS, IT, LT, LU, LV, MC, MT, NL, PL, PT, RO, SE, SI, SK, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

— before the expiration of the time limit for amending the claims and to be republished in the event of receipt of amendments

**Published:**

— with international search report

For two-letter codes and other abbreviations, refer to the "Guidance Notes on Codes and Abbreviations" appearing at the beginning of each regular issue of the PCT Gazette.

## NANOWIRE TRANSISTOR WITH SURROUNDING GATE

5

### Cross Reference To Related Applications

Benefit of priority is hereby claimed to "Grown Nanofin Transistors," U.S. Application Serial No. 11/397,430, filed on April 4, 2006; "Etched Nanofin Transistors," U.S. Application Serial No. 11/397,358, filed on April 4, 2006; "DRAM With Nanofin Transistors," U.S. Application Serial No. 11/397,413, 10 filed on April 4, 2006; and "Tunneling Transistor With Sublithographic Channel," U.S. Application Serial No. 11/397,406, filed April 4, 2006, which applications are herein incorporated by reference.

### Technical Field

15

This disclosure relates generally to semiconductor devices, and more particularly, to nanowire transistors that have a surrounding gate.

### Background

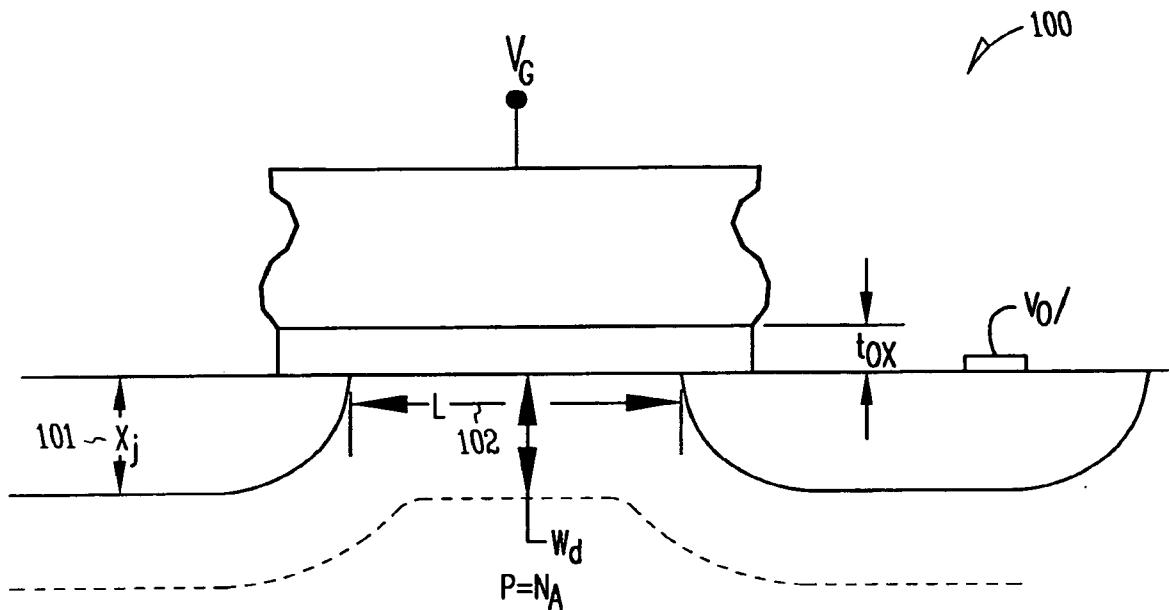

The semiconductor industry has a market driven need to reduce the size 20 of devices, such as transistors, and increase the device density on a substrate. Some product goals include lower power consumption, higher performance, and smaller sizes. FIG. 1 illustrates general trends and relationships for a variety of device parameters with scaling by a factor  $k$ . The continuous scaling of 25 MOSFET technology to the deep sub-micron region where channel lengths are less than 0.1 micron (100 nm or 1000 Å) causes significant problems in the conventional transistor structures. For example, junction depths should be much less than the channel length. Thus, with reference to the transistor 100 illustrated in FIG. 1, the junctions 101 should be on the order of a few hundred Angstroms for channels 102 that are approximately 1000 Å long. Such 30 shallow junctions are difficult to form by conventional implantation and diffusion techniques. Extremely high levels of channel doping are required to suppress short-channel effects such as drain induced barrier lowering, threshold

voltage roll off, and sub-threshold conduction. Sub-threshold conduction is particularly problematic in DRAM technology as it reduces the charge storage retention time on the capacitor cells. These extremely high doping levels result in increased leakage and reduced carrier mobility. Thus, the expected improved 5 performance attributed to a shorter channel is negated by the lower carrier mobility and higher leakage attributed to the higher doping.

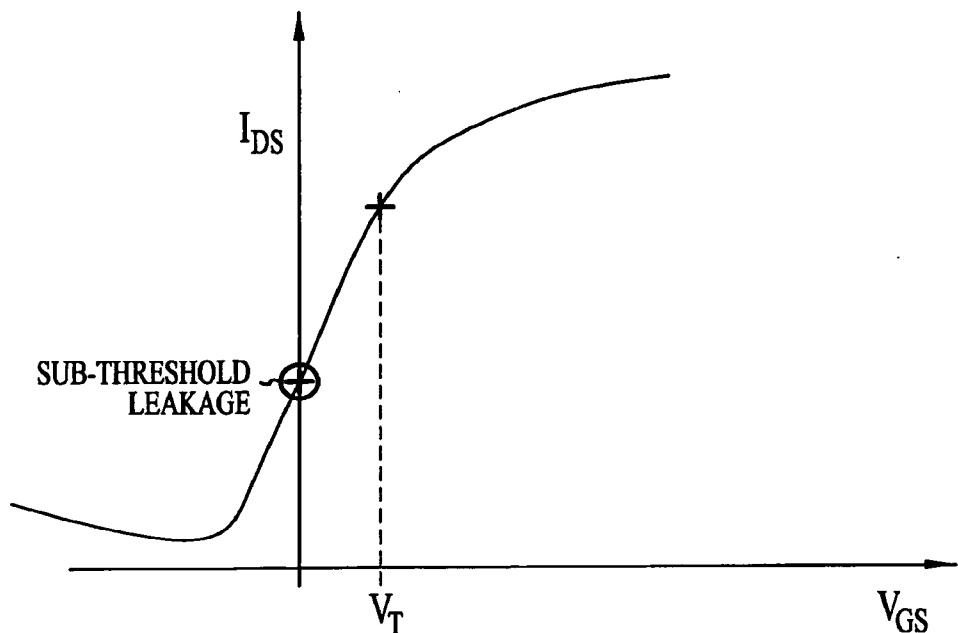

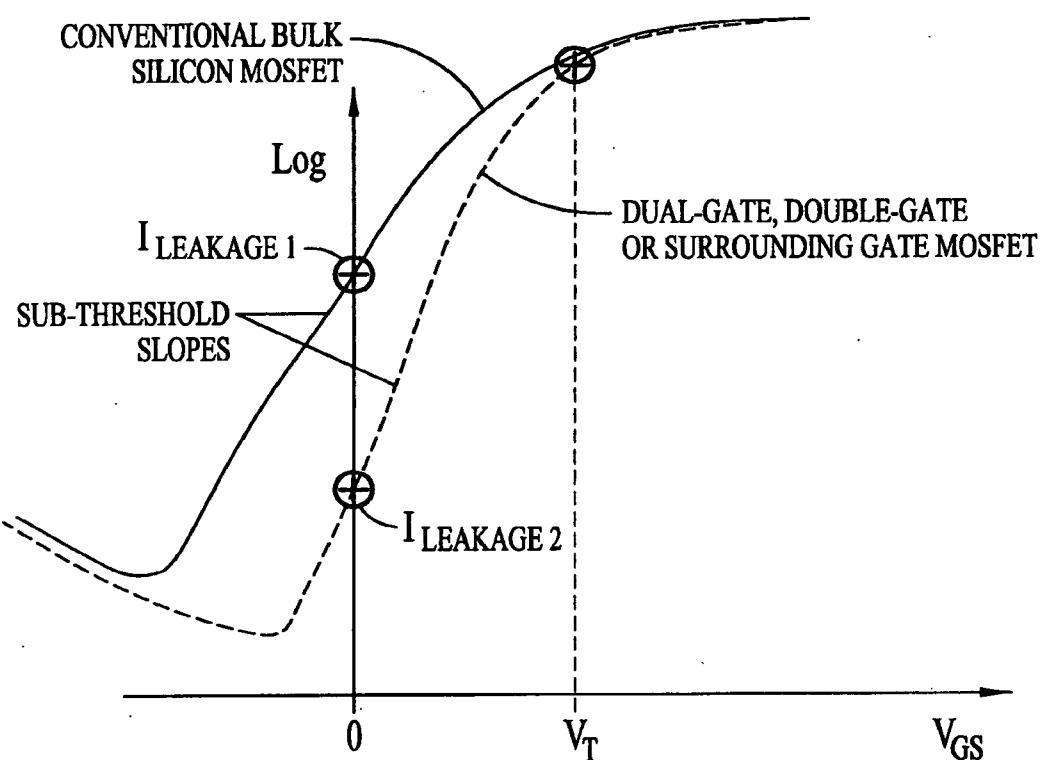

Leakage current is a significant issue in low voltage and lower power battery-operated CMOS circuits and systems, and particularly in DRAM circuits. The threshold voltage magnitudes are small to achieve significant overdrive and 10 reasonable switching speeds. However, as illustrated in FIG. 2, the small threshold results in a relatively large sub-threshold leakage current.

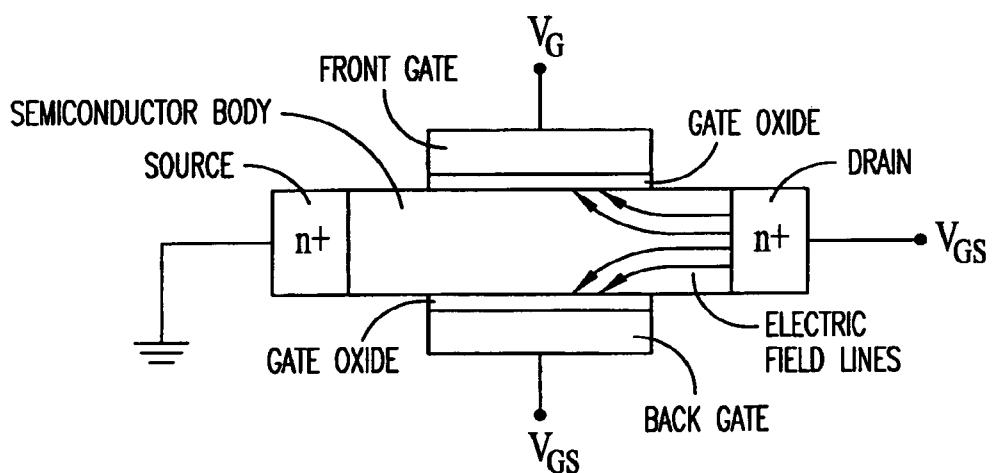

Some proposed designs to address this problem use transistors with ultra-thin bodies, or transistors where the surface space charge region scales as other transistor dimensions scale down. Dual-gated or double-gated transistor 15 structures also have been proposed to scale down transistors. As commonly used in the industry, “dual-gate” refers to a transistor with a front gate and a back gate which can be driven with separate and independent voltages, and “double-gated” refers to structures where both gates are driven when the same potential. An example of a double-gated device structure is the FinFET. “TriGate” structures 20 and surrounding gate structures have also been proposed. In the “TriGate” structure, the gate is on three sides of the channel. In the surrounding gate structure, the gate surrounds or encircles the transistor channel. The surrounding gate structure provides desirable control over the transistor channel, but the structure has been difficult to realize in practice.

25 FIG. 3 illustrates a dual-gated MOSFET with a drain, a source, and front and back gates separated from a semiconductor body by gate insulators, and also illustrates an electric field generated by the drain. Some characteristics of the dual-gated and/or double-gated MOSFET are better than the conventional bulk silicon MOSFETs, because compared to a single gate the two gates better screen 30 the electric field generated by the drain electrode from the source-end of the

channel. The surrounding gate further screens the electric field generated by the drain electrode from the source. Thus, sub-threshold leakage current characteristics are improved, because the sub-threshold current is reduced more quickly as the gate voltage is reduced when the dual-gate and/or double gate 5 MOSFET turns off. FIG. 4 generally illustrates the improved sub-threshold characteristics of dual gate, double-gate, or surrounding gate MOSFETs in comparison to the sub-threshold characteristics of conventional bulk silicon MOSFETs.

Advances have been made in the growth of II-V compound 10 semiconductor nanowires and in the fabrication of III-V compound semiconductor nanowire transistors. The growth of the II-V compound semiconductor transistors is achieved by vapor-liquid-solid (VLS) epitaxial growth of vertical nanowires on gold dots. Silicon nanowire transistors have been previously described by vapor phase epitaxial growth through a hole or by 15 solid phase epitaxial growth over a polysilicon DRAM capacitor plate to make a polycrystalline nanowire transistor.

### Summary

An embodiment of the present subject matter provides nanowire 20 transistors from amorphous semiconductor nanorods that are recrystallized on the surface of a semiconductor wafer. The silicon nanorods are formed with dimensions smaller than lithographic dimensions by a sidewall spacer technique. The recrystallization of the amorphous nanorods uses solid phase epitaxial growth. The resulting nanowires can be used as the body regions of transistors 25 where both the thickness of the body of the transistor and channel length have dimensions smaller than lithographic dimensions. The nanowire transistors have a wraparound gate. Various nanowire transistor embodiments use silicon nanowires.

One aspect of the present subject matter relates to a method for forming a 30 transistor. According to an embodiment of the method, a pillar of amorphous

semiconductor material is formed on a crystalline substrate, and a solid phase epitaxy process is performed to crystallize the amorphous semiconductor material using the crystalline substrate to seed the crystalline growth. The pillar has a sublithographic thickness. A transistor body is formed in the crystallized 5 semiconductor pillar between a first source/drain region and a second source/drain region. A surrounding gate insulator is formed around the semiconductor pillar, and a surrounding gate is formed around and separated from the semiconductor pillar by the surrounding gate insulator.

An aspect relates to a transistor. A transistor embodiment includes a 10 crystalline substrate, a first source/drain region formed in the crystalline substrate, and a crystalline semiconductor pillar formed on the substrate in contact with the first source/drain region. The transistor includes a second source/drain region formed in a top portion of the pillar, a gate insulator formed around the pillar, and a surrounding gate formed around and separated from the 15 pillar by the gate insulator. The pillar has cross-section dimensions less than a minimum feature size.

These and other aspects, embodiments, advantages, and features will become apparent from the following description of the present subject matter and the referenced drawings.

20

#### **Brief Description of the Drawings**

FIG. 1 illustrates general trends and relationships for a variety of device parameters with scaling by a factor k.

FIG. 2 illustrates sub-threshold leakage in a conventional silicon 25 MOSFET.

FIG. 3 illustrates a dual-gated MOSFET with a drain, a source, front and back gates separated from a semiconductor body by gate insulators, and an electric field generated by the drain.

FIG. 4 generally illustrates the improved sub-threshold characteristics of dual gate, double-gate, or surrounding gate MOSFETs in comparison to the sub-threshold characteristics of conventional bulk silicon MOSFETs.

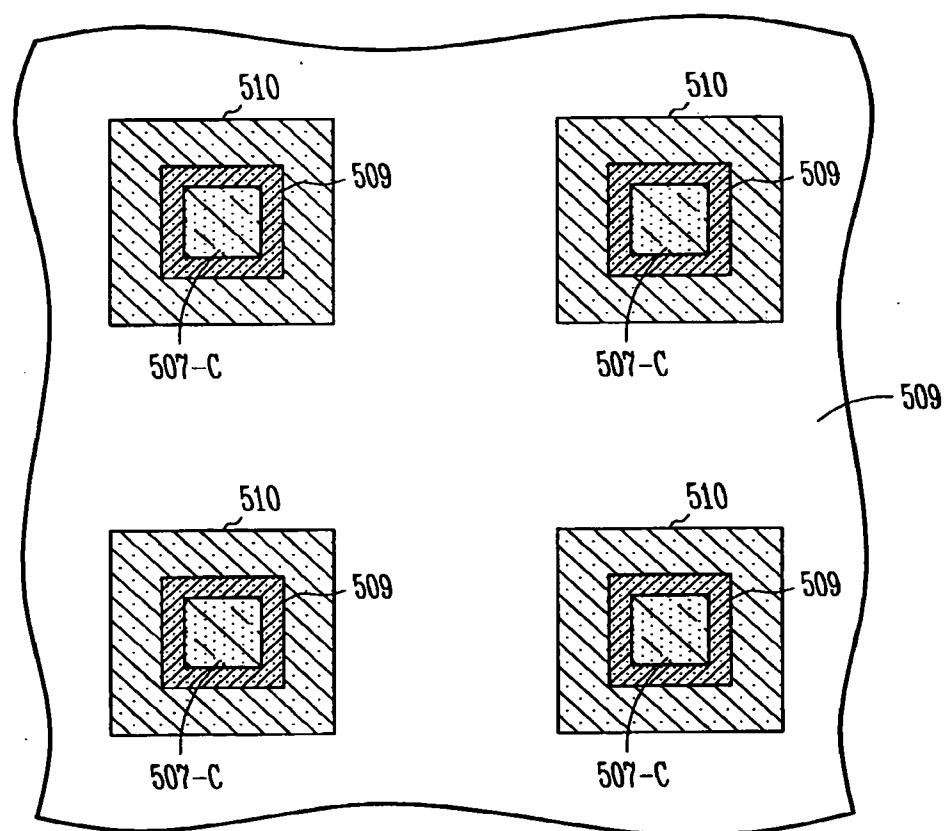

FIGS. 5A-5H illustrate an embodiment of a process to form crystalline 5 nanorods with surrounding gates.

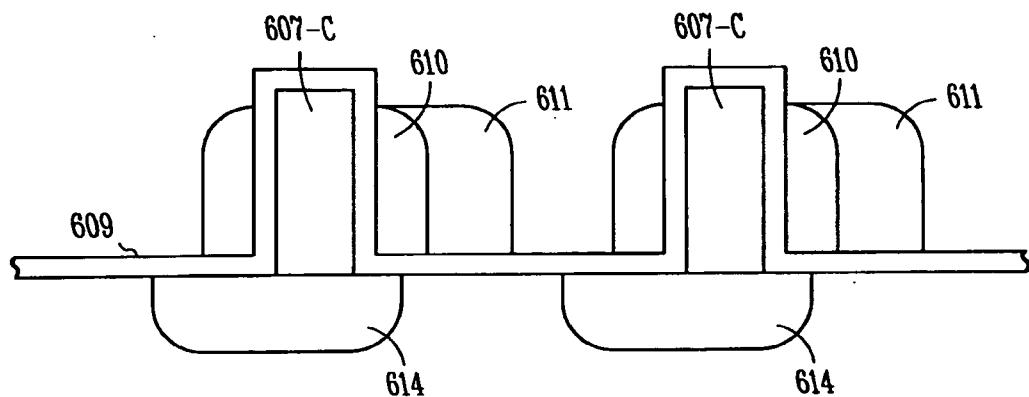

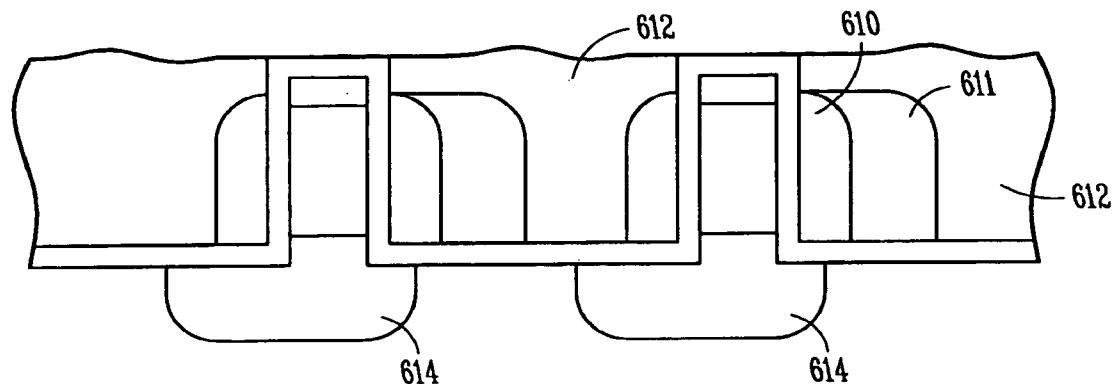

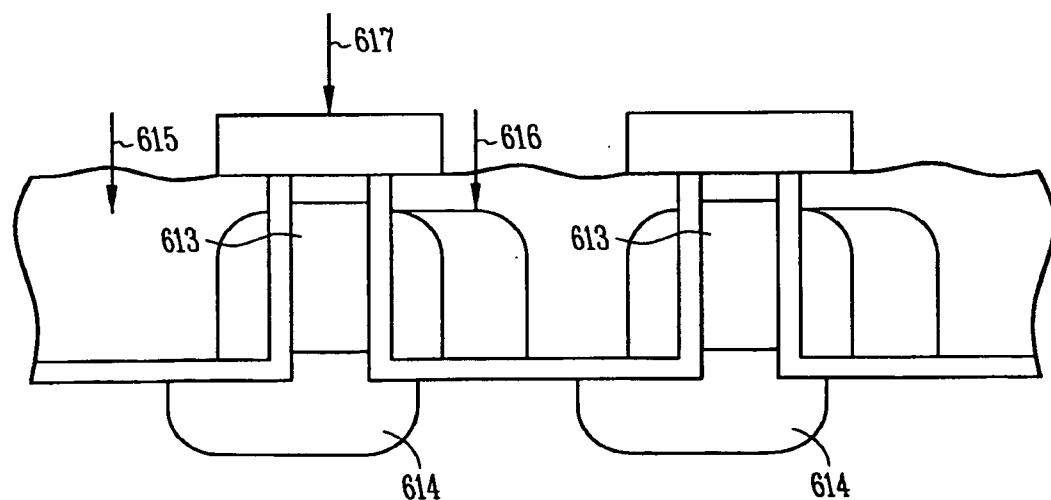

FIGS. 6A-6C illustrate an embodiment of a process to form isolated transistors with source, drain and gate contacts, using the nanorods with wraparound gates illustrated in FIGS. 5A-5H.

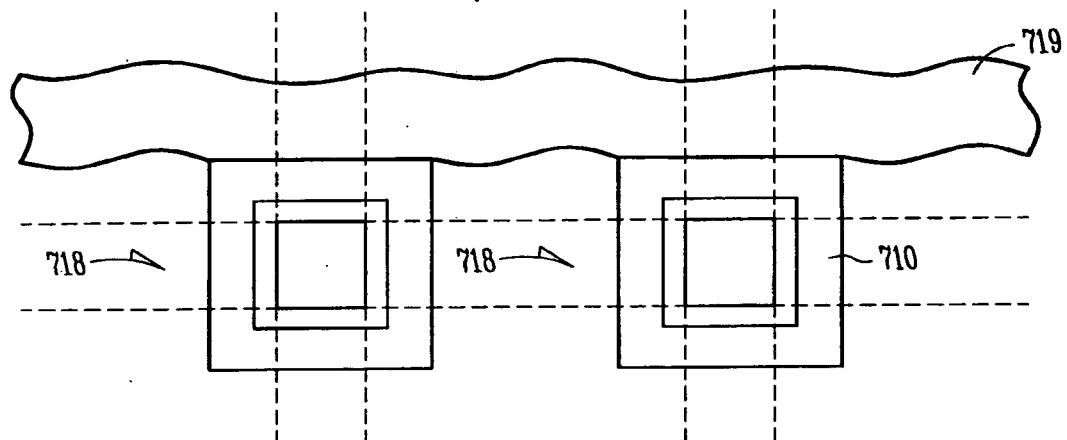

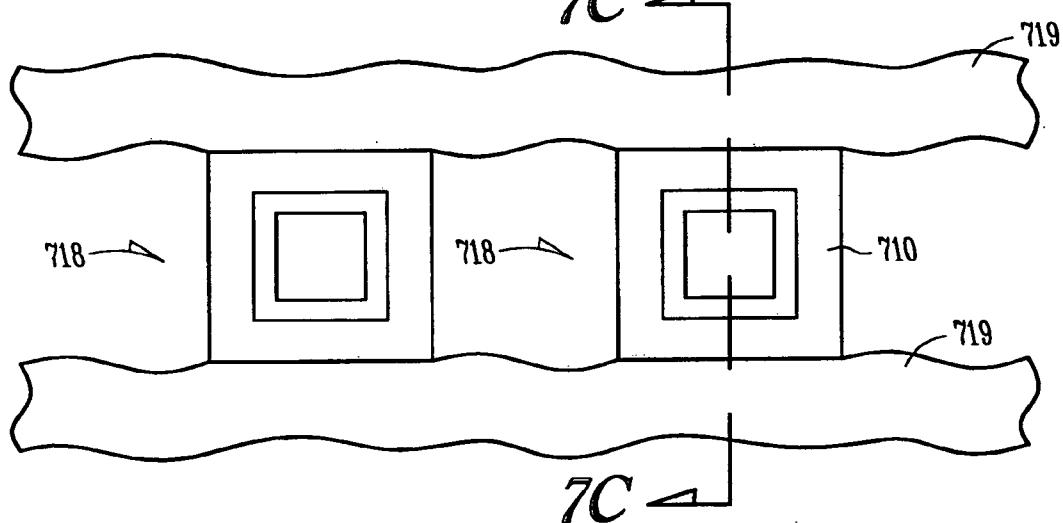

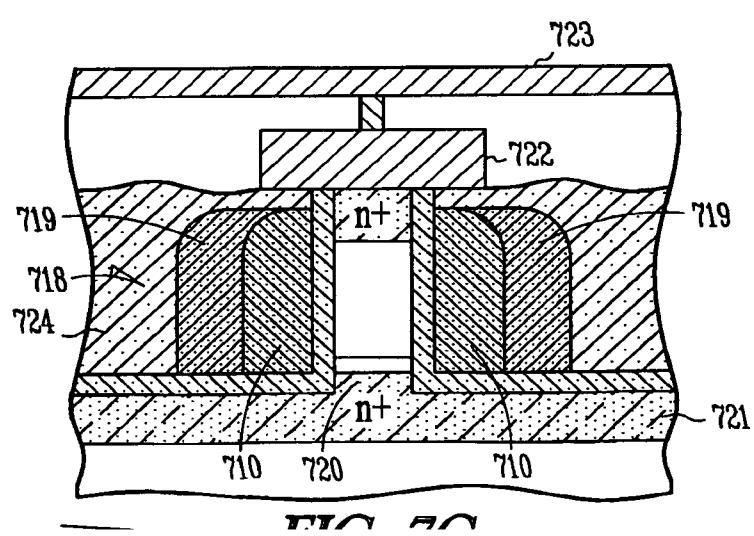

FIGS. 7A-7C illustrate an embodiment of a process to form an array of 10 transistors, using the nanorods with wraparound gates illustrated in FIGS. 5A-5H.

FIG. 8 illustrates a flow diagram for forming a nanowire transistor with surrounding gates, according to various embodiments of the present subject matter.

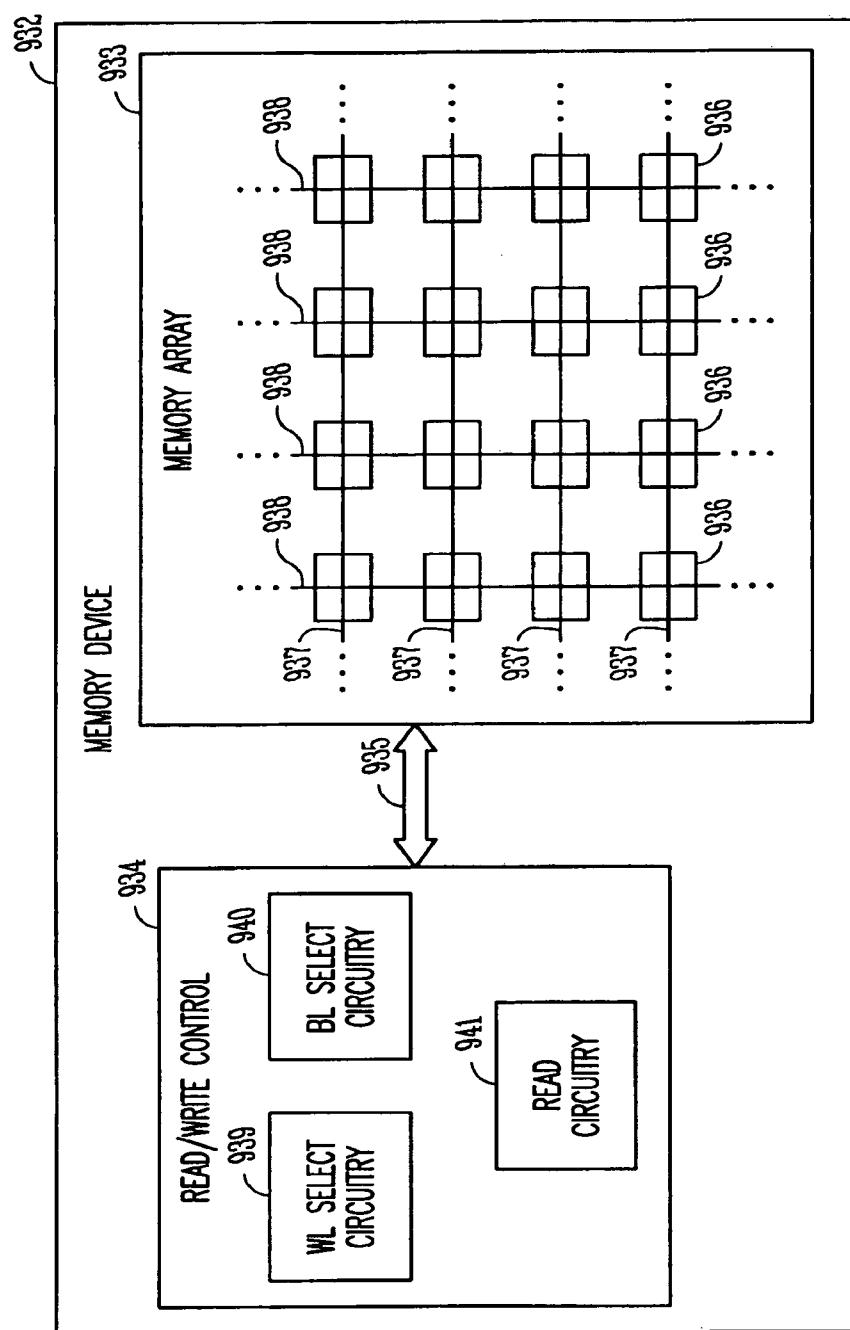

15 FIG. 9 is a simplified block diagram of a high-level organization of various embodiments of a memory device according to various embodiments of the present subject matter.

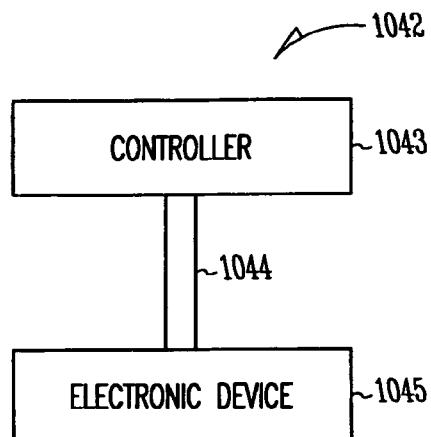

FIG. 10 illustrates a diagram for an electronic system having nanowire transistors, according to various embodiments.

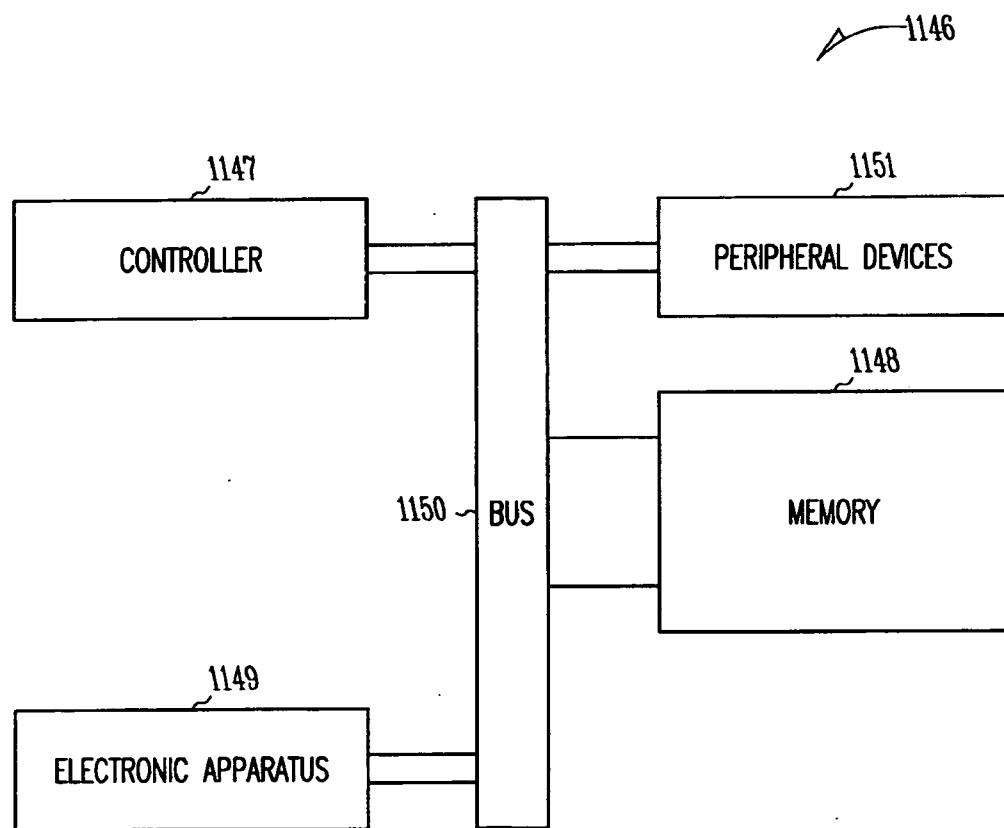

20 FIG. 11 depicts a diagram of an embodiment of a system having a controller and a memory.

### **Detailed Description**

The following detailed description refers to the accompanying drawings 25 which show, by way of illustration, specific aspects and embodiments in which the present subject matter may be practiced. These embodiments are described in sufficient detail to enable those skilled in the art to practice the present subject matter. The various embodiments of the present subject matter are not necessarily mutually exclusive as aspects of one embodiment can be combined 30 with aspects of another embodiment. Other embodiments may be utilized and

structural, logical, and electrical changes may be made without departing from the scope of the present subject matter. In the following description, the terms “wafer” and “substrate” are interchangeably used to refer generally to any structure on which integrated circuits are formed, and also to such structures 5 during various stages of integrated circuit fabrication. Both terms include doped and undoped semiconductors, epitaxial layers of a semiconductor on a supporting semiconductor or insulating material, combinations of such layers, as well as other such structures that are known in the art. The term “horizontal” as used in this application is defined as a plane parallel to the conventional plane or 10 surface of a wafer or substrate, regardless of the orientation of the wafer or substrate. The term “vertical” refers to a direction perpendicular to the horizontal as defined above. Prepositions, such as “on”, “side”, “higher”, “lower”, “over” and “under” are defined with respect to the conventional plane or surface being on the top surface of the wafer or substrate, regardless of the 15 orientation of the wafer or substrate. The following detailed description is, therefore, not to be taken in a limiting sense, and the scope of the present invention is defined only by the appended claims, along with the full scope of equivalents to which such claims are entitled.

The following discussion refers to silicon nanowire transistor 20 embodiments. Those of ordinary skill in the art will understand, upon reading and comprehending this disclosure, how to use the teaching contained herein to form nanowire transistors using other semiconductors.

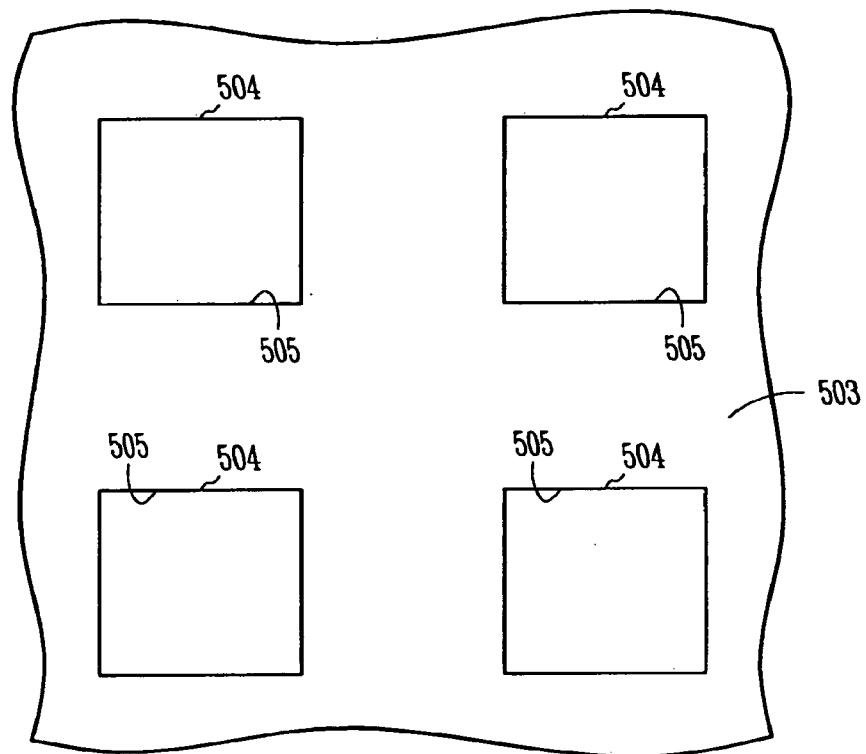

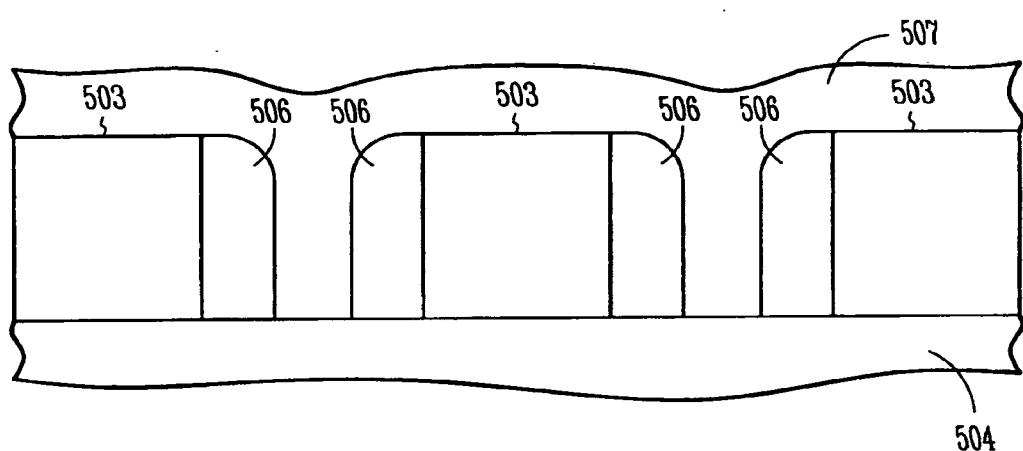

FIGS. 5A-5H illustrate an embodiment of a process to form crystalline nanorods with surrounding gates. FIG. 5A illustrates a first layer 503 on a 25 substrate 504, with holes 505 formed in the first layer. The first layer is able to be etched to define the holes within the layer. According to various embodiments, the holes 505 are formed in a silicon nitride layer 503 on a silicon substrate 504, such that the holes extend through the silicon nitride layer to the silicon substrate. In the illustrated embodiment, the holes are formed with 30 dimensions corresponding to the minimum feature size. The center of each hole

corresponds to the desired location of the nanowire transistor. An array of nanowire transistors can have a center-to-center spacing between rows and columns of 2F.

5 A layer of oxide is provided to cover the first layer after the holes have been etched therein. Various embodiments form a silicon oxide over the silicon nitride layer. Some embodiments deposit the silicon oxide by a chemical vapor deposition (CVD) process.

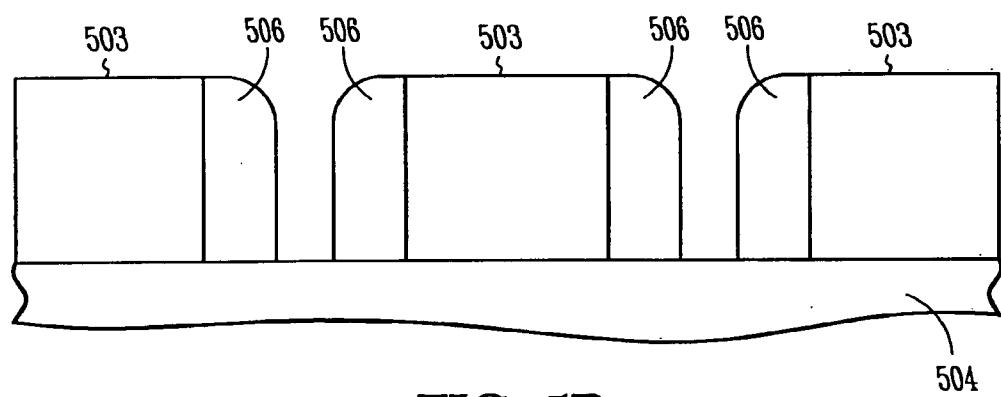

10 FIG. 5B illustrates the structure after the oxide is directionally etched to leave oxide sidewalls 506 on the sides of the hole, which function to reduce the dimensions of the resulting hole, and the resulting structure is planarized. In 100 nm technology, for example, the oxide sidewalls reduce the dimensions of the hole to about 30 nm. In this example, the thickness of the body region for the transistor will be on the order of 1/3 of the feature size. Some embodiments planarize the structure using a chemical mechanical polishing (CMP) process.

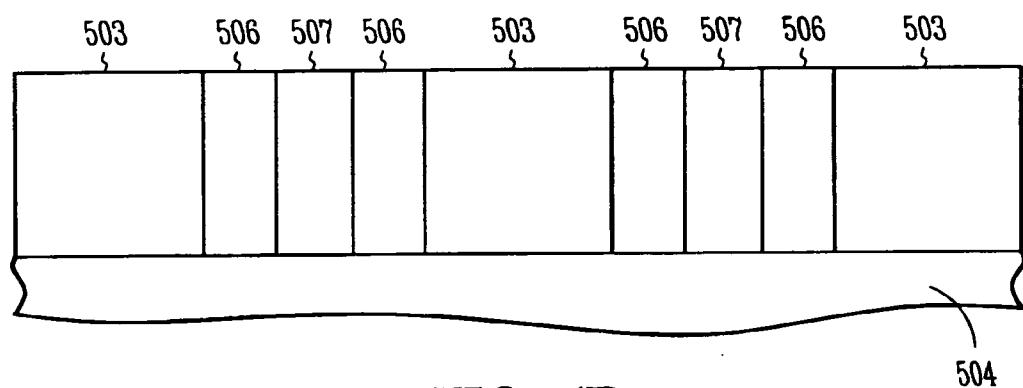

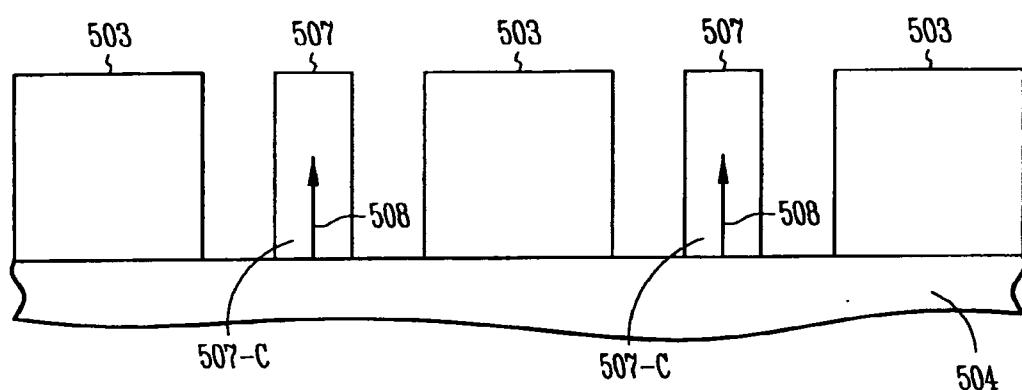

15 FIG. 5C illustrates a thick layer of an amorphous semiconductor material 507 formed over the resulting structure. The amorphous material fills the hole defined by the sidewalls 506. Various embodiments deposit amorphous silicon as the amorphous material. FIG. 5D illustrates the resulting structure after it is planarized, such as by CMP, to leave amorphous semiconductor material only in

20 the holes.

FIG. 5E illustrates the resulting structure after the sidewalls (e.g. silicon oxide sidewalls) are removed. The structure is heat treated to crystallize the amorphous semiconductor 507 (e.g. a-silicon) into crystalline nanorods (represented as 507-C) using a process known as solid phase epitaxy (SPE). The 25 amorphous semiconductor pillar 507 is in contact with the semiconductor wafer (e.g. silicon wafer), and crystal growth in the amorphous semiconductor pillar is seeded by the crystals in the wafer. The crystal formation from the SPE process is illustrated by the arrows 508 in FIG. 5E.

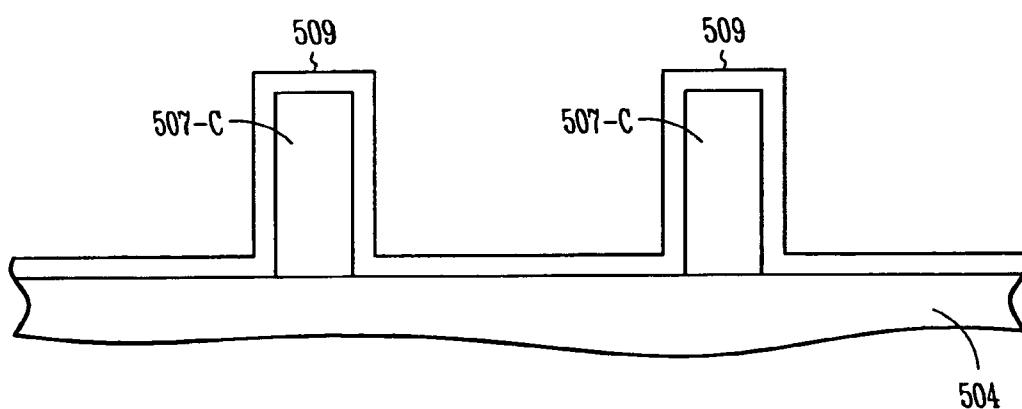

30 FIG. 5F illustrates the structure after the first layer (e.g. silicon nitride) is removed, leaving crystalline nanorods 507-C extending away from the substrate

surface, and after a gate insulator 509 is formed over the resulting structure. An embodiment forms the gate insulator by a thermal oxidation process. Thus, for an embodiment in which the wafer is a silicon wafer and the nanorods are crystalline silicon nanorods, the gate insulator is a silicon oxide. Other gate 5 insulators, such as high K insulators, may be used.

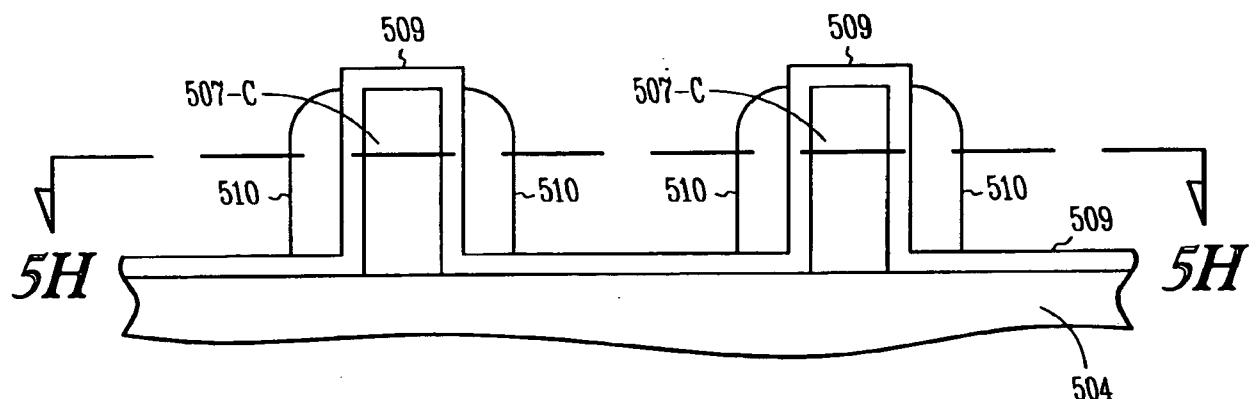

FIG. 5G illustrates a side view and FIG. 5H illustrates a cross-section view along 5H-5H of FIG. 5G view of the structure after a gate material 510 is formed on the sidewalls of the crystalline nanorods 507-C. An embodiment deposits the gate material and etches the resulting structure to leave the gate 10 material only on the sidewalls of the nanorods. Polysilicon is used as the gate material, according to various embodiments. The height of the pillars, which determines the channel length of the transistors, can be less than the minimum lithographic dimensions. Various embodiments provide a channel length on the order of approximately 100 nm. These nanorods with wraparound gates can be 15 used to form nanowire transistors with surrounding or wraparound gates. The process continues in FIGS. 6A-6C for some embodiments of standalone transistors, and continued in FIGS. 7A-7C for some embodiments of transistor arrays.

FIGS. 6A-6C illustrate an embodiment of a process to form isolated 20 transistors with source, drain and gate contacts, using the nanorods with wraparound gates illustrated in FIGS. 5A-5H. The illustrated structure includes a crystalline nanorod 607-C, a gate insulator 609, and a surrounding gate 610. Gate contacts 611 for the wraparound gates are patterned. Various embodiments deposit polysilicon to function as gate contacts for the wraparound gates. Both 25 the wraparound gate and the gate contact, also referred to as a gate pad, are recessed below the top of the nanowire. A directional etching process may be used to recess the wraparound gate and the gate pad. As illustrated in FIG. 6B, the resulting structure is filled with an insulator fill (e.g. oxide) 612 and planarized to the top of the nanowires. The top of the nanowires are exposed by 30 removing the gate insulator from the top of the nanowire. For example, an etch

can be used to remove silicon oxide from the top of the nanowire. The top of the nanowires can be doped and contact areas defined. The doped top portion 613 of the nanowires can function as a drain region. The substrate is appropriately doped to diffuse under the crystalline nanorod, and extend up into a bottom portion of the nanorod. This doped region can function as a source region. This doped region 614 also extends to a contact area. The doped region can be formed before the first layer is deposited and holes formed therein. The dopant can also be implanted and diffused before the surrounding gate is formed. Appropriate doping can be provided to provide NMOS or PMOS transistors.

10 As illustrated in FIG. 6C, a contact 615 can be etched to the buried source, a contact 616 can be etched to the buried gate pad, and a contact 617 can also be formed for the drain. Those of ordinary skill in the art will understand, upon reading and comprehending this disclosure, that other stand alone transistor designs may be used.

15 FIGS. 7A-7C illustrate an embodiment of a process to form an array of transistors, using the nanorods with wraparound gates illustrated in FIGS. 5A-5H. FIG. 7A illustrates a top view of adjacent transistors in a row of an embodiment of a transistor array. According to the illustrated embodiment, one word line 719 is formed adjacent to one row of transistors, such that the wraparound gates 710 of each transistor 718 in the row are in contact with the adjacent word line. FIG. 7B illustrates a top view of adjacent transistors in a row of another embodiment of a transistor array. According to various embodiments, polysilicon or gate material can be used for the gate wiring, a buried doped region can form a source region 720 and the source wiring 721, and metal contacts 722 and metal used for the drain wiring 723. In some embodiments, the nanowire structure with only wraparound gates is then backfilled with oxide and patterned and etched to leave oxide 724 between the pillars in one direction and expose the wrap around gates on the side. Polysilicon can be deposited and directionally etched to leave only on the sidewalls of the oxide blocks and exposed gate sides. As described with respect to FIG. 6C, the wraparound gates

can be further directionally etched to recess them below the top of the nanowire transistors. This will form the gate contacts and wiring. The structure can be planarized and backfilled with oxide and the top of the nanowires doped and contacted for the drain wiring using conventional techniques. Those of ordinary skill in the art will understand, upon reading and comprehending this disclosure, that other transistor array designs may be used.

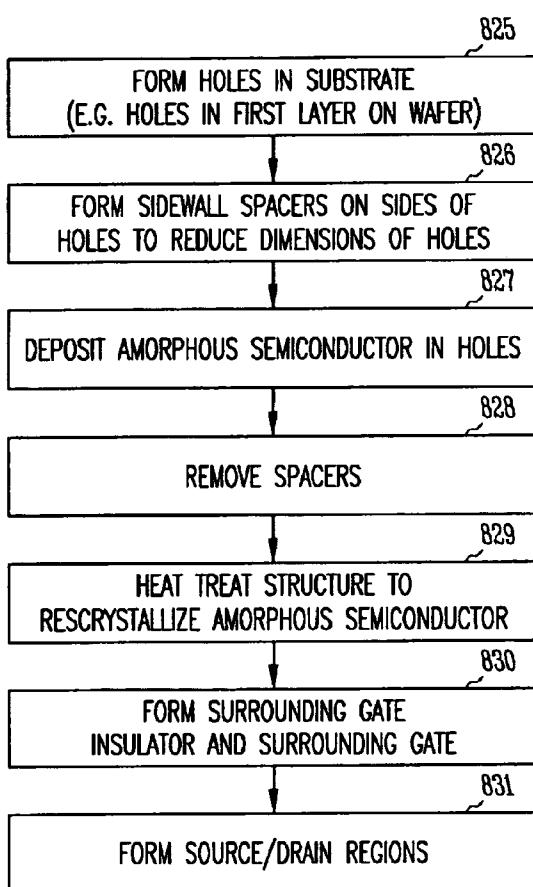

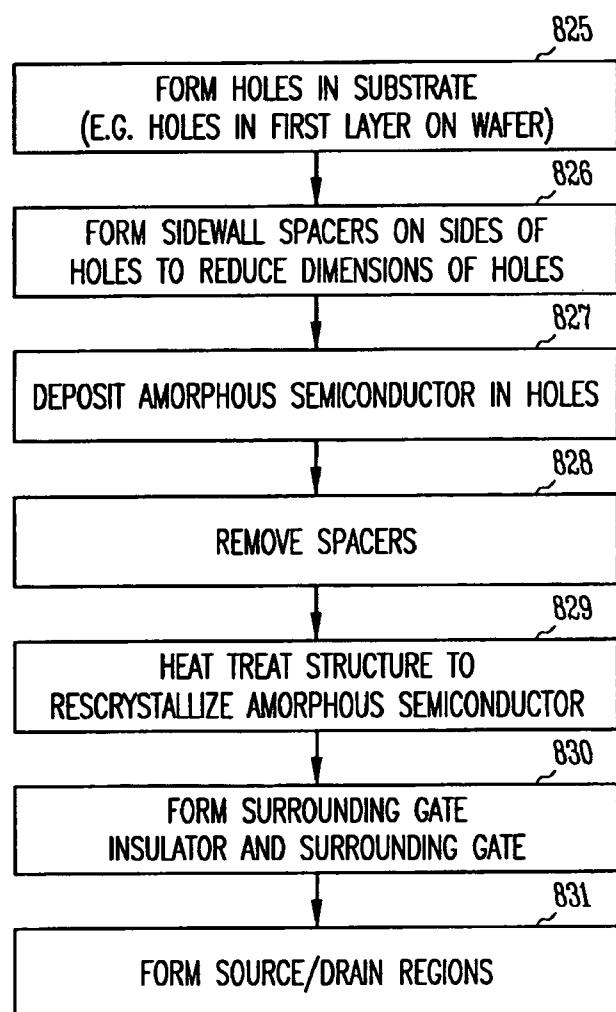

FIG. 8 illustrates a flow diagram for forming a nanowire transistor with surrounding gates, according to various embodiments of the present subject matter.

- 10 At 825, holes are formed in a substrate. For example, the substrate can include a first layer on a wafer, such as a layer of silicon nitride on a silicon wafer, and the holes are formed in the first layer to expose the wafer. The holes are defined by walls formed by the first layer. At 826, spacer sidewalls are formed within the holes against the walls formed by the first layer to effectively reduce the dimensions of the holes. An example of a spacer sidewall is silicon oxide. At 15 827, the holes are filled by an amorphous semiconductor (e.g. a-silicon). The spacer sidewalls are removed at 828, leaving pillars of amorphous semiconductor extending away from the wafer. The resulting structure is heat-treated or annealed at 829 to recrystallize the amorphous semiconductor, using the wafer to seed the crystalline growth. The recrystallization process is referred to as solid phase epitaxy (SPE). The resulting structure includes crystalline nanowires extending away from the wafer. At 830, a surrounding gate insulator and a surrounding gate are formed around the crystalline nanowires. Source/drain regions are formed at 831. The bottom of the nanowire is doped to form a first 20 source/drain region, and the top of the nanowire is doped to form a second source/drain region. The first source/drain region can be formed by doping the substrate before depositing the first layer and patterning and etching the holes. The first source/drain can also be formed by implanting dopants adjacent to the nanorod before the gate is formed. These implanted dopants are capable of 25

diffusing completely under the nanorod because the nanorods are very thin. This doping can be performed after the first layer is removed off of the substrate.

FIG. 9 is a simplified block diagram of a high-level organization of various embodiments of a memory device according to various embodiments of 5 the present subject matter. The illustrated memory device 932 includes a memory array 933 and read/write control circuitry 934 to perform operations on the memory array via communication line(s) or channel(s) 935. The illustrated memory device 932 may be a memory card or a memory module such as a single inline memory module (SIMM) and dual inline memory module (DIMM). One 10 of ordinary skill in the art will understand, upon reading and comprehending this disclosure, that semiconductor components in the memory array and / or the control circuitry are able to be fabricated using the nanowire transistors with surrounding gates, as described above. The structure and fabrication methods for these devices have been described above.

15 The memory array 933 includes a number of memory cells 936. The memory cells in the array are arranged in rows and columns. In various embodiments, word lines 937 connect the memory cells in the rows, and bit lines 938 connect the memory cells in the columns. The read/write control circuitry 934 includes word line select circuitry 939 which functions to select a desired 20 row, bit line select circuitry 940 which functions to select a desired column, and read circuitry 941 which functions to detect a memory state for a selected memory cell in the memory array 933.

FIG. 10 illustrates a diagram for an electronic system 1042 having one or 25 more nanowire transistors with surrounding gates, according to various embodiments. The electronic system includes a controller 1043, a bus 1044, and an electronic device 1045, where the bus provides communication channels between the controller and the electronic device. In various embodiments, the controller and/or electronic device include nanowire transistors as previously discussed herein. The illustrated electronic system may include, but is not 30 limited to, information handling devices, wireless systems, telecommunication

systems, fiber optic systems, electro-optic systems, and computers.

FIG. 11 depicts a diagram of an embodiment of a system 1146 having a controller 1147 and a memory 1148. The controller and/or memory may include nanowire transistors. The illustrated system also includes an electronic apparatus 5 1149 and a bus 1150 to provide communication channel(s) between the controller and the electronic apparatus, and between the controller and the memory. The bus may include an address, a data bus, and a control bus, each independently configured; or may use common communication channels to provide address, data, and/or control, the use of which is regulated by the controller. In an embodiment, the electronic apparatus 1149 may be additional memory configured similar to memory 1148. An embodiment may include a peripheral device or devices 1151 coupled to the bus. Peripheral devices may include displays, additional storage memory, or other control devices that may operate in conjunction with the controller and/or the memory. In an 10 embodiment, the controller is a processor. Any of the controller, the memory, the electronic apparatus, and the peripheral devices may include nanowire transistors. The system may include, but is not limited to, information handling devices, telecommunication systems, and computers. Applications containing nanowire transistors as described in this disclosure include electronic systems for 15 use in memory modules, device drivers, power modules, communication modems, processor modules, and application-specific modules, and may include multilayer, multichip modules. Such circuitry can further be a subcomponent of a variety of electronic systems, such as a clock, a television, a cell phone, a personal computer, an automobile, an industrial control system, an aircraft, and 20 others.

25

The memory may be realized as a memory device containing nanowire transistors according to various embodiments. It will be understood that embodiments are equally applicable to any size and type of memory circuit and are not intended to be limited to a particular type of memory device. Memory 30 types include a DRAM, SRAM (Static Random Access Memory) or Flash

memories. Additionally, the DRAM could be a synchronous DRAM commonly referred to as SGRAM (Synchronous Graphics Random Access Memory), SDRAM (Synchronous Dynamic Random Access Memory), SDRAM II, and DDR SDRAM (Double Data Rate SDRAM). Various emerging memory

5 technologies are capable of using nanowire transistors.

This disclosure includes several processes, circuit diagrams, and structures. The present subject matter is not limited to a particular process order or logical arrangement. Although specific embodiments have been illustrated and described herein, it will be appreciated by those of ordinary skill in the art

10 that any arrangement which is calculated to achieve the same purpose may be substituted for the specific embodiments shown. This application is intended to cover adaptations or variations of the present subject matter. It is to be understood that the above description is intended to be illustrative, and not restrictive. Combinations of the above embodiments, and other embodiments,

15 will be apparent to those of skill in the art upon reviewing and understanding the above description. The scope of the present subject matter should be determined with reference to the appended claims, along with the full scope of equivalents to which such claims are entitled.

**What is claimed is:**

1. A method for forming a transistor, comprising:

- 5 forming a transistor body, including:

- forming a pillar of amorphous semiconductor material on a crystalline substrate, the pillar having a sublithographic thickness; and

- 10 performing a solid phase epitaxy (SPE) process to crystallize the amorphous semiconductor material using the crystalline substrate to seed the crystalline growth, the transistor body being formed in the crystallized semiconductor pillar between a first source/drain region and a second source/drain region;

- 15 forming a surrounding gate insulator around the semiconductor pillar; and

- 20 forming a surrounding gate around and separated from the semiconductor pillar by the surrounding gate insulator.

2. The method of claim 1, wherein forming a pillar of amorphous semiconductor material on a crystalline substrate includes forming a pillar of amorphous silicon on a crystalline silicon substrate;

- 25 3. The method of claim 1, wherein forming the surrounding gate insulator includes forming a silicon oxide.

4. The method of claim 1, wherein forming a surrounding gate includes forming a polysilicon gate.

5. The method of claim 1, wherein forming a surrounding gate includes forming a metal gate.

6. The method of claim 1, further comprising recessing the surrounding gate 5 such that the surrounding gate has a height less than a height of the pillar.

7. The method of claim 1, further comprising forming the first source/drain region in the substrate and forming the second source/drain region in a top portion of the pillar.

10

8. A method for forming a transistor, comprising:

forming a transistor body, including:

- forming silicon nitride on a silicon wafer;

- etching a hole in the silicon nitride, the hole having a minimum feature size and extending through the silicon nitride to the silicon wafer;

- reducing a dimension of the hole to less than the minimum feature size, including forming silicon oxide sidewall spacers on sides of the silicon nitride that define the hole;

- 20 filling the hole with an amorphous silicon;

- removing the silicon oxide sidewall spacers to leave an amorphous silicon pillar in contact with and extending from the wafer; and

- 25 crystallizing the silicon pillar to form a crystalline silicon pillar, the transistor body being formed in the crystalline silicon pillar between a first source/drain region and a second source/drain region;

- forming a surrounding gate insulator around the semiconductor pillar;

and

forming a surrounding gate around and separated from the semiconductor pillar by the surrounding gate insulator.

9. The method of claim 8, wherein the height of the crystalline silicon pillar

5 is less than the minimum feature size.

10. The method of claim 8, wherein forming a surrounding gate insulator includes oxidizing the crystalline silicon pillar.

10 11. The method of claim 8, further comprising etching source, gate and drain contacts for a stand-alone transistor.

12. The method of claim 8, further comprising forming a source line, at least one gate line, and a drain contact for a transistor array.

15

13. A method for forming a transistor, comprising:

forming a transistor body, including:

forming silicon nitride on a silicon wafer;

etching a hole in the silicon nitride, the hole having a minimum

20 feature size and extending through the silicon nitride to

the silicon wafer;

forming silicon oxide sidewall spacers on sides of the silicon

nitride that define the hole;

filling the hole with an amorphous silicon, the amorphous silicon

25 being in contact with the silicon wafer;

removing the silicon oxide sidewall spacers to leave an

amorphous silicon pillar in contact with and extending

from the wafer; and

crystallizing the silicon pillar to form a crystalline silicon pillar,

30 the transistor body being formed in the crystalline silicon

pillar between a first source/drain region and a second source/drain region;

forming a surrounding gate insulator around the silicon pillar; and

forming a surrounding gate around and separated from the silicon pillar

5 by the surrounding gate insulator.

14. The method of claim 13, further comprising forming a first contact on the wafer in contact with the first source/drain region, forming a gate contact in contact with the surrounding gate, and forming a second contact on the silicon

10 pillar in contact with the second source/drain region.

15. The method of claim 13, wherein forming a surrounding gate insulator includes oxidizing the silicon pillar.

15 16. A method, comprising:

forming a silicon nitride layer on a silicon wafer;

etching a hole in the silicon nitride layer, the hole having a minimum feature size and extending through the silicon nitride to the silicon wafer;

forming silicon oxide sidewall spacers within the hole in contact with the

20 silicon nitride;

filling the hole with an amorphous silicon, the amorphous silicon being in contact with the silicon wafer;

removing the silicon oxide sidewall spacers to leave an amorphous silicon pillar in contact with and extending from the wafer;

25 crystallizing the silicon pillar to form a crystalline silicon pillar;

removing the silicon nitride from the wafer;

forming an insulator layer on the wafer and the silicon pillar;

forming a surrounding gate around and separated from the silicon pillar

by the surrounding gate insulator;

30 forming a first source/drain diffusion region in the wafer;

forming a gate contact adjacent to the surround gate;

etching a top surface of the surrounding gate and a top surface of the gate contact to be below a top surface of the pillar;

filling the structure with an insulator;

5 forming a second source/drain diffusion region in a top portion of the pillar; and

forming contacts through the insulator to the first source/drain region, the second source/drain region and the gate contact.

10 17. The method of claim 16, wherein forming an insulator on the wafer and the silicon pillar includes oxidizing the wafer and the silicon pillar.

18. The method of claim 16, wherein forming a surrounding gate includes forming a polysilicon gate.

15 19. A method, comprising:

forming at least one buried source conductor in a silicon wafer;

forming a silicon nitride layer on the silicon wafer;

etching a plurality of holes in the silicon nitride, the plurality of holes

20 being arranged in an array of rows and columns, each hole having a minimum feature size and extending through the silicon nitride to the silicon wafer, at least two of the plurality of holes being formed over the buried source conductor;

forming silicon oxide sidewall spacers within each hole in contact with the silicon nitride;

25 filling each hole with an amorphous silicon, the amorphous silicon being in contact with the silicon wafer, the amorphous silicon in at least two of the plurality of holes being in contact with the buried source conductor in the silicon wafer;

removing the silicon oxide sidewall spacers to leave amorphous silicon pillar in contact with and extending from the wafer, the amorphous silicon pillar having cross-sectional dimensions less than the minimum feature size; and

5       crystallizing the silicon pillar to form a crystalline silicon pillar;

removing the silicon nitride from the wafer;

forming an insulator layer on the wafer and the silicon pillar;

10      forming a surrounding gate around and separated from the silicon pillar by the surrounding gate insulator;

forming at least one gate line adjacent to each row, the at least one gate line being in contact with each surrounding gate in the row;

15      etching a top surface of the surrounding gate and a top surface of the gate contact to be below a top surface of the pillar;

filling the structure with an insulator;

forming a second source/drain diffusion region in a top portion of the pillar; and

forming a contact to the second source/drain region.

20.     The method of claim 19, wherein forming an insulator on the wafer and the silicon pillar includes oxidizing the wafer and the silicon pillar.

20

21.     The method of claim 19, wherein forming a surrounding gate includes forming a polysilicon gate.

22.     The method of claim 19, wherein forming at least one buried source conductor in a silicon wafer includes implanting a dopant in the silicon wafer.

25

23.     A transistor, comprising:

a crystalline substrate;

a first source/drain region formed in the crystalline substrate;

a crystalline semiconductor pillar formed on the substrate in contact with the first source/drain region, the semiconductor pillar having cross-section dimensions less than a minimum feature size;

5        a second source/drain region formed in a top portion of the pillar;

a gate insulator formed around the pillar; and

a surrounding gate formed around and separated from the pillar by the gate insulator.

24.      The transistor of claim 23, wherein the semiconductor pillar has a cross-

10     section dimension on the order of one third of the minimum feature size.

25.      The transistor of claim 23, wherein the semiconductor pillar has a cross-

section dimension on the order of 30 nm.

15     26.      The transistor of claim 23, wherein the gate insulator includes silicon

oxide.

27.      The transistor of claim 23, wherein the gate includes a polysilicon gate.

20     28.      The transistor of claim 23, wherein the gate includes a metal gate.

29.      A transistor, comprising:

a crystalline silicon substrate;

a first source/drain region formed in the crystalline silicon substrate;

25     a crystalline silicon pillar formed on the substrate in contact with the first

source/drain region, the silicon pillar having cross-section dimensions less than a

minimum feature size;

a second source/drain region formed in a top portion of the pillar;

a gate insulator formed around the pillar;

a surrounding gate formed around and separated from the pillar by the gate insulator; and

5 a gate contact positioned adjacent to and in contact with the surrounding gate, the surrounding gate and the gate contact being etched to have a top surface below a top surface of the pillar.

30. The transistor of claim 29, wherein the semiconductor pillar has a cross-section dimension on the order of one third of the minimum feature size.

10 31. The transistor of claim 29, wherein the semiconductor pillar has a cross-section dimension on the order of 30 nm.

32. A transistor, comprising:

a crystalline silicon substrate;

15 a first source/drain region formed in the crystalline silicon substrate; a crystalline silicon pillar formed on the substrate in contact with the first source/drain region, the silicon pillar having cross-section dimensions less than a minimum feature size;

a second source/drain region formed in a top portion of the pillar;

20 a gate insulator formed around the pillar;

a surrounding gate formed around and separated from the pillar by the gate insulator; and

25 at least one gate line positioned adjacent to and in contact with the surrounding gate, the surrounding gate and the gate line being etched to have a top surface below a top surface of the pillar.

33. The transistor of claim 32, wherein the at least one gate line includes first and second gate lines adjacent to and in contact with the surrounding gate on opposing sides of the pillar.

34. A semiconductor structure, comprising:

- a crystalline substrate; and

- a semiconductor pillar formed on the substrate in contact with the first source/drain region, the semiconductor pillar having cross-section dimensions

- 5 less than a minimum feature size, the semiconductor pillar having a crystallized bottom portion and an amorphous top portion indicative of a partially-completed solid phase epitaxy (SPE) process.

35. The structure of claim 34, further comprising a silicon nitride layer on the

10 substrate, the silicon nitride layer being separated from the pillar by a void.

1/12

$$V_G \longrightarrow V_G/k$$

$$V_0 \longrightarrow V_0/k$$

$$t_{ox} \longrightarrow t_{ox}/k$$

$$L \longrightarrow L/k$$

$$x_j \longrightarrow x_j/k$$

JUNCTION DEPTH DECREASED

$$w_d \longrightarrow w_d/k$$

$$N_A \longrightarrow k N_A$$

SUBSTRATE DOPING INCREASED

FIG. 1

2/12

FIG. 2

FIG. 3

3/12

FIG. 4

4/12

*FIG. 5A*

*FIG. 5B*

5/12

6/12

FIG. 5E

FIG. 5F

7/12

FIG. 5G

FIG. 5H

8/12

FIG. 6A

FIG. 6B

FIG. 6C

9/12

FIG. 7A

7C

FIG. 7B

723

FIG. 8C

10/12

FIG. 8

11/12

FIG. 9

12/12

FIG. 10

FIG. 11

# INTERNATIONAL SEARCH REPORT

International application No

PCT/US2007/008123

|                                     |      |            |           |            |             |           |

|-------------------------------------|------|------------|-----------|------------|-------------|-----------|

| A. CLASSIFICATION OF SUBJECT MATTER | INV. | H01L21/336 | H01L29/06 | H01L29/786 | H01L21/8242 | H01L21/20 |

|-------------------------------------|------|------------|-----------|------------|-------------|-----------|

According to International Patent Classification (IPC) or to both national classification and IPC

**B. FIELDS SEARCHED**

Minimum documentation searched (classification system followed by classification symbols)

H01L

Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched

Electronic data base consulted during the international search (name of data base and, where practical, search terms used)

EPO-Internal

**C. DOCUMENTS CONSIDERED TO BE RELEVANT**

| Category* | Citation of document, with indication, where appropriate, of the relevant passages                                             | Relevant to claim No. |

|-----------|--------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| X         | US 2005/032297 A1 (KAMINS THEODORE I [US])<br>10 February 2005 (2005-02-10)<br>paragraphs [0041] - [0047]; figure 1<br>-----   | 23-34                 |

| Y         | US 2006/046391 A1 (TANG SANH D [US] ET AL)<br>2 March 2006 (2006-03-02)<br>paragraphs [0117] - [0119]; figures 7B-10B<br>----- | 1-22                  |

| X         | US 6 855 582 B1 (DAKSHINA-MURTHY<br>SRIKANTESWARA [US] ET AL)<br>15 February 2005 (2005-02-15)<br>figures 12-14<br>-----       | 23-34                 |

| Y         | DE 199 43 390 A1 (HANSCH WALTER [DE])<br>3 May 2001 (2001-05-03)<br>column 4, line 36 - line 44<br>-----                       | 1-22                  |

Further documents are listed in the continuation of Box C.

See patent family annex.

\* Special categories of cited documents :

- \*A\* document defining the general state of the art which is not considered to be of particular relevance

- \*E\* earlier document but published on or after the international filing date

- \*L\* document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)

- \*O\* document referring to an oral disclosure, use, exhibition or other means

- \*P\* document published prior to the international filing date but later than the priority date claimed

\*T\* later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention

\*X\* document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone

\*Y\* document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art.

\*&\* document member of the same patent family

Date of the actual completion of the international search

Date of mailing of the international search report

14 August 2007

21/08/2007

Name and mailing address of the ISA/

European Patent Office, P.B. 5818 Patentlaan 2

NL - 2280 HV Rijswijk

Tel. (+31-70) 340-2040, Tx. 31 651 epo nl,

Fax: (+31-70) 340-3016

Authorized officer

Juh1, Andreas

**INTERNATIONAL SEARCH REPORT**

Information on patent family members

International application No

PCT/US2007/008123

| Patent document cited in search report | Publication date | Patent family member(s) | Publication date |

|----------------------------------------|------------------|-------------------------|------------------|

| US 2005032297                          | A1 10-02-2005    | NONE                    |                  |

| US 2006046391                          | A1 02-03-2006    | US 2007048943 A1        | 01-03-2007       |

| US 6855582                             | B1 15-02-2005    | NONE                    |                  |

| DE 19943390                            | A1 03-05-2001    | NONE                    |                  |