(19) 日本国特許庁(JP)

## (12) 特 許 公 報(B2)

(11) 特許番号

特許第4265722号

(P4265722)

(45) 発行日 平成21年5月20日(2009.5.20)

(24) 登録日 平成21年2月27日(2009.2.27)

(51) Int.Cl.

G06F 17/50 (2006.01)

F 1

G06F 17/50 658R

G06F 17/50 658M

G06F 17/50 654G

請求項の数 3 (全 9 頁)

(21) 出願番号 特願2000-238152 (P2000-238152)

(22) 出願日 平成12年8月7日 (2000.8.7)

(65) 公開番号 特開2002-49653 (P2002-49653A)

(43) 公開日 平成14年2月15日 (2002.2.15)

審査請求日 平成18年7月26日 (2006.7.26)

(73) 特許権者 308014341

富士通マイクロエレクトロニクス株式会社

東京都新宿区西新宿二丁目7番1号

(74) 代理人 100092587

弁理士 松本 真吉

(72) 発明者 五十嵐 俊二

神奈川県川崎市中原区上小田中4丁目1番

1号 富士通株式会社内

(72) 発明者 小池 和範

神奈川県川崎市中原区上小田中4丁目1番

1号 富士通株式会社内

審査官 松浦 功

最終頁に続く

(54) 【発明の名称】パターンデータ修正方法及び装置

## (57) 【特許請求の範囲】

## 【請求項 1】

設計された回路のパターンデータを修正するパターンデータ修正方法において、コンピュータにより、

图形の種類と、製作されるマスクに対応したレイヤと、座標値とを含む图形データについて、該图形が内接する矩形の隣り合う2辺の長さである图形サイズを求め、該图形サイズを該图形データに付加し、

該種類、該レイヤ及び該サイズが同一である該图形データに同一のグループ名を付加することにより、該图形データをグループ化し、

選択された图形データを修正した場合、この图形データと同一グループの他の图形データを自動修正する。 10

ことを特徴とするパターンデータ修正方法。

## 【請求項 2】

設計された回路のパターンデータを修正するパターンデータ修正装置において、

图形の種類と、製作されるマスクに対応したレイヤと、座標値とを含む图形データについて、該图形が内接する矩形の隣り合う2辺の長さである图形サイズを求め、該图形サイズを該图形データに付加し、

該種類、該レイヤ及び該サイズが同一である該图形データに同一のグループ名を付加することにより、該图形データをグループ化し、

選択された图形データを修正した場合、この图形データと同一グループの他の图形データを自動修正する。 20

タを自動修正する、

コンピュータを有することを特徴とするパターンデータ修正装置。

【請求項 3】

設計された回路のパターンデータを修正するためには、コンピュータに対し、

図形の種類と、製作されるマスクに対応したレイヤと、座標値とを含む图形データについて、該图形が内接する矩形の隣り合う2辺の長さである图形サイズを求めさせ、該图形サイズを該图形データに付加させ、

該種類、該レイヤ及び該サイズが同一である該图形データに同一のグループ名を付加させることにより、該图形データをグループ化させ、

選択された图形データを修正した場合、この图形データと同一グループの他の图形データを自動修正させる、

ためのプログラムが記録されたことを特徴とするコンピュータ読み取り可能な記録媒体。

。【発明の詳細な説明】

【0001】

【発明の属する技術分野】

本発明は、設計された回路のパターンデータを修正するパターンデータ修正方法及び装置に関する。

【0002】

【従来の技術】

半導体集積回路の多機能化及びパターン高密度化に伴い、設計データ量が増大する傾向にあり、設計されたパターンデータの修正を短時間で行なうことが要求されている。

【0003】

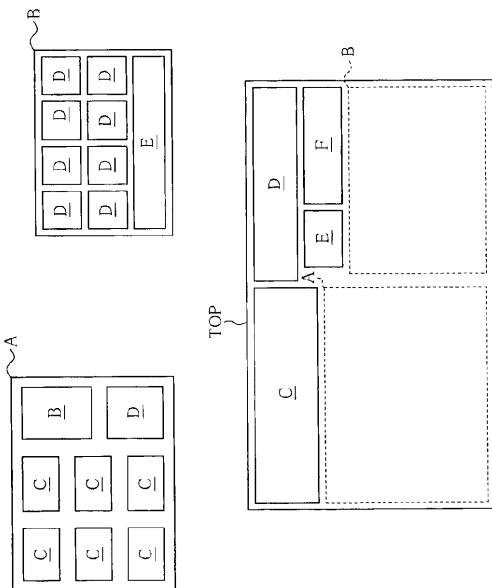

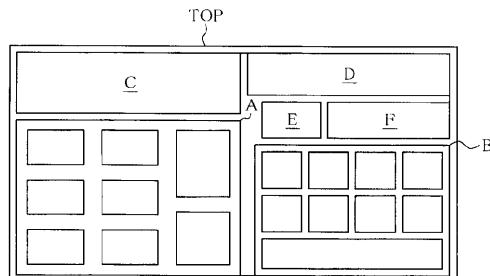

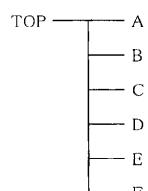

図6は、半導体集積回路の設計データのセル配置を視覚的に示す概略ブロック図である。

【0004】

例えば、半導体集積回路メーカーは、チップ全体のセルTOPのうちセルC～Fを設計し、外部のある会社にセルAの設計を依頼し、他の会社にセルBの設計を依頼し、出来上がったセルA及びBをセルTOP内に配置する。一般に、設計されたセルTOP、A及びBのCADデータのフォーマットは互いに異なり、セルA及びBをセルTOP内に配置する際にこれらのフォーマットが統一されたフォーマット、例えばGDS2フォーマットに変換される。セルTOP、A及びBの中のセル名はそれぞれ独立に付けられており、例えばセルTOP内のセルCとセルA内のセルCとは、セル名が同一であってもその内容は異なる。

【0005】

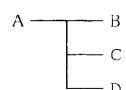

図8(A)、(B)及び(C)はそれぞれ、図6中のセルA、B及びTOPの階層構造を示す。実際にはこれらの階層構造は複雑であるが、説明上、簡単なものが示されている。

【0006】

セルA及びBをセルTOP内に配置する際、一般にフォーマットが互いに異なるので、セルA及びB内が展開されて階層構造が無くなる。

【0007】

図7は、セルTOP内にセルA及びBが配置された状態を視覚的に示す。

【0008】

図9は、図7のセルTOPに含まれる图形データを示す。各セルは、複数の图形データを含む。

【0009】

图形は、その種類が矩形(REC)の場合、対角点の座標で表され、種類が多角形(POL)の場合、各頂点の座標で表され、種類が配線の場合、両端の座標で表される。

【0010】

【発明が解決しようとする課題】

図7において、セルA内の图形を修正する場合、セルAのデータをセルTOPのファイル

10

20

30

40

50

から抽出して別ファイルとし、表示画像を見ながら入力装置を操作して、修正すべき図形を選択し修正を行なう。

【0011】

しかし、例えば同一サイズのコンタクトホールパターンを100個を修正する場合、1個ずつ修正しなければならず、1個当たりの修正時間が約10秒である場合、100個修正すると全修正時間は約20分となる。セルTOPからセルAとBの図形データを抽出し、これらを1つの別ファイルとし、セルA及びBに含まれている複数の同一図形を修正する場合についても同様である。

【0012】

本発明の目的は、このような問題点に鑑み、設計された回路のパターンデータをより短時間で修正することが可能なパターンデータ修正方法及び装置を提供することにある。 10

【0013】

【課題を解決するための手段及びその作用効果】

本発明では、設計された回路のパターンデータを修正するパターンデータ修正方法において、コンピュータにより、

同一図形データを同一グループにすることにより図形データをグループ化し、選択された図形データを修正した場合、この図形データと同一グループの他の図形データを自動修正する。

【0014】

この方法によれば、グループ化と自動修正とにより、設計された回路のパターンデータをより短時間で修正することができる。 20

【0015】

本発明の他の目的、構成及び効果は以下の説明から明らかになる。

【0016】

【発明の実施の形態】

以下、図面を参照して本発明の実施形態を説明する。

【0017】

[第1実施形態]

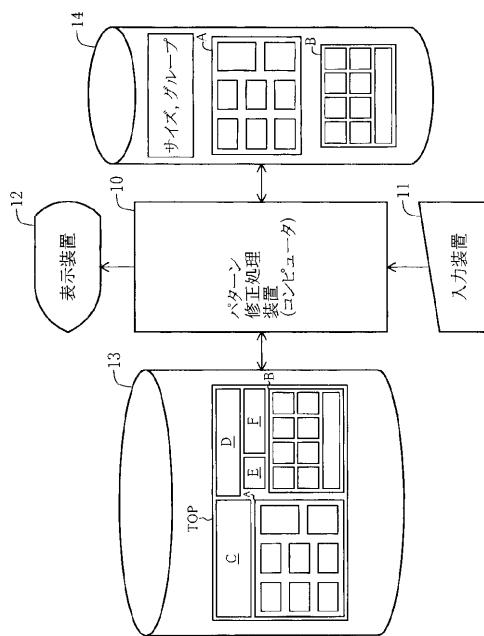

図1は、本発明の第1実施形態のパターンデータ修正装置を示す概略ブロック図である。

【0018】

この装置は、パターン修正プログラムがインストールされたコンピュータであるパターン修正処理装置10に、入力装置11、表示装置12、記憶装置13及び14が接続されたシステムである。 30

【0019】

記憶装置13には、例えば図7に示すセルTOPの設計データが格納されており、より具体的には図9に示すような図形データが格納されている。

【0020】

表示装置12の表示を見ながら入力装置11を操作して、セルTOPに含まれている例えばセルA及びBを修正対象として選択する。パターン修正処理装置10はこれに応答して、図4に示す処理を行なう。すなわち、パターン修正処理装置10は、セルA及びBをセルTOPから抽出し、これを別ファイルとして記憶装置14に格納し、記憶装置14に格納されている図9に示す図形データに対し、サイズ及びグループのデータを付加し、図2に示すようなデータを作成する。 40

【0021】

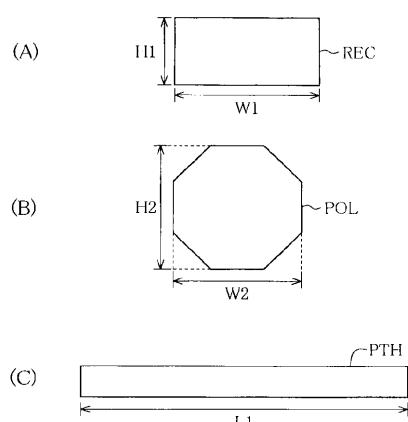

図3(A)、(B)及び(C)はそれぞれ、矩形REC、多角形POL及び配線PTHのサイズを示す。

【0022】

矩形RECのサイズは、横及び縦の長さがW1及びH1である。多角形POLのサイズは、これが内接される矩形の横及び縦の長さW2及びH2である。配線PTHのサイズは、線の長さL1であり、線幅の値はレイヤ毎に統一して与えられている。 50

## 【0023】

マスクは、レイヤ毎に製作される。

## 【0024】

図形の種類、レイヤ及びサイズが同一である場合、同一グループ名を付与する。例えばNO.1とNO.3は図形の種類、レイヤ及びサイズが同一であり、同一グループ名G1が付与されている。

## 【0025】

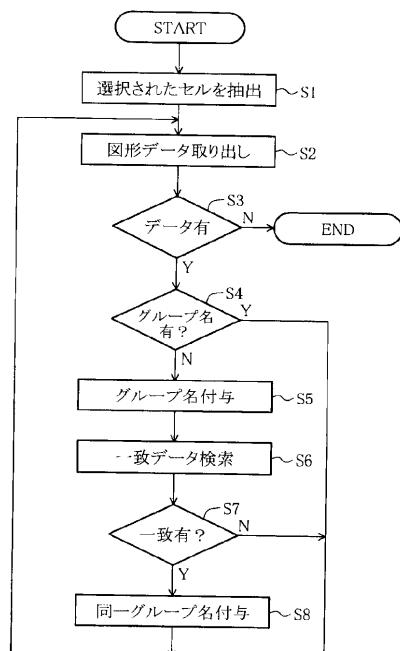

次に、図4のグループ化処理を説明する。

## 【0026】

(S1)セルA及びBをセルTOPから抽出し、これを別ファイルとして記憶装置14に格納する。 10

## 【0027】

(S2)このファイルから、次の図形データを1つ取り出す。最初は、図2中のNO.1の図形データを取り出す。

## 【0028】

(S3)取り出すべき図形データがなければ処理を終了し、そうでなければステップS4へ進む。

## 【0029】

(S4)この図形データにグループ名が付与されなければステップS2へ戻り、そうでなければステップS5へ進む。 20

## 【0030】

(S5)ステップS2で取り出した図形データにグループ名を付与する。例えば図2中のNO.1の図形に対しグループ名G1を付与する。

## 【0031】

(S6)この図形データと図形の種類、レイヤ及びサイズが一致する図形データを検索する。

## 【0032】

(S7)一致する図形データがなければステップS2へ戻り、あればステップS8へ進む。 。

## 【0033】

(S8)一致する図形データに対し、ステップS5で付与したグループ名と同一のグループ名を付与する。例えば図2のNO.3の図形データがNO.1のそれに一致する場合、NO.3の図形データにグループ名G1を付与する。 30

## 【0034】

ステップS2へ戻り、前回の次の図形データ、例えばNO.2の図形データを取り出す。

## 【0035】

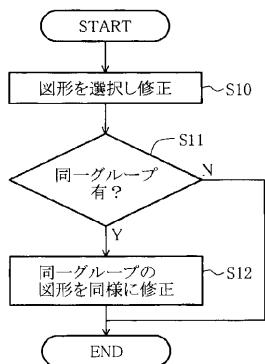

このようなグループ化処理が終了した後、図5に示す修正処理がパターン修正処理装置10により行なわれる。

## 【0036】

(S10)操作者は、表示装置12の表示を見ながら入力装置11を操作して、修正対象の図形を選択し修正する。 40

## 【0037】

(S11)ステップS10で修正した図形と同一グループ名の図形が図2中に存在すればステップS12へ進み、そうでなければこの選択図形に対する修正処理を終了する。

## 【0038】

(S12)同一グループの図形をステップS10と同様に修正する。この修正はパターン修正処理装置10により自動的に行われる。

## 【0039】

例えばステップS10で一边が1μmの矩形コンタクトホールパターンを一边が0.9μmの矩形に操作者が修正した場合、これと同一図形がパターン修正処理装置10により自 50

動的に修正される。このような処理により、設計されたパターンデータの修正処理が短時間で行なわれる。例えば100個の同一図形を修正するのに1個あたり約10秒かかり、従来では全体として約20分かかったものが、本実施形態によれば約10秒で全修正が行なわれる。

【0040】

図1において、記憶装置13に格納されているセルTOP内のセルA及びBは、この修正後、記憶装置14内のセルA及びBと置き換えられる。この際、サイズ及びグループのデータが削除される。このサイズ及びグループのデータは記憶装置14に格納され、再度セルA及びBが修正対象として選択された場合にはこのデータが用いられる。

【0041】

なお、本発明には外にも種々の変形例が含まれる。

【0042】

例えば、ポリゴンデータの場合には上記サイズの替わりに、その始点座標が(0, 0)となるように図形を平行移動したときの座標値を用いてもよい。また、修正のためにセルTOPから抽出されるセルは1つ以上であればよい。

【図面の簡単な説明】

【図1】本発明の一実施形態のパターンデータ修正装置を示す概略ブロック図である。

【図2】修正対象のセルに含まれる図形データの説明図である。

【図3】(A)、(B)及び(C)はそれぞれ、矩形、多角形及び配線のサイズを説明する図である。

【図4】図1のパターン修正処理装置10により実行されるグループ化処理の手順を示すフローチャートである。

【図5】図4の処理に続いて図1のパターン修正処理装置10により実行されるパターン修正処理の手順を示すフローチャートである。

【図6】従来の、半導体集積回路のセル配置を視覚的に示す概略ブロック図である。

【図7】従来の、セルTOP内にセルA及びBが配置された状態を視覚的に示す図である。

【図8】(A)、(B)及び(C)はそれぞれ、図6中のセルA、B及びTOPの階層構造を示す図である。

【図9】図7のセルTOPに含まれる図形データの説明図である。

【符号の説明】

10 パターン修正処理装置

11 入力装置

12 表示装置

13、14 記憶装置

A～F、TOP セル

10

20

30

【図1】

本発明の一実施形態のパターンデータ

修正装置を示す概略ブロック図

【図2】

修正対象のセルに含まれる图形データの説明図

| NO. | 種類  | レイヤ | 座標          | サインズ  | グループ |

|-----|-----|-----|-------------|-------|------|

| 1   | REC | 1   | X1,Y1,X2,Y2 | W1,H1 | G1   |

| 2   | POL | 1   | X3,Y3,...   | W2,H2 | C2   |

| 3   | REC | 1   | X4,Y4,X5,Y5 | W3,H3 | G1   |

| 4   | REC | 2   | X6,Y6,X7,Y7 | W4,H4 | G3   |

| 5   | PTH | 3   | X8,Y8,X9,Y9 | L1    | G4   |

| n   | POL | 1   | Xa,Ya,...   | Wa,Ha | G2   |

【図3】

(A)、(B)及び(C)はそれぞれ、矩形、

多角形及び配線のサイズを説明する図

【図4】

図1のパターン修正処理装置10により実行される

グループ化処理の手順を示すフローチャート

【図5】

図4の処理に続いて図1のパターン修正処理装置10により実行されるパターン修正処理の手順を示すフローチャート

【図6】

従来の、半導体集積回路のセル配置を視覚的に示す概略ブロック図

【図7】

従来の、セルTOP内にセルA及びBが配置された状態を視覚的に示す図

【図8】

(A)、(B)及び(C)はそれぞれ、図6中のセルA、B及びTOPの階層構造を示す図

(A)

(B)

(C)

## 【図9】

図7のセルTOPに含まれる図形データの説明図

| NO. | 種類  | レイヤ | 座標          |

|-----|-----|-----|-------------|

| 1   | REC | 1   | X1,Y1,X2,Y2 |

| 2   | POL | 1   | X3,Y3, ...  |

| 3   | REC | 1   | X4,Y4,X5,Y5 |

| 4   | REC | 2   | X6,Y6,X7,Y7 |

| 5   | PTH | 3   | X8,Y8,X9,Y9 |

| ⋮   | ⋮   | ⋮   | ⋮           |

| n   | POL | 1   | Xa,Ya, ...  |

---

フロントページの続き

(56)参考文献 特開平05-290130(JP,A)

特開平09-198424(JP,A)

特開2000-089448(JP,A)

特開平04-358284(JP,A)

特開平10-011599(JP,A)

特開平04-199276(JP,A)

特開2001-014362(JP,A)

(58)調査した分野(Int.Cl., DB名)

G06F 17/50