(19) 日本国特許庁(JP)

## (12) 公表特許公報(A)

(11) 特許出願公表番号

特表2004-502265

(P2004-502265A)

(43) 公表日 平成16年1月22日(2004.1.22)

(51) Int.Cl.<sup>7</sup>

G 11 C 15/04

F 1

G 11 C 15/04

6 3 1 Z

テーマコード(参考)

審査請求 未請求 予備審査請求 未請求 (全 58 頁)

|               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          |                                                                                                                                               |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| (21) 出願番号     | 特願2002-505624 (P2002-505624)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | (71) 出願人 | 502047062<br>メンコール エル. エル. シー.<br>アメリカ合衆国、19808 デラウェア<br>州、ニュー キャッスル カウンティー、<br>ウィルミントン、スイート 400、セン<br>ターヴィル ロード 2711、コーポレ<br>ーション サービス シーオー. |

| (86) (22) 出願日 | 平成12年6月7日 (2000.6.7)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | (74) 代理人 | 110000040<br>特許業務法人池内・佐藤アンドパートナー<br>ズ                                                                                                         |

| (85) 翻訳文提出日   | 平成14年2月7日 (2002.2.7)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | (72) 発明者 | ヴィラレト、イヴェス、エマヌエル<br>イスラエル、38510 ハデラ、シクン<br>ペール、ピー. オー. ボックス 874<br>8、ハキノール ストリート 9                                                            |

| (86) 國際出願番号   | PCT/IL2000/000327                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          |                                                                                                                                               |

| (87) 國際公開番号   | W02002/001570                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |                                                                                                                                               |

| (87) 國際公開日    | 平成14年1月3日 (2002.1.3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |          |                                                                                                                                               |

| (81) 指定國      | AP (GH, GM, KE, LS, MW, MZ, SD, SL, SZ,<br>TZ, UG, ZW), EA (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), EP (AT, BE,<br>CH, CY, DE, DK, ES, FI, FR, GB, GR, IE, IT, LU, MC, NL, PT, SE), 0<br>A (BF, BJ, CF, CG, CI, CM, GA, GN, GW, ML, MR, NE, SN, TD, TG), AE<br>, AG, AL, AM, AT, AU, AZ, BA, BB, BG, BR, BY, CA, CH, CN, CR, CU, C<br>Z, DE, DK, DM, DZ, EE, ES, FI, GB, GD, GE, GH, GM, HR, HU, ID, IL,<br>IN, IS, JP, KE, KG, KP, KR, LZ, LC, LR, LS, LT, LU, LV, MA, MD<br>, MG, MK, MN, MW, MX, MZ, NO, NZ, PL, PT, RO, RU, SD, SE, SG, SI, S<br>K, SL, TJ, TM, TR, TT, TZ, UA, UG, US, UZ, VN, YU, ZA, ZW |          |                                                                                                                                               |

最終頁に続く

(54) 【発明の名称】小型コールアウトメモリ

## (57) 【要約】

制限された数の線を用いることにより検索データを含むメモリセルの配置を可能とし、必要となるメモリ面積を低減し、同時に所定の特性を持つセルのみを検索するよう制限することで検索処理を加速したメモリシステム及び方法である。メモリシステムはアドレスバスとデータバスとローセレクタとカラムセレクタと二次元アレイのメモリセルを備え、各メモリセルはマスキング回路と比較回路と比較結果を格納するメモリビットを備え、さらに幾つかの実施形態ではレンジ回路を備えている。メモリはリードおよびライトモードで動作し、また、新規な高速検索モードで動作する。

**【特許請求の範囲】****【請求項 1】**

アドレスバスと、データバスと、各メモリセルが少なくとも1つのローと1つのカラムにより選択できるようにローとカラムの2次元に配列されたメモリであって各メモリセルが複数のデータバス線と接続されたメモリを備え、さらに前記各メモリセルが比較回路と、マスキング回路と、複数のメモリビットを備え、前記メモリシステムがリードモードおよびライトモードで動作し、または、検索モードで以下の動作することを特徴とするメモリシステム。

(a) 各メモリセルが、前記データバス上のデータセットと前記セル内に格納されているデータとの比較処理を実行し、当該比較処理の結果、両者がマッチングしている場合、当該比較結果を前記メモリビットに格納する。10

(b) 前記各メモリセルが、前記所定の性質を持つことを確認した場合にイネーブル信号を前記各マスキング回路または前記比較回路に選択的に送ることにより検索するセル群を所定の性質を持つセル群に制限する。

(c) 前記マスキング回路が、所定方向に最も大きなアドレスを持つセルを選択するマスキング機能を実行し、前記データバス上に当該セルのアドレスが出力されるように、前記所定の性質が選択されていることを確認する。

(d) 複数のマッチングセルがそのアドレスを前記データバス上に出力するまで前記プロセスを繰り返す。

**【請求項 2】**

前記各メモリセルが、さらに、レンジ回路を備え、前記所定の性質が、オリジンアドレスとの所定の関係であり、前記検索モードにおいて以下の処理を行なう請求項1に記載のメモリシステム。20

(a) 前記レンジ回路が、前記オリジンアドレスとの所定の関係を確認し、選択的に前記イネーブル信号を前記マスキング回路に送るレンジ機能を実行する。

(b) 前記マスキング回路が、所定方向に最も大きなアドレスを持つセルを選択するマスキング機能を実行し、前記データバス上に当該セルのアドレスが出力されるように、前記オリジンアドレスとの所定の関係が選択されていることを確認する。

(c) 複数のマッチングセルがそのアドレスを前記データバス上に出力するまで、前記プロセスを異なるオリジンアドレスについて繰り返す。30

**【請求項 3】**

前記メモリシステムが、専用レジスタを備え、各々の前記メモリセルがさらにオリジン線と接続されており、前記検索モードで以下の処理を実行する請求項2に記載のメモリシステム。

(a) 第1のステップにおいて、前記オリジンアドレスの値を前記アドレスバス上に出力して前記専用レジスタに格納し、前記比較処理を実行するために前記検索データを前記データバス線を介して前記メモリセルに通知する。

(b) 第2のステップにおいて、

(i) 前記レンジ回路が、前記オリジン線を介して得られた前記オリジンアドレスの値と前記セルアドレスの値との比較処理を行なって前記レンジ機能を実行し、前記所定の関係を確認する。40

(ii) 前記メモリビットに格納されている情報がマッチング条件を満たすことを示し、前記レンジ回路が前記所定の関係を確認した場合、前記マスキング回路がイネーブルとなり、前記マスキング回路が、前記セルのアドレスと他のマッチングセルのアドレスとの比較の結果、前記所定の方向に最も大きいアドレスであって前記オリジンアドレスとの所定の関係を満たすアドレスが前記データバス上に出力されるようにする。

(c) 複数のマッチングセルがそのアドレスを前記データバス上に出力するまで、前記プロセスを異なるオリジンアドレスについて繰り返す。

**【請求項 4】**

前記メモリセルが前記オリジン線に接続されておらず、各前記メモリセルが2つの隣接す50

るローと 1 つのカラムを入力として受け取り、前記検索モードにおいて以下の処理を実行する請求項 2 に記載のメモリシステム。

a . 第 1 のステップにおいて、

i . 前記比較機能を実行するために前記検索データが前記データバス線により前記メモリセルに渡され、オリジンアドレス値  $r_0 ; c_0$  が前記アドレスバス上に出力され、

ii . 所定方向に見て、前記オリジンアドレスのロー ( $r = r_0$ ) と等しいまたは小さいロー、または、前記オリジンアドレスのロー ( $r < r_0$ ) より小さいすべてのロー、さらに、第 2 の所定方向から見て、前記オリジンアドレスのカラム ( $c = c_0$ ) と等しいまたは小さいカラム、または、前記オリジンアドレスのカラム ( $c < c_0$ ) より小さいすべてのカラムが選択されるように、前記オリジンアドレス値がエンコードされる。

10

b . 第 2 のステップにおいて、

i . 各前記マッチングセル内の前記レンジ回路が、当該セルのアドレスと前記ローとカラムとの所定の関係について、前記セルのローの隣のローであって所定の方向において一つ大きい方のローがセレクトされているか、または、ロー  $r$  とカラム  $c$  の双方がセレクトされているか、または、当該セルのカラムの隣のカラムであって第 2 の所定の方向において一つ大きい方のカラムがセレクトされているという関係であることを確認した場合に、当該セル  $r ; c$  をイネーブルとするレンジ機能を実行する。

ii . イネーブルとされた当該セルのアドレスが前記データバス上にセットされる。

c . 複数のマッチングセルが当該アドレスを前記データバス上に出力するまで、前記プロセスを異なるオリジンアドレスについて繰り返す。

20

#### 【請求項 5】

第 1 のサイクルと第 2 のサイクルにおいてセットした後、前記比較結果を格納している前記メモリビットを不变とし、前記メモリビットと前記比較器のイネーブル信号の論理演算によって前記比較器を当該サイクルの間ディスエーブルとすることにより検索済みのアドレスをディスエーブルとし、後続の検索処理において前記レンジ機能の必要性をなくした請求項 1 から 4 のいずれかに記載のメモリシステム。

#### 【請求項 6】

前記比較結果を格納している前記メモリビットが標準的なリード手段またはライト手段を備え、前記セルのメモリビットをリセットするために新しいデータを特定のセルに書き込み、前記メモリビットがイネーブル信号を前記マスキング回路に送ることにより前記検索の範囲を前記所定の性質を持つセルに制限する請求項 1 に記載のメモリシステム。

30

#### 【請求項 7】

前記比較処理結果を格納している前記メモリビットの演算をリセットするための専用線を備え、前記専用線に接続されているすべてのセルが前記検索の範囲に含まれる請求項 1 から 6 のいずれかに記載のメモリシステム。

30

#### 【請求項 8】

2 次元メモリセルアレイ内のメモリセルであって、1 つのデータバス線と 1 つのオリジンバス線と 1 つ以上の制御線と 1 つのローと 1 つのカラムからのそれぞれの入力と、比較器を持つメモリ回路と、比較結果格納ビットと、レンジ回路と、プライオリティマスク回路とを備え、前記データバス線を介して検索データを前記メモリセルに入力し、前記比較器により当該検索データと前記セルのデータとを比較し、当該比較結果を前記比較格納ビットに格納し、前記レンジ回路が前記セルのアドレスとオリジンアドレスの所定の関係をチェックし、前記メモリビットに格納されている情報がマッチング条件を満たすことを示し、前記レンジ回路が前記所定の関係を確認した場合、前記マスキング回路がイネーブルとなり、前記マスキング回路が、前記セルのアドレスと他のマッチングセルのアドレスとの比較の結果、前記所定の方向に最も大きいアドレスであって前記オリジンアドレスとの所定の関係を満たすアドレスが前記データバス上に出力されることを特徴とするメモリセル。

40

#### 【請求項 9】

2 次元メモリセルアレイ内のメモリセルであって、1 つのデータバス線と 1 つ以上の制御

50

線と 1 つのローと 2 つのカラムからのそれぞれの入力と、比較器を持つメモリ回路と、比較結果格納ビットと、レンジ回路と、プライオリティマスク回路とを備え、前記データバスを介して検索データを前記メモリセルに入力し、前記比較器により当該検索データと前記セルデータとを比較し、当該比較結果を前記比較格納ビットに格納し、前記レンジ回路が、前記セルのアドレスと、前記ローとカラムと前記制御線の状態により前記セルに渡されるオリジンアドレスとの所定の関係をチェックし、前記メモリビットに格納されている情報がマッチング条件を満たすことを示し、前記レンジ回路が前記所定の関係を確認した場合、前記マスキング回路がイネーブルとなり、前記マスキング回路が、前記セルのアドレスと他のマッチングセルのアドレスとの比較の結果、前記所定の方向に最も大きいアドレスであって前記オリジンアドレスとの所定の関係を満たすアドレスが前記データバス上に出力されるようにする処理を実行することを特徴とするメモリセル。10

#### 【請求項 10】

前記メモリセルが 1 つのカラムと 2 つのローに接続されている請求項 5 に記載のメモリセル。

#### 【請求項 11】

前記レンジ回路を含まず、前記比較結果格納ビットにより書き込まれているデータにより選択的にディスエーブルとされる請求項 7 から 9 のいずれかに記載のメモリセル。

#### 【請求項 12】

第 1 のサイクルにおける検索処理後、第 2 のサイクルにおいて前記比較結果格納ビットと前記比較器のイネーブル信号の論理演算によってディスエーブルとされる請求項 10 に記載のメモリセル。20

#### 【請求項 13】

メモリシステムのメモリセル検索方法であって、前記メモリシステムが、アドレスバスと、データバスと、ローセレクタと、カラムセレクタと、各メモリセルが少なくとも 1 つのローと 1 つのカラムにより選択できる 2 次元メモリアレイと、複数のデータバス線を備え、前記メモリシステムがリードモードおよびライトモードで動作し、または、検索モードで以下の動作することを特徴とする方法。

a . 各メモリセルが、前記データバス上のデータセットと前記セル内に格納されているデータとの比較処理を実行し、当該比較処理の結果、両者がマッチングしている場合、当該比較結果を前記メモリビットに格納する。30

b . 前記各メモリセルが、前記所定の性質を持つことを確認した場合にイネーブル信号を選択的に生成することにより検索するセル群を制限するレンジ機能を実行する。

c . 前記各メモリセルが、所定方向に最も大きなアドレスを持つセルが選択されるようにマスキング機能を実行し、前記データバス上に当該セルのアドレスが出力されるように、前記オリジンアドレスと前記所定の関係が選択されていることを確認する。

d . 複数のマッチングセルがそのアドレスを前記データバス上に出力するまで前記プロセスを繰り返す。

#### 【請求項 14】

前記所定の性質が、所定のオリジンアドレスとの所定の関係であり、前記検索処理が以下のステップのレンジ機能を備えた請求項 2 に記載のメモリシステムについての検索方法。40

( a ) 前記メモリセルが、前記所定のオリジンアドレスとの前記所定の関係を確認し、選択的に前記イネーブル信号を生成し、レンジ機能を実行する。

( b ) 前記メモリセルが、所定方向に最も大きなアドレスを持つセルが選択されるようにマスキング機能を実行し、前記データバス上に当該セルのアドレスが出力されるように、前記オリジンアドレスと前記所定の関係が選択されていることを確認する。

( c ) すべてのマッチングセルがそのアドレスを前記データバス上に出力するまで、前記プロセスを異なるオリジンアドレスについて繰り返す。

#### 【請求項 15】

請求項 3 に記載のメモリシステムについてのメモリセルの検索方法であって、

( a ) 第 1 のステップにおいて、前記オリジンアドレス値を前記アドレスバス上に出力し50

て前記専用レジスタに格納し、前記比較処理を実行するために前記検索データを前記データバス線を介して前記メモリセルに通知する。

(b) 第2のステップにおいて、

(i) 前記レンジ回路が、前記オリジン線を介して得られた前記オリジンアドレスの値と前記セルアドレスの値との比較処理を行なって前記レンジ機能を実行し、前記所定の関係を確認する。

(ii) 前記メモリビットに格納されている情報がマッチング条件を満たすことを示し、前記レンジ回路が前記所定の関係を確認した場合、前記マスキング回路がイネーブルとなり、前記マスキング回路が、前記セルのアドレスと他のマッチングセルのアドレスとの比較の結果、前記所定の方向に最も大きいアドレスであって前記オリジンアドレスとの所定の関係を満たすアドレスが前記データバス上に出力されるようにする処理を実行する。10

(c) 複数のマッチングセルがそのアドレスを前記データバス上に出力するまで、前記プロセスを異なるオリジンアドレスについて繰り返す。

#### 【請求項16】

請求項3に記載のメモリシステムについて検索データを含むメモリセルを検索する方法であって、前記メモリセルが前記オリジン線に接続されておらず、各前記メモリセルが2つの隣接するロー信号と1つのカラム信号を入力として受け取り、前記第2の処理において以下の処理を実行する方法。

a. 第1のステップにおいて、

i. 前記比較機能を実行するために前記検索データが前記データバス線により前記メモリセルに渡され、オリジンアドレス値  $r_0 ; c_0$  がアドレスバス上に出力され、20

ii. 所定方向に見て、前記オリジンアドレスのロー ( $r = r_0$ ) と等しいまたは小さいロー、または、前記オリジンアドレスのロー ( $r < r_0$ ) より小さいすべてのロー、さらに、第2の所定方向から見て、前記オリジンアドレスのカラム ( $c = c_0$ ) と等しいまたは小さいカラム、または、前記オリジンアドレスのカラム ( $c < c_0$ ) より小さいすべてのカラムが選択されるように、前記オリジンアドレス値がエンコードされる。

b. 第2のステップにおいて、

i. 各前記マッチングセル内の前記レンジ回路が、当該セルのアドレスと前記ローとカラムとの所定の関係について、前記セルのローの隣のローであって所定の方向において一つ大きい方のローがセレクトされているか、または、ロー  $r$  とカラム  $c$  の双方がセレクトされているか、または、当該セルのカラムの隣のカラムであって第2の所定の方向において一つ大きい方のカラムがセレクトされているという関係であることを確認した場合に、当該セル  $r ; c$  をイネーブルとするレンジ機能を実行する。30

ii. イネーブルとされたアドレスが前記データバス上に選択される。

c. 複数のマッチングセルがそのアドレスを前記データバス上に出力するまで、前記プロセスを異なるオリジンアドレスについて繰り返す。

#### 【請求項17】

請求項1に記載のメモリシステムについて検索データを含むメモリセルを検索する方法であって、第1のサイクルにおいてセットした後、前記比較結果を格納している前記セル内の前記メモリビットを不变とすることにより、前記検索処理の範囲を前記第1のサイクルにおいて検索されていないセルに制限し、前記メモリビットと比較器イネーブル信号の論理演算によって比較器を当該サイクルの間ディスエーブルとすることにより検索済みのアドレスをディスエーブルとし、後続の検索処理において前記レンジ機能の必要性をなくした請求項13から16のいずれかに記載の方法。40

#### 【請求項18】

請求項1に記載のメモリシステムについて検索データを含むメモリセルを検索する方法であって、前記比較結果を格納している標準的なリード手段またはライト手段を備えるメモリビットを提供し、前記セルのメモリビットをリセットするために新しいデータを特定のセルに書き込み、前記メモリビットがイネーブル信号を前記マスキング回路に送ることにより、前記検索の範囲を前記所定の性質を持つセルに制限する請求項13から16のいず50

れかに記載の方法。

【請求項 1 9】

請求項 1 から 1 2 のいずれかに記載のメモリシステムについて検索データを含むメモリセルを検索する方法であって、前記比較処理結果を格納している前記メモリビットの演算をリセットするための専用線を備え、前記専用線に接続されているすべてのセルが前記検索の範囲に含まれる請求項 1 3 から 1 8 のいずれかに記載の方法。

【発明の詳細な説明】

【0 0 0 1】

(発明の背景)

本発明は、コールアウト機能付きメモリまたはコールアウトメモリ( COM )に関する。 10

本明細書において、コールアウト機能は下記のメモリの検索機能と定義する。( 1 )メモリセル全体の中から、検索の実行を可能とするセル群を選択する。( 2 )バス上に検索値が与えられる。( 3 )メモリがバス上に、前記検索値とマッチングするデータを持つメモリセルであって、前記選択されているセル群のうち所定方向におけるもっとも大きなアドレスを持つメモリセルのアドレスを返す。このコールアウト機能は、要求されるデータを含むメモリセルを特定するためにメモリセル全体をスキャンする必要性を無くすものであり、検索処理時間を低減するものである。コールアウト機能付きメモリの例はムコール社による PCT / I L 0 0 / 0 0 1 2 1 の国際特許出願において記載されている。 PCT / I L 0 0 / 0 0 1 2 1 記載のコールアウトメモリは、各セルが独立してアドレスバス、データバス、オリジンバスに接続されているというパラレル構造を持っている。その結果、応答時間がメモリサイズ、検索データの位置、または「コールアウト」機能を実現するために必要な論理ゲート数に依存しないものとなる。 20

【0 0 0 2】

PCT / I L 0 0 / 0 0 1 2 1 記載のコールアウトメモリは、検索データがアドレスバスにセットされるという特徴を持っている。デバイスが「コールアウト」モードで動作する場合、各メモリセルは、アドレス線を介して通知されたデータと各セル内に格納されているデータとの比較処理を実行する。複数のメモリセルにおいて比較処理結果が「マッチング」を示す場合、そのうちの一つのマッチングセルのアドレスがデータバス上に与えられる。そして、当該セルが以下の条件を満たしているか否かについて確認される。( 1 )そのアドレス値が所定の方向において、当該時点でセットされているいわゆるオリジン値より小さいものか。( 2 )マッチングデータを持つすべてセルのうち、オリジン値に最も近いアドレス値を持つものか、そして上記条件( 1 )を満たすものか。なお、データバス上に新たなオリジン値としてセットされたマッチングセルについてもこのサイクルが繰り返され、すべてのマッチングセルが見つかるまで当該処理が何度も繰り返される。 30

【0 0 0 3】

PCT / I L 0 0 / 0 0 1 2 1 記載の「コールアウト」デバイスは、従来の標準的なメモリと同様の働きを行なうモード、いわゆるノーマルモードでも動作する。

【0 0 0 4】

当業者であれば、PCT / I L 0 0 / 0 0 1 2 1 記載の「コールアウト」デバイスが、コールアウト機能を実現するためにかなり多くの線を必要とすることが分かるであろう。 40

【0 0 0 5】

PCT / I L 0 0 / 0 0 1 2 1 記載の「コールアウト」デバイスにおいて、各々のセルがアドレスバス上のデータセットとセル内に格納されているデータとの比較処理を行なう。それゆえ、各メモリセルにおいて多くのアドレス線の接続を必要とする。

【0 0 0 6】

さらに、各メモリセルは、自分のアドレスをオリジンアドレス値と比較する必要があり、もし、所定方向についてセルのアドレスがオリジンアドレスより小さい場合にセル内のプライオリティマスク回路をイネーブルとする。この機能の実現のため、各メモリセルにオリジンアドレス値を通知するための接続される線の追加が必要となる。

【0 0 0 7】

プライオリティマスク回路は、データバス上に出力するデータのビットをセットするために、検索データを記憶しそのセルアドレスが「オリジン」アドレスよりも小さいという要求を満たしている全てのメモリセルの全てのセットビットを「OR」論理で演算する。「ビットマスク」回路の機能は、もしデータバス上に自分のアドレスより大きなアドレスのデータが現れている場合に、当該自分のアドレスより大きなアドレスのビットを変化させるビット出力をマスクすることである。その結果、データバス上に残る最後のデータは、アドレスバスに与えられたデータとマッチするデータが格納されたセルで、かつ、オリジンアドレスよりも小さいアドレスを持つセルのうち最も大きなアドレスを持つセルのアドレスと同じものになる。

## 【0008】

10

それゆえ、PCT/IL00/00121に従って設計されたシステムにおいて、コールアウト機能を実現するためには、各メモリセルに接続される複数のアドレス線と複数のオリジン線が必要となる。

## 【0009】

COMデバイスをチップ上に形成するためには、各メモリセルがすべてのアドレス線とオリジン線を配線するためのスペースを確保するために十分な面積S1を持つ必要がある。各メモリセルのロジック機能を実装するためには、さらに、最低限S2のスペースが必要となる。

## 【0010】

20

S2がS1よりも大きい場合、面積を増加させることなく上記アドレス線とオリジン線を各メモリセルに接続することは可能と思われる。しかしながら、もしS1がS2よりも大きい場合は、アドレス線とオリジン線を配線するためには各メモリセルにおいてセルのロジック機能を実行するために十分なスペースを超えるスペースが必要となる。

## 【0011】

このように追加スペースが必要となることによって、1チップに実装できるセルの総数が低下し、COMの容量が小さくなる。また、メモリセルあたりのコストも増加する。

## 【0012】

コールアウト機能付きメモリを設計する上で、各メモリセルに接続される線数を低減することが求められている。

## 【0013】

30

各セルがローとカラムにより選択されるようにメモリセルを2次元アレイとして配列することが知られている。（「nMOSとCMOSのVLSIシステムデザイン入門」、Amarr Murkherjee, Prentice-Hall, 第8.3章参照）。この方法により、一つのメモリセルのアドレッシングが、ローとカラムという2つの線のみで可能となる。セルを選択するためのロジック機能はとてもシンプルで、ローとカラムのステータスの単純なAND論理のみとなる。この簡単な選択機能により、各メモリセルにおいては単純なAND論理のみで良く、スペースが低減される。

## 【0014】

コールアウト機能付きメモリにおいても同様の方法と設計を行い、必要となる論理ゲートの数を低減し、コールアウトデバイスの実装、例えばチップ上への実装を実現し、メモリデバイスのサイズの増加を招くことなくメモリセルの数を増加させることができている。

## 【0015】

(発明の要約)

本発明は、コールアウトメモリの実装面積を低減し、与えられた面積に実装するメモリセル数を増加したシステムおよび実装方法に関する。

## 【0016】

メモリ面積の低減は、各メモリセルに接続される線数を低減することによって達成される。

## 【0017】

50

コールアウトシステムの各メモリセルは、PCT/IL00/00121に開示されたものと同様のプライオリティマスク回路を備えるが、各メモリに対してアドレス線が配線も接続もされていないという新規な構成を持つメモリを備えている。その代わり、従来のメモリでしばしば適用されているように、二次元アレイ状に一つの「ロー」線と一つの「カラム」線が各メモリに配線されている。

#### 【0018】

本発明のコールアウトシステムでは、コールアウトレンジ機能を実装するために、同じ「ロー」線と「カラム」線が用いられている。ローとカラムを用い、各メモリセルはアドレス値とオリジンアドレス値との比較処理を実現し、当該比較結果に応じてプライオリティマスクを選択的に有効とする。本発明の構成により、オリジン線の各メモリへの配線の必要がなくなり、セル面積の低減が達成される。10

#### 【0019】

本発明の方法は、3つの実施形態により実現される。これらの実施形態は各メモリセルへの配線数が低減されたコールアウトデバイスを用いる。最初の2つの実施形態において、検索データはデータバス上に与えられ、オリジンアドレス値がアドレスバス上に与えられ、各メモリセルにおける比較結果はメモリセルデバイスに付加された専用の1ビットメモリセルに格納される。

#### 【0020】

第1の実施形態におけるコールアウトメモリの実装は、アドレス線がメモリセルに接続されておらず、セルは標準的なメモリデバイスのようにローとカラムに並べられており、システムは当該セルを用いてコールアウト機能を実行する。20

#### 【0021】

第2の実施形態はさらに改良された実装であり、アドレス線もオリジン線もメモリセルに接続されていない。第2の実施形態において、コールアウト機能は、オリジンアドレスとの関係に対応して選択的にローとカラムをセッティングすることによりアシストされている。

#### 【0022】

第3の実施形態において、レンジ回路は用いられていないので、さらなる面積低減が実現されている。その代わり、セル内のメモリビットが、メモリの必要性に応じてセル群のレンジを選択するために用いられており、後続のコールアウト検索処理のために当該選択されたセル群が不能とされ、または専用の指定線により当該セル群が不能とされる。30

#### 【0023】

(図面の簡単な説明)

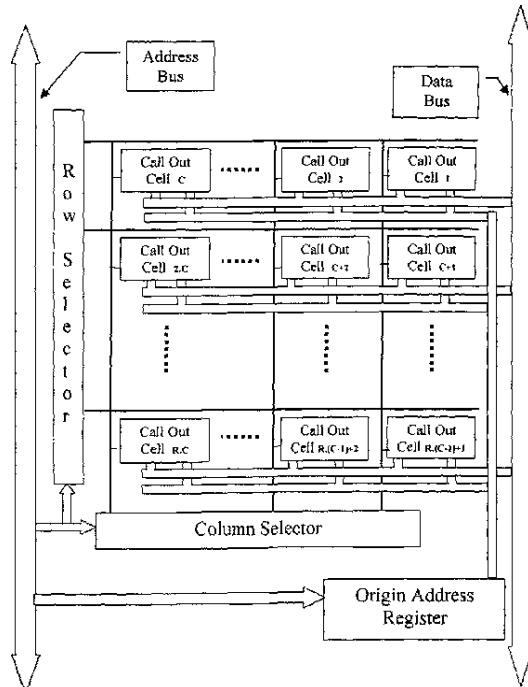

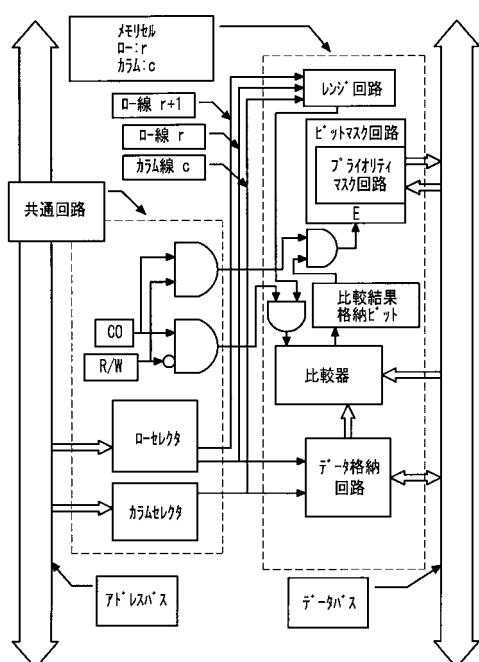

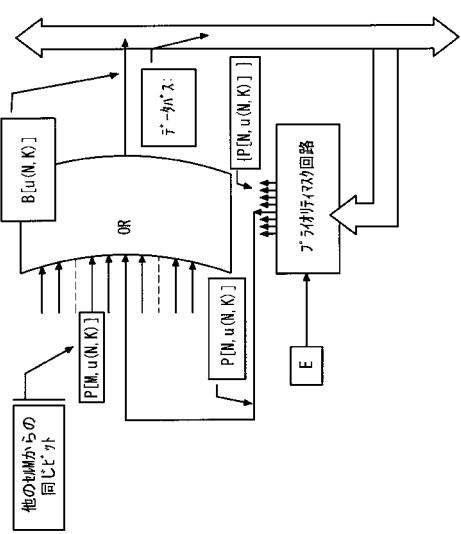

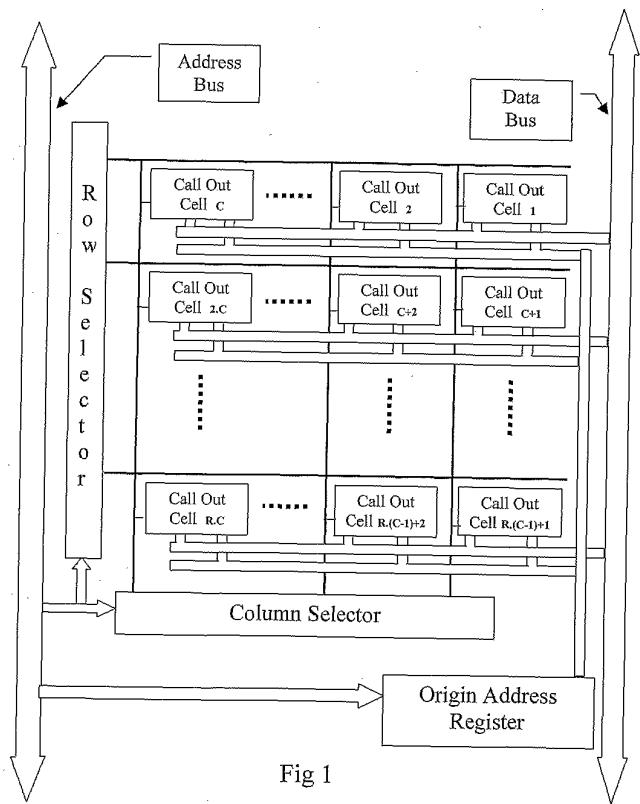

図1は、本発明にかかる、各メモリセルにアドレス線が配線されていないコールアウトメモリの模式図である。

#### 【0024】

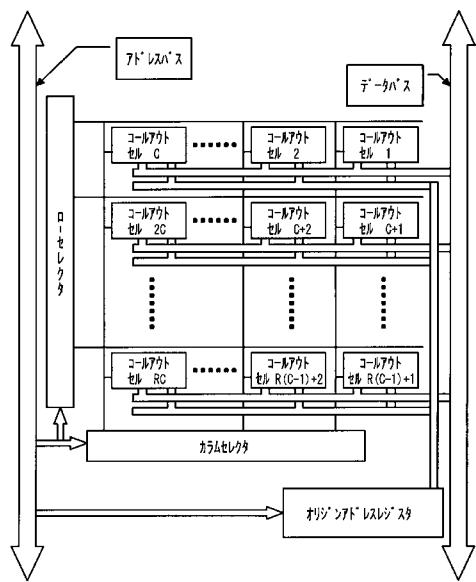

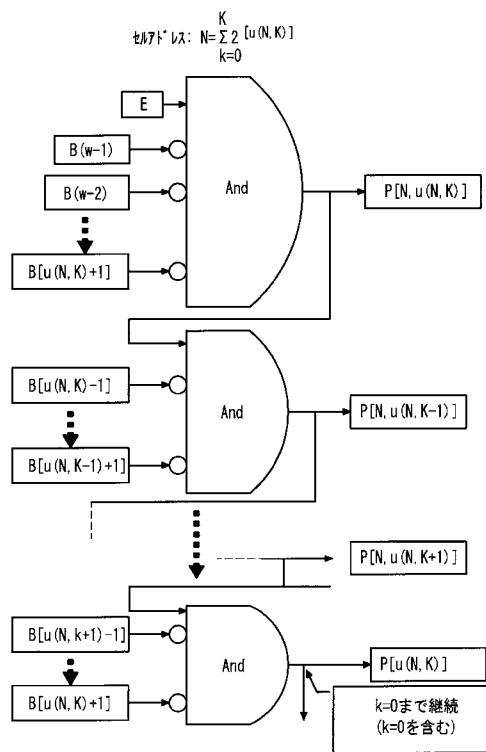

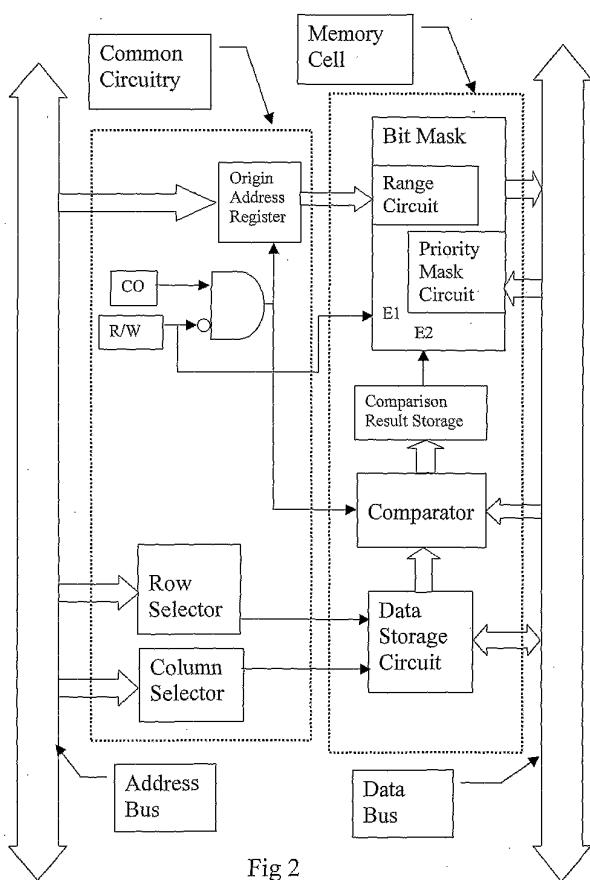

図2は、図1の構成に応じたメモリセル回路のブロック図である。

#### 【0025】

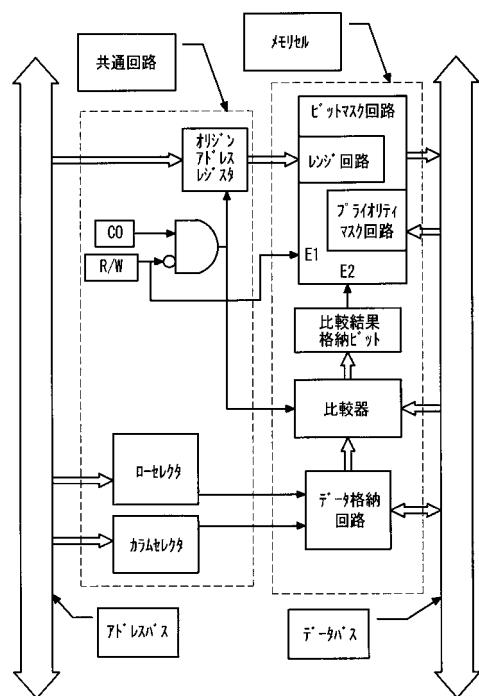

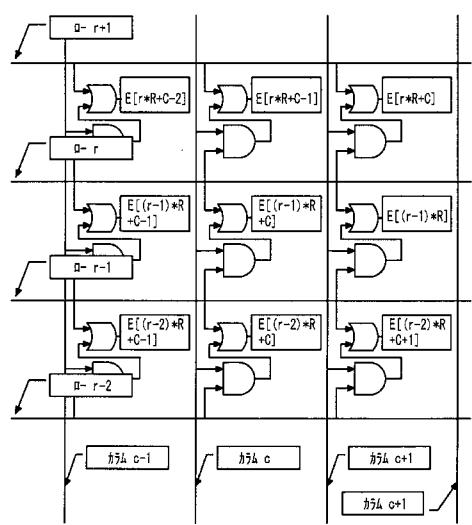

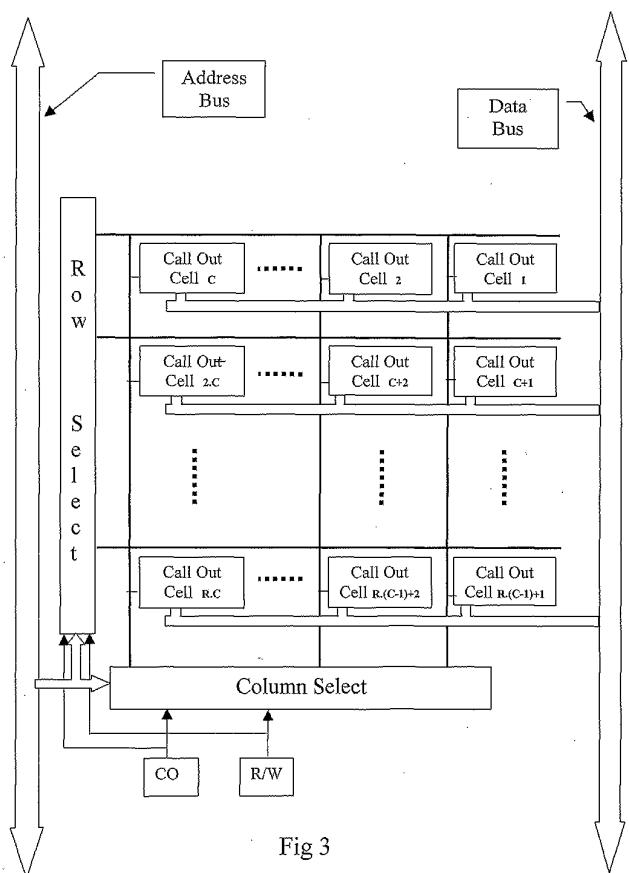

図3は、本発明にかかる、各メモリセルにオリジン線が配線されていないコールアウトメモリの模式図である。40

#### 【0026】

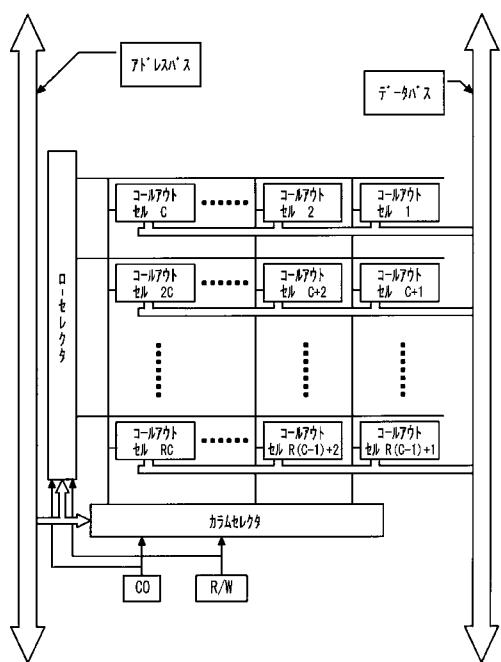

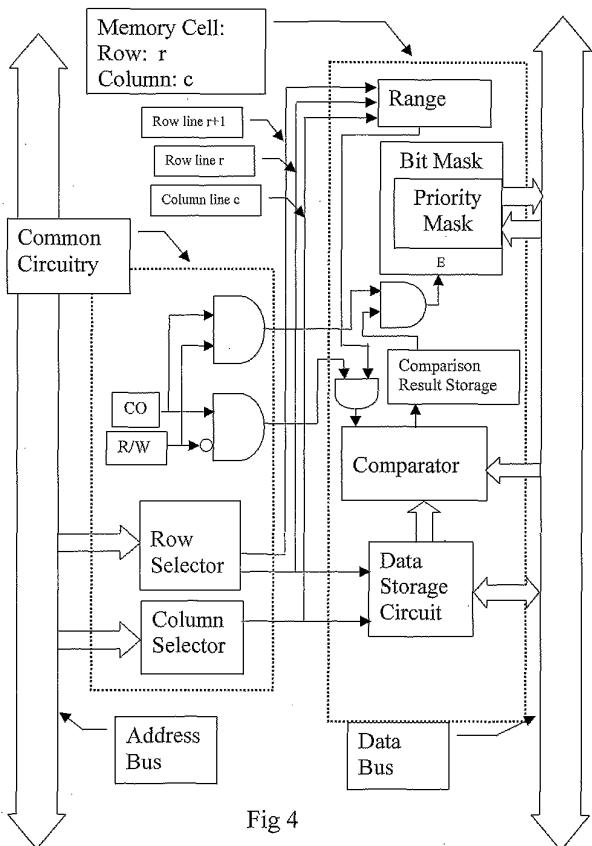

図4は、図3の構成に応じたメモリセル回路のブロック図である。

#### 【0027】

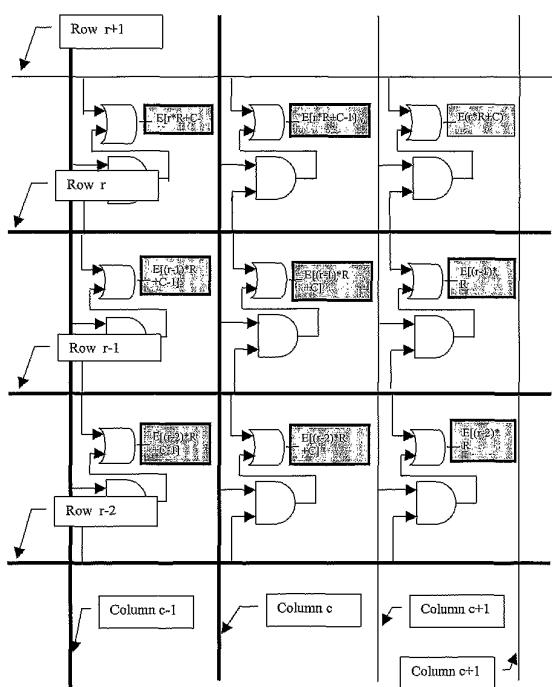

図5は、本発明にかかる、図3の構成に応じたコールアウトメモリ内のセルのレンジ回路の模式図である。

#### 【0028】

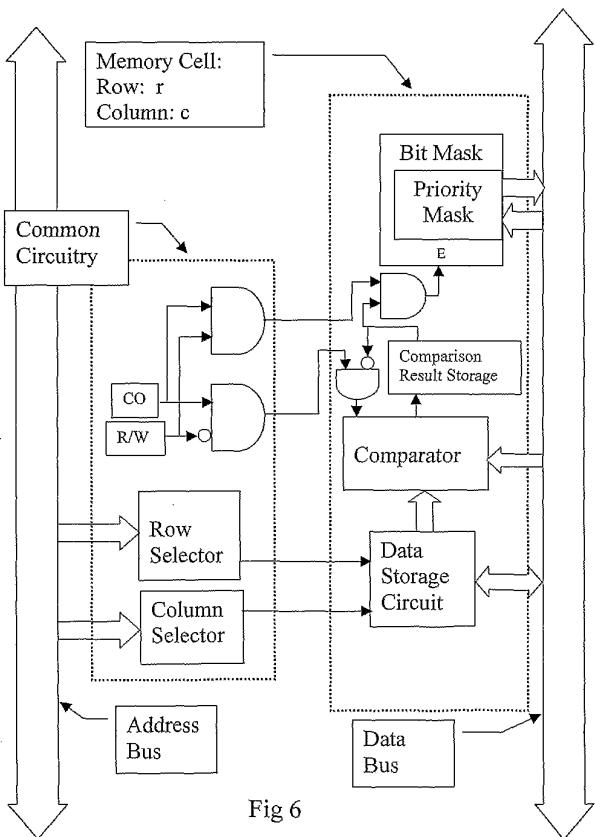

図6は、本発明にかかる、レンジ回路が設けられていないコールアウトメモリ内のセルの模式図である。

#### 【0029】

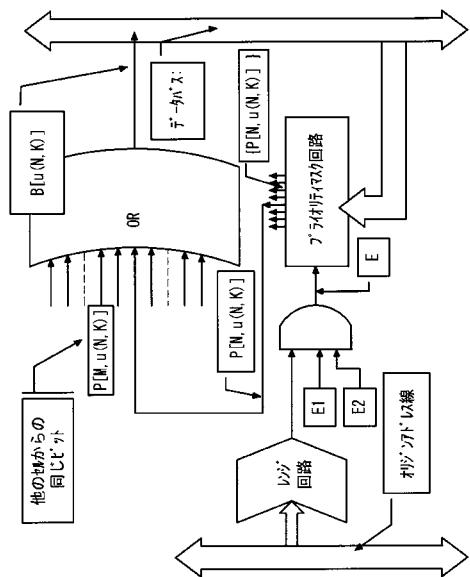

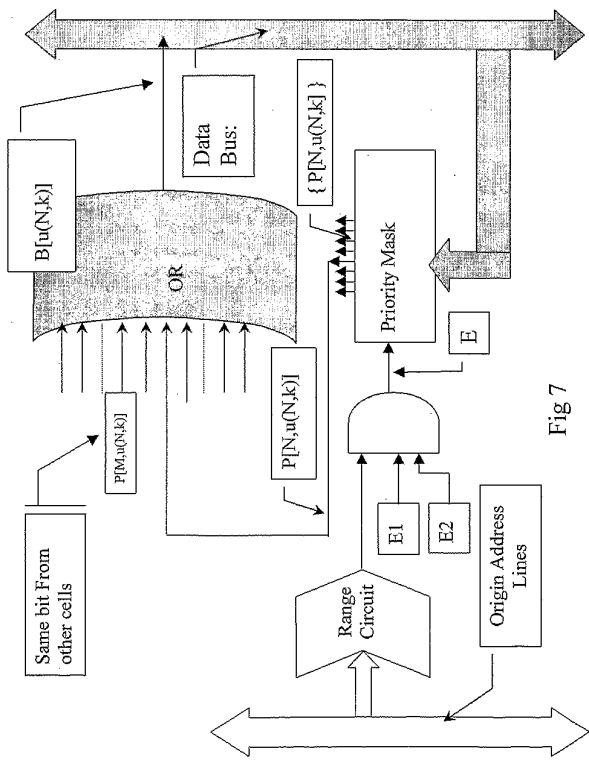

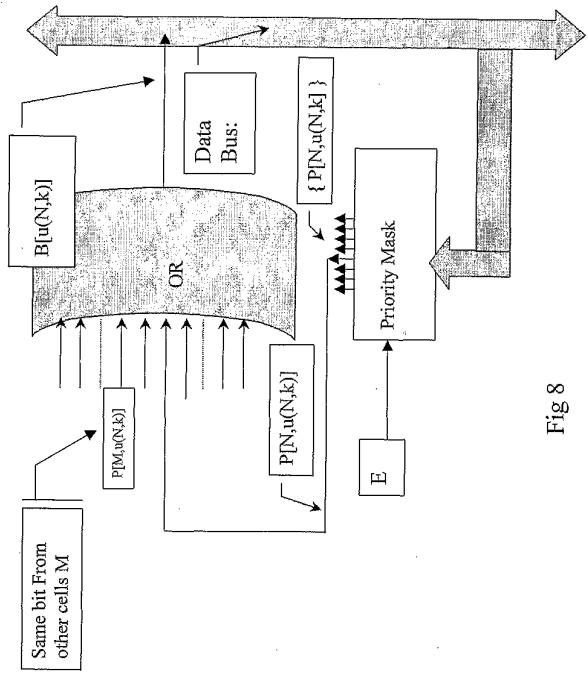

図7は、図1および図2の構成におけるビットマスク回路の模式図である。50

**【 0 0 3 0 】**

図 8 は、図 3 および図 4 の構成におけるビットマスク回路の模式図である。

**【 0 0 3 1 】**

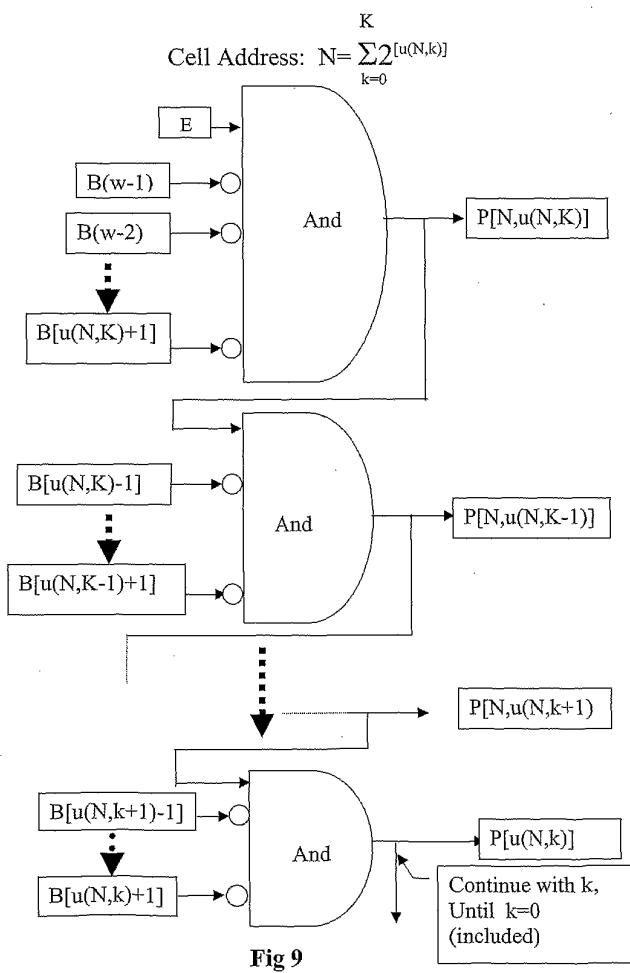

図 9 は、プライオリティマスク回路の詳細構成例を示す図である。

**【 0 0 3 2 】****(本発明の詳細な説明 )**

本発明の目的は、コールアウト機能を実現する論理ゲート数と接続線数を低減したメモリシステムおよびメモリ駆動方法を提供する。コールアウト機能とは、メモリセル全体から検索を実行する一群のメモリセルを選択し、検索するデータ値をバス上に与え、前記選択された各メモリセルにおいて前記検索するデータ値とセル内に格納されているデータ値とを比較処理を実行し、当該比較処理の結果として、複数のセルにおいて「マッチング」条件が成立していれば、マッチングしたセルのうち、もっとも大きなアドレス値を持つセルの当該アドレス値をバスに返し、すべてのマッチングするセルが見つかるまで何度もこのサイクルを繰り返し、メモリまたはその一部に格納されているデータを検索する機能を指す。

10

**【 0 0 3 3 】**

本システムの第 1 の実施形態では、図 1 に示すようにメモリセルが二次元のアレイ状、例えば、ローとカラムの二次元列に配列されている。各メモリセルは、複数のデータバス線と、複数のオリジン線と、一つのロー線と、一つのカラム線に接続されている。リード / ライトなどの他の制御線も各セルに接続されている。各メモリセルは、データ格納回路と、比較器と、以下の説明において比較結果格納ビットメモリと呼ぶ付加ビットと、レンジ回路と、ビットマスク回路とを備えている。

20

**【 0 0 3 4 】**

標準セルでは、二次元アレイ構成において、カラム線は必ずしも各メモリセルに接続される必要がないことが知られている。それゆえ、第 1 の実施形態のさらなるバリエーションでは、カラム線がデータバスのビット線をメモリセルのカラムに接続するために使われてあり、データバスのビット線はトランジスタのスイッチングを介した接続よりもカラム線を介して各メモリセルのカラムに接続される（「n MOS および CMOS 型 VLSI システム設計の入門」 Amar Murkherjee, Prentice-Hall の 8 . 3 章を参照）。

30

**【 0 0 3 5 】**

上記方法およびその他の同様の方法において、ローとカラムにより選択的にメモリセルを活性化する公知の方法はローセレクト、カラムセレクトとして知られ、選択されたローとカラムは選択されたロー（セレクティッドロー）、選択されたカラム（セレクティッドカラム）となる。

**【 0 0 3 6 】**

本発明のシステムは、ノーマルモードとコールアウトモードの 2 つのモードにより動作する。

**【 0 0 3 7 】**

ノーマルモードでは、標準的なメモリに関しては、メモリセルへのデータ入出力は、アドレスバス上でのアドレス設定により行なわれ、一つのカラムと一つのローが選択される。ローとカラムにより選択されたメモリセルは、リード / ライト線のステータスに応じて、データ転送の入力セルまたは出力セルとして選ばれる。

40

**【 0 0 3 8 】**

コールアウトモードでは、データ検索処理は以下の 2 つのステップにより実行される。

**【 0 0 3 9 】**

第 1 のステップの間、システムはコールアウトモードとライトサイクルで動作する。第 1 のステップの間、オリジンアドレス値はアドレスバス上にセットされ、検索データがデータバス上にセットされる。オリジンアドレスの値は、専用レジスタであるオリジンアドレスレジスタに格納される。

50

**【 0 0 4 0 】**

また、第1のステップの間、各メモリセルはデータバス上のデータセットと各メモリセルに格納されているデータとの比較器による比較処理を実行するために活性化される。比較結果は比較結果格納ビットとして格納される。

**【 0 0 4 1 】**

第2のステップの間、システムはコールアウトモードとリードサイクルで動作する。当該モードでは、レンジ回路および比較結果格納ビットにより選択的にビットマスク回路がイネーブルとされ、データバス上にセルアドレスを出力する。

**【 0 0 4 2 】**

本発明の第1の実施形態の構成の有利な点は、多数の線が不要となるので、メモリセル量を増加したコールアウトメモリを得ることができる点である。本発明の他の優位点は、メモリセル数を低減することなくコールアウトメモリのサイズを低減できる点である。10

**【 0 0 4 3 】**

本発明の第2の実施形態の構成において、メモリセルはローとカラムに配列されている。しかしながら、オリジンアドレス線はメモリセルに接続されていない。コールアウトモードでは第1の実施形態の上記第1のステップおよび第2のステップが用いられている。しかしながら、レンジ機能の実装が図5に示すロー線とカラム線により実現されている。

**【 0 0 4 4 】**

メモリセルは、ライン $r$ とカラム $c$ にある場合、2つのロー“ $r$ ”および“ $r + 1$ ”とカラム“ $c$ ”の入力を受け取る。すべてのセルに共通している共通回路は以下に示す方法によってローとカラムを選択する。もし、オリジンアドレスがメモリセルのロー“ $r 0$ ”とカラム“ $c 0$ ”のアドレスであれば、 $r = r 0$ であるすべてのロー“ $r$ ”が論理ステート“1”にセットされ、 $c = c 0$ であるすべてのカラム“ $c$ ”が選択される。すべての他の線は選択されない。20

**【 0 0 4 5 】**

もし、セルのローとカラムへの入力が以下の条件を満たしているならば、各セル内のレンジ回路はイネーブル信号を比較器に出力する。条件：ローにおいて“ $r + 1$ ”が選択されているか、または、当該“ $r + 1$ ”が選択されていないが、ロー“ $r$ ”とカラム“ $c$ ”の両方が選択されている。30

**【 0 0 4 6 】**

第2の実施形態では、オリジン線は各メモリに配線される必要がないが、その代わり、各メモリセルは次のロー線“ $r + 1$ ”によって選択される。この構成であれば、“ $r + 1$ ”のロー線は隣接するロー線なので配線上の困難性はない。レンジ機能はシンプルに実装されるので、各メモリセルにおける論理ゲート数が低減される。

**【 0 0 4 7 】**

第3の実施形態では、レンジ機能が削除されており、メモリ面積がさらに低減されている。その代わり、メモリビットが後続する検索処理におけるセルのセレクトとディスエーブルに用いられる。本実施形態において想定される一構成例としては、後続する検索処理においてセルのセレクトおよび／またはディスエーブルに用いられるメモリビットが比較結果格納ビットである。40

**【 0 0 4 8 】**

本発明の方法およびデバイスは、コールアウトメモリのセル面積を低減できるという効果を持っている。コールアウトメモリは、検索データを見つけるためにメモリ全体をスキヤンする必要性をなくすことにより操作時間の低減を図ることができ、本発明の方法およびデバイスは、処理時間低減及び面積低減という2つの効果を持っている。

**【 0 0 4 9 】**

本発明のデバイスは、さらに、コールアウト機能の実装に必要となる配線数とゲート数の低減によるコスト低減の効果も有しており、製造工程が単純化され、製造時間も短縮されている。

**【 0 0 5 0 】**

10

20

30

40

50

本発明の好ましい実施形態を図を参照しつつ詳しく説明する。しかしながら、本発明の明細書および特許請求の範囲の技術思想を実現する形態として想定しうる多様の改良とアプリケーションがあることは言うまでもない。

#### 【0051】

図1を参照しつつ、第1の実施形態を説明する。第1の実施形態において、メモリセルはローとカラムに配列されている。ローセレクタとカラムセレクタの2つのモジュールはローとカラムの選択に用いられている。当該ローセレクタとカラムセレクタはメモリデバイス全体に共通して利用されている（「nMOSおよびCMOS型VLSIシステム設計の入門」Amar Murkherjee, Prentice-Hallの8.3章を参照）。データバス線は各メモリセルに接続されている。

10

#### 【0052】

専用の格納部であるオリジンアドレスレジスタは、オリジンアドレス値を格納するために用いられる。当該オリジンアドレスレジスタからの配線セットはオリジン線と呼ばれ、各メモリセルに接続されている。これらオリジン線はオリジンアドレスレジスタに接続されており、オリジンアドレス値がオリジン線上にセットされる。

#### 【0053】

ここでは、アドレスバスとデータバスと制御線とをまとめてバスシステムと呼ぶ。制御線は従来のメモリにも含まれているバスシステムのリードサイクルまたはライトサイクルに用いるリード／ライト線を備えている。

20

#### 【0054】

次に、図2に示すように、第1の実施形態のコールアウトメモリは、以下の3つのモジュールを備えている。システムのバスに対するインターフェースを提供するローセレクタ、カラムセレクタ、オリジンアドレスレジスタである。

#### 【0055】

これらモジュールはデバイスの共通回路に含まれている。なお、図2には、共通回路とロー“r”とカラム“c”にある一つのメモリセルのみが示されているが、本システムのメモリは大量のメモリセル回路を備えていることは理解されよう。

#### 【0056】

各メモリセルは以下の構成要素を備えている。

30

#### 【0057】

データ格納回路。この回路はデータを格納するために用いられ、従来のメモリセル回路と同様のものである。

#### 【0058】

比較回路。この比較回路はデータバス上のデータセットとデータ格納回路内に格納されたデータが、所定の関係を有するものであるかどうかをチェックする。この所定の関係とは、如何なるものでも良く、例えば、大きい、小さい、同一、その他の関係などを含む。この所定の関係はあらかじめ定義されるか、制御線によりセットされるか、特定のバスサイクル操作においてセットされる。もしこの所定の関係の充足が確認できれば、マッチング信号が比較結果格納回路に出力される。この回路は1ビットのメモリであり、比較結果を格納するものである。

40

#### 【0059】

図2に示すように、セル回路はさらに、ビットマスク回路を備えている。この回路は、PCT/IL00/00121で開示されたものと同様のものであり、その詳細構成は図7に示されている。ビットマスク回路の役割は、イネーブルになった場合に、データバス上にセルアドレスを出力することである。マッチングデータを含むメモリセルが複数ある場合、データバス上に一つのアドレスのみを出力するためにフィードバックシステムが用いられる。この場合に出力されるアドレスは、すべてのマッチングするメモリセルのうち、所定方向で一番大きいアドレスとなる。

#### 【0060】

図2に示されるように、ビットマスク回路は、レンジ回路とプライオリティマスク回路を

50

備えている。レンジ回路は、オリジンアドレス値とメモリセルのアドレス値を比較するものである。

#### 【0061】

もし、メモリセルアドレス値の方がオリジンアドレス値よりも所定方向に見て“小さい”場合、イネーブル出力がプライオリティマスクに出力される。ここで“小さい”とは、以下の所定の関係のうちの一つの関係に該当している。“より小さい”、“小さいまたは等しい”、“大きい”、“大きいまたは等しい”。

#### 【0062】

レンジ回路によってイネーブル出力が行なわれた場合、プライオリティマスク回路は、検索データを格納したメモリであって、そのセルアドレスがオリジンアドレスよりも小さいという検索条件を満たしているすべてのメモリのすべての設定ビットについて、データバスの対応するビットを設定し、最終的にプライオリティマスク回路によって選択されたビットのみがデータバス上に現れるようにするために、“OR”論理による当該設定ビットの論理演算を実行するというプロセスを行ない、データバスに出力するビットを選択する。データバス上に現れた演算結果データは、オリジンよりも小さく、アドレスバス上のデータとマッチングするデータを持つもののうち、最も大きいアドレスを持つセルの当該アドレスと等しいものとなっている。

#### 【0063】

コールアウトメモリは2つのモードを持つことができる。ノーマルモードとコールアウトモードである。好ましい実施形態において、専用線COは図2を用いて説明した処理を指定するために用いられる。しかしながら、コールアウトメモリの動作モードを指定する方法としては、公知である多様な方法や技術を用いることができる。

#### 【0064】

ノーマルモードにおいて、メモリ機能は、アドレスがアドレスバス上に設定され、データがデータバス上に設定されるという既存のメモリのあらゆる型のメモリ機能と同様で良い。アドレスはローセレクタとカラムセレクタによって、一組のローセレクトとカラムセレクトにデコードされる。選択されたローとカラムに接続されたメモリセルは、既存のメモリと同様の方法によりデータバスとのデータ入出力のために活性化される。

#### 【0065】

コールアウトモードでは、第1のステップにおいて、メモリはコールアウトモードのライトサイクルになる。この第1のステップでは、オリジンアドレス値はアドレスバスにセットされ、検索データがデータバスにセットされる。

#### 【0066】

第1のステップの間、オリジンアドレスはオリジンレジスタに格納されており、オリジンレジスタはアドレス線上に現れるアドレスを格納するために、コールアウトモード(CO)線およびライトステータスにおけるリード/ライト線によって、活性化されている。

#### 【0067】

また、第1のステップの間、検索データはデータバス上にセットされる。各メモリセルにおいて、比較器はコールアウトモード(CO)線とライトステータスにとなっているリード/ライト線によってイネーブルとされる。セル内に格納されているデータはデータバス上のデータと比較され、もし、マッチングすれば、セル内の比較格納ビットの論理ステータスが“1”にセットされて格納される。マッチングしない場合は、比較格納ビットの論理ステータスは“0”にリセットされて格納される。

#### 【0068】

コールアウトモードの第2のステップにおいて、バスシステムはリードサイクルにセットされる。レンジ回路はオリジンアドレスとメモリセルアドレスを比較するために活性化される。もし、メモリセルアドレスがオリジンアドレスよりも所定方向から見て小さい場合、レンジ回路はイネーブル信号をプライオリティマスクに出力する。マッチングしている場合は、プライオリティマスクは結果格納ビットからイネーブル信号を受信する。プライオリティマスクは両方のイネーブル信号がセットされている場合のみイネーブルとなる。

## 【0069】

最後に、上記に説明したように、(a)マッチングデータを持ち、(b)オリジンアドレスよりも小さい(小さいまたは等しい)アドレスを持ち、さらに、上記(a)と(b)を満たすすべてのメモリセルのうち所定方向に見て最も大きいアドレスを持つというメモリセルのアドレスがデータバスに出力される。

## 【0070】

図3に示すように、第2の実施形態では、オリジン線を各メモリセルに接続しないことにより、さらに、メモリのサイズが低減されている。第2の実施形態のメモリは、第1の実施形態のメモリと同様の機能を備えている。異なる点は、ロー線とカラム線の状態に応じて実行されるレンジ機能に関する実装部分である。図4に示すように、ロー“r”とカラム“c”にあるメモリセルのレンジ回路は2つのロー“r”と“r+1”的入力と、1つのカラム“c”的入力を受ける。10

## 【0071】

ロー・セレクタとカラム・セレクタはコールアウトモードでライトサイクルである場合において以下の機能を備えている。

## 【0072】

コールアウトとライトサイクルがセットされた場合、オリジンアドレス値はアドレスバス上にセットされる。ノーマルモードでは、アドレスは1つのロー“r0”と1つのカラム“c0”にデコードされてセレクト(セット)される。コールアウトモードでは、r=r0であるすべてのロー“r”と、c=c0であるすべてのカラム“c”がセレクト(セット)される。20

## 【0073】

本実施形態では、rはr0より小さいまたは等しく、cはc0より小さいまたは等しいものとするが、他の関係、例えば、小さい、大きい、大きいまたは等しいなどの関係でもよいことは理解されよう。

## 【0074】

レンジ回路は、イネーブル信号を出力するためのシンプルな論理演算を実行する。本実施形態では、ロー“r+1”がセレクトされるか、ロー線“r”またはカラム線“c”がセレクトされた場合にイネーブル信号が出力される。

## 【0075】

図5は、本発明の実施形態2にかかる方法を説明するものであって、9つのメモリセルと、ロー線“r”，“r-1”，“r-2”と、カラム“c+1”，“c”，“c-1”に対するレンジ回路を示している。この例では、オリジンアドレス値は“r”と“c”にエンコードされ、ロー“r”，“r-1”，“r-2”と、カラム“c+1”，“c”，“c-1”がセレクトされる(図5で強調されている)。本発明の方法に応じて、レンジ回路はイネーブル信号を図5の8つのメモリセル(強調されているセル)に出力する。レンジ回路の機能はローとカラムをリザーブする役割を持つことが明らかに分かる。30

## 【0076】

第2の実施形態では、オリジンアドレスは格納される必要はない。その代わり、レンジ機能がコールアウトモードの第1のステップの間に、オリジンアドレスのロー線とカラム線により与えられるオリジンアドレス値よりも小さいアドレスを持つという条件を満たすメモリセルのセレクトによって実行される。セルがレンジ回路によりイネーブルとされた場合、イネーブル出力信号が比較回路に接続される。もし、レンジ回路が比較器をイネーブルとした場合、メモリセルがマッチングデータをもっていることを意味し、比較結果格納ビットがセットされる。当該メモリセルは、プライオリティマスクが次のステップでイネーブルとなることによりデータバス上にアドレスを出力するセルの候補となる。

## 【0077】

第1の実施形態で述べたように、プライオリティマスク回路は、検索データを格納し、かつ、セルアドレスがオリジンアドレスよりも小さいという検索要求を満たしているすべてのメモリのすべてのセットビットを“OR”論理により計算し、データバスに対応するビ40

ットがセットされて最終的にプライオリティマスク回路によってセレクトされたビットのみがデータバス上に現れるように演算するという処理によってデータバスに出力されるビットをセレクトする。データバス上に現れる演算結果データは、アドレスバス上のデータとマッチングするデータを格納しているセルで、所定方向から見てオリジンセルよりも小さいアドレスのうち最も大きいアドレスと等しいものとなる。

#### 【0078】

本実施形態2は、コールアウト機能を実行する能力を持つメモリについて、そのサイズの低減を実現したという本発明のシステムおよび方法のさらなる効果が示されている。

#### 【0079】

第3の実施形態は、図6に示すように、コールアウトメモリはレンジ回路を備えていない。その代わりに、先行するコールアウトサイクルにおいてマッチングするものが既に見つかっている場合には、比較結果格納部が比較器の役割を果たしている。 10

#### 【0080】

本実施形態において、比較結果格納ビットは、各コールアウトサイクルにおいてリセットされず、その代わり、アプリケーションの要求に応じた特定のイベントにおいてリセットされる。そのため、例えば、検索要求に応じた後続の検索処理において、既に検索済みのアドレスがディスエーブルとなる。

#### 【0081】

比較結果格納ビットは、アプリケーションの要求に応じた標準的なリード手段とライト手段を備えている。そのため、例えば、新規データの特定のセルへの書き込みにより、セルの比較結果格納ビットはリセットとされる。また、専用線がメモリまたはメモリの一部の比較結果格納ビットをリセットするために用いられても良い。 20

#### 【0082】

各セルへの特定信号をセットするために既知の多様な方法が用いられ得ることが理解されよう。これらの信号はメモリの比較機能をディスエーブルまたはイネーブルするために使われ、コールアウトサイクルの間、特定セルをスキップするための手段ともなる。

#### 【0083】

図7において、オリジンアドレス線に接続されたレンジ回路と、データバスに接続されたOR論理回路と、データバスに接続されたプライオリティ回路を備えた第1の実施形態のメモリセル用のビットマスク回路が示されている。 30

#### 【0084】

上述したように、レンジ回路は、特定セルのアドレスとオリジンアドレスを比較する処理を実行する。もし、所定方向から見てオリジンアドレスが大きいならば、当該レンジ回路はイネーブル信号を出力する。他のイネーブル信号E1は、メモリがコールアウトでリードモードになっている場合に出力される。

#### 【0085】

第3のイネーブル信号E2は、比較格納ビットから出力される。

#### 【0086】

AND機能は、3つのイネーブル信号を受け、ファイナルイネーブル信号をプライオリティマスクに出力する。

#### 【0087】

これは、以下の3つの条件が充足された場合にのみ、プライオリティマスクがイネーブルとなることを確認するためのものである。

#### 【0088】

(a) メモリがコールアウトでライトモードとなっている

(b) セルアドレスがオリジンアドレスよりも(所定方向から見て)小さい

(c) 先行のコールアウトでライトサイクルの間、データバス上に現れているデータがセル内に格納されているデータとマッチングしているものである

次に、図8に、データバスに接続されたOR論理回路と、データバスに接続されたプライオリティマスク回路を備えた第2の実施形態のメモリセルのビットマスク回路を示す。本 50

実施形態では、メモリがコールアウトでリードモードにあり、比較結果格納ビットがセットされている場合にイネーブル信号が生成される。生成されたイネーブル信号はプライオリティマスクに出力される。

【0089】

図7、8、9において、セルアドレスは、Nにより表わされている。このNは以下のように書くことができる。

【0090】

【数1】

$$N = \sum_{k=0}^K 2^{[u(N, k)]}$$

【0091】

ここで、 $u(N, k)$ はNの設定桁数の2進表現を示しており、“0”から“W-1”までの値であり(Wはセルアドレスを表現するために用いられたビット数である)、 $k+1$ は特定アドレス値Nの設定桁数であり、 $B[U]$ はデータバスのビットuの値(0か1)を示している。

【0092】

プライオリティマスク回路の処理は、以下のようになる。

【0093】

図7と図8の両図において、ビット $u(N, k)$ セットを持つすべてのメモリセル(M)からのすべての $P[M, u(N, k)]$ 線は、上述のOR論理回路に入力され、当該回路の出力はデータバス上にビット $u(N, k)$ としてセットされる。Mは、ビット $u(N, k)$ セットを持つすべてのセルのアドレスを示す任意の数である。

【0094】

コールアウトサイクルの始めにおいて、データバス線 $B[0]$ から $B[W-1]$ は、非活性(ロジック0)の初期状態となる。例えば、もし、負論理を用いている場合、すべての線が抵抗によってシステムの供給電力の正側に“プルアップ”される。第1のステップにおいては、他の多くのセルがOR回路の働きによってデータバス線をセットすることとなる。データバスの新たな状態は各セルのプライオリティマスク回路によりそれぞれ検知され、プライオリティマスクの働きによりいくつかの $P[N, u(N, k)]$ 線が非活性化される。最後に検索データを格納している最も大きいアドレスにおいてセットされていないビット $P[N, u(N, k)]$ がリセットされ、データバスは最も大きいセルアドレスにセットされる。

【0095】

上記プロセスの結果、もし、以下のうちいずれかの条件が満たされないならば、“プライオリティマスク”はすべての $P[N, u(N, k)]$ 線をゼロ論理状態にリセットする。

【0096】

- セルアドレスがオリジンアドレスより大きいまたは等しい。

【0097】

- セルに格納されているデータがデータバス上に現れているデータと等しい。

【0098】

- メモリがコールアウトモードではない。

【0099】

この処理は非同期に行なわれ、線の値を安定化させるための期間は、回路の電気的構成要素が昇圧される時間と同じオーダーである。その結果、1つのデータの検索に要する時間は、通常のリードまたはライトサイクルと同じオーダーの時間となる。

【0100】

図9に「プライオリティマスク」回路を詳細に示す。図9の「プライオリティマスク」回路は、もし、以下の条件が満たされている場合、ビット $P[N, u(N, k)]$ を出力する。

**【0101】**

もっとも大きなビットセット $u(N, K)$ に対して、

(a) “E”信号がアクティブであるか。

**【0102】**

(b)かつ、 $u(N, K)$ より大きなすべてのデータバスのビットがセットされていないか。

**【0103】**

もし、大きなビットが無いならば、最も大きなビットはビット“W-1”(ここで、Wはセルアドレスを表現するために使われるビット数を示す)となり、当該ビットは“E”信号によって直接セットされる。

**【0104】**

他のビット $u(N, K), k < K$ に対して、

(a)大きなビット $u(N, k+1)$ がセットされていること。

**【0105】**

(b)かつ、現在のビット $u(N, k)$ とそれより大きなビット $u(N, k+1)$ の間にある内部バス $B[u(N, k)]$ のすべてのビットがセットされていないこと。

**【0106】**

これは、より大きなアドレスを持つ他のセルが、そのアドレスをデータバスの現在のセルにセットされていないビットに出力したか、ビットkと現在のセルアドレスよりも小さなビットが出力されていかどうかを確認するための条件である。

**【0107】**

上記は降順検索について説明したものであって、昇順検索を実行するように定義されているシステムにおいては、データバスに最も小さなアドレスを持つマッチングメモリセルが出力されることが理解されよう。

**【0108】**

本発明のメモリシステムおよび方法は、通常使われるコンピュータと互換性を持ち、コンピュータシステムや通信システムやその他システムなどの電子システムにおいて多様で広い適用性を持ち、標準的な多様なタイプのメモリと共にまたはその代わりに用いることが可能であるという優位点を有する。

**【図面の簡単な説明】**

**【図1】**本発明にかかる、各メモリセルにアドレス線が配線されていないコールアウトメモリの模式図である。

**【図2】**図1の構成に応じたメモリセル回路のブロック図である。

**【図3】**本発明にかかる、各メモリセルにオリジン線が配線されていないコールアウトメモリの模式図である。

**【図4】**図3の構成に応じたメモリセル回路のブロック図である。

**【図5】**本発明にかかる、図3の構成に応じたコールアウトメモリ内のセルのレンジ回路の模式図である。

**【図6】**本発明にかかる、レンジ回路が設けられていないコールアウトメモリ内のセルの模式図である。

**【図7】**図1および図2の構成におけるビットマスク回路の模式図である。

**【図8】**図3および図4の構成におけるビットマスク回路の模式図である。

**【図9】**プライオリティマスク回路の詳細構成例を示す図である。

10

20

30

40

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

## 【国際公開パンフレット】

(12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(43) International Publication Date

3 January 2002 (03.01.2002)

PCT

(10) International Publication Number

**WO 02/01570 A1**

(51) International Patent Classification<sup>7</sup>: G11C 15/04,

15/00

Peer, 38510 Hadera (IL). PROKOPETS, Shmuel (IL/IL);

29 Ben Gurion St., 51265 Bnei Brak (IL).

(21) International Application Number: PCT/IL00/00327

**Agent:** CALDERON, Hana; Jacob & Hana Calderon,

Hahilazon Street 12, Crystal Building, 52522 Ramat Gan

(IL)

(22) International Filing Date: 7 June 2000 (07.06.2000)

(25) Filing Language: English

**Designated States (national):** AE, AG, AL, AM, AI, AU, AZ, BA, BB, BG, BR, BY, CA, CH, CN, CR, CU, CZ, DE, DK, DM, DZ, EE, ES, FI, GB, GD, GE, GH, GM, HR, HU,

(71) Applicant (for all designated States except US): MEM-

CAL INC (US/US); Yang, Bing; 126 Carter, Lakewood, Co

IIJ, IL, IN, IS, JP, KB, KG, KP, KR, KZ, LC, LK, LR, LS,

LT, LU, LV, MA, MD, MG, MK, MN, MW, MX, MZ, NO,

NZ, PL, PT, RO, RU, SD, SE, SG, SI, SK, SL, TJ, TM, TR,

TT, TZ, UA, UC, US, VE, VN, YU, ZA, CZ, DE

Milburn, 2 Wall Street, New York, NY 10005 (US).

Designated States (regional): ARIPO patent (GH, GM,

(72) Inventors; and

(75) Inventors/Applicants (*for US only*): **VILLARET, Yves, Emmanuel** [IL/IL]; 9 Hakinor St., P.O. Box 8748, Shikun

KE, LS, MW, MZ, SD, SL, SZ, TZ, UG, ZW), Eurasian patent (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European patent (AT, BE, CH, CY, DE, DK, ES, FI, FR, GB, GR, IE,

*[Continued on next page]*

(54) Title: CALL OUT MEMORY WITH REDUCED SURFACE

**(57) Abstract:** A memory system and method that enables locating memory cells that contain a searched data using a limited number of lines and thus reducing the necessary memory surface while at the same time accelerating the search process by limiting the search to cells having a predefined characteristic. The memory system comprises an address bus and a data bus, a row selector and a column selector and a two dimensional array of memory cells, each memory cell comprising a mask circuit, a comparator circuit, a memory bit for storing the comparison results and in some embodiments the cell also comprises a range circuit. The memory may be operated in a read and write mode or it may be operated in a novel, fast search mode.

---

**WO 02/01570 A1**

IT, LU, MC, NL, PT, SE), OAPI patent (BF, BJ, CF, CG, CI, CM, GA, GN, GW, ML, MR, NE, SN, TD, TG). *For two-letter codes and other abbreviations, refer to the "Guidance Notes on Codes and Abbreviations" appearing at the beginning of each regular issue of the PCT Gazette.*

**Published:**

— *with international search report*

WO 02/01570

PCT/IL00/00327

## Call Out Memory with Reduced Surface

### Field of the Invention

The present invention relates to memories with a Call Out function or Call Out Memories (COM). In the framework of the present application a Call Out function is defined as a function of searching a memory wherein: 1) among the total of memory cells a number of cells is selected on which a search can be performed 2) a value to be searched is presented on a bus 3) the memory returns on a bus the address of one memory cell having matching data, that memory cell being the one with the highest address in a predefined direction among all the selected cells. The Call Out function eliminates the need to scan all the memory cells in order to locate those containing the requested data, whereby operation time is considerably reduced. Examples of memories with a Call Out function have been described in Patent Application PCT/IL 00/00121 to MemCall. The Call Out Memory of PCT/IL 00/00121 has a parallel organization wherein each cell is independently connected to an Address bus, a Data Bus and an Origin Bus. As a result, response time becomes independent of memory size, of the position of the searched data or the number of logic gates necessary to implement the "Call Out" function.

The Call Out Memory of PCT/IL 00/00121 is characterized in that the data to be searched is set on the address bus. When the device operates in the "Call Out" mode, each memory cell performs a comparison between Data conveyed to the cell by the Address lines and Data stored in the cell. In case that the Comparison results in a "Match" condition for several cells, then the Address of a single Matching Cell is set on the Data Bus. That particular cell must verify the condition of having 1) an Address Value smaller in a predefined direction than a preset, so called Origin Value, and 2) having the closest Address Value to this Origin Value among all cells with Matching Data and verifying condition 1). The cycle may then be repeated with the Matching Cell that has been set on the Data Bus as the new Origin and the process can be repeated again and again until all matching cells are found.

SUBSTITUTE SHEET (RULE 26)

WO 02/01570

PCT/IL00/00327

A "Call Out" device as described in PCT/IL 00/00121 may also be operated in a so called Normal mode, wherein its function is similar to a standard Memory of one of the known types.

It will be understood by those versed in the art that the Call Out Memory device of PCT/IL 00/00121 requires a considerable number of lines in order to enable the Call Out function.

In a the Call Out device of PCT/IL 00/00121 each individual cell performs a comparison of the Data set on the Address Bus and the data stored into that cell. It is thus required that each memory cell be connected to a number of Address lines.

Further, each memory cell performs a comparison of its own Address with the Origin Address value, whereby if the Cell Address is inferior to the Origin Address in a predefined direction, then and only then a Priority Mask circuit within the cell is enabled. This function requires that an additional number of lines be used and connected to each memory cell, in order to convey the Origin Address value to each cell.

The Priority Mask circuit then selects the bits to be output to the Data Bus by a process wherein all set bits of all memory cells storing the searched data and fulfilling the requirement of the cell address being smaller than the "Origin" address are combined in an "OR" function to set the correspondent bit of the Data Bus. The overall function of the "Bit Mask" circuit is to mask the bit outputs that would cause a change in the bits of a higher address in case that they were output on the Data Bus together with that higher address. As a result, the final data seen on the Data Bus will be equal to the Address of the cell with the highest address but smaller than Origin and containing the data that match the data applied on the Address Bus.

It is therefore necessary, in order to enable the Call Out function in a system designed according to Patent PCT/IL 00/00121, that several Address Lines and several Origin Lines be connected to each of the Memory Cells respectively.

In case that a COM device is implemented in the form of a chip, each memory cell will have to be given a sufficient surface S1 in order to provide routing space for all Address and Origin lines. In order to implement the logic functions of each memory cell, another minimum space S2 is required.

WO 02/01570

PCT/IL00/00327

Where S2 is larger than S1, it may be possible to connect the above address and origin lines to each Memory Cell, without any increase of the surface requirement. However if S1 is larger than S2, then the routing of the Address lines and Origin lines will require a space for each memory cell that exceeds the space that would have been sufficient for performing the logic functions of the cell.

It will be understood that such additional space requirement will reduce the total number of cells that can be installed on one chip, thus reducing COM capacity. Also cost per memory cell will be increased.

It is therefore desirable to design a memory with a Call Out function wherein the number of lines connected to each memory cell is reduced.

It is known to arrange memory cells in a two dimensional array, such that each cell is selected by one Row and one Column. (see "Introduction to nMos and CMOS VLSI System Design", Amar Murkherjee, Prentice-Hall, Chapter 8.3). This method allows the addressing of one memory cell by means of two lines only, one Row and one Column. The logical function used to select the cell is very simple, being a simple AND function of Row and Column set state. This simplified select function reduces the surface needed for each cell, since only a simple logical AND function is needed at each Memory Cell.

It would be desirable to use a similar method and design in a Memory with a Call Out function, thus reducing the number of logical gates required and enabling the implementation of Call Out devices, for example chips, with an increased number of Memory Cells without an increase in the size of the Memory device.

### **Summary of the Invention**

The present invention relates to a system and method of implementation of a Call Out memory that enables reduction of the memory cell surface, thereby increasing the number of memory cells for a device of a given surface.

The reduction of memory surface is achieved by reducing the number of lines that need to be connected to each memory cell.

WO 02/01570

PCT/IL00/00327

Each of the memory cells of the inventive Call Out system comprises a Priority Mask circuit similar to that described in Patent PCT/IL 00/00121, but the memory is constructed in accordance with a novel design wherein the Address Lines are neither routed nor connected to each memory cell separately. Instead, only one "Row" and one "Column" are routed to each memory cell, in accordance with a two dimensional array often applied in conventional memories.

In the inventive Call Out system the same "Row" and "Column" can also be used to implement the Range function. Using the said Row and Column, each memory cell performs the function of comparing its own address value with the Origin Address, and selectively enables the Priority Mask for that cell according to the result of that comparison. Due to the inventive design, the need for routing of the Origin lines to each memory cell is eliminated, and further reduction of Cell Surface is achieved.

The inventive method may be exemplified by three preferred embodiments. All embodiments are Call Out devices with a reduced number of lines routed to each memory cell. In the first two preferred embodiments the Searched Data is presented on the Data Bus, the Origin Address Value is presented on the Address Bus, and the comparison result of each memory cell is stored in a dedicated one-bit memory cell added to each Memory Cell of the device.

In the first embodiment, a Call Out memory is implemented wherein the Address lines are not connected to the Memory Cells, and the Cells are arranged in Rows and Columns as known for certain standard memory devices while the system still enables the device to carry out the Call Out functions.

In a second embodiment, a further improvement is implemented, according to which neither the Address lines nor the Origin Lines are connected to the memory cells. In this second embodiment the Range function of the Call Out device is assisted by selective setting of the said Columns and Rows in accordance with a predefined relationship with the origin address.

In a third embodiment, the range circuit is not used such that a further reduction of surface is achieved. Instead, a memory bit within the cell is used to select the cells according to the needs of the memory and disable them for a subsequent call out search or the cells may be disabled by a designated line.

WO 02/01570

PCT/IL00/00327

**Brief Description of the Drawings.**

- Fig 1 is a schematic drawing of a Call Out memory in which Address Lines are not routed to each memory cell.

- Fig 2 is a block diagram of a circuitry with a memory cell according to the embodiment of Fig. 1

- Fig 3 is a schematic drawing of a Call Out memory in which Origin Lines are not routed to each memory cell.

- Fig 4 is a block diagram of a circuitry with a memory cell according to the embodiment of Fig. 3.

- Fig 5 is a diagram of a Range Circuit in a cell within a Call Out Memory according to the embodiment of Fig. 3.

- Fig 6 is a schematic drawing of a cell within a Call Out memory implemented without a Range circuit

- Fig 7 is a diagram of a Bit Mask circuit for the embodiment of Figs. 1 and 2

- Fig 8 is a diagram of a Bit Mask circuit for the embodiment of Figs. 3 and 4

- Fig. 9 shows a detailed example of a Priority Mask circuit

**Detailed Description of the Preferred Embodiments**

The purpose of the present invention is to provide a method and system for a memory whereby the Call Out function may be performed with a reduced number of logical gates and a reduced number of connection lines. The term Call Out function is used to designate a method of searching for data in a memory or part of it wherein among the total of memory cells a number of cells is selected on which a search can be performed; a value to be searched is presented on a Bus, for each selected memory cell a comparison is performed between the said value and the Data stored in the cell; in case that the Comparison results in a "Match" condition for several cells, then the address of a single Matching Cell with the highest address among all the selected cells is set on a Bus and the cycle may be repeated again and again until all matching cells are found.

WO 02/01570

PCT/IL00/00327

In a first embodiment of the inventive system, shown in Fig 1, Memory Cells are arranged in a two-dimensional array, i.e. in rows and columns. Each Memory cell is then connected to several Data Bus lines, to several Origin Lines, and to one Column Line and one Row Line. Additional control lines, such as a Read/Write line, are also connected to each cell. Each Memory Cell comprises a Data Storage Circuit, a Comparator, an added bit of memory that will be referred to hereinbelow as Comparison Result Storage Bit, a Range Circuit and a Bit Mask Circuit.

It is known from standard memories that in such a two dimensional array the column lines need not necessarily be connected to each of the memory cells of the column. A further variation of the first preferred embodiment is therefore suggested wherein the column lines are used to connect the bit lines of the Data Bus to the memory cells of the column by means of transistor switches rather than the column lines being connected to each individual memory cell of the column (see "Introduction to nMos and CMOS VLSI System Design", Amar Murkherjee, Prentice-Hall, Chapter 8.3).

The above described methods and any other similar method, used in the art to selectively activate cells within a Row or a Column will be further referred to as Row Select or Column Select whereas a Row or a Column selected by the said methods will be referred to as Selected Row or Selected Column.

The inventive system can be operated in two modes, Normal mode and Call Out mode.

In the Normal Mode, Data can be transferred to or from a Memory Cell as for standard memories, i.e. an address set on the address bus is processed, and one column and one row are selected. The memory cell selected by these Row and Column is then selected for the Data transfer to or from the memory, according to the state of the R/W line.

In the Call Out mode, a Data search operation is performed in two steps:

During the first step, the system is placed in the Call Out mode and Write cycle. During this first step the Origin Address value is set on the Address Bus, while the Searched Data is set on the Data Bus. The Origin Address value is stored in a dedicated register, Origin Address Register.

WO 02/01570

PCT/IL00/00327

Also during that first step, each memory cell is activated to perform a comparison between the Data set on the Data Bus and the data stored in that cell by means of a Comparator. The result of the comparison is then stored in the Comparison Result Storage bit.

During the second step, the system is placed in the Call Out mode and Read mode. In this mode the Range Circuit and the Comparison Result Storage bit selectively enable the Bit Mask circuit to output the Cell Address to the Data Bus.

It is the advantage of the invention according to the first embodiment that a large number of lines is eliminated whereby the design of Call Out memories with an increased amount of memory cells is made feasible. It is another advantage of the invention that the size of a Call Out memory device may be reduced without reducing the number of memory cells within the device.

In a second embodiment, Memory Cells are also arranged in rows and columns. However no Origin Address lines are connected to them. The same first and second steps are used in the Call Out mode, as in the case of the first embodiment. However the implementation of the Range function is now assisted by the Row and Column lines as shown in Fig. 5.

Each Memory Cell, at Line r and Column c, receives as input two Rows r and r+1, and one Column c. A circuit common to all the cells of the device will select the Rows and Columns in the following way: If Origin Address is the address of Memory Cell at Row r0 and Column c0, then all Rows r with  $r \leq r0$  will be set to logic state 1, and all Columns c with  $c \leq c0$  will be selected. All other lines will remain unselected.

The Range Circuit within the individual cell then outputs an enabling signal to the Comparator if the Rows and Columns input of the cell satisfies the following conditions: Row r+1 is selected, Or, r+1 is not selected but r and c are both selected.

In this second embodiment, Origin lines do not need to be routed to each memory cell. Instead, each memory cell is additionally selected by the next Row line r+1. This does not create difficulties in the routing, since the r+1 Row is a neighboring Row. Also the Range function is implemented in a very simple way, thus reducing the number of logic gates in each Memory Cell.

WO 02/01570

PCT/IL00/00327

In a third embodiment, the Range function is eliminated, whereby the memory surface is further reduced. Instead, a memory bit is used to select the cells and disable them for subsequent search. In accordance with one design envisaged for this embodiment, the memory bit that is used to select the cells and/or disable them for subsequent search is the Comparison Result Storage bit.

The inventive method and device have the advantage of reducing the cell surface for a Call Out memory device. As the Call Out memory considerably reduces operation time by eliminating the need to scan the whole memory in order to find the searched data, the device and method of the invention have the double advantage of being both time and space saving.

The inventive device has the further advantage of saving costs by reducing the amount of lines and gates necessary for implementing the Call Out function whereby manufacture is simplified and manufacture time is reduced.

The invention will now be described in detail in respect of the preferred embodiments and with reference to the drawings. It will be understood however that many modifications and applications of the invention may be envisaged that still remain within the scope of the specification and the claims.

In reference to Fig 1, a first embodiment is shown. In that first embodiment, Memory Cells are arranged in Rows and Columns. Two modules, namely a Row Selector and a Column Selector, are used to select Rows or Columns. The Row Selector and Column Selector are commonly used in Memory devices (see "Introduction to nMos and CMOS VLSI System Design", Amar Murkherjee, Prentice-Hall, Chapter 8.3). Data Bus Lines are also connected to each Memory Cell.

A dedicated storage section, Origin Register, is defined and used to store an Origin Address value. A set of Lines, called Origin Lines, is connected to each Memory Cell. These Origin Lines are also connected to the Origin Register, so that the Origin Address Value may be set on the Origin Lines.

WO 02/01570

PCT/IL00/00327

The ensemble of Address Bus, Data Bus and Control Lines will be referred to as Bus System. The Control Lines comprise a Read/Write Line that is used to define a Read or Write cycle for the Bus System as known for conventional memories.

Referring now to Fig. 2, the Call Out memory of the first embodiment comprises three modules: Row Selector, Column Selector and Origin Register that provide an interface to the System Bus.

These modules are comprised in the Common Circuitry of the device. It will be understood that a memory device comprises a large number of Memory Cell circuits although Fig. 2 only shows the Common Circuitry, and one Memory Cell at a given Row r and Column c.

Each Memory Cell comprises the following elements:

A Data Storage Circuit. This circuit is used to store the Data, and it is similar to equivalent circuits in memory cells commonly used in the art.

A Comparator circuit. The Comparator checks whether Data set on Data Bus and Data in the Data Storage Circuit verify a given relationship. This given relationship may be of any kind, for example Bigger than, Smaller than, Equal or any other relationship. The given relationship may be predefined, or set by some control lines, or set by a specific Bus Cycle operation. If the given relationship is verified, then a Match Signal is output to a Comparison Result Storage circuit. This circuit is a one bit memory, storing the result of the comparison.

As shown in Fig. 2, the cell circuit further comprises a Bit Mask Circuit. This circuit is similar to that described in PCT/IL 00/00121 and it is shown in detail in Fig 6. The role of the Bit Mask Circuit is to output, when enabled, the Cell Address on the Data Bus. Since several Memory Cells contain matching data, an inventive feedback system is used in order to output on the Data Bus only one Address, that Address being the highest in a predefined direction, among all matching Memory Cells.

As seen in Fig. 2, the Bit Mask circuit comprises a Range circuit and a Priority Mask circuit. The Range circuit compares the Origin Address value with the Memory Cell Address value.

WO 02/01570

PCT/IL00/00327

If the Memory Cell Address value is "Lower", in a predefined direction, to the Origin Address value, then an enabling output is issued to the Priority Mask. "Lower" here is one of the following predefined relationships: "Smaller", "Smaller or Equal", "Bigger", "Bigger or Equal".

In the event of an enabling output by the Range Circuit, the Priority Mask circuit selects the bits to be output to the Data Bus by a process wherein all set bits of all memory cells storing the searched data and fulfilling the requirement of the cell address being smaller than the Origin address are combined in an "OR" function to set the correspondent bit of the "Data Bus" and finally only the bits selected by the Priority Mask circuit are passed through to the Data Bus. The resulting data seen on the Data Bus will then be equal to the Address of the cell with the highest Address but smaller than Origin and containing the Data that match the data applied on the Address Bus.

The Call Out Memory device can be placed in two modes, Normal mode and Call Out mode. In the preferred embodiment, a dedicated line CO is used for that purpose as shown in Fig. 2. It will be understood however, that any of the various methods or techniques known in the art can be used to set the operating mode of the Call Out memory.

In the normal mode, the function of the memory is similar to that of the various types of existing memories wherein the Address is set on the Address Bus, and the Data is set on the Data Bus. The Address is decoded by the Row Selector and Column Selector into one Column select and one Row select. The Memory Cell that is connected to both selected Row and Column is activated for Data Transfer to or from Data Bus, in the usual way known for memories.

In the Call Out mode, in a first step, the memory is placed in the Call Out mode and Write Cycle. In that first step, the Origin Address Value is set on the Address Bus, and the Data to be searched is set on the Data Bus.

During that first step, the Origin Address is stored in the Origin Register, the said Origin Register being activated to store the Address set on the Address Lines by the Call Out mode (CO) and the Read/Write line in the Write state.

WO 02/01570

PCT/IL00/00327

Also during that first step, the Data to be searched is set on the Data Bus. In each Memory Cell, the Comparator is enabled by the Call Out mode (CO) and the Read/Write line in the Write state. The Data stored in the Cell is compared to the Data on the Data Bus and in the event that there is a match, the Result Storage bit of that Cell is set to logic state 1 and stored. Otherwise the Result Storage bit is reset and stored.

In a second step of the Call Out mode, the Bus system is set to a Read cycle. Then the Range Circuit is activated to compare the Origin Address with the Memory Cell Address. If the Memory Cell Address is lower (or lower or equal) than the Origin Address, in a predefined direction, then the Range Circuit outputs an enabling signal to the Priority Mask. In case of a match the Priority Mask receives another Enabling signal from the Result Storage bit. The Priority Mask is enabled only if both Enabling signals are set.

Finally, as explained before, the address of the Memory Cell having a) matching data, and b) Address inferior (or inferior or equal) to the Origin Address, and having the highest address in a predefined direction among all Memory Cells verifying a) and b), will be output on the Data Bus.

In reference to Fig 3, a second embodiment is shown wherein the size of the memory device is further reduced by the Origin Lines not being connected to each memory cell. The device designed in accordance with the second embodiment has a similar function to that of first embodiment. The only difference is in the implementation of the range function that is now performed according to the state of the Row Lines and Column Lines. As shown in Fig 4, each Memory Cell Range circuit at Row r and Column c, receives as input two Rows r and r+1, and one Column c.

The Row Selector and Column Selector now have a function in the Call Out mode and Write Cycle, as explained in the following:

When both Call Out and Write cycle are set, an Origin Address value is set on the Address Bus. In Normal mode, that Address would be encoded as one Row r0 and one Column c0 being selected (set). In Call Out mode, all Rows r with  $r \leq r_0$ , and all Columns c with  $c \leq c_0$  are selected (set).

WO 02/01570

PCT/IL00/00327

While in the preferred embodiment  $r$  smaller or equal to  $r_0$  and  $c$  smaller or equal to  $c_0$  were chosen by way of example, it will be understood that any ordering relation can be chosen, such as smaller, bigger, bigger or equal, or other.

The Range Circuit then performs a simple logical function to output an Enabling signal. In this preferred embodiment the Enabling signal will be output if Row  $r+1$  is selected, or if both Row Line  $r$  and Column Line  $c$  are selected.

Fig 5 demonstrates the inventive method of the second embodiment by showing the Range Circuit for nine Memory Cells, for Row Lines  $r$ ,  $r-1$  and  $r-2$ , and for Columns  $c+1$ ,  $c$  and  $c-1$ . In this example, the Origin Address value is encoded as  $r$  and  $c$ , so that Rows  $r$ ,  $r-1$  and  $r-2$  and Columns  $c$  and  $c-1$  are selected (weighted in Fig 5). In accordance with the inventive method, the Range Circuit outputs an Enabling signal for eight Memory cells of Fig 5 (weighted cells). It is obvious that for the Range Circuit function, the roles of Rows and Columns may be reversed.

In this second embodiment, the Origin Address need not be stored. Instead, the Range function is partly performed during the first step of the Call Out mode, by the selection of memory cells that fulfil the condition of having an address that is lower than the Origin Address value as defined by the Row Line and the Column line of the said Origin Address. Where the cell is enabled by the Range Circuit, the enabling output signal is connected to the Comparator circuit. If the Range circuit enables the Comparator, and the Memory Cell has matching Data, then the Result Storage bit will be set, and the Priority Mask will be enabled at the next step, making that Memory Cell a candidate to Output its Address on the Data Bus.

As described for the first embodiment, the Priority Mask circuit selects the bits to be output to the Data Bus by a process wherein all set bits of all memory cells storing the searched data and fulfilling the requirement of the cell address being smaller than the Origin address are combined in an "OR" function to set the correspondent bit of the "Data Bus" and finally only the bits selected by the Priority Mask circuit will be passed through to the Data Bus. The resulting data seen on the Data Bus will then be equal to the Address of the cell with the highest Address but smaller than Origin in a predefined direction and containing the Data that match the data applied on the Address Bus.

WO 02/01570

PCT/IL00/00327

This second embodiment further demonstrates the advantages of the inventive system and method, achieving an even stronger reduction in the size of a memory device that is capable of performing a Call Out function.

In a third embodiment, shown in Fig. 6, the Call Out Memory device does not comprise a Range Circuit. Instead the Comparison Result Storage is used to inhibit the comparator in case that a match has already been found in a previous Call Out cycle.

In this embodiment, the Comparison Result Storage Bit is not reset at each Call Out Cycle instead it is reset upon specific events, these events being defined according to application requirements. Thus for example, an address that has already been searched may be disabled, upon request, for subsequent searches.

The Comparison Result Storage Bit may be provided with standard reading or writing means, depending on application requirements. Thus for example writing a new data to the particular cell may reset the Comparison Result Storage bit of that cell or a designated line may be used to reset all Comparison Result Storage bits of the memory device or any part of them.

It will be understood that many ways known in the art exist for setting a specific signal for each cell. Such signal may then be used to disable or enable the comparing function of the cell, thus providing means to skip specific cells during the Call Out cycle.

In Fig. 7, a Bit Mask Circuit for a Memory Cell of the first preferred embodiment is shown with a Range Circuit connected to an Origin Address Line, an OR logical circuit connected to a Data Bus and a Priority Mask Circuit, also connected to the said Data Bus.

As explained before, the Range Circuit performs a comparison between the Address of the specific cell with the Origin Address. If the Origin Address is bigger in the predefined direction, then this circuit outputs an enabling signal. Another Enabling signal E1 is issued when the device is placed in the Call Out and Read mode.

A third Enabling signal E2 is issued from the Comparison Storage bit.

An And function gathers these three enabling signals, and outputs a final Enabling signal to the Priority Mask.

WO 02/01570

PCT/IL00/00327

This ensures that the Priority Mask will be enabled if and only if the three following conditions are fulfilled:

- a)The device is placed in the Call Out and Write mode

- b) The cell Address is smaller than Origin Address (in predefined direction)

- c)The data presented on Data Bus during previous Call Out and Write cycle was found matching the data stored in the Cell.

Referring now to Fig. 8, a Bit Mask circuit for a Memory Cell of the second preferred embodiment is shown, with an OR logical circuit connected to a Data Bus and a Priority Mask Circuit, also connected to the said Data Bus. In this embodiment an enabling signal is produced if the device is put in Call Out and Read mode and the Comparison Result Storage bit is set. The enabling signal is then applied to the Priority Mask.

In Figs. 7, 8 and 9, the cell Address is represented by N. N can then be written in the form:

$$N = \sum_{k=0}^{K} 2^{[u(N,k)]}$$

Where  $u(N,k)$  represents the set digits of the binary presentation of N and may take the values 0 to  $W - 1$  ( $W$  being the number of bits used to represent the cell address);  $k+1$  is the number of set bits for the specific address value N and  $B[U]$  represents the value (0 or 1) of bit  $u$  of the Data Bus.

The operation of the Priority Mask Circuit when enabled is as follows:

As shown in both Figs. 7 and 8, all  $P[M,u(N,k)]$  lines, from all memory cells (M) having bit  $u(N,k)$  set, are input to the said OR logical circuit, and the output of that circuit is set on the Data Bus as bit  $u(N,k)$ . M is a generic that represents the addresses of all the cells of the device having bit  $u(N,k)$  set.

WO 02/01570

PCT/IL00/00327

At the beginning of a Call Out Cycle, the Data Bus lines  $B[0]$  to  $B[w-1]$  are in an inactive (Logical 0) initial state. For example, if we use negative logic, all lines are "Pulled Up" by a resistor to the plus system power supply. In a first step the priority mask senses all these lines as inactive, and outputs the  $P[N,u(N,k)]$ . In that first step, many other cells may also set the Data Bus line by means of the OR circuit. This new state of the Data Bus will then be sensed by each of the cell Priority Mask Circuits respectively and some of the  $P[N,u(N,k)]$  lines will be deactivated, according to the rules of the priority mask. Finally, bits  $P[N,u(N,k)]$  that are not set in the address of the highest cell storing the searched data will be reset, and the Data Bus will be set to that highest cell address.

As a result of the above process, the "Priority Mask" will reset all  $P[N,u(N,k)]$  lines to zero logical state if one of the following conditions is not satisfied:

- \_ The Cell Address is higher or equal to the Origin address.

- \_ The Data Stored in Cell is equal to data presented on the Data Bus.

- \_ The device is not in the "Call Out" mode.

This process is asynchronous; the time needed for the lines to stabilize to their steady value is of the same order as the rising time of the electronic components of the circuit. As a result, the time required to search one data is of the same order as a normal read or write cycle.

Referring now to Fig. 9, the "Priority Mask" circuit is shown in detail. The "Priority Mask" circuit of Fig. 9 outputs bit  $P[N,u(N,k)]$  if the following conditions are satisfied:

For the highest bit set:  $u(N,K)$

- a)\_if the "E" signal is active.

- b)\_AND if all bits of the Data Bus higher than  $u(N,K)$  are not set.

If there is no higher bit, i.e. if the highest bit is bit  $W-1$  (where  $W$  designates the number of bits used to represent the cell address), then this bit is directly set by the "E" signal.

WO 02/01570

PCT/IL00/00327

For other bits:  $u(N,k)$ ,  $k < K$

- a) the higher bit  $u(N,k+1)$  is set

- b) AND all bits of the internal bus  $B[u(N,k)]$  between present bit  $u(N,k)$  and higher bit  $u(N,k+1)$  are not set.

This ensures that if another cell with a higher address has output its address on the Data bus, at bits that are not set in the present cell, then bits  $k$  and lower of the present cell address are not output. Finally only bits that are set in the highest matching memory will be output.

It will be understood that the above is described for a downward search and where the system is defined to conduct an upward search it is the lowest matching memory that will be output on the Data Bus.

The inventive memory system and method have the advantage of being compatible with commonly used computer devices and therefore applicable in a wide variety of electronic systems such as computer systems, communication systems, and many other systems wherein it may be used together with or in replacement of standard memory devices of different types.

**Claims:**

1. A memory system comprising an address bus and a data bus and a two dimensional array of memory cells arranged in rows and columns such that each memory cell can be selected by at least one row and one column, each of the said memory cells being connected to a plurality of data bus lines and each of the said memory cells comprising a comparator circuit, a masking circuit and a plurality of memory bits whereby the said memory system may be operated in a read and write mode or it may be operated in a search mode wherein:

- (a) each of the memory cells performs a comparing function whereby data set on the data bus are compared with the data stored in the cell and the result is stored in a memory bit that is set when the result is a match;

- (b) each of the said memory cells performs a function that limits the search to cells having a predefined characteristic by selectively sending an enabling signal to either the said masking circuit or the said comparator circuit when the said characteristic is verified;

- (c) the said masking circuit performs a masking function that results in the cell that is highest in a preset direction and verifies the said predefined common characteristic being selected for its address to be put on the data bus;

- (d) the said process may be repeated until several matching cells have put their addresses on the said data bus.

WO 02/01570

PCT/IL00/00327

2. A memory system according to claim 1 hereinabove wherein each of the memory cells further comprises a range circuit, the said predefined characteristic is a predefined relationship with a preset origin address and in the said search mode:

- (a) The said range circuit performs a range function that verifies the said predefined relationship with the said preset origin address and selectively sends the said enabling signal to the said masking circuit;

- (b) The said masking circuit performs a masking function that results in the cell that is highest in a preset direction and verifies the said predefined relationship with the origin address being selected for its address to be put on the data bus;

- (c) the said process may be repeated with a different origin address until several matching cells have put their addresses on the said data bus.

3. A memory system according to claim 2 wherein the said memory system also comprises a designated register and each of the said memory cells is further connected to an origin line and in the said search mode:

- (a) In a first step the said origin address value is put on the address bus and stored in the said designated register and the data to be searched is conveyed to the memory cells by the said data bus lines for performing the said comparing function;

- (b) in a second step:

- i. The said range function is performed by a designated range circuit that directly performs the comparison between the origin address received through the origin lines and the cell address to verify the said predefined relationship;

- ii. in the event that the information stored in the said memory bit is a match condition and the range circuit verifies the said predefined relationship, the said masking circuit is enabled and performs a logic function comparing the cell address to the addresses of other matching cells with the result that the address that is highest in a preset direction and verifying a predefined relationship with a preset origin address is put on the data bus;

- (c) the said process may be repeated with a different origin address until several matching cells have put their addresses on the said data bus.

4. A memory system according to claim 2 wherein the said memory cells are not connected to any origin lines and each memory cell receives as input two adjacent rows and one column and in the said search mode:

- a. in a first step:

- i. the data to be searched are conveyed to the memory cells by the said data bus lines for performing the said comparing function and an origin address value  $r_0; c_0$  is put on the address bus;

- ii. the said origin address value is encoded such that all rows equal to or lower than the origin address row ( $r \leq r_0$ ) or all rows lower than the origin address row ( $r < r_0$ ) in a predefined direction and all columns equal to or lower than the origin address column ( $c \leq c_0$ ) in a second predefined direction or all columns lower than the origin address column  $c < c_0$  are selected;

WO 02/01570

PCT/IL00/00327

- b. in a second step:

- i. the said range circuit within each of the matching cells performs a range function to verify a predefined relationship of the cell address with the said previously set rows and columns such that a cell r;c will be enabled only where the row that is adjacent to the cell row and exceeding the cell value by one order in a predefined direction is selected or if both row r and column c are selected or the column that is adjacent to the cell column and exceeding the cell value by one order in a second predefined direction is selected;

- ii. the address of the enabled cell is set on the said data bus;

- c. the said process may be repeated with a different origin address until several matching cells are found.

- 5. A memory system according to any of the preceding claims wherein the said memory bit storing the comparison results remains unchanged after it was set in a first cycle and in a second cycle a logical combination of the said memory bit with the comparator enabling signal will disable the comparator for that cycle, whereby any address that was already searched may be disabled for subsequent searches without the need for a range function.

- 6. A memory system according to claim 1 hereinabove wherein the said memory bit storing the comparison results is provided with standard reading or writing means, whereby the search may be limited to cells having a predefined characteristic by writing new data to a particular cell to reset the said memory bit of the said cell such that the said memory bit sends an enabling signal to the said masking circuit.

- 7. A memory system according to any of the preceding claims wherein a designated line is used to reset a multiplicity of the said memory bits that store the comparison results whereby the search will include all the cells connected to the said designated line.

WO 02/01570

PCT/IL00/00327

8. A memory cell within a two dimensional array of memory cells, the said cell receiving a Data Bus Line, an Origin Bus line, one or more Control lines, a Row and a Column and comprising a memory circuit with a Comparator, a comparison result storage bit, a Range Circuit and a Priority Mask circuit, wherein the data to be searched is conveyed to the memory cells by the said Data Bus and compared with the cell data by the said Comparator, the result is stored in the said Comparison storage bit and the said Range Circuit checks a predefined relationship between the cell address and an Origin Address whereby in the event that the information stored in the said Memory Bit is a match condition and the said Range Circuit verifies the said predefined relationship, the said Masking Circuit is enabled to perform a logic function comparing the cell address to addresses of other matching cells with the result that the address of the cell that is highest in a preset direction and verifying a predefined relationship with a preset origin address is put on the said Data Bus.

9. A memory cell within a two dimensional array of memory cells, the said cell receiving a Data Bus Line, one or more Control lines, a Row and two Columns and comprising a memory circuit with a Comparator, a comparison result storage bit, a Range Circuit and a Priority Mask circuit, wherein the data to be searched is conveyed to the memory cells by the said Data Bus and compared with the cell data by the said Comparator, the result is stored in the said Comparison storage bit and the said Range Circuit checks a predefined relationship between the cell address and an Origin Address that is conveyed to the cell by the states of the said Row and Columns and the said Control lines whereby in the event that the information stored in the said Memory Bit is a match condition and the said Range Circuit verifies the said predefined relationship, the said Masking Circuit is enabled to perform a logic function comparing the cell address to addresses of other matching cells with the result that the address that is highest in a preset direction and verifying a predefined relationship with a preset origin address is put on the said Data Bus.

WO 02/01570

PCT/IL00/00327

10. A memory cell according to Claim 5 wherein the said memory cell is connected to a single Column and two Rows.

11. A memory cell according to any of claims 7-9 that does not have a range circuit and that may be selectively disabled by data written to the Comparison Storage bit.

12. A memory cell according to claim 10 that is disabled for a second cycle after it has been searched during a first cycle by a logical combination of the said Comparison Storage bit and the comparator enabling signal.