(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6869039号

(P6869039)

(45) 発行日 令和3年5月12日(2021.5.12)

(24) 登録日 令和3年4月15日(2021.4.15)

(51) Int.Cl.

F 1

**G06F 3/0481 (2013.01)**

**G06F 3/0488 (2013.01)**

**G09F 9/00 (2006.01)**

**G09F 9/46 (2006.01)**

**G09F 9/30 (2006.01)**

GO6F 3/0481 170

GO6F 3/0488

GO9F 9/00 366A

GO9F 9/46 Z

GO9F 9/30 365

請求項の数 9 (全 75 頁) 最終頁に続く

(21) 出願番号

特願2017-14083 (P2017-14083)

(22) 出願日

平成29年1月30日(2017.1.30)

(65) 公開番号

特開2017-138980 (P2017-138980A)

(43) 公開日

平成29年8月10日(2017.8.10)

審査請求日 令和2年1月28日(2020.1.28)

(31) 優先権主張番号 特願2016-18553 (P2016-18553)

(32) 優先日 平成28年2月3日(2016.2.3)

(33) 優先権主張国・地域又は機関

日本国(JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 秋元 健吾

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 茂森 勇

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 田川 泰宏

最終頁に続く

(54) 【発明の名称】情報処理装置

(57) 【特許請求の範囲】

【請求項 1】

入出力装置と、演算装置と、を有し、

前記入出力装置は、入力位置座標情報および検知情報を供給する機能を有し、

前記入出力装置は、画像情報および制御情報を供給される機能を備え、

前記演算装置は、前記入力位置座標情報および前記検知情報を供給される機能を備え、

前記演算装置は、前記画像情報および前記制御情報を供給する機能を備え、

前記入出力装置は、表示部、入力部および検知部を備え、

前記入力部は、前記入力位置座標情報を供給する機能を備え、

前記検知部は、前記検知情報を供給する機能を備え、

前記表示部は、前記画像情報を表示する機能を備え、

前記表示部は、選択回路、第1の駆動回路、第2の駆動回路および表示パネルを備え、

前記演算装置は、前記画像情報を生成する機能を備え、

前記演算装置は、前記入力位置座標情報、前記検知情報および前記画像情報に基づいて、前記制御情報を生成する機能を備え、

前記制御情報は、第1のステータスの制御情報、第2のステータスの制御情報、または第3のステータスの制御情報を含み、

前記選択回路は、

前記第1のステータスの制御情報が供給された場合に、前記画像情報を前記第1の駆動回路に供給し、かつ、背景情報を前記第2の駆動回路に供給する機能を備え、

10

20

前記選択回路は、

前記第2のステータスの制御情報が供給された場合に、背景情報を前記第1の駆動回路に供給し、かつ、前記画像情報を前記第2の駆動回路に供給する機能を備え、

前記選択回路は、

前記第3のステータスの制御情報が供給された場合に、前記画像情報を前記第1の駆動回路と前記第2の駆動回路とに供給する機能を備える情報処理装置。

**【請求項2】**

請求項1において、

前記表示パネルは、第1の信号線と、第2の信号線と、一群の画素と、を備え、

前記一群の画素は列方向に配設され、

10

前記第1の信号線は前記列方向に配設される前記一群の画素と電気的に接続され、

前記第1の信号線は前記第1の駆動回路と電気的に接続され、

前記第2の信号線は前記列方向に配設される前記一群の画素と電気的に接続され、

前記第2の信号線は前記第2の駆動回路と電気的に接続される情報処理装置。

**【請求項3】**

請求項2において、

前記画素は、第1の表示素子および第2の表示素子を備え、

前記第1の表示素子は、反射型の表示素子を備え、

前記第1の表示素子は、前記第1の信号線と電気的に接続され、

前記第2の表示素子は、発光素子を備え、

20

前記第2の表示素子は、前記第2の信号線と電気的に接続される情報処理装置。

**【請求項4】**

請求項3において、

前記第1の表示素子は、表示をする方向に外光を反射する反射膜および反射する強度を制御する機能を備え、

前記反射膜は開口部を備え、

前記第2の表示素子は、前記開口部と重なる領域、前記開口部に向けて光を射出する機能、および発光性の有機化合物を含む層を備える情報処理装置。

**【請求項5】**

請求項1乃至請求項4のいずれか一において、

30

前記演算装置は、アイコンが選択されたとき、前記アイコンの表示される領域の座標に対して前記第3のステータスの制御情報を供給する機能を備える情報処理装置。

**【請求項6】**

請求項5において、

前記演算装置は、前記アイコンが選択された履歴に基づいて、特定のアイコンを決定する機能を備え、前記特定のアイコンの表示される領域の座標に対して前記第3のステータスの制御情報を供給する機能を備える情報処理装置。

**【請求項7】**

請求項1乃至請求項4のいずれか一において、

前記演算装置は、

40

最後の前記入力部からの入力から一定時間経過する前は、

ポインタ表示領域に対して、前記第3のステータスの制御情報を供給する機能を備え、

最後の前記入力部からの入力から前記一定時間経過した後は、

前記ポインタ表示領域に対して、前記第1のステータスの制御情報または前記第2のステータスの制御情報を供給する機能を備える情報処理装置。

**【請求項8】**

請求項1乃至請求項7のいずれか一において、

前記検知部は、照度センサを備え、

前記照度センサは、使用される環境の照度情報を含む前記検知情報を供給する機能を備える情報処理装置。

50

**【請求項 9】**

請求項 1 乃至 請求項 8 のいずれか一において、

前記入力部が、キーボード、ハードウェアボタン、ポインティングデバイス、タッチセンサ、照度センサ、撮像装置、音声入力装置、視点入力装置、姿勢検出装置、のうち一以上を含む情報処理装置。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明の一態様は、情報処理装置または半導体装置に関する。

**【0002】**

なお、本発明の一態様は、上記の技術分野に限定されない。本明細書等で開示する発明の一態様の技術分野は、物、方法、または、製造方法に関するものである。または、本発明の一態様は、プロセス、マシン、マニュファクチャ、または、組成物（コンポジション・オブ・マター）に関するものである。そのため、より具体的に本明細書で開示する本発明の一態様の技術分野としては、半導体装置、表示装置、発光装置、蓄電装置、記憶装置、それらの駆動方法、または、それらの製造方法、を一例として挙げることができる。

10

**【背景技術】****【0003】**

基板の同一面側に集光手段と画素電極を設け、集光手段の光軸上に画素電極の可視光を透過する領域を重ねて設ける構成を有する液晶表示装置や、集光方向Xと非集光方向Yを有する異方性の集光手段を用い、非集光方向Yと画素電極の可視光を透過する領域の長軸方向を一致して設ける構成を有する液晶表示装置が、知られている（特許文献1）。

20

**【先行技術文献】****【特許文献】****【0004】****【特許文献1】特開2011-191750号公報****【発明の概要】****【発明が解決しようとする課題】****【0005】**

本発明の一態様は、利便性に優れた新規な情報処理装置を提供することを課題の一とする。または、新規な情報処理装置または新規な半導体装置を提供することを課題の一とする。

30

**【0006】**

なお、これらの課題の記載は、他の課題の存在を妨げるものではない。なお、本発明の一態様は、これらの課題の全てを解決する必要はないものとする。なお、これら以外の課題は、明細書、図面、請求項などの記載から、自ずと明らかとなるものであり、明細書、図面、請求項などの記載から、これら以外の課題を抽出することが可能である。

**【課題を解決するための手段】****【0007】**

本発明の一態様は、入出力装置と、演算装置と、を有する情報処理装置である。

40

**【0008】**

入出力装置は、入力位置座標情報を供給する機能を備える。

**【0009】**

演算装置は、入力位置座標情報を供給される機能を備える。また、演算装置は、画像情報および制御情報を供給する機能を備える。

**【0010】**

入出力装置は、表示部、入力部を備える。

**【0011】**

入力部は、入力位置座標情報を供給する機能を備える。入力位置座標情報は、一つの表示部の座標の情報である。

50

## 【0012】

表示部は、画像情報を表示する機能を備える。

## 【0013】

表示部は、選択回路、第1の駆動回路、第2の駆動回路および表示パネルを備える。

## 【0014】

演算装置は、記憶部を有し、表示部にて個別のアイコンの表示される座標の情報を含むアイコン座標情報、アイコンが選択された履歴、を記憶する機能を備える。尚、本明細書中でいうアイコンとは、プログラムの実行等のコマンドと関連付けられた図形または画像である。例えば、情報処理装置の使用者は、ポインタ等を用いてアイコンを選択することにより、所定のコマンドを簡便に実行させることができる。アイコンは表示画面上でドラッグないし移動可能、あるいは表示画面上で配置可能、なものであっても良い。またアイコンの表示は広がりを持つ。すなわち各個別のアイコン座標情報はこの広がり全域を含む。

10

## 【0015】

演算装置は、入力位置座標情報とアイコン座標情報との重なりがあるかを判断する機能を備える。入力位置座標情報とアイコン座標情報との重なりがある場合、本明細書中ではアイコンが選択されたといい、このアイコンを選択されたアイコンという。

## 【0016】

また演算装置は、画像情報を生成する機能を備える。

## 【0017】

また、演算装置は、制御情報を生成する機能を備える。演算装置は、表示部の座標ごとに異なる情報を制御情報に用いることができる。また制御情報は、第1のステータスの制御情報、第2のステータスの制御情報、または第3のステータスの制御情報を含む。

20

## 【0018】

演算装置は、特定の入力位置座標情報が供給されたとき、第3のステータスの制御情報を生成する。

## 【0019】

選択回路は、演算装置から第1のステータスの制御情報または第2のステータスの制御情報が供給された場合に、画像情報を第1の駆動回路または第2の駆動回路に供給する機能を備える。このときいずれかに一方に画像情報を供給し、いずれか一方には背景情報を供給する。背景情報とは、黒色表示の情報を指す。

30

## 【0020】

選択回路は、演算装置から第3のステータスの制御情報が供給された場合に、画像情報を第1の駆動回路と、第2の駆動回路と、の双方に供給する機能を備える。

## 【0021】

ここで、演算装置からある画像情報が生成し、表示部で表示されるとき、第3のステータスの制御情報が供給された場合の表示部の表示の明るさは、第1のステータスの制御情報あるいは第2のステータスの制御情報が供給された場合に比べて大きい。このように、入出力装置中から得られた入力位置座標情報により、選択された表示は表示の明るさが大きくなり強調される、利便性に優れた新規な情報処理装置を提供することができる。

40

## 【0022】

また本発明の一態様の情報処理装置は、演算装置に、入出力装置中から得られた入力位置座標情報をもとにアイコンが選択された回数を蓄積する機能を備える。ある閾値を設定し、選択された回数すなわち選択された頻度が閾値より高いアイコンには、第3のステータスの制御情報を供給する。これにより選択された頻度の高いアイコンを、視認性において強調する、上記の情報処理装置である。

## 【0023】

また、本発明の一態様は、入出力装置に、検知情報を供給する機能を有する検知部を備える。演算装置は、検知情報を供給される機能を備える。検知部が照度センサを備える上記の情報処理装置である。

## 【0024】

50

照度センサは、使用される環境の照度情報を含む検知情報を供給する機能を備える。

【0025】

上記本発明の一態様の情報処理装置は、検知情報および画像情報に基づいてステータスを決定し、決定されたステータスの制御情報を供給する機能を備える演算装置を含んで構成される。すなわち演算装置は、供給された検知情報に基づいて、第1の駆動回路に画像情報を供給したときの表示と、第2の駆動回路に画像情報を供給したときの表示と、の表示の明るさの大小を判断する機能を備える。これにより、照度などの検知情報および画像情報に基づいて反射型の表示素子または発光素子を選択し、選択された反射型の表示素子または発光素子を用いて、画像情報を表示することができる。その結果、利便性に優れた新規な情報処理装置を提供することができる。

10

【0026】

本明細書に添付した図面では、構成要素を機能ごとに分類し、互いに独立したブロックとしてブロック図を示しているが、実際の構成要素は機能ごとに完全に切り分けることが難しく、一つの構成要素が複数の機能に係わることもあり得る。

【0027】

本明細書においてトランジスタが有するソースとドレインは、トランジスタの極性及び各端子に与えられる電位の高低によって、その呼び方が入れ替わる。一般的に、nチャネル型トランジスタでは、低い電位が与えられる端子がソースと呼ばれ、高い電位が与えられる端子がドレインと呼ばれる。また、pチャネル型トランジスタでは、低い電位が与えられる端子がドレインと呼ばれ、高い電位が与えられる端子がソースと呼ばれる。本明細書では、便宜上、ソースとドレインとが固定されているものと仮定して、トランジスタの接続関係を説明する場合があるが、実際には上記電位の関係に従ってソースとドレインの呼び方が入れ替わる。

20

【0028】

本明細書においてトランジスタのソースとは、活性層として機能する半導体膜の一部であるソース領域、或いは上記半導体膜に接続されたソース電極を意味する。同様に、トランジスタのドレインとは、上記半導体膜の一部であるドレイン領域、或いは上記半導体膜に接続されたドレイン電極を意味する。また、ゲートはゲート電極を意味する。

【0029】

本明細書においてトランジスタが直列に接続されている状態とは、例えば、第1のトランジスタのソースまたはドレインの一方のみが、第2のトランジスタのソースまたはドレインの一方のみに接続されている状態を意味する。また、トランジスタが並列に接続されている状態とは、第1のトランジスタのソースまたはドレインの一方が第2のトランジスタのソースまたはドレインの一方に接続され、第1のトランジスタのソースまたはドレインの他方が第2のトランジスタのソースまたはドレインの他方に接続されている状態を意味する。

30

【0030】

本明細書において接続とは、電気的な接続を意味しており、電流、電圧または電位が、供給可能、或いは伝送可能な状態に相当する。従って、接続している状態とは、直接接続している状態を必ずしも指すわけではなく、電流、電圧または電位が、供給可能、或いは伝送可能であるように、配線、抵抗、ダイオード、トランジスタなどの回路素子を介して間接的に接続している状態も、その範疇に含む。

40

【0031】

本明細書において回路図上は独立している構成要素どうしが接続されている場合であっても、実際には、例えば配線の一部が電極として機能する場合など、一の導電膜が、複数の構成要素の機能を併せ持っている場合もある。本明細書において接続とは、このような、一の導電膜が、複数の構成要素の機能を併せ持っている場合も、その範疇に含める。

【0032】

また、本明細書中において、トランジスタの第1の電極または第2の電極の一方がソース電極を、他方がドレイン電極を指す。

50

**【0033】**

本発明の一態様は、表示パネルは、第1の信号線と、第2の信号線と、一群の画素と、を備え、前記一群の画素は列方向に配設され、前記第1の信号線は前記列方向に配設される前記一群の画素と電気的に接続され、前記第1の信号線は前記第1の駆動回路と電気的に接続され、前記第2の信号線は前記列方向に配設される前記一群の画素と電気的に接続され、前記第2の信号線は前記第2の駆動回路と電気的に接続される情報処理装置である。

**【0034】**

本発明の一態様は、前記画素は、第1の表示素子および第2の表示素子を備え、前記第1の表示素子は、反射型の表示素子を備え、前記第1の表示素子は、前記第1の信号線と電気的に接続され、前記第2の表示素子は、発光素子を備え、前記第2の表示素子は、前記第2の信号線と電気的に接続される情報処理装置である。

10

**【0035】**

本発明の一態様は、前記第1の表示素子は、表示をする方向に外光を反射する反射膜および反射する強度を制御する機能を備え、前記反射膜は開口部を備え、前記第2の表示素子は、前記開口部と重なる領域、前記開口部に向けて光を射出する機能、および発光性の有機化合物を含む層を備える、情報処理装置である。

**【0036】**

本発明の一態様は、前記演算装置は、アイコンが選択されたとき、前記アイコンの表示される領域の座標に対応して前記第3のステータスの制御情報を、入出力装置に供給する機能を備える、情報処理装置である。

20

**【0037】**

本発明の一態様は、前記演算装置は、前記アイコンが選択された履歴に基づいて、特定のアイコンを決定する機能を備え、前記特定のアイコンの表示される領域の座標に対して前記第3のステータスの制御情報を供給する機能を備える、情報処理装置である。

**【0038】**

本発明の一態様は、前記演算装置は、最後の入力部からの入力から一定時間経過する前は、ポインタ表示領域に対して、前記第3のステータスの制御情報を供給する機能を備え、最後の入力部からの入力から一定時間経過した後は、ポインタ表示領域に対して、前記第1のステータスの制御情報または前記第2のステータスの制御情報を供給する機能を備える、情報処理装置である。

30

**【0039】**

本発明の一態様は、前記検知部は、照度センサを備え、前記照度センサは、使用される環境の照度情報を含む前記検知情報を供給する機能を備える、情報処理装置である。

**【0040】**

本発明の一態様は、前記入力部が、キーボード、ハードウェアボタン、ポインティングデバイス、タッチセンサ、照度センサ、撮像装置、音声入力装置、視点入力装置、姿勢検出装置、のうち一以上を含む、情報処理装置である。

**【発明の効果】****【0041】**

本発明の一態様によれば、利便性に優れた新規な情報処理装置を提供できる。または、新規な情報処理装置または新規な半導体装置を提供できる。

40

**【0042】**

なお、これらの効果の記載は、他の効果の存在を妨げるものではない。なお、本発明の一態様は、必ずしも、これらの効果の全てを有する必要はない。なお、これら以外の効果は、明細書、図面、請求項などの記載から、自ずと明らかとなるものであり、明細書、図面、請求項などの記載から、これら以外の効果を抽出することが可能である。

**【図面の簡単な説明】****【0043】**

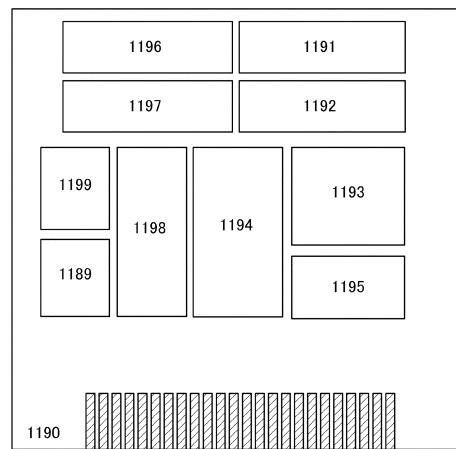

【図1】実施の形態に係る情報処理装置の構成を説明する図。

【図2】実施の形態に係る情報処理装置に用いることができるプログラムを説明するフロ

50

ーチャート。

【図3】実施の形態に係る情報処理装置を説明する図。

【図4】実施の形態に係る情報処理装置を説明する図。

【図5】実施の形態に係る情報処理装置の画像情報を説明する図。

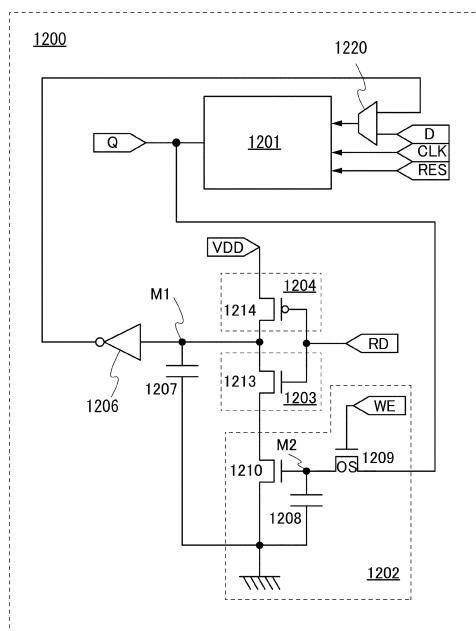

【図6】実施の形態に係る情報処理装置の回路を説明する図。

【図7】実施の形態に係る情報処理装置に用いることができるプログラムを説明するフローチャート。

【図8】実施の形態に係る情報処理装置に用いることができるプログラムを説明するフローチャート。

【図9】実施の形態に係る表示装置に用いることができる表示パネルの構成を説明する下面図。

【図10】実施の形態に係る表示装置に用いることができる表示パネルの画素回路を説明する回路図。

【図11】実施の形態に係る表示装置に用いることができる画素の反射膜の形状を説明する模式図。

【図12】実施の形態に係るトランジスタの構成を説明する図。

【図13】実施の形態に係るトランジスタの構成を説明する図。

【図14】実施の形態に係る入出力装置の構成を説明する図。

【図15】実施の形態に係る半導体装置の構成を説明する断面図および回路図。

【図16】実施の形態に係るCPUの構成を説明するブロック図。

【図17】実施の形態に係る記憶素子の構成を説明する回路図。

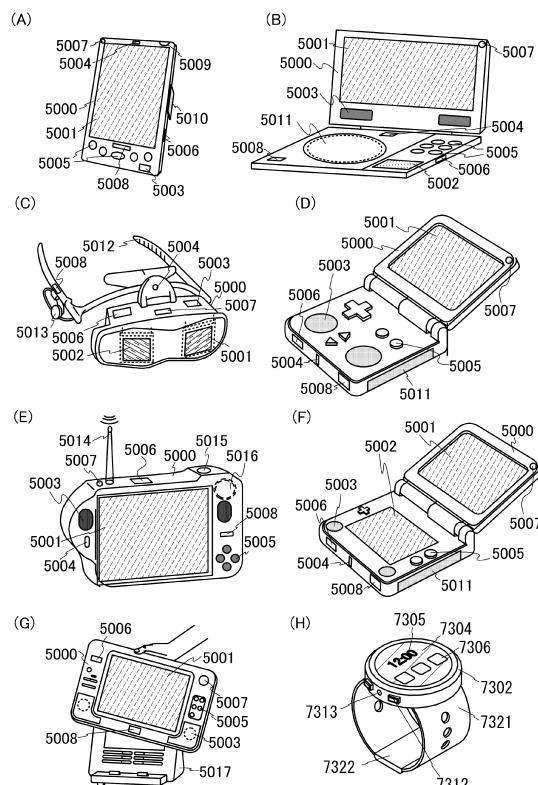

【図18】実施の形態に係る電子機器の構成を説明する図。

【図19】実施の形態に係る表示装置に用いることができる表示パネルの構成を説明する断面図。

【図20】実施の形態に係る表示装置に用いることができる表示パネルの構成を説明する断面図。

【発明を実施するための形態】

【0044】

本発明の一態様の情報処理装置は、入力位置座標情報に基づいて選択された画像情報の一部を第1の駆動回路および第2の駆動回路に供給する。

【0045】

これにより、選択された画像情報の一部が演算装置から供給されたとき、選択された画像は表示の明るさが大きく表示される。その結果、利便性に優れた新規な情報処理装置を提供することができる。

【0046】

実施の形態について、図面を用いて詳細に説明する。但し、本発明は以下の説明に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、以下に説明する発明の構成において、同一部分又は同様な機能を有する部分には同一の符号を異なる図面間で共通して用い、その繰り返しの説明は省略する。

【0047】

(実施の形態1)

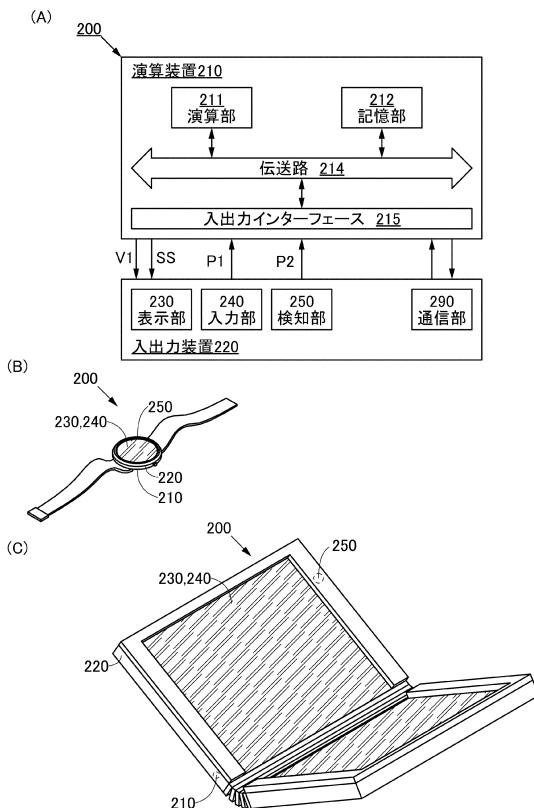

本実施の形態では、本発明の一態様の情報処理装置の構成について、図1乃至図4を参照しながら説明する。

【0048】

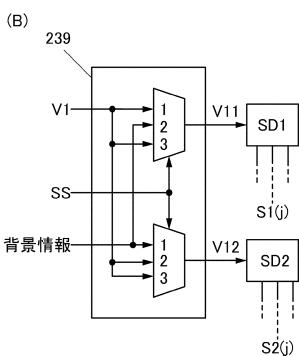

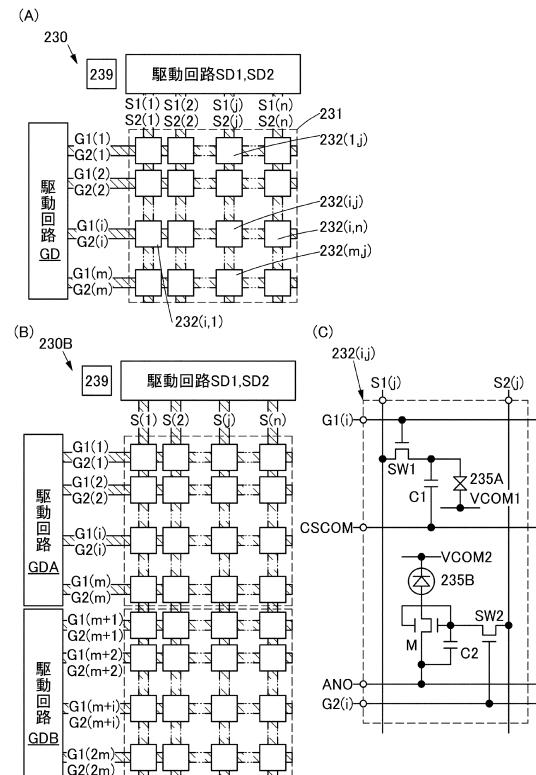

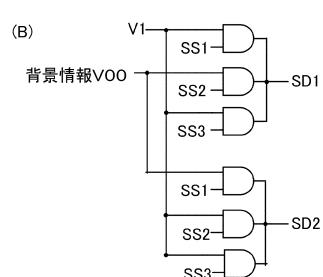

図1は本発明の一態様の情報処理装置の構成を説明する図である。図1(A)は本発明の一態様の情報処理装置に用いることができる表示部230のブロック図であり、図1(B)は図1(A)に示す選択回路239、第1の駆動回路SD1または第2の駆動回路SD2を説明するブロック図である。

10

20

30

40

50

## 【0049】

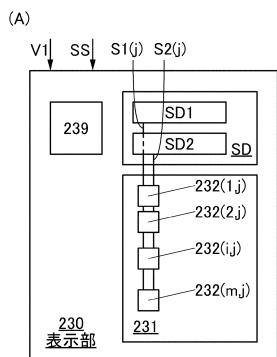

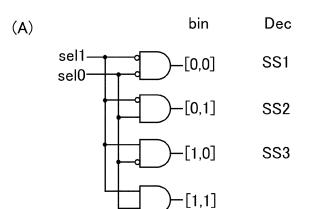

図2は本発明の一態様の情報処理装置に用いることができるプログラムを説明するフローチャートである。

## 【0050】

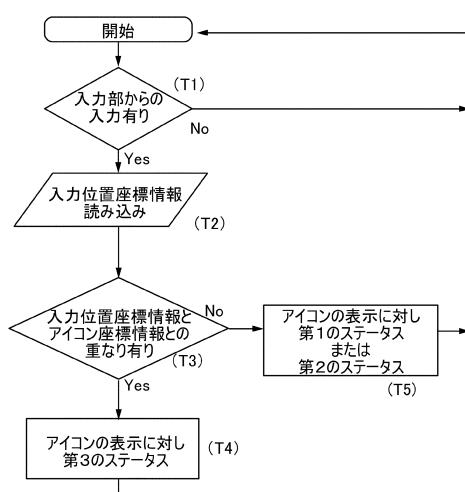

図3(A)は、情報処理装置200の構成を説明するブロック図である。図3(B)および図3(C)は、情報処理装置200の外観の一例を説明する投影図である。

## 【0051】

図4(A)は、表示部230の構成を説明するブロック図である。図4(B)は、表示部230Bの構成を説明するブロック図である。図4(C)は、画素232(i,j)の構成を説明する回路図である。

10

## 【0052】

<情報処理装置の構成例1.>

本実施の形態で説明する情報処理装置200は、入出力装置220と、演算装置210と、を有する(図3(A)参照)。

## 【0053】

入出力装置220は、入力位置座標情報P1および検知情報P2を供給する機能を備える。また、入出力装置220は、画像情報V1および制御情報SSを供給される機能を備える。

## 【0054】

演算装置210は、入力位置座標情報P1および検知情報P2を供給される機能を備える。また、演算装置210は、画像情報V1および制御情報SSを供給する機能を備える。

20

## 【0055】

入出力装置220は、表示部230、入力部240および検知情報部250を備える。

## 【0056】

入力部240は入力位置座標情報P1を供給する機能を備える。

## 【0057】

検知情報部250は検知情報P2を供給する機能を備える。

## 【0058】

表示部230は、画像情報V1を表示する機能を備える。

## 【0059】

また、表示部230は、選択回路239、第1の駆動回路SD1、第2の駆動回路SD2および表示パネルを備える(図1(A)参照)。

30

## 【0060】

演算装置210は、画像情報V1を生成する機能を備える(図3(A)参照)。また、演算装置210は、検知情報P2および画像情報V1に基づいて、制御情報SSを生成する機能を備える。なお、制御情報SSは、第1のステータス、第2のステータスまたは第3のステータスの制御情報を含む。

## 【0061】

選択回路239は、第1のステータスの制御情報SSを供給された場合に、画像情報V1を第1の駆動回路SD1に供給し、背景情報を第2の駆動回路SD2に供給する機能を備える(図1(B)参照)。

40

## 【0062】

同様に、選択回路239は、第2のステータスの制御情報SSを供給された場合に、背景情報を第1の駆動回路SD1に供給し、画像情報V1を第2の駆動回路SD2に供給する機能を備える。

## 【0063】

選択回路239は、第3のステータスの制御情報SSを供給された場合に、画像情報V1を第1の駆動回路SD1と第2の駆動回路SD2に供給する機能を備える。

## 【0064】

また、本実施の形態で説明する情報処理装置200の表示パネルは、第1の信号線S1(

50

$j$  ) と、第 2 の信号線  $S_2(j)$  と、一群の画素  $232(1, j)$  乃至画素  $232(m, j)$  と、を備える(図 1 (A) 参照)。

【0065】

一群の画素  $232(1, j)$  乃至画素  $232(m, j)$  は列方向に配設される。なお、 $i$  は 1 以上  $m$  以下の整数であり、 $j$  は 1 以上  $n$  以下の整数であり、 $m$  および  $n$  は 1 以上の整数である。

【0066】

第 1 の信号線  $S_1(j)$  は列方向に配設される一群の画素  $232(1, j)$  乃至画素  $232(m, j)$  と電気的に接続される。また、第 1 の信号線  $S_1(j)$  は第 1 の駆動回路  $S_D1$  と電気的に接続される。

10

【0067】

第 2 の信号線  $S_2(j)$  は列方向に配設される一群の画素  $232(1, j)$  乃至画素  $232(m, j)$  と電気的に接続される。また、第 2 の信号線  $S_2(j)$  は第 2 の駆動回路  $S_D2$  と電気的に接続される。

【0068】

また、本実施の形態で説明する情報処理装置 200 の画素  $232(i, j)$  は、第 1 の表示素子  $235A$  および第 2 の表示素子  $235B$  を備える(図 4 (C) 参照)。

【0069】

第 1 の表示素子  $235A$  は反射型の表示素子を備え、第 1 の表示素子  $235A$  は、第 1 の信号線  $S_1(j)$  と電気的に接続される。

20

【0070】

第 2 の表示素子  $235B$  は発光素子を備え、第 2 の表示素子  $235B$  は、第 2 の信号線  $S_2(j)$  と電気的に接続される。

【0071】

本実施の形態で説明する情報処理装置は、反射型の表示素子及び発光素子を備える画素を有する表示パネルを含んで構成される。これにより、検知情報に基づいて反射型の表示素子または発光素子を選択し、選択された反射型の表示素子または発光素子を用いて、画像情報を表示することができる。その結果、利便性に優れた新規な情報処理装置を提供することができる。

【0072】

30

また、本実施の形態で説明する情報処理装置 200 の演算装置 210 は、入力位置座標情報  $P_1$  が供給されないとき、かつ検知情報  $P_2$  があらかじめ設定した閾値以上である場合に、第 1 のステータスの制御情報  $SS$  を供給する機能を備える。

【0073】

この閾値には、一例には、反射型の表示素子のみと、発光素子のみとを、片方ずつ全白で最大の明るさで表示させ、検知情報  $P_2$  を変化させたときに、互いの表示の明るさが同等となる状態の検知情報  $P_2$  の値とすることができる。あるいは低消費電力化の目的で発光素子の表示を控えるため、反射型の表示素子のみの表示の明るさが、発光素子のみの表示の明るさの 1.5 倍としても良い。

【0074】

40

また、演算装置 210 は、入力位置座標情報  $P_1$  が供給されないとき、かつ検知情報  $P_2$  があらかじめ設定した閾値未満である場合に、第 2 のステータスの制御情報  $SS$  を供給する。

【0075】

また、本実施の形態で説明する情報処理装置 200 の検知部 250 は、照度センサを備え、検知情報  $P_2$  は、情報処理装置 200 が使用される環境の照度情報を含む(図 3 (A) 参照)。

【0076】

本実施の形態で説明する情報処理装置は、検知情報および画像情報に基づいてステータスを決定し、決定されたステータスの制御情報を供給する機能を備える演算装置を含んで構

50

成される。これにより、照度などの検知情報および画像情報に基づいて反射型の表示素子または発光素子を選択し、選択された反射型の表示素子または発光素子を用いて、画像情報を表示することができる。その結果、利便性に優れた新規な情報処理装置を提供することができる。

【0077】

また、情報処理装置200は、通信部290を有する。

【0078】

以下に、情報処理装置200を構成する個々の要素について説明する。なお、これらの構成は明確に分離できず、一つの構成が他の構成を兼ねる場合や他の構成の一部を含む場合がある。

10

【0079】

例えば入力部240が重ねられた表示部230は、入力部240であるとともに表示部230でもある。

【0080】

<構成例>

情報処理装置200は、演算装置210、入出力装置220、表示部230、検知部250または入力部240を有する。

【0081】

<演算装置210>

演算装置210は、演算部211および記憶部212を備える。また、伝送路214および入出力インターフェース215を備える。

20

【0082】

<演算部211>

演算部211は、例えばプログラムを実行する機能を備える。

【0083】

<記憶部212>

記憶部212は、例えば演算部211が実行するプログラム、初期情報、設定情報または画像等を記憶する機能を有する。またアイコン座標情報を記憶する機能を有する。

【0084】

具体的には、ハードディスク、フラッシュメモリまたは酸化物半導体を含むトランジスタ等を用いることができる。

30

【0085】

<プログラム>

例えば、入力位置座標情報P1に基づいて制御情報SSのステータスを決定するプログラムを、演算装置210に用いることができる。

【0086】

反射型の表示素子のみ、あるいは発光素子のみ、にて表示をする場合に比べ、両者の素子を同時に用いて表示をする場合、さらに表示の明るさを大きく、表示をすることができる。以下の例では、反射型の表示素子に第1のステータスの制御情報が供給されたときの表示を用いる。また、発光素子に第2のステータスの制御情報が供給されたときの表示を用いる。また反射型の表示素子と、発光素子との両方に、第3のステータスの制御情報が供給されたときの表示を用いる。

40

【0087】

第3のステータスの制御情報が供給されたときの表示は、第1のステータスの制御情報が供給されたときの表示、あるいは第2のステータスの制御情報が供給されたときの表示、に比べて表示の明るさを大きく、視覚的に強調することができる。

【0088】

具体的には、下記のステップを有するプログラムを用いることができる。

【0089】

<第1のステップ>

50

第1のステップにおいて、入力部240から供給される入力の有無を判断する。入力がある場合には第2のステップに進み、入力が無い場合には最初に戻る（図2（T1）参照）。

【0090】

<第2のステップ>

第2のステップにおいて、入力部240から供給される入力位置座標情報P1を読み込む（図2（T2）参照）。

【0091】

<第3のステップ>

第3のステップにおいて、記憶部212から供給されたアイコン座標情報を参照し、入力位置座標情報P1にて与えられた表示部の位置に、アイコン座標情報すなわちアイコンの表示との重なりがあるか判断する。重なりがある場合には第4のステップに進む。重なりが無い場合には、第5のステップに進む。 10

【0092】

<第4のステップ>

第4のステップにおいて、入力位置座標情報P1にて与えられた表示部の位置において、第3のステータスの制御情報SSを供給する（図2（T4）参照）。

【0093】

<第5のステップ>

第5のステップにおいて、入力位置座標情報P1にて与えられた表示部の位置において、第1のステータスまたは第2のステータスの制御情報SSを供給する（図2（T5）参照）。 20

以下第1のステータスの制御情報SSを供給する例を示す。

【0094】

選択されていないアイコンを表示する場合、第3のステップから最初に戻る過程で、第1のステータスの制御情報SSに基づいて、選択回路239は、画像情報V1を第1の駆動回路SD1に供給し、背景情報を第2の駆動回路SD2に供給する（図1（B）参照）。選択されたアイコンを表示する場合、第4のステップと第5のステップとを通して、第3のステータスの制御情報SSに基づいて、選択回路239は、画像情報V1を第1の駆動回路SD1および第2の駆動回路SD2に供給する。ここで最初に戻る。 30

【0095】

上記の例では、反射型の表示素子および発光素子を用いる例であるが、各表示素子画素面積、輝度、外光等の環境、により、表示の明るさの大小が逆転する場合がある。そのため反射型の表示素子および発光素子の、ステータスの割り当てを適宜変更する機能を備えても良い。

【0096】

<入出力インターフェース215、伝送路214>

入出力インターフェース215は端子または配線を備え、情報を供給し、供給される機能を備える。例えば、伝送路214と電気的に接続することができる。また、入出力装置220と電気的に接続することができる。 40

【0097】

伝送路214は配線を備え、情報を供給し、供給される機能を備える。例えば、入出力インターフェース215と電気的に接続することができる。また、演算部211、記憶部212または入出力インターフェース215と電気的に接続することができる。

【0098】

<入出力装置220>

入出力装置220は、表示部230、入力部240、検知部250または通信部290を備える。

【0099】

例えば、表示部230と、表示部230と重なる領域を備える入力部240と、を備える 50

。タッチパネル等を入出力装置 220 に用いることができる。具体的には、実施の形態 7 で説明するタッチパネルを入出力装置 220 に用いることができる。

【0100】

<表示部 230>

例えば表示パネル、選択回路 239、駆動回路 SD1 または駆動回路 SD2 を表示部 230 に用いることができる(図 1 (A) および図 4 参照)。

【0101】

表示領域 231 は、行方向に配設される複数の画素 232 (i, 1) 乃至 232 (i, n) と、列方向に配設される複数の画素 232 (1, j) 乃至 232 (m, j) と、複数の画素 232 (i, 1) 乃至 232 (i, n) と電気的に接続される走査線 G1 (i) および走査線 G2 (i) と、複数の画素 232 (1, j) 乃至 232 (m, j) と電気的に接続される信号線 S1 (j) および信号線 S2 (j) と、を備える。なお、i は 1 以上 m 以下の整数であり、j は 1 以上 n 以下の整数であり、m および n は 1 以上の整数である。

【0102】

なお、画素 232 (i, j) は、走査線 G1 (i)、走査線 G2 (i)、信号線 S1 (j) 信号線 S2 (j)、配線 ANO、配線 CS COM、配線 V COM1 および配線 V COM2 と電気的に接続される(図 4 (C) 参照)。

【0103】

また、表示部は、複数の駆動回路を有することができる。例えば、表示部 230B は、駆動回路 GDA および駆動回路 GDB を有することができる(図 4 (B) 参照)。

【0104】

<駆動回路 GD>

駆動回路 GD は、選択信号を供給する機能を有する。

【0105】

一例を挙げれば、制御情報に基づいて、30 Hz 以上、好ましくは 60 Hz 以上の頻度で一の走査線に選択信号を供給する機能を備える。

【0106】

<表示パネル>

例えば、画像情報 V1 を表示する機能を備える表示領域 231 を表示パネルに用いることができる。また、一群の画素 232 (1, j) 乃至 画素 232 (m, j) を表示領域 231 に用いることができる(図 1 (A) 参照)。

【0107】

また、第 1 の信号線 S1 (j) および第 2 の信号線 S2 (j) を表示パネルに用いることができる。

【0108】

具体的には、実施の形態 4 で説明する表示パネルを表示部 230 に用いることができる。

【0109】

<選択回路 239>

例えば、第 1 のマルチプレクサと第 2 のマルチプレクサを選択回路 239 に用いることができる(図 1 (B) 参照)。

【0110】

第 1 のマルチプレクサは、画像情報 V1 が供給される第 1 の入力部と、背景情報が供給される第 2 の入力部と、画像情報 V1 が供給される第 3 の入力部と、を備え、制御情報 SS を供給される。第 1 のマルチプレクサは第 1 のステータスの制御情報 SS が供給された場合に、画像情報 V1 を出力し、第 2 のステータスの制御情報 SS が供給された場合に、背景情報 V00 を出力し、第 3 のステータスの制御情報 SS が供給された場合に、画像情報 V1 を出力する。なお、第 1 のマルチプレクサが出力する情報を情報 V11 とする。

【0111】

第 2 のマルチプレクサは、背景情報が供給される第 1 の入力部と、画像情報 V1 が供給される第 2 の入力部と第 3 の入力部、を備え、制御情報 SS を供給される。第 2 のマルチブ

10

20

30

40

50

レクサは、第1のステータスの制御情報SSが供給された場合に、背景情報V00を出力し、第2のステータスの制御情報SSが供給された場合に、画像情報V1を出力し、第3のステータスの制御情報SSが供給された場合に、画像情報V1を出力する。なお、第2のマルチプレクサが出力する情報を情報V12とする。

【0112】

画像情報V1は表示領域231の全座標分の信号からなる。各座標における信号を逐次、選択回路239に送信することで、表示領域231の全座標の信号を選択回路239に送っている。画像情報V1のうち、ある座標の信号が送信されるタイミングにて、その座標に対する制御情報SSが送られると、画像情報V1が第1の駆動回路SD1、または第2の駆動回路SD2、または第1の駆動回路SD1と第2の駆動回路SD2、へのいずれかに供給されるかが決まる。

10

【0113】

本実施の形態において用いることができるアナログ回路の一例では、第1のステータスの制御情報SS1より高い電位に第2のステータスの制御情報SS2を、さらに高い電位に第3のステータスの制御情報SS3を、割り当てる構成とすることができる。

【0114】

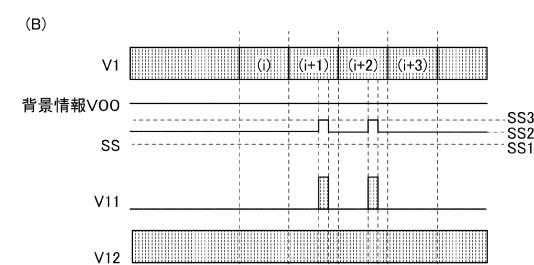

第1のステータスの制御情報SS1と、第3のステータスの制御情報SS3と、を用いて、画像情報V1から情報V11および情報V12を、生成する一例を示す。例えば、選択されていない画像に対し第1のステータス、選択された画像に対し第3のステータスを割り当てることができる（図5（A）参照）。または、選択されていない画像に対し第2のステータス、選択された画像に対し第3のステータスを割り当ててもよい（図5（B）参照）。

20

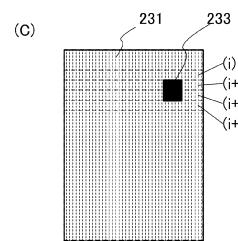

【0115】

例えば、選択された画像が、表示領域231において、 $i + 1$ 行目に配設されている画素および $i + 2$ 行目に配設されている画素に配置されており、この領域を領域233とする。このとき演算装置210は第1のステータスの制御情報SS1および第3のステータスの制御情報SS3を供給し、選択回路239は画像情報V1を含む情報V11および画像情報V1を含む情報V12を供給する（図5（A）および図5（C）参照）。このように、領域233は第1の駆動回路SD1と第2の駆動回路SD2に供給された画像情報V1により表示され、領域233を除く表示領域231は第1の駆動回路SD1に供給された画像情報V1により表示される。

30

【0116】

本実施の形態において用いることができるデジタル回路の一例として、制御情報SSを、信号線se11と、信号線se10との2本の信号線を用いて送ることができる（図6（A）参照）。信号線にHighおよびLowの電源電圧にて0と1の2値を送信したとき、組み合わせで4つの状態を表すことができる。このうち3つを第1のステータスの制御情報SS1、第2のステータスの制御情報SS2、第3のステータスの制御情報SS3、として使用する。これらの制御情報SSにより、画像情報V1、あるいは背景情報V00の信号を、それぞれ第1の駆動回路SD1、または第2の駆動回路SD2へ供給することができる（図6（B）参照）。

40

【0117】

<駆動回路SD1、駆動回路SD2>

駆動回路SD1は、情報V11に基づいて画像信号を供給する機能を有し、駆動回路SD2は、情報V12に基づいて画像信号を供給する機能を有する。なお、駆動回路SD1および駆動回路SD2に換えて、駆動回路SD1および駆動回路SD2が集積された駆動回路SDを用いることができる。

【0118】

例えば、シフトレジスタ等のさまざまな順序回路等を駆動回路SD1または駆動回路SD2に用いることができる。

【0119】

50

具体的には、シリコン基板上に形成された集積回路を駆動回路 S D に用いることができる。

【 0 1 2 0 】

駆動回路 S D 1 は、例えば反射型の表示素子と電気的に接続された画素回路に供給する信号を生成する機能を備える。具体的には、極性が反転する信号を生成する機能を備える。これにより、例えば、反射型の液晶表示素子を駆動することができる。

【 0 1 2 1 】

駆動回路 S D 2 は、例えば発光素子と電気的に接続された画素回路に供給する信号を生成する機能を備える。

【 0 1 2 2 】

< 画素 2 3 2 ( i , j ) >

10

例えば、反射型の表示素子および発光素子を画素 2 3 2 ( i , j ) に用いることができる（図 4 ( C ) 参照）。

【 0 1 2 3 】

具体的には、画素 2 3 2 ( i , j ) は、第 1 の表示素子 2 3 5 A および第 2 の表示素子 2 3 5 B を備える。また、第 1 の表示素子 2 3 5 A および第 2 の表示素子 2 3 5 B を駆動する画素回路を備える。

【 0 1 2 4 】

< 第 1 の表示素子 2 3 5 A >

例えば、光の反射または透過を制御する機能を備える表示素子を、第 1 の表示素子 2 3 5 A に用いることができる。なお、反射型の表示素子を用いると、表示パネルの消費電力を抑制することができる。

20

【 0 1 2 5 】

例えば、液晶素子と偏光板を組み合わせた構成またはシャッター方式の M E M S 表示素子等を用いることができる。具体的には、反射型の液晶表示素子を第 1 の表示素子 2 3 5 A に用いることができる。

【 0 1 2 6 】

第 1 の表示素子 2 3 5 A は、第 1 電極と、第 2 電極と、液晶層と、を有する。液晶層は、第 1 電極および第 2 電極の間の電圧を用いて配向を制御することができる液晶材料を含む。例えば、液晶層の厚さ方向（縦方向ともいう）、横方向または斜め方向の電界を、液晶材料の配向を制御する電界に用いることができる。

30

【 0 1 2 7 】

< 第 2 の表示素子 2 3 5 B >

例えば、光を射出する機能を備える表示素子を第 2 の表示素子 2 3 5 B に用いることができる。具体的には、有機 E L 素子を用いることができる。

【 0 1 2 8 】

例えば、白色の光を射出する機能を備える有機 E L 素子を第 2 の表示素子 2 3 5 B に用いることができる。または、青色の光、緑色の光または赤色の光を射出する有機 E L 素子を第 2 の表示素子 2 3 5 B に用いることができる。

【 0 1 2 9 】

40

< 画素回路 >

第 1 の表示素子 2 3 5 A または第 2 の表示素子 2 3 5 B を駆動する機能を備える回路を画素回路に用いることができる。

【 0 1 3 0 】

スイッチ、トランジスタ、ダイオード、抵抗素子、インダクタまたは容量素子等を画素回路に用いることができる。

【 0 1 3 1 】

例えば、単数または複数のトランジスタをスイッチに用いることができる。または、並列に接続された複数のトランジスタ、直列に接続された複数のトランジスタ、直列と並列が組み合わされて接続された複数のトランジスタを、一のスイッチに用いることができる。

50

## 【0132】

&lt;トランジスタ&gt;

例えば、同一の工程で形成することができる半導体膜を駆動回路および画素回路のトランジスタに用いることができる。

## 【0133】

例えば、ボトムゲート型のトランジスタまたはトップゲート型のトランジスタなどを用いることができる。

## 【0134】

ところで、例えば、アモルファスシリコンを半導体に用いるボトムゲート型のトランジスタの製造ラインは、酸化物半導体を半導体に用いるボトムゲート型のトランジスタの製造ラインに容易に改造できる。また、例えばポリシリコンを半導体に用いるトップゲート型の製造ラインは、酸化物半導体を半導体に用いるトップゲート型のトランジスタの製造ラインに容易に改造できる。10

## 【0135】

例えば、14族の元素を含む半導体を用いるトランジスタを利用することができる。具体的には、シリコンを含む半導体を半導体膜に用いることができる。例えば、単結晶シリコン、ポリシリコン、微結晶シリコンまたはアモルファスシリコンなどを半導体膜に用いたトランジスタを用いることができる。

## 【0136】

なお、半導体にポリシリコンを用いるトランジスタの作製に要する温度は、半導体に単結晶シリコンを用いるトランジスタに比べて低い。低温ポリシリコン (LTPS (Low Temperature Poly-Silicon)) を用いる場合、プロセス温度上限は 500 から 550 程度である。20

## 【0137】

また、ポリシリコンを半導体に用いるトランジスタの電界効果移動度は、アモルファスシリコンを半導体に用いるトランジスタに比べて高い。これにより、画素の開口率を向上することができる。また、極めて高い精細度で設けられた画素と、ゲート駆動回路およびソース駆動回路を同一の基板上に形成することができる。その結果、電子機器を構成する部品数を低減することができる。

## 【0138】

また、ポリシリコンを半導体に用いるトランジスタの信頼性は、アモルファスシリコンを半導体に用いるトランジスタに比べて優れる。

## 【0139】

例えば、酸化物半導体を用いるトランジスタを利用することができる。具体的には、インジウムを含む酸化物半導体またはインジウムとガリウムと亜鉛を含む酸化物半導体を半導体膜に用いることができる。

## 【0140】

一例を挙げれば、オフ状態におけるリーク電流が、半導体膜にアモルファスシリコンを用いたトランジスタより小さいトランジスタを用いることができる。具体的には、半導体膜に酸化物半導体を用いたトランジスタを用いることができる。40

## 【0141】

これにより、画素回路が画像信号を保持することができる時間を、アモルファスシリコンを半導体膜に用いたトランジスタを利用する画素回路が保持することができる時間より長くすることができる。具体的には、フリッカーの発生を抑制しながら、選択信号を 30 Hz 未満、好ましくは 1 Hz 未満より好ましくは一分に一回未満の頻度で供給することができる。その結果、情報処理装置の使用者に蓄積する疲労を低減することができる。また、駆動に伴う消費電力を低減することができる。

## 【0142】

また、例えば、化合物半導体を用いるトランジスタを利用することができる。具体的には、ガリウムヒ素を含む半導体を半導体膜に用いることができる。

10

20

30

40

50

## 【0143】

例えば、有機半導体を用いるトランジスタを利用することができる。具体的には、ポリアセレン類またはグラフェンを含む有機半導体を半導体膜に用いることができる。

## 【0144】

<入力部240>

入力部240は入力パネルを備える。

## 【0145】

例えば、入力パネルは近接センサを備え、近接センサは近接するポインタを検知する機能を備える。なお、指やスタイルスペン等をポインタに用いることができる。

## 【0146】

発光ダイオード等の発光素子、金属片またはコイル等を、スタイルスペンに用いることができる。

10

## 【0147】

例えば、静電容量型の近接センサ、電磁誘導型の近接センサ、赤外線検知型の近接センサ、光電変換素子を用いた近接センサ等を近接センサに用いることができる。

## 【0148】

静電容量型の近接センサは導電膜を備え、大気より大きい誘電率を備えるものの導電膜に対する近接を、検知する機能を備える。例えば、入力パネルの互いに異なる領域に複数の導電膜を配設し、ポインタに用いられる指等が近接する領域を、導電膜に寄生する容量の変化に基づいて特定し、入力位置座標情報を決定できる。

20

## 【0149】

また、電磁誘導型の近接センサは、金属片やコイル等の検知回路に対する近接を検知する機能を備える。例えば、入力パネルの互いに異なる領域に複数の発振回路を配設し、ポインタに用いるスタイルスペン等に配設された金属片やコイル等が近接する領域を、発振回路の回路定数の変化に基づいて特定し、入力位置座標情報を決定できる。

## 【0150】

例えば、光検知型の近接センサは、発光素子の近接を、検知する機能を備える。例えば、入力パネルの互いに異なる領域に複数の光電変換素子を配設し、ポインタに用いるスタイルスペン等に配設された発光素子が近接する領域を、光電変換素子の起電力の変化に基づいて特定し、入力位置座標情報を決定できる。

30

## 【0151】

<検知部250>

周囲の状態を検知して検知情報P2を供給する機能を備えるセンサを、検知部250に用いることができる。

## 【0152】

例えば、環境の明るさを検知する照度センサや人感センサ等を検知部250に用いることができる。

## 【0153】

例えば、カメラ、加速度センサ、方位センサ、圧力センサ、温度センサ、湿度センサ、照度センサまたはGPS (Global positioning System) 信号受信回路等を、検知部250に用いることができる。

40

## 【0154】

<通信部290>

通信部290は、ネットワークに情報を供給する機能またはネットワークから情報を取得する機能を備える。

## 【0155】

なお、本実施の形態は、本明細書で示す他の実施の形態と適宜組み合わせることができる。

## 【0156】

(実施の形態2)

50

本実施の形態では、本発明の一態様の情報処理装置に用いることができるプログラムについて、図7を参照しながら説明する。

【0157】

本実施の形態では、実施の形態1で記載した構成を用いて、入出力装置によりアイコンの選択された頻度に基づいて制御情報SSを第1のステータスの制御情報、第2のステータスの制御情報、または第3のステータスの制御情報を供給する方法を示す。さらに検知部250から演算装置に供給された検知情報に基づいて、制御情報SSを第1のステータスの制御情報、第2のステータスの制御情報、または第3のステータスの制御情報を供給する方法を示す。

【0158】

すなわちこのプログラムにより、選択頻度の低いアイコンは反射型の表示素子を用いて表示の明るさが小さく表示され、一方選択頻度の高いアイコンは発光素子および反射型の表示素子を用いて表示の明るさが大きく、すなわち強調され視認性が良く表示される。

【0159】

図7は、本発明の一態様のプログラムを説明するフローチャートである。

【0160】

<プログラムの例>

本発明の一態様のプログラムは、実施の形態1に記載のプログラムの構成に加え、情報処理装置200の置かれる環境の照度と、入出力装置によりアイコンの選択された頻度と、に基づいて、以下の様に視認性をより向上させる構成を有することができる。

【0161】

選択頻度の高いアイコンは、発光素子および反射型の表示素子を用いて表示する。

【0162】

情報処理装置200を使用する環境が薄暗いまたは暗い場合、選択頻度の低いアイコンは、発光素子を用いて表示する。このとき、暗所でも画像情報を良好に表示することができる。

【0163】

情報処理装置200を使用する環境が明るい場合、選択頻度の低いアイコンは、反射型の表示素子を用いて表示する。

【0164】

また実施の形態1同様、反射型の表示素子に第1のステータスの制御情報が供給されたときの表示を用いる。また、発光素子に第2のステータスの制御情報が供給されたときの表示を用いる。また、反射型の表示素子と発光素子両方に、第3のステータスの制御情報が供給されたときの表示を用いる。

【0165】

すなわち下記のステップを有するプログラムである。

【0166】

<第1のステップから第3のステップまで>

第1のステップ(図7(T1))から第3のステップ(図7(T3))までにおいて、図2(T1)から図2(T3)と同様に、入力部240から供給される入力の有無を判断し、入力部240から供給される入力位置座標情報P1を読み込み、アイコンの表示との範囲の重なりがあるか判断する。

【0167】

アイコンの表示との範囲の重なりがない場合、第5のステップ(図7(T5))に進む。アイコンの表示との範囲の重なりがある場合、次の第4のステップ(図7(T4))に進む。

【0168】

<第4のステップ>

第4のステップにおいて、演算装置210は、第3のステップ(図7(T3))で重なったと判断されたアイコン、すなわち選択されたアイコンに対して、その過去に選択された

10

20

30

40

50

頻度を判断する。

【0169】

アイコンが選択された頻度が高いと判断した場合、次の第7-3のステップ(図7(T7-3))に進み、アイコンの表示される座標情報すなわちアイコン座標情報に対して第3のステータスの制御情報SSを供給する。選択された頻度の判断は、入力時点からこれまでに各アイコンが選択された回数があらかじめ設定された閾値以上であるかの判断でなされ、選択された回数は入力の度に更新する。このとき、第3のステータスの制御情報SSに基づいて、選択回路239は、画像情報V1を第1の駆動回路SD1および第2の駆動回路SD2に供給する(図1(B)参照)。

【0170】

またアイコンが選択された頻度が低いと判断した場合、次の第5のステップ(図7(T5))に進む。

【0171】

<第5のステップ>

第5のステップにおいて、照度センサを検知部250に用い、照度についての検知情報P2を検知部250に供給させ、検知情報P2を所定の値と比較する。

【0172】

<第6のステップ>

第6のステップにおいて、外環境すなわち照度についての検知情報P2から制御情報として第1のステータスの制御情報または第2のステータスの制御情報を供給するか決定する。情報処理装置200を使用する環境が明るい場合、第1のステータスの制御情報を供給し反射型の表示素子での表示をする(図7(T7-1))。同じく薄暗いまたは暗い場合、第2のステータスの制御情報を供給し発光素子での表示をする(図7(T7-2))。

【0173】

情報処理装置200を使用する環境が明るい場合、第1のステータスの制御情報SSに基づいて、選択回路239は、画像情報V1を第1の駆動回路SD1に供給し、背景情報を第2の駆動回路SD2に供給する(図1(B)参照)。同じく薄暗いまたは暗い場合、第2のステータスの制御情報SSに基づいて、選択回路239は、画像情報V1を第2の駆動回路SD2に供給し、背景情報を第1の駆動回路SD1に供給する(図1(B)参照)。

。

【0174】

これにより、照度などの検知情報およびアイコンの選択頻度に基づいて制御情報のステータスを決定できる。その結果、反射型の表示素子または発光素子、もしくはその両方を選択し、選択した反射型の表示素子および/または発光素子を用いて、画像情報を表示することができる。

【0175】

なお、本実施の形態は、本明細書で示す他の実施の形態と適宜組み合わせができる。

【0176】

(実施の形態3)

本実施の形態では、本発明の一態様の情報処理装置に用いることができるプログラムについて、図8を参照しながら説明する。

【0177】

本実施の形態では、入出力装置により選択された領域の表示方法を変更することができる。本実施の形態の情報処理装置は、通常の表示を発光素子を用いて行うとき、かつ発光素子の駆動回路の不具合により欠陥が入ったとき、その欠陥領域の座標情報を入出力装置よりタッチセンサ等で入力することで、発光素子に加えて反射型の表示素子にて表示を補うことができる。

【0178】

本実施の形態のプログラムにより、入出力装置により選択された領域は反射型の表示素子

10

20

30

40

50

および発光素子で表示され、一方で選択されていない領域は発光素子にて表示される。

【0179】

本実施の形態では、通常の表示を反射型の表示素子を用いて行うとき、反射型の表示素子に加えて発光素子にて表示を補う場合にも、同様に適用できる。

【0180】

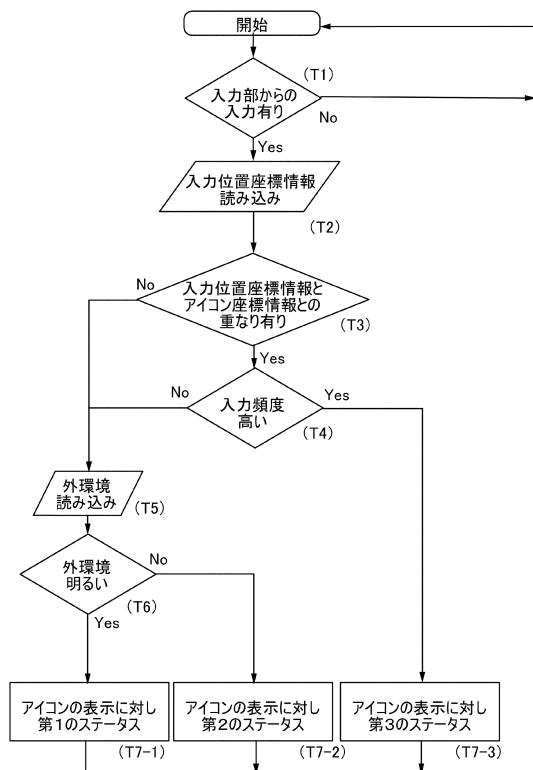

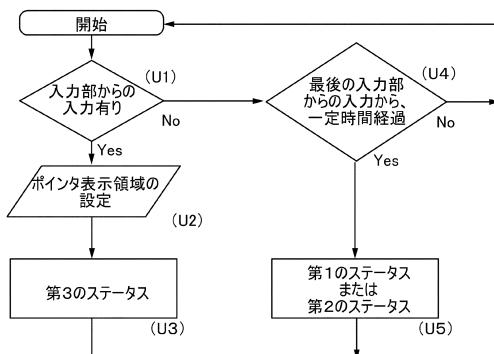

図8は、本発明の一態様のプログラムを説明するフローチャートである。

【0181】

<プログラムの例>

<第1のステップ>

第1のステップ(図8(U1))において、入力部240から供給される入力の有無を判断し、入力がある場合、第2のステップに進む。 10

【0182】

<第2のステップ>

第2のステップ(図8(U2))において、入力部240から供給される入力位置座標情報P1を読み込む。本実施の形態では、入力位置座標情報P1の含む座標を中心として一定の半径の広がりをもつポインタを表示する。本明細書中ではこのポインタの表示される領域をポインタ表示領域と設定する。次いで第3のステップに進む。

【0183】

<第3のステップ>

第3のステップにおいて、第2のステップで設定したポインタ表示領域の、表示部の座標に、第3のステータスの制御情報SSを供給する(図8(U3))。これにより、入力された位置では反射型の表示素子および発光素子で表示し、欠陥領域の表示を補足することで視認性を向上することができる。 20

【0184】

<第4のステップ>

第4のステップにおいて、最後の入力部からの入力から、一定時間経過したかを判断する。一定時間経過するということは、つまり必要な表示を確認したことを意味し、通常の表示に戻すため第5のステップに進む。

【0185】

<第5のステップ>

第5のステップにおいて、ポインタ表示領域に対応する、表示部の座標に、通常表示の制御情報すなわち第1のステータスの制御情報、または第2のステータスの制御情報を供給する。通常表示の表示方法は、実施の形態2で示されるように、検知情報P2で選択頻度の低いアイコンに割り当てた表示方法である。このように元の表示に戻すことで、必要な強調する部分を更新することができる。 30

【0186】

このポインタ表示領域は、入力位置座標情報P1が複数ある場合、複数分積算した領域を持っても良い。

【0187】

なお、本実施の形態で示される入力を、検知情報や入力位置座標情報、あるいはそれらの組み合わせによる入力としてもよい。本実施の形態は、本明細書で示す他の実施の形態と適宜組み合わせることができる。 40

【0188】

(実施の形態4)

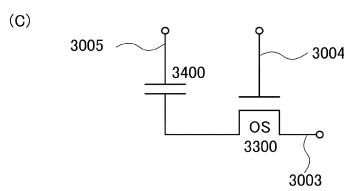

本実施の形態では、本発明の一態様の表示パネルの構成について、図9乃至図11、図19及び図20を参照しながら説明する。

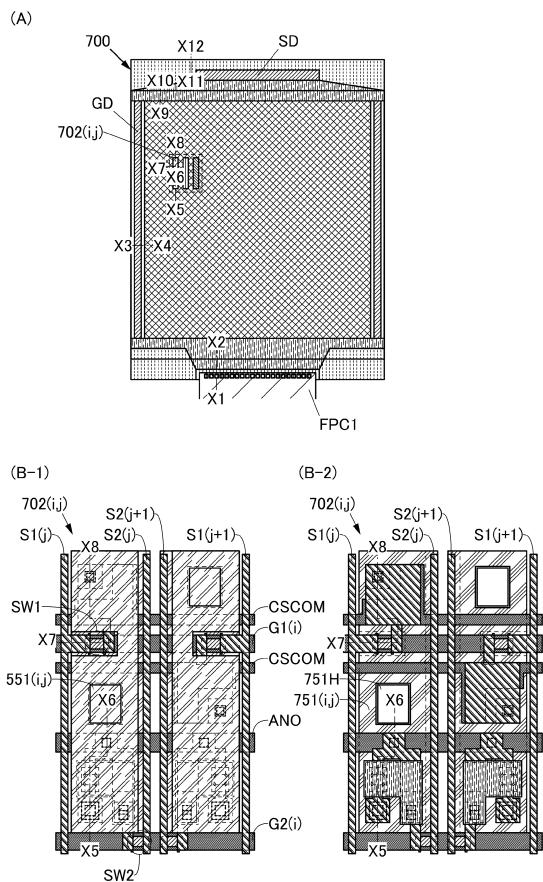

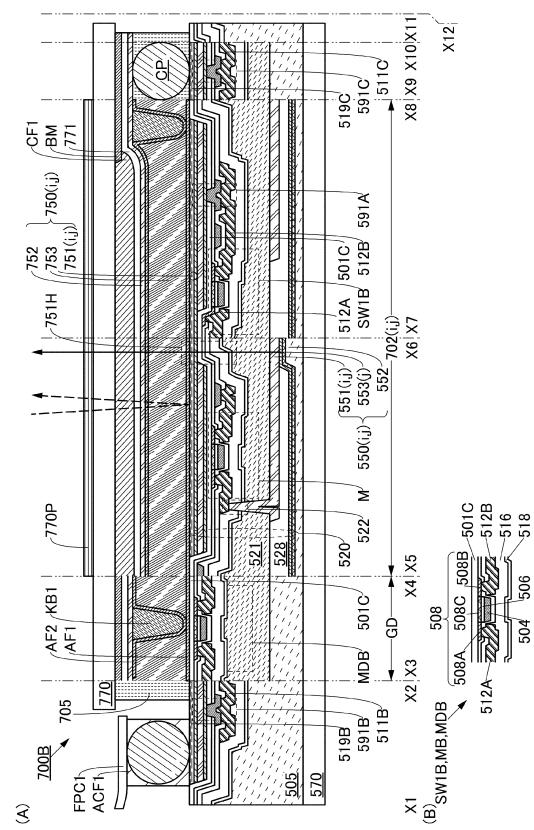

【0189】

図9は本発明の一態様の表示パネル700の構成を説明する図である。図9(A)は本発明の一態様の表示パネル700の下面図である。図9(B-1)は図9(A)の一部を説明する下面図であり、図9(B-2)は図9(B-1)に図示する一部の構成を省略して 50

説明する下面図である。

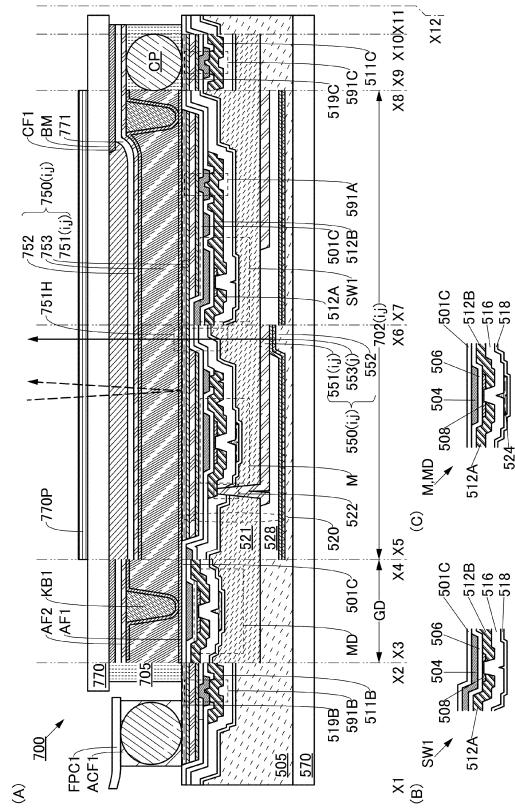

【0190】

図19は本発明の一態様の表示パネル700の構成を説明する図である。図19(A)は図9(A)の切断線X1-X2、X3-X4、X5-X6、X7-X8、X9-X10、X11-X12における断面図である。図19(B)は表示パネルの一部の構成を説明する断面図であり、図19(C)は表示パネルの他の一部の構成を説明する断面図である。

【0191】

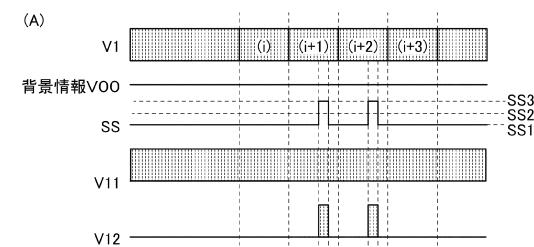

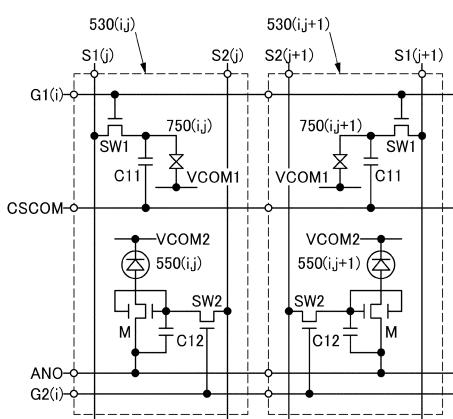

図10は本発明の一態様の表示パネル700の構成を説明する図である。図10は本発明の一態様の表示パネル700が備える画素回路530(i,j)および画素回路530(i,j+1)の回路図である。

10

【0192】

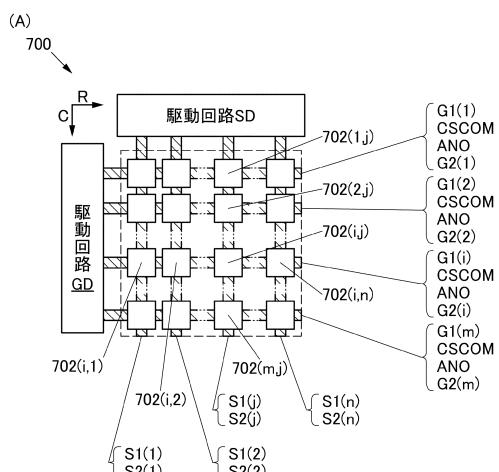

図11は本発明の一態様の表示パネル700の構成を説明する図である。図11(A)は本発明の一態様の表示パネル700に用いることができる画素および配線等の配置を説明するブロック図である。図11(B-1)および図11(B-2)は本発明の一態様の表示パネル700に用いることができる開口部751Hの配置を説明する模式図である。

【0193】

<表示パネルの構成例1. >

本実施の形態で説明する表示パネル700は、信号線S1(j)と、画素702(i,j)と、を有する(図9(B-1)および図9(B-2)参照)。

【0194】

画素702(i,j)は、信号線S1(j)と電気的に接続される。

20

【0195】

画素702(i,j)は、第1の表示素子750(i,j)と、第1の導電膜と、第2の導電膜と、絶縁膜501Cと、画素回路530(i,j)と、第2の表示素子550(i,j)と、を有する(図19(A)および図10参照)。

【0196】

第1の導電膜は、第1の表示素子750(i,j)と電気的に接続される(図19(A)参照)。例えば、第1の導電膜を、第1の表示素子750(i,j)の第1の電極751(i,j)に用いることができる。

30

【0197】

第2の導電膜は、第1の導電膜と重なる領域を備える。例えば、第2の導電膜を、スイッチSW1に用いることができるトランジスタのソース電極またはドレイン電極として機能する導電膜512Bに用いることができる。

【0198】

絶縁膜501Cは、第2の導電膜と第1の導電膜の間に挟まれる領域を備える。

【0199】

画素回路530(i,j)は、第2の導電膜と電気的に接続される。例えば、第2の導電膜をソース電極またはドレイン電極として機能する導電膜512Bに用いたトランジスタを、画素回路530(i,j)のスイッチSW1に用いることができる(図19(A)および図10参照)。

40

【0200】

第2の表示素子550(i,j)は、画素回路530(i,j)と電気的に接続される。

【0201】

絶縁膜501Cは、開口部591Aを備える(図19(A)参照)。

【0202】

第2の導電膜は、開口部591Aにおいて第1の導電膜と電気的に接続される。例えば、導電膜512Bは、第1の導電膜を兼ねる第1の電極751(i,j)と電気的に接続される。

【0203】

画素回路530(i,j)は、信号線S1(j)と電気的に接続される(図10参照)。

50

なお、導電膜 512A は、信号線 S1 (j) と電気的に接続される (図 10 および図 19 (A) 参照)。

【0204】

第 1 の電極 751 (i, j) は、絶縁膜 501C に埋め込まれた側端部を備える。

【0205】

また、本実施の形態で説明する表示パネルの画素回路 530 (i, j) は、スイッチ SW1 を備える。スイッチ SW1 はトランジスタを含み、トランジスタは、酸化物半導体を含む。

【0206】

また、本実施の形態で説明する表示パネルの第 2 の表示素子 550 (i, j) は、第 1 の表示素子 750 (i, j) が備える視野角の一部と重なる視野角を備える。言い換えると、第 1 の表示素子 750 (i, j) が表示をする方向の一部と同一の方向に表示をする機能を備える。例えば、外光を反射する強度を制御して第 1 の表示素子 750 (i, j) が表示をする方向を、破線の矢印で図中に示す。また、第 2 の表示素子 550 (i, j) が表示をする方向を、実線の矢印で図中に示す (図 19 (A) 参照)。

【0207】

また、本実施の形態で説明する表示パネルの第 2 の表示素子 550 (i, j) は、第 1 の表示素子 750 (i, j) が表示をする領域に囲まれた領域に表示をする機能を備える (図 11 (B-1) または図 11 (B-2) 参照)。なお、第 1 の表示素子 750 (i, j) は、第 1 の電極 751 (i, j) と重なる領域に表示をし、第 2 の表示素子 550 (i, j) は、開口部 751H と重なる領域に表示をする。

【0208】

また、本実施の形態で説明する表示パネルの第 1 の表示素子 750 (i, j) は、入射する光を反射する機能を備える反射膜と、反射する光の強さを制御する機能と、を有する。そして、反射膜は、開口部 751H を備える。なお、例えば、第 1 の表示素子 750 (i, j) の反射膜に、第 1 の導電膜または第 1 の電極 751 (i, j) 等を用いることができる。

【0209】

また、第 2 の表示素子 550 (i, j) は、開口部 751H に向けて光を射出する機能を有する。

【0210】

また、本実施の形態で説明する表示パネルは、画素 702 (i, j) と、一群の画素 702 (i, 1) 乃至画素 702 (i, n) と、他の一群の画素 702 (1, j) 乃至画素 702 (m, j) と、走査線 G1 (i) と、を有する (図 11 (A) 参照)。なお、i は 1 以上 m 以下の整数であり、j は 1 以上 n 以下の整数であり、m および n は 1 以上の整数である。

【0211】

また、本実施の形態で説明する表示パネルは、走査線 G2 (i) と、配線 CSCOM と、配線 ANO と、を有する。

【0212】

一群の画素 702 (i, 1) 乃至画素 702 (i, n) は、画素 702 (i, j) を含み、行方向 (図中に矢印 R で示す方向) に配設される。

【0213】

また、他の一群の画素 702 (1, j) 乃至画素 702 (m, j) は、画素 702 (i, j) を含み、行方向と交差する列方向 (図中に矢印 C で示す方向) に配設される。

【0214】

走査線 G1 (i) は、行方向に配設される一群の画素 702 (i, 1) 乃至画素 702 (i, n) と電気的に接続される。

【0215】

列方向に配設される他の一群の画素 702 (1, j) 乃至画素 702 (m, j) は、信号

10

20

30

40

50

線 S 1 ( j ) と電気的に接続される。

【 0 2 1 6 】

例えば、画素 7 0 2 ( i , j ) の行方向に隣接する画素 7 0 2 ( i , j + 1 ) は、画素 7 0 2 ( i , j ) に対する開口部 7 5 1 H の配置と異なるように画素 7 0 2 ( i , j + 1 ) に配置される開口部を備える ( 図 1 1 ( B - 1 ) 参照 )。

【 0 2 1 7 】

例えば、画素 7 0 2 ( i , j ) の列方向に隣接する画素 7 0 2 ( i + 1 , j ) は、画素 7 0 2 ( i , j ) に対する開口部 7 5 1 H の配置と異なるように画素 7 0 2 ( i + 1 , j ) に配置される開口部を備える ( 図 1 1 ( B - 2 ) 参照 )。なお、例えば、第 1 の電極 7 5 1 ( i , j ) を反射膜に用いることができる。

10

【 0 2 1 8 】

本実施の形態で説明する表示パネルは、第 1 の表示素子と、第 1 の表示素子と電気的に接続される第 1 の導電膜と、第 1 の導電膜と重なる領域を備える第 2 の導電膜と、第 2 の導電膜と第 1 の導電膜の間に挟まれる領域を備える絶縁膜と、第 2 の導電膜と電気的に接続される画素回路と、画素回路と電気的に接続される第 2 の表示素子と、を含み、絶縁膜は開口部を備え、第 2 の導電膜は第 1 の導電膜と開口部で電気的に接続される。

【 0 2 1 9 】

これにより、例えば同一の工程を用いて形成することができる画素回路を用いて、第 1 の表示素子と、第 1 の表示素子とは異なる方法を用いて表示をする第 2 の表示素子と、を駆動することができる。その結果、利便性に優れた新規な表示パネルを提供することができる。

20

【 0 2 2 0 】

また、本実施の形態で説明する表示パネルは、端子 5 1 9 B と、導電膜 5 1 1 B と、を有する ( 図 1 9 ( A ) 参照 )。

【 0 2 2 1 】

絶縁膜 5 0 1 C は、端子 5 1 9 B および導電膜 5 1 1 B の間に挟まれる領域を備える。また、絶縁膜 5 0 1 C は、開口部 5 9 1 B を備える。

【 0 2 2 2 】

端子 5 1 9 B は、開口部 5 9 1 B において導電膜 5 1 1 B と電気的に接続される。また、導電膜 5 1 1 B は、画素回路 5 3 0 ( i , j ) と電気的に接続される。なお、例えば、第 1 の電極 7 5 1 ( i , j ) または第 1 の導電膜を反射膜に用いる場合、端子 5 1 9 B の接点として機能する面は、第 1 の電極 7 5 1 ( i , j ) の、第 1 の表示素子 7 5 0 ( i , j ) に入射する光に向いている面と同じ方向に向いている。

30

【 0 2 2 3 】

これにより、端子を介して電力または信号を、画素回路に供給することができる。その結果、利便性に優れた新規な表示パネルを提供することができる。

【 0 2 2 4 】

また、本実施の形態で説明する表示パネルの第 1 の表示素子 7 5 0 ( i , j ) は、液晶材料を含む層 7 5 3 と、第 1 の電極 7 5 1 ( i , j ) および第 2 の電極 7 5 2 と、を備える。なお、第 2 の電極 7 5 2 は、第 1 の電極 7 5 1 ( i , j ) との間に液晶材料の配向を制御する電界が形成されるように配置される。

40

【 0 2 2 5 】

また、本実施の形態で説明する表示パネルは、配向膜 A F 1 および配向膜 A F 2 を備える。配向膜 A F 2 は、配向膜 A F 1 との間に液晶材料を含む層 7 5 3 を挟むように配設される。

【 0 2 2 6 】

また、本実施の形態で説明する表示パネルの第 2 の表示素子 5 5 0 ( i , j ) は、第 3 の電極 5 5 1 ( i , j ) と、第 4 の電極 5 5 2 と、発光性の有機化合物を含む層 5 5 3 ( j ) と、を備える。

【 0 2 2 7 】

50

第4の電極552は、第3の電極551(i, j)と重なる領域を備える。発光性の有機化合物を含む層553(j)は、第3の電極551(i, j)および第4の電極552の間に配設される。そして、第3の電極551(i, j)は、接続部522において、画素回路530(i, j)と電気的に接続される。

## 【0228】

また、本実施の形態で説明する表示パネルの画素702(i, j)は、着色膜CF1と、遮光膜BMと、絶縁膜771と、機能膜770Pと、を有する。

## 【0229】

着色膜CF1は、第1の表示素子750(i, j)と重なる領域を備える。遮光膜BMは、第1の表示素子750(i, j)と重なる領域に開口部を備える。

10

## 【0230】

絶縁膜771は、着色膜CF1と液晶材料を含む層753の間または遮光膜BMと液晶材料を含む層753の間に配設される。これにより、着色膜CF1の厚さに基づく凹凸を平坦にすることができます。または、遮光膜BMまたは着色膜CF1等から液晶材料を含む層753への不純物の拡散を、抑制することができます。

## 【0231】

機能膜770Pは、第1の表示素子750(i, j)と重なる領域を備える。機能膜770Pは、第1の表示素子750(i, j)との間に基板770を挟むように配設される。

## 【0232】

また、本実施の形態で説明する表示パネルは、基板570と、基板770と、機能層520と、を有する。

20

## 【0233】

基板770は、基板570と重なる領域を備える。機能層520は、基板570および基板770の間に配設される。

## 【0234】

機能層520は、画素回路530(i, j)と、第2の表示素子550(i, j)と、絶縁膜521と、絶縁膜528と、を含む。また、機能層520は、絶縁膜518および絶縁膜516を含む。

## 【0235】

絶縁膜521は、画素回路530(i, j)および第2の表示素子550(i, j)の間に配設される。

30

## 【0236】

絶縁膜528は、絶縁膜521および基板570の間に配設され、第2の表示素子550(i, j)と重なる領域に開口部を備える。第3の電極551の周縁に沿って形成される絶縁膜528は、第3の電極551および第4の電極552の短絡を防止することができます。

## 【0237】

絶縁膜518は、絶縁膜521および画素回路530(i, j)の間に配設される領域を備え、絶縁膜516は、絶縁膜518および画素回路530(i, j)の間に配設される領域を備える。

40

## 【0238】

また、本実施の形態で説明する表示パネルは、接合層505と、封止材705と、構造体KB1と、を有する。

## 【0239】

接合層505は、機能層520および基板570の間に配設され、機能層520および基板570を貼り合せる機能を備える。

## 【0240】

封止材705は、機能層520および基板770の間に配設され、機能層520および基板770を貼り合わせる機能を備える。

## 【0241】

50

構造体 K B 1 は、機能層 5 2 0 および基板 7 7 0 の間に所定の間隙を設ける機能を備える。

【 0 2 4 2 】

また、本実施の形態で説明する表示パネルは、端子 5 1 9 C と、導電膜 5 1 1 C と、導電体 C P と、を有する。

【 0 2 4 3 】

絶縁膜 5 0 1 C は、端子 5 1 9 C および導電膜 5 1 1 C の間に挟まれる領域を備える。また、絶縁膜 5 0 1 C は、開口部 5 9 1 C を備える。

【 0 2 4 4 】

端子 5 1 9 C は、開口部 5 9 1 C において導電膜 5 1 1 C と電気的に接続される。また、導電膜 5 1 1 C は、画素回路 5 3 0 ( i , j ) と電気的に接続される。 10

【 0 2 4 5 】

導電体 C P は、端子 5 1 9 C と第 2 の電極 7 5 2 の間に挟まれ、端子 5 1 9 C と第 2 の電極 7 5 2 を電気的に接続する。例えば、導電性の粒子を導電体 C P に用いることができる。

【 0 2 4 6 】

また、本実施の形態で説明する表示パネルは、駆動回路 G D と、駆動回路 S D と、を有する(図 9 ( A ) および図 11 ( A ) 参照)。

【 0 2 4 7 】

駆動回路 G D は、走査線 G 1 ( i ) と電気的に接続される。駆動回路 G D は、例えばトランジスタ M D を備える。具体的には、画素回路 5 3 0 ( i , j ) に含まれるトランジスタと同じ工程で形成することができる半導体膜を含むトランジスタをトランジスタ M D に用いることができる(図 19 ( A ) および図 19 ( C ) 参照)。 20

【 0 2 4 8 】

駆動回路 S D は、信号線 S 1 ( j ) と電気的に接続される。駆動回路 S D は、例えば端子 5 1 9 B または端子 5 1 9 C と同一の工程で形成することができる端子に導電材料を用いて電気的に接続される。

【 0 2 4 9 】

以下に、表示パネルを構成する個々の要素について説明する。なお、これらの構成は明確に分離できず、一つの構成が他の構成を兼ねる場合や他の構成の一部を含む場合がある。 30

【 0 2 5 0 】

例えば第 1 の導電膜を第 1 の電極 7 5 1 ( i , j ) に用いることができる。また、第 1 の導電膜を反射膜に用いることができる。

【 0 2 5 1 】

また、第 2 の導電膜をトランジスタのソース電極またはドレン電極の機能を備える導電膜 5 1 2 B に用いることができる。

【 0 2 5 2 】

<構成例>

本発明の一態様の表示パネルは、基板 5 7 0 、基板 7 7 0 、構造体 K B 1 、封止材 7 0 5 または接合層 5 0 5 、を有する。 40

【 0 2 5 3 】

また、本発明の一態様の表示パネルは、機能層 5 2 0 、絶縁膜 5 2 1 、絶縁膜 5 2 8 、を有する。

【 0 2 5 4 】

また、本発明の一態様の表示パネルは、信号線 S 1 ( j ) 、信号線 S 2 ( j ) 、走査線 G 1 ( i ) 、走査線 G 2 ( i ) 、配線 C S C O M 、配線 A N O を有する。

【 0 2 5 5 】

また、本発明の一態様の表示パネルは、第 1 の導電膜または第 2 の導電膜を有する。

【 0 2 5 6 】

また、本発明の一態様の表示パネルは、端子 5 1 9 B 、端子 5 1 9 C 、導電膜 5 1 1 B ま 50

たは導電膜 511C を有する。

【0257】

また、本発明の一態様の表示パネルは、画素回路 530 (i, j) またはスイッチ SW1 、を有する。

【0258】

また、本発明の一態様の表示パネルは、第1の表示素子 750 (i, j) 、第1の電極 751 (i, j) 、反射膜、開口部 751H 、液晶材料を含む層 753 、第2の電極 752 、を有する。

【0259】

また、本発明の一態様の表示パネルは、配向膜 AF1 、配向膜 AF2 、着色膜 CF1 、遮光膜 BM 、絶縁膜 771 、機能膜 770P を有する。 10

【0260】

また、本発明の一態様の表示パネルは、第2の表示素子 550 (i, j) 、第3の電極 551 (i, j) 、第4の電極 552 または発光性の有機化合物を含む層 553 (j) を有する。

【0261】

また、本発明の一態様の表示パネルは、絶縁膜 501C を有する。

【0262】

また、本発明の一態様の表示パネルは、駆動回路 GD または駆動回路 SD を有する。 20

【0263】

<基板 570 >

作製工程中の熱処理に耐えうる程度の耐熱性を有する材料を基板 570 等に用いることができる。具体的には厚さ 0.7mm の無アルカリガラスを用いることができる。または、厚さ 0.1mm 程度まで研磨した無アルカリガラスを用いることができる。

【0264】

例えば、第6世代 (1500mm × 1850mm) 、第7世代 (1870mm × 2200mm) 、第8世代 (2200mm × 2400mm) 、第9世代 (2400mm × 2800mm) 、第10世代 (2950mm × 3400mm) 等の面積が大きなガラス基板を基板 570 等に用いることができる。これにより、大型の表示装置を作製することができる。 30

【0265】

有機材料、無機材料または有機材料と無機材料等の複合材料等を基板 570 等に用いることができる。例えば、ガラス、セラミックス、金属等の無機材料を基板 570 等に用いることができる。

【0266】

具体的には、無アルカリガラス、ソーダ石灰ガラス、カリガラス、クリスタルガラス、石英またはサファイア等を、基板 570 等に用いることができる。具体的には、無機酸化物膜、無機窒化物膜または無機酸窒化物膜等を、基板 570 等に用いることができる。例えば、酸化シリコン、窒化シリコン、酸化窒化シリコン、酸化アルミニウム膜等を、基板 570 等に用いることができる。ステンレス・スチールまたはアルミニウム等を、基板 570 等に用いることができる。 40

【0267】

例えば、シリコンや炭化シリコンからなる単結晶半導体基板、多結晶半導体基板、シリコングルマニウム等の化合物半導体基板、SOI 基板等を基板 570 等に用いることができる。これにより、半導体素子を基板 570 等に形成することができる。

【0268】

例えば、樹脂、樹脂フィルムまたはプラスチック等の有機材料を基板 570 等に用いることができる。具体的には、ポリエステル、ポリオレフィン、ポリアミド、ポリイミド、ポリカーボネートまたはアクリル樹脂等の樹脂フィルムまたは樹脂板を、基板 570 等に用いることができる。

【0269】

50

例えば、金属板、薄板状のガラス板または無機材料等の膜を樹脂フィルム等に貼り合わせた複合材料を基板 570 等に用いることができる。例えば、纖維状または粒子状の金属、ガラスもしくは無機材料等を樹脂フィルムに分散した複合材料を、基板 570 等に用いることができる。例えば、纖維状または粒子状の樹脂もしくは有機材料等を無機材料に分散した複合材料を、基板 570 等に用いることができる。

#### 【0270】

また、単層の材料または複数の層が積層された材料を、基板 570 等に用いることができる。例えば、基材と基材に含まれる不純物の拡散を防ぐ絶縁膜等が積層された材料を、基板 570 等に用いることができる。具体的には、ガラスとガラスに含まれる不純物の拡散を防ぐ酸化シリコン層、窒化シリコン層または酸化窒化シリコン層等から選ばれた一または複数の膜が積層された材料を、基板 570 等に用いることができる。または、樹脂と樹脂を透過する不純物の拡散を防ぐ酸化シリコン膜、窒化シリコン膜または酸化窒化シリコン膜等が積層された材料を、基板 570 等に用いることができる。

10

#### 【0271】

具体的には、ポリエステル、ポリオレフィン、ポリアミド、ポリイミド、ポリカーボネート若しくはアクリル樹脂等の樹脂フィルム、樹脂板または積層体等を基板 570 等に用いることができる。

#### 【0272】

具体的には、ポリエステル、ポリオレフィン、ポリアミド（ナイロン、アラミド等）、ポリイミド、ポリカーボネート、ポリウレタン、アクリル樹脂、エポキシ樹脂もしくはシリコーン等のシロキサン結合を有する樹脂を含む材料を基板 570 等に用いることができる。

20

#### 【0273】

具体的には、ポリエチレンテレフタレート（P E T）、ポリエチレンナフタレート（P E N）、ポリエーテルサルファン（P E S）またはアクリル等を基板 570 等に用いることができる。

#### 【0274】

また、紙または木材などを基板 570 等に用いることができる。

#### 【0275】

例えば、可撓性を有する基板を基板 570 等に用いることができる。

30

#### 【0276】

なお、トランジスタまたは容量素子等を基板に直接形成する方法を用いることができる。また、例えば作製工程中に加わる熱に耐熱性を有する工程用の基板にトランジスタまたは容量素子等を形成し、形成されたトランジスタまたは容量素子等を基板 570 等に転置する方法を用いることができる。これにより、例えば可撓性を有する基板にトランジスタまたは容量素子等を形成できる。

#### 【0277】

<基板 770 >

例えば、透光性を備える材料を基板 770 に用いることができる。具体的には、基板 570 に用いることができる材料から選択された材料を基板 770 に用いることができる。具体的には厚さ 0.7 mm または厚さ 0.1 mm 程度まで研磨した無アルカリガラスを用いることができる。

40

#### 【0278】

<構造体 K B 1 >

例えば、有機材料、無機材料または有機材料と無機材料の複合材料を構造体 K B 1 等に用いることができる。これにより、構造体 K B 1 等を挟む構成の間に所定の間隔を設けることができる。

#### 【0279】

具体的には、ポリエステル、ポリオレフィン、ポリアミド、ポリイミド、ポリカーボネート、ポリシロキサン若しくはアクリル樹脂等またはこれらから選択された複数の樹脂の複

50

合材料などを構造体 K B 1 等に用いることができる。また、感光性を有する材料を用いて形成してもよい。

【 0 2 8 0 】

< 封止材 7 0 5 >

無機材料、有機材料または無機材料と有機材料の複合材料等を封止材 7 0 5 等に用いることができる。

【 0 2 8 1 】

例えば、熱溶融性の樹脂または硬化性の樹脂等の有機材料を、封止材 7 0 5 等に用いることができる。

【 0 2 8 2 】

例えば、反応硬化型接着剤、光硬化型接着剤、熱硬化型接着剤または／および嫌気型接着剤等の有機材料を封止材 7 0 5 等に用いることができる。

【 0 2 8 3 】

具体的には、エポキシ樹脂、アクリル樹脂、シリコーン樹脂、フェノール樹脂、ポリイミド樹脂、イミド樹脂、PVC（ポリビニルクロライド）樹脂、PVB（ポリビニルブチラル）樹脂、EVA（エチレンビニルアセテート）樹脂等を含む接着剤を封止材 7 0 5 等に用いることができる。

【 0 2 8 4 】

< 接合層 5 0 5 >

例えば、封止材 7 0 5 に用いることができる材料を接合層 5 0 5 に用いることができる。

10

【 0 2 8 5 】

< 絶縁膜 5 2 1 >

例えば、絶縁性の無機材料、絶縁性の有機材料または無機材料と有機材料を含む絶縁性の複合材料を、絶縁膜 5 2 1 等に用いることができる。

【 0 2 8 6 】

具体的には、無機酸化物膜、無機窒化物膜または無機酸化窒化物膜等またはこれらから選ばれた複数を積層した積層材料を、絶縁膜 5 2 1 等に用いることができる。例えば、酸化シリコン膜、窒化シリコン膜、酸化窒化シリコン膜、酸化アルミニウム膜等またはこれらから選ばれた複数を積層した積層材料を含む膜を、絶縁膜 5 2 1 等に用いることができる。

30

【 0 2 8 7 】

具体的には、ポリエステル、ポリオレフィン、ポリアミド、ポリイミド、ポリカーボネート、ポリシロキサン若しくはアクリル樹脂等またはこれらから選択された複数の樹脂の積層材料もしくは複合材料などを絶縁膜 5 2 1 等に用いることができる。また、感光性を有する材料を用いて形成してもよい。

【 0 2 8 8 】

これにより、例えば絶縁膜 5 2 1 と重なるさまざまな構造に由来する段差を平坦化することができる。

【 0 2 8 9 】

< 絶縁膜 5 2 8 >

例えば、絶縁膜 5 2 1 に用いることができる材料を絶縁膜 5 2 8 等に用いることができる。具体的には、厚さ 1  $\mu$ m のポリイミドを含む膜を絶縁膜 5 2 8 に用いることができる。

40

【 0 2 9 0 】

< 絶縁膜 5 0 1 C >

例えば、絶縁膜 5 2 1 に用いることができる材料を絶縁膜 5 0 1 C に用いることができる。具体的には、シリコンおよび酸素を含む材料を絶縁膜 5 0 1 C に用いることができる。これにより、画素回路または第 2 の表示素子等への不純物の拡散を抑制することができる。

【 0 2 9 1 】

例えば、シリコン、酸素および窒素を含む厚さ 2 0 0 nm の膜を絶縁膜 5 0 1 C に用いる

50

ことができる。

【0292】

なお、絶縁膜501Cは、開口部591A、開口部591Bまたは開口部591Cを有する。

【0293】

<配線、端子、導電膜>

導電性を備える材料を配線等に用いることができる。具体的には、導電性を備える材料を、信号線S1(j)、信号線S2(j)、走査線G1(i)、走査線G2(i)、配線CSCOM、配線AN0、端子519B、端子519C、導電膜511Bまたは導電膜511C等に用いることができる。

10

【0294】

例えば、無機導電性材料、有機導電性材料、金属または導電性セラミックスなどを配線等に用いることができる。

【0295】

具体的には、アルミニウム、金、白金、銀、銅、クロム、タンタル、チタン、モリブデン、タンゲステン、ニッケル、鉄、コバルト、パラジウムまたはマンガンから選ばれた金属元素などを、配線等に用いることができる。または、上述した金属元素を含む合金などを、配線等に用いることができる。特に、銅とマンガンの合金がウエットエッチング法を用いた微細加工に好適である。

20

【0296】

具体的には、アルミニウム膜上にチタン膜を積層する二層構造、窒化チタン膜上にチタン膜を積層する二層構造、窒化チタン膜上にタンゲステン膜を積層する二層構造、窒化タンタル膜または窒化タンゲステン膜上にタンゲステン膜を積層する二層構造、チタン膜と、そのチタン膜上にアルミニウム膜を積層し、さらにその上にチタン膜を形成する三層構造等を配線等に用いることができる。

【0297】

具体的には、酸化インジウム、インジウム錫酸化物、インジウム亜鉛酸化物、酸化亜鉛、ガリウムを添加した酸化亜鉛などの導電性酸化物を、配線等に用いることができる。

【0298】

具体的には、グラフェンまたはグラファイトを含む膜を配線等に用いることができる。

30

【0299】

例えば、酸化グラフェンを含む膜を形成し、酸化グラフェンを含む膜を還元することにより、グラフェンを含む膜を形成することができる。還元する方法としては、熱を加える方法や還元剤を用いる方法等を挙げることができる。

【0300】

具体的には、導電性高分子を配線等に用いることができる。

【0301】

<第1の導電膜、第2の導電膜>

例えば、配線等に用いることができる材料を第1の導電膜または第2の導電膜に用いることができる。

40

【0302】

また、第1の電極751(i, j)または配線等を第1の導電膜に用いることができる。

【0303】

また、スイッチSW1に用いることができるトランジスタの導電膜512Bまたは配線等を第2の導電膜に用いることができる。

【0304】

<画素回路530(i, j)>

画素回路530(i, j)は、信号線S1(j)、信号線S2(j)、走査線G1(i)、走査線G2(i)、配線CSCOMおよび配線AN0と電気的に接続される(図10参照)。

50

## 【0305】

画素回路 530 (i, j + 1) は、信号線 S1 (j + 1)、信号線 S2 (j + 1)、走査線 G1 (i)、走査線 G2 (i)、配線 CS COM および配線 ANO と電気的に接続される。

## 【0306】

なお、信号線 S2 (j) に供給する信号に用いる電圧が、信号線 S1 (j + 1) に供給する信号に用いる電圧と異なる場合、信号線 S1 (j + 1) を信号線 S2 (j) から離して配置する。具体的には、信号線 S2 (j + 1) を信号線 S2 (j) に隣接するように配置する。

## 【0307】

画素回路 530 (i, j) は、スイッチ SW1、容量素子 C1、スイッチ SW2、トランジスタ M および容量素子 C2 を含む。

## 【0308】

例えば、走査線 G1 (i) と電気的に接続されるゲート電極と、信号線 S1 (j) と電気的に接続される第 1 の電極と、を有するトランジスタを、スイッチ SW1 に用いることができる。

## 【0309】

容量素子 C1 は、スイッチ SW1 に用いるトランジスタの第 2 の電極に電気的に接続される第 1 の電極と、配線 CS COM に電気的に接続される第 2 の電極と、を有する。

## 【0310】

例えば、走査線 G2 (i) と電気的に接続されるゲート電極と、信号線 S2 (j) と電気的に接続される第 1 の電極と、を有するトランジスタを、スイッチ SW2 に用いることができる。

## 【0311】

トランジスタ M は、スイッチ SW2 に用いるトランジスタの第 2 の電極に電気的に接続されるゲート電極と、配線 ANO と電気的に接続される第 1 の電極と、を有する。

## 【0312】

なお、半導体膜をゲート電極との間に挟むように設けられた導電膜を備えるトランジスタを、トランジスタ M に用いることができる。例えば、トランジスタ M の第 1 の電極と同じ電位を供給することができる配線と電気的に接続される導電膜を用いることができる。

## 【0313】

容量素子 C2 は、スイッチ SW2 に用いるトランジスタの第 2 の電極に電気的に接続される第 1 の電極と、トランジスタ M の第 1 の電極に電気的に接続される第 2 の電極と、を有する。

## 【0314】

なお、第 1 の表示素子 750 (i, j) の第 1 の電極をスイッチ SW1 に用いるトランジスタの第 2 の電極と電気的に接続し、第 1 の表示素子 750 (i, j) の第 2 の電極を配線 V COM 1 と電気的に接続する。これにより、第 1 の表示素子 750 (i, j) を駆動することができる。

## 【0315】

また、第 2 の表示素子 550 (i, j) の第 1 の電極をトランジスタ M の第 2 の電極と電気的に接続し、第 2 の表示素子 550 (i, j) の第 2 の電極を配線 V COM 2 と電気的に接続する。これにより、第 2 の表示素子 550 (i, j) を駆動することができる。

## 【0316】

<スイッチ SW1、スイッチ SW2、トランジスタ M、トランジスタ MD >

例えば、ボトムゲート型またはトップゲート型等のトランジスタをスイッチ SW1、スイッチ SW2、トランジスタ M、トランジスタ MD 等に用いることができる。

## 【0317】

例えば、14族の元素を含む半導体を半導体膜に用いるトランジスタを利用することができる。具体的には、シリコンを含む半導体を半導体膜に用いることができる。例えば、单

10

20

30

40

50

結晶シリコン、ポリシリコン、微結晶シリコンまたはアモルファスシリコンなどを半導体膜に用いたトランジスタを用いることができる。

【0318】

例えば、酸化物半導体を半導体膜に用いるトランジスタを利用することができる。具体的には、インジウムを含む酸化物半導体またはインジウムとガリウムと亜鉛を含む酸化物半導体を半導体膜に用いることができる。

【0319】

一例を挙げれば、アモルファスシリコンを半導体膜に用いたトランジスタと比較して、オフ状態におけるリーク電流が小さいトランジスタをスイッチSW1、スイッチSW2、トランジスタM、トランジスタMD等に用いることができる。具体的には、酸化物半導体を半導体膜508に用いたトランジスタをスイッチSW1、スイッチSW2、トランジスタM、トランジスタMD等に用いることができる。

10

【0320】

これにより、アモルファスシリコンを半導体膜に用いたトランジスタを利用する画素回路と比較して、画素回路が画像信号を保持することができる時間を長くすることができる。具体的には、フリッカーの発生を抑制しながら、選択信号を30Hz未満、好ましくは1Hz未満より好ましくは一分に一回未満の頻度で供給することができる。その結果、情報処理装置の使用者に蓄積する疲労を低減することができる。また、駆動に伴う消費電力を低減することができる。

【0321】

20

スイッチSW1に用いることができるトランジスタは、半導体膜508および半導体膜508と重なる領域を備える導電膜504を備える(図19(B)参照)。また、スイッチSW1に用いることができるトランジスタは、導電膜512Aおよび導電膜512Bを備える。

【0322】

なお、導電膜504はゲート電極の機能を備え、絶縁膜506はゲート絶縁膜の機能を備える。また、導電膜512Aはソース電極の機能またはドレイン電極の機能の一方を備え、導電膜512Bはソース電極の機能またはドレイン電極の機能の他方を備える。

【0323】

30

また、導電膜504との間に半導体膜508を挟むように設けられた導電膜524を備えるトランジスタを、トランジスタMに用いることができる(図19(C)参照)。

【0324】

タンタルおよび窒素を含む厚さ10nmの膜と、銅を含む厚さ300nmの膜と、をこの順で積層した導電膜を導電膜504に用いることができる。

【0325】

シリコンおよび窒素を含む厚さ400nmの膜と、シリコン、酸素および窒素を含む厚さ200nmの膜と、を積層した材料を絶縁膜506に用いることができる。

【0326】

インジウム、ガリウムおよび亜鉛を含む厚さ25nmの膜を、半導体膜508に用いることができる。

40

【0327】

タンゲステンを含む厚さ50nmの膜と、アルミニウムを含む厚さ400nmの膜と、チタンを含む厚さ100nmの膜と、をこの順で積層した導電膜を、導電膜512Aまたは導電膜512Bに用いることができる。

【0328】

<第1の表示素子750(i, j)>

例えば、光の反射または透過を制御する機能を備える表示素子を、第1の表示素子750(i, j)等に用いることができる。例えば、液晶素子と偏光板を組み合わせた構成またはシャッター方式のMEMS表示素子等を用いることができる。具体的には、反射型の表示素子を用いることにより、表示パネルの消費電力を抑制することができる。例えば、反

50

射型の液晶表示素子を第1の表示素子750に用いることができる。

【0329】

IPS (In-Plane-Switching)モード、TN (Twisted Nematic)モード、FFS (Fringe Field Switching)モード、ASM (Axially Symmetric aligned Micro-cell)モード、OCB (Optically Compensated Birefringence)モード、FLC (Ferroelectric Liquid Crystal)モード、AFLC (AntiFerroelectric Liquid Crystal)モードなどの駆動方法を用いて駆動することができる液晶素子を用いることができる。

10

【0330】

また、例えば垂直配向 (VA) モード、具体的には、MVA (Multi-Domain Vertical Alignment) モード、PVA (Patterned Vertical Alignment) モード、ECB (Electrically Controlled Birefringence) モード、CPA (Continuous Pinwheel Alignment) モード、ASV (Advanced Super-View) モードなどの駆動方法を用いて駆動することができる液晶素子を用いることができる。

【0331】

例えば、サーモトロピック液晶、低分子液晶、高分子液晶、高分子分散型液晶、強誘電性液晶、反強誘電性液晶等を用いることができる。または、コレステリック相、スメクチック相、キュービック相、カイラルネマチック相、等方相等を示す液晶材料を用いることができる。または、ブルー相を示す液晶材料を用いることができる。

20

【0332】

<第1の電極751(i, j)>

例えば、配線等に用いる材料を第1の電極751(i, j)に用いることができる。具体的には、反射膜を第1の電極751(i, j)に用いることができる。

【0333】

<反射膜>

例えば、可視光を反射する材料を反射膜に用いることができる。具体的には、銀を含む材料を反射膜に用いることができる。例えば、銀およびパラジウム等を含む材料または銀および銅等を含む材料を反射膜に用いることができる。

30

【0334】

反射膜は、例えば、液晶材料を含む層753を透過してくる光を反射する。これにより、第1の表示素子750を反射型の液晶素子にすることができる。また、例えば、表面に凹凸を備える材料を、反射膜に用いることができる。これにより、入射する光をさまざまな方向に反射して、白色の表示をすることができる。

【0335】

なお、第1の電極751(i, j)を反射膜に用いる構成に限られない。例えば、液晶材料を含む層753と第1の電極751(i, j)の間に反射膜を配設する構成を用いることができる。または、反射膜と液晶材料を含む層753の間に透光性を有する第1の電極751(i, j)を配置する構成を用いることができる。

40

【0336】

<開口部751H>

非開口部の総面積に対する開口部751Hの総面積の比の値が大きすぎると、第1の表示素子750(i, j)を用いた表示が暗くなってしまう。また、非開口部の総面積に対する開口部751Hの総面積の比の値が小さすぎると、第2の表示素子550(i, j)を用いた表示が暗くなってしまう。

【0337】

また、反射膜に設ける開口部751Hの面積が小さすぎると、第2の表示素子550が射

50

出する光から取り出せる光の効率が低下してしまう。

【0338】

多角形、四角形、橢円形、円形または十字等の形状を開口部 751H の形状に用いることができる。また、細長い筋状、スリット状、市松模様状の形状を開口部 751H の形状に用いることができる。また、開口部 751H を隣接する画素に寄せて配置してもよい。好みしくは、開口部 751H を同じ色を表示する機能を備える他の画素に寄せて配置する。これにより、第 2 の表示素子 550 が射出する光が隣接する画素に配置された着色膜に入射してしまう現象（クロストークともいう）を抑制できる。

【0339】

<第 2 の電極 752>

10

例えば、可視光について透光性を有し且つ導電性を備える材料を、第 2 の電極 752 に用いることができる。

【0340】

例えば、導電性酸化物、光が透過する程度に薄い金属膜または金属ナノワイヤーを第 2 の電極 752 に用いることができる。

【0341】

具体的には、インジウムを含む導電性酸化物を第 2 の電極 752 に用いることができる。または、厚さ 1 nm 以上 10 nm 以下の金属薄膜を第 2 の電極 752 に用いることができる。または、銀を含む金属ナノワイヤーを第 2 の電極 752 に用いることができる。

【0342】

具体的には、酸化インジウム、インジウム錫酸化物、インジウム亜鉛酸化物、酸化亜鉛、ガリウムを添加した酸化亜鉛、アルミニウムを添加した酸化亜鉛などを、第 2 の電極 752 に用いることができる。

【0343】

<配向膜 AF1、配向膜 AF2>

例えば、ポリイミド等を含む材料を配向膜 AF1 または配向膜 AF2 に用いることができる。具体的には、所定の方向に配向するようにラビング処理または光配向技術を用いて形成された材料を用いることができる。

【0344】

例えば、可溶性のポリイミドを含む膜を配向膜 AF1 または配向膜 AF2 に用いることができる。

30

【0345】

<着色膜 CF1>

所定の色の光を透過する材料を着色膜 CF1 に用いることができる。これにより、着色膜 CF1 を例えばカラーフィルターに用いることができる。

【0346】

例えば、青色の光を透過する材料、緑色の光を透過する材料、赤色の光を透過する材料、黄色の光を透過する材料または白色の光を透過する材料などを着色膜 CF1 に用いることができる。

【0347】

<遮光膜 BM>

40

光の透過を妨げる材料を遮光膜 BM に用いることができる。これにより、遮光膜 BM を例えばブラックマトリクスに用いることができる。

【0348】

<絶縁膜 771>

例えば、ポリイミド、エポキシ樹脂、アクリル樹脂等を絶縁膜 771 に用いることができる。

【0349】

<機能膜 770P>

例えば、偏光板、位相差板、拡散フィルム、反射防止膜または集光フィルム等を機能膜 7

50

70Pに用いることができる。または、2色性色素を含む偏光板を機能膜770Pに用いることができる。

【0350】

また、ゴミの付着を抑制する帯電防止膜、汚れを付着しにくくする撥水性の膜、使用に伴う傷の発生を抑制するハードコート膜などを、機能膜770Pに用いることができる。

【0351】

<第2の表示素子550(i, j)>

例えば、発光素子を第2の表示素子550(i, j)に用いることができる。具体的には、有機エレクトロルミネッセンス素子、無機エレクトロルミネッセンス素子または発光ダイオードなどを、第2の表示素子550(i, j)に用いることができる。

10

【0352】

例えば、青色の光を射出するように積層された積層体、緑色の光を射出するように積層された積層体または赤色の光を射出するように積層された積層体等を、発光性の有機化合物を含む層553(j)に用いることができる。

【0353】

例えば、信号線S1(j)に沿って列方向に長い帯状の積層体を、発光性の有機化合物を含む層553(j)に用いることができる。また、発光性の有機化合物を含む層553(j)とは異なる色の光を射出する信号線S1(j+1)に沿って列方向に長い帯状の積層体を、発光性の有機化合物を含む層553(j+1)に用いることができる。

20

【0354】

また、例えば、白色の光を射出するように積層された積層体を、発光性の有機化合物を含む層553(j)および発光性の有機化合物を含む層553(j+1)に用いることができる。具体的には、青色の光を射出する蛍光材料を含む発光性の有機化合物を含む層と、緑色および赤色の光を射出する蛍光材料以外の材料を含む層または黄色の光を射出する蛍光材料以外の材料を含む層と、を積層した積層体を、発光性の有機化合物を含む層553(j)および発光性の有機化合物を含む層553(j+1)に用いることができる。

【0355】

例えば、配線等に用いることができる材料を第3の電極551(i, j)または第4の電極552に用いることができる。

【0356】

例えば、配線等に用いることができる材料から選択された、可視光について透光性を有する材料を、第3の電極551(i, j)に用いることができる。

30

【0357】

具体的には、導電性酸化物またはインジウムを含む導電性酸化物、酸化インジウム、インジウム錫酸化物、インジウム亜鉛酸化物、酸化亜鉛、ガリウムを添加した酸化亜鉛などを、第3の電極551(i, j)に用いることができる。または、光が透過する程度に薄い金属膜を第3の電極551(i, j)に用いることができる。

【0358】

例えば、配線等に用いることができる材料から選択された可視光について反射性を有する材料を、第4の電極552に用いることができる。

40

【0359】

<駆動回路GD>

シフトレジスタ等のさまざまな順序回路等を駆動回路GDに用いることができる。例えば、トランジスタMD、容量素子等を駆動回路GDに用いることができる。具体的には、トランジスタMと同一の工程で形成することができる半導体膜を備えるトランジスタを用いることができる。

【0360】

または、スイッチSW1に用いることができるトランジスタと異なる構成をトランジスタMDに用いることができる。具体的には、導電膜524を有するトランジスタをトランジスタMDに用いることができる(図19(C)参照)。

50

## 【0361】

導電膜504との間に半導体膜508を挟むように、導電膜524を配設し、導電膜524および半導体膜508の間に絶縁膜516を配設し、半導体膜508および導電膜504の間に絶縁膜506を配設する。例えば、導電膜504と同じ電位を供給する配線に導電膜524を電気的に接続する。

## 【0362】

なお、トランジスタMと同一の構成を、トランジスタMDに用いることができる。

## 【0363】

<駆動回路SD>

例えば、集積回路を駆動回路SDに用いることができる。具体的には、シリコン基板上に形成された集積回路を駆動回路SDに用いることができる。 10

## 【0364】

例えば、COG (Chip on glass) 法を用いて、画素回路530 (i, j) と電気的に接続されるパッドに駆動回路SDを実装することができる。具体的には、異方性導電膜を用いて、パッドに集積回路を実装できる。

## 【0365】

なお、パッドは、端子519Bまたは端子519Cと同一の工程で形成することができる。

## 【0366】

<表示パネルの構成例2.>

20

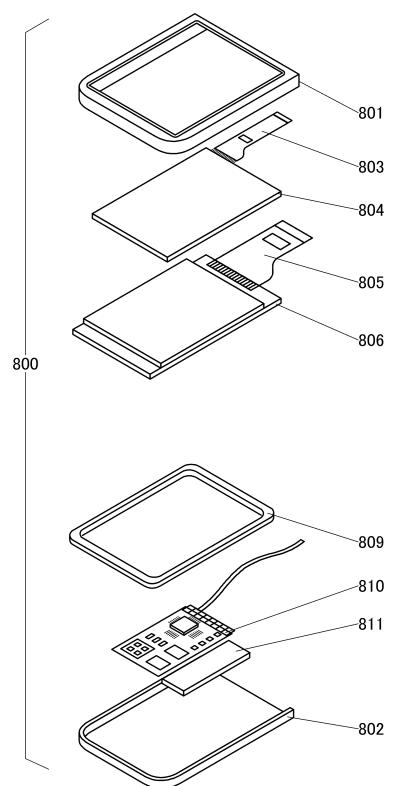

図20は本発明の一態様の表示パネル700Bの構成を説明する図である。図20(A)は図9(A)の切断線X1-X2、X3-X4、X5-X6、X7-X8、X9-X10、X11-X12における断面図である。図20(B)は表示パネルの一部の構成を説明する断面図である。

## 【0367】

なお、表示パネル700Bは、ボトムゲート型のトランジスタに換えてトップゲート型のトランジスタを有する点が、図19を参照しながら説明する表示パネル700とは異なる。ここでは、上記の説明と同様の構成を用いることができる部分について上記の説明を援用し、異なる部分について詳細に説明する。

## 【0368】

30

<スイッチSW1B、トランジスタMB、トランジスタMDB>

スイッチSW1Bに用いることができるトランジスタ、トランジスタMBおよびトランジスタMDBは、絶縁膜501Cと重なる領域を備える導電膜504と、絶縁膜501Cおよび導電膜504の間に配設される領域を備える半導体膜508と、を備える。なお、導電膜504はゲート電極の機能を備える(図20(B)参照)。

## 【0369】

半導体膜508は、導電膜504と重ならない第1の領域508Aおよび第2の領域508Bと、第1の領域508Aおよび第2の領域508Bの間に導電膜504と重なる第3の領域508Cと、を備える。

## 【0370】

40

トランジスタMDBは絶縁膜506を、第3の領域508Cおよび導電膜504の間に備える。なお、絶縁膜506はゲート絶縁膜の機能を備える。

## 【0371】

第1の領域508Aおよび第2の領域508Bは、第3の領域508Cに比べて抵抗率が低く、ソース領域の機能またはドレイン領域の機能を備える。

## 【0372】

なお、例えば本実施の形態の最後において詳細に説明する酸化物半導体の抵抗率を制御する方法を用いて、第1の領域508Aおよび第2の領域508Bを半導体膜508に形成することができる。具体的には、希ガスを含むガスを用いるプラズマ処理を適用することができる。

50

## 【0373】

また、例えば、導電膜504をマスクに用いることができる。これにより、第3の領域508Cの一部の形状を、導電膜504の端部の形状に自己整合させることができる。

## 【0374】

トランジスタMDBは、第1の領域508Aと接する導電膜512Aと、第2の領域508Bと接する導電膜512Bと、を備える。導電膜512Aおよび導電膜512Bは、ソース電極またはドレイン電極の機能を備える。

## 【0375】

トランジスタMDBと同一の工程で形成することができるトランジスタをトランジスタMBに用いることができる。

10

## 【0376】

<酸化物半導体の抵抗率の制御方法>

酸化物半導体膜の抵抗率を制御する方法について説明する。

## 【0377】

所定の抵抗率を備える酸化物半導体膜を、半導体膜508または導電膜524等に用いることができる。

## 【0378】

例えば、酸化物半導体膜に含まれる水素、水等の不純物の濃度及び/又は膜中の酸素欠損を制御する方法を、酸化物半導体の抵抗率を制御する方法に用いることができる。

## 【0379】

具体的には、プラズマ処理を水素、水等の不純物濃度及び/又は膜中の酸素欠損を増加または低減する方法に用いることができる。

20

## 【0380】

具体的には、希ガス(He、Ne、Ar、Kr、Xe)、水素、ボロン、リン及び窒素の中から選ばれた一種以上を含むガスを用いて行うプラズマ処理を適用できる。例えば、Ar雰囲気下でのプラズマ処理、Arと水素の混合ガス雰囲気下でのプラズマ処理、アンモニア雰囲気下でのプラズマ処理、Arとアンモニアの混合ガス雰囲気下でのプラズマ処理、または窒素雰囲気下でのプラズマ処理などを適用できる。これにより、キャリア密度が高く、抵抗率が低い酸化物半導体膜にすることができる。

## 【0381】

または、イオン注入法、イオンドーピング法またはプラズマイマージョンイオンインプランテーション法などを用いて、水素、ボロン、リンまたは窒素を酸化物半導体膜に注入して、抵抗率が低い酸化物半導体膜にすることができる。

30

## 【0382】

または、水素を含む絶縁膜を酸化物半導体膜に接して形成し、絶縁膜から酸化物半導体膜に水素を拡散させる方法を用いることができる。これにより、酸化物半導体膜のキャリア密度を高め、抵抗率を低くすることができる。

## 【0383】

例えば、膜中の含有水素濃度が $1 \times 10^{22} \text{ atoms/cm}^3$ 以上の絶縁膜を酸化物半導体膜に接して形成することで、効果的に水素を酸化物半導体膜に含有させることができる。具体的には、窒化シリコン膜を酸化物半導体膜に接して形成する絶縁膜に用いることができる。

40

## 【0384】

酸化物半導体膜に含まれる水素は、金属原子と結合する酸素と反応して水になると共に、酸素が脱離した格子(または酸素が脱離した部分)に酸素欠損を形成する。該酸素欠損に水素が入ることで、キャリアである電子が生成される場合がある。また、水素の一部が金属原子と結合する酸素と結合することで、キャリアである電子を生成する場合がある。これにより、キャリア密度が高く、抵抗率が低い酸化物半導体膜にすることができる。

## 【0385】

具体的には、二次イオン質量分析法(SIMS: Secondary Ion Mass

50

Spectrometry)により得られる水素濃度が、 $8 \times 10^{19}$  atoms/cm<sup>3</sup>以上、好ましくは $1 \times 10^{20}$  atoms/cm<sup>3</sup>以上、より好ましくは $5 \times 10^{20}$  atoms/cm<sup>3</sup>以上である酸化物半導体を導電膜524に好適に用いることができる。

【0386】

一方、抵抗率の高い酸化物半導体をトランジスタのチャネルが形成される半導体膜に用いることができる。具体的には半導体膜508に好適に用いることができる。

【0387】

例えば、酸素を含む絶縁膜、別言すると、酸素を放出することが可能な絶縁膜を酸化物半導体に接して形成し、絶縁膜から酸化物半導体膜に酸素を供給させて、膜中または界面の酸素欠損を補填することができる。これにより、抵抗率が高い酸化物半導体膜にことができる。

10

【0388】

例えば、酸化シリコン膜または酸化窒化シリコン膜を、酸素を放出することが可能な絶縁膜に用いることができる。

【0389】

酸素欠損が補填され、水素濃度が低減された酸化物半導体膜は、高純度真性化、又は実質的に高純度真性化された酸化物半導体膜といえる。ここで、実質的に真性とは、酸化物半導体膜のキャリア密度が、 $8 \times 10^{11}$  / cm<sup>3</sup>未満、好ましくは $1 \times 10^{11}$  / cm<sup>3</sup>未満、さらに好ましくは $1 \times 10^{10}$  / cm<sup>3</sup>未満であることを指す。高純度真性または実質的に高純度真性である酸化物半導体膜は、キャリア発生源が少ないため、キャリア密度を低くすることができる。また、高純度真性または実質的に高純度真性である酸化物半導体膜は、欠陥準位密度が低いため、トラップ準位密度を低減することができる。

20

【0390】

また、高純度真性または実質的に高純度真性である酸化物半導体膜を備えるトランジスタは、オフ電流が著しく小さく、チャネル幅が $1 \times 10^6$  μmでチャネル長Lが $10$  μmの素子であっても、ソース電極とドレイン電極間の電圧(ドレイン電圧)が1Vから10Vの範囲において、オフ電流が、半導体パラメータアナライザの測定限界以下、すなわち $1 \times 10^{-13}$  A以下という特性を備えることができる。

【0391】

上述した高純度真性または実質的に高純度真性である酸化物半導体膜をチャネル領域に用いるトランジスタは、電気特性の変動が小さく、信頼性の高いトランジスタとなる。

30

【0392】

具体的には、二次イオン質量分析法(SIMS: Secondary Ion Mass Spectrometry)により得られる水素濃度が、 $2 \times 10^{20}$  atoms/cm<sup>3</sup>以下、好ましくは $5 \times 10^{19}$  atoms/cm<sup>3</sup>以下、より好ましくは $1 \times 10^{19}$  atoms/cm<sup>3</sup>以下、 $5 \times 10^{18}$  atoms/cm<sup>3</sup>未満、好ましくは $1 \times 10^{18}$  atoms/cm<sup>3</sup>以下、より好ましくは $5 \times 10^{17}$  atoms/cm<sup>3</sup>以下、さらに好ましくは $1 \times 10^{16}$  atoms/cm<sup>3</sup>以下である酸化物半導体を、トランジスタのチャネルが形成される半導体に好適に用いることができる。

40

【0393】

なお、半導体膜508よりも水素濃度及び/又は酸素欠損量が多く、抵抗率が低い酸化物半導体膜を、導電膜524に用いる。

【0394】

また、半導体膜508に含まれる水素濃度の2倍以上、好ましくは10倍以上の濃度の水素を含む膜を、導電膜524に用いることができる。

【0395】

また、半導体膜508の抵抗率の $1 \times 10^{-8}$ 倍以上 $1 \times 10^{-1}$ 倍未満の抵抗率を備える膜を、導電膜524に用いることができる。

【0396】

10

20

30

40

50

具体的には、 $1 \times 10^{-3}$  cm以上 $1 \times 10^{-4}$  cm未満、好ましくは、 $1 \times 10^{-3}$  cm以上 $1 \times 10^{-1}$  cm未満である膜を、導電膜524に用いることができる。

#### 【0397】

なお、本実施の形態は、本明細書で示す他の実施の形態と適宜組み合わせができる。

#### 【0398】

##### (実施の形態5)

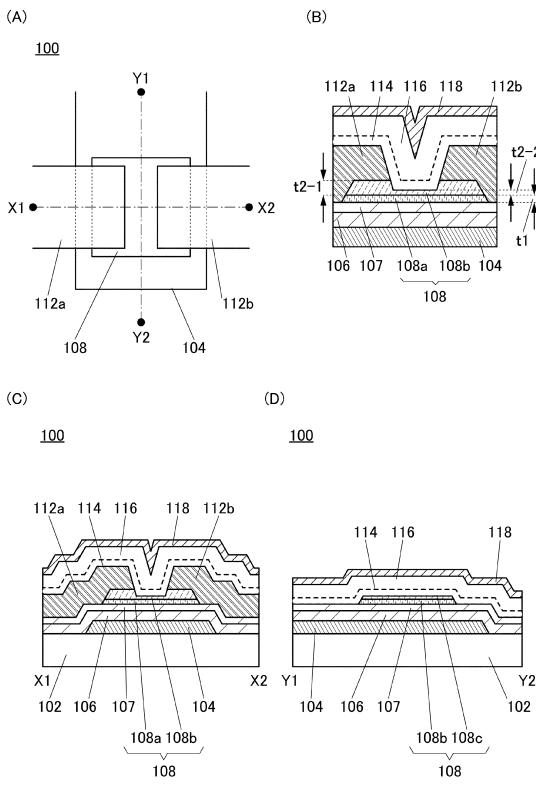

本実施の形態では、本発明の一態様の表示パネルに用いることができるトランジスタの構成について、図12を参照しながら説明する。

#### 【0399】

##### <半導体装置の構成例>

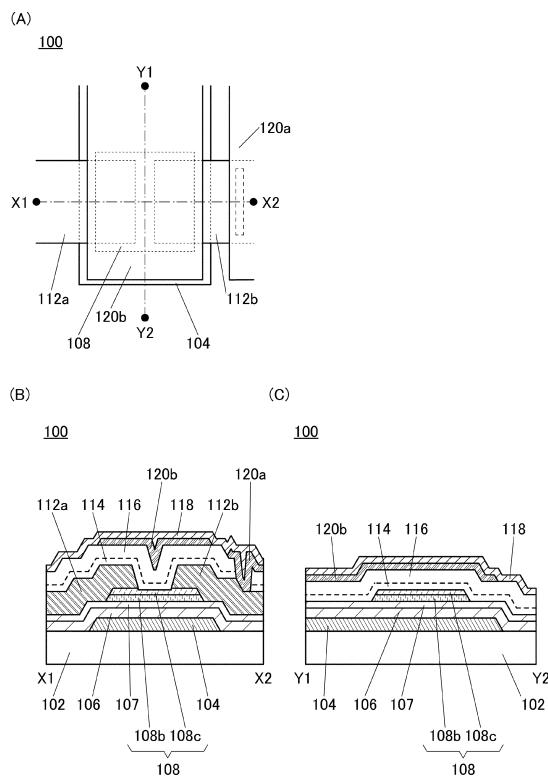

図12(A)は、トランジスタ100の上面図であり、図12(C)は、図12(A)に示す切断線X1-X2間ににおける切断面の断面図に相当し、図12(D)は、図12(A)に示す切断線Y1-Y2間ににおける切断面の断面図に相当する。なお、図12(A)において、煩雑になることを避けるため、トランジスタ100の構成要素の一部(ゲート絶縁膜として機能する絶縁膜等)を省略して図示している。また、切断線X1-X2方向をチャネル長方向、切断線Y1-Y2方向をチャネル幅方向と呼称する場合がある。なお、トランジスタの上面図においては、以降の図面においても図12(A)と同様に、構成要素の一部を省略して図示する場合がある。

#### 【0400】

なお、トランジスタ100を実施の形態4において説明する表示パネル700等に用いることができる。

#### 【0401】

例えば、トランジスタ100をスイッチSW1に用いる場合は、基板102を絶縁膜501Cに、導電膜104を導電膜504に、絶縁膜106および絶縁膜107が積層された積層膜を絶縁膜506に、酸化物半導体膜108を半導体膜508に、導電膜112aを導電膜512Aに、導電膜112bを導電膜512Bに、絶縁膜114および絶縁膜116が積層された積層膜を絶縁膜516に、絶縁膜118を絶縁膜518に、それぞれ読み替えることができる。

#### 【0402】

トランジスタ100は、基板102上のゲート電極として機能する導電膜104と、基板102及び導電膜104上の絶縁膜106と、絶縁膜106上の絶縁膜107と、絶縁膜107上の酸化物半導体膜108と、酸化物半導体膜108に電気的に接続されるソース電極として機能する導電膜112aと、酸化物半導体膜108に電気的に接続されるドレイン電極として機能する導電膜112bと、を有する。また、トランジスタ100上、より詳しくは、導電膜112a、112b及び酸化物半導体膜108上には絶縁膜114、116、及び絶縁膜118が設けられる。絶縁膜114、116、118は、トランジスタ100の保護絶縁膜としての機能を有する。

#### 【0403】

また、酸化物半導体膜108は、ゲート電極として機能する導電膜104側の第1の酸化物半導体膜108aと、第1の酸化物半導体膜108a上の第2の酸化物半導体膜108bと、を有する。また、絶縁膜106及び絶縁膜107は、トランジスタ100のゲート絶縁膜としての機能を有する。

#### 【0404】

酸化物半導体膜108としては、In-M(Mは、Ti、Ga、Sn、Y、Zr、La、Ce、Nd、またはHfを表す)酸化物、In-M-Zn酸化物を用いることができる。とくに、酸化物半導体膜108としては、In-M-Zn酸化物を用いると好ましい。

#### 【0405】

また、第1の酸化物半導体膜108aは、Inの原子数比がMの原子数比より多い第1の領域を有する。また、第2の酸化物半導体膜108bは、第1の酸化物半導体膜108a

10

20

30

40

50

よりも  $I_n$  の原子数比が少ない第 2 の領域を有する。また、第 2 の領域は、第 1 の領域よりも薄い部分を有する。

【 0 4 0 6 】

第 1 の酸化物半導体膜 108a に  $I_n$  の原子数比が M の原子数比より多い第 1 の領域を有することで、トランジスタ 100 の電界効果移動度（単に移動度、または  $\mu_{FE}$  という場合がある）を高くすることができる。具体的には、トランジスタ 100 の電界効果移動度が  $10 \text{ cm}^2 / \text{Vs}$  を超えることが可能となる。

【 0 4 0 7 】

例えば、上記の電界効果移動度が高いトランジスタを、ゲート信号を生成するゲートドライバ（とくに、ゲートドライバが有するシフトレジスタの出力端子に接続されるデマルチプレクサ）に用いることで、額縁幅の狭い（狭額縁ともいう）半導体装置または表示装置を提供することができる。

【 0 4 0 8 】

一方で、 $I_n$  の原子数比が M の原子数比より多い第 1 の領域を有する第 1 の酸化物半導体膜 108a とすることで、光照射時にトランジスタ 100 の電気特性が変動しやすくなる。しかしながら、本発明の一態様の半導体装置においては、第 1 の酸化物半導体膜 108a 上に第 2 の酸化物半導体膜 108b が形成されている。また、第 2 の酸化物半導体膜 108b のチャネル領域の膜厚が第 1 の酸化物半導体膜 108a の膜厚よりも小さい。

【 0 4 0 9 】

また、第 2 の酸化物半導体膜 108b は、第 1 の酸化物半導体膜 108a よりも  $I_n$  の原子数比が少ない第 2 の領域を有するため、第 1 の酸化物半導体膜 108a よりも  $E_g$  が大きくなる。したがって、第 1 の酸化物半導体膜 108a と、第 2 の酸化物半導体膜 108b との積層構造である酸化物半導体膜 108 は、光負バイアストレス試験による耐性が高くなる。

【 0 4 1 0 】

上記構成の酸化物半導体膜とすることで、光照射時における酸化物半導体膜 108 の光吸収量を低減させることができる。したがって、光照射時におけるトランジスタ 100 の電気特性の変動を抑制することができる。また、本発明の一態様の半導体装置においては、絶縁膜 114 または絶縁膜 116 中に過剰の酸素を含有する構成のため、光照射におけるトランジスタ 100 の電気特性の変動をさらに、抑制することができる。

【 0 4 1 1 】

ここで、酸化物半導体膜 108 について、図 12 (B) を用いて詳細に説明する。

【 0 4 1 2 】

図 12 (B) は、図 12 (C) を用いて示すトランジスタ 100 の断面の、酸化物半導体膜 108 の近傍を拡大した断面図である。

【 0 4 1 3 】

図 12 (B) において、第 1 の酸化物半導体膜 108a の膜厚を  $t_1$  として、第 2 の酸化物半導体膜 108b の膜厚を  $t_{2-1}$ 、及び  $t_{2-2}$  として、それぞれ示している。第 1 の酸化物半導体膜 108a 上には、第 2 の酸化物半導体膜 108b が設けられているため、導電膜 112a、112b の形成時において、第 1 の酸化物半導体膜 108a がエッチングガスまたはエッチング溶液等に曝されることがない。したがって、第 1 の酸化物半導体膜 108a においては、膜減りがない、または極めて少ない。一方で、第 2 の酸化物半導体膜 108b においては、導電膜 112a、112b の形成時において、第 2 の酸化物半導体膜 108b の導電膜 112a、112b と重ならない部分がエッチングされ、凹部が形成される。すなわち、第 2 の酸化物半導体膜 108b の導電膜 112a、112b と重なる領域の膜厚が  $t_{2-1}$  となり、第 2 の酸化物半導体膜 108b の導電膜 112a、112b と重ならない領域の膜厚が  $t_{2-2}$  となる。

【 0 4 1 4 】

第 1 の酸化物半導体膜 108a と第 2 の酸化物半導体膜 108b の膜厚の関係は、 $t_{2-1} > t_1 > t_{2-2}$  となると好ましい。このような膜厚の関係とすることによって、高い

10

20

30

40

50

電界効果移動度を有し、且つ光照射時における、しきい値電圧の変動量が少ないトランジスタとすることが可能となる。

【0415】

また、トランジスタ100が有する酸化物半導体膜108は、酸素欠損が形成されるとキャリアである電子が生じ、ノーマリーオン特性になりやすい。したがって、酸化物半導体膜108中の酸素欠損、とくに第1の酸化物半導体膜108a中の酸素欠損を減らすことが、安定したトランジスタ特性を得る上でも重要となる。そこで、本発明の一態様のトランジスタの構成においては、酸化物半導体膜108上の絶縁膜、ここでは、酸化物半導体膜108上の絶縁膜114及び/又は絶縁膜116に過剰な酸素を導入することで、絶縁膜114及び/又は絶縁膜116から酸化物半導体膜108中に酸素を移動させ、酸化物半導体膜108中、とくに第1の酸化物半導体膜108a中の酸素欠損を補填することを特徴とする。

【0416】

なお、絶縁膜114、116としては、化学量論的組成よりも過剰に酸素を含有する領域（酸素過剰領域）を有することがより好ましい。別言すると、絶縁膜114、116は、酸素を放出することが可能な絶縁膜である。なお、絶縁膜114、116に酸素過剰領域を設けるには、例えば、成膜後の絶縁膜114、116に酸素を導入して、酸素過剰領域を形成する。酸素の導入方法としては、イオン注入法、イオンドーピング法、プラズマイマージョンイオン注入法、プラズマ処理等を用いることができる。

【0417】

また、第1の酸化物半導体膜108a中の酸素欠損を補填するためには、第2の酸化物半導体膜108bのチャネル領域近傍の膜厚を薄くした方が好適である。したがって、 $t_2 - 2 < t_1$ の関係を満たせばよい。例えば、第2の酸化物半導体膜108bのチャネル領域近傍の膜厚としては、好ましくは1nm以上20nm以下、さらに好ましくは、3nm以上10nm以下である。

【0418】

以下に、本実施の形態の半導体装置に含まれるその他の構成要素について、詳細に説明する。

【0419】

<基板>

基板102の材質などに大きな制限はないが、少なくとも、後の熱処理に耐えうる程度の耐熱性を有している必要がある。例えば、ガラス基板、セラミック基板、石英基板、サファイア基板等を、基板102として用いてもよい。

【0420】

また、シリコンや炭化シリコンを材料とした単結晶半導体基板、多結晶半導体基板、シリコンゲルマニウム等の化合物半導体基板、SOI基板等を適用することも可能である。

【0421】

また、これらの基板上に半導体素子または絶縁膜等が設けられたものを、基板102として用いてもよい。

【0422】

なお、基板102として、ガラス基板を用いる場合、第6世代（1500mm×1850mm）、第7世代（1870mm×2200mm）、第8世代（2200mm×2400mm）、第9世代（2400mm×2800mm）、第10世代（2950mm×3400mm）等の大面積基板を用いることで、大型の表示装置を作製することができる。

【0423】

また、基板102として、可撓性基板を用い、可撓性基板上に直接、トランジスタ100を形成してもよい。または、基板102とトランジスタ100の間に剥離層を設けてもよい。剥離層は、その上に半導体装置を一部あるいは全部完成させた後、基板102より分離し、他の基板に転載するのに用いることができる。その際、トランジスタ100は耐熱性の劣る基板や可撓性の基板にも転載できる。

10

20

30

40

50

## 【0424】

<ゲート電極、ソース電極、及びドレイン電極として機能する導電膜>

ゲート電極として機能する導電膜104、及びソース電極として機能する導電膜112a、及びドレイン電極として機能する導電膜112bとしては、クロム(Cr)、銅(Cu)、アルミニウム(Al)、金(Au)、銀(Ag)、亜鉛(Zn)、モリブデン(Mo)、タンタル(Ta)、チタン(Ti)、タンゲステン(W)、マンガン(Mn)、ニッケル(Ni)、鉄(Fe)、コバルト(Co)から選ばれた金属元素、または上述した金属元素を成分とする合金か、上述した金属元素を組み合わせた合金等を用いてそれぞれ形成することができる。

## 【0425】

10

また、導電膜104、112a、112bは、単層構造でも、二層以上の積層構造としてもよい。例えば、シリコンを含むアルミニウム膜の単層構造、アルミニウム膜上にチタン膜を積層する二層構造、窒化チタン膜上にチタン膜を積層する二層構造、窒化チタン膜上にタンゲステン膜を積層する二層構造、窒化タンタル膜または窒化タンゲステン膜上にタンゲステン膜を積層する二層構造、チタン膜と、そのチタン膜上にアルミニウム膜を積層し、さらにその上にチタン膜を形成する三層構造等がある。また、アルミニウムに、チタン、タンタル、タンゲステン、モリブデン、クロム、ネオジム、スカンジウムから選ばれた一または複数を組み合わせた合金膜、もしくは窒化膜を用いてもよい。

## 【0426】

20

また、導電膜104、112a、112bには、インジウム錫酸化物、酸化タンゲステンを含むインジウム酸化物、酸化タンゲステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、インジウム亜鉛酸化物、酸化シリコンを添加したインジウム錫酸化物等の透光性を有する導電性材料を適用することもできる。

## 【0427】

また、導電膜104、112a、112bには、Cu-X合金膜(Xは、Mn、Ni、Cr、Fe、Co、Mo、Ta、またはTi)を適用してもよい。Cu-X合金膜を用いることで、ウェットエッチングプロセスで加工できるため、製造コストを抑制することが可能となる。

## 【0428】

30

<ゲート絶縁膜として機能する絶縁膜>

トランジスタ100のゲート絶縁膜として機能する絶縁膜106、107としては、プラズマ化学気相堆積(PECVD:(Plasma Enhanced Chemical Vapor Deposition))法、スパッタリング法等により、酸化シリコン膜、酸化窒化シリコン膜、窒化酸化シリコン膜、窒化シリコン膜、酸化アルミニウム膜、酸化ハフニウム膜、酸化イットリウム膜、酸化ジルコニウム膜、酸化ガリウム膜、酸化タンタル膜、酸化マグネシウム膜、酸化ランタン膜、酸化セリウム膜および酸化ネオジム膜を一種以上含む絶縁膜を、それぞれ用いることができる。なお、絶縁膜106、107の積層構造とせずに、上述の材料から選択された単層の絶縁膜、または3層以上の絶縁膜を用いてもよい。

## 【0429】

40

また、絶縁膜106は、酸素の透過を抑制するブロッキング膜としての機能を有する。例えば、絶縁膜107、114、116及び/または酸化物半導体膜108中に過剰の酸素を供給する場合において、絶縁膜106は酸素の透過を抑制することができる。

## 【0430】

なお、トランジスタ100のチャネル領域として機能する酸化物半導体膜108と接する絶縁膜107は、酸化物絶縁膜であることが好ましく、化学量論的組成よりも過剰に酸素を含有する領域(酸素過剰領域)を有することができる。別言すると、絶縁膜107は、酸素を放出することが可能な絶縁膜である。なお、絶縁膜107に酸素過剰領域を設けるには、例えば、酸素雰囲気下にて絶縁膜107を形成すればよい。または、成膜後

50

の絶縁膜 107 に酸素を導入して、酸素過剰領域を形成してもよい。酸素の導入方法としては、イオン注入法、イオンドーピング法、プラズマイマージョンイオン注入法、プラズマ処理等を用いることができる。

#### 【0431】

また、絶縁膜 107 として、酸化ハフニウムを用いる場合、以下の効果を奏する。酸化ハフニウムは、酸化シリコンや酸化窒化シリコンと比べて比誘電率が高い。したがって、酸化シリコンを用いる場合に比べて膜厚を大きくできるため、トンネル電流によるリーク電流を小さくすることができる。すなわち、オフ電流の小さいトランジスタを実現することができる。さらに、結晶構造を有する酸化ハフニウムは、非晶質構造を有する酸化ハフニウムと比べて高い比誘電率を備える。したがって、オフ電流の小さいトランジスタとするためには、結晶構造を有する酸化ハフニウムを用いることが好ましい。結晶構造の例としては、単斜晶系や立方晶系などが挙げられる。ただし、本発明の一態様は、これらに限定されない。

#### 【0432】

なお、本実施の形態では、絶縁膜 106 として窒化シリコン膜を形成し、絶縁膜 107 として酸化シリコン膜を形成する。窒化シリコン膜は、酸化シリコン膜と比較して比誘電率が高く、酸化シリコン膜と同等の静電容量を得るのに必要な膜厚が大きいため、トランジスタ 100 のゲート絶縁膜として、窒化シリコン膜を含むことで絶縁膜を物理的に厚膜化することができる。よって、トランジスタ 100 の絶縁耐圧の低下を抑制、さらには絶縁耐圧を向上させて、トランジスタ 100 の静電破壊を抑制することができる。

#### 【0433】

##### <酸化物半導体膜>

酸化物半導体膜 108 としては、先に示す材料を用いることができる。

#### 【0434】

酸化物半導体膜 108 が  $In - M - Zn$  酸化物の場合、 $In - M - Zn$  酸化物を成膜するために用いるスパッタリングターゲットの金属元素の原子数比は、 $In - M$ 、 $Zn - M$  を満たすことが好ましい。このようなスパッタリングターゲットの金属元素の原子数比として、 $In : M : Zn = 1 : 1 : 1$ 、 $In : M : Zn = 1 : 1 : 1.2$ 、 $In : M : Zn = 2 : 1 : 3$ 、 $In : M : Zn = 3 : 1 : 2$ 、 $In : M : Zn = 4 : 2 : 4$  が好ましい。

#### 【0435】

また、酸化物半導体膜 108 が  $In - M - Zn$  酸化物の場合、スパッタリングターゲットとしては、多結晶の  $In - M - Zn$  酸化物を含むターゲットを用いると好ましい。多結晶の  $In - M - Zn$  酸化物を含むターゲットを用いることで、結晶性を有する酸化物半導体膜 108 を形成しやすくなる。なお、成膜される酸化物半導体膜 108 の原子数比はそれぞれ、誤差として上記のスパッタリングターゲットに含まれる金属元素の原子数比のプラスマイナス 40 % の変動を含む。例えば、スパッタリングターゲットとして、原子数比が  $In : Ga : Zn = 4 : 2 : 4$  を用いる場合、成膜される酸化物半導体膜 108 の原子数比は、 $In : Ga : Zn = 4 : 2 : 3$  近傍となる場合がある。

#### 【0436】

例えば、第 1 の酸化物半導体膜 108a としては、上述の  $In : M : Zn = 2 : 1 : 3$ 、 $In : M : Zn = 3 : 1 : 2$ 、 $In : M : Zn = 4 : 2 : 4$  等のスパッタリングターゲットを用いて形成すればよい。また、第 2 の酸化物半導体膜 108b としては、上述の  $In : M : Zn = 1 : 1 : 1$ 、 $In : M : Zn = 1 : 1 : 1.2$  等を用いて形成すればよい。なお、第 2 の酸化物半導体膜 108b に用いるスパッタリングターゲットの金属元素の原子数比としては、 $In - M$ 、 $Zn - M$  を満たす必要はなく、 $In - M$ 、 $Zn < M$  を満たす組成でもよい。具体的には、 $In : M : Zn = 1 : 3 : 2$  等が挙げられる。

#### 【0437】

また、酸化物半導体膜 108 は、エネルギーギャップが 2 eV 以上、好ましくは 2.5 eV 以上、より好ましくは 3 eV 以上である。このように、エネルギーギャップの広い酸化

10

20

30

40

50

物半導体を用いることで、トランジスタ100のオフ電流を低減することができる。とくに、第1の酸化物半導体膜108aには、エネルギーギャップが2eV以上、好ましくは2eV以上3.0eV以下の酸化物半導体膜を用い、第2の酸化物半導体膜108bには、エネルギーギャップが2.5eV以上3.5eV以下の酸化物半導体膜を用いると、好適である。また、第1の酸化物半導体膜108aよりも第2の酸化物半導体膜108bのエネルギーギャップが大きい方が好ましい。

#### 【0438】

また、第1の酸化物半導体膜108a、及び第2の酸化物半導体膜108bの厚さは、それぞれ3nm以上200nm以下、好ましくは3nm以上100nm以下、さらに好ましくは3nm以上50nm以下とする。なお、先に記載の膜厚の関係を満たすと好ましい。

10

#### 【0439】

また、第2の酸化物半導体膜108bとしては、キャリア密度の低い酸化物半導体膜を用いる。例えば、第2の酸化物半導体膜108bは、キャリア密度が $1 \times 10^{17} \text{ cm}^{-3}$ 以下、好ましくは $1 \times 10^{15} \text{ cm}^{-3}$ 以下、さらに好ましくは $1 \times 10^{13} \text{ cm}^{-3}$ 以下、より好ましくは $1 \times 10^{11} \text{ cm}^{-3}$ 以下とする。

#### 【0440】

なお、これらに限らず、必要とするトランジスタの半導体特性及び電気特性（電界効果移動度、しきい値電圧等）に応じて適切な組成のものを用いればよい。また、必要とするトランジスタの半導体特性を得るために、第1の酸化物半導体膜108a、及び第2の酸化物半導体膜108bのキャリア密度や不純物濃度、欠陥密度、金属元素と酸素の原子数比、原子間距離、密度等を適切なものとすることが好ましい。

20

#### 【0441】

なお、第1の酸化物半導体膜108a、及び第2の酸化物半導体膜108bとしては、それぞれ不純物濃度が低く、欠陥準位密度の低い酸化物半導体膜を用いることで、さらに優れた電気特性を有するトランジスタを作製することができ好ましい。ここでは、不純物濃度が低く、欠陥準位密度の低い（酸素欠損の少ない）ことを高純度真性または実質的に高純度真性とよぶ。高純度真性または実質的に高純度真性である酸化物半導体膜は、キャリア発生源が少ないため、キャリア密度を低くすることができる。従って、該酸化物半導体膜にチャネル領域が形成されるトランジスタは、しきい値電圧がマイナスとなる電気特性（ノーマリーオンともいう。）になることが多い。また、高純度真性または実質的に高純度真性である酸化物半導体膜は、欠陥準位密度が低いため、トラップ準位密度も低くなる場合がある。また、高純度真性または実質的に高純度真性である酸化物半導体膜は、オフ電流が著しく小さく、チャネル幅が $1 \times 10^6 \mu\text{m}$ でチャネル長Lが $10 \mu\text{m}$ の素子であっても、ソース電極とドレイン電極間の電圧（ドレイン電圧）が1Vから10Vの範囲において、オフ電流が、半導体パラメータアナライザの測定限界以下、すなわち $1 \times 10^{-13} \text{ A}$ 以下という特性を得ることができる。

30

#### 【0442】

したがって、上記高純度真性、または実質的に高純度真性の酸化物半導体膜にチャネル領域が形成されるトランジスタは、電気特性の変動が小さく、信頼性の高いトランジスタとすることができます。なお、酸化物半導体膜のトラップ準位に捕獲された電荷は、消失するまでに要する時間が長く、あたかも固定電荷のように振る舞うことがある。そのため、トラップ準位密度の高い酸化物半導体膜にチャネル領域が形成されるトランジスタは、電気特性が不安定となる場合がある。不純物としては、水素、窒素、アルカリ金属、またはアルカリ土類金属等がある。

40

#### 【0443】

酸化物半導体膜に含まれる水素は、金属原子と結合する酸素と反応して水になると共に、酸素が脱離した格子（または酸素が脱離した部分）に酸素欠損を形成する。該酸素欠損に水素が入ることで、キャリアである電子が生成される場合がある。また、水素の一部が金属原子と結合する酸素と結合して、キャリアである電子を生成することができる。従って、水素が含まれている酸化物半導体膜を用いたトランジスタはノーマリーオン特性となりや

50

すい。このため、酸化物半導体膜 108 は水素ができる限り低減されていることが好ましい。具体的には、酸化物半導体膜 108 において、S I M S 分析により得られる水素濃度を、 $2 \times 10^{20}$  atoms / cm<sup>3</sup> 以下、好ましくは $5 \times 10^{19}$  atoms / cm<sup>3</sup> 以下、より好ましくは $1 \times 10^{19}$  atoms / cm<sup>3</sup> 以下、 $5 \times 10^{18}$  atoms / cm<sup>3</sup> 以下、好ましくは $1 \times 10^{18}$  atoms / cm<sup>3</sup> 以下、より好ましくは $5 \times 10^{17}$  atoms / cm<sup>3</sup> 以下、さらに好ましくは $1 \times 10^{16}$  atoms / cm<sup>3</sup> 以下とする。

#### 【 0 4 4 4 】

また、第1酸化物半導体膜 108a において、第14族元素の一つであるシリコンや炭素が含まれると、第1の酸化物半導体膜 108a において酸素欠損が増加し、n型化してしまう。このため、第1の酸化物半導体膜 108a におけるシリコンや炭素の濃度と、第1の酸化物半導体膜 108a との界面近傍のシリコンや炭素の濃度 (S I M S 分析により得られる濃度) を、 $2 \times 10^{18}$  atoms / cm<sup>3</sup> 以下、好ましくは $2 \times 10^{17}$  atoms / cm<sup>3</sup> 以下とする。

#### 【 0 4 4 5 】

また、第1の酸化物半導体膜 108a において、S I M S 分析により得られるアルカリ金属またはアルカリ土類金属の濃度を、 $1 \times 10^{18}$  atoms / cm<sup>3</sup> 以下、好ましくは $2 \times 10^{16}$  atoms / cm<sup>3</sup> 以下にする。アルカリ金属及びアルカリ土類金属は、酸化物半導体と結合するとキャリアを生成する場合があり、トランジスタのオフ電流が増大してしまうことがある。このため、第1の酸化物半導体膜 108a のアルカリ金属またはアルカリ土類金属の濃度を低減することが好ましい。

#### 【 0 4 4 6 】

また、第1の酸化物半導体膜 108a に窒素が含まれていると、キャリアである電子が生じ、キャリア密度が増加し、n型化しやすい。この結果、窒素が含まれている酸化物半導体膜を用いたトランジスタはノーマリーオン特性となりやすい。従って、該酸化物半導体膜において、窒素はできる限り低減されていることが好ましい、例えば、S I M S 分析により得られる窒素濃度は、 $5 \times 10^{18}$  atoms / cm<sup>3</sup> 以下にすることが好ましい。

#### 【 0 4 4 7 】

また、第1の酸化物半導体膜 108a、及び第2の酸化物半導体膜 108b は、それぞれ非単結晶構造でもよい。非単結晶構造は、例えば、C A A C - O S (C A x i s A l i g n e d C r y s t a l l i n e O x i d e S e m i c o n d u c t o r)、多結晶構造、微結晶構造、または非晶質構造を含む。

#### 【 0 4 4 8 】

＜トランジスタの保護絶縁膜として機能する絶縁膜＞

絶縁膜 114、116 は、酸化物半導体膜 108 に酸素を供給する機能を有する。また、絶縁膜 118 は、トランジスタ 100 の保護絶縁膜としての機能を有する。また、絶縁膜 114、116 は、酸素を有する。また、絶縁膜 114 は、酸素を透過することができる絶縁膜である。なお、絶縁膜 114 は、後に形成する絶縁膜 116 を形成する際の、酸化物半導体膜 108 へのダメージ緩和膜としても機能する。

#### 【 0 4 4 9 】

絶縁膜 114 としては、厚さが 5 nm 以上 150 nm 以下、好ましくは 5 nm 以上 50 nm 以下の酸化シリコン、酸化窒化シリコン等を用いることができる。

#### 【 0 4 5 0 】

また、絶縁膜 114 は、欠陥量が少ないことが好ましく、代表的には、E S R 測定により、シリコンのダングリングボンドに由来する  $g = 2.001$  に現れる信号のスピニ密度が $3 \times 10^{17}$  spins / cm<sup>3</sup> 以下であることが好ましい。これは、絶縁膜 114 に含まれる欠陥密度が多いと、該欠陥に酸素が結合してしまい、絶縁膜 114 における酸素の透過量が減少してしまうためである。

#### 【 0 4 5 1 】

なお、絶縁膜 114 においては、外部から絶縁膜 114 に入った酸素が全て絶縁膜 114

10

20

30

40

50

の外部に移動せず、絶縁膜 114 にとどまる酸素もある。また、絶縁膜 114 に酸素が入ると共に、絶縁膜 114 に含まれる酸素が絶縁膜 114 の外部へ移動することで、絶縁膜 114 において酸素の移動が生じる場合もある。絶縁膜 114 として酸素を透過することができる酸化物絶縁膜を形成すると、絶縁膜 114 上に設けられる、絶縁膜 116 から脱離する酸素を、絶縁膜 114 を介して酸化物半導体膜 108 に移動させることができる。

#### 【0452】

また、絶縁膜 114 は、窒素酸化物に起因する準位密度が低い酸化物絶縁膜を用いて形成することができる。なお、当該窒素酸化物に起因する準位密度は、酸化物半導体膜の価電子帯の上端のエネルギー (E<sub>V</sub>—O<sub>S</sub>) と酸化物半導体膜の伝導帯の下端のエネルギー (E<sub>C</sub>—O<sub>S</sub>) の間に形成され得る場合がある。上記酸化物絶縁膜として、窒素酸化物の放出量が少ない酸化窒化シリコン膜、または窒素酸化物の放出量が少ない酸化窒化アルミニウム膜等を用いることができる。10

#### 【0453】

なお、窒素酸化物の放出量の少ない酸化窒化シリコン膜は、昇温脱離ガス分析法において、窒素酸化物の放出量よりアンモニアの放出量が多い膜であり、代表的にはアンモニアの放出量が  $1 \times 10^{18} \text{ cm}^{-3}$  以上  $5 \times 10^{19} \text{ cm}^{-3}$  以下である。なお、アンモニアの放出量は、膜の表面温度が 50 以上 650 以下、好ましくは 50 以上 550 以下の加熱処理による放出量とする。

#### 【0454】

窒素酸化物 (NO<sub>x</sub>、x は 0 より大きく 2 以下、好ましくは 1 以上 2 以下)、代表的には NO<sub>2</sub> または NO は、絶縁膜 114 などに準位を形成する。当該準位は、酸化物半導体膜 108 のエネルギー・ギャップ内に位置する。そのため、窒素酸化物が、絶縁膜 114 及び酸化物半導体膜 108 の界面に拡散すると、当該準位が絶縁膜 114 側において電子をトラップする場合がある。この結果、トラップされた電子が、絶縁膜 114 及び酸化物半導体膜 108 界面近傍に留まるため、トランジスタのしきい値電圧をプラス方向にシフトさせてしまう。20

#### 【0455】

また、窒素酸化物は、加熱処理においてアンモニア及び酸素と反応する。絶縁膜 114 に含まれる窒素酸化物は、加熱処理において、絶縁膜 116 に含まれるアンモニアと反応するため、絶縁膜 114 に含まれる窒素酸化物が低減される。このため、絶縁膜 114 及び酸化物半導体膜 108 の界面において、電子がトラップされにくい。30

#### 【0456】

絶縁膜 114 として、上記酸化物絶縁膜を用いることで、トランジスタのしきい値電圧のシフトを低減することが可能であり、トランジスタの電気特性の変動を低減することができる。

#### 【0457】

なお、トランジスタの作製工程の加熱処理、代表的には 300 以上 350 未満の加熱処理により、絶縁膜 114 は、100K 以下の ESR で測定して得られたスペクトルにおいて g 値が 2.037 以上 2.039 以下の第 1 のシグナル、g 値が 2.001 以上 2.003 以下の第 2 のシグナル、及び g 値が 1.964 以上 1.966 以下の第 3 のシグナルが観測される。なお、第 1 のシグナル及び第 2 のシグナルのスプリット幅、並びに第 2 のシグナル及び第 3 のシグナルのスプリット幅は、X バンドの ESR 測定において約 5 mT である。また、g 値が 2.037 以上 2.039 以下の第 1 のシグナル、g 値が 2.001 以上 2.003 以下の第 2 のシグナル、及び g 値が 1.964 以上 1.966 以下である第 3 のシグナルのスピンの密度の合計が  $1 \times 10^{18} \text{ spins/cm}^3$  未満であり、代表的には  $1 \times 10^{17} \text{ spins/cm}^3$  以上  $1 \times 10^{18} \text{ spins/cm}^3$  未満である。40

#### 【0458】

なお、100K 以下の ESR スペクトルにおいて g 値が 2.037 以上 2.039 以下の第 1 シグナル、g 値が 2.001 以上 2.003 以下の第 2 のシグナル、及び g 値が 1.964 以上 1.966 以下の第 3 のシグナルのスピンの密度の合計が  $1 \times 10^{18} \text{ spins/cm}^3$  未満である。50

964以上1.966以下の第3のシグナルは、窒素酸化物( $\text{NO}_x$ 、 $x$ は0より大きく2以下、好ましくは1以上2以下)起因のシグナルに相当する。窒素酸化物の代表例としては、一酸化窒素、二酸化窒素等がある。即ち、g値が2.037以上2.039以下の第1のシグナル、g値が2.001以上2.003以下の第2のシグナル、及びg値が1.964以上1.966以下の第3のシグナルのスピンの密度の合計が少ないほど、酸化物絶縁膜に含まれる窒素酸化物の含有量が少ないといえる。

#### 【0459】

また、上記酸化物絶縁膜は、SIMSで測定される窒素濃度が $6 \times 10^{20}$ atoms/cm<sup>3</sup>以下である。

#### 【0460】

膜の表面温度が220以上350以下であり、シラン及び一酸化二窒素を用いたPECVD法を用いて、上記酸化物絶縁膜を形成することで、緻密であり、且つ硬度の高い膜を形成することができる。

#### 【0461】

絶縁膜116は、化学量論的組成を満たす酸素よりも多くの酸素を含む酸化物絶縁膜を用いて形成する。化学量論的組成を満たす酸素よりも多くの酸素を含む酸化物絶縁膜は、TDS分析にて、酸素原子に換算しての酸素の脱離量が $1.0 \times 10^{19}$ atoms/cm<sup>3</sup>以上、好ましくは $3.0 \times 10^{20}$ atoms/cm<sup>3</sup>以上である酸化物絶縁膜である。なお、上記TDSにおける膜の表面温度としては100以上700以下、または100以上500以下の範囲が好ましい。

#### 【0462】

絶縁膜116としては、厚さが30nm以上500nm以下、好ましくは50nm以上400nm以下の、酸化シリコン、酸化窒化シリコン等を用いることができる。

#### 【0463】

また、絶縁膜116は、欠陥量が少ないことが好ましく、代表的には、ESR測定により、シリコンのダングリングボンドに由来するg=2.001に現れる信号のスピン密度が $1.5 \times 10^{18}$ spins/cm<sup>3</sup>未満、さらには $1 \times 10^{18}$ spins/cm<sup>3</sup>以下であることが好ましい。なお、絶縁膜116は、絶縁膜114と比較して酸化物半導体膜108から離れているため、絶縁膜114より、欠陥密度が多くともよい。

#### 【0464】

また、絶縁膜114、116は、同種の材料の絶縁膜を用いることができるため、絶縁膜114と絶縁膜116の界面が明確に確認できない場合がある。したがって、本実施の形態においては、絶縁膜114と絶縁膜116の界面は、破線で図示している。なお、本実施の形態においては、絶縁膜114と絶縁膜116の2層構造について説明したが、これに限定されず、例えば、絶縁膜114の単層構造としてもよい。

#### 【0465】

絶縁膜118は、窒素を有する。また、絶縁膜118は、窒素及びシリコンを有する。また、絶縁膜118は、酸素、水素、水、アルカリ金属、アルカリ土類金属等のブロッキングできる機能を有する。絶縁膜118を設けることで、酸化物半導体膜108からの酸素の外部への拡散と、絶縁膜114、116に含まれる酸素の外部への拡散と、外部から酸化物半導体膜108への水素、水等の入り込みを防ぐことができる。絶縁膜118としては、例えば、窒化物絶縁膜を用いることができる。該窒化物絶縁膜としては、窒化シリコン、窒化酸化シリコン、窒化アルミニウム、窒化酸化アルミニウム等がある。なお、酸素、水素、水、アルカリ金属、アルカリ土類金属等のブロッキング効果を有する窒化物絶縁膜の代わりに、酸素、水素、水等のブロッキング効果を有する酸化物絶縁膜を設けてもよい。酸素、水素、水等のブロッキング効果を有する酸化物絶縁膜としては、酸化アルミニウム、酸化窒化アルミニウム、酸化ガリウム、酸化窒化ガリウム、酸化イットリウム、酸化窒化イットリウム、酸化ハフニウム、酸化窒化ハフニウム等がある。

#### 【0466】

10

20

30

40

50

なお、上記記載の、導電膜、絶縁膜、酸化物半導体膜などの様々な膜は、スパッタリング法やPECVD法により形成することができるが、他の方法、例えば、熱CVD(Chemical Vapor Deposition)法により形成してもよい。熱CVD法の例としてMOCVD(Metal Organic Chemical Vapor Deposition)法やALD(Atomic Layer Deposition)法を用いても良い。

#### 【0467】

熱CVD法は、プラズマを使わない成膜方法のため、プラズマダメージにより欠陥が生成されることが無いという利点を有する。

#### 【0468】

熱CVD法は、原料ガスと酸化剤を同時にチャンバー内に送り、チャンバー内を大気圧または減圧下とし、基板近傍または基板上で反応させて基板上に堆積させることで成膜を行ってもよい。

#### 【0469】

また、ALD法は、チャンバー内を大気圧または減圧下とし、反応のための原料ガスが順次チャンバーに導入され、そのガス導入の順序を繰り返すことで成膜を行ってもよい。例えば、それぞれのスイッチングバルブ(高速バルブとも呼ぶ)を切り替えて2種類以上の原料ガスを順番にチャンバーに供給し、複数種の原料ガスが混ざらないように第1の原料ガスと同時またはその後に不活性ガス(アルゴン、或いは窒素など)などを導入し、第2の原料ガスを導入する。なお、同時に不活性ガスを導入する場合には、不活性ガスはキャリアガスとなり、また、第2の原料ガスの導入時にも同時に不活性ガスを導入してもよい。また、不活性ガスを導入する代わりに真空排気によって第1の原料ガスを排出した後、第2の原料ガスを導入してもよい。第1の原料ガスが基板の表面に吸着して第1の層を成膜し、後から導入される第2の原料ガスと反応して、第2の層が第1の層上に積層されて薄膜が形成される。このガス導入順序を制御しつつ所望の厚さになるまで複数回繰り返すことで、段差被覆性に優れた薄膜を形成することができる。薄膜の厚さは、ガス導入順序を繰り返す回数によって調節することができるため、精密な膜厚調節が可能であり、微細なFETを作製する場合に適している。

#### 【0470】

MOCVD法やALD法などの熱CVD法は、上記実施形態の導電膜、絶縁膜、酸化物半導体膜、金属酸化膜などの様々な膜を形成することができ、例えば、In-Ga-ZnO膜を成膜する場合には、トリメチルインジウム、トリメチルガリウム、及びジメチル亜鉛を用いる。なお、トリメチルインジウムの化学式は、In(CH<sub>3</sub>)<sub>3</sub>である。また、トリメチルガリウムの化学式は、Ga(CH<sub>3</sub>)<sub>3</sub>である。また、ジメチル亜鉛の化学式は、Zn(CH<sub>3</sub>)<sub>2</sub>である。また、これらの組み合わせに限定されず、トリメチルガリウムに代えてトリエチルガリウム(化学式Ga(C<sub>2</sub>H<sub>5</sub>)<sub>3</sub>)を用いることもでき、ジメチル亜鉛に代えてジエチル亜鉛(化学式Zn(C<sub>2</sub>H<sub>5</sub>)<sub>2</sub>)を用いることもできる。

#### 【0471】

例えば、ALDを利用する成膜装置により酸化ハフニウム膜を形成する場合には、溶媒とハフニウム前駆体化合物を含む液体(ハフニウムアルコキシドや、テトラキスジメチルアミドハフニウム(TDMAH)などのハフニウムアミド)を気化させた原料ガスと、酸化剤としてオゾン(O<sub>3</sub>)の2種類のガスを用いる。なお、テトラキスジメチルアミドハフニウムの化学式はHf[N(CH<sub>3</sub>)<sub>2</sub>]<sub>4</sub>である。また、他の材料液としては、テトラキス(エチルメチルアミド)ハフニウムなどがある。

#### 【0472】

例えば、ALDを利用する成膜装置により酸化アルミニウム膜を形成する場合には、溶媒とアルミニウム前駆体化合物を含む液体(トリメチルアルミニウム(TMA)など)を気化させた原料ガスと、酸化剤としてH<sub>2</sub>Oの2種類のガスを用いる。なお、トリメチルアルミニウムの化学式はAl(CH<sub>3</sub>)<sub>3</sub>である。また、他の材料液としては、トリス(ジメチルアミド)アルミニウム、トリイソブチルアルミニウム、アルミニウムトリス(2,

10

20

30

40

50

2, 6, 6 - テトラメチル - 3, 5 - ヘプタンジオナート) などがある。

【0473】

例えば、A L D を利用する成膜装置により酸化シリコン膜を形成する場合には、ヘキサクロロジシランを被成膜面に吸着させ、吸着物に含まれる塩素を除去し、酸化性ガス (O<sub>2</sub>、一酸化二窒素) のラジカルを供給して吸着物と反応させる。

【0474】

例えば、A L D を利用する成膜装置によりタンゲステン膜を成膜する場合には、W F<sub>6</sub> ガスとB<sub>2</sub>H<sub>6</sub> ガスを順次繰り返し導入して初期タンゲステン膜を形成し、その後、W F<sub>6</sub> ガスとH<sub>2</sub> ガスを用いてタンゲステン膜を形成する。なお、B<sub>2</sub>H<sub>6</sub> ガスに代えてSiH<sub>4</sub> ガスを用いてもよい。

10

【0475】

例えば、A L D を利用する成膜装置により酸化物半導体膜、例えばIn - Ga - ZnO 膜を成膜する場合には、In(CH<sub>3</sub>)<sub>3</sub> ガスとO<sub>3</sub> ガスを順次繰り返し導入してIn - O 層を形成し、その後、Ga(CH<sub>3</sub>)<sub>3</sub> ガスとO<sub>3</sub> ガスを用いてGaO 層を形成し、更にその後Zn(CH<sub>3</sub>)<sub>2</sub> ガスとO<sub>3</sub> ガスを用いてZnO 層を形成する。なお、これらの層の順番はこの例に限らない。また、これらのガスを混ぜてIn - Ga - O 層やIn - Zn - O 層、Ga - Zn - O 層などの混合化合物層を形成しても良い。なお、O<sub>3</sub> ガスに代えてAr 等の不活性ガスで水をバーリングして得られたH<sub>2</sub>O ガスを用いても良いが、Hを含まないO<sub>3</sub> ガスを用いる方が好ましい。また、In(CH<sub>3</sub>)<sub>3</sub> ガスにかえて、In(C<sub>2</sub>H<sub>5</sub>)<sub>3</sub> ガスを用いても良い。また、Ga(CH<sub>3</sub>)<sub>3</sub> ガスにかえて、Ga(C<sub>2</sub>H<sub>5</sub>)<sub>3</sub> ガスを用いても良い。また、Zn(CH<sub>3</sub>)<sub>2</sub> ガスを用いても良い。

20

【0476】

なお、本実施の形態は、本明細書で示す他の実施の形態と適宜組み合わせができる。

【0477】

(実施の形態6)

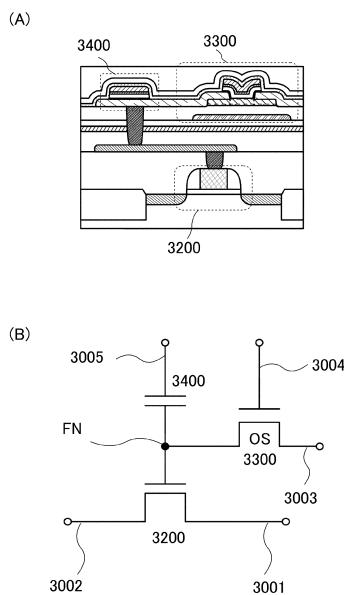

本実施の形態では、本発明の一態様の表示パネルに用いることができるトランジスタの構成について、図13を参照しながら説明する。

【0478】

<半導体装置の構成例>

30

図13(A)は、トランジスタ100の上面図であり、図13(B)は、図13(A)に示す切断線X1-X2間ににおける切断面の断面図に相当し、図13(C)は、図13(A)に示す切断線Y1-Y2間ににおける切断面の断面図に相当する。なお、図13(A)において、煩雑になることを避けるため、トランジスタ100の構成要素の一部(ゲート絶縁膜として機能する絶縁膜等)を省略して図示している。また、切断線X1-X2方向をチャネル長方向、切断線Y1-Y2方向をチャネル幅方向と呼称する場合がある。なお、トランジスタの上面図においては、以降の図面においても図13(A)と同様に、構成要素の一部を省略して図示する場合がある。

【0479】