(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2014-187085

(P2014-187085A)

(43) 公開日 平成26年10月2日(2014.10.2)

(51) Int.Cl.

**H01L 29/812 (2006.01)**

**H01L 29/778 (2006.01)**

**H01L 21/338 (2006.01)**

**H01L 29/808 (2006.01)**

**H01L 21/337 (2006.01)**

F 1

H 01 L 29/80

H 01 L 29/80

H 01 L 29/80

H 01 L 29/78

テーマコード(参考)

H 5 F 1 O 2

W 5 F 1 4 O

C

3 O 1 B

審査請求 未請求 請求項の数 16 O L (全 14 頁) 最終頁に続く

(21) 出願番号

特願2013-59337(P2013-59337)

(22) 出願日

平成25年3月22日(2013.3.22)

(71) 出願人 000003078

株式会社東芝

東京都港区芝浦一丁目1番1号

(74) 代理人 100119035

弁理士 池上 徹真

(74) 代理人 100141036

弁理士 須藤 章

(74) 代理人 100088487

弁理士 松山 允之

(72) 発明者 斎藤 泰伸

東京都港区芝浦一丁目1番1号 株式会社

東芝内

(72) 発明者 藤本 英俊

東京都港区芝浦一丁目1番1号 株式会社

東芝内

最終頁に続く

(54) 【発明の名称】半導体装置

## (57) 【要約】

【課題】ゲートリーキ電流が低減された半導体装置を提供する。

【解決手段】実施形態の半導体装置は、第1の窒化物半導体からなる第1の半導体層と、上記第1の半導体層上に形成され、上記第1の窒化物半導体よりバンドギャップの大きい第2の窒化物半導体からなる第2の半導体層と、第2の半導体層上に形成されるソース電極と、上記第2の半導体層上に形成されるドレイン電極と、上記ソース電極とドレイン電極の間の上記第2の半導体層上に形成され、上記第2の半導体層とショットキー接合する第1のゲート電極と、上記ソース電極と上記第1のゲート電極との間の上記第2の半導体層上に、絶縁膜を介して形成され、第1のゲート電極と電気的に接続される第2のゲート電極と、上記ドレイン電極と上記第1のゲート電極との間の上記第2の半導体層上に、絶縁膜を介して形成され、第1のゲート電極と電気的に接続される第3のゲート電極と、を備える。

【選択図】図1

## 【特許請求の範囲】

## 【請求項 1】

第1の窒化物半導体からなる第1の半導体層と、

前記第1の半導体層上に形成され、前記第1の窒化物半導体よりバンドギャップの大きい第2の窒化物半導体からなる第2の半導体層と、

前記第2の半導体層上に形成されるソース電極と、

前記第2の半導体層上に形成されるドレイン電極と、

前記ソース電極と前記ドレイン電極の間の前記第2の半導体層上に形成され、前記第2の半導体層とショットキー接合する第1のゲート電極と、

前記ソース電極と前記第1のゲート電極との間の前記第2の半導体層上に、絶縁膜を介して形成され、前記第1のゲート電極と電気的に接続される第2のゲート電極と、

前記ドレイン電極と前記第1のゲート電極との間の前記第2の半導体層上に、絶縁膜を介して形成され、前記第1のゲート電極と電気的に接続される第3のゲート電極と、

を備え、

前記第1の閾値が、前記第2および第3の閾値よりも高く、

前記第2および前記第3のゲート電極直下の前記第2の半導体層の膜厚が、前記第1のゲート電極直下の前記第2の半導体層の膜厚よりも薄く、

前記第2および第3の閾値が、前記第1、第2および第3のゲート電極にオフ時に印加される電圧よりも高く、

前記第2および第3の閾値と、前記第1の閾値の差の絶対値が1V以下で、

前記第2および第3のゲート電極のゲート長が、前記第1のゲート電極のゲート長よりも長く、

前記第1の窒化物半導体が $\text{Al}_x\text{Ga}_{1-x}\text{N}$ ( $0 < X < 1$ )であり、前記第2の窒化物半導体が、 $\text{Al}_y\text{Ga}_{1-y}\text{N}$ ( $0 < Y < 1$ 、 $X < Y$ )であることを特徴とする半導体装置。 10

## 【請求項 2】

第1の窒化物半導体からなる第1の半導体層と、

前記第1の半導体層上に形成され、前記第1の窒化物半導体よりバンドギャップの大きい第2の窒化物半導体からなる第2の半導体層と、

前記第2の半導体層上に形成されるソース電極と、

前記第2の半導体層上に形成されるドレイン電極と、

前記ソース電極と前記ドレイン電極の間の前記第2の半導体層上に形成され、前記第2の半導体層とショットキー接合する第1のゲート電極と、

前記ソース電極と前記第1のゲート電極との間の前記第2の半導体層上に、絶縁膜を介して形成され、前記第1のゲート電極と電気的に接続される第2のゲート電極と、

前記ドレイン電極と前記第1のゲート電極との間の前記第2の半導体層上に、絶縁膜を介して形成され、前記第1のゲート電極と電気的に接続される第3のゲート電極と、

を備えることを特徴とする半導体装置。 30

## 【請求項 3】

前記第1の閾値が、前記第2および第3の閾値よりも高いことを特徴とする請求項2記載の半導体装置。 40

## 【請求項 4】

前記第2および前記第3のゲート電極直下の前記第2の半導体層の膜厚が、前記第1のゲート電極直下の前記第2の半導体層の膜厚よりも薄いことを特徴とする請求項2または請求項3記載の半導体装置。

## 【請求項 5】

前記第2および前記第3のゲート電極直下の前記第2の半導体層に、フッ素または塩素を含有する半導体領域を備えることを特徴とする請求項2または請求項3記載の半導体装置。

## 【請求項 6】

10

20

30

40

50

前記第2および第3の閾値が、前記第1、第2および第3のゲート電極にオフ時に印加される電圧よりも高いことを特徴とする請求項3記載の半導体装置。

**【請求項7】**

前記第2および第3の閾値と、前記第1の閾値の差の絶対値が1V以下であることを特徴とする請求項3記載の半導体装置。

**【請求項8】**

前記第2および第3のゲート電極のゲート長が、前記第1のゲート電極のゲート長よりも長いことを特徴とする請求項2ないし請求項7いずれか一項記載の半導体装置。

**【請求項9】**

第1の窒化物半導体からなる第1の半導体層と、

前記第1の半導体層上に形成され、前記第1の窒化物半導体よりバンドギャップの大きい第2の窒化物半導体からなる第2の半導体層と、

前記第2の半導体層上に形成されるソース電極と、

前記第2の半導体層上に形成されるドレイン電極と、

前記ソース電極と前記ドレイン電極の間の前記第2の半導体層上に形成され、p型の第3の窒化物半導体と金属との積層構造の第1のゲート電極と、

前記ソース電極と前記第1のゲート電極との間の前記第2の半導体層上に、絶縁膜を介して形成され、前記第1のゲート電極と電気的に接続される第2のゲート電極と、

前記ドレイン電極と前記第1のゲート電極との間の前記第2の半導体層上に、絶縁膜を介して形成され、前記第1のゲート電極と電気的に接続される第3のゲート電極と、

を備えることを特徴とする半導体装置。

**【請求項10】**

前記第1の閾値が、前記第2および第3の閾値よりも高いことを特徴とする請求項9記載の半導体装置。

**【請求項11】**

前記第2および前記第3のゲート電極直下の前記第2の半導体層の膜厚が、前記第1のゲート電極直下の前記第2の半導体層の膜厚よりも薄いことを特徴とする請求項9または請求項10記載の半導体装置。

**【請求項12】**

前記第2および前記第3のゲート電極直下の前記第2の半導体層に、フッ素または塩素を含有する半導体領域を備えることを特徴とする請求項9または請求項10記載の半導体装置。

**【請求項13】**

前記第2および第3の閾値が、前記第1、第2および第3のゲート電極にオフ時に印加される電圧よりも高いことを特徴とする請求項10記載の半導体装置。

**【請求項14】**

前記第2および第3の閾値と、前記第1の閾値の差の絶対値が1V以下であることを特徴とする請求項10記載の半導体装置。

**【請求項15】**

前記第2および第3のゲート電極のゲート長が、前記第1のゲート電極のゲート長よりも長いことを特徴とする請求項9ないし請求項14いずれか一項記載の半導体装置。

**【請求項16】**

前記第1の窒化物半導体が $A_{1-x}Ga_{1-x}N(0 < X < 1)$ であり、前記第2の窒化物半導体が、 $A_{1-y}Ga_{1-y}N(0 < Y < 1, X < Y)$ であり、前記第3の窒化物半導体が $A_{1-z}Ga_{1-z}N(0 < Z < 1)$ であることを特徴とする請求項9ないし請求項15いずれか一項記載の半導体装置。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明の実施形態は、半導体装置に関する。

10

20

30

40

50

## 【背景技術】

## 【0002】

スイッチング電源やインバータ回路などに用いられるスイッチング素子には高耐圧、低オン抵抗が求められる。そして、窒化物半導体を用いたスイッチング素子は、その優れた材料特性から、耐圧とオン抵抗の間のトレードオフ関係を改善できる。そのため、低オン抵抗化と高耐圧化が可能であるとして有望視されている。

## 【0003】

窒化物半導体を用いたスイッチング素子として、AlGaN/GaNヘテロ構造を用いたHEMT (High Electron Mobility Transistor) がある。そして、AlGaN/GaNヘテロ構造を用いたHEMTのゲート電極構造の一つとして、ショットキー型ゲート電極構造がある。ショットキー型ゲート電極構造は、ゲート電極が半導体層に対してショットキー接合している。

10

## 【0004】

ショットキー型ゲート電極構造のHEMTは、電荷トラップの一因となるゲート絶縁膜を備えないため、閾値変動が比較的小ないとされる。もっとも、ショットキー型ゲート電極構造のHEMTでは、オフ時のゲートリーコンダクション電流が問題となる。

20

## 【先行技術文献】

## 【特許文献】

## 【0005】

【特許文献1】特開2004-214471号公報

【特許文献2】特開2007-180454号公報

## 【発明の概要】

## 【発明が解決しようとする課題】

## 【0006】

本発明が解決しようとする課題は、ゲートリーコンダクション電流を低減することができる半導体装置を提供することにある。

30

## 【課題を解決するための手段】

## 【0007】

実施形態の半導体装置は、第1の窒化物半導体からなる第1の半導体層と、上記第1の半導体層上に形成され、上記第1の窒化物半導体よりバンドギャップの大きい第2の窒化物半導体からなる第2の半導体層と、第2の半導体層上に形成されるソース電極と、上記第2の半導体層上に形成されるドレイン電極と、を備える。さらに、上記ソース電極とドレイン電極の間の上記第2の半導体層上に形成され、上記第2の半導体層とショットキー接合する第1のゲート電極と、上記ソース電極と上記第1のゲート電極との間の上記第2の半導体層上に、絶縁膜を介して形成され、第1のゲート電極と電気的に接続される第2のゲート電極と、上記ドレイン電極と上記第1のゲート電極との間の上記第2の半導体層上に、絶縁膜を介して形成され、第1のゲート電極と電気的に接続される第3のゲート電極と、を備える。

## 【図面の簡単な説明】

## 【0008】

40

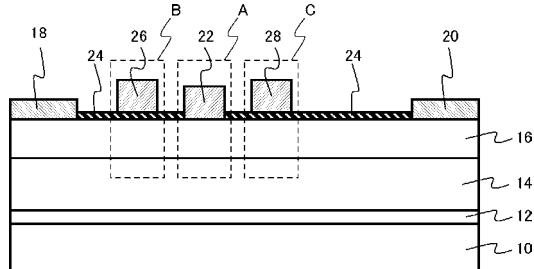

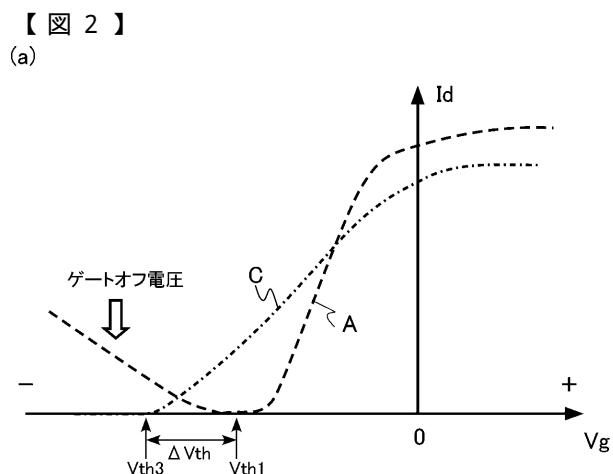

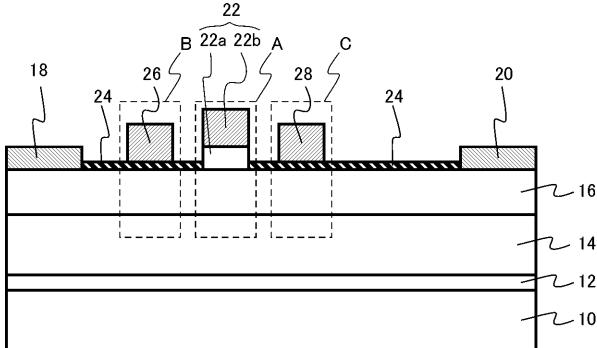

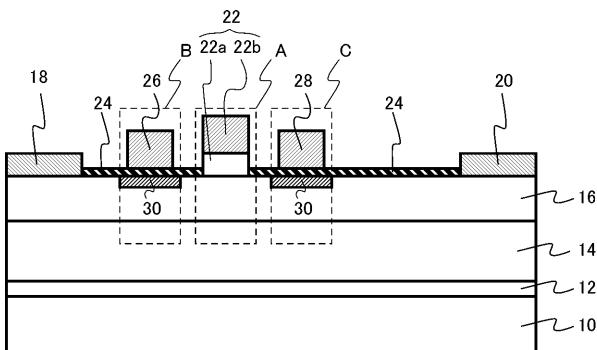

【図1】第1の実施形態の半導体装置の構成を示す模式断面図である。

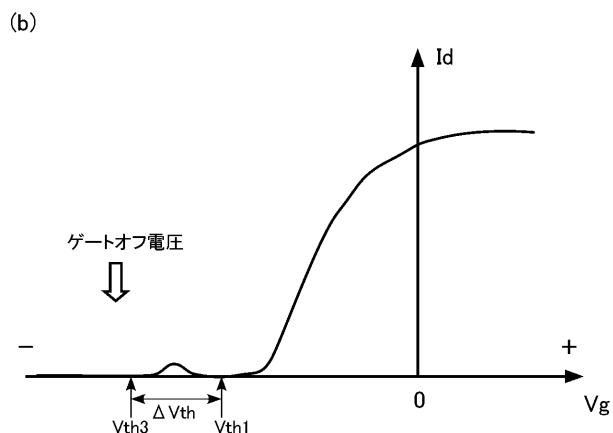

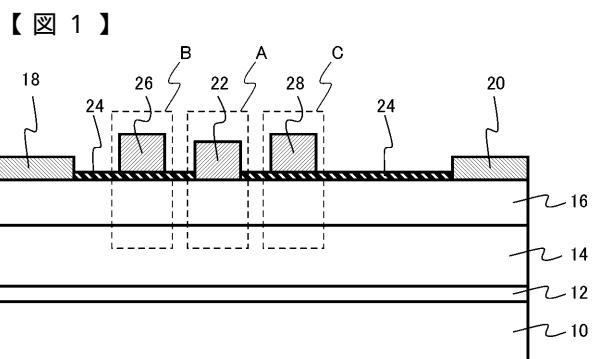

【図2】第1の実施形態の半導体装置の効果を説明する図である。

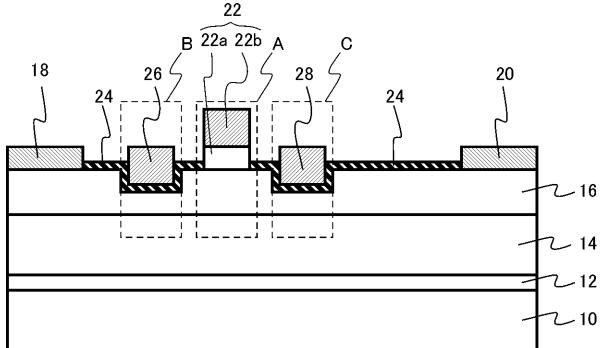

【図3】第2の実施形態の半導体装置の構成を示す模式断面図である。

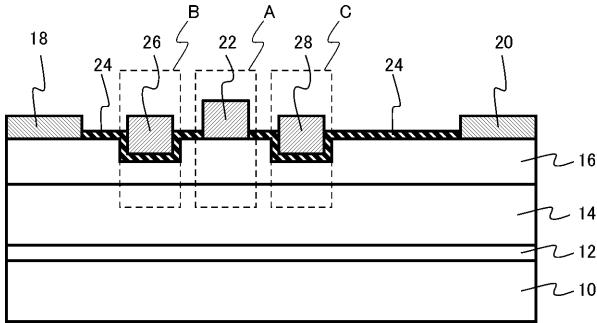

【図4】第3の実施形態の半導体装置の構成を示す模式断面図である。

【図5】第4の実施形態の半導体装置の構成を示す模式断面図である。

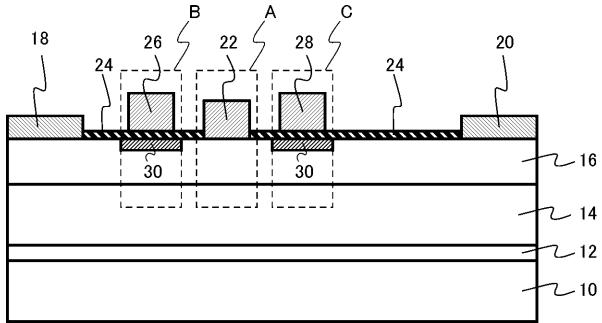

【図6】第5の実施形態の半導体装置の構成を示す模式断面図である。

【図7】第6の実施形態の半導体装置の構成を示す模式断面図である。

## 【発明を実施するための形態】

## 【0009】

本明細書中、トランジスタの「閾値が低い」とは、相対的に閾値がマイナスの方向にあ

50

る場合を意味する、また、トランジスタの「閾値が高い」とは、相対的に閾値がプラスの方向にある場合を意味する。

【0010】

例えば、ノーマリーオンの、閾値が負の2つのトランジスタの閾値を比較する場合、閾値が低いとは絶対値が大きいことを意味し、閾値が高いとは絶対値が小さいことを意味する。

【0011】

また、例えば、ノーマリーオフの、閾値が正の2つのトランジスタの閾値を比較する場合、閾値が低いとは絶対値が小さいことを意味し、閾値が高いとは絶対値が大きいことを意味する。

10

【0012】

(第1の実施形態)

本実施形態の半導体装置は、第1の窒化物半導体からなる第1の半導体層と、上記第1の半導体層上に形成され、上記第1の窒化物半導体よりバンドギャップの大きい第2の窒化物半導体からなる第2の半導体層と、第2の半導体層上に形成されるソース電極と、上記第2の半導体層上に形成されるドレイン電極と、を備える。さらに、上記ソース電極とドレイン電極の間の上記第2の半導体層上に形成され、上記第2の半導体層とショットキー接合する第1のゲート電極と、上記ソース電極と上記第1のゲート電極との間の上記第2の半導体層上に、絶縁膜を介して形成され、第1のゲート電極と電気的に接続される第2のゲート電極と、上記ドレイン電極と上記第1のゲート電極との間の上記第2の半導体層上に、絶縁膜を介して形成され、第1のゲート電極と電気的に接続される第3のゲート電極と、を備えている。

20

【0013】

図1は、本実施形態の半導体装置の構成を示す模式断面図である。本実施形態の半導体装置は、ノーマリーオンのHEMTである。ヘテロ接合を用いたHEMTは、チャネル移動度が高いため、オン抵抗を小さくすることが可能であり、パワーエレクトロニクス用半導体装置に適している。また、高いチャネル移動度は高周波動作にも適している。

20

【0014】

本実施形態の半導体装置は、基板10、基板10上に形成されるバッファ層12、バッファ層12上に形成される第1の半導体層14、第1の半導体層14上に形成される第2の半導体層16を備える。

30

【0015】

基板10は、例えば、シリコン(Si)からなる。シリコン以外にも、例えば、サファイア(Al<sub>2</sub>O<sub>3</sub>)や炭化珪素(SiC)を適用することも可能である。

【0016】

バッファ層12は、基板10と第1の半導体層14との間の格子不整合を緩和する機能を備える。バッファ層12は、例えば、窒化アルミニウムガリウム(Al<sub>x</sub>Ga<sub>1-x</sub>N(0 < X < 1))の多層構造で形成される。

40

【0017】

第1の半導体層14は動作層(チャネル層)であり、第2の半導体層16は障壁層(電子供給層)である。第2の半導体層16は第1の半導体層14よりもバンドギャップが大きい窒化物半導体で形成される。

【0018】

第1の半導体層14を形成する第1の窒化物半導体は、例えば、アンドープの窒化ガリウムまたは窒化アルミニウムガリウム(Al<sub>x</sub>Ga<sub>1-x</sub>N(0 < X < 1))である。第1の窒化物半導体は、n型またはp型であってもかまわない。第1の半導体層14の膜厚は、例えば、0.5~3μmである。

【0019】

また、第2の半導体層16を形成する第2の窒化物半導体は、例えば、n型の窒化アルミニウムガリウム(Al<sub>y</sub>Ga<sub>1-y</sub>N(0 < Y < 1, X < Y))である。第2の窒化物

50

半導体は、アンドープであってもかまわない。第2の半導体層16の膜厚は、例えば、20~50nmである。

#### 【0020】

なお、第1および第2の窒化物半導体は、必ずしも、上記材料に限られるものではなく、上記以外の窒化物半導体を適用することも可能である。

#### 【0021】

第1の半導体層14と第2の半導体層16との間には、ヘテロ接合界面が形成される。トランジスタのオン動作時は、ヘテロ接合界面に二次元電子ガスが形成されキャリアとなる。

#### 【0022】

第2の半導体層16上には、ソース電極18とドレイン電極20が形成される。ソース電極18とドレイン電極20は、例えば、金属電極であり、金属電極は、例えば、アルミニウム(A1)を主成分とする電極である。ソース電極18およびドレイン電極20と、第2の半導体層16との間は、オーミックコンタクトである。ソース電極18とドレイン電極20との距離は、例えば、10μm程度である。

10

#### 【0023】

そして、ソース電極18とドレイン電極20の間の第2の半導体層16上に、第1のゲート電極22が形成される。第1のゲート電極22は第2の半導体層16に対し、ショットキー接合する。第1のゲート電極のゲート長は、例えば、1μmである。

20

#### 【0024】

第1のゲート電極22は、例えば、金属電極である。金属電極は、例えば、ニッケル(Ni)電極、チタン(Ti)電極、または、白金(Plt)である。これら金属の合金あるいは積層構造であってもかまわない。また、ゲート電極の低抵抗化のために、抵抗の低い金(Au)等を上層に積層させてもかまわない。

#### 【0025】

また、ソース電極18と第1のゲート電極22との間の第2の半導体層16上に、絶縁膜24を介して第2のゲート電極26が形成される。第2のゲート電極26は、第1のゲート電極22と電気的に接続される。第2のゲート電極26のゲート長は、例えば、1μmである。

30

#### 【0026】

さらに、ドレイン電極20と第1のゲート電極22との間の第2の半導体層16上に、絶縁膜24を介して第3のゲート電極28が形成される。第3のゲート電極28は、第1のゲート電極22と電気的に接続される。第3のゲート電極28のゲート長は、例えば、1μmである。

#### 【0027】

絶縁膜24は、第2および第3のゲート電極26、28のゲート絶縁膜として機能する。絶縁膜24は、例えば、材料として形成容易で安定性の高い窒化シリコン膜である。もっとも、絶縁膜24は、窒化シリコン膜に限定されることなく、例えば、酸化シリコン膜、酸窒化シリコン膜、酸化アルミニウム膜等その他の材料を適用することが可能である。

40

#### 【0028】

第2のゲート電極26および第3のゲート電極28は、例えば、金属電極である。金属電極は、例えば、ニッケル(Ni)電極、チタン(Ti)電極、または、白金(Plt)である。これら金属の合金あるいは積層構造であってもかまわない。また、ゲート電極の低抵抗化のために、抵抗の低い金(Au)等を上層に積層させてもかまわない。

#### 【0029】

なお、図1中、破線の枠線Aは、第1のゲート電極22で制御されるトランジスタ構造、破線の枠線Bは、第2のゲート電極26で制御されるトランジスタ構造、破線の枠線Cは、第3のゲート電極28で制御されるトランジスタ構造をそれぞれ示す。

#### 【0030】

図2は、本実施形態の半導体装置の効果を説明する図である。図2(a)が、本実施形

50

態の第1のゲート電極22で制御されるトランジスタ構造および第3のゲート電極26で制御されるトランジスタ構造の、ドレイン電流のゲート電圧依存性を示す説明図である。図2(b)が、本実施形態のHEMTのドレイン電流のゲート電圧依存性を示す説明図である。いずれの図においても、横軸がゲート電圧、縦軸がドレイン電流である。

#### 【0031】

図2(a)中、第1のゲート電極22で制御されるトランジスタ構造(以下、構造Aとも称する)の特性は点線Aで示される。構造Aは、第1の閾値( $V_{th1}$ )が負の値を備える。すなわち、ノーマリーオンのトランジスタとなっている。構造Aはショットキー型ゲート電極構造のトランジスタである。

#### 【0032】

構造Aでは、ゲート電圧が第1の閾値( $V_{th1}$ )を超えて、プラス側に大きくなつていくと、ドレイン電流が増加していく。一方、ゲート電圧が第1の閾値( $V_{th1}$ )を超えて、マイナス側に増加すると、一旦、流れなくなつたドレイン電流が再び流れはじめる。いいかえれば、ピンチオフ後、ゲート電圧の負の絶対値が大きくなるとドレイン電流が増加に転じる。この電流が、ゲート電極とドレイン電極間に流れるゲートリーク電流である。ゲート電極がショットキー接合で形成される構造Aだけでは、このゲートリーク電流を抑制することが困難である。

#### 【0033】

一方、図2(a)中、第3のゲート電極28で制御されるトランジスタ構造(以下、構造Cとも称する)の特性は、一点鎖線Cで示される。構造Cは、第3の閾値( $V_{th3}$ )が負の値を備える。すなわち、ノーマリーオンのトランジスタとなっている。そして、構造Bは、ゲート電極と半導体層との間に絶縁層を備える、MIS(Metal Insulator Semiconductor)型ゲート電極構造のトランジスタである。

#### 【0034】

構造Cでも、ゲート電圧が第3の閾値( $V_{th3}$ )を超えて、プラス側に大きくなつていくと、ドレイン電流が増加していく。しかし、第3のゲート電極28と第2の半導体層16との間に絶縁膜24があることから、ゲート電圧が第3の閾値( $V_{th3}$ )を超えて、マイナス側に増加しても、ゲート電極28とドレイン電極20間に流れるゲートリーク電流は微小である。

#### 【0035】

なお、図2(a)中には、表示しないが、第2のゲート電極で制御されるトランジスタ構造(以下、構造Bとも称する)もMIS型ゲート電極構造のトランジスタであり、その特性も、構造Cの特性と同様となる。

#### 【0036】

本実施形態のHEMTにおいては、MIS型ゲート電極構造の構造B、ショットキー型ゲート電極構造の構造A、MIS型ゲート電極構造の構造Cがソース電極18と、ドレイン電極20間に直列に接続されるトランジスタ構造となっている。したがって、このHEMTのドレイン電流のゲート電圧依存性は、構造Bと構造Cの特性が同様と仮定すると、図2(b)に示すように、図2(a)の構造Aと構造Cの特性を重畠させた特性となる。すなわち、構造Aと構造Cとのドレイン電流の小さい方のドレイン電流で、HEMT全体のドレイン電流が規定されることになる。

#### 【0037】

本実施形態では、第1の閾値( $V_{th1}$ )が、第2および第3の閾値( $V_{th2}$ 、 $V_{th3}$ )よりも高い。したがって、第1の閾値( $V_{th1}$ )と第3の閾値( $V_{th3}$ )の大小関係は、図2(a)(b)に示した通りである。

#### 【0038】

HEMT全体でみると、図2(b)に示すように、ゲート電圧0Vでドレイン電流が流れオン状態にある。そして、ゲート電圧を0Vからマイナス方向に増加させていくと、まずショットキー型ゲート電極構造の構造Aの第1の閾値( $V_{th1}$ )でピンチオフ状態になり、トランジスタがオフとなる。さらに、ゲート電圧をマイナス側に増加させていくと

10

20

30

40

50

、ショットキー型ゲート電極構造の第1のゲート電極22にゲートリーク電流が流れようとする。

#### 【0039】

一方で、MIS型ゲート電極構造の構造Cは、構造Aよりもマイナス側の第3の閾値( $V_{th3}$ )でピンチオフ状態になる。このため、HEMT全体では、マイナス側にゲート電圧を増加させても、第3の閾値( $V_{th3}$ )よりマイナス側では、第1のゲート電極22に流れようとするゲートリーク電流が、構造Cにより遮断される。このため、結果としてゲートリーク電流が抑制される。

#### 【0040】

このように、本実施形態のHEMTでは、ショットキー型ゲート電極構造とMIS型ゲート電極構造を直列につなげることで、ゲートリーク電流を抑制することが可能となる。また、界面準位への電荷のトラップ等により閾値変動の生じやすいMIS型ゲート電極構造の第2および第3閾値( $V_{th2}$ 、 $V_{th3}$ )ではなく、閾値変動の生じにくいショットキー型ゲート電極構造の第1の閾値( $V_{th1}$ )により、HEMT全体の閾値が規定される。

#### 【0041】

したがって、例え第2および第3閾値( $V_{th2}$ 、 $V_{th3}$ )の閾値が変動したとしても、HEMT全体ではその影響は観察されにくい。よって、ゲートリーク電流が抑制され、かつ、閾値変動の小さいHEMTが実現される。

#### 【0042】

なお、図2(a)、(b)に示すように、第2および第3の閾値( $V_{th2}$ 、 $V_{th3}$ )が、第1、第2および第3のゲート電極22、26、28にオフ時に印加される電圧(図2中、白矢印)よりも、高いことが望ましい。これにより、HEMTのオフ時に、構造Bおよび構造Cのピンチオフ状態が保たれ、ゲートリーク電流が一層抑制できるからである。

#### 【0043】

また、第2および第3の閾値( $V_{th2}$ 、 $V_{th3}$ )と、第1の閾値( $V_{th1}$ )の差の絶対値(図2中の $V_{th}$ )が0.1V以上1V以下であることが望ましい。0.1V未満では、第2および第3の閾値( $V_{th2}$ 、 $V_{th3}$ )が変動した場合に、第1の閾値( $V_{th1}$ )よりも閾値が高くなり、HEMT全体の閾値が変動しやすい第2または第3の閾値( $V_{th2}$ 、 $V_{th3}$ )で規定されることになるおそれがあるからである。また、1Vを超えると、MIS型ゲート電極構造(構造B、C)によるショットキー型ゲート電極構造(構造A)のゲートリーク電流の遮断が不十分になるおそれがあるからである。すなわち、第2および第3の閾値( $V_{th2}$ 、 $V_{th3}$ )と、第1の閾値( $V_{th1}$ )が離れてすぎていると、第1の閾値( $V_{th1}$ )よりもゲート電圧をマイナス側にシフトさせていく場合、しばらくの間、構造B、Cによるピンチオフが生じないため、ゲートリーク電流の遮断が不十分になるおそれがある。

#### 【0044】

なお、本実施形態のHEMTにおいて、ショットキー型ゲート電極構造、MIS型ゲート電極構造それぞれの閾値、すなわち、第1、第2、第3の閾値は、素子構造、材料、不純物濃度等が与えることにより、解析的または数値計算により算出することが可能である。

#### 【0045】

また、第2および第3のゲート電極26、28のゲート長が、第1のゲート電極22のゲート長よりも長いことが望ましい。これにより、MIS型ゲート電極構造である構造B、Cの遮断特性が向上し、ゲートリーク電流の遮断特性が向上するからである。

#### 【0046】

##### (第2の実施形態)

本実施形態の半導体装置は、第1のゲート電極が、p型の第3の窒化物半導体と金属との積層構造であること以外は、第1の実施形態と同様である。したがって、第1の実施形

10

20

30

40

50

態と重複する内容については、記述を省略する。

【0047】

図3は、本実施形態の半導体装置の構成を示す模式断面図である。図3に示すように、本実施形態の半導体装置は、第1のゲート電極が、p型の第3の窒化物半導体22aと金属22bとの積層構造である。

【0048】

すなわち、破線の枠線Aで示される第1のゲート電極で制御されるトランジスタ構造(構造A)が、いわゆる接合型ゲート電極構造を備えている。接合型ゲート電極構造も、ショットキー型ゲート電極構造と同様、電荷トラップの一因となるゲート絶縁膜を備えないため、閾値変動が小さい。

10

【0049】

p型の第3の窒化物半導体22aは、例えば、マグネシウム(Mg)をp型不純物として含有する窒化ガリウム(GaN)である。

【0050】

本実施形態によれば、p型の第3の窒化物半導体22aにより第1の半導体層(チャネル層)14のポテンシャルが引きあげられる。このため、構造Aの第1の閾値(V<sub>th1</sub>)をプラス方向に移動させることができになる。すなわち、第1の閾値(V<sub>th1</sub>)を高くすることが容易となる。よって、ノーマリーオフのHEMTを形成することが容易になる。

20

【0051】

また、第1の実施形態と同様、ゲートリーク電流が抑制され、かつ、閾値変動の小さいHEMTが実現される。

【0052】

(第3の実施形態)

本実施形態の半導体装置は、第2および第3のゲート電極直下の第2の半導体層の膜厚が、第1のゲート電極直下の第2の半導体層の膜厚よりも薄いこと以外は、第1の実施形態と同様である。したがって、第1の実施形態と重複する内容については、記述を省略する。

30

【0053】

図4は、本実施形態の半導体装置の構成を示す模式断面図である。図4に示すように、本実施形態の半導体装置は、第2および第3のゲート電極26、28直下の第2の半導体層16の膜厚が、第1のゲート電極22直下の第2の半導体層16の膜厚よりも薄い。

【0054】

すなわち、破線の枠線Bで示される第2のゲート電極26で制御されるトランジスタ構造(構造B)、破線の枠線Cで示される第3のゲート電極28で制御されるトランジスタ構造(構造C)が、いわゆるリセス構造を備えている。

40

【0055】

本実施形態によれば、構造Bと構造Cとをリセス構造にすることにより、MIS型ゲート電極構造である構造Bおよび構造Cの閾値を高くすることが容易になる。また、リセス構造の深さを変えることにより閾値の調整も容易になる。

【0056】

したがって、構造Aの第1の閾値(V<sub>th1</sub>)と、構造B、Cの第2および第3の閾値(V<sub>th2</sub>、V<sub>th3</sub>)との差を最適な値に調整することが容易となる。特に、第1の閾値(V<sub>th1</sub>)と、第2および第3の閾値(V<sub>th2</sub>、V<sub>th3</sub>)とを近づけることが容易となる。

【0057】

したがって、ゲートリーク電流を抑制することがより一層容易となるHEMTが実現される。また、閾値変動の小さいHEMTが実現される点においては、第1の実施形態と同様である。

50

【0058】

(第4の実施形態)

本実施形態の半導体装置は、第2および第3のゲート電極直下の第2の半導体層の膜厚が、第1のゲート電極直下の第2の半導体層の膜厚よりも薄いこと以外は、第2の実施形態と同様である。したがって、第2の実施形態と重複する内容については、記述を省略する。

【0059】

図5は、本実施形態の半導体装置の構成を示す模式断面図である。図5に示すように、本実施形態の半導体装置は、第2および第3のゲート電極26、28直下の第2の半導体層16の膜厚が、第1のゲート電極22直下の第2の半導体層16の膜厚よりも薄い。

【0060】

すなわち、破線の枠線Bで示される第2のゲート電極26で制御されるトランジスタ構造(構造B)、破線の枠線Cで示される第3のゲート電極28で制御されるトランジスタ構造(構造C)が、いわゆるリセス構造を備えている。

【0061】

本実施形態によれば、構造Bと構造Cとをリセス構造にすることにより、MIS型ゲート電極構造である構造Bおよび構造Cの閾値を高くすることが容易になる。また、リセス構造の深さを変えることにより閾値の調整も容易になる。したがって、構造Aの第1の閾値( $V_{th1}$ )と、構造B、Cの第2および第3の閾値( $V_{th2}$ 、 $V_{th3}$ )との差を最適な値に調整することが容易となる。特に、第1の閾値( $V_{th1}$ )と、第2および第3の閾値( $V_{th2}$ 、 $V_{th3}$ )とを近づけることが容易となる。

【0062】

したがって、ゲートリーク電流を抑制することがより一層容易となるHEMTが実現される。また、閾値変動の小さいHEMTが実現される点においては、第2の実施形態と同様である。

【0063】

(第5の実施形態)

本実施形態の半導体装置は、第2および第3のゲート電極直下の第2の半導体層に、フッ素または塩素を含有する半導体領域を備えること以外は、第1の実施形態と同様である。したがって、第1の実施形態と重複する内容については、記述を省略する。

【0064】

図6は、本実施形態の半導体装置の構成を示す模式断面図である。図6に示すように、本実施形態の半導体装置は、第2および第3のゲート電極26、28直下の第2の半導体層16に、フッ素(F)または塩素(C1)を含有する半導体領域30を備える。

【0065】

半導体領域30は、例えば、フッ素(F)または塩素(C1)を第2の半導体層16にイオン注入することにより形成することが可能である。

【0066】

本実施形態によれば、半導体領域30設けることにより、MIS型ゲート電極構造である構造Bおよび構造Cの閾値を高くすることが可能になる。すなわち、負イオンであるフッ素(F)または塩素(C1)を第2の半導体層16中に導入されることにより、電界を打ち消す作用が生じ、閾値を高くすることが可能になる。

【0067】

また、フッ素(F)または塩素(C1)量を変えることにより閾値の調整も容易になる。したがって、構造Aの第1の閾値( $V_{th1}$ )と、構造B、Cの第2および第3の閾値( $V_{th2}$ 、 $V_{th3}$ )との差を最適な値に調整することが容易となる。特に、第1の閾値( $V_{th1}$ )と、第2および第3の閾値( $V_{th2}$ 、 $V_{th3}$ )とを近づけることが容易となる。

【0068】

したがって、ゲートリーク電流を抑制することがより一層容易となるHEMTが実現される。また、閾値変動の小さいHEMTが実現される点においては、第1の実施形態と同

10

20

30

40

50

様である。

**【0069】**

(第6の実施形態)

本実施形態の半導体装置は、第2および第3のゲート電極直下の第2の半導体層に、フッ素または塩素を含有する半導体領域を備えること以外は、第2の実施形態と同様である。したがって、第2の実施形態と重複する内容については、記述を省略する。

**【0070】**

図7は、本実施形態の半導体装置の構成を示す模式断面図である。図7に示すように、本実施形態の半導体装置は、第2および第3のゲート電極26、28直下の第2の半導体層16に、フッ素(F)または塩素(C1)を含有する半導体領域30を備える。

10

**【0071】**

半導体領域30は、例えば、フッ素(F)または塩素(C1)を第2の半導体層16にイオン注入することにより形成することが可能である。

**【0072】**

本実施形態によれば、半導体領域30設けることにより、MIS型ゲート電極構造である構造Bおよび構造Cの閾値を高くすることが可能になる。すなわち、負イオンであるフッ素(F)または塩素(C1)を第2の半導体層16中に導入されることにより、電界を打ち消す作用が生じ、閾値を高くすることが可能になる。

**【0073】**

また、フッ素(F)または塩素(C1)量を変えることにより閾値の調整も容易になる。したがって、構造Aの第1の閾値(V<sub>th1</sub>)と、構造B、Cの第2および第3の閾値(V<sub>th2</sub>、V<sub>th3</sub>)との差を最適な値に調整することが容易となる。特に、第1の閾値(V<sub>th1</sub>)と、第2および第3の閾値(V<sub>th2</sub>、V<sub>th3</sub>)とを近づけることが容易となる。

20

**【0074】**

したがって、ゲートリーケ電流を抑制することがより一層容易となるHEMTが実現される。また、閾値変動の小さいHEMTが実現される点においては、第2の実施形態と同様である。

**【0075】**

以上の実施形態では、第1ないし第3のゲート電極が物理的に分離された断面構造を例示して説明した。しかしながら、第1ないし第3のゲート電極が物理的に一体化した構造であってもかまわない。

30

**【0076】**

また、以上の実施形態ではHEMTを半導体装置の例として説明したが、HEMT以外の電界効果型トランジスタにも、本発明を適用することが可能である。また、電界効果型トランジスタにショットキバリアダイオード等の素子を組み合わせた集積回路も本発明の半導体装置の範囲に含まれる。

40

**【0077】**

本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。

**【符号の説明】**

**【0078】**

10 基板

12 パッファ層

14 第1の半導体層

16 第2の半導体層

50

- 1 8 ソース電極

2 0 ドレイン電極

2 2 第1のゲート電極

2 2 a 第3の窒化物半導体

2 2 b 金属層

2 4 絶縁層

2 6 第2のゲート電極

2 8 第3のゲート電極

3 0 半導体領域

10

【図3】

【図5】

【図4】

【図6】

【図7】

---

フロントページの続き

|               |           |            |

|---------------|-----------|------------|

| (51) Int.Cl.  | F I       | テーマコード(参考) |

| H 01 L 27/098 | (2006.01) |            |

| H 01 L 29/78  | (2006.01) |            |

| H 01 L 21/336 | (2006.01) |            |

(72)発明者 吉岡 啓

東京都港区芝浦一丁目1番1号 株式会社東芝内

(72)発明者 内原 士

東京都港区芝浦一丁目1番1号 株式会社東芝内

(72)発明者 安本 恭章

東京都港区芝浦一丁目1番1号 株式会社東芝内

(72)発明者 梁瀬 直子

東京都港区芝浦一丁目1番1号 株式会社東芝内

(72)発明者 小野 祐

東京都港区芝浦一丁目1番1号 株式会社東芝内

F ターム(参考) 5F102 GB01 GC01 GC05 GD01 GD04 GD10 GJ02 GJ03 GJ10 GK04

GK08 GL04 GM04 GQ01 GR04 GR07 GR12 GS01 GT01 GT03

GV07 GV08

5F140 AA06 AA24 BA01 BA02 BA06 BA09 BB06 BB16 BB18 BD07

BD09 BD11 BF05 BF07 BF11 BF15 BF46 BJ05