(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6526427号

(P6526427)

(45) 発行日 令和1年6月5日(2019.6.5)

(24) 登録日 令和1年5月17日(2019.5.17)

|                          |                      |

|--------------------------|----------------------|

| (51) Int.Cl.             | F 1                  |

| HO 1 L 21/8234 (2006.01) | HO 1 L 27/088 E      |

| HO 1 L 27/088 (2006.01)  | HO 1 L 29/78 6 1 9 A |

| HO 1 L 21/336 (2006.01)  | HO 1 L 29/78 6 1 8 B |

| HO 1 L 29/786 (2006.01)  | HO 1 L 29/78 6 1 7 L |

| HO 1 L 21/28 (2006.01)   | HO 1 L 29/78 6 2 7 A |

請求項の数 2 (全 60 頁) 最終頁に続く

|              |                               |           |                     |

|--------------|-------------------------------|-----------|---------------------|

| (21) 出願番号    | 特願2015-12993 (P2015-12993)    | (73) 特許権者 | 000153878           |

| (22) 出願日     | 平成27年1月27日(2015.1.27)         |           | 株式会社半導体エネルギー研究所     |

| (65) 公開番号    | 特開2015-164181 (P2015-164181A) |           | 神奈川県厚木市長谷398番地      |

| (43) 公開日     | 平成27年9月10日(2015.9.10)         | (72) 発明者  | 官入 秀和               |

| 審査請求日        | 平成30年1月18日(2018.1.18)         |           | 神奈川県厚木市長谷398番地 株式会社 |

| (31) 優先権主張番号 | 特願2014-15495 (P2014-15495)    |           | 半導体エネルギー研究所内        |

| (32) 優先日     | 平成26年1月30日(2014.1.30)         |           |                     |

| (33) 優先権主張国  | 日本国(JP)                       | 審査官       | 辻 勇貴                |

最終頁に続く

(54) 【発明の名称】半導体装置の作製方法

## (57) 【特許請求の範囲】

## 【請求項 1】

チャネルに単結晶半導体を有する第1のトランジスタを形成し、

前記第1のトランジスタ上に配線を形成し、

前記配線上に第1の絶縁膜を形成し、

前記第1の絶縁膜上に第2の絶縁膜を形成し、

前記第2の絶縁膜上に酸化物半導体膜を形成し、

前記酸化物半導体膜上に第1の電極及び第2の電極を形成し、

前記第2の絶縁膜上、前記第1の電極上及び前記第2の電極上にゲート絶縁膜を形成し、

前記ゲート絶縁膜上にマスクを形成し、

前記マスクを用いて前記配線に達する開口を前記ゲート絶縁膜、前記第1の絶縁膜及び前記第2の絶縁膜に設け、

前記開口を埋めるように第1の導電膜及び第2の導電膜の積層を形成し、

前記第2の導電膜に平坦化処理を行い、

前記第1の導電膜及び前記平坦化処理を行った第2の導電膜をエッティングすることによって、前記ゲート絶縁膜上に第1のゲート電極及び第3の電極、前記第1のゲート電極上に第2のゲート電極、並びに、前記第3の電極上に第4の電極、を形成し、

前記第1の絶縁膜は、水または水素の拡散を低減することができる機能を有することを特徴とする半導体装置の作製方法。

**【請求項 2】**

請求項1において、

前記平坦化処理は、化学機械研磨法であることを特徴とする半導体装置の作製方法。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明の一態様は、電界効果トランジスタを有する半導体装置に関する。

**【0002】**

なお、本発明の一態様は、上記の技術分野に限定されない。本明細書等で開示する発明の一態様の技術分野は、物、方法、または、製造方法に関するものである。または、本発明の一態様は、プロセス、マシン、マニュファクチャ、または、組成物（コンポジション・オブ・マター）に関するものである。そのため、より具体的に本明細書で開示する本発明の一態様の技術分野としては、半導体装置、表示装置、液晶表示装置、発光装置、照明装置、蓄電装置、記憶装置、それらの駆動方法、または、それらの製造方法、を一例として挙げることができる。10

**【0003】**

なお、本明細書等において、半導体装置とは、半導体特性を利用することで機能しうる装置全般を指す。トランジスタなどの半導体素子をはじめ、半導体回路、演算装置、記憶装置は、半導体装置の一態様である。撮像装置、表示装置、液晶表示装置、発光装置、電気光学装置、発電装置（薄膜太陽電池、有機薄膜太陽電池等を含む）、及び電子機器は、20半導体装置を有している場合がある。

**【背景技術】****【0004】**

半導体材料を用いてトランジスタを構成する技術が注目されている。該トランジスタは集積回路（IC）や画像表示装置（単に表示装置とも表記する）のような電子デバイスに広く応用されている。トランジスタに適用可能な半導体材料としてシリコン系半導体材料が広く知られているが、その他の材料として酸化物半導体が注目されている。

**【0005】**

例えば、酸化物半導体として酸化亜鉛、またはIn-Ga-Zn系酸化物半導体を用いてトランジスタを作製する技術が開示されている（特許文献1及び特許文献2参照）。30

**【0006】**

また、近年では電子機器の高性能化、小型化、または軽量化に伴い、微細化されたトランジスタなどの半導体素子を高密度に集積した集積回路の要求が高まっている。

**【先行技術文献】****【特許文献】****【0007】**

【特許文献1】特開2007-123861号公報

【特許文献2】特開2007-96055号公報

**【発明の概要】****【発明が解決しようとする課題】****【0008】**

本発明の一態様は、微細化に適した半導体装置を提供することを課題の一とする。

**【0009】**

または、半導体装置に良好な電気特性を付与することを課題の一とする。または、信頼性の高い半導体装置を提供することを課題の一とする。または、新規な構成の半導体装置を提供することを課題の一とする。

**【0010】**

なお、これらの課題の記載は、他の課題の存在を妨げるものではない。なお、本発明の一態様は、これらの課題の全てを解決する必要はないものとする。なお、これら以外の課題は、明細書、図面、請求項などの記載から、自ずと明らかとなるものであり、明細書、50

図面、請求項などの記載から、これら以外の課題を抽出することが可能である。

【課題を解決するための手段】

【0011】

本発明の一態様は、第1のトランジスタと、第1のトランジスタの上方に位置する第2のトランジスタと、第1のトランジスタと第2のトランジスタとの間に位置する絶縁膜と、第1のトランジスタと絶縁膜との間に位置する配線と、電極と、を有し、電極と配線とは、互いに重なる領域を有し、絶縁膜は、水または水素の拡散を低減することができる機能を有し、第1のトランジスタのチャネルは、単結晶半導体を有し、第2のトランジスタのチャネルは、酸化物半導体を有し、第2のトランジスタのゲート電極は、電極が有する材料と同じ材料を含むことを特徴とする半導体装置である。

10

【0012】

また、本発明の他の一態様は、第1のトランジスタと、第1のトランジスタの上方に位置する第2のトランジスタと、第1のトランジスタと第2のトランジスタとの間に位置する絶縁膜と、第1のトランジスタと絶縁膜との間に位置する配線と、電極と、を有し、電極と配線とは、互いに重なる領域を有し、絶縁膜は、水または水素の拡散を低減することができる機能を有し、第1のトランジスタのゲート電極と、配線と、電極と、第2のトランジスタのソースまたはドレインの一方とは、互いに電気的に接続され、第1のトランジスタのチャネルは、単結晶半導体を有し、第2のトランジスタのチャネルは、酸化物半導体を有し、第2のトランジスタのゲート電極は、電極が有する材料と同じ材料を含むことを特徴とする半導体装置である。

20

【0013】

また、上記構成において、第2のトランジスタのゲート電極の上面の高さと電極の上面の高さとが揃っていてもよい。

【0014】

また、上記構成において、第2のトランジスタと絶縁膜との間に、第2の絶縁膜を有し、第2の絶縁膜は、化学量論的組成を満たす酸素よりも多くの酸素を含む領域を有すると好ましい。

【0015】

また、上記構成において、電極は、複数の膜を有し、第2のトランジスタのゲート電極は、複数の膜を有すると好ましい。

30

【0016】

また、上記構成の電極が有する複数の膜において、配線に接する領域を有する膜は仕事関数を調整する機能を有することが好ましい。

【0017】

また、上記構成において、第2のトランジスタは、第2のゲート電極を有し、第2のゲート電極は、配線が有する材料と同じ材料を含んでもよい。

【0018】

また、本発明の他の一態様は、上記の半導体装置と、表示装置と、を有することを特徴とする電子機器である。

【0019】

また、本発明の他の一態様は、チャネルに単結晶半導体を有する第1のトランジスタを形成し、第1のトランジスタ上に配線を形成し、配線上に第1の絶縁膜を形成し、第1の絶縁膜上に第2の絶縁膜を形成し、第2の絶縁膜上に酸化物半導体膜を形成し、酸化物半導体膜上に第1の電極及び第2の電極を形成し、第2の絶縁膜上、第1の電極上及び第2の電極上にゲート絶縁膜を形成し、ゲート絶縁膜上にマスクを形成し、マスクを用いて配線に達する開口をゲート絶縁膜、第1の絶縁膜及び第2の絶縁膜に設け、開口を埋めるように第1の導電膜及び第2の導電膜の積層を形成し、第2の導電膜に平坦化処理を行い、第1の導電膜及び平坦化処理を行った第2の導電膜をエッティングすることによって、ゲート絶縁膜上に第1のゲート電極及び第3の電極、第1のゲート電極上に第2のゲート電極、並びに、第3の電極上に第4の電極、を形成し、第1の絶縁膜は、水または水素の拡散

40

50

を低減することができる機能を有することを特徴とする半導体装置の作製方法である。

【0020】

また、上記作製方法において、平坦化処理は、化学機械研磨法であってもよい。

【発明の効果】

【0021】

本発明の一態様によれば、微細化に適した半導体装置を提供することができる。

【0022】

または、半導体装置に良好な電気特性を付与することができる。または、信頼性の高い半導体装置を提供することができる。または、新規な構成の半導体装置を提供することができる。なお、これらの効果の記載は、他の効果の存在を妨げるものではない。なお、本発明の一態様は、必ずしも、これらの効果の全てを有する必要はない。なお、これら以外の効果は、明細書、図面、請求項などの記載から、自ずと明らかとなるものであり、明細書、図面、請求項などの記載から、これら以外の効果を抽出することが可能である。

【図面の簡単な説明】

【0023】

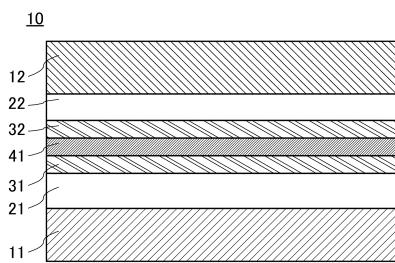

【図1】実施の形態に係る、半導体装置に含まれる積層構造を説明する図。

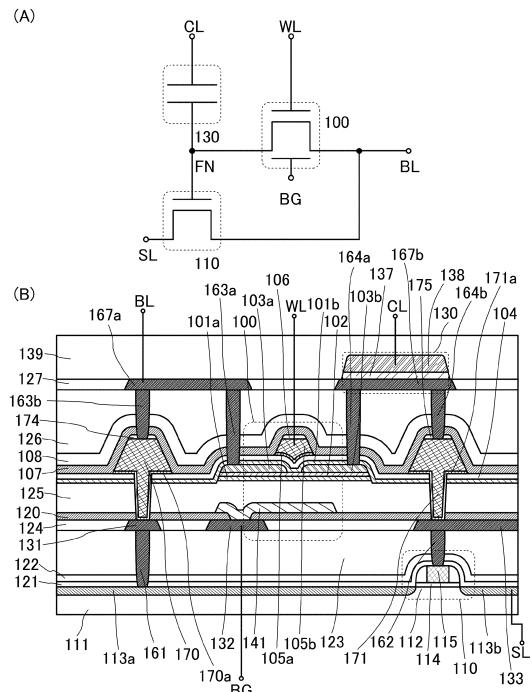

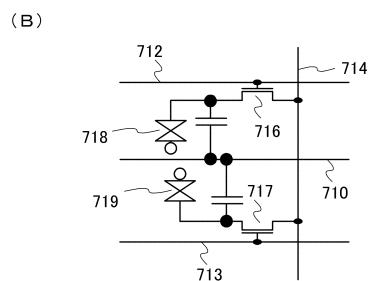

【図2】実施の形態に係る、半導体装置の回路図及び構成例。

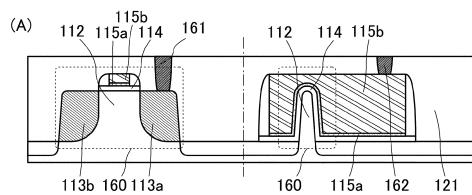

【図3】実施の形態に係る、半導体装置の構成例。

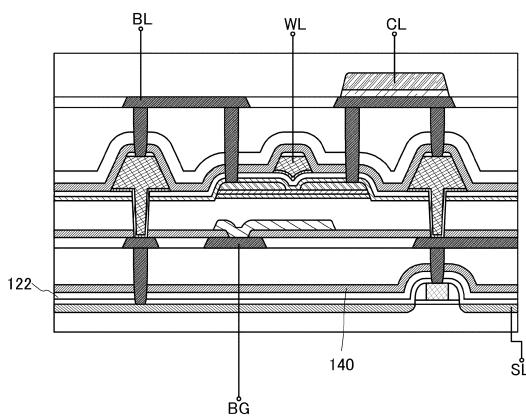

【図4】実施の形態に係る、半導体装置の構成例。

【図5】実施の形態に係る、バンド構造を説明する図。

【図6】実施の形態に係る、半導体装置の構成例。

【図7】実施の形態に係る、半導体装置の構成例。

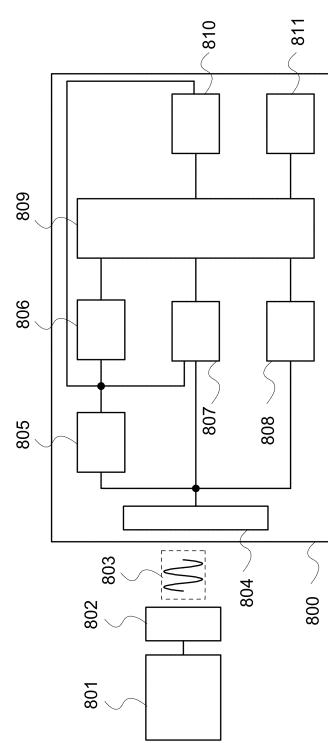

【図8】実施の形態に係る、半導体装置の構成例。

【図9】実施の形態に係る、半導体装置の構成例。

【図10】実施の形態に係る、半導体装置の構成例。

【図11】実施の形態に係る、半導体装置の構成例。

【図12】実施の形態に係る、半導体装置の構成例。

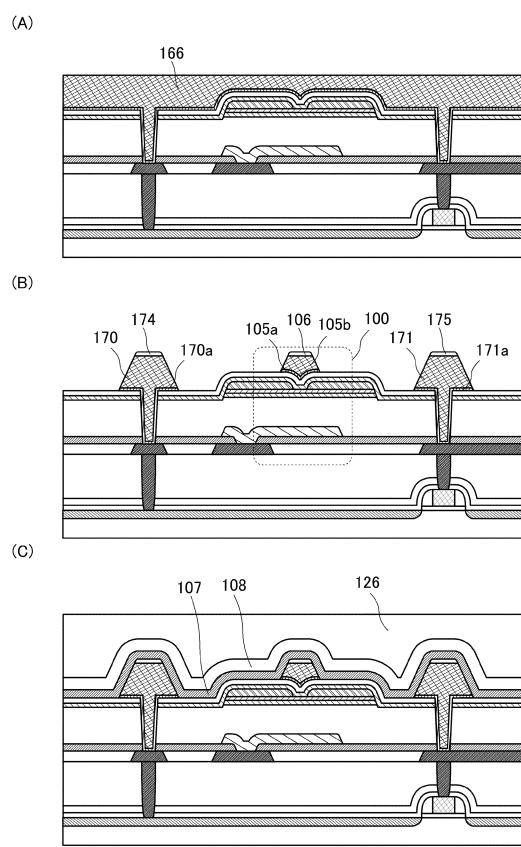

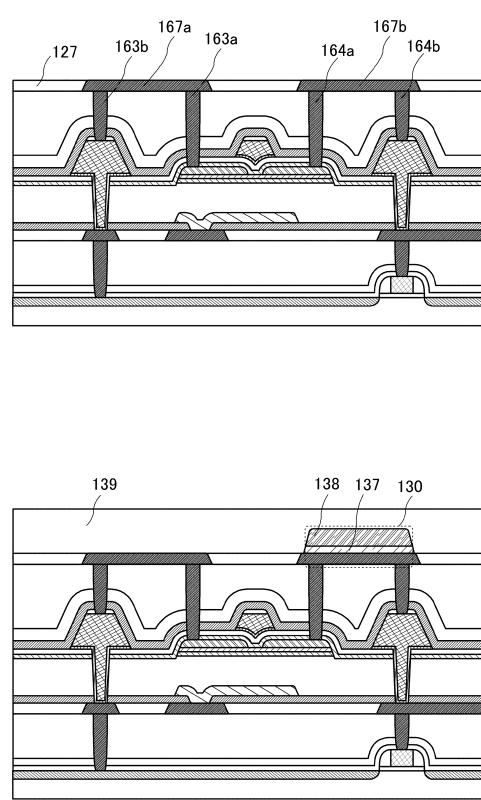

【図13】実施の形態に係る、半導体装置の作製方法例を説明する図。

【図14】実施の形態に係る、半導体装置の作製方法例を説明する図。

【図15】実施の形態に係る、半導体装置の作製方法例を説明する図。

【図16】実施の形態に係る、半導体装置の作製方法例を説明する図。

【図17】C A A C - O S の断面における C s 補正高分解能 TEM 像、および C A A C - O S の断面模式図。

【図18】C A A C - O S の平面における C s 補正高分解能 TEM 像。

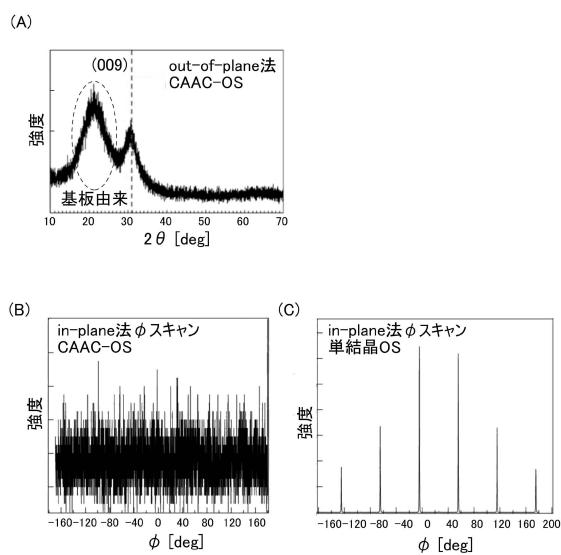

【図19】C A A C - O S および単結晶酸化物半導体の X R D による構造解析を説明する図。

【図20】C A A C - O S の電子回折パターンを示す図。

【図21】I n - G a - Z n 系酸化物の電子照射による結晶部の変化を示す図。

【図22】実施の形態に係る、回路図。

【図23】実施の形態に係る、R F タグの構成例。

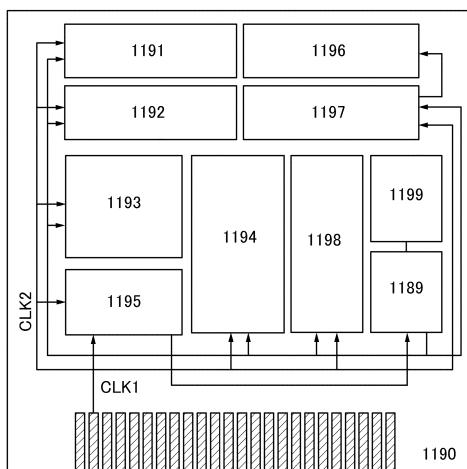

【図24】実施の形態に係る、C P U の構成例。

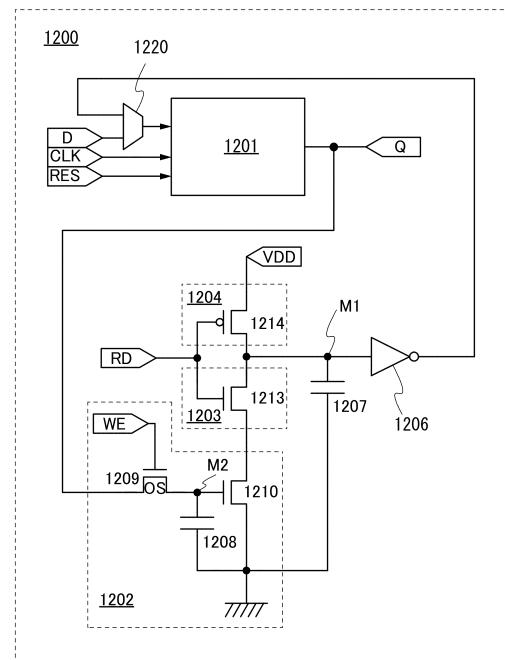

【図25】実施の形態に係る、記憶素子の回路図。

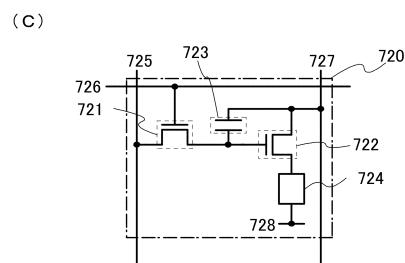

【図26】実施の形態に係る、表示装置の上面図及び回路図。

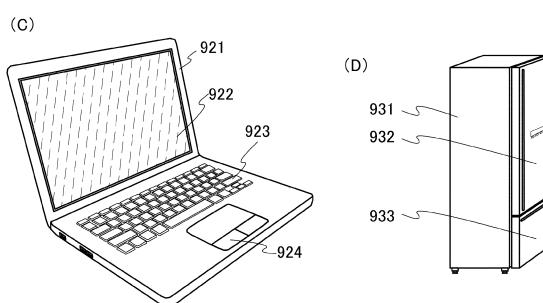

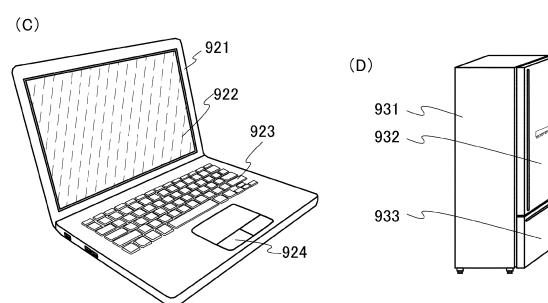

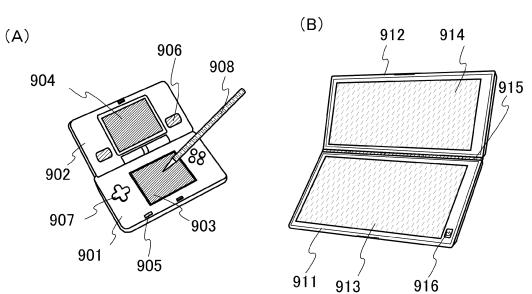

【図27】実施の形態に係る、電子機器。

【図28】実施の形態に係る、R F デバイスの使用例。

【発明を実施するための形態】

【0024】

実施の形態について、図面を用いて詳細に説明する。但し、本発明は以下の説明に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本発明は以下に示す実施の形態

10

20

30

40

50

の記載内容に限定して解釈されるものではない。

【0025】

なお、以下に説明する発明の構成において、同一部分又は同様な機能を有する部分には同一の符号を異なる図面間で共通して用い、その繰り返しの説明は省略する。また、同様の機能を指す場合には、ハッチパターンを同じくし、特に符号を付さない場合がある。

【0026】

なお、本明細書で説明する各図において、各構成の大きさ、層の厚さ、または領域は、明瞭化のために誇張されている場合がある。よって、必ずしもそのスケールに限定されない。

【0027】

なお、本明細書等における「第1」、「第2」等の序数詞は、構成要素の混同を避けるために付すものであり、数的に限定するものではない。

10

【0028】

トランジスタは半導体素子の一種であり、電流や電圧の増幅や、導通または非導通を制御するスイッチング動作などを実現することができる。本明細書におけるトランジスタは、IGFET (Insulated Gate Field Effect Transistor) や薄膜トランジスタ (TFT : Thin Film Transistor) を含む。

【0029】

なお、本明細書において、「膜」という表記と、「層」という表記と、を互いに入れ替えることが可能である。また、「絶縁体」という表記と、「絶縁膜（または絶縁層）」という表記と、を互いに入れ替えることが可能である。また、「導電体」という表記と、「導電膜（または導電層）」という表記と、を互いに入れ替えることが可能である。また、「半導体」という表記は、「半導体膜（または半導体層）」という表記と、を互いに入れ替えることが可能である。

20

【0030】

本明細書において、「平行」とは、二つの直線が -10° 以上 10° 以下の角度で配置されている状態をいう。したがって、-5° 以上 5° 以下の場合も含まれる。また、「略平行」とは、二つの直線が -30° 以上 30° 以下の角度で配置されている状態をいう。また、「垂直」とは、二つの直線が 80° 以上 100° 以下の角度で配置されている状態をいう。したがって、85° 以上 95° 以下の場合も含まれる。また、「略垂直」とは、二つの直線が 60° 以上 120° 以下の角度で配置されている状態をいう。

30

【0031】

また、本明細書において、結晶が三方晶または菱面体晶である場合、六方晶系として表す。

【0032】

(実施の形態1)

[積層構造の構成例]

以下では、本発明の一態様の半導体装置に適用することのできる積層構造の例について説明する。図1は、以下で示す積層構造10の断面概略図である。

40

【0033】

積層構造10は、第1のトランジスタを含む第1の層11、第1の絶縁膜21、第1の配線層31、バリア膜41、第2の配線層32、第2の絶縁膜22、及び第2のトランジスタを含む第2の層12が、順に積層された積層構造を有している。

【0034】

第1の層11に含まれる第1のトランジスタは、第1の半導体材料を含んで構成される。また、第2の層12に含まれる第2のトランジスタは、第2の半導体材料を含んで構成される。第1の半導体材料と第2の半導体材料は、同一の材料であってもよいが、異なる半導体材料とすることが好ましい。第1のトランジスタ及び第2のトランジスタは、それぞれ半導体膜、ゲート電極、ゲート絶縁膜、ソース電極及びドレイン電極（またはソース

50

領域及びドレイン領域)を有する。

【0035】

例えば、第1の半導体材料、または第2の半導体材料として用いることのできる半導体としては、例えば、シリコンや炭化ケイ素、ゲルマニウム、ヒ化ガリウム、ガリウムヒ素リジン、窒化ガリウム等の半導体材料、III-V族半導体材料の代表的な半導体材料として、B、Al、Ga、In、Tlから選択された一つ以上とN、P、As、Sbから選択された一つ以上を組み合わせた化合物半導体材料、II-VI族半導体材料の代表的な半導体材料として、Mg、Zn、Cd、Hgから選択された一つ以上とO、S、Se、Teから選択された一つ以上を組み合わせた化合物半導体材料、有機半導体材料、または酸化物半導体材料などが挙げられる。

10

【0036】

ここでは、第1の半導体材料として単結晶シリコンを、第2の半導体材料として酸化物半導体を用いた場合について説明する。

【0037】

バリア膜41は、これよりも下層から水及び水素が上層に拡散することを抑制する機能を有する層である。なお、バリア膜41はこの上方に設けられる電極または配線と、下方に設けられる電極または配線とを電気的に接続するための開口やプラグを有していてもよい。例えば、第1の配線層31に含まれる配線または電極と、第2の配線層32に含まれる配線または電極とを電気的に接続するプラグを有する。

【0038】

第1の配線層31及び第2の配線層32に含まれる配線または電極に用いる材料としては、金属または合金材料のほか、導電性の金属窒化物を用いることができる。また、このような材料を含む層を単層で、若しくは2層以上積層して用いてもよい。

20

【0039】

第1の絶縁膜21は第1の層11と第1の配線層31とを電気的に絶縁する機能を有する。また、第1の絶縁膜21には、第1の層11に含まれる第1のトランジスタ、電極または配線と、第1の配線層31に含まれる電極または配線とを電気的に接続するための開口やプラグを有していてもよい。

【0040】

第2の絶縁膜22は、第2の層12と第2の配線層32とを電気的に絶縁する機能を有する。また、第2の絶縁膜22には、第2の層12に含まれる第2のトランジスタ、電極または配線と、第2の配線層32に含まれる電極または配線とを電気的に接続するための開口やプラグを有していてもよい。

30

【0041】

また、第2の絶縁膜22は、酸化物を含むことが好ましい。特に加熱により一部の酸素が脱離する酸化物材料を含むことが好ましい。好適には、化学量論的組成を満たす酸素よりも多くの酸素を含む酸化物を用いることが好ましい。第2の半導体材料として酸化物半導体を用いた場合、第2の絶縁膜22から脱離した酸素が酸化物半導体に供給され、酸化物半導体中の酸素欠損を低減することが可能となる。その結果、第2のトランジスタの電気特性の変動を抑制し、信頼性を高めることができる。

40

【0042】

ここで、バリア膜41よりも下層では、水素や水などを出来る限り低減させておくことが好ましい。水素や水は酸化物半導体にとって電気特性の変動を引き起こす要因となりうる。また、バリア膜41を介して下層から上層へ拡散する水素や水は、バリア膜41により抑制することができるが、バリア膜41に設けられる開口やプラグ等を介して水素や水が上層に拡散してしまう場合がある。

【0043】

バリア膜41よりも下層に位置する各層に含まれる水素や水を低減させるため、バリア膜41を形成する前、またはバリア膜41にプラグを形成するための開口を形成した直後に、バリア膜41よりも下層に含まれる水素や水を除去するための加熱処理を施すことが

50

好ましい。半導体装置を構成する導電膜などの耐熱性や、トランジスタの電気特性が劣化しない程度であれば、加熱処理の温度は高いほど好ましい。具体的には、例えば450以上、好ましくは490以上、より好ましくは530以上の温度とすればよいが、650以上で行ってもよい。不活性ガス雰囲気下または減圧雰囲気下で1時間以上、好ましくは5時間以上、より好ましくは10時間以上の加熱処理を行うことが好ましい。また、加熱処理の温度は第1の層11や第1の配線層31に含まれる配線または電極の材料、及び第1の絶縁膜21に設けられるプラグの材料の耐熱性を考慮して決定すればよいが、例えば当該材料の耐熱性が低い場合には、550以下、または600以下、または650以下、または800以下の温度で行えばよい。また、このような加熱処理は、少なくとも1回以上行えばよいが、複数回行うとより好ましい。

10

#### 【0044】

バリア膜41より下層に設けられる絶縁膜は、昇温脱離ガス分光法分析(TDS分析ともよぶ)によって測定される、基板表面温度が400での水素分子( $m/z = 2$ )の脱離量が、300での水素分子の脱離量の130%以下が好ましく、110%以下であることがより好ましい。または、TDS分析によって測定される基板表面温度が450での水素分子の脱離量が、350での水素分子の脱離量の130%以下が好ましく、110%以下であることがより好ましい。

#### 【0045】

また、バリア膜41自体に含まれる水や水素も低減されていることが好ましい。例えばバリア膜41として、TDS分析によって測定される基板表面温度が20から600の範囲における水素分子の脱離量が、 $2 \times 10^{15}$ 個/ $\text{cm}^2$ 未満、好ましくは $1 \times 10^{15}$ 個/ $\text{cm}^2$ 未満、より好ましくは $5 \times 10^{14}$ 個/ $\text{cm}^2$ 未満である材料を用いることが好ましい。または、TDS分析によって測定される基板表面温度が20から600の範囲における水分子( $m/z = 18$ )の脱離量が、 $1 \times 10^{16}$ 個/ $\text{cm}^2$ 未満、好ましくは $5 \times 10^{15}$ 個/ $\text{cm}^2$ 未満、より好ましくは $2 \times 10^{12}$ 個/ $\text{cm}^2$ 未満である材料をバリア膜41に用いることが好ましい。

20

#### 【0046】

また、第1の層11に含まれる第1のトランジスタの半導体膜に単結晶シリコンを用いた場合には、当該加熱処理は、シリコンの不対結合手(ダングリングボンドともいう)を水素によって終端化する処理(水素化処理とも呼ぶ)を兼ねることができる。水素化処理により第1の層11及び第1の絶縁膜21に含まれる水素の一部が脱離して第1のトランジスタの半導体膜に拡散し、シリコン中のダングリングボンドを終端させることで、第1のトランジスタの信頼性を向上させることができる。

30

#### 【0047】

バリア膜41に用いることのできる材料としては、窒化シリコン、窒化酸化シリコン、酸化アルミニウム、酸化窒化アルミニウム、酸化ガリウム、酸化窒化ガリウム、酸化イットリウム、酸化窒化イットリウム、酸化ハフニウム、酸化窒化ハフニウムなどが挙げられる。特に、酸化アルミニウムは水や水素に対するバリア性に優れているため好ましい。

#### 【0048】

バリア膜41は水や水素を透過しにくい材料の膜のほかに、他の絶縁材料を含む膜を積層させて用いてもよい。例えば、酸化シリコンまたは酸化窒化シリコンを含む膜、金属酸化物を含む膜などを積層させて用いてもよい。

40

#### 【0049】

また、バリア膜41は、酸素を透過しにくい材料を用いることが好ましい。上述した材料は、水素、水に加え酸素に対してもバリア性に優れた材料である。このような材料を用いることで、第2の絶縁膜22を加熱した時に放出される酸素がバリア膜41よりも下層に拡散することを抑制することができる。その結果、第2の絶縁膜22から放出され、第2の層12中の第2のトランジスタの半導体膜に供給されうる酸素の量を増大させることができる。

#### 【0050】

50

このように、バリア膜41よりも下層に位置する各層に含まれる水素や水の濃度を減少する、または水素や水を除去することでバリア膜41により水素や水が第2の層12へ拡散することを抑制する。また、バリア膜41は、水素や水の放出を抑制する。そのため、第2の絶縁膜22や、第2の層12に含まれる第2のトランジスタを構成する各層における水素及び水の含有量を、極めて低いものとすることができます。例えば、第2の絶縁膜22、第2のトランジスタの半導体膜、またはゲート絶縁膜に含まれる水素濃度を $5 \times 10^{-8} \text{ cm}^{-3}$ 未満、好ましくは $1 \times 10^{-8} \text{ cm}^{-3}$ 未満、さらに好ましくは $3 \times 10^{-7} \text{ cm}^{-3}$ 未満にまで低減することができる。

#### 【0051】

本発明の一態様の半導体装置に、上記積層構造10を適用することにより、第1の層11に含まれる第1のトランジスタと、第2の層12に含まれる第2のトランジスタのいずれにおいても、高い信頼性を両立することが可能となり、極めて信頼性の高い半導体装置を実現できる。

#### 【0052】

##### [構成例]

図2(A)は、本発明の一態様の半導体装置の回路図の一例である。図2(A)に示す半導体装置は、第1のトランジスタ110と、第2のトランジスタ100と、容量130と、配線SLと、配線BLと、配線WLと、配線CLと、配線BGと、を有する。

#### 【0053】

第1のトランジスタ110は、ソースまたはドレインの一方が配線BLと電気的に接続し、他方が配線SLと電気的に接続し、ゲートが第2のトランジスタ100のソースまたはドレインの一方及び容量130の一方の電極と電気的に接続する。第2のトランジスタ100は、ソースまたはドレインの他方が配線BLと電気的に接続し、ゲートが配線WLと電気的に接続する。容量130は、他方の電極が配線CLと電気的に接続する。また、配線BGは第2のトランジスタ100の第2のゲートと電気的に接続する。なお、第1のトランジスタ110のゲートと、第2のトランジスタ100のソースまたはドレインの一方と、容量130の一方の電極の間のノードをノードFNと呼ぶ。

#### 【0054】

図2(A)に示す半導体装置は、第2のトランジスタ100が導通状態(オン状態)の時に配線BLの電位に応じた電位を、ノードFNに与える。また、第2のトランジスタ100が非導通状態(オフ状態)のときに、ノードFNの電位を保持する機能を有する。すなわち、図2(A)に示す半導体装置は、記憶装置のメモリセルとしての機能を有する。なお、ノードFNと電気的に接続する液晶素子や有機EL(Electroluminescence)素子などの表示素子を有する場合、図2(A)の半導体装置は表示装置の画素として機能させることもできる。

#### 【0055】

第2のトランジスタ100の導通状態、非導通状態の選択は、配線WLまたは配線BGに与える電位によって制御することができる。また、配線WLまたは配線BGに与える電位によって第2のトランジスタ100のしきい値電圧を制御することができる。第2のトランジスタ100として、オフ電流の小さいトランジスタを用いることによって、非導通状態におけるノードFNの電位を長期間に渡って保持することができる。したがって、半導体装置のリフレッシュ頻度を低減することができるため、消費電力の小さい半導体装置を実現することができる。なお、オフ電流の小さいトランジスタの一例として、酸化物半導体を用いたトランジスタが挙げられる。

#### 【0056】

なお、配線CLには基準電位や接地電位、または任意の固定電位などの定電位が与えられる。このとき、ノードFNの電位によって、第2のトランジスタ100の見かけ上のしきい値電圧が変動する。見かけ上のしきい値電圧の変動により、第1のトランジスタ110の導通状態、非導通状態が変化することを利用し、ノードFNに保持された電位の情報をデータとして読み出すことができる。

10

20

30

40

50

## 【0057】

本発明の一態様の半導体装置は、バリア膜よりも下層の水素濃度が十分に低減されている、もしくは、水素の拡散・放出が抑制されているため、その結果、その上層の酸化物半導体を用いたトランジスタは、極めて低いオフ電流を実現することができる。

## 【0058】

図2(A)に示す半導体装置をマトリクス状に配置することで、記憶装置(メモリセルアレイ)を構成することができる。

## 【0059】

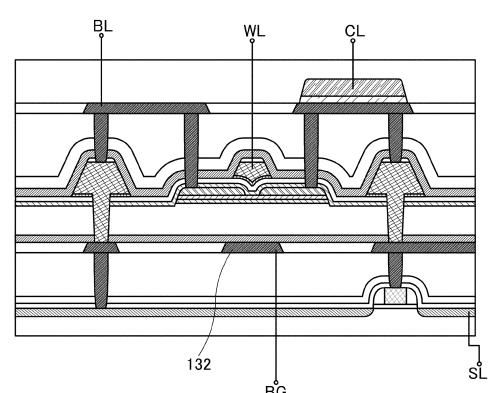

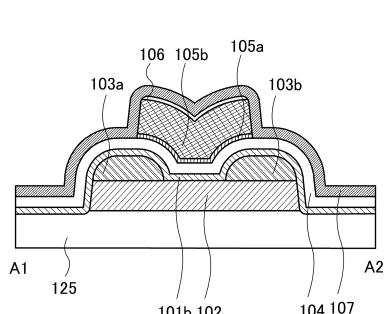

図2(B)に、図2(A)で示した回路を実現可能な半導体装置の断面構成の一例を示す。

10

## 【0060】

半導体装置は、第1のトランジスタ110、第2のトランジスタ100、及び容量130を有する。第2のトランジスタ100は第1のトランジスタ110の上方に設けられ、第1のトランジスタ110と第2のトランジスタ100の間にはバリア膜120が設けられている。

## 【0061】

## 〔第1の層〕

第1のトランジスタ110は、半導体基板111上に設けられ、半導体基板111の一部からなる半導体膜112、ゲート絶縁膜114、ゲート電極115、及びソース領域またはドレイン領域として機能する低抵抗層113a及び低抵抗層113bを有する。

20

## 【0062】

第1のトランジスタ110は、pチャネル型、nチャネル型のいずれでもよいが、回路構成や駆動方法に応じて適切なトランジスタを用いればよい。

## 【0063】

半導体膜112のチャネルが形成される領域やその近傍の領域や、ソース領域またはドレイン領域となる低抵抗層113a及び低抵抗層113b等において、シリコン系半導体などの半導体を含むことが好ましく、単結晶シリコンを含むことが好ましい。または、Ge(ゲルマニウム)、SiGe(シリコンゲルマニウム)、GaAs(ガリウムヒ素)、GaAlAs(ガリウムアルミニウムヒ素)などを有する材料で形成してもよい。結晶格子に応力を与え、格子間隔を変化させることで有効質量を制御したシリコンを用いた構成としてもよい。またはGaAsとGaAlAs等を用いることで、第1のトランジスタ110をHEMT(High Electron Mobility Transistor)としてもよい。

30

## 【0064】

低抵抗層113a及び低抵抗層113bは、半導体膜112に適用される半導体材料に加え、ヒ素、リンなどのn型の導電性を付与する元素、またはホウ素などのp型の導電性を付与する元素を含む。

## 【0065】

ゲート電極115は、ヒ素、リンなどのn型の導電性を付与する元素、もしくはホウ素などのp型の導電性を付与する元素を含むシリコンなどの半導体材料、金属材料、合金材料、または金属酸化物材料などの導電性材料を用いることができる。耐熱性と導電性を両立するタンゲステンやモリブデンなどの高融点材料を用いることが好ましく、特にタンゲステンを用いることが好ましい。

40

## 【0066】

ここで、第1のトランジスタ110を含む構成が、上記積層構造10における第1の層11に対応する。

## 【0067】

ここで、第1のトランジスタ110に換えて図3(A)に示すようなトランジスタ160を用いてもよい。図3(A)の左側にトランジスタ160のチャネル長方向の断面を、右側にチャネル幅方向の断面を示す。図3(A)に示すトランジスタ160はチャネルが

50

形成される半導体膜 112 (半導体基板の一部) が凸形状を有し、その側面及び上面に沿ってゲート絶縁膜 114、ゲート電極 115a 及びゲート電極 115b が設けられている。なお、ゲート電極 115a は仕事関数を調整する材料を用いてもよい。このようなトランジスタ 160 は半導体基板の凸部を利用していることから FIN 型トランジスタとも呼ばれる。なお、凸部の上部に接して、凸部を形成するためのマスクとして機能する絶縁膜を有していてもよい。また、ここでは半導体基板の一部を加工して凸部を形成する場合を示したが、SOI 基板を加工して凸形状を有する半導体膜を形成してもよい。

#### 【0068】

##### 〔第1の絶縁膜〕

第1のトランジスタ 110 を覆って、絶縁膜 121、絶縁膜 122、及び絶縁膜 123 が順に積層して設けられている。

10

#### 【0069】

半導体膜 112 にシリコン系半導体材料を用いた場合、絶縁膜 122 は水素を含むことが好ましい。水素を含む絶縁膜 122 を第1のトランジスタ 110 上に設け、加熱処理を行うことで絶縁膜 122 中の水素により半導体膜 112 中のダンギングボンドが終端され、第1のトランジスタ 110 の信頼性を向上させることができる。

#### 【0070】

絶縁膜 123 はその下層に設けられる第1のトランジスタ 110 などによって生じる段差を平坦化する平坦化膜として機能する。絶縁膜 123 の上面は、平坦性を高めるために化学機械研磨 (CMP : Chemical Mechanical Polishing) 法等を用いた平坦化処理により平坦化されていてもよい。

20

#### 【0071】

また、絶縁膜 121、絶縁膜 122、絶縁膜 123 には低抵抗層 113a や低抵抗層 113b 等と電気的に接続するプラグ 161、第1のトランジスタ 110 のゲート電極 115 と電気的に接続するプラグ 162 等が埋め込まれていてもよい。なお、本明細書等において、電極と、電極と電気的に接続する配線とが一体物であってもよい。すなわち、配線の一部が電極として機能する場合や、電極の一部が配線として機能する場合もある。

#### 【0072】

絶縁膜 121、絶縁膜 122、絶縁膜 123 を含む構成が、上記積層構造 10 における第1の絶縁膜 21 に相当する。

30

#### 【0073】

##### 〔第1の配線層〕

絶縁膜 123 の上部には、配線 131、配線 132 及び配線 133 等が設けられている。

#### 【0074】

配線 131 はプラグ 161 と電気的に接続する。また、配線 133 はプラグ 162 と電気的に接続する。

#### 【0075】

ここで、配線 131、配線 132 及び配線 133 等を含む構成が、上記積層構造 10 における第1の配線層 31 に相当する。

40

#### 【0076】

配線 131、配線 132 及び配線 133 等の材料としては、金属材料、合金材料、または金属酸化物材料などの導電性材料を用いることができる。耐熱性と導電性を両立するタンクステンやモリブデンなどの高融点材料を用いることが好ましく、特にタンクステンを用いることが好ましい。

#### 【0077】

また、配線 131、配線 132 及び配線 133 等は、絶縁膜 124 に埋め込まれるように設けられ、絶縁膜 124 と配線 131、配線 132 及び配線 133 等の各々の上面は平坦化されていることが好ましい。

#### 【0078】

50

## 【バリア膜】

バリア膜120は、絶縁膜124、配線131、配線132及び配線133等の上面を覆って設けられている。バリア膜120は、上記積層構造10におけるバリア膜41に相当する。バリア膜120の材料としては、上記バリア膜41についての記載を援用できる。

## 【0079】

また、バリア膜120は配線132と後述する配線141とを電気的に接続するための開口を有している。

## 【0080】

## 【第2の配線層】

10

バリア膜120上に、配線141が設けられている。配線141を含む構成が、上記積層構造10における第2の配線層32に相当する。

## 【0081】

配線141は、バリア膜120に設けられた開口を介して配線132と電気的に接続する。配線141の一部は後述する第2のトランジスタ100のチャネル形成領域に重畠して設けられ、第2のトランジスタ100の第2のゲート電極としての機能を有する。

## 【0082】

なお、図4(A)に示すように、第2のトランジスタ100の第2のゲート電極として、配線132を用いる構成としてもよい。

## 【0083】

20

ここで、配線141等を構成する材料としては、金属材料、合金材料、または金属酸化物材料などの導電性材料を用いることができる。特に、耐熱性を要する場合にはタンゲステンやモリブデンなどの高融点材料を用いることが好ましい。また、導電性を考慮すると、低抵抗な金属材料または合金材料を用いることが好ましく、アルミニウム、クロム、銅、タンタル、チタンなどの金属材料、または当該金属材料を含む合金材料を単層で、または積層して用いてもよい。

## 【0084】

また、配線141等を構成する材料として、リン、ホウ素、炭素、窒素、または遷移金属元素などの主成分以外の元素を含む金属酸化物を用いることが好ましい。このような金属酸化物は、高い導電性を実現できる。例えば、In-Ga系酸化物、In-Zn系酸化物、In-M-Zn系酸化物(MはAl、Ti、Ga、Y、Zr、La、Ce、NdまたはHf)などの金属酸化物に、上述の元素を含ませて導電性を高めた材料を用いることができる。さらに、このような金属酸化物は酸素を透過しにくいため、バリア膜120に設けられる開口をこのような材料を含む配線141で覆うことで、後述する絶縁膜125を加熱処理したときに放出される酸素が、バリア膜120よりも下方へ拡散することを抑制することができる。その結果、絶縁膜125から放出され、第2のトランジスタ100の半導体膜へ供給されうる酸素の量を増大させることができる。

30

## 【0085】

なお、図4(B)に示すように、配線141と同時に成膜されて、同時にエッチングされる配線141a、配線141bを設けてもよい。配線141a、配線141bは、配線131、配線133などと接続されている。

40

## 【0086】

## 【第2の絶縁膜】

バリア膜120、配線141を覆って、絶縁膜125が設けられている。ここで絶縁膜125を含む領域が上記積層構造10における第2の絶縁膜22に相当する。

## 【0087】

絶縁膜125の上面は上述した平坦化処理によって平坦化されていることが好ましい。

## 【0088】

絶縁膜125は、加熱により一部の酸素が脱離する酸化物材料を用いることが好ましい。

50

## 【0089】

加熱により酸素を脱離する酸化物材料として、化学量論的組成を満たす酸素よりも多くの酸素を含む酸化物を用いることが好ましい。化学量論的組成を満たす酸素よりも多くの酸素を含む酸化物膜は、加熱により一部の酸素が脱離する。化学量論的組成を満たす酸素よりも多くの酸素を含む酸化物膜は、TDS分析にて、酸素原子に換算しての酸素の脱離量が  $1.0 \times 10^{18}$  atoms/cm<sup>3</sup> 以上、好ましくは  $3.0 \times 10^{20}$  atoms/cm<sup>3</sup> 以上である酸化物膜である。なお、上記TDS分析時における膜の表面温度としては 100 以上 700 以下、または 100 以上 500 以下の範囲が好ましい。

## 【0090】

例えはこのような材料として、酸化シリコンまたは酸化窒化シリコンを含む材料を用いることが好ましい。または、金属酸化物を用いることもできる。なお、本明細書中において、酸化窒化シリコンとは、その組成として窒素よりも酸素の含有量が多い材料を指し、窒化酸化シリコンとは、その組成として、酸素よりも窒素の含有量が多い材料を示す。

## 【0091】

## 〔第2の層〕

絶縁膜125の上部には、第2のトランジスタ100が設けられている。第2のトランジスタ100を含む構成が、上記積層構造10における第2の層12に相当する。

## 【0092】

第2のトランジスタ100は、絶縁膜125の上面に接する酸化物膜101aと、酸化物膜101aの上面に接する半導体膜102と、半導体膜102の上面と接し、半導体膜102と重なる領域で離間する電極103a及び電極103bと、半導体膜102の上面に接する酸化物膜101bと、酸化物膜101b上にゲート絶縁膜104と、ゲート絶縁膜104及び酸化物膜101bを介して半導体膜102と重なるゲート電極105a、ゲート電極105bと、を有する。また、第2のトランジスタ100を覆って、絶縁膜107、絶縁膜108、及び絶縁膜126が設けられている。

## 【0093】

なお、電極103a(及び/又は、電極103b)の、少なくとも一部(又は全部)は、半導体膜102(及び/又は、酸化物膜101a)などの半導体膜の、表面、側面、上面、及び/又は、下面の少なくとも一部(又は全部)に設けられている。

## 【0094】

または、電極103a(及び/又は、電極103b)の、少なくとも一部(又は全部)は、半導体膜102(及び/又は、酸化物膜101a)などの半導体膜の、表面、側面、上面、及び/又は、下面の少なくとも一部(又は全部)と、接触している。または、電極103a(及び/又は、電極103b)の、少なくとも一部(又は全部)は、半導体膜102(及び/又は、酸化物膜101a)などの半導体膜の少なくとも一部(又は全部)と、接触している。

## 【0095】

または、電極103a(及び/又は、電極103b)の、少なくとも一部(又は全部)は、半導体膜102(及び/又は、酸化物膜101a)などの半導体膜の、表面、側面、上面、及び/又は、下面の少なくとも一部(又は全部)と、電気的に接続されている。または、電極103a(及び/又は、電極103b)の、少なくとも一部(又は全部)は、半導体膜102(及び/又は、酸化物膜101a)などの半導体膜の一部(又は全部)と、電気的に接続されている。

## 【0096】

または、電極103a(及び/又は、電極103b)の、少なくとも一部(又は全部)は、半導体膜102(及び/又は、酸化物膜101a)などの半導体膜の、表面、側面、上面、及び/又は、下面の少なくとも一部(又は全部)に、近接して配置されている。または、電極103a(及び/又は、電極103b)の、少なくとも一部(又は全部)は、半導体膜102(及び/又は、酸化物膜101a)などの半導体膜の一部(又は全部)に、近接して配置されている。

10

20

30

40

50

## 【0097】

または、電極 103a (及び/又は、電極 103b) の、少なくとも一部 (又は全部) は、半導体膜 102 (及び/又は、酸化物膜 101a) などの半導体膜の、表面、側面、上面、及び/又は、下面の少なくとも一部 (又は全部) の横側に配置されている。または、電極 103a (及び/又は、電極 103b) の、少なくとも一部 (又は全部) は、半導体膜 102 (及び/又は、酸化物膜 101a) などの半導体膜の一部 (又は全部) の横側に配置されている。

## 【0098】

または、電極 103a (及び/又は、電極 103b) の、少なくとも一部 (又は全部) は、半導体膜 102 (及び/又は、酸化物膜 101a) などの半導体膜の、表面、側面、上面、及び/又は、下面の少なくとも一部 (又は全部) の斜め上側に配置されている。または、電極 103a (及び/又は、電極 103b) の、少なくとも一部 (又は全部) は、半導体膜 102 (及び/又は、酸化物膜 101a) などの半導体膜の一部 (又は全部) の斜め上側に配置されている。

10

## 【0099】

または、電極 103a (及び/又は、電極 103b) の、少なくとも一部 (又は全部) は、半導体膜 102 (及び/又は、酸化物膜 101a) などの半導体膜の、表面、側面、上面、及び/又は、下面の少なくとも一部 (又は全部) の上側に配置されている。または、電極 103a (及び/又は、電極 103b) の、少なくとも一部 (又は全部) は、半導体膜 102 (及び/又は、酸化物膜 101a) などの半導体膜の一部 (又は全部) の上側に配置されている。

20

## 【0100】

半導体膜 102 は、チャネルが形成される領域において、シリコン系半導体などの半導体を含んでいてもよい。特に、半導体膜 102 は、シリコンよりもバンドギャップの大きな半導体を含むことが好ましい。好適には、半導体膜 102 は酸化物半導体を含んで構成される。シリコンよりもバンドギャップが広く、且つキャリア密度の小さい半導体材料を用いると、トランジスタのオフ状態における電流を低減できるため好ましい。

## 【0101】

例えば、上記酸化物半導体として、少なくともインジウム (In) もしくは亜鉛 (Zn) を含むことが好ましい。より好ましくは、In - M - Zn 系酸化物 (M は Al, Ti, Ga, Ge, Y, Zr, Sn, La, Ce または Hf 等の金属) で表記される酸化物を含む。

30

## 【0102】

特に、半導体膜として、複数の結晶部を有し、当該結晶部は c 軸が半導体膜の被形成面、または半導体膜の上面に対し垂直に配向し、且つ隣接する結晶部間には粒界を有さない酸化物半導体膜を用いることが好ましい。

## 【0103】

半導体膜としてこのような材料を用いることで、電気特性の変動が抑制され、信頼性の高いトランジスタを実現できる。

## 【0104】

40

なお、半導体膜に適用可能な酸化物半導体の好ましい形態とその形成方法については、後の実施の形態で詳細に説明する。

## 【0105】

本発明の一態様の半導体装置は、酸化物半導体膜と、該酸化物半導体膜と重なる絶縁膜との間に、酸化物半導体膜を構成する金属元素のうち、少なくとも一の金属元素を構成元素として含む酸化物膜を有することが好ましい。これにより、酸化物半導体膜と、該酸化物半導体膜と重なる絶縁膜との界面にトラップ準位が形成されることを抑制することができる。

## 【0106】

すなわち、本発明の一態様は、酸化物半導体膜の少なくともチャネル形成領域における

50

上面及び底面が、酸化物半導体膜の界面準位形成防止のためのバリア膜として機能する酸化物膜に接する構成とすることが好ましい。このような構成とすることにより、酸化物半導体膜中及び界面においてキャリアの生成要因となる酸素欠損の生成及び不純物の混入を抑制することが可能となるため、酸化物半導体膜を高純度真性化することができる。高純度真性化とは、酸化物半導体膜を真性または実質的に真性にすることをいう。よって、当該酸化物半導体膜を含むトランジスタの電気特性の変動を抑制し、信頼性の高い半導体装置を提供することが可能となる。

【0107】

なお、本明細書等において実質的に真性という場合、酸化物半導体膜のキャリア密度は、 $1 \times 10^{17} / \text{cm}^3$  未満、 $1 \times 10^{15} / \text{cm}^3$  未満、または $1 \times 10^{13} / \text{cm}^3$  未満である。酸化物半導体膜を高純度真性化することで、トランジスタに安定した電気特性を付与することができる。

【0108】

酸化物膜101aは、絶縁膜125と半導体膜102との間に設けられている。

【0109】

酸化物膜101bは、半導体膜102とゲート絶縁膜104の間に設けられている。より具体的には、酸化物膜101bは、その下面が電極103a及び電極103bの上面、及びその上面がゲート絶縁膜104の下面に接して設けられている。

【0110】

酸化物膜101a及び酸化物膜101bは、それぞれ半導体膜102と同一の金属元素を一種以上含む酸化物を含む。

【0111】

なお、半導体膜102と酸化物膜101aの境界、及び半導体膜102と酸化物膜101bの境界は不明瞭である場合がある。

【0112】

例えば、酸化物膜101a及び酸化物膜101bは、In若しくはGaを含み、代表的には、In-Ga系酸化物、In-Zn系酸化物、In-M-Zn系酸化物（MはAl、Ti、Ga、Y、Zr、La、Ce、NdまたはHf）であり、且つ半導体膜102よりも伝導帯の下端のエネルギーが真空準位に近い材料を用いる。代表的には、酸化物膜101aまたは酸化物膜101bの伝導帯の下端のエネルギーと、半導体膜102の伝導帯の下端のエネルギーとの差が、0.05eV以上、0.07eV以上、0.1eV以上、または0.15eV以上、且つ2eV以下、1eV以下、0.5eV以下、または0.4eV以下とすることが好ましい。

【0113】

半導体膜102を挟むように設けられる酸化物膜101a及び酸化物膜101bに、半導体膜102に比べてスタビライザとして機能するGaの含有量の多い酸化物を用いることにより、半導体膜102からの酸素の放出を抑制することができる。

【0114】

半導体膜102として、例えばIn:Ga:Zn = 1:1:1または3:1:2の原子数比のIn-Ga-Zn系酸化物を用いた場合、酸化物膜101aまたは酸化物膜101bとして、例えばIn:Ga:Zn = 1:3:2、1:3:4、1:3:6、1:6:4、1:6:8、1:6:10、または1:9:6などの原子数比のIn-Ga-Zn系酸化物を用いることができる。なお、半導体膜102、酸化物膜101a及び酸化物膜101bの原子数比はそれぞれ、誤差として上記の原子数比のプラスマイナス20%の変動を含む。また、酸化物膜101aと酸化物膜101bは、組成の同じ材料を用いてもよいし、異なる組成の材料を用いてもよい。

【0115】

また、半導体膜102としてIn-M-Zn系酸化物を用いた場合、半導体膜102となる半導体膜を成膜するために用いるターゲットは、該ターゲットが含有する金属元素の原子数比をIn:M:Zn = x<sub>1</sub>:y<sub>1</sub>:z<sub>1</sub>としたときに、x<sub>1</sub>/y<sub>1</sub>の値が1/3以

10

20

30

40

50

上 6 以下、好ましくは 1 以上 6 以下であり、 $z_1 / y_1$  が 1 / 3 以上 6 以下、好ましくは 1 以上 6 以下の原子数比の酸化物を用いることが好ましい。なお、 $z_1 / y_1$  を 6 以下とすることで、後述する C A A C - O S 膜が形成されやすくなる。ターゲットの金属元素の原子数比の代表例としては、 $I_{n : M : Z_n} = 1 : 1 : 1$ 、 $3 : 1 : 2$  などがある。

#### 【 0 1 1 6 】

また、酸化物膜 101a、酸化物膜 101b として  $I_{n : M : Z_n}$  系酸化物を用いた場合、酸化物膜 101a、酸化物膜 101b となる酸化物膜を成膜するために用いるターゲットは、該ターゲットが含有する金属元素の原子数比を  $I_{n : M : Z_n} = x_2 : y_2 : z_2$  としたときに、 $x_2 / y_2 < x_1 / y_1$  であり、 $z_2 / y_2$  の値が 1 / 3 以上 6 以下、好ましくは 1 以上 6 以下の原子数比の酸化物を用いることが好ましい。なお、 $z_2 / y_2$  を 6 以下とすることで、後述する C A A C - O S 膜が形成されやすくなる。ターゲットの金属元素の原子数比の代表例としては、 $I_{n : M : Z_n} = 1 : 3 : 4$ 、 $1 : 3 : 6$ 、 $1 : 3 : 8$  などがある。

#### 【 0 1 1 7 】

また、酸化物膜 101a 及び酸化物膜 101b に、半導体膜 102 に比べて伝導帯の下端のエネルギーが真空準位に近い材料を用いることにより、半導体膜 102 に主としてチャネルが形成され、半導体膜 102 が主な電流経路となる。このように、チャネルが形成される半導体膜 102 を、同じ金属元素を含む酸化物膜 101a 及び酸化物膜 101b で挟持することにより、これらの界面準位の生成が抑制され、トランジスタの電気特性における信頼性が向上する。

#### 【 0 1 1 8 】

なお、これに限らず、必要とするトランジスタの半導体特性及び電気特性（電界効果移動度、しきい値電圧等）に応じて適切な組成のものを用いればよい。また、必要とするトランジスタの半導体特性を得るために、半導体膜 102、酸化物膜 101a、酸化物膜 101b のキャリア密度や不純物濃度、欠陥密度、金属元素と酸素の原子数比、原子間距離、密度等を適切なものとすることが好ましい。

#### 【 0 1 1 9 】

ここで、酸化物膜 101a と半導体膜 102 との間には、酸化物膜 101a と半導体膜 102 との混合領域を有する場合がある。また、半導体膜 102 と酸化物膜 101b との間には、半導体膜 102 と酸化物膜 101b との混合領域を有する場合がある。混合領域は、界面準位密度が低くなる。そのため、酸化物膜 101a、半導体膜 102 及び酸化物膜 101b の積層体は、それぞれの界面近傍において、エネルギーが連続的に変化する（連続接合ともいう。）バンド構造となる。

#### 【 0 1 2 0 】

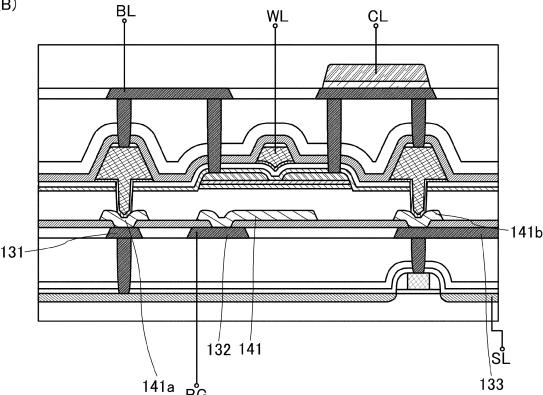

ここで、バンド構造について説明する。バンド構造は、理解を容易にするため絶縁膜 125、酸化物膜 101a、半導体膜 102、酸化物膜 101b 及びゲート絶縁膜 104 の伝導帯下端のエネルギー（E\_c）を示す。

#### 【 0 1 2 1 】

図 5 (A)、図 5 (B) に示すように、酸化物膜 101a、半導体膜 102、酸化物膜 101b において、伝導帯下端のエネルギーが連続的に変化する。これは、酸化物膜 101a、半導体膜 102、酸化物膜 101b を構成する元素が共通することにより、酸素が相互に拡散しやすい点からも理解される。したがって、酸化物膜 101a、半導体膜 102、酸化物膜 101b は組成が異なる層の積層体ではあるが、物性的に連続であるということもできる。

#### 【 0 1 2 2 】

主成分を共通として積層された酸化物膜は、各層を単に積層するのではなく連続接合（ここでは特に伝導帯下端のエネルギーが各層の間で連続的に変化する U 字型の井戸構造）が形成されるように作製する。すなわち、各層の界面にトラップ中心や再結合中心のような欠陥準位を形成するような不純物が存在しないように積層構造を形成する。仮に、積層された多層膜の層間に不純物が混在していると、エネルギー・バンドの連続性が失われ、界

10

20

30

40

50

面でキャリアがトラップあるいは再結合により消滅してしまう。

【0123】

なお、図5(A)では、酸化物膜101aと酸化物膜101bのEcが同様である場合について示したが、それぞれが異なっていてもよい。例えば、酸化物膜101aよりも酸化物膜101bのEcが高いエネルギーを有する場合、バンド構造の一部は、図5(B)のように示される。

【0124】

図5(A)、図5(B)より、半導体膜102がウェル(井戸)となり、第2のトランジスタ100において、チャネルが半導体膜102に形成されることがわかる。なお、酸化物膜101a、半導体膜102、酸化物膜101bは伝導帯下端のエネルギーが連続的に変化しているため、U字型井戸(U Shape Well)とも呼ぶことができる。また、このような構成で形成されたチャネルを埋め込みチャネルということもできる。

【0125】

なお、酸化物膜101a及び酸化物膜101bと、酸化シリコン膜などの絶縁膜との界面近傍には、不純物や欠陥に起因したトラップ準位が形成され得る。酸化物膜101a及び酸化物膜101bがあることにより、半導体膜102と当該トラップ準位とを遠ざけることができる。ただし、酸化物膜101aまたは酸化物膜101bのEcと、半導体膜102のEcとのエネルギー差が小さい場合、半導体膜102の電子が該エネルギー差を越えてトラップ準位に達することがある。トラップ準位に電子が捕獲されことで、絶縁膜界面にマイナスの固定電荷が生じ、トランジスタのしきい値電圧はプラス方向にシフトしてしまう。

【0126】

したがって、トランジスタのしきい値電圧の変動を低減するには、酸化物膜101a及び酸化物膜101bのEcと、半導体膜102のEcとの間にエネルギー差を設けることが必要となる。それぞのの当該エネルギー差は、0.1eV以上が好ましく、0.15eV以上がより好ましい。

【0127】

なお、酸化物膜101a、半導体膜102、酸化物膜101bには、結晶部が含まれることが好ましい。特にc軸に配向した結晶を用いることでトランジスタに安定した電気特性を付与することができる。

【0128】

また、図5(B)に示すようなバンド構造において、酸化物膜101bを設けず、半導体膜102とゲート絶縁膜104の間にIn-Ga酸化物(たとえば、原子数比でIn:Ga = 7:93)を設けてもよい。

【0129】

半導体膜102は、酸化物膜101a及び酸化物膜101bよりも電子親和力の大きい酸化物を用いる。例えば、半導体膜102として、酸化物膜101a及び酸化物膜101bよりも電子親和力の0.07eV以上1.3eV以下、好ましくは0.1eV以上0.7eV以下、さらに好ましくは0.15eV以上0.4eV以下大きい酸化物を用いる。なお、電子親和力は、真空準位と伝導帯下端のエネルギーとの差である。

【0130】

ここで、半導体膜102の厚さは、少なくとも酸化物膜101aよりも厚く形成することが好ましい。半導体膜102が厚いほど、トランジスタのオン電流を高めることができる。また、酸化物膜101aは、半導体膜102の界面準位の生成を抑制する効果が失われない程度の厚さであればよい。例えば、半導体膜102の厚さは、酸化物膜101aの厚さに対して、1倍よりも大きく、好ましくは2倍以上、より好ましくは4倍以上、より好ましくは6倍以上とすればよい。なお、トランジスタのオン電流を高める必要のない場合にはその限りではなく、酸化物膜101aの厚さを半導体膜102の厚さ以上としてもよい。

【0131】

10

20

30

40

50

また、酸化物膜 101b も酸化物膜 101a と同様に、半導体膜 102 の界面準位の生成を抑制する効果が失われない程度の厚さであればよい。例えば、酸化物膜 101a と同等またはそれ以下の厚さとすればよい。酸化物膜 101b が厚いと、ゲート電極による電界が半導体膜 102 に届きにくくなる恐れがあるため、酸化物膜 101b は薄く形成することが好ましい。例えば、半導体膜 102 の厚さよりも薄くすればよい。なお、これに限られず、酸化物膜 101b の厚さはゲート絶縁膜 104 の耐圧を考慮して、トランジスタを駆動させる電圧に応じて適宜設定すればよい。

#### 【0132】

ここで、例えば、半導体膜 102 が、構成元素の異なる絶縁膜（例えば酸化シリコン膜を含む絶縁膜など）と接する場合、これらの界面に界面準位が形成され、該界面準位はチャネルを形成することがある。このような場合、しきい値電圧の異なる第 2 のトランジスタが出現し、トランジスタの見かけ上のしきい値電圧が変動することがある。しかしながら、本構成のトランジスタにおいては、半導体膜 102 を構成する金属元素を一種以上含んで酸化物膜 101a を有しているため、酸化物膜 101a と半導体膜 102 との界面に界面準位を形成しにくくなる。よって酸化物膜 101a を設けることにより、トランジスタのしきい値電圧などの電気特性のばらつきや変動を低減することができる。

#### 【0133】

また、ゲート絶縁膜 104 と半導体膜 102 との界面にチャネルが形成される場合、該界面で界面散乱がおこり、トランジスタの電界効果移動度が低下する場合がある。しかしながら、本構成のトランジスタにおいては、半導体膜 102 を構成する金属元素を一種以上含んで酸化物膜 101b を有しているため、半導体膜 102 と酸化物膜 101b との界面ではキャリアの散乱が起こりにくく、トランジスタの電界効果移動度を高くすることができる。

#### 【0134】

電極 103a 及び電極 103b は、一方がソース電極として機能し、他方がドレイン電極として機能する。

#### 【0135】

電極 103a は、プラグ 163a、配線 167a、プラグ 163b 及び電極 170 を介して配線 131 と電気的に接続する。また、電極 103b は、プラグ 164a、配線 167b、プラグ 164b 及び電極 171 を介して配線 133 と電気的に接続する。

#### 【0136】

電極 103a 及び電極 103b は、アルミニウム、チタン、クロム、ニッケル、銅、イットリウム、ジルコニア、モリブデン、銀、タンタル、またはタングステンなどの金属、またはこれを主成分とする合金を単層構造または積層構造として用いる。例えば、シリコンを含むアルミニウム膜の単層構造、チタン膜上にアルミニウム膜を積層する二層構造、タングステン膜上にアルミニウム膜を積層する二層構造、銅 - マグネシウム - アルミニウム合金膜上に銅膜を積層する二層構造、チタン膜上に銅膜を積層する二層構造、タングステン膜上に銅膜を積層する二層構造、チタン膜または窒化チタン膜と、そのチタン膜または窒化チタン膜上に重ねてアルミニウム膜または銅膜を積層し、さらにその上にチタン膜または窒化チタン膜を形成する三層構造、モリブデン膜または窒化モリブデン膜と、そのモリブデン膜または窒化モリブデン膜上に重ねてアルミニウム膜または銅膜を積層し、さらにその上にモリブデン膜または窒化モリブデン膜を形成する三層構造等がある。なお、酸化インジウム、酸化錫または酸化亜鉛を含む透明導電材料を用いてもよい。

#### 【0137】

ゲート絶縁膜 104 は、例えば、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、酸化アルミニウム、酸化ハフニウム、酸化タンタル、酸化ジルコニア、チタン酸ジルコン酸鉛 (PZT)、チタン酸ストロンチウム (SrTiO<sub>3</sub>) または (Ba, Sr)TiO<sub>3</sub> (BST) などのいわゆる hig h - k 材料を含む絶縁膜を単層または積層で用いることができる。またはこれらの絶縁膜に例えば酸化アルミニウム、酸化ビスマス、酸化ゲルマニウム、酸化ニオブ、酸化シリコン、酸化チタン、酸化タングステン、酸化イット

10

20

30

40

50

リウム、酸化ジルコニウムを添加してもよい。またはこれらの絶縁膜を窒化処理しても良い。上記の絶縁膜に酸化シリコン、酸化窒化シリコンまたは窒化シリコンを積層して用いてもよい。

【0138】

また、ゲート絶縁膜104として、絶縁膜125と同様に、化学量論的組成を満たす酸素よりも多くの酸素を含む酸化物絶縁膜を用いることが好ましい。

【0139】

なお、特定の材料をゲート絶縁膜に用いると、特定の条件でゲート絶縁膜に電子を捕獲せしめて、しきい値電圧を増大させることもできる。例えば、酸化シリコンと酸化ハフニウムの積層膜のように、ゲート絶縁膜の一部に酸化ハフニウム、酸化アルミニウム、酸化タンタルのような電子捕獲準位の多い材料を用い、より高い温度（半導体装置の使用温度あるいは保管温度よりも高い温度、あるいは、125以上450以下、代表的には150以上300以下）の下で、ゲート電極の電位をソース電極やドレイン電極の電位より高い状態を、1秒以上、代表的には1分以上維持することで、半導体膜からゲート電極に向かって、電子が移動し、そのうちのいくらかは電子捕獲準位に捕獲される。

10

【0140】

このように電子捕獲準位に必要な量の電子を捕獲させたトランジスタは、しきい値電圧がプラス側にシフトする。ゲート電極の電圧の制御によって電子の捕獲する量を制御することができ、それに伴ってしきい値電圧を制御することができる。また、電子を捕獲せしめる処理は、トランジスタの作製過程におこなえばよい。

20

【0141】

例えば、トランジスタのソース電極あるいはドレイン電極に接続する配線の形成後、あるいは、前工程（ウェハー処理）の終了後、あるいは、ウェハーダイシング工程後、あるいは、パッケージ後等、工場出荷前のいずれかの段階で行うとよい。いずれの場合にも、その後に125以上の温度に1時間以上さらされないことが好ましい。

30

【0142】

ゲート電極105a、ゲート電極105bは、例えばアルミニウム、クロム、銅、タンタル、チタン、モリブデン、タンクステンから選ばれた金属、または上述した金属を成分とする合金か、上述した金属を組み合わせた合金等を用いて形成することができる。また、マンガン、ジルコニウムのいずれか一または複数から選択された金属を用いてもよい。また、リン等の不純物元素をドーピングした多結晶シリコンに代表される半導体、ニッケルシリサイド等のシリサイドを用いてもよい。例えば、アルミニウム膜上にチタン膜を積層する二層構造、窒化チタン膜上にチタン膜を積層する二層構造、窒化チタン膜上にタンクステン膜を積層する二層構造、窒化タンタル膜または窒化タンクステン膜上にタンクステン膜を積層する二層構造、チタン膜と、そのチタン膜上にアルミニウム膜を積層し、さらにその上にチタン膜を形成する三層構造等がある。また、アルミニウムに、チタン、タンタル、タンクステン、モリブデン、クロム、ネオジム、スカンジウムから選ばれた一または複数を組み合わせた合金膜、もしくは窒化膜を用いてもよい。

【0143】

また、ゲート電極105a、ゲート電極105bは、インジウム錫酸化物、酸化タンクステンを含むインジウム酸化物、酸化タンクステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、インジウム亜鉛酸化物、酸化シリコンを添加したインジウム錫酸化物等の透光性を有する導電性材料を適用することもできる。また、上記透光性を有する導電性材料と、上記金属の積層構造とすることもできる。

40

【0144】

ゲート電極105aとなる導電膜は、ゲート絶縁膜104、酸化物膜101b、絶縁膜125及びバリア膜120に開口を設ける際のマスクとして用いることができる。また、該導電膜は、ゲート電極の仕事関数を制御する機能を有している。

【0145】

50

また、ゲート電極 105a となる導電膜を用いて電極 170 に接する導電膜 170a、電極 171 に接する導電膜 171a が設けられる。

【0146】

また、ゲート電極 105b、電極 170 及び電極 171 は、同一材料、同一工程で形成される。また、ゲート電極 105b の上面の高さ、電極 170 の上面の高さ及び電極 171 の上面の高さは揃っている。なお、ここで「揃っている」とは、基準にした上面の高さのプラスマイナス 20% 以下、好ましくはプラスマイナス 10% 以下、より好ましくはプラスマイナス 5% 以下のずれを含むものとする。

【0147】

絶縁膜 126、絶縁膜 107、絶縁膜 108、ゲート絶縁膜 104、酸化物膜 101b 10、絶縁膜 125 及びバリア膜 120 を一括で開口することは開口の深さが深くなってしまうため加工上困難であるが、本発明の一態様では、開口を分割する（具体的には、ゲート絶縁膜 104、酸化物膜 101b、絶縁膜 125 及びバリア膜 120 に設けられる開口、及び絶縁膜 126、絶縁膜 107 及び絶縁膜 108 に設けられる開口）ことで配線や電極のコンタクト部分の形状の異常を抑制することができる。

【0148】

また、ゲート電極 105a とゲート絶縁膜 104 の間に、In - Ga - Zn 系酸窒化物半導体膜、In - Sn 系酸窒化物半導体膜、In - Ga 系酸窒化物半導体膜、In - Zn 系酸窒化物半導体膜、Sn 系酸窒化物半導体膜、In 系酸窒化物半導体膜、金属窒化膜（InN、ZnN 等）等を設けてもよい。これらの膜は 5 eV 以上、好ましくは 5.5 eV 20 以上の仕事関数を有し、トランジスタのしきい値電圧をプラスにシフトすることができ、所謂ノーマリーオフ特性のスイッチング素子を実現できる。例えば、In - Ga - Zn 系酸窒化物半導体膜を用いる場合、少なくとも半導体膜 102 より高い窒素濃度、具体的には 7 原子% 以上の In - Ga - Zn 系酸窒化物半導体膜を用いる。

【0149】

また、ゲート電極 105b 上に絶縁膜 106、電極 170 上に絶縁膜 174、電極 171 上に絶縁膜 175 が形成される。

【0150】

絶縁膜 107 は、バリア膜 120 と同様、水や水素が拡散しにくい材料を用いることが好ましい。また、特に、絶縁膜 107 として酸素を透過しにくい材料を用いることが好ましい。

【0151】

酸素を透過しにくい材料を含む絶縁膜 107 で半導体膜 102 を覆うことで、半導体膜 102 から絶縁膜 107 よりも上方に酸素が放出されることを抑制することができる。さらに、絶縁膜 125 から脱離した酸素を絶縁膜 107 よりも下側に閉じ込めることができるため、半導体膜 102 に供給しうる酸素の量を増大させることができる。

【0152】

また、水や水素を透過しにくい絶縁膜 107 により、外部から酸化物半導体にとっての不純物である水や水素が混入することを抑制でき、第 2 のトランジスタ 100 の電気特性的変動が抑制され、信頼性の高いトランジスタを実現できる。

【0153】

なお、絶縁膜 107 よりも下側に、絶縁膜 125 と同様の、加熱により酸素が脱離する絶縁膜を設け、ゲート絶縁膜 104 を介して半導体膜 102 の上側からも酸素を供給する構成としてもよい。

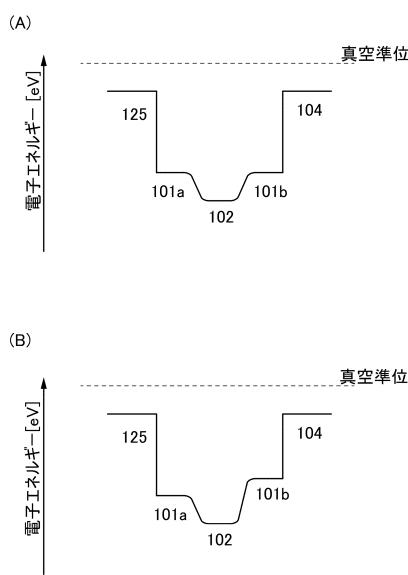

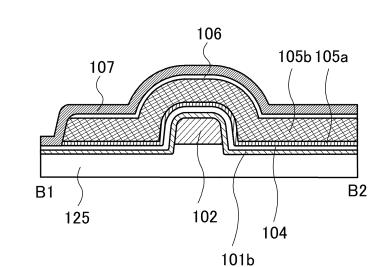

【0154】

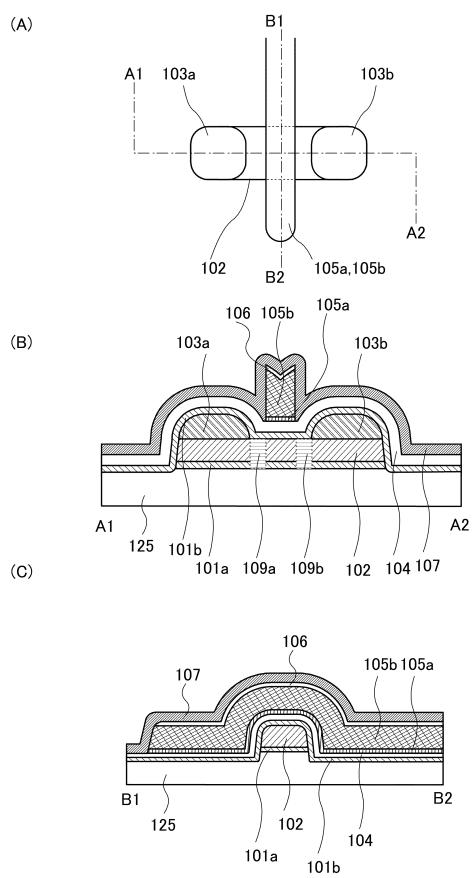

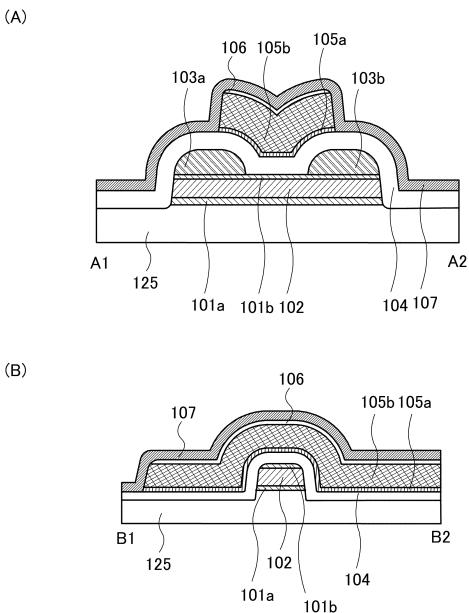

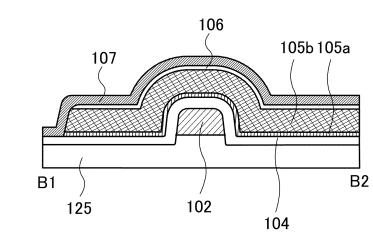

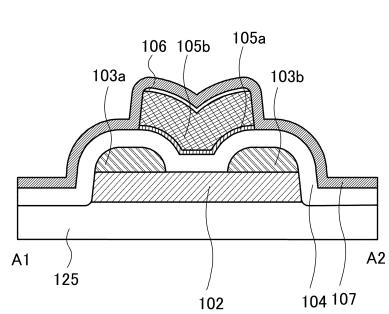

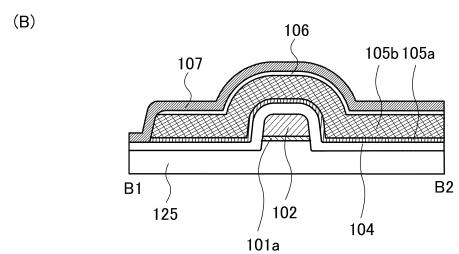

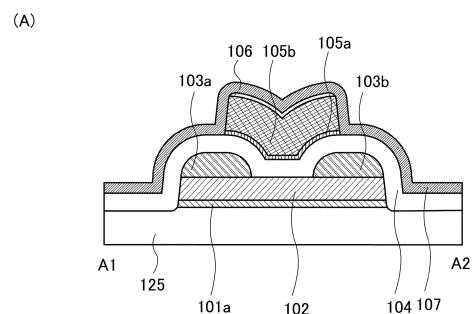

ここで、第 2 のトランジスタ 100 に適用可能なトランジスタの構成例について示す。図 6 (A) は以下で例示するトランジスタの上面概略図であり、図 6 (B)、図 6 (C) はそれぞれ、図 6 (A) 中の切断線 A1 - A2、B1 - B2 で切断したときの断面概略図である。なお、図 6 (B) はトランジスタのチャネル長方向の断面に相当し、図 6 (C) はトランジスタのチャネル幅方向の断面に相当する。

10

20

30

40

50

## 【0155】

図6(C)に示すように、トランジスタのチャネル幅方向の断面において、ゲート電極が半導体膜102の上面及び側面に面して設けられることで、半導体膜102の上面近傍だけでなく側面近傍にまでチャネルが形成され、実効的なチャネル幅が増大し、オン状態における電流(オン電流)を高めることができる。特に、半導体膜102の幅が極めて小さい(例えば50nm以下、好ましくは30nm以下、より好ましくは20nm以下)場合には、半導体膜102の内部にまでチャネルが形成される領域が広がるため、微細化するほどオン電流に対する寄与が高まる。

## 【0156】

なお、図7(A)、図7(B)、図7(C)に示すように、ゲート電極105bの幅を狭くしてもよい。その場合、例えば、電極103a及び電極103bや、ゲート電極105bなどをマスクとして、半導体膜102などに、アルゴン、水素、リン、ホウ素などの不純物を導入することができる。その結果、半導体膜102などにおいて、低抵抗領域109a、109bを設けることができる。なお、低抵抗領域109a、109bは、必ずしも、設けなくてもよい。なお、図6だけでなく、他の図面においても、ゲート電極105bの幅を狭くすることができる。

10

## 【0157】

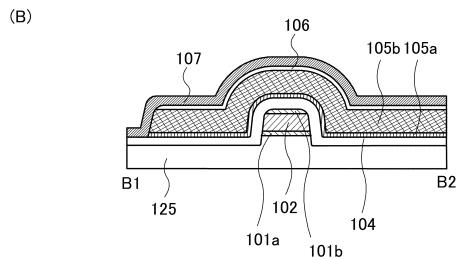

図8(A)、図8(B)に示すトランジスタは、図3で例示したトランジスタと比較して、酸化物膜101bが電極103a及び電極103bの下面に接して設けられている点で主に相違している。

20

## 【0158】

このような構成とすることで、酸化物膜101a、半導体膜102及び酸化物膜101bを構成するそれぞれの膜の成膜時において、大気に触れさせることなく連続的に成膜することができるため、各々の界面欠陥を低減することができる。

## 【0159】

また、上記では、半導体膜102に接して酸化物膜101a及び酸化物膜101bを設ける構成を説明したが、酸化物膜101aまたは酸化物膜101bの一方、または両方を設けない構成としてもよい。

## 【0160】

なお、図8においても、図6と同様に、ゲート電極105bの幅を狭くすることができる。その場合の例を、図9(A)、図9(B)に示す。なお、図6、図8だけでなく、他の図面においても、ゲート電極105bの幅を狭くすることができる。

30

## 【0161】

図10(A)、図10(B)では、酸化物膜101aと酸化物膜101bを設けない場合の例を示している。また、図11(A)、図11(B)では、酸化物膜101aを設け、酸化物膜101bを設けない場合の例を示している。また、図12(A)、図12(B)では、酸化物膜101bを設け、酸化物膜101aを設けない場合の例を示している。

## 【0162】

なお、チャネル長とは、例えば、トランジスタの上面図において、半導体(またはトランジスタがオン状態のときに半導体の中で電流の流れる部分)とゲート電極とが重なる領域、またはチャネルが形成される領域における、ソース(ソース領域またはソース電極)とドレイン(ドレイン領域またはドレイン電極)との間の距離をいう。なお、一つのトランジスタにおいて、チャネル長が全ての領域で同じ値をとるとは限らない。即ち、一つのトランジスタのチャネル長は、一つの値に定まらない場合がある。そのため、本明細書では、チャネル長は、チャネルの形成される領域における、いずれか一の値、最大値、最小値または平均値とする。

40

## 【0163】

チャネル幅とは、例えば、半導体(またはトランジスタがオン状態のときに半導体の中で電流の流れる部分)とゲート電極とが重なる領域、またはチャネルが形成される領域における、ソースまたはドレインの幅をいう。なお、一つのトランジスタにおいて、チャネ

50

ル幅がすべての領域で同じ値をとるとは限らない。即ち、一つのトランジスタのチャネル幅は、一つの値に定まらない場合がある。そのため、本明細書では、チャネル幅は、チャネルの形成される領域における、いずれか一の値、最大値、最小値または平均値とする。

【0164】

なお、トランジスタの構造によっては、実際にチャネルの形成される領域におけるチャネル幅（以下、実効的なチャネル幅と呼ぶ。）と、トランジスタの上面図において示されるチャネル幅（以下、見かけ上のチャネル幅と呼ぶ。）と、が異なる場合がある。例えば、立体的な構造を有するトランジスタでは、実効的なチャネル幅が、トランジスタの上面図において示される見かけ上のチャネル幅よりも大きくなり、その影響が無視できなくなる場合がある。例えば、微細かつ立体的な構造を有するトランジスタでは、半導体の上面に形成されるチャネル領域の割合に対して、半導体の側面に形成されるチャネル領域の割合が大きくなる場合がある。その場合は、上面図において示される見かけ上のチャネル幅よりも、実際にチャネルの形成される実効的なチャネル幅の方が大きくなる。

【0165】

ところで、立体的な構造を有するトランジスタにおいては、実効的なチャネル幅の、実測による見積もりが困難となる場合がある。例えば、設計値から実効的なチャネル幅を見積もるためにには、半導体の形状が既知という仮定が必要である。したがって、半導体の形状が正確にわからない場合には、実効的なチャネル幅を正確に測定することは困難である。

【0166】

そこで、本明細書では、トランジスタの上面図において、半導体とゲート電極とが重なる領域における、ソースとドレインとが向かい合っている部分の長さである見かけ上のチャネル幅を、「囲い込みチャネル幅（SCW：Surrounded Channel Width）」と呼ぶ場合がある。また、本明細書では、単にチャネル幅と記載した場合には、囲い込みチャネル幅または見かけ上のチャネル幅を指す場合がある。または、本明細書では、単にチャネル幅と記載した場合には、実効的なチャネル幅を指す場合がある。なお、チャネル長、チャネル幅、実効的なチャネル幅、見かけ上のチャネル幅、囲い込みチャネル幅などは、断面TEM像などを取得して、その画像を解析することなどによって、値を決定することができる。

【0167】

なお、トランジスタの電界効果移動度や、チャネル幅当たりの電流値などを計算して求める場合、囲い込みチャネル幅を用いて計算する場合がある。その場合には、実効的なチャネル幅を用いて計算する場合とは異なる値をとる場合がある。

【0168】

以上が第2のトランジスタ100についての説明である。

【0169】

第2のトランジスタ100を覆う絶縁膜126は、その下層の凹凸形状を被覆する平坦化膜として機能する。また、絶縁膜108は、絶縁膜126を成膜する際の保護膜としての機能を有していてもよい。絶縁膜108は不要であれば設けなくてもよい。

【0170】

酸化物膜101b、ゲート絶縁膜104、絶縁膜107、絶縁膜108及び絶縁膜126には、電極103aと電気的に接続するプラグ163a、及びプラグ163b、電極103bと電気的に接続するプラグ164a、及びプラグ164b等が埋め込まれている。

【0171】

また、配線167a及び配線167bは、絶縁膜127に埋め込まれるように設けられ、絶縁膜127と配線167a及び配線167bの各々の上面は平坦化されていることが好ましい。

【0172】

絶縁膜137は、配線167bと導電膜138とが重畳する領域において、容量130の誘電層として機能する。また、絶縁膜139は、その下層の凹凸形状を被覆する平坦化

10

20

30

40

50

膜として機能する。

【0173】

ここで、第1のトランジスタ110のゲート電極115、容量130の第1の電極として機能する配線167b、及び第2のトランジスタ100の電極103bを含むノードが、図2(A)に示すノードFNに相当する。

【0174】

本発明の一態様の半導体装置は、第1のトランジスタ110と、第1のトランジスタの上方に位置する第2のトランジスタ100とを有するため、これらを積層して設けることにより素子の占有面積を縮小することができる。さらに、第1のトランジスタ110と第2のトランジスタ100との間に設けられたバリア膜120により、これよりも下層に存在する水や水素等の不純物が第2のトランジスタ100側に拡散することを抑制できる。 10

【0175】

また、図3(B)に示すように、水素を含む絶縁膜122上に、バリア膜120と同様の材料を含む絶縁膜140を設ける構成としてもよい。このような構成とすることで、水素を含む絶縁膜122中に残存した水や水素が上方に拡散することを効果的に抑制することができる。この場合、絶縁膜140を形成する前と、絶縁膜140を形成した後であってバリア膜120を形成するよりも前に、水や水素を除去するための加熱処理を合計2回以上行なうことが好ましい。

【0176】

以上が構成例についての説明である。

20

【0177】

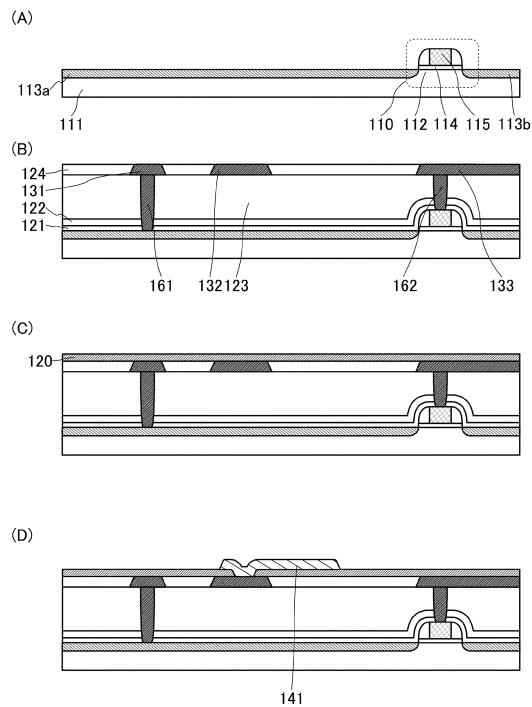

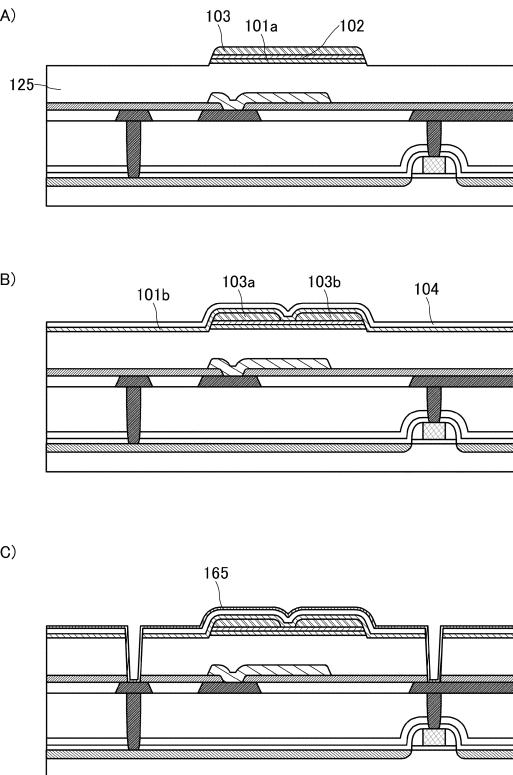

[作製方法例]

以下では、上記構成例で示した半導体装置の作製方法の一例について、図13乃至図16を用いて説明する。

【0178】

まず、半導体基板111を準備する。半導体基板111としては、例えば、単結晶シリコン基板(p型の半導体基板、またはn型の半導体基板を含む)、炭化シリコンや窒化ガリウムなどの化合物半導体基板などを用いることができる。また、半導体基板111として、SOI基板を用いてもよい。以下では、半導体基板111として単結晶シリコンを用いた場合について説明する。 30

【0179】

続いて、半導体基板111に素子分離層(図示せず)を形成する。素子分離層はLOCOS(Local Oxidation of Silicon)法またはSTI(Shallow Trench Isolation)法等を用いて形成すればよい。

【0180】

同一基板上にp型のトランジスタとn型のトランジスタを形成する場合、半導体基板111の一部にnウェルまたはpウェルを形成してもよい。例えば、n型の半導体基板111にp型の導電性を付与するホウ素などの不純物元素を添加してpウェルを形成し、同一基板上にn型のトランジスタとp型のトランジスタを形成してもよい。

【0181】

続いて、半導体基板111上にゲート絶縁膜114となる絶縁膜を形成する。例えば、表面窒化処理後に酸化処理を行い、シリコンと窒化シリコン界面を酸化して酸化窒化シリコン膜を形成してもよい。例えばNH<sub>3</sub>雰囲気中で700にて熱窒化シリコン膜を表面に形成後に酸素ラジカル酸化を行うことで酸化窒化シリコン膜が得られる。

40

【0182】

当該絶縁膜は、スパッタリング法、CVD(Chemical Vapor Deposition)法(熱CVD法、MOCVD(Metal Organic CVD)法、PECVD(Plasma Enhanced CVD)法等を含む)、MBE(Molecular Beam Epitaxy)法、ALD(Atomic Layer Deposition)法、またはPLD(Pulsed Laser Deposit 50

ion) 法等で成膜することにより形成してもよい。

【0183】

続いて、ゲート電極 115 となる導電膜を成膜する。導電膜としては、タンタル、タンゲステン、チタン、モリブデン、クロム、ニオブ等から選択された金属、またはこれらの金属を主成分とする合金材料若しくは化合物材料を用いることが好ましい。また、リン等の不純物を添加した多結晶シリコンを用いることができる。また、金属窒化物膜と上記の金属膜の積層構造を用いてもよい。金属窒化物としては、窒化タンゲステン、窒化モリブデン、窒化チタンを用いることができる。金属窒化物膜を設けることにより、金属膜の密着性を向上させることができ、剥離を防止することができる。また、ゲート電極 115 の仕事関数を制御する金属膜を設けてもよい。

10

【0184】

導電膜は、スパッタリング法、蒸着法、CVD 法（熱 CVD 法、MOCVD 法、PECVD 法等を含む）などにより成膜することができる。また、プラズマによるダメージを減らすには、熱 CVD 法、MOCVD 法あるいは ALD 法が好ましい。

【0185】

続いて、当該導電膜上にリソグラフィ法等を用いてレジストマスクを形成し、当該導電膜の不要な部分を除去する。その後、レジストマスクを除去することにより、ゲート電極 115 を形成することができる。

【0186】

ここで、被加工膜の加工方法について説明する。被加工膜を微細に加工する場合には、様々な微細加工技術を用いることができる。例えば、リソグラフィ法等で形成したレジストマスクに対してスリミング処理を施す方法を用いてもよい。また、リソグラフィ法等でダミーパターンを形成し、当該ダミーパターンにサイドウォールを形成した後にダミーパターンを除去し、残存したサイドウォールをレジストマスクとして用いて、被加工膜をエッチングしてもよい。また、被加工膜のエッチングとして、高いアスペクト比を実現するために、異方性のドライエッチングを用いることが好ましい。また、無機膜または金属膜からなるハードマスクを用いてもよい。

20

【0187】

レジストマスクの形成に用いる光は、例えば i 線（波長 365 nm）、g 線（波長 436 nm）、h 線（波長 405 nm）、またはこれらを混合させた光を用いることができる。そのほか、紫外線や KrF レーザ光、または ArF レーザ光等を用いることもできる。また、液浸露光技術により露光を行ってもよい。また、露光に用いる光として、極端紫外光（EUV : Extreme Ultra-violet）や X 線を用いてもよい。また、露光に用いる光に換えて、電子ビームを用いることもできる。極端紫外光、X 線または電子ビームを用いると、極めて微細な加工が可能となるため好ましい。なお、電子ビームなどのビームを走査することにより露光を行う場合には、フォトマスクは不要である。

30

【0188】

また、レジストマスクとなるレジスト膜を形成する前に、被加工膜とレジスト膜との密着性を改善する機能を有する有機樹脂膜を形成してもよい。当該有機樹脂膜は、例えばスピニコート法などにより、その下層の段差を被覆して表面を平坦化するように形成することができ、当該有機樹脂膜の上層に設けられるレジストマスクの厚さのばらつきを低減できる。また、特に微細な加工を行う場合には、当該有機樹脂膜として、露光に用いる光に対する反射防止膜として機能する材料を用いることが好ましい。このような機能を有する有機樹脂膜としては、例えば BARC (Bottom Anti-Reflection Coating) 膜などがある。当該有機樹脂膜は、レジストマスクの除去と同時に除去するか、レジストマスクを除去した後に除去すればよい。

40

【0189】

ゲート電極 115 の形成後、ゲート電極 115 の側面を覆うサイドウォールを形成してもよい。サイドウォールは、ゲート電極 115 の厚さよりも厚い絶縁膜を成膜した後に、異方性エッチングを施し、ゲート電極 115 の側面部分のみ当該絶縁膜を残存させること

50

により形成できる。

【0190】

サイドウォールの形成時にゲート絶縁膜114となる絶縁膜も同時にエッティングされることにより、ゲート電極115及びサイドウォールの下部にゲート絶縁膜114が形成される。または、ゲート電極115を形成した後にゲート電極115またはゲート電極115を加工するためのレジストマスクをエッティングマスクとして当該絶縁膜をエッティングすることによりゲート絶縁膜114を形成してもよい。または、当該絶縁膜に対してエッティングによる加工を行わずに、そのままゲート絶縁膜114として用いることもできる。

【0191】

続いて、半導体基板111のゲート電極115（及びサイドウォール）が設けられていない領域にリンなどのn型の導電性を付与する元素、またはホウ素などのp型の導電性を付与する元素を添加する。この段階における断面概略図が図13（A）に相当する。

10

【0192】

続いて、絶縁膜121を形成した後、上述した導電性を付与する元素の活性化のための第1の加熱処理を行う。

【0193】

絶縁膜121は、例えば酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、酸化アルミニウム、酸化窒化アルミニウム、窒化酸化アルミニウム、窒化アルミニウムなどを用いればよく、積層または単層で設ける。絶縁膜121はスパッタリング法、CVD法（熱CVD法、MOCVD法、PECVD法等を含む）、MBE法、ALD法またはPLD法などを用いて形成することができる。特に、当該絶縁膜をCVD法、好ましくはプラズマCVD法によって成膜すると、被覆性を向上させることができるために好ましい。またプラズマによるダメージを減らすには、熱CVD法、MOCVD法あるいはALD法が好ましい。

20

【0194】

第1の加熱処理は、希ガスや窒素ガスなどの不活性ガス雰囲気下、または減圧雰囲気下にて、例えば、400以上でかつ基板の歪み点未満で行うことができる。

【0195】

この段階で第1のトランジスタ110が形成される。

【0196】

30

続いて、絶縁膜122及び絶縁膜123を形成する。

【0197】

絶縁膜122は、絶縁膜121に用いることのできる材料のほか、酸素と水素を含む窒化シリコン（SiNOH）を用いると、加熱によって脱離する水素の量を多くすることができるため好ましい。また、絶縁膜123は、絶縁膜121に用いることのできる材料のほか、TEOS（Tetra-Ethyl-Ortho-Silicate）若しくはシリコン等と、酸素若しくは亜酸化窒素等とを反応させて形成した段差被覆性の良い酸化シリコンを用いることが好ましい。

【0198】

絶縁膜122及び絶縁膜123は、例えば、スパッタリング法、CVD法（熱CVD法、MOCVD法、PECVD法等を含む）、MBE法、ALD法またはPLD法などを用いて形成することができる。特に、当該絶縁膜をCVD法、好ましくはプラズマCVD法によって成膜すると、被覆性を向上させることができるために好ましい。また、プラズマによるダメージを減らすには、熱CVD法、MOCVD法あるいはALD法が好ましい。

40

【0199】

続いて絶縁膜123の上面を、CMP法等を用いて平坦化する。

【0200】

その後、半導体膜112中のダングリングボンドを絶縁膜122から脱離する水素によって終端するための第2の加熱処理を行う。

【0201】

50

第2の加熱処理は、上記積層構造の説明で例示した条件で行うことができる。

【0202】

続いて、絶縁膜121、絶縁膜122、及び絶縁膜123に低抵抗層113a、低抵抗層113b及びゲート電極115等に達する開口を形成する。その後、開口を埋めるように導電膜を形成し、絶縁膜123の上面が露出するように、該導電膜に平坦化処理を施すことにより、プラグ161やプラグ162等を形成する。導電膜の形成は、例えばスパッタリング法、CVD法(熱CVD法、MOCVD法、PECVD法等を含む)、MBE法、ALD法またはPLD法などを用いて形成することができる。

【0203】

続いて、絶縁膜123上に導電膜を成膜する。その後上記と同様の方法によりレジストマスクを形成し、導電膜の不要な部分をエッチングにより除去する。その後レジストマスクを除去することにより、配線131、配線132及び配線133を形成することができる。

【0204】

続いて、配線131、配線132及び配線133を覆って絶縁膜を成膜し、各配線の上面が露出するように平坦化処理を施すことにより、絶縁膜124を形成する。この段階における断面概略図が図13(B)に相当する。

【0205】

絶縁膜124となる絶縁膜は、絶縁膜121等と同様の材料及び方法により形成することができる。

【0206】

絶縁膜124を形成した後、第3の加熱処理を行うことが好ましい。第3の加熱処理により、各層に含まれる水や水素を脱離させることにより、水や水素の含有量を低減することができる。後述するバリア膜120を形成する直前に第3の加熱処理を施し、バリア膜120よりも下層に含まれる水素や水を徹底的に除去した後に、バリア膜120を形成することで、後の工程でバリア膜120よりも下層側に水や水素が拡散・放出してしまうことを抑制することができる。

【0207】

第3の加熱処理は、上記積層構造の説明で例示した条件で行うことができる。

【0208】

続いて、絶縁膜124、配線131、配線132及び配線133等上にバリア膜120を形成する(図13(C))。

【0209】

バリア膜120は、例えばスパッタリング法、CVD法(熱CVD法、MOCVD法、PECVD法等を含む)、MBE法、ALD法またはPLD法などを用いて形成することができる。特に、当該絶縁膜をCVD法、好ましくはプラズマCVD法によって成膜すると、被覆性を向上させることができるため好ましい。また、プラズマによるダメージを減らすには、熱CVD法、MOCVD法あるいはALD法が好ましい。

【0210】

バリア膜120を形成した後に、バリア膜120に含まれる水や水素を低減あるいは脱離ガスを抑制するための加熱処理を行ってもよい。

【0211】

続いて、バリア膜120上に、上記と同様の方法によりレジストマスクを形成し、バリア膜120の不要な部分をエッチングにより除去する。その後、レジストマスクを除去することにより、配線132に達する開口を形成する。

【0212】

続いて、バリア膜120上に導電膜を形成した後、上記と同様の方法によりレジストマスクを形成し、導電膜の不要な部分をエッチングにより除去する。その後、レジストマスクを除去することにより、配線141を形成することができる(図13(D))。

【0213】

10

20

30

40

50

続いて、絶縁膜125を成膜する。

【0214】

絶縁膜125は、例えばスパッタリング法、CVD法(熱CVD法、MOCVD法、PECVD法等を含む)、MBE法、ALD法またはPLD法などを用いて形成することができる。特に、当該絶縁膜をCVD法、好ましくはプラズマCVD法によって成膜すると、被覆性を向上させることができるため好ましい。また、プラズマによるダメージを減らすには、熱CVD法、MOCVD法あるいはALD法が好ましい。

【0215】

絶縁膜125に酸素を過剰に含有させるためには、例えば酸素雰囲気下にて絶縁膜125の成膜を行えばよい。または、成膜後の絶縁膜125に酸素を導入して酸素を過剰に含有する領域を形成してもよく、双方の手段を組み合わせてもよい。

10

【0216】

例えば、成膜後の絶縁膜125に酸素(少なくとも酸素ラジカル、酸素原子、酸素イオンのいずれかを含む)を導入して酸素を過剰に含有する領域を形成する。酸素の導入方法としては、イオン注入法、イオンドーピング法、プラズマイマージョンイオン注入法、プラズマ処理などを用いることができる。

【0217】

酸素導入処理には、酸素を含むガスを用いることができる。酸素を含むガスとしては、酸素、一酸化二窒素、二酸化窒素、二酸化炭素、一酸化炭素などを用いることができる。また、酸素導入処理において、酸素を含むガスに希ガスを含ませてもよく、例えば、二酸化炭素と水素とアルゴンの混合ガスを用いることができる。

20

【0218】

また、絶縁膜125を形成した後、その上面の平坦性を高めるためにCMP法等を用いた平坦化処理を行ってもよい。

【0219】

続いて、酸化物膜101aとなる酸化物膜と、半導体膜102となる半導体膜を順に成膜する。当該酸化物膜と半導体膜は、大気に触れさせることなく連続して成膜するが好ましい。

【0220】

酸化物膜及び半導体膜を成膜後、第4の加熱処理を行うことが好ましい。加熱処理は、250以上650以下、好ましくは300以上500以下の温度で、不活性ガス雰囲気、酸化性ガスを10ppm以上含む雰囲気、または減圧状態で行えばよい。また、加熱処理の雰囲気は、不活性ガス雰囲気で加熱処理した後に、脱離した酸素を補うために酸化性ガスを10ppm以上含む雰囲気で行ってもよい。加熱処理は、半導体膜を成膜した直後に行ってもよいし、半導体膜を加工して島状の半導体膜102を形成した後に行ってもよい。加熱処理により、絶縁膜125や酸化物膜から半導体膜に酸素が供給され、半導体膜中の酸素欠損を低減することができる。

30

【0221】

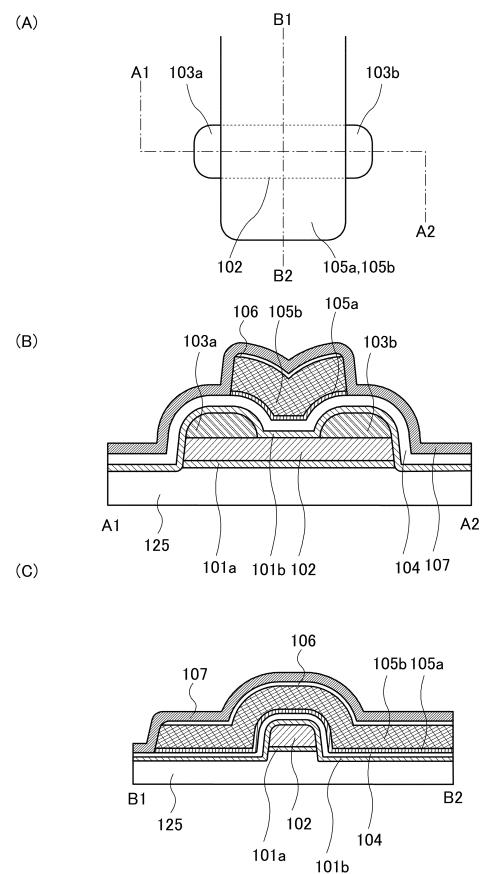

その後、半導体膜上にハードマスクとなる導電膜及び上記と同様の方法によりレジストマスクを形成し、導電膜の不要な部分をエッチングにより除去する。その後、導電膜をマスクとして半導体膜と酸化物膜の不要な部分をエッチングにより除去する。その後レジストマスクを除去することにより、島状の導電膜103、島状の酸化物膜101aと島状の半導体膜102の積層構造を形成することができる(図14(A))。

40

【0222】

導電膜の形成は、例えばスパッタリング法、CVD法(熱CVD法、MOCVD法、PECVD法等を含む)、MBE法、ALD法またはPLD法などを用いて形成することができる。特に、当該導電膜をCVD法、好ましくはプラズマCVD法によって成膜すると、被覆性を向上させることができるため好ましい。また、プラズマによるダメージを減らすには、熱CVD法、MOCVD法あるいはALD法が好ましい。

【0223】

50

なお、図14(A)に示すように、酸化物膜及び半導体膜のエッティングの際に、絶縁膜125の一部がエッティングされ、酸化物膜101a及び半導体膜102に覆われていない領域における絶縁膜125が薄膜化することがある。したがって、当該エッティングにより絶縁膜125が消失しないよう、絶縁膜125を予め厚く形成しておくことが好ましい。

【0224】

続いて、導電膜103上に上記と同様の方法によりレジストマスクを形成し、導電膜103の不要な部分をエッティングにより除去する。その後、レジストマスクを除去することにより、電極103a及び電極103bを形成することができる。その後、酸化物膜101b及びゲート絶縁膜104を形成する(図14(B))。

【0225】

続いて、ゲート絶縁膜104上に上記と同様の方法によりレジストマスクを形成し、該マスクを用いてゲート絶縁膜104、酸化物膜101b、絶縁膜125及びバリア膜120に、配線131及び配線133等に達する開口を形成する。その後、導電膜165を成膜する(図14(C))。なお、導電膜165は、後に形成されるゲート電極の仕事関数を制御する膜として機能する。

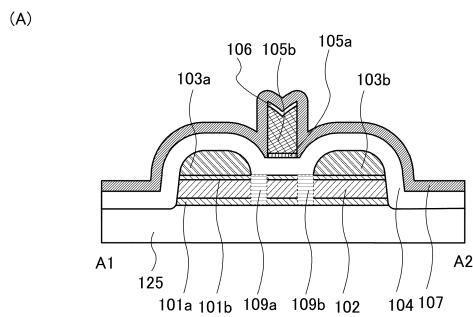

【0226】

続いて、開口を埋めるように導電膜を形成し、導電膜の上面を、CMP法等を用いて平坦化された導電膜166を形成する(図15(A))。

【0227】

続いて、導電膜166上に絶縁膜を成膜し、絶縁膜上に上記と同様の方法によりレジストマスクを形成し、絶縁膜の不要な部分をエッティングにより除去し、絶縁膜106、絶縁膜174及び絶縁膜175が形成される。絶縁膜106、絶縁膜174及び絶縁膜175をマスクにして導電膜165及び導電膜166の不要な部分をエッティングにより除去し、ゲート電極105a、ゲート電極105b、導電膜170a、電極170、導電膜171a及び電極171が形成される。なお、レジストマスクは、絶縁膜106、絶縁膜174及び絶縁膜175形成後またはゲート電極105a、ゲート電極105b、導電膜170a、電極170、導電膜171a及び電極171形成後に除去する、またはエッティング時に消失する(図15(B))。絶縁膜106、絶縁膜174及び絶縁膜175をマスクすることでエッティング時にレジストマスクが消失してもゲート電極105a、ゲート電極105b、導電膜170a、電極170、導電膜171a及び電極171を位置精度よく形成することができる。なお、絶縁膜106、絶縁膜174及び絶縁膜175としては、例えば、窒化シリコン膜を用いることができる。

【0228】

なお、このとき、平坦化された導電膜166からゲート電極105b、電極170及び電極171を形成するため、ゲート電極105bの上面の高さ、電極170の上面の高さ及び電極171の上面の高さは揃っている。

【0229】

また、ゲート電極105aは、仕事関数を制御する機能を有する導電膜で形成されており、トランジスタのしきい値を制御することができる。

【0230】

なお、本実施の形態では、絶縁膜106、絶縁膜174及び絶縁膜175が設けられているがこれに限られず、絶縁膜106、絶縁膜174及び絶縁膜175を除去してもよい。また、導電膜166上に絶縁膜を形成したがこれに限られず、絶縁膜を形成しない構成にしてもよい。

【0231】

この段階で第2のトランジスタ100が形成される。

【0232】

続いて、絶縁膜107を形成する。絶縁膜107は、例えばスパッタリング法、CVD法(熱CVD法、MOCVD法、PECVD法等を含む)、MBE法、ALD法またはPLD法などを用いて形成することができる。特に、当該絶縁膜をCVD法、好ましくはブ

10

20

30

40

50

ラズマ CVD 法によって成膜すると、被覆性を向上させることができるため好ましい。また、プラズマによるダメージを減らすには、熱 CVD 法、MOCVD 法あるいは ALD 法が好ましい。

【0233】

絶縁膜 107 の成膜後、第 5 の加熱処理を行うことが好ましい。加熱処理により、絶縁膜 125 等から半導体膜 102 に対して酸素を供給し、半導体膜 102 中の酸素欠損を低減することができる。また、このとき、絶縁膜 125 から脱離した酸素は、バリア膜 120 及び絶縁膜 107 によってブロックされ、バリア膜 120 よりも下層及び絶縁膜 107 よりも上層には拡散しないため、当該酸素を効果的に閉じ込めることができる。そのため半導体膜 102 に供給しうる酸素の量を増大させることができ、半導体膜 102 中の酸素欠損を効果的に低減することができる。 10

【0234】

続いて、絶縁膜 108 及び絶縁膜 126 を順に形成する（図 15（C））。絶縁膜 108 及び絶縁膜 126 は、例えばスパッタリング法、CVD 法（熱 CVD 法、MOCVD 法、PECVD 法、APCVD（Atmospheric Pressure CVD）法等を含む）、MBE 法、ALD 法または PLD 法などを用いて形成することができる。特に、絶縁膜 108 を DC スパッタ法によって成膜すると、バリア性の高い膜を生産性良く厚く成膜できるため好ましい。また、ALD 法によって成膜すると、イオンダメージを減らし、被覆性を良好なものとすることができますため好ましい。また、絶縁膜 126 として有機樹脂などの有機絶縁材料を用いる場合には、スピンドルコート法などの塗布法を用いて形成してもよい。また、絶縁膜 126 を形成した後にその上面に対して平坦化処理を行うことが好ましい。また、熱処理を行い流動化させて平坦化しても良い。また、平坦性をより良好なものとするために、絶縁膜 126 を形成した後に CVD 法を用いて絶縁膜を積層した後にその上面に対して平坦化処理を行うことが好ましい。 20

【0235】

続いて、上記と同様の方法により、絶縁膜 126、絶縁膜 108、絶縁膜 107、絶縁膜 174、絶縁膜 175、ゲート絶縁膜 104 及び酸化物膜 101b に開口を設け、電極 103a に達するプラグ 163a、電極 170 に達するプラグ 163b、電極 103b に達するプラグ 164a 及び電極 171 に達するプラグ 164b を形成する。その後、プラグ 163a 及びプラグ 163b と接する配線 167a、プラグ 164a 及びプラグ 164b と接する配線 167b を形成する。 30

【0236】

続いて、配線 167a 及び配線 167b を覆って絶縁膜を成膜し、各配線の上面が露出するように平坦化処理を施すことにより、絶縁膜 127 を形成する（図 16（A））。

【0237】

続いて、配線 167b 上に絶縁膜 137 が形成され、絶縁膜 137 上に導電膜 138 が形成される。この段階で、容量 130 が形成される。容量 130 は、一部が第 1 の電極として機能する配線 167b と、第 2 の電極として機能する導電膜 138 と、これらに挟持された絶縁膜 137 によって構成されている。

【0238】

続いて、絶縁膜 139 を形成する（図 16（B））。

【0239】

以上の工程により、本発明の一態様の半導体装置を作製することができる。

【0240】

（実施の形態 2）

本実施の形態では、本発明の一態様の半導体装置の半導体膜に好適に用いることのできる酸化物半導体について説明する。

【0241】

酸化物半導体は、エネルギーギャップが 3.0 eV 以上と大きく、酸化物半導体を適切な条件で加工し、そのキャリア密度を十分に低減して得られた酸化物半導体膜が適用され 50

たトランジスタにおいては、オフ状態でのソースとドレイン間のリーク電流（オフ電流）を、従来のシリコンを用いたトランジスタと比較して極めて低いものとすることができます。

#### 【0242】

適用可能な酸化物半導体としては、少なくともインジウム（In）あるいは亜鉛（Zn）を含むことが好ましい。特にInとZnを含むことが好ましい。また、該酸化物半導体を用いたトランジスタの電気特性のばらつきを減らすためのスタビライザとして、それに加えてガリウム（Ga）、スズ（Sn）、ハフニウム（Hf）、ジルコニウム（Zr）、チタン（Ti）、スカンジウム（Sc）、イットリウム（Y）、ランタノイド（例えば、セリウム（Ce）、ネオジム（Nd）、ガドリニウム（Gd））から選ばれた一種、または複数種が含まれていることが好ましい。

#### 【0243】

例えば、酸化物半導体として、酸化インジウム、酸化スズ、酸化亜鉛、In-Zn系酸化物、Sn-Zn系酸化物、Al-Zn系酸化物、Zn-Mg系酸化物、Sn-Mg系酸化物、In-Mg系酸化物、In-Ga系酸化物、In-Ga-Zn系酸化物（IGZOとも表記する）、In-Al-Zn系酸化物、In-Sn-Zn系酸化物、Sn-Ga-Zn系酸化物、Al-Ga-Zn系酸化物、Sn-Al-Zn系酸化物、In-Hf-Zn系酸化物、In-Zr-Zn系酸化物、In-Ti-Zn系酸化物、In-Sc-Zn系酸化物、In-Y-Zn系酸化物、In-La-Zn系酸化物、In-Ce-Zn系酸化物、In-Pr-Zn系酸化物、In-Nd-Zn系酸化物、In-Sm-Zn系酸化物、In-Eu-Zn系酸化物、In-Gd-Zn系酸化物、In-Tb-Zn系酸化物、In-Dy-Zn系酸化物、In-Ho-Zn系酸化物、In-Er-Zn系酸化物、In-Tm-Zn系酸化物、In-Yb-Zn系酸化物、In-Lu-Zn系酸化物、In-Sn-Ga-Zn系酸化物、In-Hf-Ga-Zn系酸化物、In-Al-Ga-Zn系酸化物、In-Sn-Al-Zn系酸化物、In-Sn-Hf-Zn系酸化物、In-Hf-Al-Zn系酸化物を用いることができる。

#### 【0244】

ここで、In-Ga-Zn系酸化物とは、InとGaとZnを主成分として有する酸化物という意味であり、InとGaとZnの比率は問わない。また、InとGaとZn以外の金属元素が入っていてもよい。

#### 【0245】

また、酸化物半導体として、 $InMO_3 (ZnO)_m$  ( $m > 0$ 、且つ、 $m$ は整数でない) で表記される材料を用いてもよい。なお、Mは、Ga、Fe、Mn及びCoから選ばれた一の金属元素または複数の金属元素、若しくは上記のスタビライザとしての元素を示す。

#### 【0246】

例えば、 $In:Ga:Zn = 1:1:1$ 、 $In:Ga:Zn = 1:3:2$ 、 $In:Ga:Zn = 1:3:4$ 、 $In:Ga:Zn = 1:3:6$ 、 $In:Ga:Zn = 3:1:2$ あるいは $In:Ga:Zn = 2:1:3$ の原子数比のIn-Ga-Zn系酸化物やその組成の近傍の酸化物を用いるとよい。

#### 【0247】

酸化物半導体膜に水素が多量に含まれると、酸化物半導体と結合することによって、水素の一部がドナーとなり、キャリアである電子を生じてしまう。これにより、トランジスタのしきい値電圧がマイナス方向にシフトしてしまう。そのため、酸化物半導体膜の形成後において、脱水化処理（脱水素化処理）を行い酸化物半導体膜から、水素、又は水分を除去して不純物が極力含まれないように高純度化することが好ましい。

#### 【0248】

なお、酸化物半導体膜への脱水化処理（脱水素化処理）によって、酸化物半導体膜から酸素も同時に減少してしまうことがある。よって、酸化物半導体膜への脱水化処理（脱水素化処理）によって増加した酸素欠損を補填するため酸素を酸化物半導体膜に加える処理

10

20

30

40

50

を行うことが好ましい。本明細書等において、酸化物半導体膜に酸素を供給する場合を、加酸素化処理と記す場合がある、または酸化物半導体膜に含まれる酸素を化学量論的組成よりも多くする場合を過酸素化処理と記す場合がある。

【0249】

このように、酸化物半導体膜は、脱水化処理（脱水素化処理）により、水素または水分が除去され、加酸素化処理により酸素欠損を補填することによって、i型（真性）化またはi型に限りなく近く実質的にi型（真性）である酸化物半導体膜とすることができる。なお、実質的に真性とは、酸化物半導体膜中にドナーに由来するキャリアが極めて少なく（ゼロに近く）、キャリア密度が $1 \times 10^{17} / \text{cm}^3$ 以下、 $1 \times 10^{16} / \text{cm}^3$ 以下、 $1 \times 10^{15} / \text{cm}^3$ 以下、 $1 \times 10^{14} / \text{cm}^3$ 以下、 $1 \times 10^{13} / \text{cm}^3$ 以下であることをいう。10

【0250】

また、このように、i型又は実質的にi型である酸化物半導体膜を備えるトランジスタは、極めて優れたオフ電流特性を実現できる。例えば、酸化物半導体膜を用いたトランジスタがオフ状態のときのドレイン電流を、室温（25程度）にて $1 \times 10^{-18} \text{ A}$ 以下、好ましくは $1 \times 10^{-21} \text{ A}$ 以下、さらに好ましくは $1 \times 10^{-24} \text{ A}$ 以下、または85にて $1 \times 10^{-15} \text{ A}$ 以下、好ましくは $1 \times 10^{-18} \text{ A}$ 以下、さらに好ましくは $1 \times 10^{-21} \text{ A}$ 以下とすることができます。なお、トランジスタがオフ状態とは、nチャネル型のトランジスタの場合、ゲート電圧がしきい値電圧よりも十分小さい状態をいう。具体的には、ゲート電圧がしきい値電圧よりも1V以上、2V以上または3V以上小さければ、トランジスタはオフ状態となる。20

【0251】

<酸化物半導体の構造について>

以下では、酸化物半導体の構造について説明する。

【0252】

酸化物半導体は、単結晶酸化物半導体と、それ以外の非単結晶酸化物半導体とに分けられる。非単結晶酸化物半導体としては、C A A C - O S (C Axis Aligned Crystalline Oxide Semiconductor)、多結晶酸化物半導体、微結晶酸化物半導体、非晶質酸化物半導体などがある。

【0253】

また別の観点では、酸化物半導体は、非晶質酸化物半導体と、それ以外の結晶性酸化物半導体とに分けられる。結晶性酸化物半導体としては、単結晶酸化物半導体、C A A C - O S、多結晶酸化物半導体、微結晶酸化物半導体などがある。30

【0254】

< C A A C - O S >

まずは、C A A C - O Sについて説明する。なお、C A A C - O Sを、C A N C (C - Axis Aligned nanocrystals)を有する酸化物半導体と呼ぶこともできる。

【0255】

C A A C - O Sは、c軸配向した複数の結晶部（ペレットともいう。）を有する酸化物半導体の一つである。40

【0256】

透過型電子顕微鏡（T E M : Transmission Electron Microscope）によって、C A A C - O Sの明視野像と回折パターンとの複合解析像（高分解能T E M像ともいう。）を観察すると、複数のペレットを確認することができる。一方、高分解能T E M像ではペレット同士の境界、即ち結晶粒界（グレインバウンダリーともいう。）を明確に確認することができない。そのため、C A A C - O Sは、結晶粒界に起因する電子移動度の低下が起こりにくいといえる。

【0257】

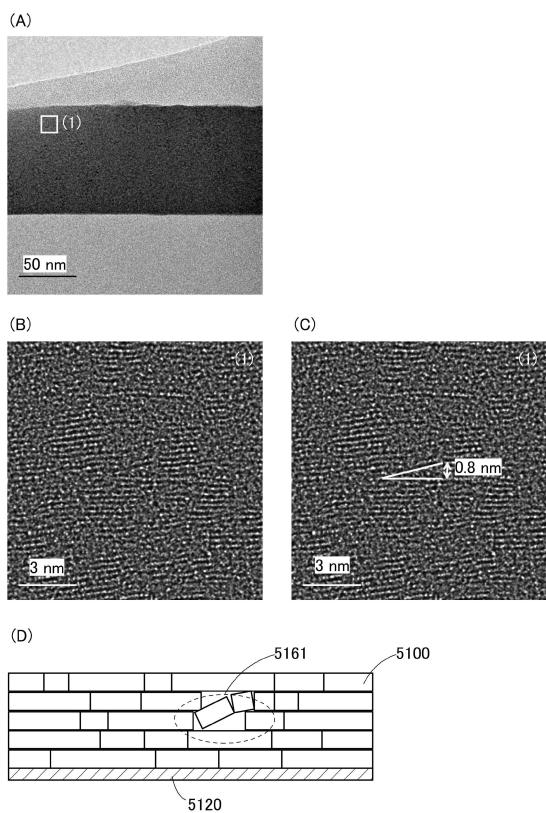

以下では、T E Mによって観察したC A A C - O Sについて説明する。図17（A）に

50

、試料面と略平行な方向から観察した C AAC - OS の断面の高分解能 TEM 像を示す。高分解能 TEM 像の観察には、球面収差補正 (Spherical Aberration Corrector) 機能を用いた。球面収差補正機能を用いた高分解能 TEM 像を、特に Cs 補正高分解能 TEM 像と呼ぶ。Cs 補正高分解能 TEM 像の取得は、例えば、日本電子株式会社製原子分解能分析電子顕微鏡 JEM - ARM 200 F などによって行うことができる。

#### 【0258】

図 17 (A) の領域 (1) を拡大した Cs 補正高分解能 TEM 像を図 17 (B) に示す。図 17 (B) より、ペレットにおいて、金属原子が層状に配列していることを確認できる。金属原子の各層の配列は、C AAC - OS の膜を形成する面 (被形成面ともいう。) または上面の凹凸を反映しており、C AAC - OS の被形成面または上面と平行となる。

10

#### 【0259】

図 17 (B) に示すように、C AAC - OS は特徴的な原子配列を有する。図 17 (C) は、特徴的な原子配列を、補助線で示したものである。図 17 (B) および図 17 (C) より、ペレット一つの大きさは 1 nm 以上のものや、3 nm 以上のものがあり、ペレットとペレットとの傾きにより生じる隙間の大きさは 0.8 nm 程度であることがわかる。したがって、ペレットを、ナノ結晶 (nc : nanocrystal) と呼ぶこともできる。

#### 【0260】

ここで、Cs 補正高分解能 TEM 像をもとに、基板 5120 上の C AAC - OS のペレット 5100 の配置を模式的に示すと、レンガまたはブロックが積み重なったような構造となる (図 17 (D) 参照。)。図 17 (C) で観察されたペレットとペレットとの間で傾きが生じている箇所は、図 17 (D) に示す領域 5161 に相当する。

20

#### 【0261】

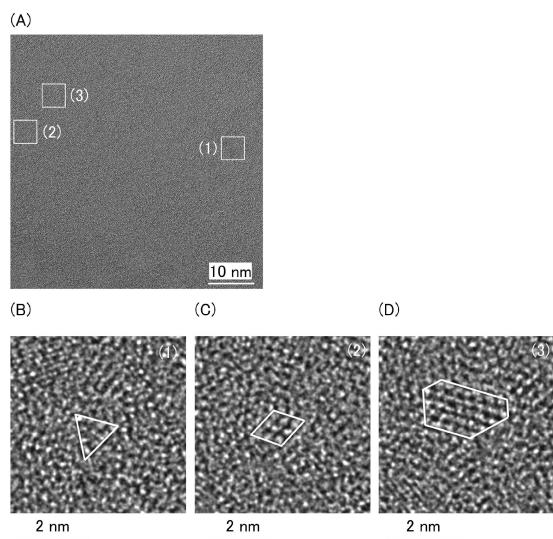

また、図 18 (A) に、試料面と略垂直な方向から観察した C AAC - OS の平面の Cs 補正高分解能 TEM 像を示す。図 18 (A) の領域 (1)、領域 (2) および領域 (3) を拡大した Cs 補正高分解能 TEM 像を、それぞれ図 18 (B)、図 18 (C) および図 18 (D) に示す。図 18 (B)、図 18 (C) および図 18 (D) より、ペレットは、金属原子が三角形状、四角形状または六角形状に配列していることを確認できる。しかしながら、異なるペレット間で、金属原子の配列に規則性は見られない。

30

#### 【0262】

次に、X 線回折 (XRD : X - Ray Diffraction) によって解析した C AAC - OS について説明する。例えば、InGaZnO<sub>4</sub> の結晶を有する C AAC - OS に対し、out - of - plane 法による構造解析を行うと、図 19 (A) に示すように回折角 (2θ) が 31° 近傍にピークが現れる場合がある。このピークは、InGaZnO<sub>4</sub> の結晶の (009) 面に帰属されることから、C AAC - OS の結晶が c 軸配向性を有し、c 軸が被形成面または上面に略垂直な方向を向いていることが確認できる。

#### 【0263】

なお、C AAC - OS の out - of - plane 法による構造解析では、2θ が 31° 近傍のピークの他に、2θ が 36° 近傍にもピークが現れる場合がある。2θ が 36° 近傍のピークは、C AAC - OS 中の一部に、c 軸配向性を有さない結晶が含まれることを示している。より好ましい C AAC - OS は、out - of - plane 法による構造解析では、2θ が 31° 近傍にピークを示し、2θ が 36° 近傍にピークを示さない。

40

#### 【0264】

一方、C AAC - OS に対し、c 軸に略垂直な方向から X 線を入射させる in - plane 法による構造解析を行うと、2θ が 56° 近傍にピークが現れる。このピークは、InGaZnO<sub>4</sub> の結晶の (110) 面に帰属される。C AAC - OS の場合は、2θ を 56° 近傍に固定し、試料面の法線ベクトルを軸 (c 軸) として試料を回転させながら分析 (スキャン) を行っても、図 19 (B) に示すように明瞭なピークは現れない。これに対し、InGaZnO<sub>4</sub> の単結晶酸化物半導体であれば、2θ を 56° 近傍に固定して

50

スキャンした場合、図19(C)に示すように(110)面と等価な結晶面に帰属されるピークが6本観察される。したがって、XRDを用いた構造解析から、CAAC-OSは、a軸およびb軸の配向が不規則であることが確認できる。

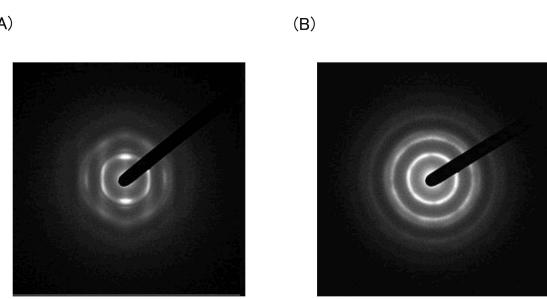

#### 【0265】

次に、電子回折によって解析したCAAC-OSについて説明する。例えば、InGaZnO<sub>4</sub>の結晶を有するCAAC-OSに対し、試料面に平行にプローブ径が300nmの電子線を入射させると、図20(A)に示すような回折パターン(制限視野透過電子回折パターンともいう。)が現れる場合がある。この回折パターンには、InGaZnO<sub>4</sub>の結晶の(009)面に起因するスポットが含まれる。したがって、電子回折によっても、CAAC-OSに含まれるペレットがc軸配向性を有し、c軸が被形成面または上面に略垂直な方向を向いていることがわかる。一方、同じ試料に対し、試料面に垂直にプローブ径が300nmの電子線を入射させたときの回折パターンを図20(B)に示す。図20(B)より、リング状の回折パターンが確認される。したがって、電子回折によっても、CAAC-OSに含まれるペレットのa軸およびb軸は配向性を有さないことがわかる。なお、図20(B)における第1リングは、InGaZnO<sub>4</sub>の結晶の(010)面および(100)面などに起因すると考えられる。また、図20(B)における第2リングは(110)面などに起因すると考えられる。

#### 【0266】

また、CAAC-OSは、欠陥準位密度の低い酸化物半導体である。酸化物半導体の欠陥としては、例えば、不純物に起因する欠陥や、酸素欠損などがある。したがって、CAAC-OSは、不純物濃度の低い酸化物半導体ということもできる。また、CAAC-OSは、酸素欠損の少ない酸化物半導体ということもできる。

#### 【0267】

酸化物半導体に含まれる不純物は、キャリアトラップとなる場合や、キャリア発生源となる場合がある。また、酸化物半導体中の酸素欠損は、キャリアトラップとなる場合や、水素を捕獲することによってキャリア発生源となる場合がある。

#### 【0268】

なお、不純物は、酸化物半導体の主成分以外の元素で、水素、炭素、シリコン、遷移金属元素などがある。例えば、シリコンなどの、酸化物半導体を構成する金属元素よりも酸素との結合力の強い元素は、酸化物半導体から酸素を奪うことで酸化物半導体の原子配列を乱し、結晶性を低下させる要因となる。また、鉄やニッケルなどの重金属、アルゴン、二酸化炭素などは、原子半径(または分子半径)が大きいため、酸化物半導体の原子配列を乱し、結晶性を低下させる要因となる。

#### 【0269】

また、欠陥準位密度の低い(酸素欠損が少ない)酸化物半導体は、キャリア密度を低くすることができる。そのような酸化物半導体を、高純度真性または実質的に高純度真性な酸化物半導体と呼ぶ。CAAC-OSは、不純物濃度が低く、欠陥準位密度が低い。即ち、高純度真性または実質的に高純度真性な酸化物半導体となりやすい。したがって、CAAC-OSを用いたトランジスタは、しきい値電圧がマイナスとなる電気特性(ノーマリーオンともいう。)になることが少ない。また、高純度真性または実質的に高純度真性な酸化物半導体は、キャリアトラップが少ない。酸化物半導体のキャリアトラップに捕獲された電荷は、放出するまでに要する時間が長く、あたかも固定電荷のように振る舞うことがある。そのため、不純物濃度が高く、欠陥準位密度が高い酸化物半導体を用いたトランジスタは、電気特性が不安定となる場合がある。一方、CAAC-OSを用いたトランジスタは、電気特性の変動が小さく、信頼性の高いトランジスタとなる。

#### 【0270】

また、CAAC-OSは欠陥準位密度が低いため、光の照射などによって生成されたキャリアが、欠陥準位に捕獲されることが少ない。したがって、CAAC-OSを用いたトランジスタは、可視光や紫外光の照射による電気特性の変動が小さい。

#### 【0271】

10

20

30

40

50

## &lt;微結晶酸化物半導体&gt;

次に、微結晶酸化物半導体について説明する。

## 【0272】

微結晶酸化物半導体は、高分解能TEM像において、結晶部を確認することができる領域と、明確な結晶部を確認することのできない領域と、を有する。微結晶酸化物半導体に含まれる結晶部は、1nm以上100nm以下、または1nm以上10nm以下の大きさであることが多い。特に、1nm以上10nm以下、または1nm以上3nm以下の微結晶であるナノ結晶を有する酸化物半導体を、n c - O S (nanocrystalline Oxide Semiconductor)と呼ぶ。n c - O Sは、例えば、高分解能TEM像では、結晶粒界を明確に確認できない場合がある。なお、ナノ結晶は、C A A C - O Sにおけるペレットと起源を同じくする可能性がある。そのため、以下ではn c - O Sの結晶部をペレットと呼ぶ場合がある。

## 【0273】

n c - O Sは、微小な領域（例えば、1nm以上10nm以下の領域、特に1nm以上3nm以下の領域）において原子配列に周期性を有する。また、n c - O Sは、異なるペレット間で結晶方位に規則性が見られない。そのため、膜全体で配向性が見られない。したがって、n c - O Sは、分析方法によっては、非晶質酸化物半導体と区別が付かない場合がある。例えば、n c - O Sに対し、ペレットよりも大きい径のXRD装置を用いて構造解析を行うと、out-of-plane法による解析では、結晶面を示すピークが検出されない。また、n c - O Sに対し、ペレットよりも大きいプローブ径（例えば50nm以上）の電子線を用いる電子回折（制限視野電子回折ともいう。）を行うと、ハローパターンのような回折パターンが観測される。一方、n c - O Sに対し、ペレットの大きさと近いかペレットより小さいプローブ径の電子線を用いるナノビーム電子回折を行うと、スポットが観測される。また、n c - O Sに対しナノビーム電子回折を行うと、円を描くように（リング状に）輝度の高い領域が観測される場合がある。さらに、リング状の領域内に複数のスポットが観測される場合がある。

## 【0274】

このように、ペレット（ナノ結晶）間では結晶方位が規則性を有さないことから、n c - O Sを、RANC (Random Aligned nanocrystals)を有する酸化物半導体、またはNANC (Non-Aligned nanocrystals)を有する酸化物半導体と呼ぶこともできる。

## 【0275】

n c - O Sは、非晶質酸化物半導体よりも規則性の高い酸化物半導体である。そのため、n c - O Sは、非晶質酸化物半導体よりも欠陥準位密度が低くなる。ただし、n c - O Sは、異なるペレット間で結晶方位に規則性が見られない。そのため、n c - O Sは、C A A C - O Sと比べて欠陥準位密度が高くなる。

## 【0276】

## &lt;非晶質酸化物半導体&gt;

次に、非晶質酸化物半導体について説明する。

## 【0277】

非晶質酸化物半導体は、膜中における原子配列が不規則であり、結晶部を有さない酸化物半導体である。石英のような無定形状態を有する酸化物半導体が一例である。

## 【0278】

非晶質酸化物半導体は、高分解能TEM像において結晶部を確認することができない。

## 【0279】

非晶質酸化物半導体に対し、XRD装置を用いた構造解析を行うと、out-of-plane法による解析では、結晶面を示すピークが検出されない。また、非晶質酸化物半導体に対し、電子回折を行うと、ハローパターンが観測される。また、非晶質酸化物半導体に対し、ナノビーム電子回折を行うと、スポットが観測されず、ハローパターンのみが観測される。

## 【0280】

非晶質構造については、様々な見解が示されている。例えば、原子配列に全く秩序性を有さない構造を完全な非晶質構造 (completely amorphous structure) と呼ぶ場合がある。また、最近接原子間距離または第2近接原子間距離まで秩序性を有し、かつ長距離秩序性を有さない構造を非晶質構造と呼ぶ場合もある。したがって、最も厳格な定義によれば、僅かでも原子配列に秩序性を有する酸化物半導体を非晶質酸化物半導体と呼ぶことはできない。また、少なくとも、長距離秩序性を有する酸化物半導体を非晶質酸化物半導体と呼ぶことはできない。よって、結晶部を有することから、例えば、CAAC-OSおよびnc-OSを、非晶質酸化物半導体または完全な非晶質酸化物半導体と呼ぶことはできない。

10

## 【0281】

<非晶質ライク酸化物半導体>

なお、酸化物半導体は、nc-OSと非晶質酸化物半導体との間の構造を有する場合がある。そのような構造を有する酸化物半導体を、特に非晶質ライク酸化物半導体 (a-like OS: amorphous-like Oxide Semiconductor) と呼ぶ。

## 【0282】

a-like OSは、高分解能TEM像において鬆(ボイドともいう。)が観察される場合がある。また、高分解能TEM像において、明確に結晶部を確認することのできる領域と、結晶部を確認することのできない領域と、を有する。

20

## 【0283】

鬆を有するため、a-like OSは、不安定な構造である。以下では、a-like OSが、CAAC-OSおよびnc-OSと比べて不安定な構造であることを示すため、電子照射による構造の変化を示す。

## 【0284】

電子照射を行う試料として、a-like OS(試料Aと表記する。)、nc-OS(試料Bと表記する。)およびCAAC-OS(試料Cと表記する。)を準備する。いずれの試料もIn-Ga-Zn系酸化物である。

## 【0285】

まず、各試料の高分解能断面TEM像を取得する。高分解能断面TEM像により、各試料は、いずれも結晶部を有することがわかる。

30

## 【0286】

なお、どの部分を一つの結晶部と見なすかの判定は、以下のように行えばよい。例えば、InGaZnO<sub>4</sub>の結晶の単位格子は、In-O層を3層有し、またGa-Zn-O層を6層有する、計9層がc軸方向に層状に重なった構造を有することが知られている。これらの近接する層同士の間隔は、(009)面の格子面間隔(d値ともいう。)と同程度であり、結晶構造解析からその値は0.29nmと求められている。したがって、格子縞の間隔が0.28nm以上0.30nm以下である箇所を、InGaZnO<sub>4</sub>の結晶部と見なすことができる。なお、格子縞は、InGaZnO<sub>4</sub>の結晶のa-b面に対応する。

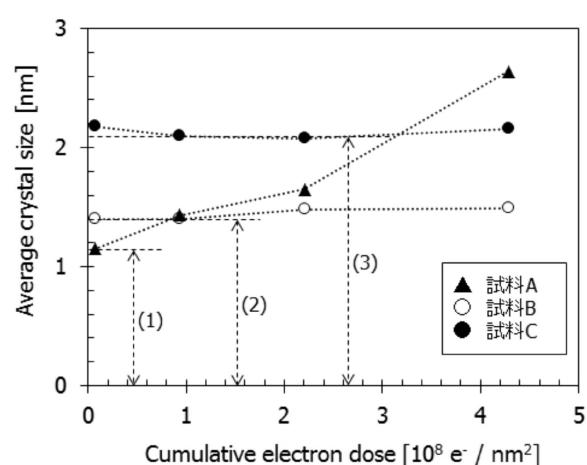

## 【0287】

図21は、各試料の結晶部(22箇所から45箇所)の平均の大きさを調査した例である。ただし、上述した格子縞の長さを結晶部の大きさとしている。図21より、a-like OSは、電子の累積照射量に応じて結晶部が大きくなっていくことがわかる。具体的には、図21中に(1)で示すように、TEMによる観察初期においては1.2nm程度の大きさだった結晶部(初期核ともいう。)が、累積照射量が4.2×10<sup>8</sup>e<sup>-</sup>/nm<sup>2</sup>においては2.6nm程度の大きさまで成長していることがわかる。一方、nc-OSおよびCAAC-OSは、電子照射開始時から電子の累積照射量が4.2×10<sup>8</sup>e<sup>-</sup>/nm<sup>2</sup>までの範囲で、結晶部の大きさに変化が見られないことがわかる。具体的には、図21中の(2)および(3)で示すように、電子の累積照射量によらず、nc-OSおよびCAAC-OSの結晶部の大きさは、それぞれ1.4nm程度および2.1nm程度

40

50

であることがわかる。

【0288】

このように、a-like OSは、電子照射によって結晶部の成長が見られる場合がある。一方、nc-OSおよびCAAC-OSは、電子照射による結晶部の成長がほとんど見られないことがわかる。即ち、a-like OSは、nc-OSおよびCAAC-OSと比べて、不安定な構造であることがわかる。

【0289】

また、鬆を有するため、a-like OSは、nc-OSおよびCAAC-OSと比べて密度の低い構造である。具体的には、a-like OSの密度は、同じ組成の単結晶の密度の78.6%以上92.3%未満となる。また、nc-OSの密度およびCAAC-OSの密度は、同じ組成の単結晶の密度の92.3%以上100%未満となる。単結晶の密度の78%未満となる酸化物半導体は、成膜すること自体が困難である。

【0290】

例えば、In:Ga:Zn = 1:1:1 [原子数比] を満たす酸化物半導体において、菱面体晶構造を有する単結晶InGaZnO<sub>4</sub>の密度は6.357 g / cm<sup>3</sup>となる。よって、例えば、In:Ga:Zn = 1:1:1 [原子数比] を満たす酸化物半導体において、a-like OSの密度は5.0 g / cm<sup>3</sup>以上5.9 g / cm<sup>3</sup>未満となる。また、例えば、In:Ga:Zn = 1:1:1 [原子数比] を満たす酸化物半導体において、nc-OSの密度およびCAAC-OSの密度は5.9 g / cm<sup>3</sup>以上6.3 g / cm<sup>3</sup>未満となる。

10

20

【0291】

なお、同じ組成の単結晶が存在しない場合がある。その場合、任意の割合で組成の異なる単結晶を組み合わせることにより、所望の組成における単結晶に相当する密度を見積もることができる。所望の組成の単結晶に相当する密度は、組成の異なる単結晶を組み合わせる割合に対して、加重平均を用いて見積もればよい。ただし、密度は、可能な限り少ない種類の単結晶を組み合わせて見積もることが好ましい。

【0292】

以上のように、酸化物半導体は、様々な構造をとり、それぞれが様々な特性を有する。なお、酸化物半導体は、例えば、非晶質酸化物半導体、a-like OS、微結晶酸化物半導体、CAAC-OSのうち、二種以上を有する積層膜であってもよい。

30

【0293】

CAAC-OS膜は、例えば以下の方法により形成することができる。

【0294】

CAAC-OS膜は、例えば、多結晶である酸化物半導体スパッタリング用ターゲットを用い、スパッタリング法によって成膜する。

【0295】

成膜時の基板温度を高めることで、基板到達後にスパッタリング粒子のマイグレーションが起こる。具体的には、基板温度を100以上740以下、好ましくは200以上500以下として成膜する。成膜時の基板温度を高めることで、スパッタリング粒子が基板に到達した場合、基板上でマイグレーションが起り、スパッタリング粒子の平らな面が基板に付着する。このとき、スパッタリング粒子が正に帯電することで、スパッタリング粒子同士が反発しながら基板に付着するため、スパッタリング粒子が偏って不均一に重なることがなく、厚さの均一なCAAC-OS膜を成膜することができる。

40

【0296】

成膜時の不純物混入を低減することで、不純物によって結晶状態が崩れることを抑制できる。例えば、成膜室内に存在する不純物濃度（水素、水、二酸化炭素及び窒素など）を低減すればよい。また、成膜ガス中の不純物濃度を低減すればよい。具体的には、露点が-80以下、好ましくは-100以下である成膜ガスを用いる。

【0297】

また、成膜ガス中の酸素割合を高め、電力を最適化することで成膜時のプラズマダメー

50

ジを軽減すると好ましい。成膜ガス中の酸素割合は、30体積%以上、好ましくは100体積%とする。

【0298】

または、C A A C - O S 膜は、以下の方法により形成する。

【0299】

まず、第1の酸化物半導体膜を1nm以上10nm未満の厚さで成膜する。第1の酸化物半導体膜はスパッタリング法を用いて成膜する。具体的には、基板温度を100以上500以下、好ましくは150以上450以下とし、成膜ガス中の酸素割合を30体積%以上、好ましくは100体積%として成膜する。

【0300】

次に、加熱処理を行い、第1の酸化物半導体膜を結晶性の高い第1のC A A C - O S 膜とする。加熱処理の温度は、350以上740以下、好ましくは450以上650以下とする。

また、加熱処理の時間は1分以上24時間以下、好ましくは6分以上4時間以下とする。また、加熱処理は、不活性雰囲気または酸化性雰囲気で行えばよい。好ましくは、不活性雰囲気で加熱処理を行った後、酸化性雰囲気で加熱処理を行う。不活性雰囲気での加熱処理により、第1の酸化物半導体膜の不純物濃度を短時間で低減することができる。一方、不活性雰囲気での加熱処理により第1の酸化物半導体膜に酸素欠損が生成されることがある。その場合、酸化性雰囲気での加熱処理によって該酸素欠損を低減することができる。なお、加熱処理は10000Pa以下、100Pa以下、10Pa以下または1Pa以下の減圧下で行ってもよい。減圧下では、第1の酸化物半導体膜の不純物濃度をさらに短時間で低減することができる。

10

【0301】

第1の酸化物半導体膜は、厚さが1nm以上10nm未満であることにより、厚さが10nm以上である場合と比べ、加熱処理によって容易に結晶化させることができる。

【0302】

次に、第1の酸化物半導体膜と同じ組成である第2の酸化物半導体膜を10nm以上50nm以下の厚さで成膜する。第2の酸化物半導体膜はスパッタリング法を用いて成膜する。具体的には、基板温度を100以上500以下、好ましくは150以上450以下とし、成膜ガス中の酸素割合を30体積%以上、好ましくは100体積%として成膜する。

20

【0303】

次に、加熱処理を行い、第2の酸化物半導体膜を第1のC A A C - O S 膜から固相成長させることで、結晶性の高い第2のC A A C - O S 膜とする。加熱処理の温度は、350以上740以下、好ましくは450以上650以下とする。また、加熱処理の時間は1分以上24時間以下、好ましくは6分以上4時間以下とする。また、加熱処理は、不活性雰囲気または酸化性雰囲気で行えばよい。好ましくは、不活性雰囲気で加熱処理を行った後、酸化性雰囲気で加熱処理を行う。不活性雰囲気での加熱処理により、第2の酸化物半導体膜の不純物濃度を短時間で低減することができる。一方、不活性雰囲気での加熱処理により第2の酸化物半導体膜に酸素欠損が生成されることがある。その場合、酸化性雰囲気での加熱処理によって該酸素欠損を低減することができる。なお、加熱処理は10000Pa以下、100Pa以下、10Pa以下または1Pa以下の減圧下で行ってもよい。減圧下では、第2の酸化物半導体膜の不純物濃度をさらに短時間で低減することができる。

30

【0304】

以上のようにして、合計の厚さが10nm以上であるC A A C - O S 膜を形成することができる。

【0305】

本実施の形態は、少なくともその一部を本明細書中に記載する他の実施の形態と適宜組み合わせて実施することができる。

【0306】

40

50

## (実施の形態 3 )

本実施の形態では、本発明の一態様のトランジスタを利用した回路の一例について図面を参照して説明する。

## 【0307】

## [回路構成例]

実施の形態1に示した構成において、トランジスタや配線、電極の接続構成を異ならすことにより、様々な回路を構成することができる。以下では、本発明の一態様の半導体装置を用いることにより実現できる回路構成の例を説明する。

## 【0308】

## [CMOS回路]

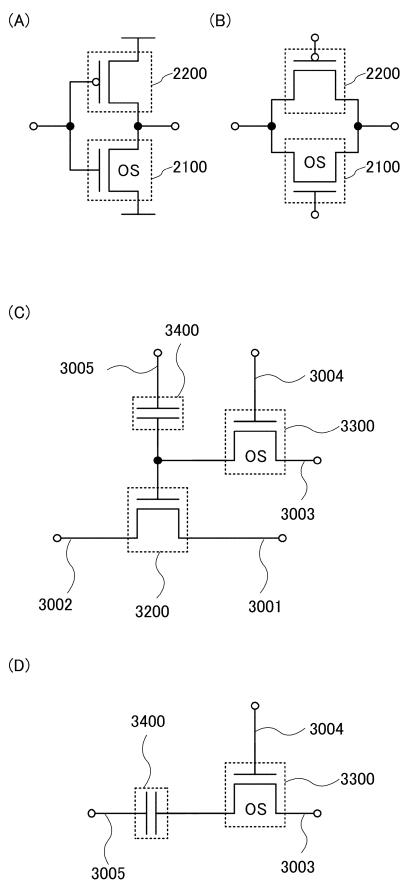

10

図22(A)に示す回路図は、pチャネル型のトランジスタ2200とnチャネル型のトランジスタ2100を直列に接続し、且つそれぞれのゲートを接続した、いわゆるCMOS回路の構成を示している。なお、図中、第2の半導体材料が適用されたトランジスタには「OS」の記号を付して示している。

## 【0309】

## [アナログスイッチ]

また、図22(B)に示す回路図は、トランジスタ2100とトランジスタ2200のそれぞれのソースとドレインを接続した構成を示している。このような構成とすることで、いわゆるアナログスイッチとして機能させることができる。

## 【0310】

20

## [記憶装置の例]

本発明の一態様であるトランジスタを使用し、電力が供給されない状況でも記憶内容の保持が可能で、且つ、書き込み回数にも制限が無い半導体装置(記憶装置)の一例を図22(C)に示す。

## 【0311】

図22(C)に示す半導体装置は、第1の半導体材料を用いたトランジスタ3200と第2の半導体材料を用いたトランジスタ3300、及び容量素子3400を有している。なお、トランジスタ3300としては、上記実施の形態で例示したトランジスタを用いることができる。

## 【0312】

30

トランジスタ3300は、酸化物半導体を有する半導体膜にチャネルが形成されるトランジスタである。トランジスタ3300は、オフ電流が小さいため、これを用いることにより長期にわたり記憶内容を保持することができる。つまり、リフレッシュ動作を必要としない、或いは、リフレッシュ動作の頻度が極めて少ない半導体記憶装置とすることが可能となるため、消費電力を十分に低減することができる。

## 【0313】

図22(C)において、第1の配線3001はトランジスタ3200のソース電極と電気的に接続され、第2の配線3002はトランジスタ3200のドレイン電極と電気的に接続されている。また、第3の配線3003はトランジスタ3300のソース電極またはドレイン電極の一方と電気的に接続され、第4の配線3004はトランジスタ3300のゲート電極と電気的に接続されている。そして、トランジスタ3200のゲート電極、及びトランジスタ3300のソース電極またはドレイン電極の他方は、容量素子3400の電極の一方と電気的に接続され、第5の配線3005は容量素子3400の電極の他方と電気的に接続されている。

40

## 【0314】

図22(C)に示す半導体装置では、トランジスタ3200のゲート電極の電位が保持可能という特徴を活かすことで、次のように、情報の書き込み、保持、読み出しが可能である。

## 【0315】

情報の書き込み及び保持について説明する。まず、第4の配線3004の電位を、トランジ

50

ンジスタ3300がオン状態となる電位にして、トランジスタ3300をオン状態とする。これにより、第3の配線3003の電位が、トランジスタ3200のゲート電極、及び容量素子3400に与えられる。すなわち、トランジスタ3200のゲート電極には、所定の電荷が与えられる（書き込み）。ここでは、異なる二つの電位レベルを与える電荷（以下Lowレベル電荷、Highレベル電荷という）のいずれかが与えられるものとする。その後、第4の配線3004の電位を、トランジスタ3300がオフ状態となる電位にして、トランジスタ3300をオフ状態とすることにより、トランジスタ3200のゲート電極に与えられた電荷が保持される（保持）。

#### 【0316】

トランジスタ3300のオフ電流は極めて小さいため、トランジスタ3200のゲート電極の電荷は長時間にわたって保持される。 10

#### 【0317】

次に情報の読み出しについて説明する。第1の配線3001に所定の電位（定電位）を与えた状態で、第5の配線3005に適切な電位（読み出し電位）を与えると、トランジスタ3200のゲート電極に保持された電荷量に応じて、第2の配線3002は異なる電位をとる。一般に、トランジスタ3200をnチャネル型とすると、トランジスタ3200のゲート電極にHighレベル電荷が与えられている場合の見かけのしきい値 $V_{th\_H}$ は、トランジスタ3200のゲート電極にLowレベル電荷が与えられている場合の見かけのしきい値 $V_{th\_L}$ より低くなるためである。ここで、見かけのしきい値電圧とは、トランジスタ3200を「オン状態」とするために必要な第5の配線3005の電位をいうものとする。したがって、第5の配線3005の電位を $V_{th\_H}$ と $V_{th\_L}$ の間の電位 $V_0$ とすることにより、トランジスタ3200のゲート電極に与えられた電荷を判別できる。例えば、書き込みにおいて、Highレベル電荷が与えられていた場合には、第5の配線3005の電位が $V_0$  ( $> V_{th\_H}$ ) となれば、トランジスタ3200は「オン状態」となる。Lowレベル電荷が与えられていた場合には、第5の配線3005の電位が $V_0$  ( $< V_{th\_L}$ ) となっても、トランジスタ3200は「オフ状態」のままである。このため、第2の配線3002の電位を判別することで、保持されている情報を読み出すことができる。 20

#### 【0318】

なお、メモリセルをアレイ状に配置して用いる場合、所望のメモリセルの情報のみを読み出せることが必要になる。このように情報を読み出さない場合には、ゲート電極の状態にかかわらずトランジスタ3200が「オフ状態」となるような電位、つまり、 $V_{th\_H}$ より小さい電位を第5の配線3005に与えればよい。または、ゲート電極の状態にかかわらずトランジスタ3200が「オン状態」となるような電位、つまり、 $V_{th\_L}$ より大きい電位を第5の配線3005に与えればよい。 30

#### 【0319】

図22(D)に示す半導体装置は、トランジスタ3200を設けていない点で主に図22(C)と相違している。この場合も上記と同様の動作により情報の書き込み及び保持動作が可能である。 40

#### 【0320】

次に、情報の読み出しについて説明する。トランジスタ3300がオン状態となると、浮遊状態である第3の配線3003と容量素子3400とが導通し、第3の配線3003と容量素子3400の間で電荷が再分配される。その結果、第3の配線3003の電位が変化する。第3の配線3003の電位の変化量は、容量素子3400の電極の一方の電位（あるいは容量素子3400に蓄積された電荷）によって、異なる値をとる。

#### 【0321】

例えば、容量素子3400の電極の一方の電位をV、容量素子3400の容量をC、第3の配線3003が有する容量成分をCB、電荷が再分配される前の第3の配線3003の電位をVB0とすると、電荷が再分配された後の第3の配線3003の電位は、 $(CB \times VB0 + C \times V) / (CB + C)$ となる。したがって、メモリセルの状態として、容量 50

素子 3400 の電極の一方の電位が  $V_1$  と  $V_0$  ( $V_1 > V_0$ ) の 2 状態をとるとすると、電位  $V_1$  を保持している場合の第 3 の配線 3003 の電位 ( $= (C_B \times V_B 0 + C \times V_1) / (C_B + C)$ ) は、電位  $V_0$  を保持している場合の第 3 の配線 3003 の電位 ( $= (C_B \times V_B 0 + C \times V_0) / (C_B + C)$ ) よりも高くなることがわかる。

【0322】

そして、第 3 の配線 3003 の電位を所定の電位と比較することで、情報を読み出すことができる。

【0323】

この場合、メモリセルを駆動させるための駆動回路に上記第 1 の半導体材料が適用されたトランジスタを用い、トランジスタ 3300 として第 2 の半導体材料が適用されたトランジスタを駆動回路上に積層して設ける構成とすればよい。 10

【0324】

本実施の形態に示す半導体装置では、チャネル形成領域に酸化物半導体を用いたオフ電流の極めて小さいトランジスタを適用することで、極めて長期にわたり記憶内容を保持することが可能である。つまり、リフレッシュ動作が不要となるか、または、リフレッシュ動作の頻度を極めて低くすることが可能となるため、消費電力を十分に低減することができる。また、電力の供給がない場合（ただし、電位は固定されていることが望ましい）であっても、長期にわたって記憶内容を保持することが可能である。

【0325】

また、本実施の形態に示す半導体装置では、情報の書き込みに高い電圧を必要とせず、素子の劣化の問題もない。例えば、従来の不揮発性メモリのように、フローティングゲートへの電子の注入や、フローティングゲートからの電子の引き抜きを行う必要がないため、ゲート絶縁層の劣化といった問題が全く生じない。すなわち、開示する発明に係る半導体装置では、従来の不揮発性メモリで問題となっている書き換え可能回数に制限はなく、信頼性が飛躍的に向上する。さらに、トランジスタのオン状態、オフ状態によって、情報の書き込みが行われるため、高速な動作も容易に実現しうる。 20

【0326】

本実施の形態は、少なくともその一部を本明細書中に記載する他の実施の形態と適宜組み合わせて実施することができる。

【0327】

（実施の形態 4）

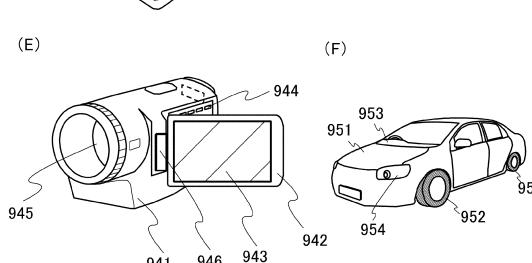

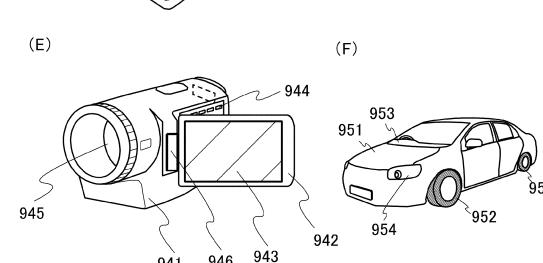

本実施の形態では、上記実施の形態で例示したトランジスタ、または記憶装置を含む RF タグについて、図 23 を用いて説明する。 30

【0328】

本実施の形態における RF タグは、内部に記憶回路を有し、記憶回路に必要な情報を記憶し、非接触手段、例えば無線通信を用いて外部と情報の授受を行うものである。このような特徴から、RF タグは、物品などの個体情報を読み取ることにより物品の識別を行う個体認証システムなどに用いることが可能である。なお、これらの用途に用いるためには極めて高い信頼性が要求される。

【0329】

RF タグの構成について図 23 を用いて説明する。図 23 は、RF タグの構成例を示すブロック図である。 40

【0330】

図 23 に示すように RF タグ 800 は、通信器 801（質問器、リーダ / ライタなどともいう）に接続されたアンテナ 802 から送信される無線信号 803 を受信するアンテナ 804 を有する。また、RF タグ 800 は、整流回路 805、定電圧回路 806、復調回路 807、変調回路 808、論理回路 809、記憶回路 810、ROM 811 を有している。なお、復調回路 807 に含まれる整流作用を示すトランジスタに逆方向電流を十分に抑制することが可能な材料、例えば、酸化物半導体が用いられた構成としてもよい。これにより、逆方向電流に起因する整流作用の低下を抑制し、復調回路の出力が飽和すること 50

を防止できる。つまり、復調回路の入力に対する復調回路の出力を線形に近づけることができる。なお、データの伝送形式は、一対のコイルを対向配置して相互誘導によって交信を行う電磁結合方式、誘導電磁界によって交信する電磁誘導方式、電波を利用して交信する電波方式の3つに大別される。本実施の形態に示すRFタグ800は、そのいずれの方式に用いることも可能である。

#### 【0331】

次に各回路の構成について説明する。アンテナ804は、通信器801に接続されたアンテナ802との間で無線信号803の送受信を行うためのものである。また、整流回路805は、アンテナ804で無線信号を受信することにより生成される入力交流信号を整流、例えば、半波2倍圧整流し、後段に設けられた容量素子により、整流された信号を平滑化することで入力電位を生成するための回路である。なお、整流回路805の入力側または出力側には、リミッタ回路を設けてもよい。リミッタ回路とは、入力交流信号の振幅が大きく、内部生成電圧が大きい場合に、ある電力以上の電力を後段の回路に入力しないように制御するための回路である。

10

#### 【0332】

定電圧回路806は、入力電位から安定した電源電圧を生成し、各回路に供給するための回路である。なお、定電圧回路806は、内部にリセット信号生成回路を有していてもよい。リセット信号生成回路は、安定した電源電圧の立ち上がりを利用して、論理回路809のリセット信号を生成するための回路である。

20

#### 【0333】

復調回路807は、入力交流信号を包絡線検出することにより復調し、復調信号を生成するための回路である。また、変調回路808は、アンテナ804より出力するデータに応じて変調をおこなうための回路である。

#### 【0334】

論理回路809は復調信号を解析し、処理を行うための回路である。記憶回路810は、入力された情報を保持する回路であり、ロウデコーダ、カラムデコーダ、記憶領域などを有する。また、ROM811は、固有番号(ID)などを格納し、処理に応じて出力をを行うための回路である。

#### 【0335】

なお、上述の各回路は、必要に応じて、適宜、取捨することができる。

30

#### 【0336】

ここで、先の実施の形態で説明した記憶回路を、記憶回路810に用いることができる。本発明の一態様の記憶回路は、電源が遮断された状態であっても情報を保持できるため、RFタグに好適に用いることができる。さらに本発明の一態様の記憶回路は、データの書き込みに必要な電力(電圧)が従来の不揮発性メモリに比べて著しく小さいため、データの読み出し時と書き込み時の最大通信距離の差を生じさせないことも可能である。さらに、データの書き込み時に電力が不足し、誤動作または誤書き込みが生じることを抑制することができる。

#### 【0337】

また、本発明の一態様の記憶回路は、不揮発性のメモリとして用いることが可能であるため、ROM811に適用することもできる。その場合には、生産者がROM811にデータを書き込むためのコマンドを別途用意し、ユーザーが自由に書き換えできないようにしておくことが好ましい。生産者が出荷前に固有番号を書込んだのちに製品を出荷することで、作製したRFタグすべてについて固有番号を付与するのではなく、出荷する良品にのみ固有番号を割り当てることが可能となり、出荷後の製品の固有番号が不連続になることがなく出荷後の製品に対応した顧客管理が容易となる。

40

#### 【0338】

本実施の形態は、少なくともその一部を本明細書中に記載する他の実施の形態と適宜組み合わせて実施することができる。

#### 【0339】

50

## (実施の形態 5 )

本実施の形態では、少なくとも実施の形態で説明したトランジスタを用いることができ、先の実施の形態で説明した記憶装置を含む C P U について説明する。

## 【 0 3 4 0 】

図 2 4 は、先の実施の形態で説明したトランジスタを少なくとも一部に用いた C P U の一例の構成を示すブロック図である。

## 【 0 3 4 1 】

図 2 4 に示す C P U は、基板 1 1 9 0 上に、 A L U 1 1 9 1 ( A L U : A r i t h m e t i c l o g i c u n i t 、演算回路)、 A L U コントローラ 1 1 9 2 、インストラクションデコーダ 1 1 9 3 、インタラプトコントローラ 1 1 9 4 、タイミングコントローラ 1 1 9 5 、レジスタ 1 1 9 6 、レジスタコントローラ 1 1 9 7 、バスインターフェース 1 1 9 8 ( Bus I / F ) 、書き換え可能な R O M 1 1 9 9 、及び R O M インターフェース 1 1 8 9 ( R O M I / F ) を有している。基板 1 1 9 0 は、半導体基板、 S O I 基板、ガラス基板などを用いる。 R O M 1 1 9 9 及び R O M インターフェース 1 1 8 9 は、別チップに設けてもよい。もちろん、図 2 4 に示す C P U は、その構成を簡略化して示した一例にすぎず、実際の C P U はその用途によって多種多様な構成を有している。例えば、図 2 4 に示す C P U または演算回路を含む構成を一つのコアとし、当該コアを複数含み、それぞれのコアが並列で動作するような構成としてもよい。また、 C P U が内部演算回路やデータバスで扱えるビット数は、例えば 8 ビット、 16 ビット、 32 ビット、 64 ビットなどとすることができる。

10

20

## 【 0 3 4 2 】

バスインターフェース 1 1 9 8 を介して C P U に入力された命令は、インストラクションデコーダ 1 1 9 3 に入力され、デコードされた後、 A L U コントローラ 1 1 9 2 、インタラプトコントローラ 1 1 9 4 、レジスタコントローラ 1 1 9 7 、タイミングコントローラ 1 1 9 5 に入力される。

## 【 0 3 4 3 】

A L U コントローラ 1 1 9 2 、インタラプトコントローラ 1 1 9 4 、レジスタコントローラ 1 1 9 7 、タイミングコントローラ 1 1 9 5 は、デコードされた命令に基づき、各種制御を行なう。具体的に A L U コントローラ 1 1 9 2 は、 A L U 1 1 9 1 の動作を制御するための信号を生成する。また、インタラプトコントローラ 1 1 9 4 は、 C P U のプログラム実行中に、外部の入出力装置や、周辺回路からの割り込み要求を、その優先度やマスク状態から判断し、処理する。レジスタコントローラ 1 1 9 7 は、レジスタ 1 1 9 6 のアドレスを生成し、 C P U の状態に応じてレジスタ 1 1 9 6 の読み出しや書き込みを行なう。

30

## 【 0 3 4 4 】

また、タイミングコントローラ 1 1 9 5 は、 A L U 1 1 9 1 、 A L U コントローラ 1 1 9 2 、インストラクションデコーダ 1 1 9 3 、インタラプトコントローラ 1 1 9 4 、及びレジスタコントローラ 1 1 9 7 の動作のタイミングを制御する信号を生成する。例えばタイミングコントローラ 1 1 9 5 は、基準クロック信号 C L K 1 を元に、内部クロック信号 C L K 2 を生成する内部クロック生成部を備えており、内部クロック信号 C L K 2 を上記各種回路に供給する。

40

## 【 0 3 4 5 】

図 2 4 に示す C P U では、レジスタ 1 1 9 6 に、メモリセルが設けられている。レジスタ 1 1 9 6 のメモリセルとして、先の実施の形態に示したトランジスタを用いることができる。

## 【 0 3 4 6 】

図 2 4 に示す C P U において、レジスタコントローラ 1 1 9 7 は、 A L U 1 1 9 1 からの指示に従い、レジスタ 1 1 9 6 における保持動作の選択を行う。すなわち、レジスタ 1 1 9 6 が有するメモリセルにおいて、フリップフロップによるデータの保持を行うか、容量素子によるデータの保持を行うかを、選択する。フリップフロップによるデータの保持

50

が選択されている場合、レジスタ 1196 内のメモリセルへの、電源電圧の供給が行われる。容量素子におけるデータの保持が選択されている場合、容量素子へのデータの書き換えが行われ、レジスタ 1196 内のメモリセルへの電源電圧の供給を停止することができる。

【0347】

図 25 は、レジスタ 1196 として用いることのできる記憶素子の回路図の一例である。記憶素子 1200 は、電源遮断で記憶データが揮発する回路 1201 と、電源遮断で記憶データが揮発しない回路 1202 と、スイッチ 1203 と、スイッチ 1204 と、論理素子 1206 と、容量素子 1207 と、選択機能を有する回路 1220 と、を有する。回路 1202 は、容量素子 1208 と、トランジスタ 1209 と、トランジスタ 1210 と、を有する。なお、記憶素子 1200 は、必要に応じて、ダイオード、抵抗素子、インダクタなどのその他の素子をさらに有していても良い。

10

【0348】

ここで、回路 1202 には、先の実施の形態で説明した記憶装置を用いることができる。記憶素子 1200 への電源電圧の供給が停止した際、回路 1202 のトランジスタ 1209 のゲートには接地電位 (0V)、またはトランジスタ 1209 がオフする電位が入力され続ける構成とする。例えば、トランジスタ 1209 のゲートが抵抗等の負荷を介して接地される構成とする。

【0349】

スイッチ 1203 は、一導電型（例えば、n チャネル型）のトランジスタ 1213 を用いて構成され、スイッチ 1204 は、一導電型とは逆の導電型（例えば、p チャネル型）のトランジスタ 1214 を用いて構成した例を示す。ここで、スイッチ 1203 の第 1 の端子はトランジスタ 1213 のソースとドレインの一方に対応し、スイッチ 1203 の第 2 の端子はトランジスタ 1213 のソースとドレインの他方に対応し、スイッチ 1203 はトランジスタ 1213 のゲートに入力される制御信号 RD によって、第 1 の端子と第 2 の端子の間の導通または非導通（つまり、トランジスタ 1213 のオン状態またはオフ状態）が選択される。スイッチ 1204 の第 1 の端子はトランジスタ 1214 のソースとドレインの一方に対応し、スイッチ 1204 の第 2 の端子はトランジスタ 1214 のソースとドレインの他方に対応し、スイッチ 1204 はトランジスタ 1214 のゲートに入力される制御信号 RD によって、第 1 の端子と第 2 の端子の間の導通または非導通（つまり、トランジスタ 1214 のオン状態またはオフ状態）が選択される。

20

【0350】

トランジスタ 1209 のソースとドレインの一方は、容量素子 1208 の一対の電極のうちの一方、及びトランジスタ 1210 のゲートと電気的に接続される。ここで、接続部分をノード M2 とする。トランジスタ 1210 のソースとドレインの一方は、低電源電位を供給することのできる配線（例えば GND 線）に電気的に接続され、他方は、スイッチ 1203 の第 1 の端子（トランジスタ 1213 のソースとドレインの一方）と電気的に接続される。スイッチ 1203 の第 2 の端子（トランジスタ 1213 のソースとドレインの他方）はスイッチ 1204 の第 1 の端子（トランジスタ 1214 のソースとドレインの一方）と電気的に接続される。スイッチ 1204 の第 2 の端子（トランジスタ 1214 のソースとドレインの他方）は電源電位 VDD を供給することのできる配線と電気的に接続される。スイッチ 1203 の第 2 の端子（トランジスタ 1213 のソースとドレインの他方）と、スイッチ 1204 の第 1 の端子（トランジスタ 1214 のソースとドレインの一方）と、論理素子 1206 の入力端子と、容量素子 1207 の一対の電極のうちの一方とは電気的に接続される。ここで、接続部分をノード M1 とする。容量素子 1207 の一対の電極のうちの他方は、一定の電位が入力される構成とすることができます。例えば、低電源電位 (GND 等) または高電源電位 (VDD 等) が入力される構成とすることができます。容量素子 1207 の一対の電極のうちの他方は、低電源電位を供給することのできる配線（例えば GND 線）と電気的に接続される。容量素子 1208 の一対の電極のうちの他方は、一定の電位が入力される構成とすることができます。例えば、低電源電位 (GND 等)

30

40

50

) または高電源電位 ( V D D 等 ) が入力される構成とすることができる。容量素子 1208 の一対の電極のうちの他方は、低電源電位を供給することのできる配線 ( 例えは G N D 線 ) と電気的に接続される。

【 0 3 5 1 】

なお、容量素子 1207 及び容量素子 1208 は、トランジスタや配線の寄生容量等を積極的に利用することによって省略することも可能である。

【 0 3 5 2 】

トランジスタ 1209 の第 1 ゲート ( 第 1 のゲート電極 ) には、制御信号 W E が入力される。スイッチ 1203 及びスイッチ 1204 は、制御信号 W E とは異なる制御信号 R D によって第 1 の端子と第 2 の端子の間の導通状態または非導通状態を選択され、一方のスイッチの第 1 の端子と第 2 の端子の間が導通状態のとき他方のスイッチの第 1 の端子と第 2 の端子の間は非導通状態となる。

10

【 0 3 5 3 】

トランジスタ 1209 のソースとドレインの他方には、回路 1201 に保持されたデータに対応する信号が入力される。図 25 では、回路 1201 から出力された信号が、トランジスタ 1209 のソースとドレインの他方に入力される例を示した。スイッチ 1203 の第 2 の端子 ( トランジスタ 1213 のソースとドレインの他方 ) から出力される信号は、論理素子 1206 によってその論理値が反転された反転信号となり、回路 1220 を介して回路 1201 に入力される。

【 0 3 5 4 】

20

なお、図 25 では、スイッチ 1203 の第 2 の端子 ( トランジスタ 1213 のソースとドレインの他方 ) から出力される信号は、論理素子 1206 及び回路 1220 を介して回路 1201 に入力する例を示したがこれに限定されない。スイッチ 1203 の第 2 の端子 ( トランジスタ 1213 のソースとドレインの他方 ) から出力される信号が、論理値を反転させられることなく、回路 1201 に入力されてもよい。例えば、回路 1201 内に、入力端子から入力された信号の論理値が反転した信号が保持されるノードが存在する場合に、スイッチ 1203 の第 2 の端子 ( トランジスタ 1213 のソースとドレインの他方 ) から出力される信号を当該ノードに入力することができる。

【 0 3 5 5 】

また、図 25 において、記憶素子 1200 に用いられるトランジスタのうち、トランジスタ 1209 以外のトランジスタは、酸化物半導体以外の半導体でなる層または基板 1190 にチャネルが形成されるトランジスタとすることができる。例えば、シリコン層またはシリコン基板にチャネルが形成されるトランジスタとすることができる。また、記憶素子 1200 に用いられるトランジスタ全てを、チャネルが酸化物半導体膜で形成されるトランジスタとすることもできる。または、記憶素子 1200 は、トランジスタ 1209 以外にも、チャネルが酸化物半導体膜で形成されるトランジスタを含んでいてもよく、残りのトランジスタは酸化物半導体以外の半導体でなる層または基板 1190 にチャネルが形成されるトランジスタとすることもできる。

30

【 0 3 5 6 】

図 25 における回路 1201 には、例えばフリップフロップ回路を用いることができる。また、論理素子 1206 としては、例えばインバータやクロックドインバータ等を用いることができる。

40

【 0 3 5 7 】

本発明の一態様における半導体装置では、記憶素子 1200 に電源電圧が供給されない間は、回路 1201 に記憶されていたデータを、回路 1202 に設けられた容量素子 1208 によって保持することができる。

【 0 3 5 8 】

また、酸化物半導体膜にチャネルが形成されるトランジスタはオフ電流が極めて小さい。例えば、酸化物半導体膜にチャネルが形成されるトランジスタのオフ電流は、結晶性を有するシリコンにチャネルが形成されるトランジスタのオフ電流に比べて著しく低い。そ

50

のため、当該トランジスタをトランジスタ 1209 として用いることによって、記憶素子 1200 に電源電圧が供給されない間も容量素子 1208 に保持された信号は長期間にわたり保たれる。こうして、記憶素子 1200 は電源電圧の供給が停止した間も記憶内容（データ）を保持することが可能である。

【0359】

また、スイッチ 1203 及びスイッチ 1204 を設けることによって、プリチャージ動作を行うことを特徴とする記憶素子であるため、電源電圧供給再開後に、回路 1201 が元のデータを保持しなおすまでの時間を短くすることができる。

【0360】

また、回路 1202 において、容量素子 1208 によって保持された信号はトランジスタ 1210 のゲートに入力される。そのため、記憶素子 1200 への電源電圧の供給が再開された後、容量素子 1208 によって保持された信号を、トランジスタ 1210 の状態（オン状態、またはオフ状態）に変換して、回路 1202 から読み出すことができる。それ故、容量素子 1208 に保持された信号に対応する電位が多少変動していても、元の信号を正確に読み出すことが可能である。

【0361】

このような記憶素子 1200 を、プロセッサが有するレジスタやキャッシュメモリなどの記憶装置に用いることで、電源電圧の供給停止による記憶装置内のデータの消失を防ぐことができる。また、電源電圧の供給を再開した後、短時間で電源供給停止前の状態に復帰することができる。よって、プロセッサ全体、もしくはプロセッサを構成する一つ、または複数の論理回路において、短い時間でも電源停止を行うため、消費電力を抑えることができる。

【0362】

本実施の形態では、記憶素子 1200 を C P U に用いる例として説明したが、記憶素子 1200 は、D S P (D i g i t a l S i g n a l P r o c e s s o r)、カスタム L S I、P L D (P r o g r a m m a b l e L o g i c D e v i c e) 等の L S I、R F (R a d i o F r e q u e n c y) デバイスにも応用可能である。

【0363】

本実施の形態は、少なくともその一部を本明細書中に記載する他の実施の形態と適宜組み合わせて実施することができる。

【0364】

（実施の形態 6）

本実施の形態では、本発明の一態様の表示パネルの構成例について説明する。

【0365】

[構成例]

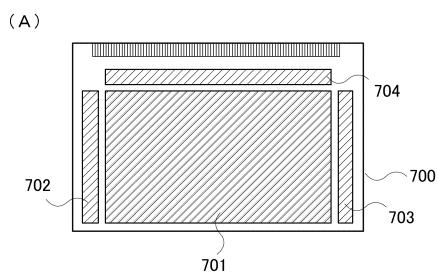

図 26 (A) は、本発明の一態様の表示パネルの上面図であり、図 26 (B) は、本発明の一態様の表示パネルの画素に液晶素子を適用する場合に用いることができる画素回路を説明するための回路図である。また、図 26 (C) は、本発明の一態様の表示パネルの画素に有機 E L 素子を適用する場合に用いることができる画素回路を説明するための回路図である。

【0366】

画素部に配置するトランジスタは、上記実施の形態に従って形成することができる。また、当該トランジスタは n チャネル型とすることが容易なので、駆動回路のうち、n チャネル型トランジスタで構成することができる駆動回路の一部を画素部のトランジスタと同一基板上に形成する。このように、画素部や駆動回路に上記実施の形態に示すトランジスタを用いることにより、信頼性の高い表示装置を提供することができる。

【0367】

アクティブマトリクス型表示装置のブロック図の一例を図 26 (A) に示す。表示装置の基板 700 上には、画素部 701、第 1 の走査線駆動回路 702、第 2 の走査線駆動回路 703、信号線駆動回路 704 を有する。画素部 701 には、複数の信号線が信号線駆

10

20

30

40

50

動回路 704 から延伸して配置され、複数の走査線が第 1 の走査線駆動回路 702、及び第 2 の走査線駆動回路 703 から延伸して配置されている。なお走査線と信号線との交差領域には、各々、表示素子を有する画素がマトリクス状に設けられている。また、表示装置の基板 700 は FPC (Flexible Printed Circuit) 等の接続部を介して、タイミング制御回路（コントローラ、制御 IC ともいう）に接続されている。

【0368】

図 26 (A) では、第 1 の走査線駆動回路 702、第 2 の走査線駆動回路 703、信号線駆動回路 704 は、画素部 701 と同じ基板 700 上に形成される。そのため、外部に設ける駆動回路等の部品の数が減るので、コストの低減を図ることができる。また、基板 700 外部に駆動回路を設けた場合、配線を延伸させる必要が生じ、配線間の接続数が増える。同じ基板 700 上に駆動回路を設けた場合、その配線間の接続数を減らすことができ、信頼性の向上、又は歩留まりの向上を図ることができる。

【0369】

〔液晶パネル〕

また、画素の回路構成の一例を図 26 (B) に示す。ここでは、VA 型液晶表示パネルの画素に適用することができる画素回路を示す。

【0370】

この画素回路は、一つの画素に複数の画素電極を有する構成に適用できる。それぞれの画素電極は異なるトランジスタに接続され、各トランジスタは異なるゲート信号で駆動できるように構成されている。これにより、マルチドメイン設計された画素の個々の画素電極に印加する信号を、独立して制御できる。

【0371】

トランジスタ 716 のゲート配線 712 と、トランジスタ 717 のゲート配線 713 には、異なるゲート信号を与えることができるよう分離されている。一方、データ線として機能するソース電極又はドレイン電極 714 は、トランジスタ 716 とトランジスタ 717 で共通に用いられている。トランジスタ 716 とトランジスタ 717 は上記実施の形態で説明するトランジスタを適宜用いることができる。これにより、信頼性の高い液晶表示パネルを提供することができる。

【0372】

トランジスタ 716 と電気的に接続する第 1 の画素電極と、トランジスタ 717 と電気的に接続する第 2 の画素電極形状について説明する。第 1 の画素電極と第 2 の画素電極の形状は、スリットによって分離されている。第 1 の画素電極は V 字型に広がる形状を有し、第 2 の画素電極は第 1 の画素電極の外側を囲むように形成される。

【0373】