(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3752943号

(P3752943)

(45) 発行日 平成18年3月8日(2006.3.8)

(24) 登録日 平成17年12月22日(2005.12.22)

(51) Int.C1.

F 1

HO3K 17/16 (2006.01)

HO3K 17/695 (2006.01)HO3K 17/16

HO3K 17/687H

B

請求項の数 6 (全 15 頁)

(21) 出願番号 特願2000-27319 (P2000-27319)

(22) 出願日 平成12年1月31日 (2000.1.31)

(65) 公開番号 特開2001-217697 (P2001-217697A)

(43) 公開日 平成13年8月10日 (2001.8.10)

審査請求日 平成13年12月13日 (2001.12.13)

(73) 特許権者 000005108

株式会社日立製作所

東京都千代田区丸の内一丁目6番6号

(74) 代理人 100075096

弁理士 作田 康夫

(72) 発明者 宮崎 英樹

茨城県日立市大みか町七丁目1番1号

株式会社 日立製作所 日立

研究所内

(72) 発明者 鈴木 勝徳

茨城県日立市大みか町七丁目1番1号

株式会社 日立製作所 日立

研究所内

最終頁に続く

(54) 【発明の名称】半導体素子の駆動装置及びその制御方法

## (57) 【特許請求の範囲】

## 【請求項1】

主電流が入出力する第1端子及び第2端子と制御ゲート端子とを有する半導体素子と、

入力信号に応じて前記制御ゲート端子に制御電源から供給される制御電圧を印加または除去することにより前記主電流を通流または遮断する駆動回路手段とを備えた半導体素子の駆動装置であって、

前記駆動回路手段は、第1の抵抗可変手段と第2の抵抗可変手段とを有し、

前記第1の抵抗可変手段は、前記制御ゲート端子のゲート電圧に応じて抵抗値が変化する第1の抵抗手段と、前記入力信号に応じて該第1の抵抗手段に流れる電流を通流または遮断するスイッチ手段とを有し、

前記第2の抵抗可変手段は、前記第1端子と前記第2端子との間の電圧に応じて抵抗値が変化する第2の抵抗手段を有し、

前記駆動回路手段は、前記主電流の遮断時において、前記制御電源の正極と負極との間の電圧を前記第1の抵抗手段と前記第2の抵抗手段とで分圧した電圧を前記制御ゲート端子に印加することを特徴とする半導体素子の駆動装置。

## 【請求項2】

請求項1において、

前記第1の抵抗可変手段は、さらに、前記制御ゲート端子と前記第2端子との間の電圧を検出する第1の電圧検出手段を有し、

前記第1の電圧検出手段の出力に応じて前記第1の抵抗手段の抵抗値が変化することを

特徴とする半導体素子の駆動装置。

【請求項 3】

請求項 1 において、

前記第 1 の抵抗手段は、前記制御ゲート端子と前記第 2 端子との間に接続される抵抗器と、該抵抗器に並列に接続される容量手段とを備えたことを特徴とする半導体素子の駆動装置。

【請求項 4】

請求項 1 から請求項 3 において、

前記第 2 の抵抗可変手段は、さらに、前記第 1 端子と第 2 端子との間の電圧を検出する第 2 の電圧検出手段と、該第 2 の電圧検出手段の出力と予め設定した基準値との差を比較する增幅手段とを有し、

前記增幅手段の出力に応じて前記第 2 の抵抗手段の抵抗値が変化することを特徴とする半導体素子の駆動装置。

【請求項 5】

請求項 1 において、

前記第 1 の抵抗手段は、前記制御ゲート端子と前記第 2 端子との間に接続されていることを特徴とする半導体素子の駆動装置。

【請求項 6】

主電流が入出力する第 1 端子及び第 2 端子と制御ゲート端子とを有する半導体素子と、

20

入力信号に応じて前記制御ゲート端子に印加される制御電圧を変化させることにより前記

主電流を通流または遮断する駆動回路手段とを備えた半導体素子の駆動装置であって、

前記駆動回路手段は、前記制御ゲート端子のゲート電圧に応じて抵抗値が変化する第 1

の抵抗可変手段と、前記第 1 端子と前記第 2 端子との間の電圧に応じて抵抗値が変化する

第 2 の抵抗可変手段とを有し、

前記駆動回路手段は、前記主電流の遮断時において、前記制御電源の正極と負極との間の電圧を前記第 1 の抵抗可変手段と前記第 2 の抵抗可変手段とで分圧した電圧を前記制御ゲート端子に印加することを特徴とする半導体素子の駆動装置。

【発明の詳細な説明】

【0001】

【発明の属する技術分野】

本発明は半導体素子の駆動装置に係わり、特に半導体素子が電流を通流、遮断する過渡時に発生する過電圧を抑制させる駆動装置とその制御方法に関する。

【0002】

【従来の技術】

電気自動車等、電池を電源とする電力変換システムでは、電池と負荷（モータ等）の間にインバータなどの電力変換装置を備えており、電力変換装置に使用するパワー半導体素子としては、電圧が低い場合はパワー MOSFET、高い場合には IGBT が用いられる。パワー MOSFET や IGBT はいずれも電圧駆動型素子であり、低損失化の要求から一層の低オン抵抗化が望まれる。電圧駆動型のパワー半導体素子はそのオン抵抗が素子の表面付近に形成されゲート電圧に応じて電流を制限するチャネル部の抵抗と、素子のオフ時に空乏層を形成する半導体基板部の抵抗の和で決まる。チャネル部の抵抗は微細化で減少するが、基板部の抵抗は素子の耐電圧で決まり、オフ時に素子に印加される電圧を低減しない限り抵抗を下げるることはできない。一方、電源の電圧を下げるパワー半導体素子の電圧を低減しようとしても、負荷への電力供給が一定であれば逆に素子に流れる電流が増加する。この場合、大電流を高速に遮断する為、サージ電圧（或いはスパイク電圧と呼ぶ）が増大する結果を招く。そこで、過渡的なサージ電圧をスナバ回路やゲート駆動回路等の回路的な対策で抑制し、持続的に印加される電源電圧は電源電圧を下げることで素子の耐電圧を低減することが考えられる。

【0003】

素子がターンオン或いはターンオフする際に発生するサージ電圧を抑制する回路手法の一

10

20

30

40

50

例として特開平6-291631号公報に開示される駆動回路がある。この回路は電圧駆動型パワー半導体素子の入力 - 出力端子間の電圧を検出し、この検出値に応じてゲート抵抗を変化させ、素子のゲート電圧が増加或いは減少する速度を遅くする。電圧駆動型のパワー半導体素子はゲート電圧により通流可能な電流を制限する飽和特性を持ち、ゲート電圧の増加或いは減少を抑制すれば電流のスイッチング速度もまた緩和される。素子の各端子間には寄生容量を有するが、特に入力端子とゲート端子間の帰還容量は過渡時において、ゲート電流により充電或いは放電の時間が制限される為、前述の従来技術はこの性質を利用してスイッチング時の電圧変化 ( $dV/dt$ ) も緩和している。このようにして電流変化 ( $di/dt$ )、或いは電圧変化 ( $dV/dt$ ) が緩和されると、 $di/dt$ ,  $dV/dt$  が招くサージ電圧も低減する。特開平6-291631号公報には入力 - 出力端子間の電圧と共にゲート電圧を検出し、この検出結果に応じてゲート抵抗を変化させる手段も記載されている。本従来技術に関連した論文が平成7年電気学会産業応用部門全国大会論文誌No.88「IGBT駆動用ソフトスイッチングゲート駆動回路の検討」に記載されている。本論文に記載された駆動回路は、ターンオフ時にまず、スイッチング素子の入力 - 出力端子間の電圧を検出し、ゲート抵抗を小から大へと変化させる。続いてゲート電圧を検出しゲート抵抗を大から小へと変化させる。この駆動回路によりスイッチング時のサージ電圧は抑制されたが、オン及びオフ時に電圧と電流波形がオーバーラップする期間が長くなり、従来のゲート駆動回路を使用した場合に比べてスイッチング損失が大幅に増加することが報告されている。

#### 【0004】

10

##### 【発明が解決しようとする課題】

前述の従来技術の問題点を説明するため、電圧駆動型パワー半導体素子のターンオフ動作を次の4つの期間に分ける。尚、ここではモータなど誘導性の負荷を対象にしている。

1 ゲート電圧放電期間；オフ信号の印加により抵抗を介してゲート電流が流れ、ゲートに蓄積した電荷を放電する期間である。ゲート電圧はゲート容量と抵抗の積を時定数とする指數関数に従って時間と共に減少する。この期間中の入力 - 出力端子間の主電流及び電圧はオン時の値を維持している。

2 電圧上昇期間；素子は飽和動作に入り、ゲート電流によって帰還容量が充電され、この充電程度に応じて入力 - 出力端子間の電圧が増加する期間である。ゲート電流は帰還容量の充電に使われる為、この期間中にゲート電圧はほぼ一定の値となる。帰還容量は電圧依存性を持ち、入力 - 出力端子間の電圧に応じて減少する為、入力 - 出力端子間の電圧増加は途中から速くなる。

3 電流下降期間；入力 - 出力端子間の電圧が電源電圧に到達した時点から主電流が減少を始める。主電流が減少し始めてから完全にゼロになるまでの期間を電流下降期間と呼ぶ。帰還容量充電期間の終了時点からゲート電圧は再び減少し、主電流はこのゲート電圧の瞬時値に応じて減少する。

4 オフ定期間；ゲート電圧はしきい値以下まで減少し、パワー半導体素子が電流を遮断する状態に維持されている期間である。

#### 【0005】

30

前述の従来技術の場合は、ゲート電圧放電期間はゲート抵抗値を小さくし、電圧上昇期間の途中で入力 - 出力端子間の電圧が増加したことを検出しゲート抵抗値を増加させる。そして電圧上昇期間と電流下降期間にはゲート抵抗値を大きい値に維持させる。次にゲート電圧を検出してこの値がしきい値以下になったことでオフの定期間に入ったことを検知し、ゲート抵抗を再び小さい値にする。

#### 【0006】

40

一般的なゲート駆動回路では、ゲート電圧放電期間の開始からオフ定期間の終了までゲート抵抗は小さく一定値であり、電圧上昇期間及び電流下降期間はそれぞれ数十から百  $n$  s 程度と短い。一方、前記従来技術で電圧上昇期間にゲート抵抗値が小から大へと変化すると、電圧上昇期間及び電流下降期間はそれぞれ約 1 ~ 数  $\mu$  s 程度に伸びる。しかしながら、検出或いは動作上の時間遅延があると、ゲート抵抗を小から大へ増加させる動作が間

50

に合わなくなる。この場合、ゲート抵抗が小さい状態で電流を遮断する為、電流変化 ( $d i / d t$ ) によりサージ電圧が発生する。このようにサージ電圧が抑制できない事態もあることが第一の問題点である。

【0007】

第二の問題は遅延時間の増加である。PWM (パルス幅変調) 制御方式のインバータで搬送波の周波数を数 kHz とすれば、インバータ上下素子の非ラップ時間は一般的に  $5 \mu s$  が上限であり、上記のように電圧上昇期間だけで  $3 \sim 5 \mu s$  になってしまふと PWM 制御には適さなくなる。

【0008】

また、ゲート抵抗値の増加により電圧上昇期間から電流下降期間におけるスイッチング損失は増加するが、サージ電圧を抑制しつつ同時にスイッチング損失をできる限り小さくすることが第3の問題である。

【0009】

更に誘導性負荷に対してはパワー半導体素子の入出力端子間に還流用のダイオードを設けるが、このダイオードが逆回復する際のサージ電圧を抑制することは困難であった。

【0010】

【課題を解決するための手段】

本発明は上記の問題点を考慮してなされたものである。

【0011】

本発明による駆動装置の代表的な一つは、主電流が入出力する第1端子及び第2端子と制御ゲート端子とを有する半導体素子と、入力信号に応じて制御ゲート端子に印加される制御電圧を変化させることにより主電流を通流または遮断する駆動回路手段とを備えた半導体素子の駆動装置であって、駆動回路手段は、制御ゲート端子のゲート電圧に応じて抵抗値が変化する第1の抵抗可変手段と、第1端子と第2端子との間の電圧に応じて抵抗値が変化する第2の抵抗可変手段とを有し、駆動回路手段は、主電流の遮断時において、制御電源の正極と負極との間の電圧を第1の抵抗可変手段と第2の抵抗可変手段とで分圧した電圧を制御ゲート端子に印加する。

【0012】

また、本発明による駆動装置の他の代表的な一つは、主電流が入出力する第1端子及び第2端子と制御ゲート端子とを有する半導体素子と、入力信号に応じて制御ゲート端子に制御電源から供給される制御電圧を印加または除去することにより主電流を通流または遮断する駆動回路手段とを備えた半導体素子の駆動装置であって、駆動回路手段は、第1の抵抗可変手段と第2の抵抗可変手段とを有し、第1の抵抗可変手段は、制御ゲート端子のゲート電圧に応じて抵抗値が変化する第1の抵抗手段と、入力信号に応じて該第1の抵抗手段に流れる電流を通流または遮断するスイッチ手段とを有し、第2の抵抗可変手段は、第1端子と第2端子との間の電圧に応じて抵抗値が変化する第2の抵抗手段を有し、駆動回路手段は、主電流の遮断時において、制御電源の正極と負極との間の電圧を第1の抵抗手段と第2の抵抗手段とで分圧した電圧を制御ゲート端子に印加する。

【0013】

より望ましくは、第1の抵抗可変手段は、さらに、制御ゲート端子と第2端子との間の電圧を検出する第1の電圧検出手段を有し、第1の電圧検出手段の出力に応じて第1の抵抗手段の抵抗値が変化するものである。

【0014】

また、より望ましくは、第2の抵抗可変手段は、さらに、第1端子と第2端子との間の電圧を検出する第2の電圧検出手段と、第2の電圧検出手段の出力と予め設定した基準値との差を比較する增幅手段とを有し、增幅手段の出力に応じて第2の抵抗手段の抵抗値が変化するものである。

【0018】

【発明の実施の形態】

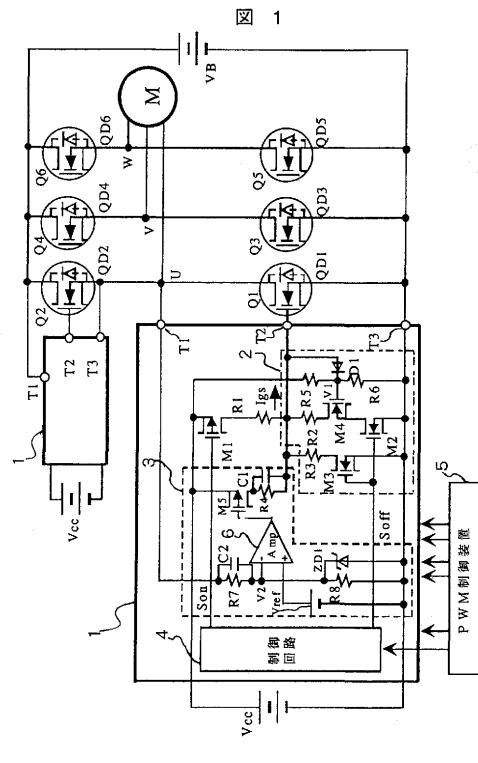

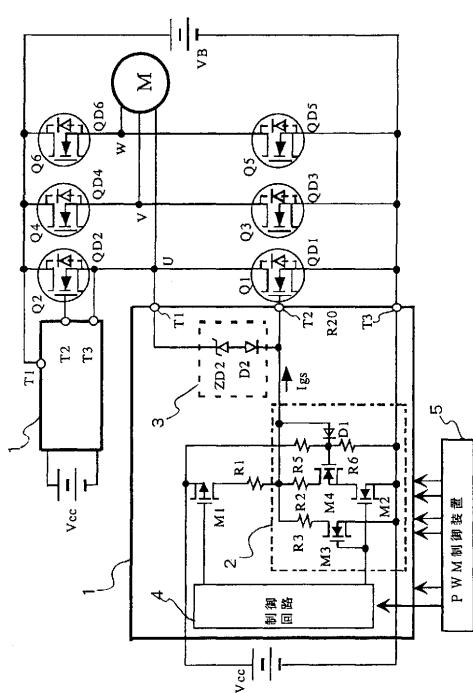

以下、本発明の第1実施例として図1から図3を参照して説明する。図1は本発明の駆動

10

20

30

40

50

装置を備えたパワー半導体素子を含む電力変換装置の構成を表している。主回路は電源 V B の正極と負極間にパワーMOSFET (例 Q 1) とその内蔵ダイオード (例 QD 1) からなるパワー半導体素子 6 ケを 3 相ブリッジに接続し、一般的な 3 相インバータの構成となっている。各相の出力端子は U, V, W でありモータ M に接続している。パワーMOSFET Q 1 ~ Q 6 にはそれぞれ駆動装置 1 を備えている。駆動装置 1 の内部構成として、制御電源 Vcc の正極と Q 1 のゲート端子間に P チャンネルMOSFET M 1 及び抵抗 R 1 を直列に接続したゲート充電手段を備える。PWM 制御装置 5 から駆動装置 1 に備えた制御回路 4 に駆動信号が送られ、制御回路 4 は Q 1 に対するオン信号 Son とオフ信号 S off を作成する。オン信号 Son が M 1 のゲート端子に与えられると M 1 がオンし、R 1 を介して Q 1 にゲート電流を供給し、Q 1 のゲート・ソース端子間の入力容量 Cgs を充電する。鎖線で囲んだ領域 2 が第 1 の抵抗可変手段であり、抵抗 R 2、N チャンネルMOSFET M 4 及び M 2 を直列に接続した第 1 のゲート放電回路を Q 1 のゲートとソース端子間に並列に備え、この第 1 のゲート放電回路に並列に抵抗 R 3、N チャンネルMOSFET M 3 を直列に接続した第 2 のゲート放電回路を備える。ここで、M 2 と M 3 はゲート端子が共通接続であり、ゲート端子に制御回路 4 から伝達されるオフ信号 S off が与えられるとオン状態となる。また第 1 の抵抗可変手段 2 の内部には、制御電源 Vcc の正極と負極間に抵抗 R 5 と R 6 を直列に接続し両抵抗の接続点がカソード、Q 1 のゲート端子がアノードとなる極性に接続されたダイオード D 1 を備える。抵抗 R 5, R 6 及び D 1 で N チャンネルMOSFET M 4 に関するバイアス回路を構成している。このバイアス回路は、Vcc を R 5 と R 6 で分圧した電圧 (V 1 と定義する) と Q 1 のゲート・ソース間電圧 Vgs を比較して大きい方の電圧を M 4 のゲートに印加する。信号 S off が M 2, M 3 に入力されるとこれらの素子はオンするが、S off が印加された直後は、分圧値 V 1 より Q 1 のゲート・ソース間電圧 Vgs が大きく、この値が M 4 のゲートに印加される。Vgs と等しい電圧の供給を得て、M 4 のオン抵抗は小さい値となる。先に定義した第 1 のゲート放電回路 (R 2, M 4, M 2) の合成抵抗を RT 1 とし、第 2 のゲート放電回路 (R 3, M 3) の合成抵抗を RT 2 とすれば、M 4 のゲート電圧がほぼ Vgs の定格値に近い条件では、RT 1 が RT 2 より小さくなるよう選定する。この時の RT 1 / RT 2 の比率は 10 分の 1 以下が望ましい。

#### 【0019】

次に破線で囲んだ領域 3 が第 2 の抵抗可変手段であり、その内部には Vcc の正極と Q 1 のゲート端子間に直列接続した P チャンネルMOSFET M 5 と抵抗 R 4 からなるゲート充電回路を備え、抵抗 R 4 には並列にキャパシタ C 1 を設ける。また Q 1 ノードレイン端子とソース端子間に抵抗 R 7 と R 8 で構成する分圧手段を備え、Q 1 ノードレイン・ソース間電圧 Vds を分圧した値 (V 2) を得る。ここで R 8 には並列にツエナーダイオード Z D 1 を接続し、上記 V 2 の上限値を ZD 1 の降服電圧までとする。また、R 7 には並列にキャパシタ C 2 を接続し、Vds の過渡的な変化に対しても C 2 のインピーダンスと R 8 で分圧値を決め、Vds がその後、定常値に落ち着くと R 7 と R 8 で分圧値 V 2 が決まるようになっている。このようなキャパシタ C 2 の働きをスピードアップコンデンサと呼ぶ。先に述べた R 4 に並列なキャパシタ C 1 もスピードアップコンデンサとして働く。即ち、M 5 がオンした瞬間には C 1 のインピーダンスで抵抗 R 4 オーバーイパスさせている。分圧値 V 2 と基準値 Vref はそれぞれ増幅器 6 の ( - ) 入力端子と ( + ) 入力端子に入力する。増幅器 6 では分圧値 V 2 が基準値 Vref を超えて増加すると出力の電位が下がり、その結果 P チャンネルMOSFET M 5 がオンする。

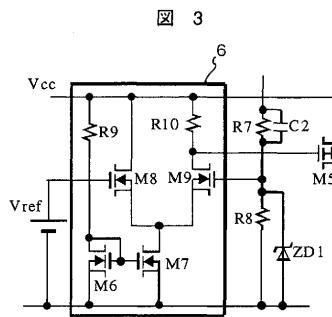

#### 【0020】

増幅器 6 の詳細な構成を図 3 に示す。基本は差動増幅器であり、抵抗 R 9 と N チャンネルMOSFET M 6 と M 7 のカレントミラー回路で定電流源を作っており、差動部を構成する N チャンネルMOSFET M 8 と M 9 の電流合計値は定電流に等しい。一般的な差動増幅器では M 8 ノードレイン端子と M 9 ノードレイン端子はカレントミラー型の負荷が接続されており、増幅器の利得を高くとれるようになっている。一方、図 3 の構成では M 8 ノードレイン側には負荷抵抗がなく、M 9 ノードレイン側にのみ抵抗 R 10 を設けてい

る。前述の定電流をM 8のオン抵抗（基準値 $V_{ref}$ に依存する）とM 9のオン抵抗（基準値 $V_2$ に依存する）にR 10を加算した合成抵抗の2つで分流する形となり利得が小さく、M 5のゲート電圧は分圧値 $V_2$ と基準値 $V_{ref}$ の差電圧に応じて線形的に増加する特性にしている。図1の実施例は後述するように、制御電圧 $V_{cc}$ を第1抵抗可変手段と第2抵抗可変手段で分圧してQ 1のゲート端子に印加し、Q 1のゲート電圧 $V_{gs}$ の時間的な変化を抑制することでスイッチング時のサージ電圧を抑制する。この場合に第1抵抗可変手段或いは第2抵抗可変手段の利得（ $V_{gs}$ 或いは $V_{ds}$ の検出値に対する抵抗の変化率）が高すぎると、Q 1の電圧 $V_{ds}$ 及び $V_{gs}$ が振動的になる。そこで、これらの利得は適度に小さいことが望ましく、図3はその一例である。

## 【0021】

10

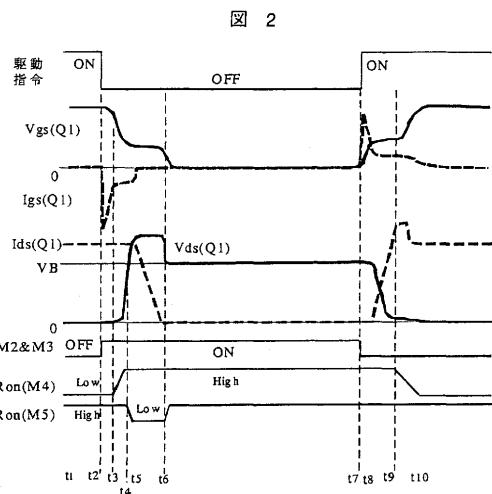

次に図1及び図3の実施例によるサージ電圧抑制効果を図2の動作波形を用いて説明する。

## 【0022】

図2はQ 1への駆動指令に対するQ 1のゲート・ソース間電圧 $V_{gs}$ （Q 1）、ゲート電流 $I_{gs}$ （Q 1）、ドレイン・ソース間電圧 $V_{ds}$ （Q 1）、ドレイン電流 $I_{ds}$ （Q 1）の各波形と、M 2及びM 3のオン、オフ動作、並びにM 4のオン抵抗 $R_{on}$ （M 4）、M 5のオン抵抗 $R_{on}$ （M 5）の時間的变化を表わしている。時刻 $t_1$ から $t_2$ まではQ 1はオン状態にあり、 $t_2$ 以降 $t_7$ までがオフ動作である。時刻 $t_2$ において図示していないがM 1がオフし、図2のようにM 2とM 3がオンする。ここで $t_2$ 以前のオン状態では $V_{gs}$ （Q 1）は制御電圧 $V_{cc}$ とほぼ等しい電圧値まで充電されており、M 2がオンするとM 4のゲート・ソース間には $V_{gs}$ （Q 1）とほぼ等しいゲート電圧が印加される。この結果、M 4のオン抵抗 $R_{on}$ （M 4）は非常に小さい値まで減少する。抵抗 $R_2$ と $R_{on}$ （M 4）及びM 2のオン抵抗の和は抵抗 $R_3$ とM 3のオン抵抗の和に比べて前述のように1/10以下であると仮定すると、抵抗 $R_2$ と $R_{on}$ （M 4）及びM 2のオン抵抗の和がゲート電圧の放電抵抗となり、Q 1のゲート・ソース間に蓄積した電荷は急速に放電される。これが $t_2$ ～ $t_3$ の期間であり、前述のゲート電圧放電期間に相当する。この時、Q 1のゲート電流 $I_{gs}$ （Q 1）はターンオフ動作中、最大の電流値になる。

20

## 【0023】

30

次に $t_3$ 以降になるとQ 1のゲート電圧 $V_{gs}$ （Q 1）が減少した結果、M 4のゲート電圧も減少しそのオン抵抗 $R_{on}$ （M 4）は $V_{gs}$ （Q 1）の減少に依存して高くなる。図2には図示していないが、図1中の電圧 $V_1$ が低下するためである。また、 $R_{on}$ （M 4）の増加に伴い $I_{gs}$ （Q 1）は低下する。この状態が $t_3$ ～ $t_4$ の期間に継続され、途中、帰還容量が $I_{gs}$ （Q 1）により充電され、ドレイン・ソース間電圧 $V_{ds}$ （Q 1）が増加する。これが電圧上昇期間に相当する。 $V_{gs}$ （Q 1）が或る電圧（例えば制御電圧 $V_{cc}$ の1/2から1/3以下）より小さくなると $R_{on}$ （M 4）の増加も著しくなり、抵抗 $R_2$ と $R_{on}$ （M 4）及びM 2のオン抵抗の和は抵抗 $R_3$ とM 3のオン抵抗の和に対し10倍以上に増加するようM 4の電流特性を選ぶ。この結果、 $t_3$ の期間途中からQ 1のゲート・ソース間抵抗はほぼ抵抗 $R_3$ とM 3のオン抵抗の和に等しくなり、更に、M 3のオン抵抗は $R_3$ の抵抗値に比べて十分小さく選ぶことから、Q 1のゲート・ソース間抵抗としては抵抗 $R_3$ のみを考慮すれば良い。尚、ドレイン・ソース間電圧 $V_{ds}$ （Q 1）の時間変化（d $V/dt$ ）は $R_{on}$ （M 4）の増加に伴い小さくなる。

40

## 【0024】

電圧上昇期間の途中で $V_{ds}$ （Q 1）をR 7とR 8で分圧した値 $V_2$ が基準値 $V_{ref}$ 以上になると、增幅器6によって $(V_2 - V_{ref})$ の差電圧に応じた出力電圧がM 5のゲート電圧として印加されM 5がオンする。M 5がオンした時刻を $t_4$ とする。図2では分圧値 $V_2$ と基準値 $V_{ref}$ がほぼ等しくなる際の $V_{ds}$ （Q 1）がほぼ主電源の電圧 $V_B$ に等しくなるよう、 $V_{ref}$ の値を選んでいる。ここで、本実施例では $t_3$ ～ $t_4$ の期間中にまず、Q 1のゲート電圧 $V_{gs}$ （Q 1）に応じてM 4のオン抵抗 $R_{on}$ （M 4）が増加するが、この効果としてQ 1のゲート放電抵抗値が増加し、Q 1の帰還容量の充電電流（ $I_{gs}$ （Q 1））が減り、帰還容量の充電は遅くなる。これはドレイン・ソース間電圧 $V_{ds}$ （Q 1）の電圧

50

上昇も遅くなることを意味しており、前述の公知例のように電圧上昇が速すぎて  $V_{ds}(Q1)$  の検出に遅延が生じることを防いでいる。またスピードアップコンデンサ  $C2$  の効果で分圧電圧  $V2$  の増加も速くなっている、これも  $V_{ds}(Q1)$  の検出遅延の短縮化に寄与している。更に、 $M5$  がオンした直後、スピードアップコンデンサ  $C1$  によって  $M5$  の直列インピーダンスが一瞬小さくなるが、これも抵抗可変手段の動作遅延を短縮化させる効果がある。

#### 【0025】

$t_4 \sim t_6$  までの期間は第1の抵抗可変手段2と第2の抵抗可変手段3がいずれも動作している。第1の抵抗可変手段は  $Q1$  のゲート・ソース間に抵抗  $R2$  と  $R_{on}(M4)$  及び  $M2$  のオン抵抗の和と抵抗  $R3$  と  $M3$  のオン抵抗の和をそれぞれ、並列に合成した値  $R_T1$  を有し、一方の第2の抵抗可変手段は抵抗  $R4$  と  $R_{on}(M5)$  の和で決まる値  $R_T2$  を有するため、 $Q1$  のゲート電圧は制御電源  $V_{cc}$  を  $R_T1$  と  $R_T2$  で分圧した値になる。この値を  $V_o$  と仮定すると、 $t_5 \sim t_6$  の電流下降期間において電流変化 ( $di/dt$ ) がサージ電圧を発生させようとしても、 $V_{ds}(Q1)$  の増加に対し増幅器の働きで  $R_{on}(M5)$  が更に減少して、 $V_o$  を増加させる動作が働く。 $V_o$  が増加すると  $Q1$  の過渡的なインピーダンスが低くなり、電流遮断が抑制される傾向に働く。このようにして、第1の抵抗可変手段と第2の抵抗可変手段の分圧とはゲート電圧  $V_{gs}(Q1)$  とドレイン電圧  $V_{ds}(Q1)$  をそれぞれ検出し、 $V_{gs}(Q1)$  が安定な値  $V_o$  になるようフィードバック制御させる効果を持つ。この効果により電流変化 ( $di/dt$ ) は抑制され、サージ電圧は最小限に抑えられる。図1には図示していないが、主電源  $V_B$  から  $Q1$  に電流を供給する配線の寄生インダクタンスを  $L_s$ 、 $Q1$  が遮断する主電流の瞬時値を  $I$ 、サージ電圧を含む  $V_{gs}(Q1)$  の最大値を  $V_c$  とすれば、 $Q1$  が電流  $I$  を遮断するために要する時間  $t_f$  は

$$L_s \cdot di/dt = V_c - V_B \quad (1)$$

の関係があり、また、 $di/dt$  を線形近似すると

$$t_f = L_s \times I / (V_c - V_B) \quad (2)$$

で表わすことができる。この  $t_f$  が  $t_5 \sim t_6$  の間に等しく、この時間にはドレイン電圧  $V_{ds}(Q1)$  とドレイン電流  $I_{ds}(Q1)$  の重なりが生じターンオフ損失となるが、その値は配線の寄生インダクタンス  $L_s$  に貯えられた電磁エネルギーに等しい。この電磁エネルギーはターンオフ時に必ず発生することから、ターンオフ損失も必要最小限に抑制されていると言える。

#### 【0026】

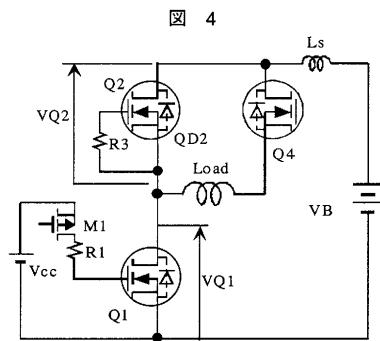

図2で時刻  $t_7$  以降はターンオン動作であるが、図1の実施例は  $Q1$  のターンオン時には特別な働きはせず、従来の駆動装置と同様に  $M1$  のオンにより抵抗  $R1$  を介して  $Q1$  のゲート・ソース間に電流を供給し、ゲート電圧を増加させる。この時、 $Q2$  に並列に設けられた還流ダイオード  $QD2$  が逆回復するが、このダイオードの逆回復時に発生するサージ電圧も本発明の駆動装置1で抑制することが可能である。この説明は図4と図5を用いて詳細に述べる。

#### 【0027】

図4はダイオード  $QD2$  が逆回復する際の状態を説明する図である。図4に記載した回路部品で図1と同一のものには同じ記号を記載しており、説明は省略する。図1と異なる点として、3相インバータの各パワー半導体素子を  $Q1$ 、 $Q2$ 、及び  $Q4$  の3つしか記載していないが、これは  $QD2$  の動作を説明する為に必要な素子のみを記載し残りを省略しただけであり、正確な構成は図1と同じである。図4で  $Q2$  のゲート・ソース間に抵抗  $R3$  しか接続していないが、実際の構成は図1の  $Q1$  に対する駆動装置1と同じである。図4で  $Q2$  がオフ、 $QD2$  に電流が流れている還流状態を想定すると、 $Q2$  のゲート・ソース間電圧はほぼ零であることから図1で述べた  $M4$  はそのオン抵抗が高抵抗状態にある。また、前述のように  $M3$  のオン抵抗を  $R3$  の抵抗値に比べて十分小さく選んでいる為、 $QD2$  が還流状態にある場合の  $Q2$  のゲート・ソース間抵抗としては抵抗  $R3$  のみを考慮すれば良い。尚図4で新規に記載した部品として  $L_s$  があるが、 $L_s$  は  $Q2$  のゲート主電源  $V_B$  の正極と  $Q2$  及び  $Q4$  ノードレイン端子をつなぐ配線の寄生インダクタンスである。

10

20

20

30

40

50

また負荷は図1ではモータMであったが、図4では誘導性負荷として記載している。

【0028】

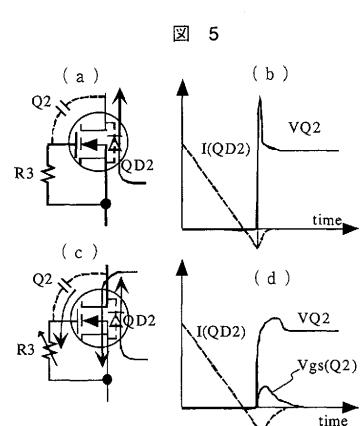

図5にはダイオードQD2が逆回復する際の動作説明と、動作波形をそれぞれ示す。まず、図5(a)は従来の駆動装置を用いた場合である。図5(a)の抵抗R3は本発明のR3に比べて抵抗値が1/10以下とする。従来の駆動装置では図2に示したt2期間のターンオフ開始からt7期間のオフ定常の終了までゲート抵抗が変化せず、一般的にオフゲート抵抗はt2~t3期間に大きなゲート電流を流すことを目的に選定されるが、図5(b)に従来の駆動装置における動作波形を示すが、還流電流I(QD2)はQD2のアノードからカソードに向かう極性を正として表示している。図5(b)でI(QD2)が減少し、やがて零以下になるがQD2に蓄積された電子とホールを全て排出するまでは逆極性の電流が流れる。これが逆回復と呼ばれる現象である。逆回復電流はピークに達した時点以降減少し始め、QD2にはカソードを正とする逆電圧(図中のVQ2)が印加される。この逆電圧は図5(b)に示したように電圧変化(dV/dt)が大きく、かつスパイク電圧が重畠する。このスパイク電圧は寄生インダクタンスLsと逆回復電流が減少する際の電流変化(dI/dt)により発生する。このように(dV/dt)が大きく、かつスパイク電圧が重畠した電圧VQ2によりQ2ノードレイン・ゲート間帰還容量を充電する電流が流れ、この充電電流はR3を介してQ2のソースへと向かう。従来の駆動装置では抵抗R3が小さいが、帰還容量の充電電流がR3で発生させる電圧降下は小さく、一般的にこの電圧降下はQ2のゲートしきい値電圧以下になるよう抵抗R3の値を選定していた。

10

【0029】

図5(c)には本発明の駆動装置を用いた場合の動作を示す。QD2が逆回復し電圧変化(dV/dt)の大きい電圧VQ2が発生するまでの現象は従来の場合と同じである。ここで、電圧VQ2によりQ2の帰還容量を充電する電流が流れ、この充電電流がR3に電圧降下を発生させる場合、本発明では抵抗R3が従来に比べ10倍以上大きいが、Q2のゲート・ソース間には図5(d)に示すような電圧が生じる。この電圧のピーク値はQ2のゲートしきい値電圧よりわずかに大きくなるようにR3の値を決めておく。この結果、MOSFETQ2は一瞬、オンして図5(c)に示すようなドレインからソースに向かう電流が流れる。オンしたMOSFETQ2はゲート電圧が十分大きくなっているが、その抵抗は図2のt1~t2期間と比べて大きいが、図5(a)の従来でオフ状態にある場合に比べるとはるかに小さい値になる。そして、QD2の逆回復電流に加えてQ2の電流が流れることで、図5(d)の電流I(QD2)は図5(b)に比べて導通期間が長く、かつ電流変化(dI/dt)は小さくなっている。このようにして(dI/dt)が小さくなると、図5(b)のようなスパイク電圧は発生せず、寄生インダクタンスLsに蓄積した電磁エネルギーは電圧VQ2とI(QD2)の積で決まる損失によって消費される。本発明は従来の駆動装置では避けていたMOSFETQ2のdV/dt誤点弧を発生させ、これを用いてスパイク電圧を抑制させている。逆回復時の電圧変化(dV/dt)により流れるMOSFETQ2の電流は従来の駆動装置を用いた場合に比べてスイッチング損失を増加させる欠点もあるが、R3の抵抗値を最適に選定すればQ2が導通したことで発生する損失の増加を最小限に抑えることも可能である。また、本発明のようにスパイク電圧を抑制すれば素子Q2の耐圧を従来より小さくできるが、Q2のオン抵抗を低減することができる。本発明によれば、スイッチング損失は増加するものの、素子の耐圧を低減することでオン抵抗を減少させ定常損失を低減することができる。定常損失の低減がスイッチング損失の増加に比べて大きければ、全体としては低損失化の効果になる。

30

40

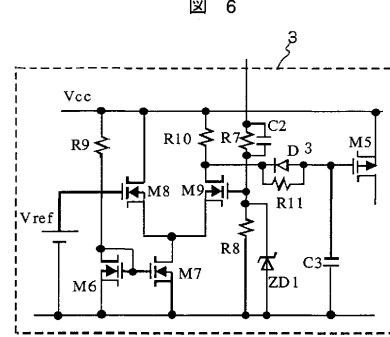

【0030】

図6は図1に示した第2の抵抗可変手段3に関する第2の実施例である。図1の構成と異なる点は図1が増幅器の出力を直接M5のゲートに印加しているのに対して、図6ではダイオードD3とこれに並列な抵抗R11、及びD3のアノード端子とVccの負極間に設けたキャパシタC3で構成される遅延手段を介してM5のゲートに印加することである。この遅延手段の効果でM5のゲート電位が下がる場合はC3の電圧が抵抗の小さいD3を介

50

して放電され、その時間遅延はわずかである。一方、M 5 のゲート電位が上がる場合はC 3 の電圧が抵抗の大きいR 1 1 を介して充電され、R 1 1 とC 3 の時定数により時間遅延が発生する。この遅延手段によれば、図2の時刻t 6においてV<sub>ds</sub>(Q 1)が減少した際にもM 5 が急に流していた電流を遮断するのではなく、ゆっくりと遮断に向かう。これは時刻t 6直後のゲート電圧V<sub>gs</sub>(Q 1)がゆっくりと減少する効果をモータらし、V<sub>ds</sub>(Q 1)の波形振動を抑制することができる。遅延手段にもうけた抵抗R 1 1 とキャパシタC 3 で決まる時定数は、Q 1ノードレイン・ソース間寄生容量(C<sub>oss</sub>)と図4に記載したように配線の寄生インダクタンスL<sub>s</sub>で決まる共振周期に対して約5～10倍程度長くなるように選定すればV<sub>ds</sub>(Q 1)が時刻t 6以降で振動することを防止することができる。

10

### 【0031】

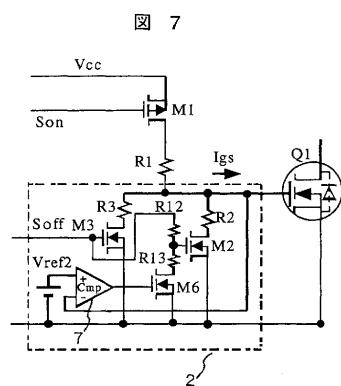

図7は図1に示した第1の抵抗可変手段2に関する第2の実施例である。図7が図1と異なる点は、まず抵抗R 2とnチャンネルMOSFET M 2をQ 1のゲート・ソース間に並列に接続し、制御信号S<sub>off</sub>を抵抗R 1 2, R 1 3、及びMOSFET M 6からなる直列接続に供給する。R 1 2とR 1 3の接続箇所からM 2にゲート信号を供給する。M 6はQ 1のゲート・ソース間電圧V<sub>gs</sub>(Q 1)と基準電圧V<sub>ref</sub>2を比較し、ゲート電圧V<sub>gs</sub>(Q 1)が基準電圧V<sub>ref</sub>2より高い場合はM 6はオフ、低くなるとM 6がオンするよう比較器7から信号を出力する。即ち、V<sub>gs</sub>(Q 1)がV<sub>ref</sub>2より高い場合はM 6がオフしている為、M 2には抵抗R 1 2を介して制御信号S<sub>off</sub>の電圧がそのまま印加される。この場合、抵抗R 2とR 3が並列になるが、図1と同様にR 2はR 3に比べ1/10以下に選び、合成抵抗がほぼR 2だけになるようにする。Q 1のゲート電圧V<sub>gs</sub>(Q 1)はこの合成抵抗によって急速に放電される。

20

### 【0032】

次に、V<sub>gs</sub>(Q 1)がV<sub>ref</sub>2より低くなるとM 6がオンしている為、制御信号S<sub>off</sub>をR 1 2とR 1 3で分圧した電圧がM 2のゲート電圧として印加される。ゲート電圧がR 1 2とR 1 3の分圧により減少すると、M 2のオン抵抗は高くなる。M 2のオン抵抗が増加し、その値が抵抗R 3に比べてはるかに大きくなるようM 2の電流特性を選んでおくと、Q 1のゲート・ソース間に接続された合成抵抗はほぼR 3に等しい値になる。この結果、Q 1のゲート電圧V<sub>gs</sub>(Q 1)は増加した合成抵抗によってゆっくりと放電され、図1及び図2で述べた動作と同じようになる。図1と図7を比較すると、図1の場合のM 2とM 4はターンオフ初期に大きなゲート電流を流す為、電流定格の大きなMOSFETが必要である。図7のM 2も同様に定格の大きなMOSFETが必要であるが、M 6はR 1 2とR 1 3で電流を制限する為、M 2に比べると小さな電流定格で良い。使用するMOSFETの電流定格を下げることができれば低コスト化につながり、特に駆動装置を集積回路化する場合には低コストに効果的である。

30

### 【0033】

図8には本発明の駆動装置に関する第2の実施例を示す。尚、図8に示すインバータ型の電力変換装置は図1と同じであり、駆動装置1の破線で囲んだ第2の抵抗可変手段3だけが異なっている。図8における第2の抵抗可変手段3は、Q 1のパワーMOSFETを例にすると、Q 1ノードレイン端子とゲート端子間にツエナーダイオードZD 2とダイオードD 2からなる直列接続を備える。本発明では、Q 1ノードレイン・ソース間電圧V<sub>ds</sub>(Q 1)を上記ZD 2とD 2からなる直列接続と第1の抵抗可変手段2で分圧し、この分圧した電圧をQ 1のゲート電圧として印加させることが特徴である。パワー半導体素子の過電圧保護用として図8と同様にドレイン端子とゲート端子間にツエナーダイオードを備えた例はこれまでにもあるが、スイッチング時に発生するサージ電圧を抑制する目的でこの方法を用いると、毎回のスイッチングでツエナーダイオードが降服し電流が流れる為、ツエナーダイオードの損失が問題になる。本発明はツエナーダイオードと抵抗可変手段を併用することでサージ電圧を抑制すると共に、ツエナーダイオードの損失を低減することが狙いである。

40

### 【0034】

50

尚、ツエナーダイオードZD2の降服電圧は、主電源の電圧VBに等しい特性を選ぶことが損失及び遅延時間の低減の点で望ましい。

#### 【0035】

図9は図8の駆動装置を用いた場合の動作波形であり、時刻t4までの動作は図2と同様である。時刻t4においてQ1ノードレイン・ソース間電圧Vds(Q1)がツエナーダイオードZD2の降服電圧を越えるとZD2に電流が流れ、この電流はR2, M4, M2からなる第1のゲート放電抵抗と、R3とM3からなる第2のゲート放電抵抗に流れる。ここで、第1のゲート放電抵抗にM4が無く、制御信号に応じてオンするM2とR2だけの場合を想定してみる。第2のゲート放電抵抗は設けていても前述のようにR2の値はR3に比べて1/10以下である為、合成したゲート放電抵抗はほぼR2に等しく、小さな値になる。これは従来、過電圧保護用としてツエナーダイオードを備えた例と同じ特性になる。即ち、小抵抗R2がQ1のゲート・ソース間電圧Vgs(Q1)を減少させている状況であり、R2を流れるゲート電流は大きい。ZD2が降服するとZD2の電流はR2に流れ、その電流はR2を通るゲート電流にほぼ等しい値まで増加する。この時、R2が通流可能な電流はQ1のゲート・ソース間電圧Vgs(Q1)をR2で割った値である。ZD2の電流がR2に通流可能な電流値まで増加すると、ゲート電圧Vgs(Q1)はそれ以上は減少せず、電流は緩やかに遮断される。又、電流変化(dI/dt)が小さくなる為、サージ電圧も抑制できる。図8でt5～t6の電流下降期間がこれに相当し、Q1ノードレイン・ソース間電圧Vds(Q1)をZD2とR2で分圧した電圧がQ1のゲート・ソース間電圧Vgs(Q1)として印加されていると言える。一方、R2に通流可能な電流はR2の値が小さいほど大きくなり、ツエナーダイオードにはこの電流と降服電圧の積で決まる損失が発生する。

#### 【0036】

次に本発明による駆動装置の場合は図2で述べたように、時刻t3まではM4のオン抵抗が小さいが、それ以降はQ1のゲート電圧Vgs(Q1)の減少に依存してM4のオン抵抗が増加し、時刻t4ではゲート放電抵抗の合成値はR2に比べて10倍以上、大きいR3になっている。この為、ZD2が降服した際に流れる電流もM4が無い場合に比べて大幅に低減する。従って、Q1のサージ電圧を抑制すると共に、ツエナーダイオードの損失も大幅に低減する事が達成できる。

#### 【0037】

図10は前述のスピードアップコンデンサの原理を用いて第1の抵抗可変手段を達成する実施例である。鎖線2で囲む第1の抵抗可変手段以外の構成は図8と同じであり、その説明は省略する。本実施例における第1の抵抗可変手段はQ1のゲート・ソース間に抵抗R2と駆動信号SoffによりスイッチングするM2を直列に備え、R2には並列にスピードアップコンデンサC4を備える。図9の動作波形に示したt2～t3期間において、Q1のゲート電圧が急峻に変化し大きなゲート電流が流れる場合にはスピードアップコンデンサC4のインピーダンスがR2より小さくなり、ゲート電流を流す。次のt3～t6期間においてQ1のゲート電圧の時間的变化が小さくなると、C4のインピーダンスが高くなりR2がゲート抵抗として働く。そこで、図10においては抵抗R2の値を図8の例に比べて10倍程度大きくしておき、ターンオフ初期のt2～t3期間ではC2を抵抗手段としてゲート電流の放電に使用し、ツエナーダイオードZD2が降服するt4～t6期間ではR2をゲート抵抗として用いれば、図8で述べた原理によってツエナーダイオードの電流を軽減して低損失化を図ることができる。尚、C4の容量はQ1のゲート・ソース間容量と同等な値が望ましい。

#### 【0038】

図1～図10に記載した駆動装置1でキャパシタC1～C4を除くMOSFET、抵抗、ツエナーダイオード、増幅器、比較器はいずれも集積回路(IC)に適した部品であり、これらを1つ或いは複数のICチップで構成しても良い。IC化により回路の動作遅延は大幅に短縮化され、本発明の狙いにとってより適した特性が得られる。

#### 【0039】

10

20

20

30

40

40

50

図11は本発明による駆動装置を備えたインバータ装置に大容量電池から電力を供給する電力変換システムの構成である。

【0040】

図11でパワー半導体素子Q1～Q6で構成される3相インバータと、これに負荷として接続されたモータM、Q1～Q6に具備された図1或いは図8と同じ駆動装置1、及び駆動装置1に電力を供給する制御電源Vcc、駆動装置1にPWM制御信号を伝える制御装置5はいずれも図1或いは図8に記載した内容と同じであり、これらの説明は省略する。Ls1はそれぞれ平滑コンデンサCFと3相インバータを接続する配線の寄生インダクタンス、Ls2も同様に電池VBと平滑コンデンサCFを接続する配線の寄生インダクタンスである。次に電池VBは等価回路的に表現すると、内部抵抗RBと開路電圧VBOで表すことができる。この電池VBを充電、或いは放電する電流を電流センサ8で計測し、電池の状態監視装置9に電流計測結果を逐次、伝えている。また、状態監視装置9は電池VBの電圧も計測しており、計測した電池VBの電流、電圧情報から内部抵抗RBと開路電圧VBOを推定し、制御装置5に伝達する。

【0041】

本発明は電池VBが大電流を通電した場合、その正負極間電圧は内部抵抗RBの影響で真の電圧（開路電圧VBO）より減少或いは増加して現れることから、この原理を前述の駆動装置に関する制御方法として応用することが狙いである。

【0042】

前述の(1)、(2)式で述べたように、平滑コンデンサCF（容量をCfとする）からパワー半導体素子を含む閉回路内に存在する配線の寄生インダクタンスをLs1、Q1～Q6のパワー半導体素子が出力する主電流の瞬時値をI（電池にとっては放電電流）、この電流の実効値をIav、電池の正負極間電圧をVB、開路電圧をVBO、電池の内部抵抗をRB、駆動装置によってサージ電圧を抑制した場合のパワー半導体素子の最大電圧値をVc（図2でt5～t6期間のVds(Q1)に相当する）、パワー半導体素子が電流を遮断する時間をtfとすれば、これらのパラメータには次の関係がある。

電流遮断期間に発生するサージ電圧は

$$Ls1 \times dI / dt = Vc - VB \quad (3)$$

電流遮断時のdI/dtを線形近似すると、

$$dI / dt = I / tf \quad (4)$$

電池の正負極間電圧はパワー半導体素子がオン定常期間中に流した電流の実効値Iavと内部抵抗の影響で減少しており、

$$VB = VBO - RB \times Iav \quad (5)$$

と表すことができる。(3)式のサージ電圧は電流を遮断し始メタ時刻（図2のt5）からLs1に蓄えられた電磁エネルギーが消費されるまで（図2のt6）の期間において、電流がdI/dtの勾配で変化しながらも流れ続けることを意味する。しかしながら、この電流は平滑コンデンサと配線の寄生インダクタ、及びパワー半導体素子の間で流れ、電池から電流を供給するわけではない。そこで、電池は(5)式に記載した内部抵抗と電流による電圧降下分(RB × Iav)が回復してゆく。この回復過程は内部抵抗RBと平滑コンデンサの容量Cfを時定数とする指數関数的な電圧変化となる。一方、パワー半導体素子のサージ電圧を抑制する観点から考えると、RBとCfの時定数は電流下降期間(t5～t6)に対して十分長く、(3)式のVBが低い値に維持されている方が好ましい。

Vcはパワー半導体素子の耐圧に対して80～90%の値に選定すれば、VBが低いほど電流下降期間のdI/dtを大きく選ぶことができ、(4)式のtfが短くなる。これは公知例で問題であった遅延時間を短くしてPWMの非ラップ時間を探るにつながる。Rbを例えば20m、Cfを5000μFと仮定すると、時定数は100μsであり、電流下降時間tfを上記時定数の10%以下に選べば電池電圧の回復に対して十分短く、電池電圧は電流遮断以前の値にほぼ等しい。PWMの非ラップ時間は前述のように上限5μsであり、上記時定数の例に対しては5%に相当し10%以下の条件を満足している。遅延時間の制御は図1の基準値Vref、或いは図8のツエナーダイオードZD2の降

10

20

30

40

50

服電圧を用いて、電流下降期間における電圧のクランプ値  $V_c$  を設定すれば良い。尚、(3)～(5)式は遮断電流の振幅  $I$  に依存しており、上記  $V_c$  の設定には主電流の最大値、或いは熱的には最大主電流に対する実効値を考慮する。

#### 【0043】

また、(3)及び(4)式より時間  $t_f$  は

$$t_f = L \times I / (V_c - V_b + R_B \times I_{av}) \quad (6)$$

と表されることから、制御装置5は電池の状態監視装置9から得る情報に基づき、(6)式の計算を実施し、PWM信号に  $t_f$  より長い非ラップ時間を設けることができる。この制御方法によれば、遮断電流の振幅  $I$  が変化した場合でも正確な電流下降時間  $t_f$  を把握でき、非ラップ時間に反映することができる。

10

#### 【0044】

##### 【発明の効果】

本発明による駆動装置によれば、それぞれ制御電圧と入出力端子間電圧に応じて変化する第1、第2の抵抗可変手段で分圧したゲート電圧をパワー半導体素子に印加することで電流下降期間に生じるサージ電圧を安定に抑制することができる。

#### 【0045】

本発明による制御方法によれば還流ダイオードが逆回復する際に、これに並列なパワー半導体素子を短時間に  $dV/dt$  点弧させ、サージ電圧を抑制することが可能になる。 $dV/dt$  点弧によりスイッチング損失はわずかに増加するが、耐圧を下げることで定常損失を大幅に低減し、全体では低損失化の効果がある。さらに、内部抵抗の影響を考慮して、第2抵抗可変手段の基準値、或いはツエナーダイオードの降服電圧を設定することにより、サージ抑制時の電圧を最適化し電流下降時間を短縮することができる。また、この時間を考慮した PWM 制御の非ラップ時間が設定可能となる。

20

#### 【図面の簡単な説明】

【図1】本発明の第1実施例を示す駆動装置の回路図。

【図2】動作波形図。

【図3】利得を適正化した増幅器の回路図。

【図4】ダイオードが逆回復を説明する回路図。

【図5】ダイオードが逆回復する際の動作説明図。

【図6】遅延手段を設けた増幅器の回路図。

30

【図7】第1の抵抗可変手段に関する第2の実施例。

【図8】本発明の第2実施例を示す駆動装置の回路図。

【図9】動作説明図。

【図10】第1の抵抗可変手段に関する第3の実施例。

【図11】本発明の制御方法を示す電力変換装置のブロック図。

#### 【符号の説明】

1 … 駆動装置、2 … 第1の抵抗可変手段、3 … 第2の抵抗可変手段、4 … 制御回路、5 … PWM制御装置、6 … 増幅器、7 … 比較器、8 … 電流センサ、9 … 電池の状態監視装置、Q1～Q2 … パワー半導体素子、QD1～QD6 … 還流用ダイオード、M1～M9 … MOSFET、R1～R11 … 抵抗、C1～C4 … キャパシタ、ZD1、ZD2 … ツエナーダイオード、D1～D3 … ダイオード、M … モータ、VB … 電源（或いは電池）、Vcc … 制御電源、Vref及びVref2 … 基準値。

40

【図1】

【図2】

【図3】

【図4】

【図6】

【図5】

【図7】

【図 8】

図 8

【図 9】

図 9

【図 10】

図 10

【図 11】

図 11

---

フロントページの続き

(72)発明者 立野 孝治

茨城県日立市大みか町七丁目1番1号 株式会社 日立製作所 日立研究所内

(72)発明者 坂野 順一

茨城県日立市大みか町七丁目1番1号 株式会社 日立製作所 日立研究所内

(72)発明者 岩村 将弘

茨城県日立市大みか町七丁目1番1号 株式会社 日立製作所 日立研究所内

(72)発明者 森 瞳宏

茨城県日立市大みか町七丁目1番1号 株式会社 日立製作所 日立研究所内

審査官 柳下 勝幸

(56)参考文献 特開平10-023743 (JP, A)

特開平06-291631 (JP, A)

特開平11-346147 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H03K 17/00-17/70