(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3872927号

(P3872927)

(45) 発行日 平成19年1月24日(2007.1.24)

(24) 登録日 平成18年10月27日(2006.10.27)

(51) Int.C1.

F 1

H02M 3/07 (2006.01)

H02M 3/07

H03K 5/02 (2006.01)

H03K 5/02

H03K 19/0185 (2006.01)

H03K 19/00 101 E

請求項の数 12 (全 20 頁)

(21) 出願番号

特願2000-80410 (P2000-80410)

(22) 出願日

平成12年3月22日 (2000.3.22)

(65) 公開番号

特開2001-268893 (P2001-268893A)

(43) 公開日

平成13年9月28日 (2001.9.28)

審査請求日

平成16年11月26日 (2004.11.26)

(73) 特許権者 000003078

株式会社東芝

東京都港区芝浦一丁目1番1号

(74) 代理人 100058479

弁理士 鈴江 武彦

(74) 代理人 100084618

弁理士 村松 貞男

(74) 代理人 100092196

弁理士 橋本 良郎

(74) 代理人 100091351

弁理士 河野 哲

(74) 代理人 100088683

弁理士 中村 誠

(74) 代理人 100070437

弁理士 河井 将次

最終頁に続く

(54) 【発明の名称】昇圧回路

## (57) 【特許請求の範囲】

## 【請求項1】

初段の入力端子に電源電位または接地電位が印加され、各々の出力端子が順次次段の入力端子にそれぞれ接続された複数の昇圧ユニットと、

上記昇圧ユニットの最終段の出力電位で制御され、最終段より前の段の昇圧ユニットの出力電位を転送する出力回路部と、

上記出力回路部から出力される正または負の昇圧電位を電源の一方に用いて、上記正または負の昇圧電位と接地電位間の振幅のリセット信号を生成し、上記各昇圧ユニットに供給することにより、各昇圧ユニットにおける電荷が残存するトランジスタのゲートノードをリセットするリセットパルス発生器と、

上記リセットパルス発生器における上記正または負の昇圧電位が印加されるノードを、上記電荷が残存するトランジスタのゲートノードのリセット後にディスチャージするディスチャージ回路と

を具備することを特徴とする昇圧回路。

## 【請求項2】

前記昇圧ユニットは、電流通路の一端が前記入力端子に接続され、電流通路の他端が前記出力端子に接続された第1MOSトランジスタと、電流通路の一端が前記入力端子に接続され、電流通路の他端が上記第1MOSトランジスタのゲートに接続され、ゲートが出力端子に接続された第2MOSトランジスタと、電流通路の一端が上記第1MOSトランジスタのゲートに接続され、電流通路の他端に電源電圧または接地電位が印加され、ゲー

10

20

トに前記リセット信号が供給されるリセット用の第3MOSトランジスタと、電流通路の一端が上記第2MOSトランジスタのゲートに接続され、電流通路の他端に電源電圧または接地電位が印加され、ゲートに前記リセット信号が供給されるリセット用の第4MOSトランジスタと、一方の電極が前記出力端子に接続され、他方の電極に第1のクロック信号が供給される第1のキャパシタと、一方の電極が前記第1MOSトランジスタのゲートに接続され、他方の電極に第2のクロック信号が供給される第2のキャパシタとを備えることを特徴とする請求項1に記載の昇圧回路。

#### 【請求項3】

前記昇圧ユニットは、電流通路の一端が前記入力端子に接続され、電流通路の他端が前記出力端子に接続された第1MOSトランジスタと、電流通路の一端が前記入力端子に接続され、電流通路の他端が上記第1MOSトランジスタのゲートに接続され、ゲートが出力端子に接続された第2MOSトランジスタと、電流通路の一端が上記第1MOSトランジスタのゲートに接続され、電流通路の他端に電源電圧または接地電位が印加され、ゲートに前記リセット信号が供給されるリセット用の第3MOSトランジスタと、電流通路の一端が上記第2MOSトランジスタのゲートに接続され、電流通路の他端に電源電圧または接地電位が印加され、ゲートに前記リセット信号が供給されるリセット用の第4MOSトランジスタと、一方の電極が前記出力端子に接続される第1のキャパシタと、一方の電極が前記第1MOSトランジスタのゲートに接続される第2のキャパシタと、一方の電極が前記第1のキャパシタの他方の電極に接続され、他方の電極に第1のクロック信号が供給される第3のキャパシタと、電流通路の一端が前記第1のキャパシタの他方の電極に接続され、電流通路の他端に電源電位または接地電位が印加され、ゲートに前記リセット信号が供給されるリセット用の第5MOSトランジスタと、一方の電極が前記第2のキャパシタの他方の電極に接続され、他方の電極に第2のクロック信号が供給される第4のキャパシタと、電流通路の一端が前記第2のキャパシタの他方の電極に接続され、電流通路の他端に電源電位または接地電位が印加され、ゲートに前記リセット信号が供給されるリセット用の第6MOSトランジスタとを備えることを特徴とする請求項1に記載の昇圧回路。

#### 【請求項4】

一方の電極が前記リセット信号発生器における上記正または負の昇圧電位が印加されるノードに接続され、他方の電極に接地電位または電源電圧が印加される第5のキャパシタを更に具備することを特徴とする請求項1に記載の昇圧回路。

#### 【請求項5】

前記リセットパルス発生器は、正電圧と接地電位間の電圧で動作し、リセット信号のハイレベルを前記正電位にシフトするハイレベルシフタと、上記正電圧と前記出力回路部から出力される負の昇圧電位間の電圧で動作し、上記ハイレベルシフタの出力のロウレベルを上記負の昇圧電位にレベルシフトするロウレベルシフタと、上記正電圧と前記出力回路部から出力される負の昇圧電位間の電圧で動作する奇数段のインバータ回路と、偶数段目のインバータ回路の出力信号と奇数段目のインバータ回路の出力信号が供給され、前記各昇圧ユニットに前記リセット信号を供給する論理回路とを備え、

前記ディスチャージ回路は、正電圧と接地電位間の電圧で動作し、ディスチャージインターブル信号のハイレベルを前記正電位にシフトするハイレベルシフタと、上記正電圧と前記出力回路部から出力される負の昇圧電位間の電圧で動作し、上記ハイレベルシフタの出力のロウレベルを上記負の昇圧電位にレベルシフトするロウレベルシフタと、上記正電圧と前記出力回路部から出力される負の昇圧電位間の電圧で動作する偶数段のインバータ回路と、電流通路の一端が上記リセットパルス発生器における負の昇圧電位が印加される電源線に接続され、電流通路の他端が接地点に接続され、ゲートに前記偶数段目のインバータ回路の出力信号が供給される第7MOSトランジスタとを備える

ことを特徴とする請求項1に記載の昇圧回路。

#### 【請求項6】

前記リセットパルス発生器は、前記出力回路部から出力される正の昇圧電圧と接地電位

10

20

30

40

50

間の電圧で動作し、リセット信号のハイレベルを前記昇圧電圧にシフトするハイレベルシフタと、上記正の昇圧電圧と上記接地電位間の電圧で動作し、前記各昇圧ユニットに前記リセット信号を供給する偶数段のインバータ回路とを備え、

前記ディスチャージ回路は、昇圧電圧と接地電位間の電圧で動作し、ディスチャージイネーブル信号のハイレベルを前記昇圧電圧にシフトするハイレベルシフタと、上記昇圧電圧と接地電位間の電圧で動作する偶数段のインバータ回路と、電流通路の一端が上記リセットパルス発生器における正の昇圧電位が印加される電源線に接続され、電流通路の他端が電源に接続され、ゲートに上記偶数段目のインバータ回路の出力信号が供給される第7MOSトランジスタとを備える

ことを特徴とする請求項1に記載の昇圧回路。

10

#### 【請求項7】

位相の異なるクロック信号に応答して、順次電荷を転送して昇圧を行う昇圧回路と、前記昇圧回路の出力電圧に基づいて動作する回路とを具備し、

前記昇圧回路は、初段の入力端子に電源電位または接地電位が印加され、各々の出力端子が順次次段の入力端子にそれぞれ接続された複数の昇圧ユニットと、前記昇圧ユニットの最終段の出力電位で制御され、最終段より前の段の昇圧ユニットの出力電位を転送する出力回路部と、前記出力回路部から出力される正または負の昇圧電位を電源の一方に用いて、前記正または負の昇圧電位と接地電位間の振幅のリセット信号を生成し、前記各昇圧ユニットに供給することにより、各昇圧ユニットにおける電荷が残存するトランジスタのゲートノードをリセットするリセットパルス発生器と、前記リセットパルス発生器における前記正または負の昇圧電位が印加されるノードを、前記電荷が残存するトランジスタのゲートノードのリセット後にディスチャージするディスチャージ回路とを備えることを特徴とする電圧発生回路。

20

#### 【請求項8】

前記各昇圧ユニットはそれぞれ、電流通路の一端が前記入力端子に接続され、電流通路の他端が前記出力端子に接続された第1MOSトランジスタと、電流通路の一端が前記入力端子に接続され、電流通路の他端が前記第1MOSトランジスタのゲートに接続され、ゲートが出力端子に接続された第2MOSトランジスタと、電流通路の一端が前記第1MOSトランジスタのゲートに接続され、電流通路の他端に電源電圧または接地電位が印加され、ゲートに前記リセット信号が供給されるリセット用の第3MOSトランジスタと、電流通路の一端が前記第2MOSトランジスタのゲートに接続され、電流通路の他端に電源電圧または接地電位が印加され、ゲートに前記リセット信号が供給されるリセット用の第4MOSトランジスタと、一方の電極が前記出力端子に接続され、他方の電極に第1のクロック信号が供給される第1のキャパシタと、一方の電極が前記第1MOSトランジスタのゲートに接続され、他方の電極に第2のクロック信号が供給される第2のキャパシタとを備えることを特徴とする請求項7に記載の電圧発生回路。

30

#### 【請求項9】

前記各昇圧ユニットはそれぞれ、電流通路の一端が前記入力端子に接続され、電流通路の他端が前記出力端子に接続された第1MOSトランジスタと、電流通路の一端が前記入力端子に接続され、電流通路の他端が前記第1MOSトランジスタのゲートに接続され、ゲートが出力端子に接続された第2MOSトランジスタと、電流通路の一端が前記第1MOSトランジスタのゲートに接続され、電流通路の他端に電源電圧または接地電位が印加され、ゲートに前記リセット信号が供給されるリセット用の第3MOSトランジスタと、電流通路の一端が前記第2MOSトランジスタのゲートに接続され、電流通路の他端に電源電圧または接地電位が印加され、ゲートに前記リセット信号が供給されるリセット用の第4MOSトランジスタと、一方の電極が前記出力端子に接続される第1のキャパシタと、一方の電極が前記第1MOSトランジスタのゲートに接続される第2のキャパシタと、一方の電極が前記第1のキャパシタの他方の電極に接続され、他方の電極に第1のクロック信号が供給される第3のキャパシタと、電流通路の一端が前記第1のキャパシタの他方の電極に接続され、電流通路の他端に電源電圧または接地電位が印加され、ゲートに前記リセット信号が供給されるリセット用の第5MOSトランジスタと、一方の電極が前記第3のキャパシタの他方の電極に接続され、他方の電極に第2のクロック信号が供給される第4のキャパシタと、一方の電極が前記第3のキャパシタの他方の電極に接続され、他方の電極に第3のクロック信号が供給される第5のキャパシタとを備えることを特徴とする請求項7に記載の電圧発生回路。

40

50

リセット信号が供給されるリセット用の第5MOSトランジスタと、一方の電極が前記第2のキャパシタの他方の電極に接続され、他方の電極に第2のクロック信号が供給される第4のキャパシタと、電流通路の一端が前記第2のキャパシタの他方の電極に接続され、電流通路の他端に電源電位または接地電位が印加され、ゲートに前記リセット信号が供給されるリセット用の第6MOSトランジスタとを備えることを特徴とする請求項7に記載の電圧発生回路。

#### 【請求項10】

一方の電極が前記リセット信号発生器における前記正または負の昇圧電位が印加されるノードに接続され、他方の電極に接地電位または電源電圧が印加される第5のキャパシタを更に具備することを特徴とする請求項7に記載の電圧発生回路。 10

#### 【請求項11】

前記リセットパルス発生器は、正電圧と接地電位間の電圧で動作し、リセット信号のハイレベルを前記正電位にシフトするハイレベルシフタと、前記正電圧と前記出力回路部から出力される負の昇圧電位間の電圧で動作し、前記ハイレベルシフタの出力のロウレベルを前記負の昇圧電位にレベルシフトするロウレベルシフタと、前記正電圧と前記出力回路部から出力される負の昇圧電位間の電圧で動作する奇数段のインバータ回路と、偶数段目のインバータ回路の出力信号と奇数段目のインバータ回路の出力信号が供給され、前記各昇圧ユニットに前記リセット信号を供給する論理回路とを備え、

前記ディスチャージ回路は、正電圧と接地電位間の電圧で動作し、ディスチャージイネーブル信号のハイレベルを前記正電位にシフトするハイレベルシフタと、前記正電圧と前記出力回路部から出力される負の昇圧電位間の電圧で動作し、前記ハイレベルシフタの出力のロウレベルを前記負の昇圧電位にレベルシフトするロウレベルシフタと、前記正電圧と前記出力回路部から出力される負の昇圧電位間の電圧で動作する偶数段のインバータ回路と、電流通路の一端が前記リセットパルス発生器における負の昇圧電位が印加される電源線に接続され、電流通路の他端が接地点に接続され、ゲートに前記偶数段目のインバータ回路の出力信号が供給される第7MOSトランジスタとを備えることを特徴とする請求項7に記載の電圧発生回路。 20

#### 【請求項12】

前記リセットパルス発生器は、前記出力回路部から出力される正の昇圧電圧と接地電位間の電圧で動作し、リセット信号のハイレベルを前記昇圧電圧にシフトするハイレベルシフタと、前記正の昇圧電圧と前記接地電位間の電圧で動作し、前記各昇圧ユニットに前記リセット信号を供給する偶数段のインバータ回路とを備え、 30

前記ディスチャージ回路は、昇圧電圧と接地電位間の電圧で動作し、ディスチャージイネーブル信号のハイレベルを前記昇圧電圧にシフトするハイレベルシフタと、前記昇圧電圧と接地電位間の電圧で動作する偶数段のインバータ回路と、電流通路の一端が前記リセットパルス発生器における正の昇圧電位が印加される電源線に接続され、電流通路の他端が電源に接続され、ゲートに前記偶数段目のインバータ回路の出力信号が供給される第7MOSトランジスタとを備えることを特徴とする請求項7に記載の電圧発生回路。

#### 【発明の詳細な説明】

##### 【0001】

##### 【発明の属する技術分野】

この発明は、複数の昇圧ユニット（昇圧セル）における各々の出力端子を順次次段の入力端子にそれぞれ接続し、位相の異なるクロック信号に応答して各昇圧ユニットの入力端子から出力端子に順次電荷を転送して昇圧動作を行う昇圧回路に関するもので、特に各々の昇圧ユニットにおける電荷が残存するトランジスタのゲートノードのリセット技術に関する。

##### 【0002】

##### 【従来の技術】

図10は、従来の昇圧回路の構成例を示す回路図である。この昇圧回路については、IEEE Journal of Solid-State Circuits.Vol.27, No.11, November 1992, pp.1540-1546, A.Umeza 50

wa et al. "A 5-V-Only Operation 0.6- $\mu$ m Flash EEPROM with Row Decoder Scheme in Triple Well Structure"に記載されている。

#### 【0003】

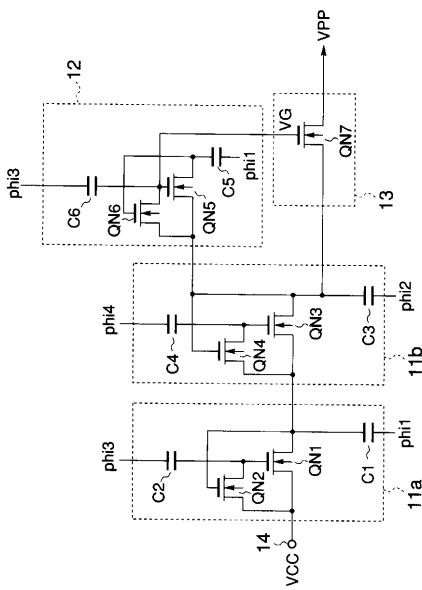

この昇圧回路は、昇圧ユニット（昇圧セル）11a, 11b、昇圧ユニット12及び出力回路部13で構成されている。各昇圧ユニット11a, 11b, 12はそれぞれ、2つのMOSトランジスタ（MOSFET）と2つのキャパシタで構成され、各々の出力端子と入力端子がそれぞれ順次接続されている。

#### 【0004】

すなわち、上記昇圧ユニット11aは、Nチャネル型MOSトランジスタQN1, QN2とキャパシタC1, C2を備えている。上記MOSトランジスタQN1, QN2の電流通路の一端はそれぞれ、電源電圧VCCが印加される電源端子14に接続される。上記MOSトランジスタQN2の電流通路の他端はMOSトランジスタQN1のゲートに接続され、ゲートは上記MOSトランジスタQN1の電流通路の他端に接続される。上記キャパシタC1の一方の電極は、上記MOSトランジスタQN1の電流通路の他端に接続され、このキャパシタC1の他方の電極にはクロック信号phi1が供給される。また、上記キャパシタC2の一方の電極は、上記MOSトランジスタQN1のゲートに接続され、このキャパシタC2の他方の電極にはクロック信号phi3が供給される。

10

#### 【0005】

同様に、上記昇圧ユニット11bは、Nチャネル型MOSトランジスタQN3, QN4とキャパシタC3, C4を備えている。上記MOSトランジスタQN3, QN4の電流通路の一端はそれぞれ、上記MOSトランジスタQN1の電流通路の他端に接続される。上記MOSトランジスタQN4の電流通路の他端はMOSトランジスタQN3のゲートに接続され、ゲートは上記MOSトランジスタQN3の電流通路の他端に接続される。上記キャパシタC3の一方の電極は、上記MOSトランジスタQN3の電流通路の他端に接続され、このキャパシタC3の他方の電極にはクロック信号phi2が供給される。上記キャパシタC4の一方の電極は、上記MOSトランジスタQN3のゲートに接続され、このキャパシタC4の他方の電極にはクロック信号phi4が供給される。

20

#### 【0006】

また、上記昇圧ユニット12は、Nチャネル型MOSトランジスタQN5, QN6とキャパシタC5, C6を備えている。上記MOSトランジスタQN5, QN6の電流通路の一端はそれぞれ、上記MOSトランジスタQN3の電流通路の他端に接続される。上記MOSトランジスタQN6の電流通路の他端はMOSトランジスタQN5のゲートに接続され、ゲートは上記MOSトランジスタQN5の電流通路の他端に接続される。上記キャパシタC5の一方の電極は、上記MOSトランジスタQN5の電流通路の他端に接続され、このキャパシタC5の他方の電極には上記クロック信号phi1が供給される。上記キャパシタC6の一方の電極は、上記MOSトランジスタQN5のゲートに接続され、このキャパシタC6の他方の電極には上記クロック信号phi3が供給される。

30

#### 【0007】

上記出力回路部13は、Nチャネル型MOSトランジスタQN7によって構成されている。上記MOSトランジスタQN7の電流通路の一端は、上記MOSトランジスタQN3の電流通路の他端に接続され、このMOSトランジスタQN7のゲートは上記MOSトランジスタQN5のゲートに接続される。そして、上記MOSトランジスタQN7の電流通路の他端から、電源電圧VCCを昇圧した正の電圧VPPを出力するようになっている。

40

#### 【0008】

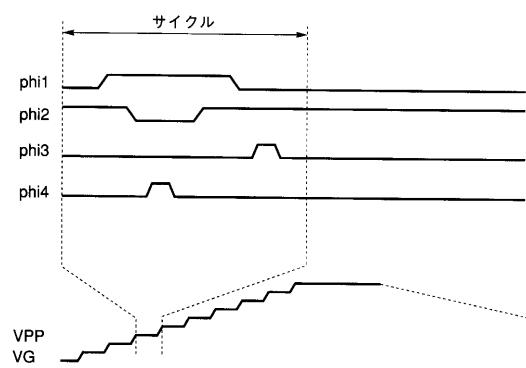

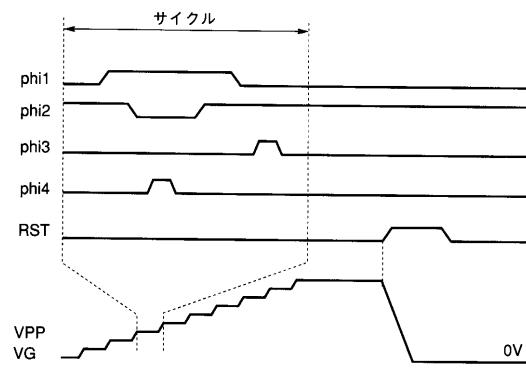

上記のような構成において、図11のタイミングチャートに示すように、位相の異なる4相のクロック信号phi1, phi2, phi3, phi4が入力されると、これらのクロック信号の1サイクル毎に、昇圧ユニット11a, 11bによって電源電圧VCCが順次昇圧されてMOSトランジスタQN7の電流通路の一端に供給される。また、この昇圧された電圧が昇圧ユニット12に供給されて更に昇圧されて電圧VGが生成され、上記MOSトランジスタQN7のゲートに供給される。このように、最終段の転送MOSトラン

50

ジスタQ N 7のゲートが昇圧ユニット1 2によってオーバードライブされ、MOSトランジスタQ N 7の閾値電圧による出力電圧V PPの低下が抑制される。

#### 【0009】

ところで、上記のような4相型の昇圧回路では、昇圧動作の終了後、各MOSトランジスタのゲートノードに高い電圧がフローティングのまま残ってしまうと、再昇圧動作時に転送MOSトランジスタQ N 1, Q N 3, Q N 7がオン状態を維持し、昇圧動作ができなくなってしまう。

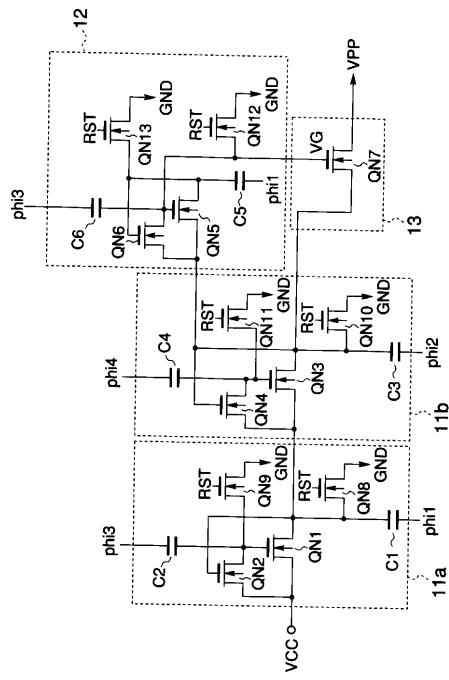

#### 【0010】

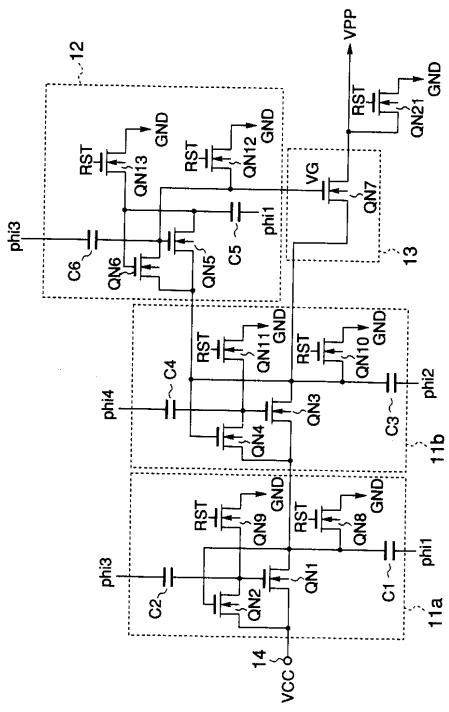

そこで、図12に示すように、上記図10に示した回路における各MOSトランジスタQ N 1～Q N 6のゲートと各キャパシタC 1～C 6との接続ノードと接地点(GND)間にそれぞれ、リセット用のNチャネル型MOSトランジスタQ N 8～Q N 13を設けた構成が提案されている。これらのMOSトランジスタQ N 8～Q N 13のゲートには、リセット信号RSTが供給される。

#### 【0011】

上記のような構成において、図13のタイミングチャートに示すように、最終段の転送用MOSトランジスタQ N 7のゲート電圧VGは、各クロック信号phi 1～phi 4の1サイクル毎に上昇していき、出力電圧V PPは所望の電圧に昇圧される。そして、昇圧動作が終了した時点でリセット信号RSTをハイレベルにしてMOSトランジスタQ N 8～Q N 13をオンさせ、各MOSトランジスタQ N 1～Q N 6のゲートと各キャパシタC 1～C 6との接続ノードをそれぞれ接地して放電すれば、転送MOSトランジスタQ N 1, Q N 3, Q N 7を強制的にオフさせることができ、再昇圧動作で誤動作することはない。

#### 【0012】

更に、図14に示すように、上記図12に示した昇圧回路における出力電圧V PPの出力ノードと接地点GND間に、リセット用のNチャネル型MOSトランジスタQ N 21を設けた構造も知られている。そして、昇圧動作の終了後、このMOSトランジスタQ N 21のゲートにリセット信号RSTを供給することにより、出力ノードも接地してリセットする。

#### 【0013】

このように、正の電圧を発生する昇圧回路の場合には、ソースを接地し、ゲートに接地電位と電源電圧VCC間の振幅のリセット信号が入力されるNチャネル型MOSトランジスタを用いることで、比較的容易に各ノードのリセットを行うことができる。

#### 【0014】

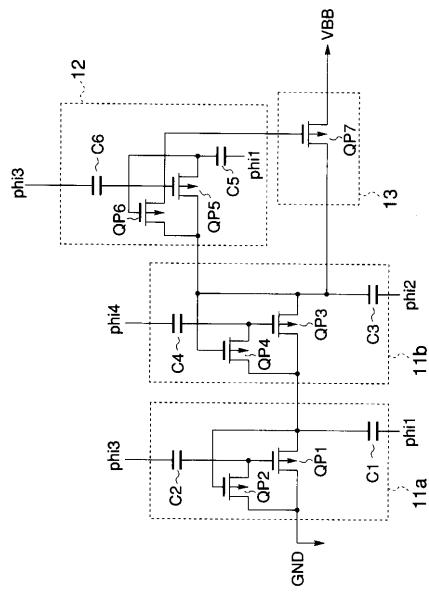

また、上述した文献には、図15に示すような負電圧を発生する昇圧回路も開示されている。この回路は、上記図10に示した回路におけるNチャネル型MOSトランジスタQ N 1～Q N 7に代えて、Pチャネル型MOSトランジスタQ P 1～Q P 7を設けたものである。また、初段の昇圧ユニットの11aの入力端子、すなわちMOSトランジスタQ N 1, Q N 2の電流通路の一端は、電源端子14に代えて接地点GNDに接続する。

#### 【0015】

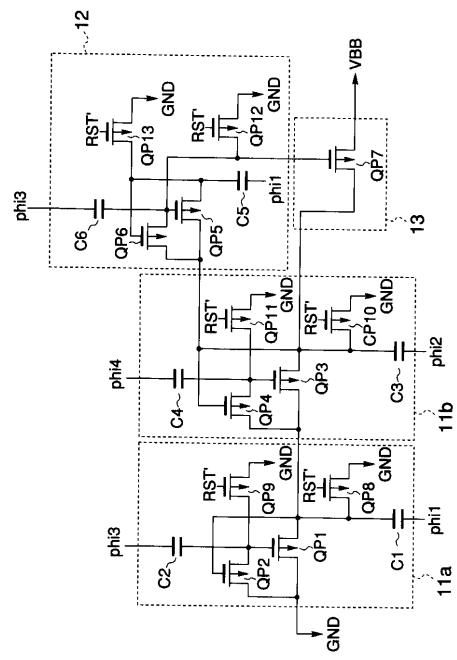

同様に、上記図12に示した回路におけるNチャネル型MOSトランジスタQ N 1～Q N 13に代えて、Pチャネル型MOSトランジスタQ P 1～Q P 13を設けた図16に示すような構成の負の昇圧電圧を発生する昇圧回路にも適用できる。

#### 【0016】

ところで、図16に示すような負の昇圧電圧を発生する昇圧回路を構成した場合、リセット用のPチャネル型MOSトランジスタQ P 8～Q P 13のゲートには、接地電位と所定の負の昇圧電位間の振幅のリセット信号RST'を与える必要がある。しかし、通常のリセット信号RSTは接地電位と電源電位間の振幅の信号であるため、そのまま単純にPチャネル型MOSトランジスタQ P 8～Q P 13のゲートに与えることはできない。このようなリセット信号RST'を生成するために、別の負電圧発生回路を設けることは勿論可能であるが、回路が増えるとともに制御が複雑化するという問題がある。

#### 【0017】

10

20

30

40

50

**【発明が解決しようとする課題】**

上記のように従来の昇圧回路は、電荷が残存するトランジスタのゲートノードをリセットするために、振幅の大きなりセット信号を生成する必要があり、リセット信号のために別の電圧発生回路を用いると回路規模が増大したり、制御が複雑化するという問題があった。

**【0018】**

この発明は上記のような事情に鑑みてなされたもので、その目的とするところは、電荷が残存するトランジスタのゲートノードをリセットする構成であっても、回路規模の増大を抑制できるとともに制御の簡単化も図れる昇圧回路を提供することにある。

**【0021】**

10

**【課題を解決するための手段】**

この発明の一態様に係る昇圧回路は、初段の入力端子に電源電位または接地電位が印加され、各々の出力端子が順次次段の入力端子にそれぞれ接続された複数の昇圧ユニットと、上記昇圧ユニットの最終段の出力電位で制御され、最終段より前の段の昇圧ユニットの出力電位を転送する出力回路部と、上記出力回路部から出力される正または負の昇圧電位を電源の一方に用いて、上記正または負の昇圧電位と接地電位間の振幅のリセット信号を生成し、上記各昇圧ユニットに供給することにより、各昇圧ユニットにおける電荷が残存するトランジスタのゲートノードをリセットするリセットパルス発生器と、上記リセットパルス発生器における上記正または負の昇圧電位が印加されるノードを、上記電荷が残存するトランジスタのゲートノードのリセット後にディスチャージするディスチャージ回路とを具備する。

20

**【0022】**

上記のような構成によれば、リセット信号の生成に昇圧部の出力電圧自身を用いるので、簡単な論理回路のみで構成でき、別の負電圧発生回路を用いる必要がなくなり、比較的簡単な制御で昇圧ユニットの電荷が残存するトランジスタのゲートノードをリセットできる。従って、回路規模の増大を抑制できるとともに制御の簡単化も図れる昇圧回路を提供できる。

**【0023】**

**【発明の実施の形態】**

以下、この発明の実施の形態について図面を参照して説明する。

30

**[第1の実施の形態]**

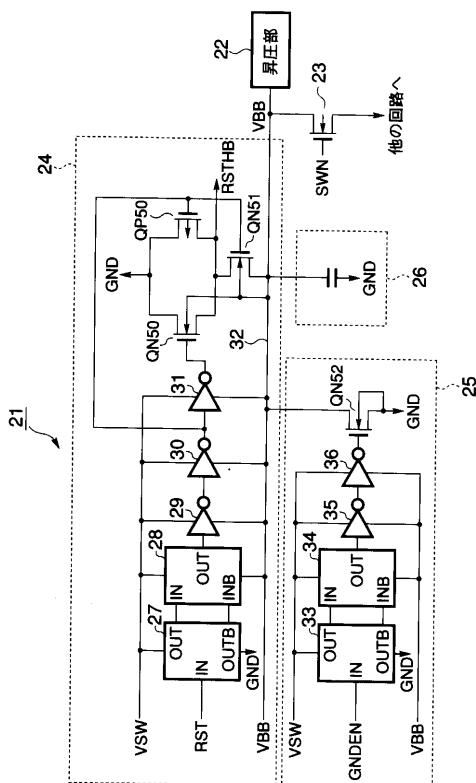

図1は、この発明の第1の実施の形態に係る昇圧回路について説明するためのもので、4相型負電圧発生昇圧回路である。この回路は、いわゆる降圧回路であるが、以降の説明では負電圧を発生する昇圧回路として説明する。

**【0024】**

この4相型負電圧発生昇圧回路は、リセット信号発生部21、昇圧部22及びトランジスタ部23で構成されている。トランジスタ部23は、昇圧部22と他の回路との間に設けられ、スイッチング信号SWNによってオン／オフ制御されることにより、昇圧部22から出力される負電圧VBBを負荷となる他の回路へ供給したり、遮断したりする。

**【0025】**

40

上記リセット信号発生部21は、リセットパルス発生器24、ディスチャージ回路25及びキャパシタ26から構成されている。上記リセットパルス発生器24は、ハイレベルシフタ27、ロウレベルシフタ28、インバータ回路29～31、Nチャネル型MOSトランジスタQN50、QN51、及びPチャネル型MOSトランジスタQP50等から構成されている。上記ハイレベルシフタ27、ロウレベルシフタ28及びインバータ回路29～31はそれぞれ、入力端子と出力端子とが順次接続されている。上記ハイレベルシフタ27は正電圧VSWと接地点GND間の電圧で動作し、上記ロウレベルシフタ28及びインバータ回路29～31はそれぞれ、正電圧VSWと昇圧部22から出力される負電圧VBBで動作する。上記正電圧VSWは、電源電圧VCCでも良いし、電源電圧VCCCから発生した別の電圧でも良い。リセット信号RSTは、ハイレベルシフタ27の入力端子I

50

Nに供給され、このハイレベルシフタ27の出力端子OUT, OUTBから出力される信号がロウレベルシフタ28の入力端子IN, INBに供給される。このロウレベルシフタ28の出力端子OUTから出力される信号は、インバータ回路28の入力端子に供給され、このインバータ回路29の出力信号がインバータ回路30の入力端子に供給される。インバータ回路30の出力信号は、インバータ回路31の入力端子及び上記MOSトランジスタQ P 50, Q N 51のゲートに供給される。上記インバータ回路31の出力信号は、上記MOSトランジスタQ N 50のゲートに供給される。

#### 【0026】

上記MOSトランジスタQ N 50, Q N 51の電流通路の一端はそれぞれ接地点GNDに接続され、他端はMOSトランジスタQ N 51の電流通路の一端に共通接続される。このMOSトランジスタQ N 51の電流通路の他端は、電源線32に接続される。この電源線32には、昇圧部22で発生した負電圧VBBが供給される。そして、上記MOSトランジスタQ N 50, Q P 50, Q N 51の電流通路の接続点から内部リセット信号RSTHBを発生し、昇圧部22に供給する。この内部リセット信号RSTHBは、リセット信号RSTがロウレベルの時には0V、ハイレベルの時にはVBBレベルとなる。

10

#### 【0027】

上記ディスチャージ回路25は、ハイレベルシフタ33、ロウレベルシフタ34、インバータ回路35, 36、及びNチャネル型MOSトランジスタQ N 52等から構成されている。上記ハイレベルシフタ33、ロウレベルシフタ34及びインバータ回路35, 36はそれぞれ、入力端子と出力端子とが順次接続されている。上記ハイレベルシフタ33は、正電圧VSWと接地点GND間の電圧で動作し、ロウレベルシフタ34及びインバータ回路35, 36はそれぞれ、正電圧VSWと昇圧回路22から出力される負電圧VBBで動作する。ディスチャージ信号GNDENは、ハイレベルシフタ33の入力端子INに供給され、このハイレベルシフタ33の出力端子OUT, OUTBから出力される信号がロウレベルシフタ34の入力端子IN, INBに供給される。このロウレベルシフタ34の出力端子OUTから出力される信号は、インバータ回路35の入力端子に供給され、このインバータ回路35の出力信号がインバータ回路36の入力端子に供給される。インバータ回路36の出力信号は、上記MOSトランジスタQ N 52のゲートに供給される。上記MOSトランジスタQ N 52の電流通路の一端は、電源線32に接続され、他端は接地点GNDに接続されている。

20

#### 【0028】

上記キャパシタ26は、上記電源線32と接地点GND間に接続されている。このキャパシタ26は、上記昇圧部22中の内部リセット信号RSTHBが入力されるPチャネル型MOSトランジスタの全ゲート容量と同程度、またはそれに比べて大きい容量を有するキャパシタまたは寄生容量である。このキャパシタ26としてはゲート容量を用いても良いし、2つのポリシリコン層間、2つの金属層間、またはポリシリコン層と金属間の静電容量でも良い。

30

#### 【0029】

なお、負電圧VBBが供給される電源線32には、この電源線32が配線されるPNジャンクション容量やMOSトランジスタのゲート電極とソース領域とのオーバーラップ容量等の大きい寄生容量が付随することがある。この場合には、外付けのキャパシタ26は不要になる。内部リセット信号RSTHBが入力されるPチャネル型MOSトランジスタの全ゲート容量と同程度、またはそれに比べて大きい容量が必要なのは、キャパシタ26の一方の電極側の負電圧VBBは、リセット時にゲート容量との分割電圧になつてもPチャネル型MOSトランジスタのオン抵抗が十分に低くなるようにするためである。

40

#### 【0030】

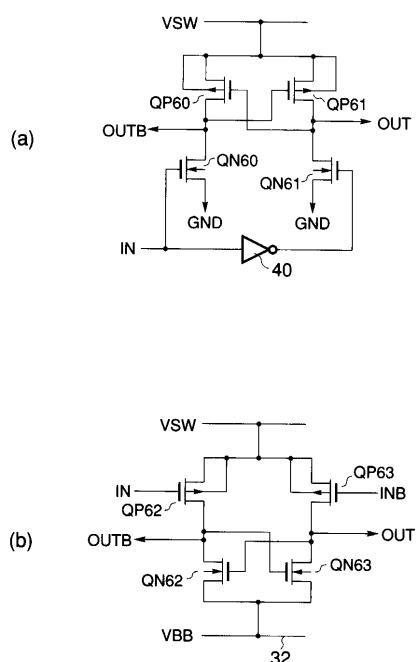

図2(a)は、上記図1に示した回路におけるハイレベルシフタ27, 33の構成例を示す回路図である。このハイレベルシフタは、Pチャネル型MOSトランジスタQ P 60, Q P 61、Nチャネル型MOSトランジスタQ N 60, Q N 61及びインバータ40で構成されている。上記MOSトランジスタQ P 60, Q P 61の電流通路の一端及びバック

50

ゲートには、正電圧VSWが印加される。これらMOSトランジスタQ P 6 0 , Q P 6 1の電流通路の他端と接地点GND間にはそれぞれ、MOSトランジスタQ N 6 0 , Q N 6 1の電流通路が接続されている。上記MOSトランジスタQ P 6 0 のゲートは、上記MOSトランジスタQ P 6 1 , Q N 6 1の電流通路の接続点（出力端子OUT）に接続される。また、上記MOSトランジスタQ P 6 1のゲートは、上記MOSトランジスタQ P 6 0 , Q N 6 0の電流通路の接続点（出力端子OUTB）に接続される。上記MOSトランジスタQ N 6 0 のゲートは入力端子INに接続される。この入力端子INには、インバータ40の入力端子が接続され、インバータ40の出力端子はMOSトランジスタQ N 6 1のゲートに接続されている。

## 【0031】

10

上記入力端子INに供給されたリセット信号RSTまたはディスチャージ信号GNDENのハイレベルは、正電圧VSWにレベルシフトされ、出力端子OUTまたはOUTBから相補的に出力される。

## 【0032】

図2(b)は、上記図1に示した回路におけるロウレベルシフタ28, 34の構成例を示す回路図である。このロウレベルシフタは、Pチャネル型MOSトランジスタQ P 6 2 , Q P 6 3、及びNチャネル型MOSトランジスタQ N 6 2 , Q N 6 3で構成されている。上記MOSトランジスタQ P 6 2 , Q P 6 3の電流通路の一端及びバックゲートには、正電圧VSWが印加される。これらMOSトランジスタQ P 6 2 , Q P 6 3の電流通路の他端と負電圧VBBが印加される電源線32間にはそれぞれ、MOSトランジスタQ N 6 2 , Q N 6 3の電流通路が接続されている。上記MOSトランジスタQ P 6 2 のゲートには入力端子INが接続されており、上記MOSトランジスタQ P 6 3のゲートには入力端子INBが接続されている。これらの入力端子IN, INBにはそれぞれ、ハイレベルシフタ27または33の出力端子OUT, OUTBがそれぞれ接続される。上記MOSトランジスタQ N 6 2 のゲートは、上記MOSトランジスタQ P 6 3 , Q N 6 3の電流通路の接続点（出力端子OUT）に接続される。また、上記MOSトランジスタQ N 6 3のゲートは、上記MOSトランジスタQ P 6 2 , Q N 6 2の電流通路の接続点（出力端子OUTB）に接続される。

20

## 【0033】

30

上記入力端子IN, INBに供給されたハイレベルシフタの出力信号のロウレベルは、負電圧VBBにレベルシフトされ、出力端子OUT, OUTBから相補的に出力される。よって、上記ハイレベルシフタとロウレベルシフタを通過したリセット信号RSTまたはディスチャージイネーブル信号GNDENは、正電圧VSWと負電圧VBB間の振幅の信号となる。

## 【0034】

なお、上記図2(b)に示したロウレベルシフタは、出力端子OUTとOUTBを備えているが、図1に示した回路構成の場合には、出力端子OUTのみを利用している。

## 【0035】

40

また、図3(a)は、上記図1に示した回路におけるインバタ回路29~31, 35, 36の構成例を示す回路図である。このインバタ回路は、正電圧VSWと負電圧VBBを電源電圧として動作するCMOSインバタ構成になっている。すなわち、入力端子INにはPチャネル型MOSトランジスタQ P 7 0 とNチャネル型MOSトランジスタQ N 7 0のゲートが接続される。上記MOSトランジスタQ P 7 0の電流通路の一端とバックゲートに正電圧VSWが印加される。また、Nチャネル型MOSトランジスタQ N 7 0の電流通路の一端には、負電圧VBBが印加される。これらMOSトランジスタQ P 7 0 , Q N 7 0の電流通路の他端は共通接続され、出力端子OUTに接続されている。

## 【0036】

上記構成にあっては、入力端子INに供給された信号が反転され、この反転信号のハイレベルは正電圧VSW、ロウレベルは負電圧VBBとなって出力端子OUTから出力される。

50

**【0037】**

図3(b)は、上記図1に示した回路におけるインバータ回路29~31, 35, 36の他の構成例を示す回路図である。このインバータ回路は、Pチャネル型MOSトランジスタQ P71とNチャネル型MOSトランジスタQ N71, Q N72とで構成されている。上記MOSトランジスタQ P71, Q N71, Q N72の電流通路は直列接続されている。MOSトランジスタQ P71の電流通路の一端とバックゲートには、正電圧V SWが印加される。上記MOSトランジスタQ N72の電流通路の一端には、負電圧V BBが印加される。第1の入力端子IN1にはMOSトランジスタQ P71, Q N72のゲートが接続され、第2の入力端子IN2にはMOSトランジスタQ N71のゲートが接続される。そして、上記MOSトランジスタQ P71, Q N71の電流通路の接続点に、出力端子OUTが接続されている。

10

**【0038】**

上記構成のインバータ回路において、第1, 第2の入力端子IN1, IN2を短絡して用いる。この構成では、MOSトランジスタQ P71とQ N72間にMOSトランジスタQ N71が介在されることにより、より高い耐圧を確保できる。なお、短絡した入力端子IN1, IN2に供給された信号が反転され、この反転信号のハイレベルが正電圧V SW、ロウレベルが負電圧V BBとなって出力端子OUTから出力される点は図3(a)に示した回路と同様である。

**【0039】**

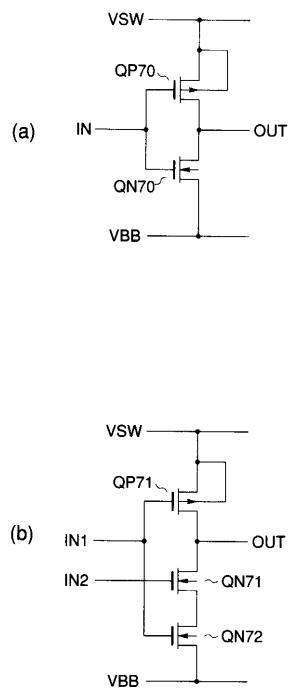

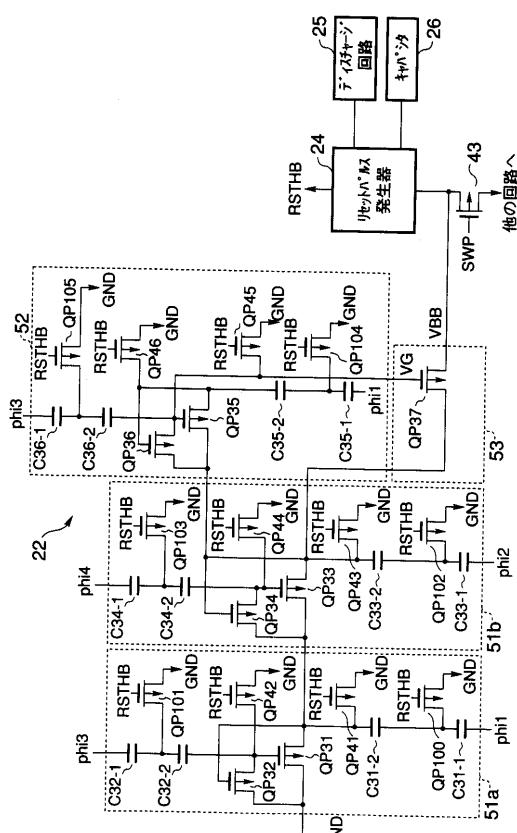

図4は、上記図1に示した回路における昇圧部22の構成例について説明するための回路図である。この昇圧部22は、昇圧ユニット(昇圧セル)51a, 51b、昇圧ユニット52、及び出力回路部53で構成されている。各昇圧ユニット51a, 51b, 52はそれぞれ、4つのMOSトランジスタ(MOSFET)と2つのキャパシタで構成され、各自的の出力端子と入力端子がそれぞれ順次接続されている。

20

**【0040】**

すなわち、上記昇圧ユニット51aは、Pチャネル型MOSトランジスタQ P31, Q P32, Q P41, Q P42とキャパシタC31, C32を備えている。上記MOSトランジスタQ P1, Q P2の電流通路の一端はそれぞれ、接地点GNDに接続される。上記MOSトランジスタQ P32の電流通路の他端はMOSトランジスタQ P31のゲートに接続され、ゲートは上記MOSトランジスタQ P31の電流通路の他端に接続される。上記キャパシタC31の一方の電極は、上記MOSトランジスタQ P31の電流通路の他端に接続され、このキャパシタC31の他方の電極にはクロック信号ph i1が供給される。上記キャパシタC32の一方の電極は、上記MOSトランジスタQ P31のゲートに接続され、このキャパシタC32の他方の電極にはクロック信号ph i3が供給される。上記MOSトランジスタQ P41の電流通路は、MOSトランジスタQ P32のゲートと接地点GND間に接続され、このMOSトランジスタQ P41のゲートには上記リセット信号発生部21から出力される内部リセット信号RSTHBが供給される。また、上記MOSトランジスタQ P42の電流通路は、MOSトランジスタQ P31のゲートと接地点GND間に接続され、このMOSトランジスタQ P42のゲートには上記内部リセット信号RSTHBが供給される。

30

**【0041】**

同様に、上記昇圧ユニット51bは、Pチャネル型MOSトランジスタQ P33, Q P34, Q P43, Q P44とキャパシタC33, C34を備えている。上記MOSトランジスタQ P33, Q P34の電流通路の一端はそれぞれ、上記MOSトランジスタQ P31の電流通路の他端に接続される。上記MOSトランジスタQ P34の電流通路の他端はMOSトランジスタQ P33のゲートに接続され、ゲートは上記MOSトランジスタQ P33の電流通路の他端に接続される。上記キャパシタC33の一方の電極は、上記MOSトランジスタQ P33の電流通路の他端に接続され、このキャパシタC33の他方の電極にはクロック信号ph i2が供給される。上記キャパシタC34の一方の電極は、上記MOSトランジスタQ P33のゲートに接続され、このキャパシタC34の他方の電極にはク

40

50

ロック信号 p h i 4 が供給される。上記MOSトランジスタ Q P 4 3 の電流通路は、MOSトランジスタ Q P 3 4 のゲートと接地点 GND間に接続され、このMOSトランジスタ Q P 4 3 のゲートには上記内部リセット信号 R S T H B が供給される。また、上記MOSトランジスタ Q P 4 4 の電流通路は、MOSトランジスタ Q P 3 3 のゲートと接地点 GND間に接続され、このMOSトランジスタ Q P 4 4 のゲートには上記内部リセット信号 R S T H B が供給される。

#### 【 0 0 4 2 】

また、上記昇圧ユニット 5 2 は、Pチャネル型MOSトランジスタ Q P 3 5 , Q P 3 6 , Q P 4 5 , Q P 4 6 とキャパシタ C 3 5 , C 3 6 を備えている。上記MOSトランジスタ Q P 3 5 , Q P 3 6 の電流通路の一端はそれぞれ、上記MOSトランジスタ Q P 3 3 の電流通路の他端に接続される。上記MOSトランジスタ Q P 3 6 の電流通路の他端はMOSトランジスタ Q P 3 5 のゲートに接続され、ゲートは上記MOSトランジスタ Q P 3 5 の電流通路の他端に接続される。上記キャパシタ C 3 5 の一方の電極は、上記MOSトランジスタ Q P 3 5 の電流通路の他端に接続され、このキャパシタ C 3 5 の他方の電極にはクロック信号 p h i 1 が供給される。上記キャパシタ C 3 6 の一方の電極は、上記MOSトランジスタ Q P 3 5 のゲートに接続され、このキャパシタ C 3 6 の他方の電極にはクロック信号 p h i 3 が供給される。上記MOSトランジスタ Q P 4 5 の電流通路は、MOSトランジスタ Q P 3 5 のゲートと接地点 GND間に接続され、このMOSトランジスタ Q P 4 5 のゲートには上記内部リセット信号 R S T H B が供給される。また、上記MOSトランジスタ Q P 4 6 の電流通路は、MOSトランジスタ Q P 3 6 のゲートと接地点 GND間に接続され、このMOSトランジスタ Q P 4 6 のゲートには上記内部リセット信号 R S T H B が供給される。

10

20

#### 【 0 0 4 3 】

上記出力回路部 5 3 は、Pチャネル型MOSトランジスタ Q N 3 7 によって構成されている。上記MOSトランジスタ Q N 3 7 の電流通路の一端は、上記MOSトランジスタ Q P 3 3 の電流通路の他端に接続され、このMOSトランジスタ Q P 3 7 のゲートは上記MOSトランジスタ Q P 3 5 のゲートに接続される。そして、上記MOSトランジスタ Q N 3 7 の電流通路の他端から、昇圧した負電圧 V B B を出力するようになっている。

#### 【 0 0 4 4 】

上記のように、昇圧部 2 2 の回路構成は、基本的には図 1 6 に示した回路と同様であるが、リセット用の各MOSトランジスタ Q P 4 1 ~ Q P 4 6 のゲートに供給する内部リセット信号 R S T H B として、リセット信号発生回路 2 1 の出力信号を用いている。このリセット信号発生回路 2 1 は、この昇圧部 2 2 から出力される負電圧 V B B を用いて上記内部リセット信号 R S T H B を生成する。

30

#### 【 0 0 4 5 】

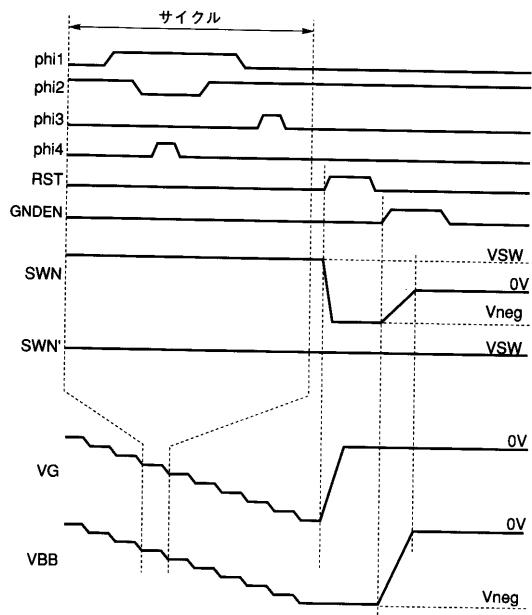

図 5 は、上記図 1 乃至図 4 に示した昇圧回路の動作を説明するためのタイミングチャートである。図示するように、従来の昇圧回路と同様にクロック信号 p h i 1 , p h i 2 , p h i 3 , p h i 4 が入力されると、これらクロック信号の 1 サイクル毎にMOSトランジスタ Q P 3 7 のゲート電圧 V G と出力電圧 V B B が低下して行く。そして、出力電圧 V B B が所望の昇圧レベル V n e g まで低下し、リセット信号 R S T が入力されると、このリセット信号 R S T から内部リセット信号 R S T が生成されてリセット用のMOSトランジスタ Q P 4 1 ~ Q P 4 6 のゲートが駆動され、各MOSトランジスタ Q P 3 1 ~ Q P 3 7 のゲートを接地点 ( 0 V ) にする。このとき、スイッチング信号 S W N を上記負の昇圧レベル V n e g にしてトランジスタ部 2 3 を遮断する。この時点では、出力電圧 V B B は負の昇圧レベル V n e g を保持している。その後、ディスチャージ信号 G N D E N がハイレベルとなると、出力電圧 V B B とスイッチング信号 S W N は、接地点 ( 0 V ) となる。

40

#### 【 0 0 4 6 】

ここで、リセット信号 R S T のタイミングによらず、トランジスタ部 2 3 をオンさせる場合には、S W N ' に示すように正電圧 V S W に固定すれば良い。

50

## 【0047】

上記のような構成によれば、リセット信号の生成に昇圧部22の出力電圧VBB自身を用いるので、静電容量といくつかの論理回路のみで接地電位と所定の負の昇圧電位間の振幅のリセット信号を容易に発生することが可能となる。よって、別の負電圧発生回路を用いる必要がなくなり、回路規模の増大を抑制できるとともに制御の簡単化も図れる。

## 【0048】

なお、図4に示した昇圧部22において、負電圧VBBの出力ノードと接地点GND間に、リセット用のPチャネル型MOSトランジスタを設け、昇圧動作の終了後、このMOSトランジスタのゲートに内部リセット信号RSTを供給し、出力ノードも接地してリセットするように構成しても良いのは勿論である。

10

## 【0049】

## [第2の実施の形態]

図6乃至図8はそれぞれ、この発明の第2の実施の形態に係る昇圧回路について説明するためのもので、4相型正電圧発生昇圧回路に適用した例である。正電圧発生回路の内部(電荷が残存する)トランジスタのゲートノードを接地電位にリセットするには、電源電圧VCCの振幅の信号で可能であるが、この場合には内部トランジスタのゲートノードを0Vから昇圧する必要があるため効率が悪い。そこで、昇圧回路の出力電圧VPPをリセット用のMOSトランジスタのゲートに与えることによって、内部トランジスタのゲートノードをVCCレベルにリセットできるようにしている。従って、内部トランジスタのゲートノードがVCCレベルから昇圧することになるので、0Vにリセットする場合に比べて昇圧に必要な電荷をVCC分減らすことができる。

20

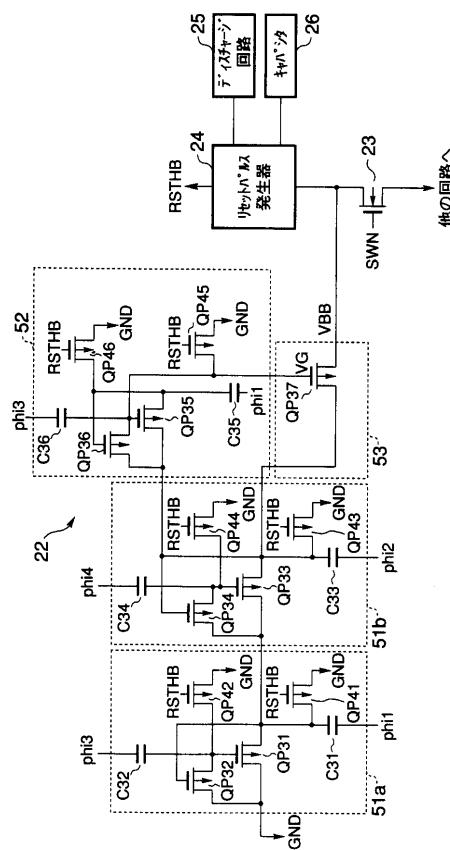

## 【0050】

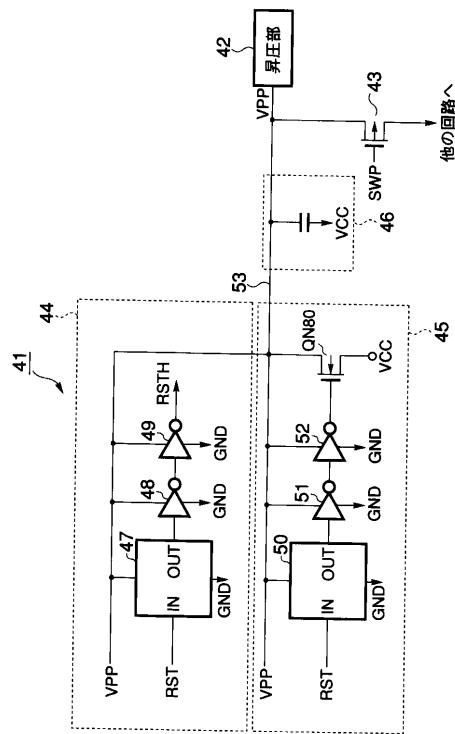

図6に示す4相型正電圧発生昇圧回路は、リセット信号発生部41、昇圧部42及びこれらの回路部41, 42間を接続するトランジスタ部43とで構成されている。上記トランジスタ部43は、昇圧部42の出力端と他の回路との間に設けられ、スイッチング信号SWPによってオン/オフ制御されることにより、昇圧部42から出力される正電圧VPPを負荷となる他の回路へ供給したり、遮断したりする。

## 【0051】

上記リセット信号発生部41は、リセットパルス発生器44、ディスチャージ回路45及びキャパシタ46から構成されている。上記リセットパルス発生器44は、ハイレベルシフタ47、インバータ回路48, 49等から構成されている。上記ハイレベルシフタ47及びインバータ回路48, 49はそれぞれ、入力端子と出力端子とが順次接続されており、昇圧回路42から出力される正の昇圧電圧VPPと接地点GND間の電圧で動作する。リセット信号RSTは、ハイレベルシフタ47の入力端子INに供給され、このハイレベルシフタ47の出力端子OUTから出力される信号がインバータ回路48の入力端子に供給され、このインバータ回路48の出力信号がインバータ回路49の入力端子に供給される。このインバータ回路49の出力信号は、内部リセット信号RSTHとして出力される。この内部リセット信号RSTHは、リセット信号RSTがロウレベルの時には0V、ハイレベルの時にはVPPレベルとなる。

30

## 【0052】

上記ディスチャージ回路45は、ハイレベルシフタ50、インバータ回路51, 52、Nチャネル型MOSトランジスタQN80等から構成されている。上記ハイレベルシフタ50及びインバータ回路51, 52はそれぞれ、入力端子と出力端子とが順次接続されており、昇圧部42から出力される昇圧電圧VPPと接地点GND間の電圧で動作する。ディスチャージ信号GNDENは、ハイレベルシフタ50の入力端子INに供給され、このハイレベルシフタ50の出力端子OUTから出力される信号がインバータ回路51の入力端子に供給され、このインバータ回路51の出力信号がインバータ回路52の入力端子に供給される。このインバータ回路52の出力信号は、上記MOSトランジスタQN80のゲートに供給される。上記MOSトランジスタQN80の電流通路の一端は、昇圧部42の出力電圧VPPが供給される電源線53に接続され、他端は電源VCCに接続されている

40

50

。

### 【0053】

上記キャパシタ46は、上記電源線53と電源VCC間に接続されている。このキャパシタ46は、第1の実施の形態と同様に、上記昇圧部42中の内部リセット信号RSTHが入力されるNチャネル型MOSトランジスタの全ゲート容量と同程度、またはそれに比べて大きい容量を有するキャパシタまたは寄生容量である。このキャパシタ46としてはゲート容量を用いても良いし、2つのポリシリコン層間、2つの金属層間、またはポリシリコン層と金属層間の静電容量でも良い。

### 【0054】

なお、昇圧電圧VPPが供給される電源線53には、この電源線53が配線されるPNジャンクション容量やMOSトランジスタのゲート電極とソース領域とのオーバーラップ容量等の大きい寄生容量が付随することがある。この場合には、外付けのキャパシタ46は不要になる。内部リセット信号RSTHが入力されるNチャネル型MOSトランジスタの全ゲート容量と同程度、またはそれに比べて大きい容量が必要なのは、キャパシタ46の一方の電極側の電圧VPPは、リセット時にゲート容量との分割電圧になってしまってもNチャネル型MOSトランジスタのオン抵抗が十分に低くなるようにするためである。

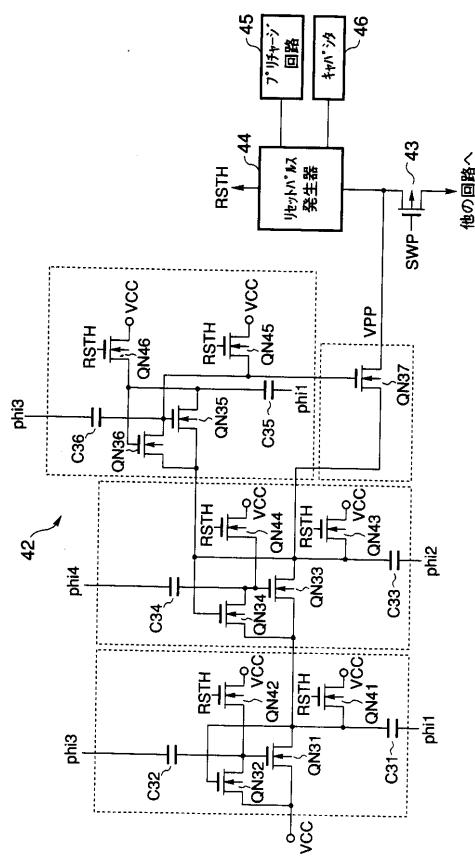

### 【0055】

図7は、上記図6に示した回路における昇圧部42の構成例について説明するための回路図である。この回路は、上記図4に示した回路におけるPチャネル型MOSトランジスタQ P 3 1 ~ Q P 3 7 , Q P 4 1 ~ Q P 4 6に代えてNチャネル型MOSトランジスタQ N 3 1 ~ Q N 3 7 , Q N 4 1 ~ Q N 4 6を設けたものである。そして、上記各MOSトランジスタQ N 4 1 ~ Q N 4 6のゲートには、上記リセット信号発生部41から出力される内部リセット信号RSTHを供給している。また、各リセット用MOSトランジスタQ N 4 1 ~ Q N 4 6の電流通路の一端を接地点に代えて電源VCCに接続している。

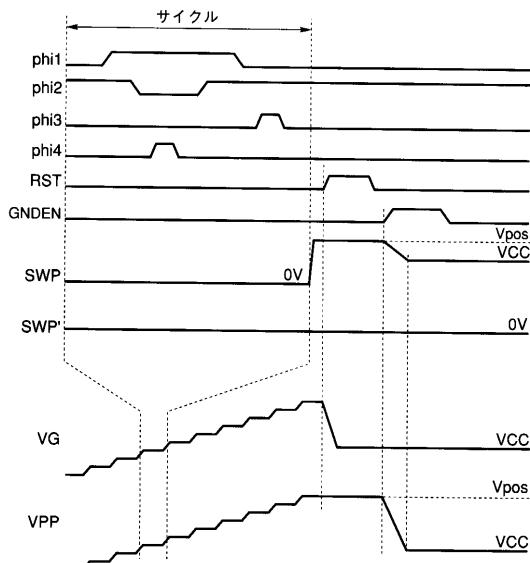

### 【0056】

このような構成であっても、図8のタイミングチャートに示すように、クロック信号p h i 1 , p h i 2 , p h i 3 , p h i 4が入力されると、これらクロック信号の1サイクル毎にMOSトランジスタQ N 3 7のゲート電圧VGと出力電圧VPPが上昇して行く。そして、リセット信号RSTが入力されると、このリセット信号RSTから内部リセット信号RSTHが生成されてリセット用のMOSトランジスタQ N 4 1 ~ Q N 4 6のゲートを駆動し、各MOSトランジスタQ N 3 1 ~ Q N 3 7のゲートを昇圧電圧VPPにする。このとき、スイッチング信号SWPを上記正の昇圧レベルVposにしてトランジスタ部43を遮断する。この時点では、出力電圧VPPは正の昇圧レベルVposを保持している。その後、ディスチャージ信号GNDENがハイレベルとなると、出力電圧VPPとスイッチング信号VposはVCCレベルとなる。

### 【0057】

ここで、リセット信号RSTのタイミングによらず、トランジスタ部43をオンさせる場合には、SWP'に示すように0Vに固定すればよい。

### 【0058】

このように、本実施の形態では、昇圧部42の出力電圧VPPをリセット用のMOSトランジスタQ N 4 1 ~ Q N 4 6のゲートに与えることによって、内部トランジスタのゲートノードをVCCレベルにリセットする。よって、内部トランジスタのゲートノードをVCCレベルから昇圧開始することになるので、0Vにリセットする場合に比べて昇圧に必要な電荷をVCC分減らすことができる。

### 【0059】

#### [第3の実施の形態]

図9は、この発明の第3の実施の形態に係る昇圧回路について説明するためのもので、上記図1に示した第1の実施の形態における昇圧部22の他の構成例を具体的に示している。すなわち、図4に示した回路における各キャパシタC31~C36をそれぞれ直列接続した2個のキャパシタC31-1, C31-2~C36-1, C36-2で構成するとと

10

20

30

40

50

もに、これらキャパシタ C 3 1 - 1 , C 3 1 - 2 ~ C 3 6 - 1 , C 3 6 - 2 の接続ノードと接地点 GND 間にもリセット用の MOS トランジスタ QP100 ~ QP105 を設けたものである。

#### 【 0 0 6 0 】

この第 3 の実施の形態は、次のような点を配慮したものである。すなわち、昇圧回路の内部電圧は、出力電圧よりも高くなる。このため、キャパシタに絶縁膜の厚さが薄いものを用いた場合、内部の最大電圧は絶縁膜の耐圧を超える恐れがある。勿論、十分な耐圧のある厚い絶縁膜のキャパシタを用いることも可能であるが、例えば半導体記憶装置のように薄い絶縁膜を有するキャパシタと同一工程で形成することができず、製造工程が複雑化する。そこで、本実施の形態では、薄い絶縁膜のキャパシタ C 3 1 - 1 , C 3 1 - 2 ~ C 3 6 - 1 , C 3 6 - 2 を直列に接続して用いている。これらのキャパシタ C 3 1 - 1 , C 3 1 - 2 ~ C 3 6 - 1 , C 3 6 - 2 として MOS 型のものを用いると、2つのキャパシタの接続ノードには PN 接合が形成される。この接続ノードは確実にリセットする必要があるが、従来のように電源電圧 VCC レベルの振幅のリセット信号を用いるよりリセットすることができなかった。しかし、昇圧された負電圧 VBB と接地電位間の振幅のリセット信号 RSTHB を用いることにより、これらのキャパシタ C 3 1 - 1 , C 3 1 - 2 ~ C 3 6 - 1 , C 3 6 - 2 の接続ノードを確実にリセットできる。

10

#### 【 0 0 6 1 】

なお、上記図 7 に示した回路における各キャパシタ C 3 1 ~ C 3 6 をそれぞれ直列接続した 2 個のキャパシタで構成するとともに、これらキャパシタの接続ノードと電源 VCC 間にリセット用の MOS トランジスタを設けても良いのは勿論である。

20

#### 【 0 0 6 2 】

上述したように、4 相型電圧発生昇圧回路のリセット信号に昇圧部の出力電圧自身を用いてリセット信号を生成することによって、別の電圧発生回路を用いる必要がなくなり、簡単な論理回路のみで構成できるため、比較的容易に内部トランジスタのゲートノードのリセットを行うことができる。

#### 【 0 0 6 3 】

##### 【 発明の効果 】

以上説明したように、この発明によれば、電荷が残存するトランジスタのゲートノードをリセットする構成であっても、回路規模の増大を抑制できるとともに制御の簡単化も図れる昇圧回路が得られる。

30

##### 【 図面の簡単な説明 】

【 図 1 】この発明の第 1 の実施の形態に係る昇圧回路について説明するためのもので、4 相型負電圧発生昇圧回路を示す回路図。

【 図 2 】図 1 に示した回路の具体的な構成例を示すもので、( a ) 図はハイレベルシフタの構成例、( b ) 図はロウレベルシフタの構成例を示す回路図。

【 図 3 】図 1 に示した回路の具体的な構成例を示すもので、( a ) 図はインバータ回路の構成例、( b ) 図はインバータ回路の他の構成例を示す回路図。

【 図 4 】図 1 に示した回路における昇圧部の構成例について説明するための回路図。

【 図 5 】図 1 乃至図 4 に示した昇圧回路の動作を説明するためのタイミングチャート。

40

【 図 6 】この発明の第 2 の実施の形態に係る昇圧回路について説明するためのもので、4 相型正電圧発生昇圧回路を示す回路図。

【 図 7 】図 6 に示した回路における昇圧部の構成例について説明するための回路図。

【 図 8 】図 6 及び図 7 に示した回路の動作を説明するためのタイミングチャート。

【 図 9 】この発明の第 3 の実施の形態に係る昇圧回路について説明するためのもので、図 1 に示した第 1 の実施の形態における昇圧部の他の構成例を説明するための回路図。

【 図 10 】従来の昇圧回路の構成例を示す回路図。

【 図 11 】図 10 に示した昇圧回路の動作を説明するためのタイミングチャート。

【 図 12 】従来の昇圧回路の他の構成例を示す回路図。

【 図 13 】図 12 に示した昇圧回路の動作を説明するためのタイミングチャート。

50

【図14】従来の昇圧回路の更に他の構成例を示す回路図。

【図15】負電圧を発生する従来の昇圧回路の構成例を示す回路図。

【図16】負電圧を発生する従来の昇圧回路の他の構成例を示す回路図。

【符号の説明】

2 1 , 4 1 ... リセット信号発生部

2 2 , 4 2 ... 昇圧部

2 3 , 4 3 ... パルス発生部

2 4 , 4 4 ... リセットパルス発生器

2 5 , 4 5 ... ディスチャージ回路

2 6 , 4 6 ... キャパシタ

2 7 , 3 3 , 4 7 , 5 0 ... ハイレベルシフタ

2 8 , 3 4 ... ロウレベルシフタ

2 9 ~ 3 1 , 3 5 , 3 6 , 4 8 , 4 9 , 5 1 , 5 2 ... インバータ回路

3 2 , 5 2 ... 電源線

Q P 3 1 ~ Q P 3 7 , Q P 4 1 ~ Q P 4 6 , Q P 5 0 , Q P 6 0 ~ Q P 6 3 , Q P 7 0 ,

Q P 7 1 ... P チャネル型MOSトランジスタ

Q N 3 1 ~ Q N 3 7 , Q N 4 1 ~ Q N 4 6 , Q N 5 0 , Q N 5 1 , Q N 6 0 ~ Q N 6 3 ,

Q N 7 0 ~ Q N 7 2 , Q N 8 0 ... N チャネル型MOSトランジスタ

C 3 1 ~ C 3 6 , C 3 1 - 1 , C 3 1 - 2 ~ C 3 6 - 1 , C 3 6 - 2 ... キャパシタ

p h i 1 ~ p h i 4 ... クロック信号

R S T H , R S T H B ... リセット信号

G N D E N ... ディスチャージ信号

10

20

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

---

フロントページの続き

(72)発明者 丹沢 徹

神奈川県川崎市幸区小向東芝町1番地 株式会社東芝マイクロエレクトロニクスセンター内

審査官 三島木 英宏

(56)参考文献 特開平07-111093(JP,A)

(58)調査した分野(Int.Cl., DB名)

H02M 3/07,

H03K 5/02,

H03K 19/0185