(12)发明专利

(10)授权公告号 CN 105005542 B

(45)授权公告日 2019.01.15

(21)申请号 201510187635.1

(74)专利代理机构 北京戈程知识产权代理有限

(22)申请日 2009.10.05

公司 11314

(65)同一申请的已公布的文献号

代理人 程伟 王锦阳

申请公布号 CN 105005542 A

(51)Int.CI.

(43)申请公布日 2015.10.28

606F 13/40(2006.01)

(30)优先权数据

(56)对比文件

12/245,686 2008.10.03 US

CN 1890653 A, 2007.01.03,

12/340,510 2008.12.19 US

CN 1791868 A, 2006.06.21,

(62)分案原申请数据

CN 1983226 A, 2007.06.20,

200980147694.9 2009.10.05

US 2006/0267993 A1, 2006.11.30,

审查员 李文浩

(73)专利权人 先进微装置公司

地址 美国加利福尼亚州

专利权人 ATI技术无限责任公司

(72)发明人 S·索尔基 S·莫雷因

M·S·格罗斯曼

权利要求书1页 说明书9页 附图6页

(54)发明名称

多处理器架构与方法

(57)摘要

本申请揭露多处理器架构与方法。实施例提供替换使用外部桥集成电路(IC)架构。例如，一实施例多任务周边总线，因而多个处理器可使用一个周边接口槽而不需要外部桥IC。实施例可使用已知的总线协议。

1. 一种多处理器系统,包括:

周边组件总线;以及

多个周边组件,各自通过多个单独的传送/接收 (TX/RX) 道直接耦合至所述周边组件总线,因而所述多个周边组件与所述周边组件总线连接且通讯而作为一周边装置;

其中,所述多个周边组件包括多个处理器;以及

其中,所述多个周边组件更通过单独的传送/接收 (TX/RX) 道直接彼此耦合,且每一个处理器从所述周边组件总线接收数据、将从所述周边组件总线接收的所有数据转送至剩余的处理器。

2. 如权利要求1所述的多处理器系统,其中所述多个周边组件利用地址判断是否接收所述数据。

3. 如权利要求1所述的多处理器系统,其中所述多个处理器包括至少一个是制图处理单元 (GPU) 的处理器。

4. 如权利要求2所述的多处理器系统,其中每一个周边组件用以接收通过所述周边组件总线传送的所有数据,以及决定可应用的数据。

5. 如权利要求1所述的多处理器系统,其中所述周边组件总线包括所述处理器直接耦合的周边组件互连快送总线。

6. 一种计算器可读取的媒体,具有指令储存在所述计算器可读取的媒体上,当在多处理器系统中执行时,造成进行一种方法,所述方法包括:

在多个处理器与周边总线之间通过总线的传送/接收 (TX/RX) 道的单独组通讯总线数据;

在所述多个处理器之间通过未耦合至所述总线的传送/接收 (TX/RX) 道通讯数据;

利用地址判断所述多个处理器的其中一个与所述周边总线通讯;以及

其中,每一个处理器从所述周边总线接收数据、将从所述周边总线接收的所有数据转送至剩余的处理器。

7. 如权利要求6所述的计算器可读取的媒体,其中所述多个处理器包括至少一个制图处理单元 (GPU),以及其中所述周边总线包括所述处理器直接耦合的周边组件互连快送总线,其中所述在所述多个处理器之间通讯数据的步骤是通讯总线数据。

8. 一种多处理器电路,包括:

周边组件连接器,耦合至周边组件总线;

多个周边组件,各自通过多个单独的传送/接收 (TX/RX) 道直接耦合至所述周边组件连接器,其中所述多个周边组件更通过单独的传送/接收 (TX/RX) 道而直接彼此耦合,且每一个周边组件将从所述周边组件连接器接收的所有数据转送至剩余的周边组件;

其中,所述周边组件利用地址决定是否接收所述数据;以及

其中,所述多个周边组件包括至少一个制图处理单元 (GPU)。

9. 如权利要求8所述的多处理器电路,其中,

每一个所述周边组件是以地址为基础被存取;

所述周边组件总线包括所述周边组件直接耦合的周边组件互连快送总线;以及

所述周边组件连接器是周边组件互连快送槽。

## 多处理器架构与方法

[0001] 本申请是申请号为200980147694.9,申请日为2009年10月5日,发明名称为“多处理器架构与方法”的中国专利申请的分案申请。

### 技术领域

[0002] 本申请是关于计算器与其他数字系统中数据转换的领域。

### 背景技术

[0003] 本申请主张2008年10月3日申请的美国申请案12/245,686为优先权案。本申请也主张2008年12月19日申请的美国申请案12/340,510为优先权案,这是美国申请案12/245,686的部分连续案。这两件申请整体内容皆并入本申请作为参考。

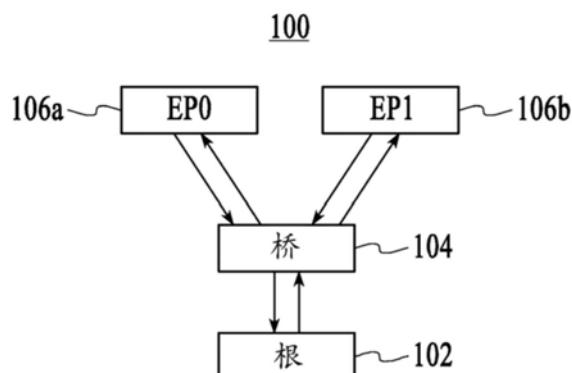

[0004] 随着计算器与其他数字系统变得更复杂与更有能力,在系统成分或组件之间促进数据转换的方法与硬件持续演化。要被转换的数据包含代表数据、指令或是其他信号的信号。在运作非常大数据量应用的系统中,例如制图应用的系统中,数据转换的速度与效率特别关键。在典型系统中,制图处理能力是中心处理单元(CPU)的一部分,或是分别的特殊目的处理器,例如制图处理单元(GPU)与CPU通讯且辅助处理用于例如视频游戏应用的制图数据。可在系统中包含一或多个GPU。在习知多GPU系统中,桥接宿主接口(例如PCI快速(PCIe®)总线)接口必须在点对点(peer to per)交通与宿主交通之间分享带宽。交通主要包括内存数据转换,但通常可包含指令。图1是习知系统100的方块图,包含根(root)102。典型根102试算机芯片组,包含中心处理器(CPU)、宿主桥104以及两个终端EP0 106a与106b。终端是总线终端,以及可以是多种周边组件,例如特殊目的处理器,例如制图处理单元GPU)。根102通过一或多个总线而耦合至桥104,以与周边组件通讯。一些周边组件终端(例如GPUs)由于功能涉及大量数据,所以需要总线上相对大量的带宽。理想是提供较少组件数目的架构,以及在组件之间提供有效率的数据转换。例如,桥集成电路(ICs)的成本相对高。除此之外,典型桥IC的尺寸可和制图处理单元(GPU)相比,制图处理单元需要额外的印刷电路板面积以即可加至层数。桥IC也需要额外的环绕组件,用于电力、带子(straps)、时钟以及可能是只读内存(ROM)。

### 发明内容

[0005] 本发明提供一种系统,所述系统包括周边组件总线;以及多个周边组件,通过多个个别的传送/接收(TX/RX)道直接耦合至所述周边组件总线,因而所述多个周边组件与所述周边组件总线连接且通讯而作为一周边装置;其中,所述多个周边组件包括多个处理器;以及其中,所述多个周边组件更通过个别的传送/接收(TX/RX)道直接彼此耦合,且每一个处理器从所述周边总线接收数据、将从所述周边总线接收的所有数据转送至剩余的处理器。

[0006] 本发明还提供一种计算器可读取的媒体,具有指令储存在所述计算器可读取的媒体上,当在多处理器系统中执行时,造成进行一种方法,所述方法包括在多个处理器与周边总线之间通过总线的传送/接收(TX/RX)道的个别组通讯总线数据;在所述多个处理器之间

通过未耦合至所述总线的传送/接收 (TX/RX) 道通讯数据;利用地址判断所述多个处理器的其中一个与所述周边总线通讯;以及其中,每一个处理器从所述周边总线接收数据、将从所述周边总线接收的所有数据转送至所述处理器。

[0007] 本发明又提供一种电路,包括:周边组件连接器,耦合至周边组件总线;多个周边组件,通过多个个别的传送/接收 (TX/RX) 道直接耦合至所述周边组件连接器,其中所述多个周边组件更通过个别的传送/接收 (TX/RX) 道而直接彼此耦合,且每一个周边组件将从所述周边组间连接器接收的所有数据转送至剩余的周边组件;其中,所述周边组件利用地址决定是否接收所述数据;以及其中,所述多个周边组件包括至少一个制图处理单元 (GPU)。

## 附图说明

- [0008] 图1是具有周边组件的习知处理系统的方块图。

- [0009] 图2是根据实施例,说明具有多任务周边组件的多处理器系统的部分的方块图。

- [0010] 图3是根据实施例,说明具有周边组件的处理系统的部分的方块图。

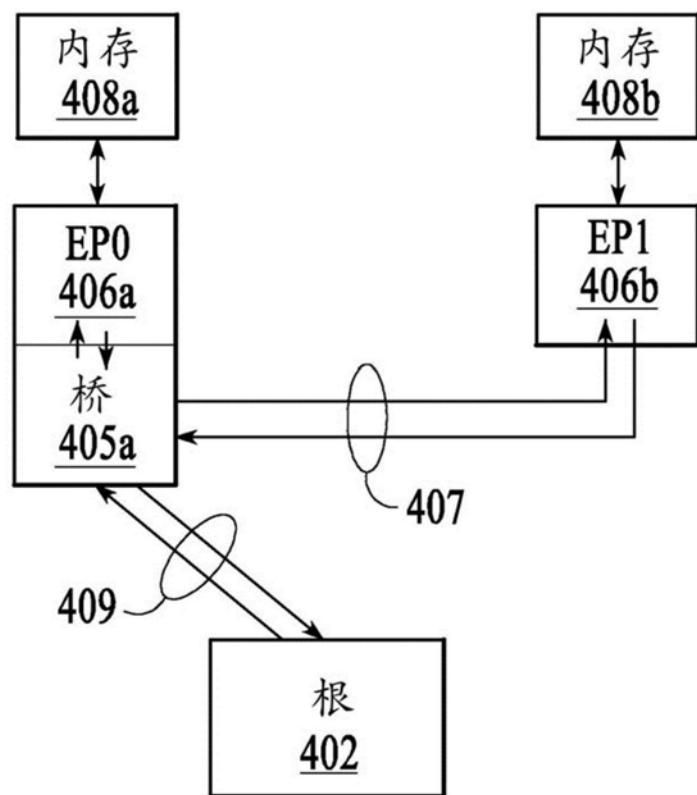

- [0011] 图4是根据实施例,说明具有周边组件的处理系统的更详细方块图。

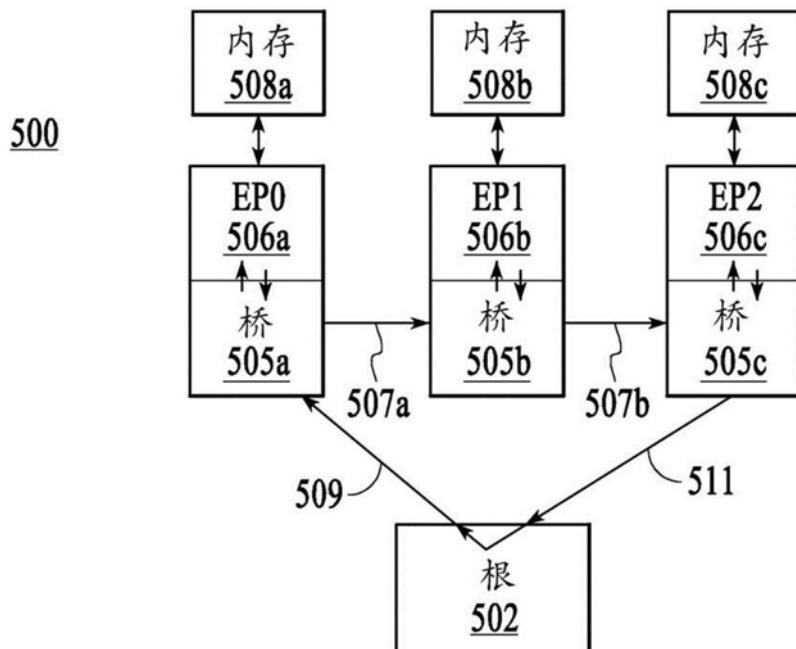

- [0012] 图5是实施例的方块图,其中一总线终点包含内部桥。

- [0013] 图6是实施例的方块图,其包括多于两个总线终点,各总线终点包含内部桥。

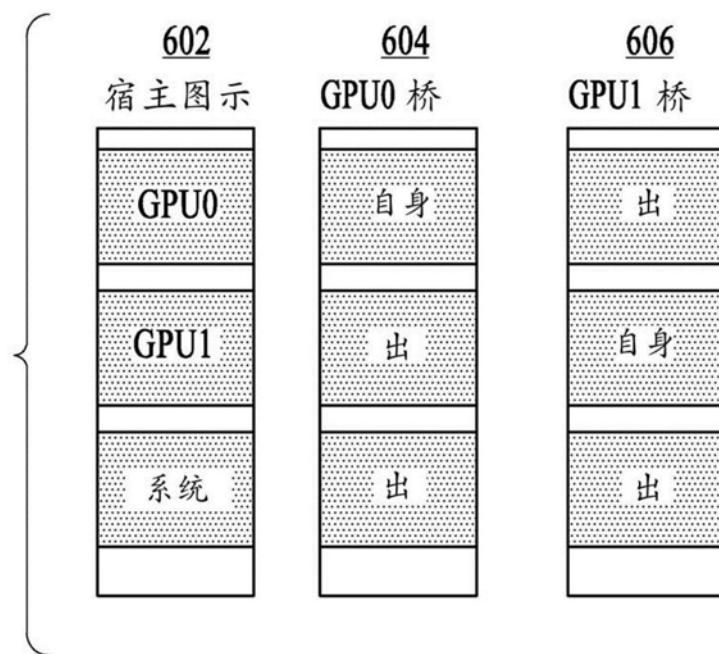

- [0014] 图7是根据实施例,显示总线地址空间架构,从系统中不同组件的透视说明内存空间的方块图。

## 具体实施方式

[0015] 本申请揭露多处理器架构与方法的实施例。实施例提供替代使用外部桥集成电路 (IC) 架构。例如,实施例多任务 (multiplex) 周边总线,因而多处理器可使用一个周边接口槽,而不需要外部桥IC。其他实施例包含系统,所述系统具有多个总线终点通过宿主总线桥而耦合至总线根,所述宿主总线桥是内部连接到至少一个总线终点。除此之外,总线终点直接彼此耦合。实施例可使用已知的总线规则 (bus protocol)。

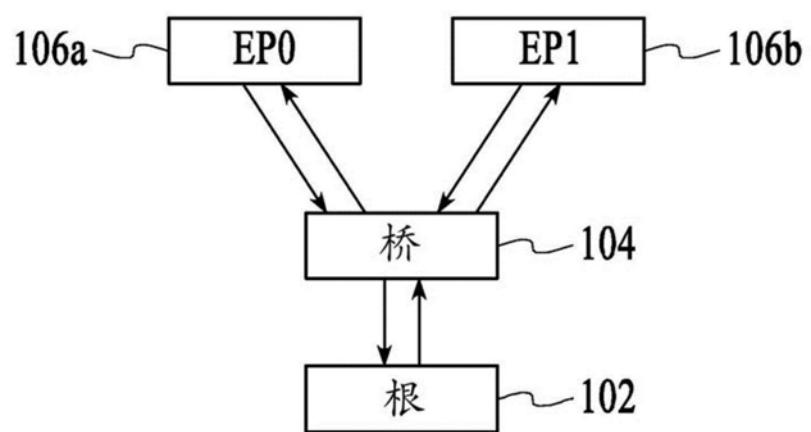

[0016] 图2是根据实施例的示意方块图,说明具有多任务周边组件总线的多处理器系统 700 的部分。在这个范例系统中,有两个GPU、主GPU702A以及从GPU 702B。每一个GPU 702 具有16个周边组件互连快送 (PCIe®) 传送 (TX) 道以及16个PCIe®接收 (RX) 道。每一个GPU 702 包含个别的数据链接层706以及个别的物理层 (PHY) 704。GPU 702A的八个TX/RX道连接至X16 PCIe®连接器一半的TX/RX道或是槽708。GPU 702B的八个TX/RX道连接至X16 PCIe®连接器剩余的TX/RX道或是槽708。GPU 702A与GPU 702B各自的剩余TX/RX道是彼此连接,在GPU 702之间提供直接高速连接。

[0017] PCIe® x16 槽708 (正常连至一个GPU) 分为两个部分,槽的一半是连接至GPU 702A,以及另一半是连接至GPU 702B。每一个GPU 702基本上回响另一个GPU 702的另一半数据。亦即GPU接收的数据会传送至另一个。每一个GPU 702见到PCIe®总线接收的所有数据,每一个GPU 702内部决定是否回答请求或意见。而后每一个GPU 702适当响应或是不做任何事。可使用一些数据或指令,例如“重新启动”用于所有的GPU 702。

[0018] 从系统阶层观点,或是从周边总线的观点,PCIe®总线上只有一个PCIe®负载 (装

置)。GPU 702A或GPU 702B以地址为基础被存取。例如,对于地址区存取(Address Domain Access),主GPU 702A可被分配一半的地址区,以及从GPU 702B可分配到另一半。系统可在主/从模式中运作,或是在单/多GPU模式中操作,以及可用带子(straps)辨识模式。

[0019] 由参考数目辨识不同的数据路径。711是指参考时序(REF CLK)路径。709是指8道RX-2路径。713是指8道RX-1路径。715是指8道TX-1路径。控制信号710是非PCIe®信号,例如带子(straps)。每一个GPU 702中的PHY 704回响数据至适当的道或通道。可以依序完成道连接,帮助优化系设计与/或支持具有少于16道的PCIe®槽。两个GPU显示为系统的范例,但是架构可扩充至n-GPUs。除此之外,GPU 702是周边组件的一个范例,如前所述可被耦合。与周边组件总线正常通讯的任何其他周边组件可同样被耦合。

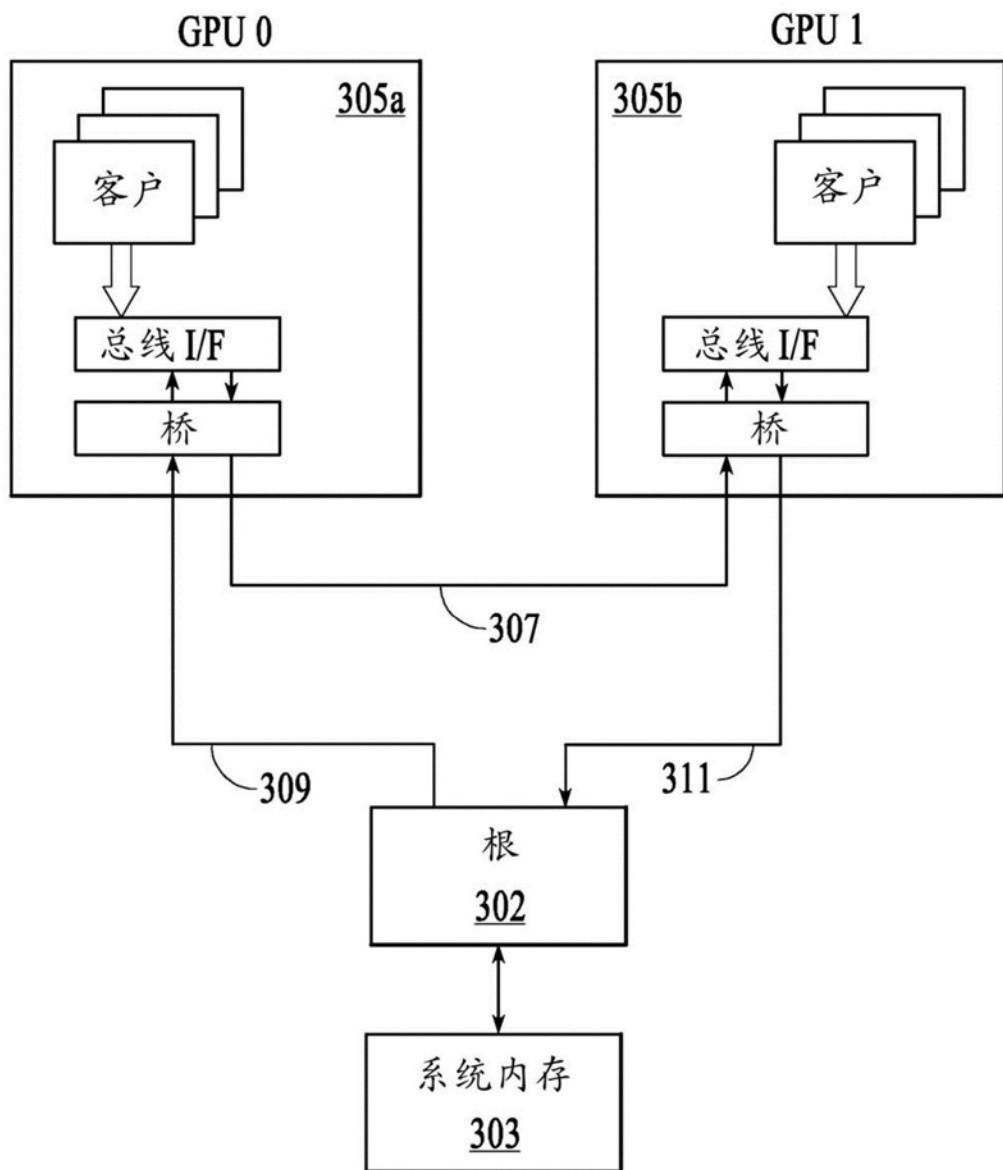

[0020] 图3根据实施例所示的方块图,说明具有周边组件的处理系统200的部分。系统200包含总线根(bus root)202,这与图1的总线根102类似。实施例中的总线根202是包含CPU与系统内存的芯片组。根202通过总线209耦合至包含内部桥205a的终端EP0 206a。实施例中的总线209是PCI快送(PCIe®)总线,但并不受限于此实施例。EP0 206a耦合至另一终端EP1 206b。EP1 206b包含内部桥205b。EP0 205a与EP1 205b通过总线207穿过个别的桥。EP1 206b通过总线211穿过桥205b耦合至根202。终端EP0 206a与EP1 206b各自包含个别的局部内存208a与208b。从个别的根202,209与211分别传送与接收标准双向点对点数据链接的道(lanes)。

[0021] 在实施例中,EP0 206a与EP1 206b是相同的。如以下进一步说明,在不同的实施例中,桥205b并不是必需的,但可被用于达到具有终端版本的目的,例如一种版本的GPU,而不是制造两种不同版本。注意可单独使用EP0,通过总线207与211直接连接至根202。

[0022] 当EP0与EP1存在时,含有桥205会排除需求例如图1桥104的外部桥。相较于图1的“Y”或“T”形成,系统200在回路中移动数据(在这例子中是顺时钟方向)。左终点EP0可直接传送数据至右终点EP1。从EP1返回至EP0的路径是经过根202。因此,根能将来自EP1的数据封包反射回至EP0。换句话说,当架构用于终点对根交易时,提供在相同线对上点对点交易的外观。

[0023] EP0 206a与EP1 206b也可用于习知的架构中。亦即EP0 206a与EP1 206b通过总线209与211各自直接与根202通讯,在此架构中,各自为双向通讯。

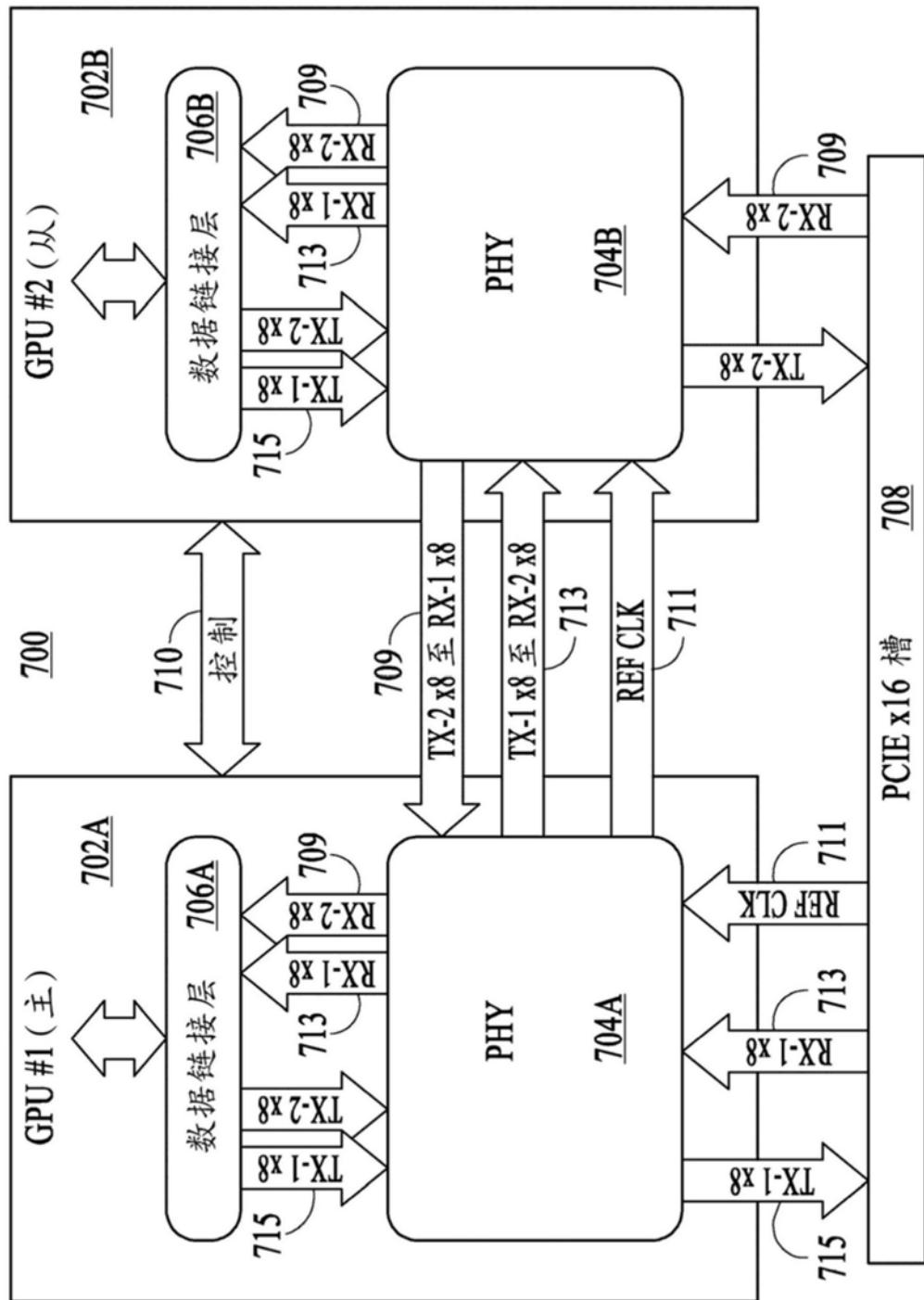

[0024] 图4是根据实施例的更详细方块图,说明具有周边组件的处理系统。系统300类似系统200,但显示更多的细节。系统300包含总线根302耦合至系统内存303。总线根302更通过总线309耦合至终点305a。为了说明特定实施例,终点305a与305b是GPU,但实施例并不受限于GPU。GPU0 305a包含多客户。客户包含逻辑,例如着色器单元(shader unit)与译码器单元,用于执行任务。客户通过总线接口(VF)逻辑耦合至内部桥,控制GPU进行的所有读取操作与存写操作。

[0025] GPU0 305a通过总线307从GPU0 305a的内部桥至GPU1 305b耦合至GPU1 305b。在实施例中,GPUs 305b与GPU0 305a相同,以及包含多客户、内部桥与I/F逻辑。每一个GPU典型连接至局部内存单元,通常是GDDR DRAM。GPU1 305b通过总线311而耦合至总线根302。在实施例中,如箭头所指,例如读取请求与完成的数据与其他信息从总线根302至GPU0 305a至GPU1 305b的顺时钟回路流动。

[0026] 在其他实施例中,GPUs 305其中之一不包含桥。在其他实施例中,数据反时钟方向

流动而不是顺时钟方向流动。

[0027] 在实施例中,决定数据路由的协议图1的架构具有相同的通讯架构。特别地,305b的桥必须呈现在连结307至桥305a作为上游埠,而305a中桥上对应的附接点必须呈现在连结309至根302作为下游埠。再者,当在进入连结上接收所有请求的返回路径时,包埋的桥必须可以知道出发的连结,即使两个链接的实体路由不同。这可由对于每一个GPU设定链模式架构带而达到。如果带设定为零,桥假设传送与接收连结为上游埠,很多任务或是桥装置。如果带设定为一,桥假设菊链(daisy-chain)架构。

[0028] 在另一实施例中,根的点对点桥功能是两步骤工艺,GP1 305b据以存写数据至系统内存303或缓冲。而后当分别操作时,GP0 305a通过总线根302返回读取数据。

[0029] 如果内部桥是外部桥(如图1所示),则总线根302正常响应请求。在实施例中,GP0 305a桥是主动的,而GPU1 305b的桥是作为线路以及简单传送数据。这使得总线根302知道总线309与311是正常的周边互连。当总线根从GPU0 305a读取总线根时,如果数据直接来自于GPU0 305a,则此桥传送数据通过GPU1 305b的桥,以及返回至总线根302。

[0030] 图5是系统400的方块图,其中多个总线终端的其中之一包含内部桥。系统400包含总线根402以及包含桥405a的EP0 406a。EP0 406a耦合至根402通过总线409穿过桥405a,以及耦合至EP1b406b通过总线407穿过桥405a。每一个终点EP0 406a与EP1 406b包含个别的局部内存408a与408b。

[0031] 图6是系统500的方块图,包含超过两个总线终端,各自包含内部桥。系统500包含总线根501,以及含有桥505a与局部内存508a的EP0 506a。系统500更包含具有桥505b与局部内存508b的EP1 506b,以及具有桥505c与内部内存508c的桥505c。

[0032] EP0 506a耦合是根502通过总线509穿过桥505a,以及也耦合至EP1b 506b通过总线507a穿过桥506b。EP0 506b耦合至EP1c 506c通过总线507b穿过桥506c。其他实施例包含加入环状架构的额外终点。在其他实施例中,系统包含超过两个终点506,但是最右边的终点不包含内部桥。在其他实施例中,数据流是反时钟方向,如图所示。

[0033] 请再次参阅图4,根据实施例,内部桥上有两个逻辑端口。一埠是在GPU0 305a的桥中“开启”,以及一埠是在GPU1 305b的桥中“关闭”。总线根302可在总线309上传送请求而进行存写操作。标准地址方案是指桥传送请求至总线I/F。如果是对于GPU1 305b请求,桥把请求导引至总线307。因此,在实施例中,GP0 305a与GP1 305b的个别内部桥编程不同。

[0034] 图7的方块图说明总线地址范围的分配以及从不同组件的内存空间概示。同时也参阅图4,602是说明总线根或是宿主处理器302的内存。604是说明GP0 305a内部桥的内存。606是说明GP1 305b内部桥的内存。总线地址范围分割范围给GP0 305a、GP1 305b与系统302内存空间。设定GP0 305a桥,因而进入到GP0 305a范围的请求被导引到自身的局部内存。来自根或来自GP0 305a进入GP1 305b或系统302的请求被导引到GP0 305a的输出埠。GP1 305b设定稍有不同,因此进入到GP1 305b范围的请求被导引到自身的局部内存。从GP0 305a或是从GP1 305b到根或是GP0 305a范围的请求被导引到GP1 305b的输出埠。

[0035] 宿主知道总线像图1所示。GP1 05b可通过桥而向宿主处理器302制造请求,以及请求会传送到宿主处理器302。当宿主处理器302返回请求时,会通过GP0 305a的桥,具有逻辑用来决定请求与数据被导引到何处。

[0036] 可在两种路径中进行从GP1 305b至GP0 305a的存写操作。GP1 305b传送数据至

系统内存303中的内存位置。而后, GPU0 305a在学习到数据在系统内存303中之后, GPU0 305a读取数据。

[0037] 读取数据请求其他分割交易操作的完成信息必须沿着和请求相同方向的线路旅行。因此,除了上述地址基础的请求路由之外,装置基础的路由必须用类似的方式设定。例如, GPU0 305a的内部桥辨识请求与完成信息的路径是通过总线307。

[0038] 实施例包含电力管理,改善高负载使用例子中的电力使用。例如,在具有一点制图处理的使用例子中, GPU1 305b的逻辑电力关闭,以及GPU1 305b中的桥功能减少到从输入端口至输出端口的简单通过功能。再者, GPU0 305a的功能减少,不处理从输入埠路由至输出埠的转换。在实施例中,有个别的电力供应用于GPU1 305b的桥功能。软件侦测电力降低的条件。实施例包含用于桥的个别电力调节器与/或个别内部电源,分别从装置的剩余逻辑调降电力。

[0039] 即使在不包含上述电力管理的实施例中,由于不需要外部桥(如图1所示),所以保留系统板面积。保留了外部桥所需要的板面积与电力以及它的接脚。另一方面,不需要每一个GPU具有自己的内部桥。在另一实施例中, GPU1 305b不具有内部桥,如图5所示。

[0040] 在包含用于加法电路板 (add-in circuit board) 多槽的系统中,实施系统300的架构。或者,系统300是焊接的系统 (soldered system),例如在移动装置上。

[0041] 总线307、309与311可以是PCIe®总线或是任何其他的类似周边互连总线。

[0042] 本申请描述的任何电路实施可通过控制制造工艺与屏蔽工作,而后用于制造相关电路。对熟知此技艺的人士熟知这些制造工艺控制与屏蔽工作产生,包含储存计算器指令在计算器可读取的媒体,包含例如Verilog、VHDL或是其他硬件描述语言的指令。

[0043] 本申请的实施例包含系统,所述系统包括:周边组件连接器耦合至周边组件总线;以及多个周边组件通过多个个别传送/接收 (TX/RX) 道而直接耦合至周边组件连接器,因而多个周边组件出现在周边组件总线,成为一个周边装置耦合至周边组件连接器。

[0044] 在实施例中,多个周边组件通过个别的传送/接收 (TX/RX) 道而进一步直接彼此耦合。

[0045] 在实施例中,多个周边组件的至少一个是制图处理单元 (GPU)。

[0046] 在实施例中,周边组件连接器是周边组件互连快送 (PCIe®) 槽,以及其中周边组件总线是PCIe®总线。

[0047] 在实施例中,每一个周边组件是用以接收通过周边组件连接器传送的所有数据,以及决定可使用的数据。

[0048] 在实施例中,每一个周边组件将接收的所有数据转送至剩余的周边组件。

[0049] 在实施例中,以地址为基础,存取每一个周边组件。

[0050] 本申请的实施例包含多处理器方法,所述方法包括通过总线的个别传送/接收 (TX/RX) 道组,耦合多个处理器至周边总线;耦合所述多个处理器至未耦合到总线的所述多个处理器的彼此TX/RX道,从所述总线直接传送数据至所述多个处理器,其中所述多个处理器的每一个处理器是可定地址的;以及在处理器之间直接传送数据。

[0051] 在实施例中,所述多个处理器包括制图处理单元 (GPU)。

[0052] 在实施例中,所述多个处理器包括多个GPU,以及其中所述周边总线包括周边组件

互连快送(PCIe®)总线,所述GPU直接耦合至所述周边组件互连快送(PCIe®)总线。

[0053] 在实施例中,更包括通过个别的TX/RX道,耦合所述GPU直接比次通讯。

[0054] 在实施例中,更包括GPU从所述总线接收数据,以及传送所述数据至另一个GPU。

[0055] 本申请的实施利包含计算器可读取媒体,储存计算器可读取指令,用以制造电路,所述电路包括周边组件连接器耦合至周边组件总线;以及多个周边组件通过多个个别的传送/接收(TX/RX)道而直接耦合至所述周边组件连接器,因而所述多个周边组件出现在所述周边组件总线,成为一周边装置耦合至所述周边组件连接器,其中所述多个周边组件更通过个别的传输/接收(TX/RX)道而直接彼此耦合。

[0056] 在实施例中,所述指令包括硬件描述语言指令。

[0057] 本申请的实施利包含计算可读取的媒体,具有指令储存于其中,当在多处理器系统中执行时,造成进行一方法,所述方法包括:耦合多个处理器至周边总线,通过所述总线的各组传送/接收(TX/RX)道;耦合所述多个处理器至未连接到所述总线的所述多个处理器的彼此TX/RX道;传送数据至所述多个处理器,从所述总线直接至所述多个处理器,其中所述多个处理器的每一个处理器是可定地址的;以及在处理器之间直接传送数据。

[0058] 在实施例中,所述多个处理器包括制图处理单元(GPU)。

[0059] 在实施例中,所述多个处理器包括多个GPU,以及其中所述周边总线包括周边组件互连快送(PCIe®)总线,所述GPU直接耦合至周边组件互连快送(PCIe®)总线。

[0060] 在实施例中,所述方法更包括耦合GPU通过个别TX/RX道而直接彼此通讯。

[0061] 在实施例中,所述方法更包括GPU从总线接收数据以及传送所述数据至另一个GPU。

[0062] 本申请的实施利包含系统,所述系统包括总线根,总线根包括中心处理单元用以通过组线而与周边组件通讯;以及第一周边组件直接耦合至组线根以及更直接耦合至第二周边组件,所述第一周边组件包括内部桥,用以接收数据与传送数据,其中接收与传送包括所述第一周边组件与所述第二周边组件之间的直接通讯。

[0063] 在实施例中,所述第一周边组件与所述第二周边组件各自用于与所述总线根直接通讯,以传送与接收数据。

[0064] 在实施例中,接收与传送更包括通过所述总线根,从所述第二周边组件传送请求与数据至所述第一周边组件。

[0065] 在实施例中,接收与传送更包括从所述第一周边组件传送请求或数据至所述第二周边组件,通过所述第一周边组件的内部桥至第二周边组件。

[0066] 在实施例中,总线根用以进行存写操作,其中存写操作至所述第二周边组件包括所述总线根传送存写请求至所述第一周边组件的内部桥,以及所述第一周边组件的内部桥直接传送所述存写请求至所述第二周边组件。

[0067] 在实施例中,所述第二周边组件的内部总线接口接收所述存写请求。

[0068] 在实施例中,总线根用以进行存写操作,其中存写操作至所述第一周边组件包括所述总线根传送存写请求至所述桥,以及所述桥传送所述存写请求至所述第一周边组件的内部总线接口。

[0069] 在实施例中,所述总线根用以进行读取操作,其中读取操作至所述第一周边组件包括所述总线根传送读取请求至所述桥,以及所述桥传送所述读取请求至所述第一周边组

件的内部总线接口。

[0070] 在实施例中,总线根用以进行读取操作,其中读取操作至所述第二周边组件包括所述总线根传送读取请求至所述桥,以及所述桥直接传送所述读取请求至所述第二周边组件。

[0071] 在实施例中,所述桥包括逻辑用以决定对于所接收存写请求、所接收读取请求与所接收数据的路由。

[0072] 在实施例中,所述第二周边组件包括内部桥,用以接收数据与传送数据,以及当所述内部桥不用接收数据与传送数据时,所述第二周边组件更用已被下降电力。

[0073] 在实施例中,所述第二周边组件更包括用于使用内部桥的电源。

[0074] 在实施例中,所述第一周边组件与所述第二周边组件各包括制图处理单元(GPU)。

[0075] 在实施例中,所述第一周边组件与所述第二周边组件各自更包括多个客户耦合至个别总线接口,其中所述客户包括视频处理逻辑,所述视频处理逻辑包括shader units与编码器/译码器单元。

[0076] 本申请的实施例包含在多处理器系统中通讯的方法,所述方法包括总线根直接传送请求至第一周边组件,其中所述请求包括读取请求与存写请求,所述第一周边组件通过所述第一周边组件的内部桥中的第一总线而接收所述请求;以及所述内部桥决定所述请求的适当路由,其中适当路由包括针对第二周边组件的路由请求,通过第二总线直接从所述桥至所述第二周边组件的总线接口;以及针对第一周边组件的路由请求至所述第一周边组件的总线接口。

[0077] 在实施例中,更包括所述第二组件,通过第三总线直接传送数据至所述总线根,响应读取请求。

[0078] 在实施例中,更包括第二周边组件接收所述第二周边组件的内部桥中的请求。

[0079] 在实施例中,更包括所述第一周边组件通过所述第二总线传送读取请求至所述第二周边组件,所述第二周边组件传送数据,通过所述第三总线,响应所述读取请求至所述总线根,以及所述总线根通过所述第一总线传送所述数据至所述桥。

[0080] 本申请的实施例包含计算器可读取的媒体,具有储存的指令,当在多处理系统中执行时,造成进行通讯方法,所述方法包括:总线根直接传送请求至第一周边组件,其中所述请求包括读取请求与存写请求,所述第一周边组件通过所述第一周边组件的内部桥中第一总线而接收请求;以及所述内部桥决定所述请求的适当路由,其中适当路由包括针对第二周边组件的路由请求,通过第二总线从所述桥直接至所述第二周边组件的总线接口;以及针对第一周边组件的路由请求,至所述第一周边组件的总线接口。

[0081] 在实施例中,所述方法更包括第二组件,通过第三总线,直接传送数据至所述总线根,响应读取请求。

[0082] 在实施例中,所述方法更包括第二周边组件接收所述第二周边组件的内部桥中的请求。

[0083] 在实施例中,所述方法更包括:所述第一周边组件通过所述第二总线而传送读取请求至所述第二周边组件;所述第二周边组件通过所述第三总线传送数据至所述总线根,响应读取请求;以及所述总线根通过所述第一总线传送所述数据至所述桥。

[0084] 在实施例中,所述指令包括硬件描述语言指令,用来产生应用特定集成电路

(ASIC) ,进行所述方法。

[0085] 上述的实施例可被实施成为编程在任何一种电路的功能,包含但不限于可编程的逻辑设备 (PLDs) ,例如场可编程的栅数组 (FPGAs) 、可编程的数组逻辑 (PAL) 装置、电性可编程的逻辑与内存装置,以及标准的胞元基础装置,以及应用特定集成电路 (ASICs) 与完全客制集成电路。实施实施例的一些其他可能性包含具有内存 (例如电性可消除的可编程的只读内存 (EEPROM) 、快闪内存等) 微控制器、包埋的微控制器、韧件、软件等。再者,实施例可包埋在微处理器中,所述微处理器具有软件为基础的电路仿真、分离逻辑 (序列的或组合的) 、客户装置、模糊 (神经) 逻辑、量子装置以及上述任何装置型式的组合。当然可提供以下装置技术在不同的组件型式中,例如金属氧化物半导体场效晶体管 (MOSFET) 技术,例如互补金属氧化物半导体 (CMOS) 、二极技术,例如发射器耦合逻辑 (ECL) 、聚合物技术 (例如硅接合的聚合物与金属接合的聚合物-金属结构) 、混合的模拟与数字等。

[0086] 本申请说明书与权利要求书中使用的“处理器”一词包含处理器核心或是处理器的一部分。再者,虽然一或多个GPU以及一或多个CPU通常在本申请是分别指示,但是在实施例中, GPU与CPU皆可包含在单一集成电路封包或是单一单晶粒 (monolithic die) 。因此,单一装置在实施例中进行所主张的方法。

[0087] 除非内容清楚要求,否则整个说明书与权利要求书中,“包括”与类似用词解读为包含的意思,相对于排除或消耗的意思;也就是“包含但不限于”的意思。单数或复数的用词也分别包含复数或单数。除此之外,本申请中“此处”、“以下”、“上方”、“下方”以及类似用词是指本申请整体而不是本申请的任何特定部分。当“或”一字用于参考两个或多个项目时,这个字涵盖这个字所有的下列解释、表列项目的任一个、表列项目的全部以及表列项目的任何组合。

[0088] 所述方法与系统的上述实施例描述不用于排除或限制本发明成为特定形式。虽然本案描述的方法与系统的特定实施例与范例是为了说明本发明,熟知此技艺的人士应理解在本发明范围内不同的均等修饰是可能的。本申请揭露内容的教导可用于其他系统,不只适用于上述包含制图处理或视频处理的系统。可在许多不同架构中,进行上述不同操作,分不可不同于以上所述。除此之外,虽然本申请描述许多架构,但都不是用来限制本申请。

[0089] 在其他实施例中,本申请所描述的一些或全部硬件与软件功能可存在打印机、相机、电视、数字多功能碟 (DVD) 播放器、DVR或PVR、手持装置、移动电话或其他装置。可结合上述的组件与不同实施例的作用,用来提供其他实施例。根据上述详细说明,可对所述方法与系统制造这些与其他改变。

[0090] 一般而言,在权利要求书中,用语不应解读为对所述方法与系统限制于说明书与权利要求书中揭露的特定实施例,而是应解读为包含在权利要求下操作的任何处理系统与方法。因此,所述方法与系统不受限于揭露内容,所述方法与系统的范围是由权利要求书决定。

[0091] 虽然所述方法与系统呈现为权利要求形式,发明人在权利要求形式中考虑不同面向的所述方法与系统。例如,虽然所述方法与系统仅有一方面是主张在计算器可读取媒体中实施,但是其他方面也可以在计算器可读取媒体中实施。此计算器可读取媒体可由计算装置 (例如个人计算器、个人数字助理、PVR、移动装置或类似物) 执行的储存指令,或是可为执行时设计用来产生装置 (GPU、ASIC或类似物) 的指令,或是软件应用,操作时进行上述内

容。本申请主张的发明可实施在计算器码(例如HDL、Verilog等),它的产生、储存、合成与使用是用来产生GDSII数据(或是它的均等物)。而后可在此数据基础上,制造ASIC。

[0092] 因此,发明人保留权利在申请本案之后可增加额外的权利要求,追求所述方法与系统其他的权利要求形式。

100

图1

图2

200

1

图3

300

图4

400

图5

图6

图7