#### (12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

### (19) World Intellectual Property Organization

International Bureau

(43) International Publication Date

21 March 2013 (21.03.2013)

(10) International Publication Number WO 2013/039957 A2

(51) International Patent Classification: H05K 3/10 (2006.01) **G01R 1/073** (2006.01) H05K 1/11 (2006.01)

(21) International Application Number:

PCT/US2012/054736

(22) International Filing Date:

12 September 2012 (12.09.2012)

(25) Filing Language:

English

(26) Publication Language:

English

(30) Priority Data: 61/535,812 16 September 2011 (16.09.2011)

US 13/610,076 11 September 2012 (11.09.2012) US

(71) Applicant (for all designated States except US): CAS-CADE MICROTECH, INC. [US/US]; 9100 SW Gemini Drive, Beaverton, OR 97008 (US).

(72) Inventors; and

- (75) Inventors/Applicants (for US only): DUCKWORTH, Koby L. [US/US]; 4712 Masters Drive, Newberg, OR 97132 (US). HILL, Eric [US/US]; 8207 SW Terwilliger Boulevard, Portland, OR 97219 (US). JOLLEY, Mike [US/US]; 14325 SW Stallion Drive, Beaverton, OR 97008 (US). SCHULTZ, Kurt [US/US]; 46975 NW Chrysler Drive, Banks, OR 97106 (US). CURTIS, Jody [US/US]; 109400 SW Barnes Road, #230, Portland, OR 97225 (US).

- Agent: D'ASCENZO, David S.; Dascenzo Intellectual Property Law, P.C., 522 SW 5th Avenue, Suite 925, Portland, OR 97204 (US).

- (81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BN, BR, BW, BY, BZ, CA, CH, CL, CN, CO, CR, CU, CZ, DE, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IS, JP, KE, KG, KM, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LT, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PA, PE, PG, PH, PL, PT, QA, RO, RS, RU, RW, SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TH, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

- (84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH,

[Continued on next page]

(54) Title: RISERS INCLUDING A PLURALITY OF HIGH ASPECT RATIO ELECTRICAL CONDUITS AND SYSTEMS AND METHODS OF MANUFACTURE AND USE THEREOF

(57) Abstract: Risers including a plurality of high aspect ratio electrical conduits, as well as systems and methods of manufacture and/or use of the risers and/or the high aspect ratio electrical conduits. The systems and methods may include incorporation of the plurality of high aspect ratio electrical conduits within a substantially planar- body that may include and/or be formed from a solid dielectric material. The plurality of electrical conduits may be configured to conduct a plurality of electric currents between a first surface of the body and a second, substantially opposed, surface of the body. The surfaces may include a plurality of contact pads configured to provide a robust and/or corrosion-resistant surface and/or to improve electrical contact between the riser and another device. The risers also may include a layered structure, wherein the layers are sequentially formed to increase a thickness of the riser and/or the aspect ratio of the electrical conduits.

##

GM, KE, LR, LS, MW, MZ, NA, RW, SD, SL, SZ, TZ, Declarations under Rule 4.17: UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, RU, TJ, TM), European (AL, AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MK, MT, NL, NO, PL, PT, RO, RS, SE, SI, SK, SM, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

of inventorship (Rule 4.17(iv))

#### Published:

without international search report and to be republished upon receipt of that report (Rule 48.2(g))

# RISERS INCLUDING A PLURALITY OF HIGH ASPECT RATIO ELECTRICAL CONDUITS AND SYSTEMS AND METHODS OF MANUFACTURE AND USE THEREOF

#### Related Application

The present application claims priority to U.S. Patent Application Serial No. 13/610,076, which was filed on September 11, 2012, and to U.S. Provisional Patent Application Serial No. 61/535,812, which was filed on September 16, 2011, and the complete disclosures of which are hereby incorporated by reference.

5

10

15

20

25

30

35

#### Field of the Disclosure

The present disclosure is directed generally to risers that include a plurality of high aspect ratio electric conduits that may transfer a plurality of electric currents between a first side of the riser and a second side of the riser, systems that include the risers, and methods of manufacturing and/or using the risers.

#### Background of the Disclosure

The size of discrete circuit elements present on an electronic device, such as an integrated circuit device, continues to decrease. In addition, the number of bond and/or test pads that may be present on an individual die is increasing, leading to smaller and smaller pitches (i.e., distances) between adjacent pads, as well as smaller lengths, widths, and/or surface areas for individual pads. These changes represent significant challenges for manufacturing, testing, and/or packaging of the electronic devices due to the precise nature of the manufacturing steps that may be needed to physically define and/or spatially align the various layers present within the electronic devices, to contact the electronic devices with test probes during testing, and/or to assemble the electronic devices within a package.

In addition, the length of vertical interconnects, which are present within the electronic devices and/or within test structures and/or assembly structures that may be configured to electrically contact the electronic devices, continues to increase. Vertical interconnects also may be referred to herein as contacts, vias, and/or electrical conduits. This increase in vertical interconnect length, coupled with the decrease in pad pitch and a decrease in vertical interconnect cross-sectional area that may be needed to accommodate the decreased pitch, may produce a need for high aspect ratio (A/R) vertical interconnects, in which the length of the vertical interconnect is much greater than a characteristic cross-sectional dimension.

Current manufacturing technologies may provide for horizontal interconnects, such as horizontal metal lines that may be utilized in the backend architecture of electronic devices, that may include large aspect ratios. However, these horizontal metal wires are created using

manufacturing processes that may provide for lithographically defining an entire length of the horizontal interconnect.

In contrast, current manufacturing technologies typically define vertical interconnects by lithographically defining their cross-sectional area and then using one or more etch process to define the length of the vertical interconnect (either by defining a void in a dielectric material into which the vertical interconnect may be deposited or by defining the vertical interconnect itself). The etch process may be followed by one or more deposition processes, which may deposit either a dielectric material around an already defined vertical interconnect or may deposit the vertical interconnect within the already defined void. While these manufacturing technologies may provide for the creation of vertical interconnects with relatively smaller aspect ratios, inherent limitations of both the etch and the deposition processes may preclude their use to produce high aspect ratio vertical interconnects.

5

10

15

20

High aspect ratio vertical interconnects may be utilized in a variety of processes and/or architectures. As an illustrative, non-exclusive example, a riser, or spacer, present within a probe head that may be utilized for testing of an electronic device may include a thickness and vertical interconnect pitch that falls in the high aspect ratio regime. As another illustrative, non-exclusive example, through silicon vias, which may be utilized to electrically connect an electronic device that is present on a first side of a substrate with a pad and/or an electronic device that is present on a second, substantially opposed, side of the substrate, may include and/or be high aspect ratio vertical interconnects. Thus, there exists a need for high aspect ratio vertical interconnects, as well as for systems and methods of manufacture and use thereof.

#### Summary of the Disclosure

Risers including a plurality of high aspect ratio electrical conduits, as well as systems and methods of manufacture and/or use of the risers and/or the high aspect ratio electrical conduits. The systems and methods may include incorporation of the plurality of high aspect ratio electrical conduits within a substantially planar body that may include and/or be formed from a solid dielectric material. The plurality of electrical conduits may be configured to conduct a plurality of electric currents between a first surface of the body and a second, substantially opposed, surface of the body. The surfaces may include a plurality of contact pads that are configured to provide a robust and/or corrosion-resistant surface and/or to improve electrical contact between the riser and another device. The risers also may include a layered structure, in which the layers are formed sequentially to increase a thickness of the riser and/or the aspect ratio of the electrical conduits.

5

10

15

20

In some embodiments, the plurality of electrical conduits may be formed prior to the body. In some embodiments, the plurality of electrical conduits may be formed and/or placed within a plurality of voids formed within the body. In some embodiments, the plurality of electrical conduits may be formed in the body. In some embodiments, the plurality of electrical conduits includes a plurality of metallic bump pads that are stacked on top of one another to form a stack of metallic bump pads. In some embodiments, the plurality of electrical conduits includes a plurality of metallic wires. In some embodiments, the plurality of electrical conduits includes a plurality of deposited electrical conduits. In some embodiments, the plurality of electrical conduits includes a conductivity-enhancing material that is incorporated into the dielectric material.

#### Brief Description of the Drawings

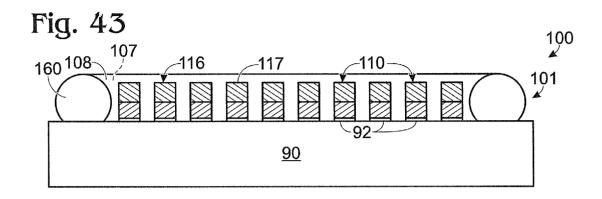

Fig. 1 is a schematic representation of illustrative, non-exclusive examples of a test system that includes a probe head assembly that may include a device under test riser according to the present disclosure.

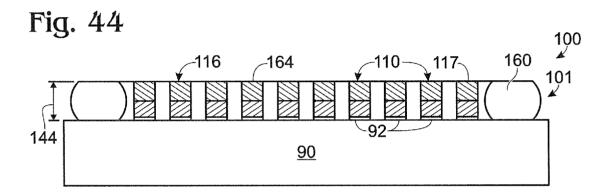

- Fig. 2 is a schematic representation of an illustrative, non-exclusive example of a portion of a probe head assembly that includes a device under test riser according to the present disclosure.

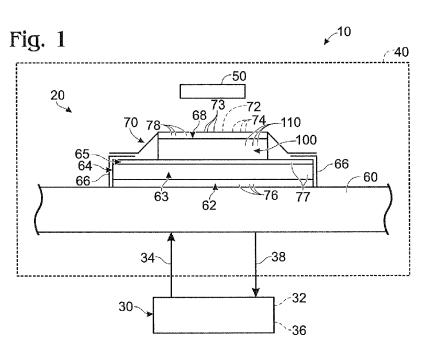

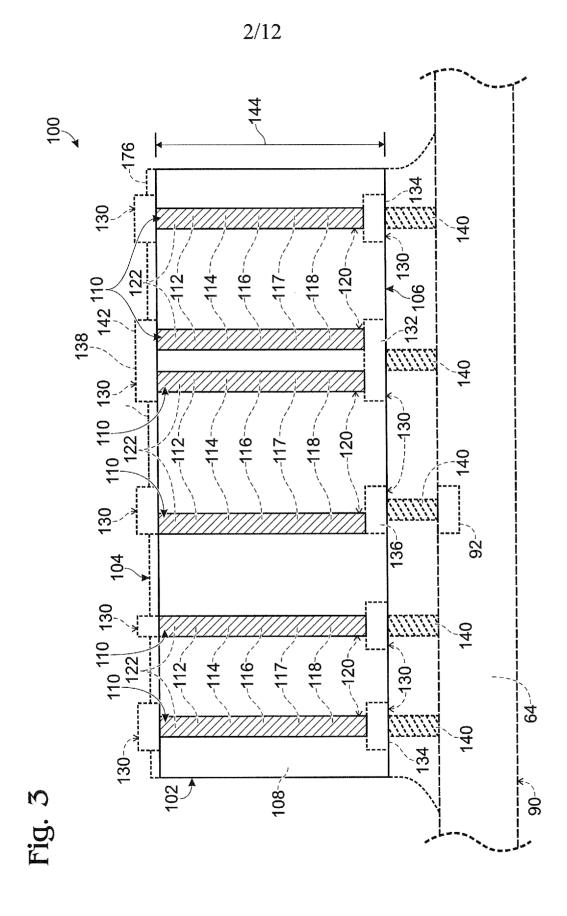

- Fig. 3 is a schematic representation of illustrative, non-exclusive examples of a device under test riser according to the present disclosure that may be operatively attached to a substrate.

10

25

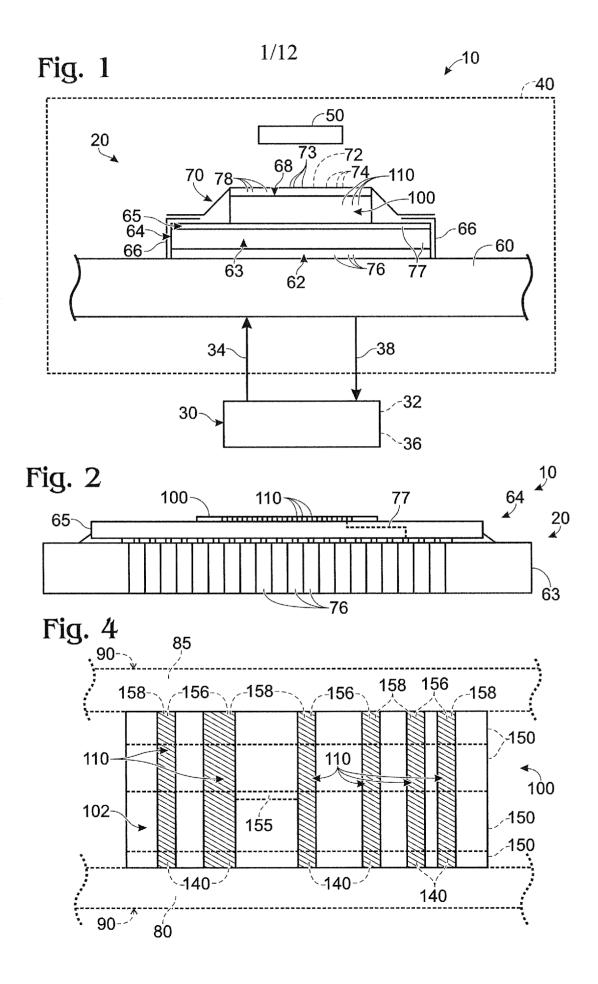

- Fig. 4 is a schematic representation of illustrative, non-exclusive examples of a device under test riser according to the present disclosure that may be formed on a substrate.

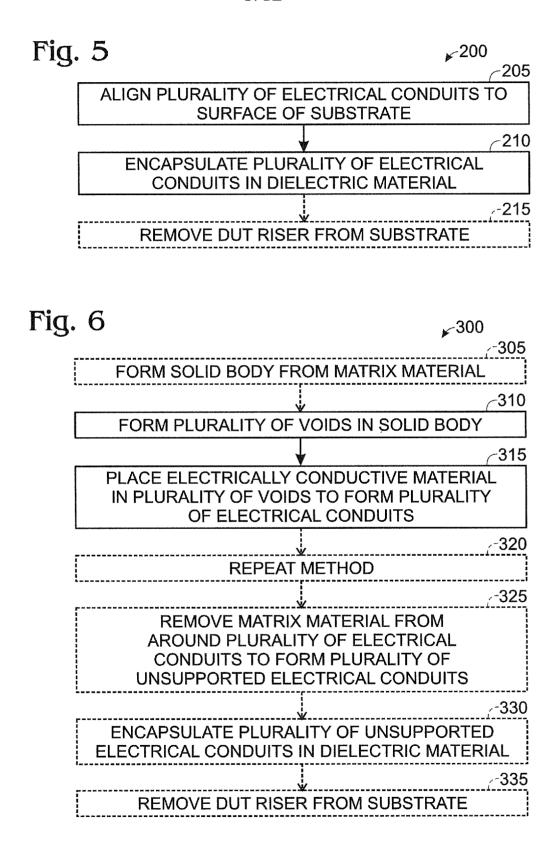

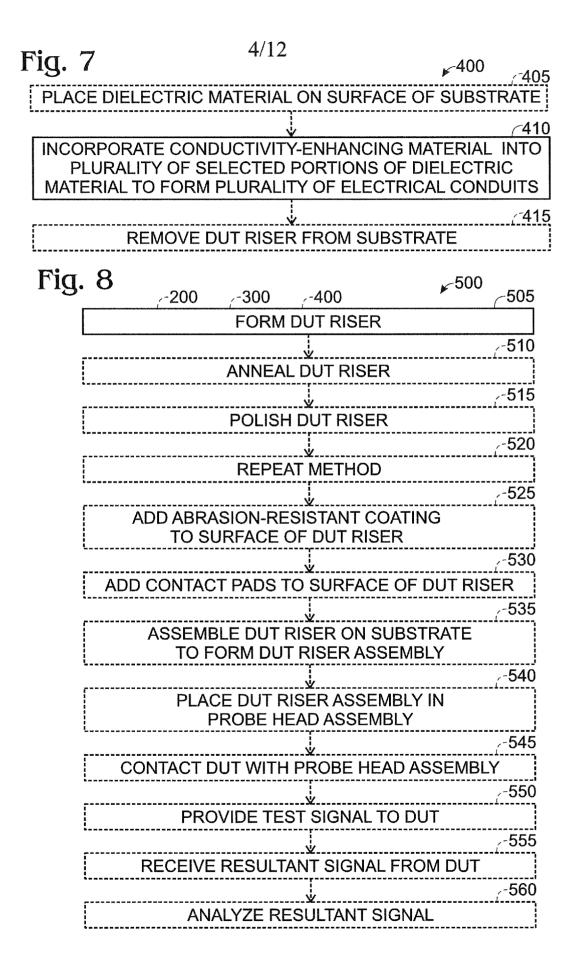

- Fig. 5 is a flowchart depicting methods of forming a device under test riser according to the present disclosure.

- Fig. 6 is another flowchart depicting methods of forming a device under test riser according to the present disclosure.

- Fig. 7 is another flowchart depicting methods of forming a device under test riser according to the present disclosure.

- Fig. 8 is a flowchart depicting illustrative, non-exclusive examples of methods of forming and/or using device under test risers according to the present disclosure.

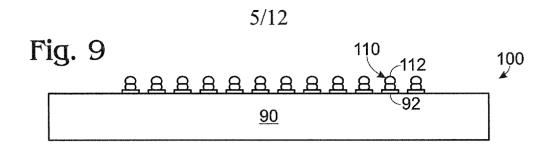

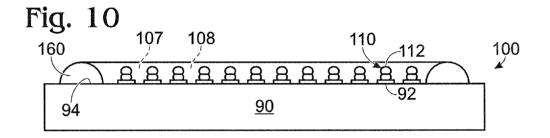

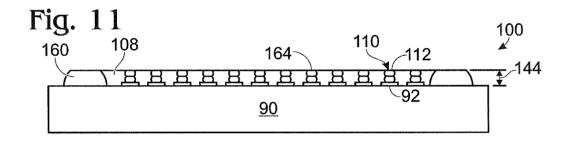

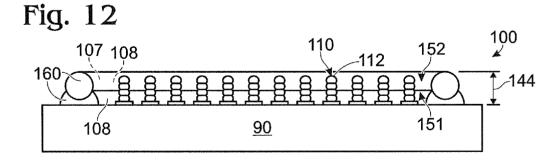

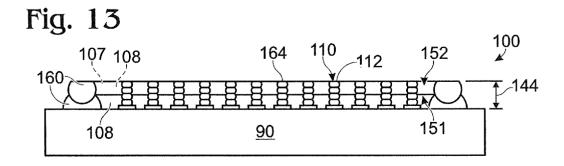

- Figs. 9-13 are schematic representations of process flows that may be utilized to create a device under test riser according to the present disclosure that includes a plurality of metallic bump pads.

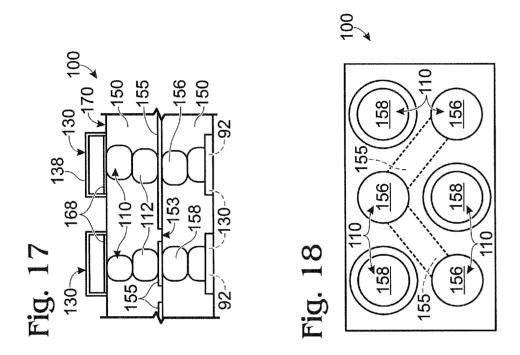

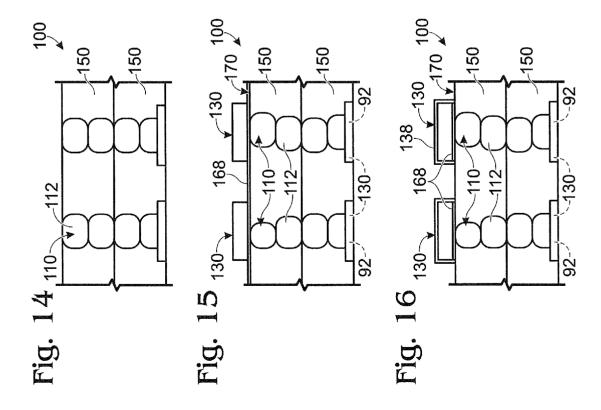

- Figs. 14-16 are schematic representations of process flows that may be utilized to produce a contact pad on device under test risers according to the present disclosure.

- Figs. 17-18 are schematic representations of illustrative, non-exclusive examples of device under test risers that include one or more passive electronic components according to the present disclosure.

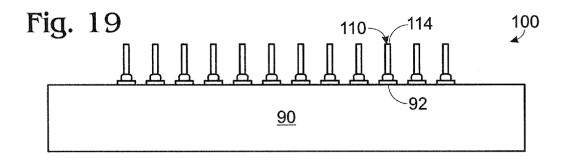

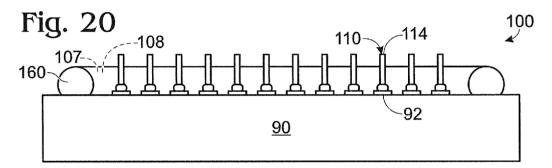

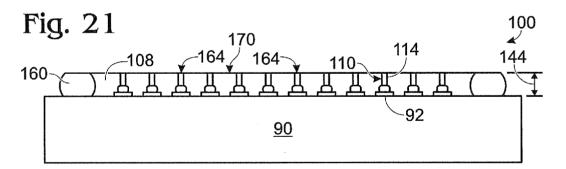

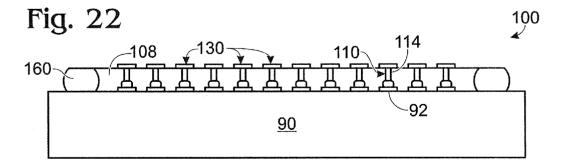

- Figs. 19-22 are schematic representations of illustrative, non-exclusive examples of process flows that may be utilized to create a device under test riser according to the present disclosure that includes a plurality of metallic wires.

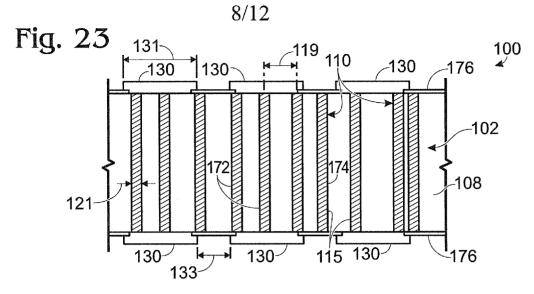

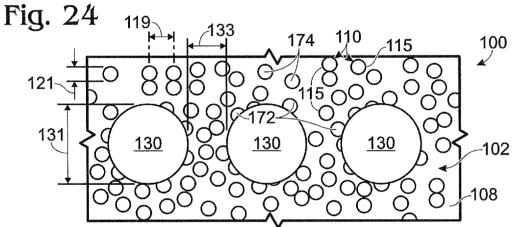

- Figs. 23-24 are schematic representations of illustrative, non-exclusive examples of device under test risers according to the present disclosure that include a plurality of ferromagnetic wires.

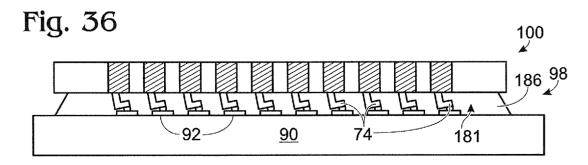

Figs. 25-29 are schematic representations of illustrative, non-exclusive examples of process flows that may be utilized to create a device under test riser according to the present disclosure.

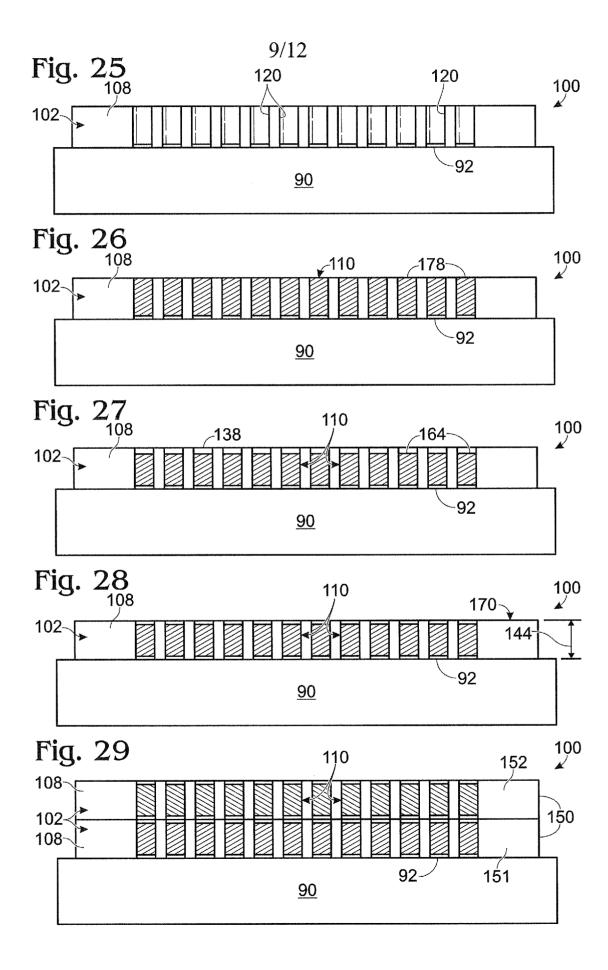

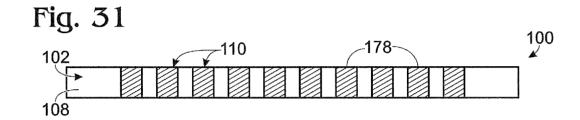

Figs. 30-31 are schematic representations of illustrative, non-exclusive examples of process flows that may be utilized to create a device under test riser according to the present disclosure.

5

10

15

20

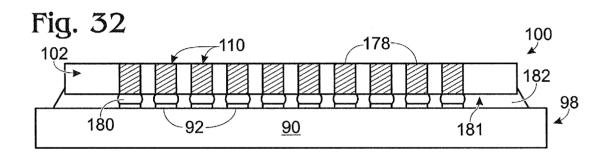

Fig. 32 is a schematic representation of an illustrative, non-exclusive example of a device under test riser according to the present disclosure assembled on a substrate.

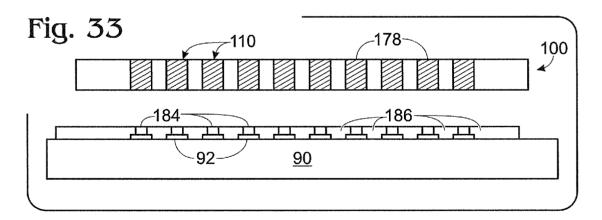

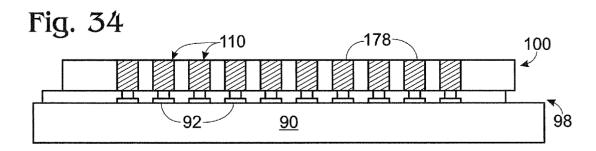

Figs. 33-34 are schematic representations of illustrative, non-exclusive examples of process flows that may be utilized to assemble a device under test riser according to the present disclosure on a substrate.

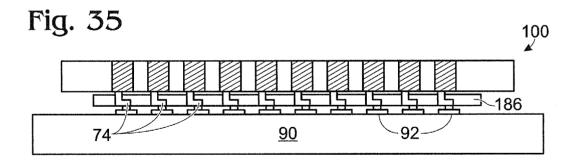

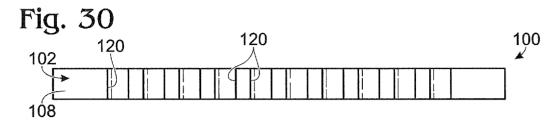

Figs. 35-36 are schematic representations of illustrative, non-exclusive examples of process flows that may be utilized to assemble a device under test riser according to the present disclosure on a substrate.

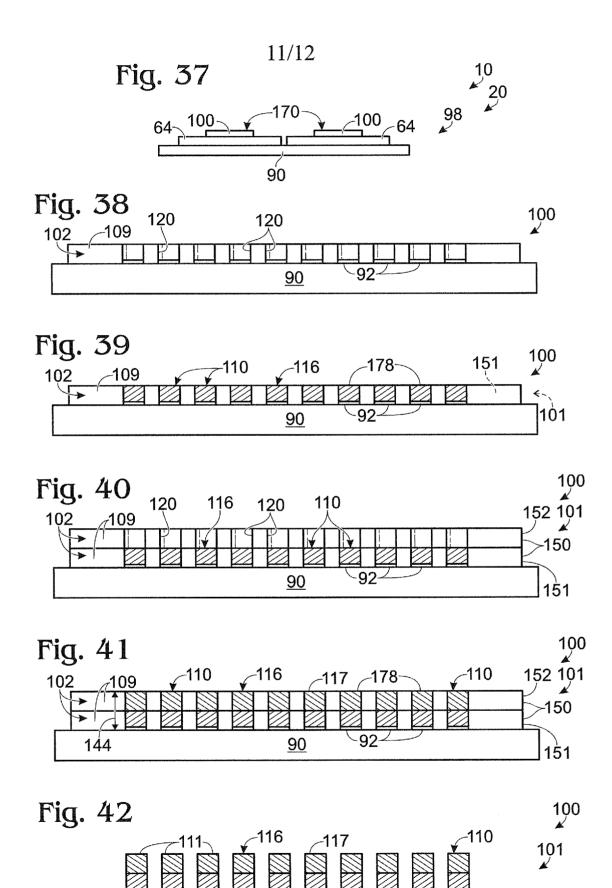

Fig. 37 is a schematic representation of an illustrative, non-exclusive example of a portion of a probe head that includes a plurality of device under test risers according to the present disclosure.

Figs. 38-44 are schematic representations of process flows that may be utilized to create a device under test riser according to the present disclosure that includes a plurality of composite pillars.

#### Detailed Description and Best Mode of the Disclosure

Fig. 1 is a schematic, partially exploded, representation of illustrative, non-exclusive examples of a test system 10 that may include a probe head assembly 20 that may include a device under test (DUT) riser 100 according to the present disclosure. In Fig. 1, test system 10 may include a control system 30 that is in electrical communication with probe head assembly 20. Control system 30 may be configured to provide a test signal 34 to probe head assembly 20, which may be in electrical communication with a device under test (DUT) 50 and which may provide a corresponding test signal to DUT 50. Similarly, DUT 50 may generate a resultant signal from the test signal that is supplied thereto, and probe head assembly 20 may provide a corresponding resultant signal 38 to control system 30. At least a portion of test system 10, such as probe head assembly 20 and/or DUT 50, may be contained within an enclosure 40.

5

10

15

20

25

30

35

Control system 30 may include any suitable structure that is configured to provide test signal 34 to the probe head assembly, receive resultant signal 38 from the probe head assembly, and/or control the operation of test system 10, including controlling the operation of other components thereof. As an illustrative, non-exclusive example, control system 30 may include a signal generator 32 that is configured to generate the test signal and/or a signal analyzer 36 that is configured to receive and/or analyze the resultant signal.

In general, control system 30 may be configured to control the operation of test system 10, and test system 10, probe head assembly 20, and/or DUT riser 100 may be utilized to test the functionality and/or performance of DUT 50. As discussed in more detail herein, this may include electrically and/or optically testing DUT 50. Illustrative, non-exclusive examples of DUTs 50 according to the present disclosure include any suitable semiconductor device, electronic device, microprocessor, integrated circuit, memory device, and/or controller.

Probe head assembly 20 may include and/or be in electrical and/or mechanical communication with a plurality of components. In the illustrative, non-exclusive example of Fig. 1, the probe head assembly may be mounted on a load board 60 and may include a wide pitch interposer 62, a space transformer assembly 64 (which may include and/or be in electrical and/or physical contact with DUT riser 100), a probe head frame 66, a narrow and/or a fine pitch interposer 68, and/or device under test contacting assembly 70.

Load board 60 may include any suitable structure that is configured to function as a mounting and/or bearing surface for at least a portion of the components of the probe head assembly. Wide pitch interposer 62 may include a substantially planar structure that includes a plurality of wide pitch interposer electrical conduits 76 that may be configured to transfer a plurality of electric currents between a first and a second surface thereof without substantially

changing a spatial relationship among the plurality of electric conduits. A pitch, or spacing, among the plurality of wide pitch interposer electrical conduits that are contained within the wide pitch interposer may be on the order of 0.8 millimeters (mm), while a length of the wide pitch interposer electrical conduits may be less than 5 mm, less than 4 mm, less than 3 mm, less than 2 mm, or less than 1 mm.

5

10

15

20

25

30

35

Space transformer assembly 64 may include a wide pitch riser 63 and a space transformer 65, and space transformer assembly 64 includes a plurality of space transformer electrical conduits 77 that are in electrical communication with the plurality of wide pitch interposer electrical conduits 76 and also with a plurality of narrow pitch interposer electrical conduits 78 of narrow pitch interposer 68. Thus, space transformer assembly 64 may be configured to decrease, route, change, adjust, and/or transform a spacing of the plurality of space transformer electrical conduits from the relatively wide spacing of wide pitch interposer 62 to a narrower spacing that may be associated with the electrical conduits of narrow pitch interposer 68.

As discussed in more detail herein, DUT riser 100 may be in electrical and/or physical communication with both space transformer assembly 64 and narrow pitch interposer 68, and DUT riser 100 may include a plurality of DUT riser electrical conduits 110, which additionally or alternatively may be referred to herein as riser electrical conduits 110, high aspect ratio electrical conduits 110, and/or electrical conduits 110. DUT riser electrical conduits 110 may be configured to transfer the plurality of electrical currents between the space transformer assembly and the narrow pitch interposer. A pitch, or spacing, and an arrangement of the plurality of DUT riser electrical conduits 110 may be similar to, matched to, and/or complementary to a pitch, or spacing, and an arrangement of the plurality of narrow pitch interposer electrical conduits 78. However, a thickness of DUT riser 100 may be significantly greater than a thickness of narrow pitch interposer 68, and a length of the plurality of DUT riser electrical conduits 110 also may be significantly greater than a length of the plurality of narrow pitch interposer electrical conduits 78. Thus, and as discussed in more detail herein, an aspect ratio (A/R) of the plurality of DUT riser electrical conduits may preclude the use of standard manufacturing technologies for their formation. Additionally or alternatively, it is within the scope of the present disclosure that the thickness of DUT riser 100 may be at least substantially the same as and/or less than the thickness of narrow pitch interposer 68 and/or that probe head assembly 20 may not include DUT riser 100.

Device under test contacting assembly 70 may include any suitable structure that is configured to form a plurality of electrical connections with DUT 50 and/or to provide test signals 34 to and/or receive resultant signals 38 from the DUT. As an illustrative, non-exclusive example, the DUT contacting assembly may include a plurality of probe tips 73 that

are configured to provide the plurality of electrical connections. As another illustrative, non-exclusive example, DUT contacting assembly 70 may include a membrane contacting layer 72 and/or a plurality of rocking beam interposers 74. Membrane contacting layer 72 may, additionally or alternatively, be referred to herein as a membrane contacting assembly 72. Illustrative, non-exclusive examples of test systems 10, membrane contacting layers 72, and/or rocking beam interposers 74 are disclosed in U.S. Provisional Patent Application Nos. 61/410,242, 61/446,379, and 61/484,116 and in U.S. Patent Nos. 5,914,613, 6,256,882, and 7,862,391, the complete disclosures of which are hereby incorporated by reference.

5

10

15

20

25

30

35

DUT riser 100 may be configured to change, or adjust, a distance between space transformer assembly 64 and/or space transformer 65 and DUT contacting assembly 70. Additionally or alternatively, when the DUT contacting assembly includes membrane contacting assembly 72, DUT riser 100 may be configured to adjust a force that is applied to membrane contacting assembly 72 by space transformer assembly 64, to adjust a deflection, or tension, of the membrane contacting assembly when mounted within probe head assembly 20, and/or to provide clearance between membrane contacting assembly 72 and an upper surface of space transformer 65 and/or one or more components that may be present thereon. As an illustrative, non-exclusive example, a thickness of space transformer assembly 64 and/or space transformer 65 may vary depending upon the particular DUT that is to be tested, or probed, by test system 10. Under these conditions, DUT riser 100 may be configured to account for this variation in the thickness of space transformer assembly 64 and/or space transformer 65. As an illustrative, non-exclusive example, a space transformer assembly and/or space transformer with a decreased thickness may be utilized with a DUT riser with an increased thickness. Conversely, a space transformer assembly and/or space transformer with an increased thickness may be utilized with a DUT riser with a decreased thickness.

Fig. 1 is an illustrative, non-exclusive example of test system 10 including probe head assembly 20 that may be utilized with the systems and methods according to the present disclosure. As such, additional components may be present within test system 10 and/or probe head assembly 20, one or more components illustrated in Fig. 1 may not be present in test system 10 and/or probe head assembly 20, and/or one or more components illustrated in Fig. 1 may be combined and/or formed simultaneously with one or more other components illustrated in Fig. 1, without departing from the scope of the present disclosure.

In addition, Fig. 1 schematically illustrates DUT 50 as being vertically above probe head assembly 20 that includes DUT riser 100. However, this illustrative, non-exclusive example is so illustrated simply for clarity and consistency with the subsequent Figures that further illustrate DUT riser 100. Thus, test system configurations in which DUT 50 is

vertically below probe head assembly 20, as well as any other suitable DUT to probe head configuration, are also within the scope of the present disclosure.

Furthermore, while the systems and methods disclosed herein are specifically applicable to DUT riser 100 and are so discussed herein, there are a number of other applications in which a high aspect ratio, narrow pitch device may be utilized. Thus, while the proceeding and subsequent discussion will, for convenience, refer to DUT riser 100, it is within the scope of the present disclosure that DUT riser 100 also may be referred to herein as including and/or forming a portion of a spacer 100, an interposer 100, and/or an electronic device 100. Additionally or alternatively, DUT riser electrical conduits 110 also may be referred to herein as high aspect ratio vertical interconnects 110, through silicon vias (TSVs) 110, vias 110, high aspect ratio vias 110, contacts 110, electrical pillars 110, and/or high aspect ratio contacts 110.

5

10

15

20

25

30

35

Fig. 2 is a schematic representation of an illustrative, non-exclusive example of a portion of probe head assembly 20 and/or space transformer assembly 64 that includes DUT riser 100 according to the present disclosure. In Fig. 2, wide pitch riser 63 includes wide pitch interposer electrical conduits 76 and is in electrical communication with and operatively attached to space transformer 65, which includes space transformer electrical conduits 77 (one of which is schematically illustrated in Fig. 2). In addition, space transformer 65 is in electrical communication with DUT riser 100, which includes DUT riser electrical conduits 110. It is within the scope of the present disclosure that wide pitch riser 63 and space transformer 65 may be operatively attached to one another and in electrical communication with each other using any suitable structure.

Similarly, and as discussed in more detail herein, DUT riser 100 may be in physical and/or electrical communication with space transformer 65 using any suitable structure. As an illustrative, non-exclusive example, DUT riser 100 may be formed separately from and operatively attached to space transformer 65. As another illustrative, non-exclusive example, DUT riser 100 may be formed on, formed with, and/or form a portion of space transformer 65.

Fig. 3 provides an illustrative, non-exclusive example of a DUT riser 100 that may be formed separately from and operatively attached to a substrate 90, such as space transformer assembly 64. DUT riser 100 includes a substantially planar body 102 that includes a first surface 104, or side 104, and a second, substantially opposed, surface 106, or side 106. DUT riser 100 also includes a plurality of DUT riser electrical conduits 110, which also may be referred to herein as a plurality of electrical conduits 110 and/or as electrical conduits 110.

DUT riser electrical conduits 110 may be configured to conduct a plurality of electric currents between first surface 104 and second surface 106. Electrical conduits 110 may refer

to a specific group of electrical conduits that are present within DUT riser 100. Thus, it is within the scope of the present disclosure that the DUT riser also may include other electrical conduits in addition to the plurality of electrical conduits 110 or that the plurality of electrical conduits 110 may include each electrical conduit that is present within DUT riser 100.

5

10

15

20

25

30

35

Body 102 may include any suitable structure that is configured to define first surface 104 and second surface 106, to provide mechanical support to electrical conduits 110, to electrically insulate electrical conduits 110 from one another, and/or to provide mechanical support for one or more electronic devices and/or structures that may be mounted on and/or coupled to first surface 104 and/or second surface 106 and/or that may be located within body 102. Illustrative, non-exclusive examples of suitable materials for a body 102 include a solid dielectric material 108 including polymers, semiconductors, epoxies, silicon oxide, polyimides, photopolymers, spin-on-glass, rigid dielectric materials, non-resilient dielectric materials, and/or non-elastomeric dielectric materials.

As discussed in more detail herein, body 102 may be formed around and/or formed after electrical conduits 110. However, electrical conduits 110 also may be formed after and/or placed within body 102. Illustrative, non-exclusive examples of electrical conduits 110 include any suitable conductive material, metal, copper, copper alloy, gold, gold alloy, nickel, nickel alloy, aluminum, carbon nanotubes, graphene, doped semiconductor material, rigid conductive material, at least substantially rigid conductive material, and/or combinations thereof.

Substrate 90 may include any suitable structure that is configured to be operatively attached to and/or in electrical communication with DUT riser 100. Illustrative, non-exclusive examples of substrates 90 include any suitable semiconductor package (including a package that might be utilized during packaging and assembly of the DUT), wide pitch interposer, and/or narrow pitch interposer. It is within the scope of the present disclosure that the materials of construction of DUT riser 100 and/or substrate 90 may be selected such that a coefficient of thermal expansion of the substrate may be at least substantially similar to, if not the same as, a coefficient of thermal expansion of the DUT riser. This may include coefficients of thermal expansion that differ by less than 20%, less than 15%, less than 10%, less than 5%, less than 5%, less than 15%, less than 10%, or less than 0.5%.

Electrical conduits 110 may include any suitable structure that is configured to conduct the plurality of electric currents between first surface 104 and second surface 106. As an illustrative, non-exclusive example, and as discussed in more detail herein, electrical conduits 110 may include a plurality of metallic bump pads 112, which also may be referred to as a plurality of stud bumps 112 and/or a plurality of bump pads 112 that are in electrical

communication with one another and that may, additionally or alternatively, also be referred to herein as a pillar of metallic bump pads 112.

Illustrative, non-exclusive examples of suitable bump pads 112 include bump pads that may be the same as, or at least substantially similar to, metallic bumps that are utilized in a standard stud bump process. When electrical conduits 110 include metallic bump pads 112, the metallic bump pads may be added to the plurality of electrical conduits in a sequential fashion, with the number of metallic bump pads present in an individual electrical conduit being increased until a desired length of the electrical conduit is reached. Each of the plurality of metallic bump pads may include a substantially circular, or spheroidal, shape and may be stacked, one on top of the other, to produce the electrical conduits. Thus, each of the electrical conduits may include a continuous, nonlinear, and/or substantially periodic longitudinal cross-sectional shape and/or profile.

5

10

15

20

25

30

35

As another illustrative, non-exclusive example, and as discussed in more detail herein, electrical conduits 110 may include a plurality of metallic wires 114, which also may be referred to herein as a plurality of wire pillars 114. The metallic wires may be formed separately from and placed within the DUT riser and may be randomly, regularly, and/or systematically located within body 102 using any suitable system and/or method, an illustrative, non-exclusive example of which includes a pick-and-place process that may place the metallic wires into body 102 singularly or in groups. Additional illustrative, non-exclusive examples of methods of locating metallic wires 114 within body 102 are discussed in more detail herein.

It is within the scope of the present disclosure that metallic wires 114 may be formed in any suitable manner and/or include any suitable material and/or materials of construction. As an illustrative, non-exclusive example, metallic wires 114 may include and/or be any suitable electrically conductive material, illustrative, non-exclusive examples of which include metals, copper, aluminum, gold, silver, graphite, carbon nanotubes, conductive polymers, and/or conductive and/or doped semiconductor materials. The metallic wires also may be referred to herein as conductive wires 114 and/or conductive pillars 114. Illustrative, non-exclusive examples, of methods of forming metallic wires 114 may include extruding, drawing, rolling, deposition, lithography, and/or etching.

As yet another illustrative, non-exclusive example, and as also discussed in more detail herein, electrical conduits 110 also may include a plurality of deposited electrical conduits 116. Deposited electrical conduits 116 may be formed using any suitable process, illustrative, non-exclusive examples of which include physical vapor deposition, chemical vapor deposition, evaporation, sputtering, epitaxial growth, and/or plating. When electrical conduits 110 include deposited electrical conduits 116, a cross-sectional shape of the

deposited electrical conduits and/or a location of the deposited electrical conduits may be defined by a lithographic process and/or by an etching process.

It is within the scope of the present disclosure that deposited electrical conduits 116 may be deposited in a single process step, or layer. However, it is also within the scope of the present disclosure that deposited electrical conduits 116 may be deposited in a series, or plurality, of process steps that are performed to produce the composite electrical conduits in a plurality of layers, with each layer of the plurality of layers increasing a total length of the deposited electrical conduits. When the deposited electrical conduits are deposited in a plurality of layers, the deposited electrical conduits also may be referred to herein as composite pillars 117, layered pillars 117, and/or stacked pillars 117.

5

10

15

20

25

30

35

As yet another illustrative, non-exclusive example, and as also discussed in more detail herein, electrical conduits 110 also may include a plurality of metallic conduits 118 that are formed within a void 120 present within body 102. Metallic conduits 118 may be formed in any suitable manner, including those discussed in more detail herein with reference to deposited conduits 116. Similarly, voids 120 may be formed in any suitable manner, illustrative, non-exclusive examples of which include etching, mechanical drilling, laser drilling, and/or lithography.

As yet another illustrative, non-exclusive example, and as also discussed in more detail herein, electrical conduits 110 may include a conductive region 122 that is incorporated into, or formed in, body 102. As illustrative, non-exclusive examples, conductive region 122 may include a dopant that may be implanted into dielectric material 108 and/or a conductive phase region within body 102 that may be formed from a material with a conductivity that varies with phase, an illustrative, non-exclusive example of which includes a chalcogenide glass.

DUT riser 100 also may include one or more contact pads 130 that are configured to provide an increased surface area and/or increased durability region for contact between electrical conduits 110 and a device that may be in electrical communication with DUT riser 100, such as substrate 90, space transformer assembly 64, fine pitch interposer 68, device under test contacting assembly 70, membrane contacting layer 72, and/or rocking beam interposer 74 (as illustrated in Fig. 1). Contact pads 130 may include any suitable size, location, and/or orientation and may be in electrical communication with one or more electrical conduits 110.

As an illustrative, non-exclusive example, and as shown at 132 in Fig. 3, the contact pads may be in electrical communication with a plurality of electrical conduits 110, including two, three, four, five, six, eight, ten, or more than ten electrical conduits 110. As another illustrative, non-exclusive example, and as shown at 134 in Fig. 3, a central axis of the contact

pads may be aligned with a central axis of the electrical conduits with which the contact pads are in electrical communication.

As yet another illustrative, non-exclusive example, and as shown at 136 in Fig. 3, the central axis of the contact pads may not be aligned with the central axis of the electrical conduits with which the contact pads are in electrical communication and/or the contact pads may be aligned with an electrical pad 92, or another complementary structure, that is present on substrate 90. This may provide for registration, or alignment, of contact pads 130 with electrical pads 92 even if electrical conduit 110 is not aligned, or not perfectly aligned, with electrical pad 92.

5

10

15

20

25

30

35

As yet another illustrative, non-exclusive example, contact pads 130 may include planar contact pads that include a circular, square, and/or rectangular shape. A minimum length, or dimension, of the contact pads may be less than 150 micrometers (um), including less than 140 um, less than 130 um, less than 120 um, less than 110 um, less than 100 um, less than 90 um, less than 80 um, less than 70 um, less than 60 um, less than 50 um, less than 40 um, less than 30 um, less than 20 um, less than 15 um, or less than 10 um. The minimum length, or dimension, of the contact pads also may be greater than 1 um, greater than 2.5 um, greater than 5 um, greater than 10 um, greater than 15 um, or greater than 20 um.

Additionally or alternatively, a root mean square surface roughness of the contact pads may be less than a threshold surface roughness. Illustrative, non-exclusive examples of threshold surface roughnesses according to the present disclosure include threshold surface roughnesses of less than 10 um, less than 9 um, less than 8 um, less than 7 um, less than 6 um, less than 5 um, less than 4 um, less than 3 um, less than 2 um, less than 1 um, less than 0.5 um, or less than 0.25 um.

Contact pads 130 also may include an abrasion-resistant surface 138 and/or a corrosion-resistant surface 142 that is/are configured to increase a durability of the contact pads. As an illustrative, non-exclusive example, abrasion-resistant surface 138 and/or corrosion-resistant surface 142 may include one or more surface layers and/or films, illustrative, non-exclusive examples of which include hard gold alloys, ruthenium, osmium, iridium, diamond-like carbon, and/or rhodium. In addition, first surface 104 and/or second surface 106 of DUT riser 100 may include and/or be covered by an abrasion-resistant coating 176.

DUT riser 100 may be formed in any suitable manner and/or with any suitable process. As an illustrative, non-exclusive example, and as discussed in more detail herein, the DUT riser may be formed on an intermediate substrate and subsequently placed into electrical communication with substrate 90. When the DUT riser is formed on an intermediate substrate, it may be operatively attached to and/or placed into electrical communication with

substrate 90 in any suitable manner and/or with any suitable process. As an illustrative, non-exclusive example, one or more attachment structures 140 may be configured to attach DUT riser 100 to substrate 90 and/or to provide electrical communication therebetween. Illustrative, non-exclusive examples of suitable attachment structures 140 according to the present disclosure include solder, adhesive, patterned conductive adhesive, anisotropically conductive adhesive, and/or rocking beam interposers, as discussed in more detail herein. Additionally or alternatively, DUT riser 100 may be in electrical communication with substrate 90 but not be operatively attached thereto. As an illustrative, non-exclusive example, the DUT riser may be mechanically pressed into electrical contact with substrate 90.

5

10

15

20

25

30

35

As discussed in more detail herein, the pitch, or spacing, of electrical conduits 110 associated with DUT riser 100 may be significantly less than the pitch, or spacing, of the electrical conduits associated with wide pitch interposer 62 (which is illustrated in Fig. 1). Illustrative, non-exclusive examples of pitches of DUT riser electrical conduits 110 according to the present disclosure include pitches of less than 150 um, less than 140 um, less than 130 um, less than 120 um, less than 110 um, less than 100 um, less than 90 um, less than 80 um, less than 70 um, less than 60 um, less than 50 um, less than 40 um, less than 30 um, less than 20 um, less than 15 um, or less than 10 um. Additionally or alternatively, DUT riser electrical conduits 110 according to the present disclosure may include pitches of greater than 0.5 um, greater than 1 um, greater than 2.5 um, greater than 5 um, greater than 10 um, greater than 15 um, or greater than 20 um.

In addition, the DUT riser may include any suitable number of electrical conduits 110. Illustrative, non-exclusive examples of the number of electrical conduits present within DUT riser 100 include at least 1,000 electrical conduits, at least 2,000, at least 2,500, at least 5,000, at least 10,000, at least 15,000, at least 25,000, at least 50,000, at least 50,000, at least 75,000, at least 100,000, at least 250,000, at least 500,000, at least 750,000, or at least 1,000,000 electrical conduits.

DUT risers 100 also may include any suitable thickness 144. Additionally or alternatively, electrical conduits 110 associated with the DUT riser also may include any suitable length. Illustrative, non-exclusive examples of DUT riser thicknesses according to the present disclosure include thicknesses of at least 25 um, at least 50 um, at least 5 um, at least 100 um, at least 150 um, at least 200 um, at least 250 um, at least 300 um, at least 400 um, at least 500 um, at least 750 um, at least 1000 um, 50-500 um, 100-400 um, 200-350 um, or 150-300 um.

As discussed in more detail herein, electrical conduits 110 associated with DUT riser 100 may include high aspect ratio electrical conduits. As used herein, the term "aspect ratio" may refer to a ratio of a length of a feature to a characteristic cross-sectional dimension of the

feature. Illustrative, non-exclusive examples of characteristic cross-sectional dimensions according to the present disclosure include any suitable diameter, effective diameter, and/or minimum cross-sectional dimension. Illustrative, non-exclusive examples of aspect ratios for DUT riser electrical conduits according to the present disclosure include aspect ratios of at least 4:1, at least 5:1, at least 6:1, at least 7:1, at least 8:1, at least 9:1, at least 10:1, at least 12:1, at least 14:1, at least 16:1, at least 18:1, at least 20:1, at least 24:1, at least 24:1, at least 26:1, at least 30:1.

5

10

15

20

25

30

35

Electrical conduits 110 associated with DUT riser 100 may be perpendicular to, or at least substantially perpendicular to, a plane defined by first surface 104 and/or second surface 106. As an illustrative, non-exclusive example, electrical conduits 110 may be within a threshold angle of being perpendicular to the first surface and/or the second surface. Illustrative, non-exclusive examples of threshold angles according to the present disclosure include threshold angles of less than 10 degrees, less than 8 degrees, less than 6 degrees, less than 4 degrees, or less than 2 degrees.

Each of the plurality of electric currents that are transferred between first surface 104 and second surface 106 of DUT riser 100 may include an amplitude of at least 0.5 amps, at least 0.75 amps, at least 1 amp, at least 1.25 amps, at least 1.5 amps, at least 1.75 amps, at least 2 amps, at least 2.25 amps, at least 2.5 amps, at least 3 amps, at least 3.5 amps, at least 4 amps, or at least 5 amps. Additionally or alternatively, each of the plurality of electric currents may be transferred through DUT riser 100 with a duty cycle of at least 10%, at least 15%, at least 20%, at least 25%, at least 30%, at least 35%, or at least 40%.

A plane defined by first surface 104 may be parallel to a plane defined by second surface 106 and/or may be within a threshold amount of being parallel to the plane defined by second surface 106, wherein the threshold amount may be defined as a difference between a maximum distance between first surface 104 and second surface 106 (or a maximum thickness of DUT riser 100) and a minimum distance between first surface 104 and second surface 106 (or a minimum thickness of DUT riser 100). Illustrative, non-exclusive examples of threshold amounts according to the present disclosure include threshold amounts of less than 15 um, less than 14 um, less than 12 um, less than 10 um, less than 8 um, less than 6 um, or less than 5 um.

Additionally and/or alternatively, the plane defined by first surface 104 and/or the plane defined by second surface 106 may be flat, at least substantially flat, and/or within a flatness threshold of being flat. Illustrative, non-exclusive examples of flatness thresholds according to the present disclosure include flatness thresholds of less than 20 um, less than 15 um, less than 10 um, less than 8 um, less than 6 um, or less than 5 um.

Fig. 4 provides an illustrative, non-exclusive example of a DUT riser 100 that may be formed on and/or from substrate 90. The DUT riser of Fig. 4 may include some or all of the illustrative, non-exclusive examples of structures, features, and/or dimensions that are discussed in more detail herein with reference to Fig. 3. In addition, the DUT riser of Fig. 3 may include some or all of the illustrative, non-exclusive examples of structures, features, and/or dimensions that are discussed herein with reference to Fig. 4.

As schematically illustrated in Fig. 4, DUT risers 100 according to the present disclosure optionally may include more than one layer 150, and in such an embodiment may be described as including a plurality of layers 150. In Fig. 4, four layers 150 are indicated, but it is within the scope of the present disclosure that a DUT riser 100 may include fewer or more layers 150, such as a single layer 150, two layers 150, three layers 150, or more than four layers 150. In addition, DUT riser 100 optionally may be located between and/or configured to provide a plurality of electrical connections between and/or conduct the plurality of electric currents between two substrates 90, such as, first device 80 and second device 85.

As schematically depicted in Fig. 4, DUT riser 100 may be formed on first device 80. It is within the scope of the present disclosure that DUT riser 100 may not be configured to be removed from the first device and/or may not be configured to be removed from the first device without damage to and/or destruction of the DUT riser, the first device, and/or attachment structure 140. When DUT riser 100 is formed on first device 80, it is within the scope of the present disclosure that the plurality of electrical conduits may be formed on the first device prior to application of body 102 to the first device. In contrast, body 102 may be applied to first device 80, with the plurality of electrical conduits being subsequently formed or otherwise inserted, created, and/or positioned within body 102. Additionally or alternatively, it is also within the scope of the present disclosure that DUT riser 100 and/or electrical conduits 110 thereof may be formed in and/or form a portion of first device 80.

Layers 150 may include any of the illustrative, non-exclusive examples of structures, features, and/or dimensions that are discussed in more detail herein with reference to DUT riser 100. Each of the plurality of DUT riser layers 150, when present, may be in electrical and physical contact with at least one other of the plurality of layers, and the electrical conduits associated with the layers may be configured and/or aligned to provide the plurality of electrical connections between first device 80 and second device 85. When the DUT riser includes a plurality of layers 150, electrical conduits 110 associated therewith may include composite, or layered, electrical conduits that are formed by the plurality of layers, as shown in Fig. 4.

DUT risers 100 that include layers 150 also may include one or more passive electronic components 155 that may be present between two or more layers of the DUT riser. Illustrative, non-exclusive examples of passive electronic components 155 according to the present disclosure include any suitable resistor, capacitor, inductor, transformer, and/or electrical conduit.

5

10

15

20

25

30

35

Passive electronic components 155, when present, may be configured to conduct an electric current between two or more of the electric conduits that are present within the DUT riser. As an illustrative, non-exclusive example, electrical conduits 110 may include a plurality of ground conduits 156, and passive electronic component 155 may be configured to electrically connect at least a portion, a substantial portion, a majority, or all of the plurality of ground conduits. As another illustrative, non-exclusive example, electrical conduits 110 may include a plurality of power supply conduits 158, and passive electronic components 155 may be configured to electrically connect at least a portion, a substantial portion, a majority, or all of the plurality of power supply conduits.

Figs. 5-8 provide illustrative, non-exclusive examples of methods according to the present disclosure. These include methods of forming a DUT riser in Figs. 5-7, as well as methods of finishing, assembling, and/or utilizing the DUT riser in Fig. 8. Although not required, the methods of Figs. 5-8 may be used to form, finish, assemble, and/or utilize DUT risers 100 according to the present disclosure.

Fig. 5 is a flowchart depicting illustrative, non-exclusive examples of methods 200 according to the present disclosure of forming a DUT riser. Methods 200 may be broadly categorized as methods of forming a DUT riser, such as DUT riser 100, with such methods including the formation of the electrical conduits prior to the formation of a body and/or dielectric material that may surround, encapsulate, and/or insulate the electrical conduits from one another and/or define an external shape of the DUT riser.

Methods 200 include aligning a plurality of electrical conduits to a surface of a substrate at 205, and encapsulating the plurality of electrical conduits in a dielectric material at 210. The methods optionally also may include removing the DUT riser that may be formed by the method from the substrate, as indicated at 215.

Aligning the plurality of electrical conduits to the surface of the substrate at 205 may include the use of any suitable method and/or apparatus to accomplish the alignment. As an illustrative, non-exclusive example, the aligning may include attaching the plurality of electrical conduits directly to the surface of the substrate and/or attaching the plurality of electrical conduits to an intermediate layer that is formed on the surface of the substrate. As another illustrative, non-exclusive example, the aligning may include adhering the plurality of electrical conduits to the surface of the substrate.

As yet another illustrative, non-exclusive example, the aligning may include soldering, welding, brazing, and/or spot welding the plurality of electrical conduits to the substrate and/or alloying at least a portion of each of the plurality of electrical conduits with at least a portion of the surface of the substrate. It is within the scope of the present disclosure that the aligning may occur sequentially, with one, or several, of the plurality of electrical conduits being aligned on and/or affixed to the substrate prior to another one, or several, of the plurality of electrical conduits being aligned on and/or affixed to the substrate. However, it is also within the scope of the present disclosure that the aligning may occur simultaneously, such as when all, or at least substantially all, of the plurality of electrical conduits are aligned on and/or affixed to the substrate at the same, or at least substantially the same, time. As an illustrative, non-exclusive example, and as discussed in more detail herein, the plurality of electrical conduits may be fabricated separately from the substrate and/or may be fabricated on an intermediate substrate and then placed on the surface of the substrate using any suitable system and/or method, an illustrative, non-exclusive example of which includes a pick-and-place system and/or method. As yet another illustrative, non-exclusive example, the aligning may include establishing electrical communication between the plurality of electrical conduits and the surface of the substrate.

5

10

15

20

25

30

35

It is within the scope of the present disclosure that the aligning may include systematically aligning, randomly aligning, and/or regularly aligning. When the aligning includes systematically aligning the plurality of electrical conduits, this may include selectively locating each of the plurality of electrical conduits such that a location of each of the plurality of electrical conduits, as well as a relative location of each of the plurality of electrical conduits with respect to the other of the plurality of electrical conduits, may correspond to a predetermined, fixed, and/or desired location and/or relative location. As an illustrative, non-exclusive example, this may include selectively locating each of the plurality of electrical conduits such that a location of each of the plurality of electrical conduits corresponds to a location of an electrical pad or other electrical contacting structure that is present on a substrate and/or device with which the DUT riser is configured to be in electrical communication.

When the aligning includes randomly and/or regularly aligning the plurality of electrical conduits, this may include aligning the plurality of electrical conduits such that they are spaced apart but at an average conduit pitch, or spacing, that is less than an average pad pitch, or spacing, of the electrical pad or other electrical contacting structure that is present on the substrate and/or device with which the DUT riser is configured to be in electrical communication. Additionally or alternatively, randomly and/or regularly aligning the plurality of electrical conduits also may include providing a plurality of electrical conduits

that include an average diameter that is less than the average pad pitch and/or an average gap, or space, between adjacent pads. This may include electrical conduit diameters that are less than 75%, less than 70%, less than 60%, less than 50%, less than 40%, less than 30%, less than 25%, less than 20%, less than 15%, or less than 10% of the average pad pitch and/or the average gap between adjacent pads.

5

10

15

20

25

30

35

As discussed in more detail herein, the plurality of electrical conduits may be and/or include a metallic wire. When the plurality of electrical conduits includes a metallic wire, the aligning may include attaching the metallic wire to the substrate. Additionally or alternatively, and as also discussed in more detail herein, the plurality of electrical conduits may include a ferromagnetic wire. When the plurality of electrical conduits includes a ferromagnetic wire, the aligning may include applying a magnetic and/or electric field to the ferromagnetic wire. Applying the magnetic and/or electric field may include placing the plurality of electrical conduits between two planar surfaces and generating the magnetic and/or electric field between the two planar surfaces. When the plurality of electrical conduits includes the metallic wire, the metallic wire may be formed prior to performing the method.

As also discussed in more detail herein, the plurality of electrical conduits also may include a plurality of metallic bump pads that are in electrical communication with one another and which are operatively attached to one another to form a stack of metallic bump pads. When the plurality of electrical conduits includes the plurality of metallic bump pads, the aligning may include attaching a first metallic bump pad to the surface and subsequently attaching a second metallic bump pad to the first metallic bump pad. The attaching may be repeated until a length of the stack of metallic bump pads corresponds to a desired length of the metallic conduit.

As also discussed in more detail herein, the plurality of electrical conduits may be formed on the substrate. When the plurality of electrical conduits is formed on the substrate, the aligning may include depositing a conductive layer on the surface of the substrate and patterning the conductive layer to produce the plurality of electrical conduits. Illustrative, non-exclusive examples of depositing include physical vapor deposition, chemical vapor deposition, sputtering, evaporation, epitaxial growth, and/or plating. Illustrative, non-exclusive examples of patterning include lithographically defining a location of the plurality of electrical conduits and etching the conductive layer to produce and/or define the plurality of electrical conduits.

Encapsulating the plurality of electrical conduits in a dielectric material at 210 may include the use of any suitable system and/or method to coat, cover, surround, and/or otherwise encapsulate the plurality of electrical conduits with the dielectric material. It is

within the scope of the present disclosure that the encapsulating may include encapsulating the plurality of electrical conduits without substantially disturbing a location of each of the plurality of electrical conduits.

As an illustrative, non-exclusive example, the encapsulating may include flowing the dielectric material on the surface of the substrate and around the plurality of electrical conduits. As another illustrative, non-exclusive example, the flowing may include placing an encapsulation dam on the surface of the substrate to constrain a flow of the dielectric material within a desired region, or portion, of the substrate prior to flowing the dielectric material. As another illustrative, non-exclusive example, the encapsulating also may include curing the dielectric material.

5

10

15

20

25

30

35

Performing steps 205 and 210 may produce a DUT riser, or at least a partially finished DUT riser, that may be present on the surface of the substrate. When the substrate includes an intermediate substrate, optionally removing the DUT riser from the surface of the intermediate substrate at 215 may include the use of any suitable systems and/or methods to remove the DUT riser from the surface. As illustrative, non-exclusive examples, the removing may include dissolving the intermediate substrate, dissolving a sacrificial and/or intermediate layer that forms the surface of the intermediate substrate, and/or physically separating the DUT riser from the intermediate substrate.

Fig. 6 is a flowchart depicting illustrative, non-exclusive examples of methods 300 according to the present disclosure of forming a DUT riser. Methods 300 may be broadly categorized as methods of forming a DUT riser, such as DUT riser 100, with such methods including the formation of voids within a matrix material prior to formation of the electrical conduits within the matrix material.

Methods 300 optionally include forming a solid body from a matrix material at 305. The methods further include forming a plurality of voids in the solid body at 310 and placing an electrically conductive material in the plurality of voids to form a plurality of electrical conduits at 315. The methods also may include optionally repeating the methods at 320, removing the matrix material from around the plurality of electrical conduits to form a plurality of unsupported electrical conduits at 325, encapsulating the plurality of unsupported electrical conduits in a dielectric material at 330, and/or removing the DUT riser from a substrate at 335.

Optionally forming the solid body at 305 may include forming a solid body that does not include the plurality of voids and/or forming the plurality of voids concurrently with forming the solid body. This may include forming the solid body on the surface of the substrate and/or forming the solid body as an independent body that is not present on and/or is removed from the surface of the substrate. As illustrative, non-exclusive examples, this may

include flowing the matrix material onto the surface of a substrate, coating the matrix material onto the surface of the substrate, depositing the matrix material onto the surface of the substrate (including depositing using chemical vapor deposition, physical vapor deposition, evaporation, sputtering, screening, plating, and/or epitaxial growth), casting the matrix material, extruding the matrix material, molding the matrix material, and/or blowing the matrix material.

Matrix materials according to the present disclosure include any suitable material that may form the solid body, include and/or be made to include the plurality of voids that are discussed in more detail with reference to step 310, electrically insulate the plurality of electrical conduits formed at step 315 from one another, and/or be removed from around the plurality of electrical conduits without disturbing a location and/or orientation of the plurality of electrical conduits as discussed in more detail herein with reference to step 325. Illustrative, non-exclusive examples of matrix materials according to the present disclosure include dielectric materials, including the dielectric materials that are discussed in more detail herein. Additional illustrative, non-exclusive examples of matrix materials according to the present disclosure include materials that include a high etch selectivity relative to the material(s) that comprise the electrical conduits. As an illustrative, non-exclusive example, the electrical conduits may include gold, and the matrix material may include a metal, and the matrix material may include photoresist and/or silicon oxides.

Forming the plurality of voids at 310 may include forming a plurality of voids that includes at least one hole and/or trench within the solid body. As an illustrative, non-exclusive example, the solid body may include a photoresist, and forming the plurality of voids may include lithographically forming and/or developing the plurality of voids. As another illustrative, non-exclusive example, forming the plurality of voids may include drilling the plurality of voids with a drill bit. As another illustrative, non-exclusive example, forming the plurality of voids may include ablating a portion of the solid body to form the plurality of voids. As an illustrative, non-exclusive example, the ablating may include laser ablating and/or electron beam ablating. As yet another illustrative, non-exclusive example, forming the plurality of voids may include etching away a portion of the solid body to form the plurality of voids, wherein a location of the plurality of voids optionally may be defined lithographically. As an illustrative, non-exclusive example, the etching may include chemical etching, wet etching, dry etching, and/or plasma etching.

Placing the electrically conductive material within the plurality of voids to form the plurality of electrical conduits at 315 may include the use of any suitable system and/or method to place, or position, the electrically conductive material. As illustrative, non-

exclusive examples, and as discussed in more detail herein, the placing may include inserting the electrically conductive material into the plurality of voids, and such inserting may include inserting a metallic wire and/or a stack of metallic bump pads. As another illustrative, non-exclusive example, the placing may include depositing the electrically conductive material, and such depositing may include physical vapor deposition, chemical vapor deposition, screening, epitaxially growing, sputtering, and/or plating. When the solid body is present on the surface of a substrate, the placing also may include attaching the plurality of electrical conduits to the surface of the substrate and/or establishing electrical communication between the plurality of electrical conduits and the surface of the substrate and/or one or more electrical pads present on the surface of the substrate.

5

10

15

20

25

30

35

It is within the scope of the present disclosure that, prior to the placing, the method also may include coating at least one of a first surface of the solid body and a second surface of the solid body with a masking photoresist and patterning the masking photoresist. The masking photoresist may be configured to mask, or control, the portion(s) of the solid body that will come into contact with the electrically conductive material, thereby increasing process control, flexibility, and/or DUT riser reliability.

The patterning may include removing at least a portion of the masking photoresist that covers at least a portion of the plurality of voids. Subsequent to the depositing, the method also may include removing the masking photoresist from the solid body.

In some embodiments, the solid body of DUT riser 100 may not be present on, adhered to, and/or otherwise operatively attached to a substrate during the placing. Under these conditions, the solid body may include a first exposed surface that is in fluid communication with at least a portion of the plurality of voids, as well as a second exposed surface that is also in fluid communication with at least a portion of the plurality of voids. When the solid body includes the first and second exposed surfaces, the placing may include supplying at least a first portion of the electrically conductive material from a side of the DUT riser that includes the first exposed surface and/or supplying at least a second portion of the electrically conductive material from a side of the DUT riser that includes the second exposed surface. Supplying the conductive material to the voids present within the solid body from both the first surface and the second surface may decrease a distance that the electrically conductive material must travel within the voids prior to being deposited within the voids, decrease the effective aspect ratio of the voids for the supplying step due to the decreased distance, and/or increase a uniformity and/or reliability of the plurality of electrical conduits that are formed during the placing.

It is within the scope of the present disclosure that, prior to the placing, the methods also may include depositing an intermediate layer onto the solid body. When present, these

intermediate layers may be configured to direct the placing within target, or desired, regions of the solid body, such as within the voids formed therein, increase adhesion between the solid body and the electrical conduits, improve the uniformity of the placing, and/or serve as a barrier layer to diffusion of the electrically conductive material into the solid body. Illustrative, non-exclusive examples of intermediate layers according to the present disclosure include a seed layer, a barrier layer, and a conductive layer. It is within the scope of the present disclosure that the depositing may include selectively depositing the intermediate layer. As an illustrative, non-exclusive example, the selectively depositing may include selectively depositing the intermediate layer within at least a portion of the plurality of voids and/or on a surface that defines at least a portion of the plurality of voids.

In some embodiments, the solid body may be present on, adhered to, and/or otherwise operatively attached to a substrate during the placing. Under these conditions, at least a portion of the plurality of voids may be in fluid communication with one or more conductive pads that may be present on a surface of the substrate. When the portion of the plurality of voids is in fluid communication with one or more conductive pads that are present on the surface of the substrate, the method also may include cleaning the portion of the plurality of pads, such as to remove a surface contaminant, prior to the placing. The cleaning may improve the reliability of the placing process, thereby improving the uniformity and/or reliability of the plurality of electrical conduits.

Repeating the method at 320 may include repeating each of step 305, 310, and 315 to increase the thickness of the DUT riser and/or the length of the plurality of the electrical conduits. When the method is repeated, forming the solid body from the matrix material at 305 may include forming a second, or subsequent, solid body on an upper surface of the DUT riser and/or attaching the solid body to the upper surface of the DUT riser. In addition, repeating the formation of the plurality of voids at 310 may include forming the plurality of voids within the second, or subsequent, solid body and/or forming the plurality of voids such that the plurality of voids is aligned and/or in fluid communication with a top surface of the plurality of electrical conduits. Similarly, placing the electrically conductive material into the plurality of voids at 315 may include placing the electrical conductive material into electrical communication with the plurality of electrical conduits, thereby increasing the length of the plurality of electrical conduits to form a plurality of composite, layered, and/or stacked pillars, or composite, layered, and/or stacked electrical conduits, that define the plurality of electrical conduits.

Removing the matrix material from around the plurality of electrical conduits to form a plurality of unsupported electrical conduits at 325 may include the use of any suitable system and/or method to remove the matrix material without damage to and/or disturbance of

the plurality of electrical conduits. When the solid body was formed on the surface of a substrate, it is within the scope of the present disclosure that the plurality of electrical conduits may remain attached to and/or in electrical communication with the surface of the substrate when the matrix material is removed from the surface of the substrate. Illustrative, non-exclusive examples of processes and/or methods that may be utilized to remove the matrix material include etching and/or dissolution.

5

10

15

20

25

30

35

Encapsulating the plurality of unsupported electrical conduits at 330 may include the use of any suitable systems and/or methods to encapsulate the plurality of unsupported electrical conduits within the matrix material. Illustrative, non-exclusive examples of the encapsulating are discussed in more detail herein with reference to step 210 of Fig. 5.

When the solid body is present on the substrate during the placing, performing at least steps 310 and 315 may produce a DUT riser, or at least a partially finished DUT riser, that may be present on a surface of the substrate. When the substrate includes an intermediate substrate, optionally removing the DUT riser from the surface of the intermediate substrate at 335 may include the use of any suitable systems and/or methods to remove the DUT riser from the surface, including those discussed in more detail herein with reference to Fig. 5.

Fig. 7 is a flowchart depicting illustrative, non-exclusive examples of methods 400 according to the present disclosure of forming a DUT riser. Methods 400 may be broadly categorized as methods of forming a DUT riser, such as DUT riser 100, with such methods including the formation of the electrical conduits within the body of the DUT riser. Methods 400 optionally may include placing a dielectric material on a surface of a substrate at 405, and incorporating a conductivity-enhancing material into a plurality of selected portions of the dielectric material and/or changing the phase of the dielectric material to enhance the conductivity of the dielectric material and form a plurality of electrical conduits, as indicated at 410. The methods further optionally may include removing the DUT riser from the substrate, as indicated at 415.

Placing the dielectric material on the surface of the substrate at 405 may include the use of any suitable system and/or methods to form a layer of dielectric material on the surface of the substrate. Illustrative, non-exclusive examples of the placing include physical vapor deposition, chemical vapor deposition, evaporation, sputtering, spin-coating, laminating, dipping, and/or flowing.

The dielectric material may include any suitable material that may be made conductive through incorporation of the conductivity-enhancing material. Illustrative, non-exclusive examples of dielectric materials according to the present disclosure include a semiconductor material, silicon, gallium arsenide, germanium, chalcogenide glass, and/or a semiconducting polymer.

The conductivity-enhancing material may include any suitable material that may increase the conductivity of the dielectric material, thus providing for formation of the plurality of electrical conduits. An illustrative, non-exclusive example of conductivity-enhancing materials according to the present disclosure includes a dopant. When the conductivity-enhancing material includes a dopant, the incorporating may include implanting the dopant into, or otherwise locating the dopant within, the dielectric material.

5

10

15

20

25

30

35

As discussed in more detail herein with reference to Figs. 5 and 6, the substrate may include an intermediate substrate. When the substrate includes an intermediate substrate, optionally removing the DUT riser, or partially formed DUT riser, from the substrate at 415 may include the use of any of the systems and methods that are discussed with reference to Figs. 5 and 6.

Fig. 8 provides additional illustrative, non-exclusive examples of methods 500 of forming and/or using DUT risers (such as DUT risers 100) according to the present disclosure. Methods 500 include forming a DUT riser at 505 and optionally may include annealing the DUT riser at 510, polishing the DUT riser at 515, and/or repeating the method at 520. The methods 500 further optionally may include adding additional structure to the DUT riser, such as adding an abrasion-resistant coating to the DUT riser at 525 and/or adding contact pads to the DUT riser at 530. The methods also optionally may include assembling the DUT riser on a substrate to form a DUT riser assembly at 535 and/or placing the DUT riser assembly in a probe head assembly at 540. The methods further optionally may include using the probe head assembly to electrically test a device under test (DUT), which may include contacting the device under test with the probe head assembly at 545, providing a test signal to the device under test at 550, receiving a resultant signal from the device under test at 555, and/or analyzing the resultant signal at 560.

Forming the DUT riser at 505 may include forming a DUT riser according to the present disclosure using any suitable method. As illustrative, non-exclusive examples, the forming may include the use of methods 200, methods 300, and/or methods 400 that are discussed in more detail herein.

Annealing the DUT riser at 510 may include heating, baking, or otherwise curing the DUT riser. The annealing may include annealing to remove solvents from the DUT riser, increase a rigidity of the DUT riser, reduce a residual stress in the DUT riser, and/or provide dimensional stability to the DUT riser.

Polishing the DUT riser at 515 may include the use of any suitable polishing and/or lapping systems and/or methods. The polishing may include decreasing a thickness of the DUT riser, decreasing a length of at least a portion of the plurality electrical conduits that are present within the DUT riser, decreasing a surface roughness of the DUT riser, increasing a

parallelism between a plane defined by a first surface of the DUT riser and a plane defined by a second surface of the DUT riser, and/or exposing an end of the plurality of electrical conduits that is proximal to at least one of the first surface of the DUT riser and the second surface of the DUT riser. The polishing may include polishing the first surface and/or the second surface of the DUT riser.

5

10

15

20

25

30

35

Repeating the method at 520 may include repeating any suitable portion, or portions, of the method. As an illustrative, non-exclusive example, the repeating may include repeating the method to increase the thickness of the DUT riser, the length of the plurality of electrical conduits that are included within the DUT riser, and/or the aspect ratio of the plurality of electrical conduits that are included within the DUT riser.

As another illustrative, non-exclusive example, the DUT riser may include an upper surface, and the repeating may include adding one or more additional DUT riser layers to the upper surface of the DUT riser to form a layered DUT riser structure including a plurality of layers, such as shown in the illustrative, non-exclusive example of Fig. 4. As yet another illustrative, non-exclusive example, the repeating may include adding a passive electronic component to the DUT riser such that the passive electronic component is present between two or more of the layers of the DUT riser. The repeating may include repeating the method any suitable number of times. As illustrative, non-exclusive examples, this may include repeating the method at least two, at least three, at least four, at least five, at least six, at least seven, at least eight, at least nine, or at least ten times.

Adding an abrasion-resistant coating at 525 may include the use of any suitable systems and/or methods to apply, deposit, or otherwise affix the abrasion-resistant coating to at least one surface of the DUT riser. Illustrative, non-exclusive examples of abrasion-resistant coatings according to the present disclosure include a coating of, and/or which includes, a dielectric material.

Adding contact pads to a surface of the DUT riser at 530 may include forming a plurality of contact pads on one or more surfaces of the DUT riser. As discussed in more detail herein, the plurality of contact pads may be in electrical communication with the plurality of electrical conduits that are included in the DUT riser, and the plurality of contact pads may provide a robust, durable, chemically inert, and/or systematically located surface for forming an electrical contact between the DUT riser and one or more other devices that may be in electrical communication with the DUT riser.