(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4754682号

(P4754682)

(45) 発行日 平成23年8月24日(2011.8.24)

(24) 登録日 平成23年6月3日(2011.6.3)

(51) Int.Cl.

F 1

|             |               |                  |      |           |

|-------------|---------------|------------------|------|-----------|

| <b>G09G</b> | <b>3/36</b>   | <b>(2006.01)</b> | G09G | 3/36      |

| <b>G02F</b> | <b>1/13</b>   | <b>(2006.01)</b> | G02F | 1/13 505  |

| <b>G02F</b> | <b>1/133</b>  | <b>(2006.01)</b> | G02F | 1/133 505 |

| <b>G02F</b> | <b>1/1335</b> | <b>(2006.01)</b> | G02F | 1/1335    |

| <b>G03B</b> | <b>21/00</b>  | <b>(2006.01)</b> | G03B | 21/00 E   |

請求項の数 5 (全 22 頁) 最終頁に続く

(21) 出願番号 特願2000-350515 (P2000-350515)

(22) 出願日 平成12年11月17日 (2000.11.17)

(65) 公開番号 特開2001-222265 (P2001-222265A)

(43) 公開日 平成13年8月17日 (2001.8.17)

審査請求日 平成19年11月6日 (2007.11.6)

(31) 優先権主張番号 特願平11-330514

(32) 優先日 平成11年11月19日 (1999.11.19)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 ▼ひろ▲木 正明

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 西島 篤宏

最終頁に続く

(54) 【発明の名称】表示装置

## (57) 【特許請求の範囲】

## 【請求項 1】

3個の表示パネルを有する投射型の表示装置であって、

黒点である欠陥画素の座標を特定する手段と、

前記3個の表示パネルのうち前記欠陥画素を有する表示パネルを特定する手段と、

前記欠陥画素と同座標の画素において前記3個の表示パネルにより合成された映像の輝度と、前記欠陥画素に隣接する画素と同座標の画素において前記3個の表示パネルにより合成された映像の輝度との差が緩和されるように、前記欠陥画素を有する表示パネルが有する画素のうち前記欠陥画素に隣接する画素の輝度と、前記欠陥画素を有する表示パネル以外の表示パネルが有する画素のうち前記欠陥画素の座標と同座標の画素の輝度とを補正する手段と、を有することを特徴とする投射型の表示装置。

## 【請求項 2】

3個の表示パネルを有する投射型の表示装置であって、

欠陥画素の座標を特定する手段と、

前記3個の表示パネルのうち前記欠陥画素を有する表示パネルを特定する手段と、

前記欠陥画素が黒点か輝点かの判別を行う手段と、

前記判別を行う手段により輝点と判別された前記欠陥画素を黒点にリペアする手段と、

前記欠陥画素と同座標の画素において前記3個の表示パネルにより合成された映像の輝度と、前記欠陥画素に隣接する画素と同座標の画素において前記3個の表示パネルにより合成された映像の輝度との差が緩和されるように、前記欠陥画素を有する表示パネルが有

10

20

する画素のうち前記判別を行う手段により黒点と判別された前記欠陥画素又は前記リペアする手段により黒点にリペアされた前記欠陥画素に隣接する画素の輝度と、前記欠陥画素を有する表示パネル以外の表示パネルが有する画素のうち前記欠陥画素の座標と同座標の画素の輝度とを補正する手段と、を有することを特徴とする投射型の表示装置。

#### 【請求項 3】

請求項 2において、

前記リペアは、レーザー照射により行われることを特徴とする投射型の表示装置。

#### 【請求項 4】

請求項 1乃至 3 のいずれか一において、

前記表示パネルは、アクティブマトリクス型の表示パネルであることを特徴とする投射型の表示装置。 10

#### 【請求項 5】

請求項 1乃至 4 のいずれか一において、

前記表示パネルは、液晶パネルであることを特徴とする投射型の表示装置。

#### 【発明の詳細な説明】

##### 【0001】

##### 【発明の属する技術分野】

本発明は、投射型表示装置に関する。本発明は、表示装置の中でも特にアクティブマトリクス型の表示装置に関する。代表的には、リア型の投射型液晶表示装置およびフロント型の投射型液晶表示装置に関する。 20

##### 【0002】

##### 【従来の技術】

最近安価なガラス基板上に半導体薄膜を形成した半導体装置、例えば薄膜トランジスタ(TFT)を作製する技術が急速に発達してきている。その理由は、アクティブマトリクス型液晶表示装置(液晶パネル)の需要が高まってきたことによる。

##### 【0003】

また、この液晶パネルの画素部に光源からの強い光を照射し、レンズを通してスクリーンに照射することによって拡大された映像を楽しむ投射型液晶表示装置(液晶プロジェクタ)が注目を浴びてきている。

##### 【0004】

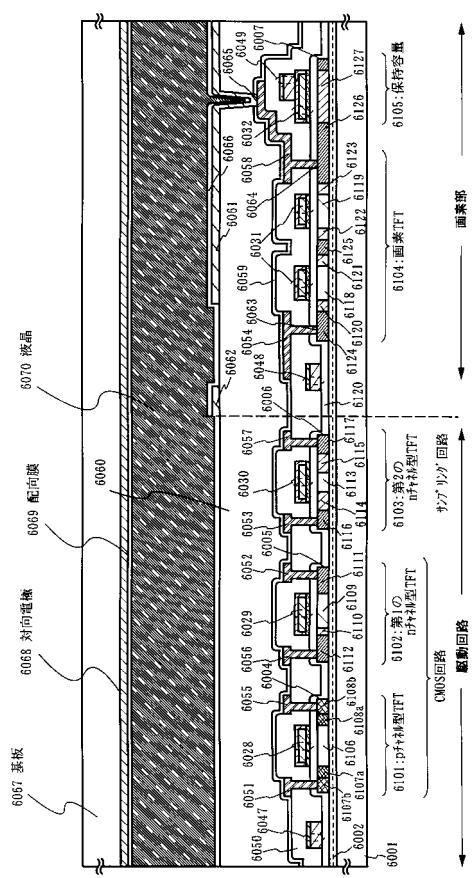

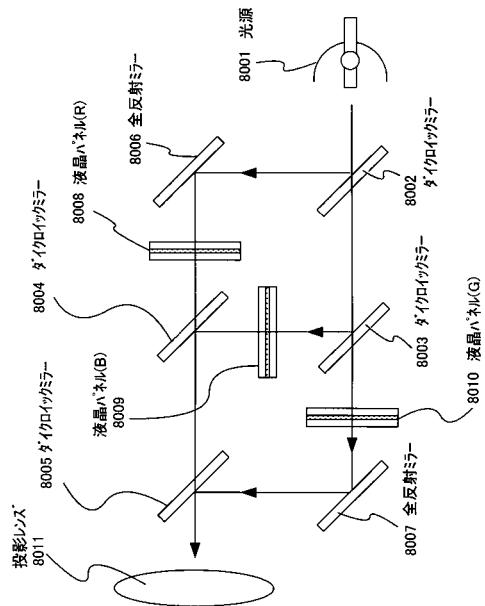

図18に液晶パネルを3枚用いた従来の3板式液晶プロジェクタの概略構成図を示す。8001は光源であり、白色光源が用いられる。8002、8003、8004および8005はダイクロイックミラーであり、一定の波長域の光のみを反射し、他の光を透過させる。8002は赤の光のみを反射し、他の光を透過する。同様に、8003および8004は青の光のみを反射し、他の光を透過する。また、8005は緑の光のみを反射し、他の光を透過する。8006および8007は全反射ミラーである。8008、8009および8010は液晶パネルであり、それぞれ、赤、青、緑の映像を表示する。 30

##### 【0005】

##### 【発明が解決しようとする課題】

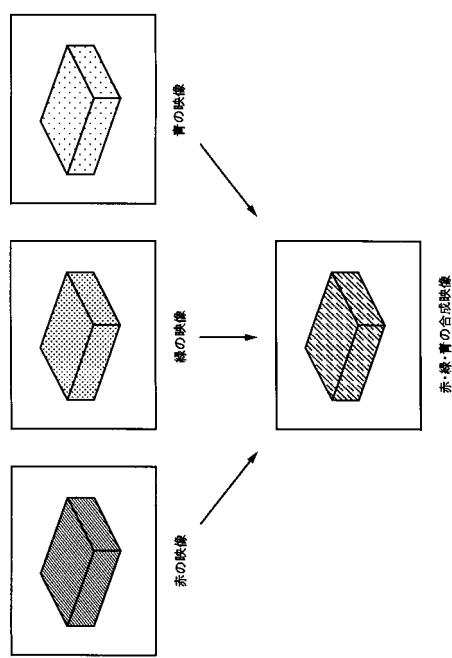

図19を参照する。図19には、3板式のプロジェクタの原理を示している。図19に示すように、3板式のプロジェクタは、赤の映像と緑の映像と青の映像とを合成することによってカラー映像を提供している。 40

##### 【0006】

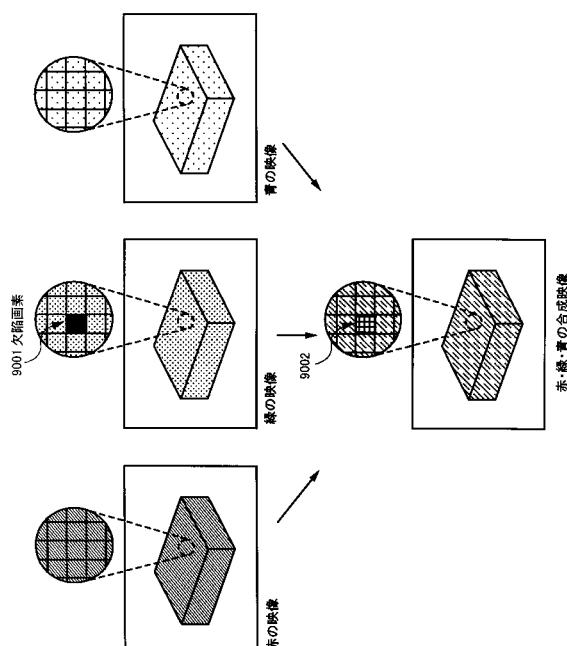

ここで、図20に示すように、緑の映像を表示する液晶パネル8010(ノーマリーホワイト)に欠陥画素が存在する場合について説明する。なお、その欠陥画素9001が輝点である場合には、その欠陥画素にレーザー照射等の処理を行い黒点化させる。

##### 【0007】

緑の映像を表示する液晶パネル8010に欠陥画素9001が存在する場合には、緑の映像中には、その黒点による欠陥が表示されてしまう。ここで、赤の映像を表示する液晶パネル8008および青の映像を表示する液晶パネル8009には、欠陥画素が無いとする 50

。すると、三色の映像が合成されたカラー映像において、緑の映像に欠陥が生じていた結果、画素の輝度が低下し、赤の映像と青の映像が合成されて、その欠陥が存在する画素 9002 には紫がかった映像が表示されることになる。

【0008】

よって、この欠陥部分の映像が目立ち、映像の劣化を引き起こしてしまう。

【0009】

そこで、本発明は上記の問題を鑑みてなされたものであり、欠陥画素を有する表示パネルを用いる場合においても、映像の劣化を防ぐことができる表示装置を提供するものである。

【0010】

10

【課題を解決するための手段】

本発明は、表示パネルに欠陥画素がある場合、その欠陥画素の位置座標を特定したデータに基づき所定の座標に相当する画素の輝度を上げ、所定の範囲における輝度の平均値（以下、平均輝度と呼ぶ）が一定となるようなデータ補正を行ない、映像表示を行うことを特徴としている。

【0011】

こうすることによって、欠陥画素がある表示パネルの映像において欠陥画素による劣化が目立たなくなり、映像の劣化を極力防ぐことができる。

【0012】

20

なお、欠陥画素の位置座標を特定する手段としては、公知の技術、例えば CCD カメラ等による撮像画像処理で特定する方法、 TFT 基板のみで OLED 素子と CCD カメラで特定する方法、 TFT 基板側に画素読み出し回路を混載して特定する方法等を用いればよい。

【0013】

なお、本発明においては、輝度の補正を行うための補正テーブルをあらかじめ作成しておいて、通常の使用時には、その補正テーブルによって映像データの補正が行われるようにする。

【0014】

また、欠陥画素が黒点ではなく輝点である場合には、そのレーザー等でリペアし黒点としてから上述の補正を実行する。

【0015】

30

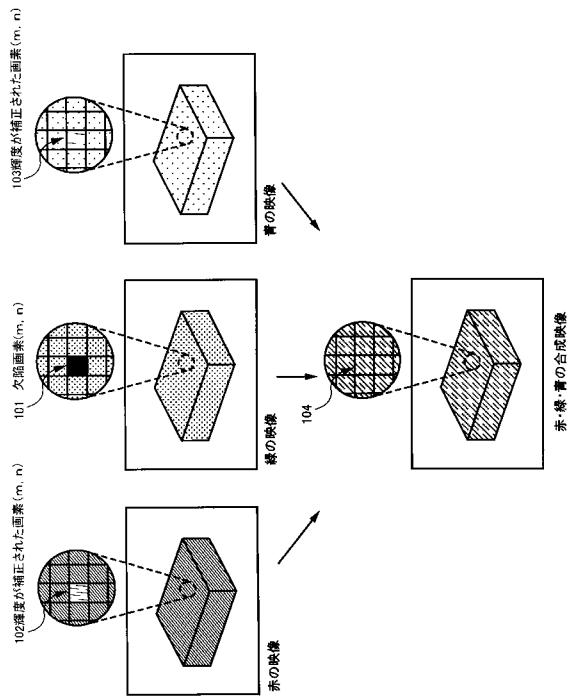

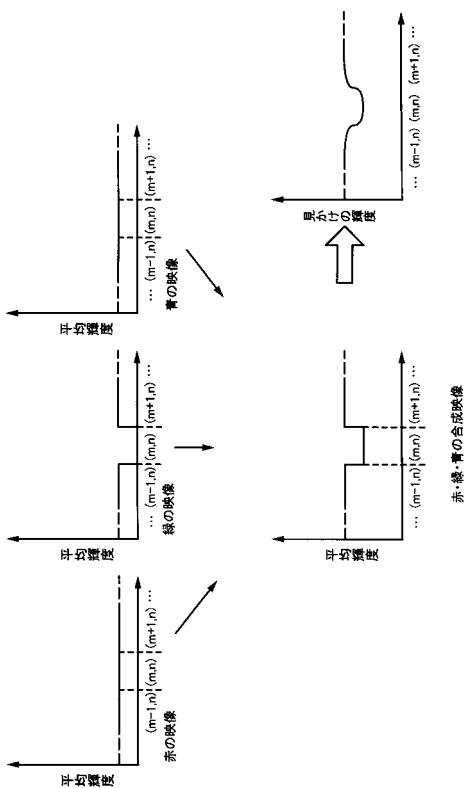

図1を参照する。図1には、3板式の投射型表示装置において、赤の映像と緑の映像と青の映像とが合成されてカラー映像が提供される様子が示されている。

【0016】

図1に示す例においては、緑の映像を表示する表示パネルに欠陥画素 101 が存在する。その欠陥画素 101 は黒点であるとする。その欠陥画素 101 が輝点である場合には、その欠陥画素にレーザー等の黒点化処理を行い黒点化させる。従って、緑の映像中には、その黒点による欠陥が表示されてしまう。ここで、赤の映像を表示する表示パネルおよび青の映像を表示する表示パネルには欠陥画素が無く、正常な映像が表示されるとする。従来では、赤、緑、青の各色の映像が合成されたカラー映像において、緑の映像に欠陥画素が存在していた結果、ある座標の緑の映像輝度がゼロとなり、赤の映像と青の映像のみが合成されて、その欠陥が存在する画素 104 には紫がかった映像が表示されることになる。このままでは画素 104 が目立ってしまい、良好な表示を得ることができない。

40

【0017】

そこで、本発明は、図1に示すように、赤の映像を表示する表示パネルおよび青の映像を表示する表示パネルにおいて、緑の映像を表示する表示パネルの欠陥画素と同座標 (m, n) の画素の輝度補正（具体的には、画素 102 および画素 103 の平均輝度を上げる補正）を行うことを特徴としている。人間の視覚は、色度感度よりも明暗感度に敏感である。従って、欠陥画素と同座標の画素の輝度を上げるだけで3つの表示パネルの映像を合成映像において欠陥画素が目立たなくなり、映像の劣化を極力防ぐことができる。

【0018】

50

勿論、ここでは3枚の表示パネルを用いた投射型表示装置における縁の表示パネルに欠陥画素が存在していた例を示したが、特に縁の表示パネルに限定されないことはいうまでもない。

【0019】

ここで、本願発明の構成を以下に記載する。

【0020】

本明細書で開示する発明の構成は、

3個の表示パネルを有する投射型の表示装置において、前記3個の表示パネルのうち欠陥画素を有する表示パネルを特定する手段と、

前記欠陥画素の座標を特定する手段と、

前記3個の表示パネルのうち前記欠陥画素を有する表示パネル以外の表示パネルにおいて前記欠陥画素の座標と同座標の画素の輝度を上げる手段とを有することを特徴とする欠陥画素補正システムである。 10

【0021】

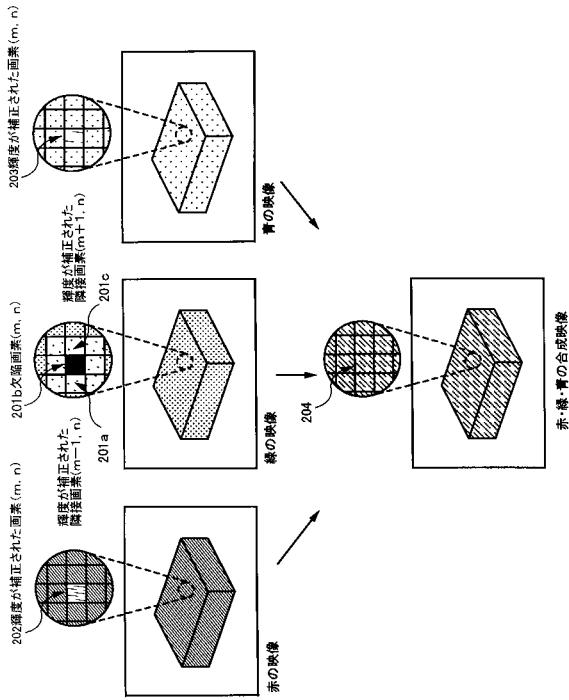

また、本明細書で開示する他の発明は、図3に示すように、上記構成に加え、さらに縁の表示パネルの欠陥画素と隣接する画素の輝度を上げる補正を行なうことを特徴としている。欠陥画素と同座標の画素の輝度を上げるとともに、隣接する画素の輝度を上げる補正を行うことによって、3つの表示パネルの合成映像における欠陥画素が目立たなくなり、映像の劣化を極力防ぐことができる。

【0022】

勿論、ここでは3枚の表示パネルを用いた投射型表示装置における縁の表示パネルに欠陥画素が存在していた例を示したが、特に縁の表示パネルに限定されないことはいうまでもない。 20

【0023】

本明細書で開示する他の発明の構成は、

3個の表示パネルを有する投射型の表示装置において、前記3個の表示パネルのうち欠陥画素を有する表示パネルを特定する手段と、

前記欠陥画素の座標を特定する手段と、

前記欠陥画素の座標と隣接する座標の画素の輝度を上げる手段と、

前記3個の表示パネルのうち前記欠陥画素を有する表示パネル以外の表示パネルにおいて前記欠陥画素の座標と同座標の画素の輝度を上げる手段とを有することを特徴とする欠陥画素補正システムである。 30

【0024】

また、本明細書で開示する他の発明の構成は、

光源と、

前記光源から出射された光を3つの光に分離する光学系と、

少なくとも1個の欠陥画素を有する1個の表示パネルを含む3個の表示パネルと、

前記3個の表示パネルの映像を合成し、スクリーンに投射する光学系と、

前記欠陥画素の存在する表示パネル以外の表示パネルにおいて前記欠陥画素の座標と同座標の画素の輝度を上げる欠陥画素補正システムとを有することを特徴とする投射型の表示装置である。 40

【0025】

また、本明細書で開示する他の発明は、

欠陥画素を有する1個の表示パネルを有する表示装置において、欠陥画素の位置座標を特定する手段と、

前記欠陥画素と隣接する画素の輝度を上げる手段と

を有することを特徴とする欠陥画素補正システムである。

【0026】

即ち、1枚の表示パネルを用いた直視型表示装置において、表示パネルの欠陥画素と隣接する画素の輝度を上げる補正を行なうことを特徴としている。隣接する画素の輝度を上げ 50

る補正を行うことで表示パネルの映像において欠陥画素が目立たなくなり、映像の劣化を極力防ぐことができる。特に、画素サイズが微小なものである場合には効果的である。

#### 【0027】

##### 【発明の実施の形態】

本願発明の実施形態について、以下に説明する。

#### 【0028】

ここで、図20に示すように緑の表示パネルに欠陥画素による黒点が座標(m, n)に一つ存在していた場合を仮定する。この時の座標(m, n)、座標(m-1, n)、及び座標(m+1, n)の各画素における平均輝度を図21に示した。この場合、赤、緑、青の各色の映像が合成されたカラー映像において、図21に示すように座標(m, n)の緑の平均輝度がゼロとなり、赤の平均輝度と青の平均輝度のみが合成される。色表示としては紫がかかった色が表示され、さらに合計された平均輝度も低下してしまっていた。10

#### 【0029】

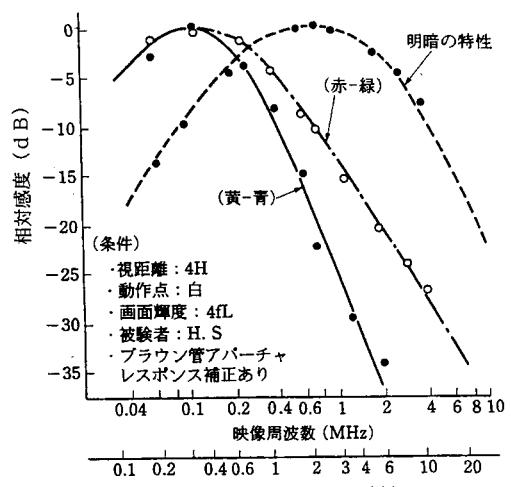

図22(テレビジョン学会誌: No. 3, pp. 29-35, 1977年)に示すように、人間の視覚は、空間周波数により明暗感度の特性と色度感度の特性が異なっている。色度感度と明暗感度とを比較すると、相対感度においては最大8:1(明暗感度: 色度感度)と色度感度のほうが低く、映像周波数は、空間周波数帯域の1/3~1/4となっている。即ち、人間の視覚は、色の認識力よりも明暗の認識力のほうが優れている。

#### 【0030】

従って、液晶パネルによる表示を人間の目で見た場合、欠陥画素による平均輝度の低下を認識しやすいため、欠陥画素の箇所が目立っていた。20

#### 【0031】

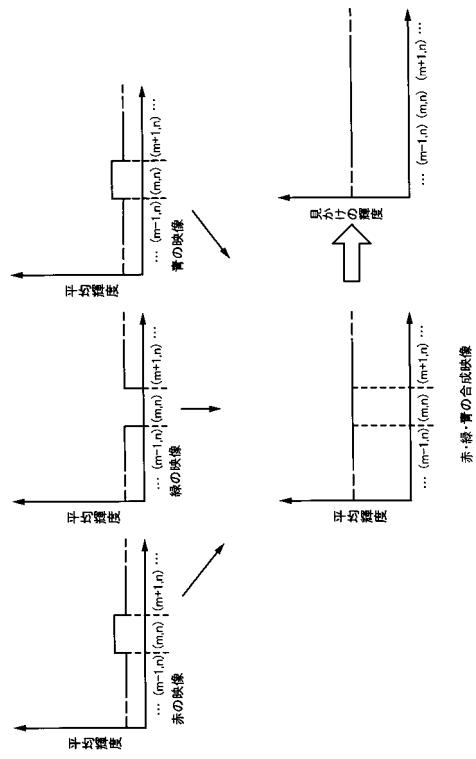

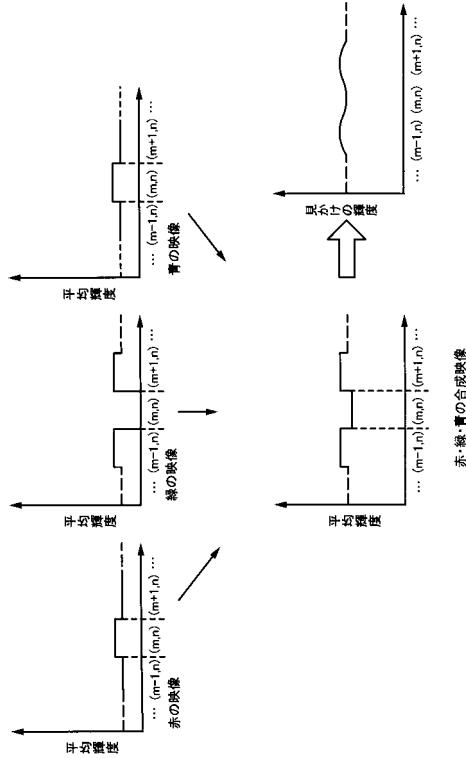

そこで、図2に示すように、緑以外の表示パネル(赤または青)の座標(m, n)に位置している画素の平均輝度をあげ、見かけの輝度が一定の値になるように補正することが本発明の特徴である。

#### 【0032】

なお、図2では赤及び青の表示パネルの座標(m, n)に位置している画素の輝度を両方あげ、見かけの輝度を一定とした例を示したが、特に限定されない。例えば、赤の表示パネルのみの平均輝度を上げる補正を行ってもよいし、青の表示パネルのみの平均輝度を上げる補正を行ってもよい。また、見かけの輝度も概略一定になることが好ましいが、従来(図21)よりも輝度差を緩和する程度の補正でも十分な効果が得られる。30

#### 【0033】

こうして、表示パネルに欠陥画素による黒点が存在している場合でも、人の目では欠陥画素の位置を認識不可能にすることができる。

#### 【0034】

また、上記構成に加え、図3及び図4に示すように、欠陥画素の座標(m, n)に隣接して位置している8個の座標(座標(m±1, n±1)、座標(m±1, n)、及び座標(m, n±1))の画素における平均輝度をあげ、見かけの輝度がほぼ一定の値になるように補正する構成としてもよい。なお、図3及び図4では、緑の表示パネルにおける欠陥画素(m, n)に隣接して位置している8個の座標の平均輝度をあげた例を示したが、赤の表示パネルにおける8個の座標の平均輝度を上げてもよいし、青の表示パネルにおける8個の座標の平均輝度を上げてもよいし、全ての表示パネル(赤、青、緑)における8個の座標の平均輝度を上げてもよい。また、欠陥画素に隣接する8個の画素に限定されることなく、そのうちの数個であってもよいし、8個以上の画素の平均輝度を上げる補正を行ってもよい。40

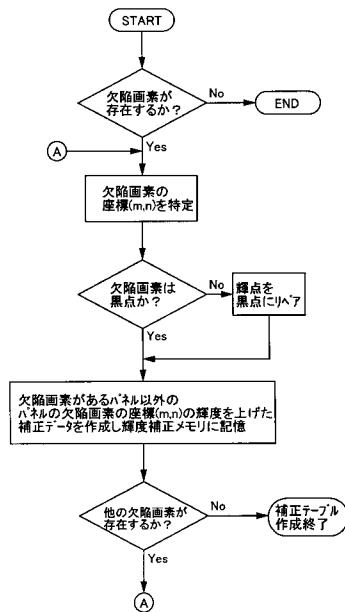

#### 【0035】

ここで、本発明における欠陥画素補正システムの動作の流れを図5のフローチャートを用いて説明する。ここでは液晶パネルを表示装置に組み込む前に欠陥画素補正システムの補正テーブルを作成する手法について説明する。

#### 【0036】

10

20

30

40

50

まず、液晶パネルに欠陥画素が存在するかを確認する。欠陥画素が存在するかを確認する手段としては、公知の技術、例えば C C D カメラ等による撮像画像処理で特定する方法、T F T 基板のみで O E 素子と C C D カメラで特定する方法、T F T 基板側に画素読み出し回路を混載して特定する方法等を用いればよい。

【 0 0 3 7 】

欠陥画素が存在しないなら終了し、欠陥画素のない正常なパネルとして使用できる。もし、欠陥画素が存在するならば、その欠陥画素の座標を特定する。そして、欠陥画素が黒点か輝点かを確認する。本明細書では、黒点とは光の透過率が終始ほぼ 0 % ( 任意単位 ) となっている画素の状態をいい、輝点とは光の透過率が終始ほぼ 1 0 0 % ( 任意単位 ) となっている画素の状態をいう。もし、欠陥画素が輝点であれば、レーザー等によって黒点にリペアする。

【 0 0 3 8 】

そして、欠陥画素座標入力回路に欠陥画素の座標を入力し、その欠陥画素がある液晶パネルを赤、緑、青のいずれかの映像の表示に使用するかを入力する。この入力によって、欠陥画素がある液晶パネル以外の液晶パネルに映像を供給するデジタルビデオデータ補正回路では、欠陥画素と同座標の画素の輝度を上げるための補正データが作成され、輝度補正メモリに記憶される。

【 0 0 3 9 】

上述の操作を全ての欠陥画素について繰り返す ( " A " に戻る )。全ての欠陥画素について補正データの作成が終了したら、その液晶パネルの補正データの作成が終了し補正テーブルが完成する。同様に、表示装置に組み込む 3 個の液晶パネル全てについての補正テーブルの作成を行い、対応する輝度補正メモリに記憶させる。

【 0 0 4 0 】

次いで、補正テーブルの作成が終了した 3 個の液晶パネルを表示装置に組み込む。

【 0 0 4 1 】

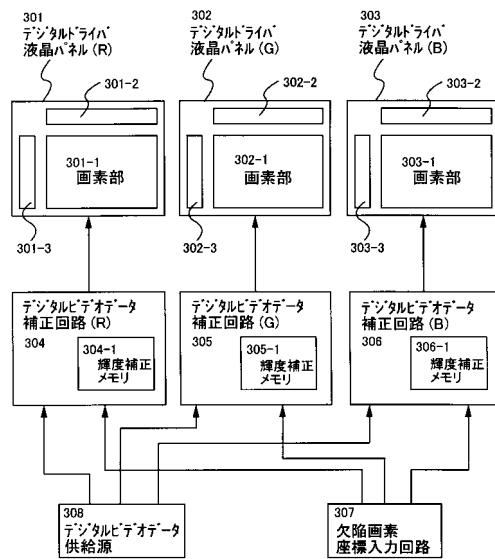

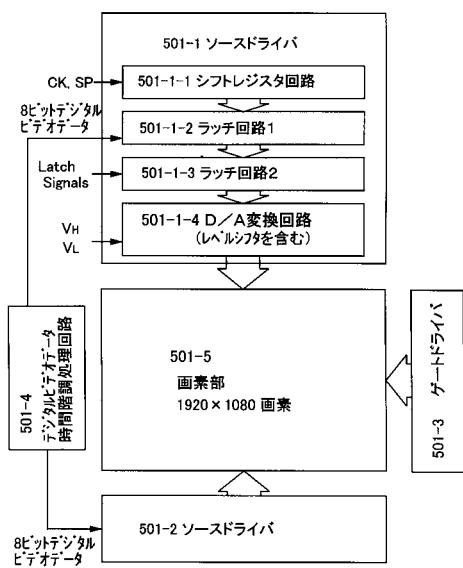

ここで、上記補正テーブルが記憶された輝度補正メモリを組み込んだ回路ブロック図の一例を図 6 を用いて説明する。

【 0 0 4 2 】

3 0 1、3 0 2 および 3 0 3 は表示パネルであり、ここでは、デジタルドライバを有する液晶パネルである。3 0 1、3 0 2、3 0 3 はそれぞれ、赤 ( R )、緑 ( G )、青 ( B ) の映像を画素部に表示する。3 0 1 - 2、3 0 2 - 2 および 3 0 3 - 2 はソースドライバ、3 0 1 - 3、3 0 2 - 3 および 3 0 3 - 3 はゲートドライバである。なお、液晶パネル 3 0 1、3 0 2 および 3 0 3 は全て同じ仕様の液晶パネルである。また、投射型の表示装置の表示パネルとして用いられ得るものであれば、液晶パネル以外のものを用いても良い。

【 0 0 4 3 】

外部にあるデジタルビデオデータ供給源 3 0 8 からデジタルビデオデータが、デジタルビデオデータ補正回路 3 0 4、3 0 5、3 0 6 に供給される。デジタルビデオデータ補正回路 ( R ) 3 0 4 には赤の映像を形成するデジタルビデオデータが、デジタルビデオデータ補正回路 ( G ) 3 0 5 には緑の映像を形成するデジタルビデオデータが、またデジタルビデオデータ補正回路 ( B ) 3 0 6 には青の映像を形成するデジタルビデオデータがそれぞれ供給される。

【 0 0 4 4 】

デジタルビデオデータ補正回路 3 0 4、3 0 5、3 0 6 は、それぞれ液晶パネル 3 0 1、3 0 2、3 0 3 にデジタルビデオデータを供給する。なお、デジタルビデオデータ補正回路 3 0 4、3 0 5、3 0 6 は、それぞれ輝度補正メモリを有している。また、デジタルビデオデータ補正回路は、入力されたデジタルビデオデータを輝度補正メモリ 3 0 4 - 1、3 0 5 - 1、3 0 6 - 1 に記憶されたテーブルに基づいて補正し、補正したデジタルビデオデータを液晶パネルに供給する。

【 0 0 4 5 】

10

20

40

50

欠陥画素座標入力回路 307 は、入力された欠陥画素の座標情報を前記欠陥画素の無い液晶パネルのデジタルビデオデータ補正回路に送出する。この座標情報に基づき、デジタルビデオデータ補正回路は、補正テーブルを作成し輝度補正メモリに記憶する。

#### 【0046】

表示装置の動作中は、外部からデジタルビデオデータがデジタルビデオデータ補正回路に入力され、作成された補正テーブルに従ってデジタルビデオデータが変換され補正デジタルビデオデータが作成される。補正デジタルビデオデータは、液晶パネルに入力され、液晶パネルは補正デジタルビデオデータをもとに映像を表示する。

#### 【0047】

なお、ここでは、デジタルドライバを有する液晶パネルを例にとって示したが、アナログドライバを有する液晶パネルにも本発明は適用し得る。その場合、デジタルビデオデータ補正回路から供給されるデジタルビデオデータは、D/A 変換回路でアナログビデオデータに変換された後、液晶パネルに入力されることになる。10

#### 【0048】

また、上記欠陥画素補正システムを表示装置、特に投射型表示装置に組み込み一体化させることは可能である。

#### 【0049】

また、上記欠陥画素補正システムに加え、ガンマ補正等の画像補正を行ってもよい。

#### 【0050】

また、上記構成においては 3 個のパネルを用いた例を示したが、1 個のパネルを用いた場合においても、欠陥画素に隣接する 8 個の画素の輝度を補正することによって、欠陥画素を人の目に目立たないようにすることができます。特に、微小な画素サイズである場合、効果的である。20

#### 【0051】

以上の構成でなる本願発明について、以下に示す実施例でもってさらに詳細な説明を行うこととする。

#### 【0052】

##### 【実施例】

##### 【実施例 1】

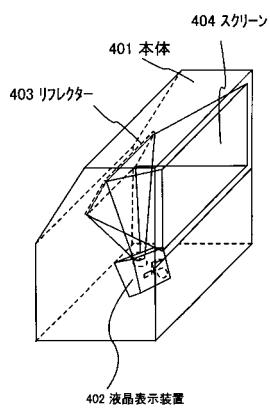

本実施例では、本発明の投射型表示装置の例としてリアプロジェクタを示す。図 7 には、本実施例のリアプロジェクタの透視図が示されている。401 はリアプロジェクタ本体、402 は本発明の投射型表示装置、403 はリフレクタ、404 はスクリーンである。30

#### 【0053】

投射型表示装置は、液晶パネルを 3 枚用い、光源（ここでは白色光源）と、一定の波長域の光のみを反射し、他の光を透過させるダイクロイックミラーと、全反射ミラー等を備えている。

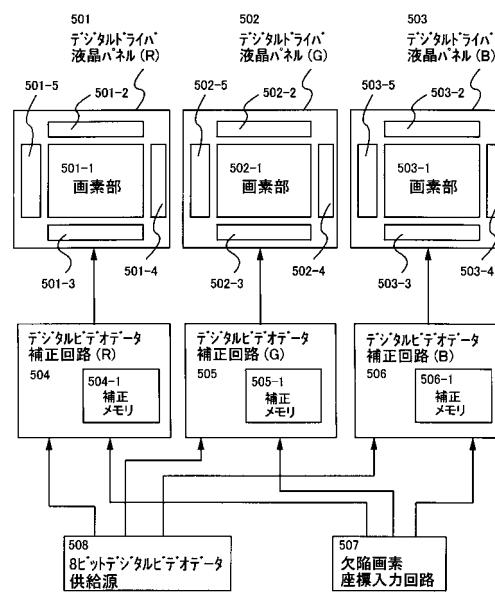

#### 【0054】

ここでは、デジタルドライバを有する液晶パネルを用いた。液晶パネルは、赤（R）、緑（G）、青（B）の映像を表示する画素部、ソースドライバ、ゲートドライバ、デジタルビデオデータ分割回路等を備えている。なお、3 枚の液晶パネルは全て同じ仕様の液晶パネルである。40

#### 【0055】

外部にあるデジタルビデオデータ供給源から 8 ビットデジタルビデオデータが、デジタルビデオデータ補正回路に供給される。デジタルビデオデータ補正回路（R）には赤の映像を形成する 8 ビットデジタルビデオデータが、デジタルビデオデータ補正回路（G）には緑の映像を形成する 8 ビットデジタルビデオデータが、またデジタルビデオデータ補正回路（B）には青の映像を形成する 8 ビットデジタルビデオデータがそれぞれ供給される。

#### 【0056】

デジタルビデオデータ補正回路は、それぞれの液晶パネルに 8 ビットデジタルビデオデータを供給する。なお、デジタルビデオデータ補正回路は、それぞれ輝度補正メモリを有し50

ている。また、デジタルビデオデータ補正回路は、入力された8ビットデジタルビデオデータを輝度補正メモリに記憶された補正テーブルに基づいて補正し、補正されたデジタルビデオデータを液晶パネルに供給する。

【0057】

欠陥画素座標入力回路は、入力された欠陥画素の座標情報を欠陥画素の無い液晶パネルのデジタルビデオデータ補正回路に送出する。この座標情報に基づき、デジタルビデオデータ補正回路は、補正データを作成し輝度補正メモリに記憶する。

【0058】

なお、補正テーブルの作成のステップは実施の形態で述べた通りである。

【0059】

こうすることによって、3つ表示パネルの映像を合成映像において欠陥画素が目立たなくなり、映像の劣化を極力防ぐことができる。よって、少々欠陥画素が存在する液晶パネルをも有効に用いることができる。

【0060】

[実施例2]

本実施例においては、上述の実施例1とは異なる構成を有する3板式のプロジェクタについて説明する。

【0061】

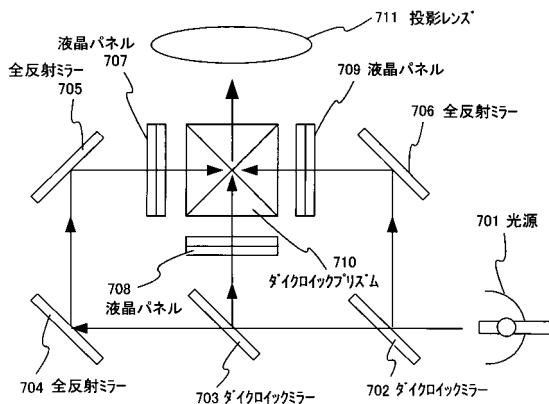

図10において、701は光源、702および703はダイクロイックミラー、704、705および706は全反射ミラー、707、708および709は液晶パネル、710はダイクロイックプリズム、711は投影レンズである。

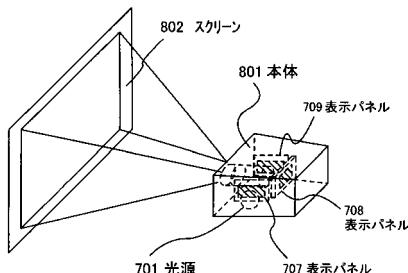

【0062】

また、図11は、図10に示した光学エンジンをフロントプロジェクタに組み込んだ図である。なお、図11において図10に対応する部分は同一の符号を用いた。図11中、801は本体、802はスクリーンである。

【0063】

[実施例3]

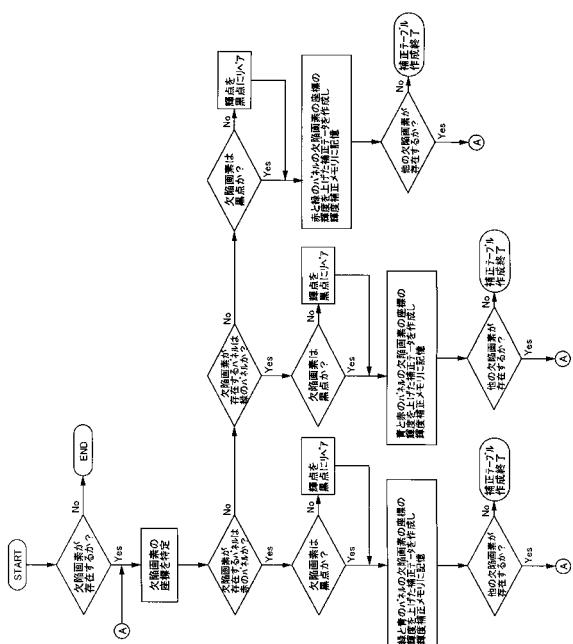

本実施例では実施例1とは異なる本発明における欠陥画素補正システムの操作方法のフローチャートを図12に示す。なお、ここでは、3個の液晶パネルを既に組み込んである表示装置に対応させた例について説明する。

【0064】

まず、表示装置を動作させ、スクリーンに投射されたカラー映像に欠陥画素が存在するかを確認する。欠陥画素が存在しないなら終了し、以後通常の使用を行う。もし、欠陥画素が存在するならば、欠陥画素の座標を特定する。そして、欠陥画素が存在する液晶パネルが、赤、緑、青のいずれの映像を表示するパネルなのかを特定する。

【0065】

当該欠陥画素が存在する液晶パネルが赤の液晶パネルであれば、その欠陥画素が黒点かどうかを確認する。その欠陥画素が黒点であれば、欠陥画素座標入力回路に欠陥画素の座標を入力する。欠陥画素座標入力回路は、緑と青の液晶パネルに映像を供給するデジタルビデオデータ補正回路に欠陥画素の座標を送出する。デジタルビデオデータ補正回路は、欠陥画素と同座標の画素の輝度を上げるデータを作成し、輝度補正メモリに記憶する。

【0066】

当該欠陥画素が存在する液晶パネルが緑の液晶パネルであれば、その欠陥画素が黒点かどうかを確認する。その欠陥画素が黒点であれば、欠陥画素座標入力回路に欠陥画素の座標を入力する。欠陥画素座標入力回路は、青と赤の液晶パネルに映像を供給するデジタルビデオデータ補正回路に欠陥画素の座標を送出する。デジタルビデオデータ補正回路は、欠陥画素と同座標の画素の輝度を上げるデータを作成し、輝度補正メモリに記憶する。

【0067】

当該欠陥画素が存在する液晶パネルが赤の液晶パネルでもなく緑の液晶パネルでもない場合は、青の液晶パネルに欠陥画素が存在することになる。この場合も、その欠陥画素が黒

10

20

30

40

50

点かどうかを確認する。その欠陥画素が黒点であれば、欠陥画素座標入力回路に欠陥画素の座標を入力する。欠陥画素座標入力回路は、赤と緑の液晶パネルに映像を供給するデジタルビデオデータ補正回路に欠陥画素の座標を送出する。デジタルビデオデータ補正回路は、欠陥画素と同座標の画素の輝度を上げるデータを作成し、輝度補正メモリに記憶する。

#### 【0068】

上述のステップを全ての欠陥画素について繰り返す（“A”に戻る）。

#### 【0069】

この様にして、表示装置に組み込む3個の液晶パネル全てについての補正データの作成が終了し、補正テーブルが完成する。

10

#### 【0070】

以後、入力されるデジタルビデオデータは、デジタルビデオデータ補正回路の輝度補正メモリに記憶された補正テーブルに基づいて変換される。

#### 【0071】

こうすることによって、3つの表示パネルの合成映像において欠陥画素が目立たなくなり、映像の劣化を極力防ぐことができる。よって、いくつか欠陥画素が存在する液晶パネルをも有効に用いて良好な表示装置を提供することができ、生産性が向上する。

#### 【0072】

#### [実施例4]

本実施例では、本発明に用いる液晶パネルの作製方法例について説明する。ここでは画素部の画素TFTと、画素部の周辺に設けられる駆動回路（ソースドライバ、ゲートドライバ、D/A変換回路、デジタルビデオデータ時間階調処理回路等）のTFTを同一基板上に作製する方法について工程に従って詳細に説明する。但し、説明を簡単にするために、駆動回路ではシフトレジスタ回路、パッファ回路、D/A変換回路などの基本回路であるCMOS回路と、nチャネル型TFTとを図示することにする。

20

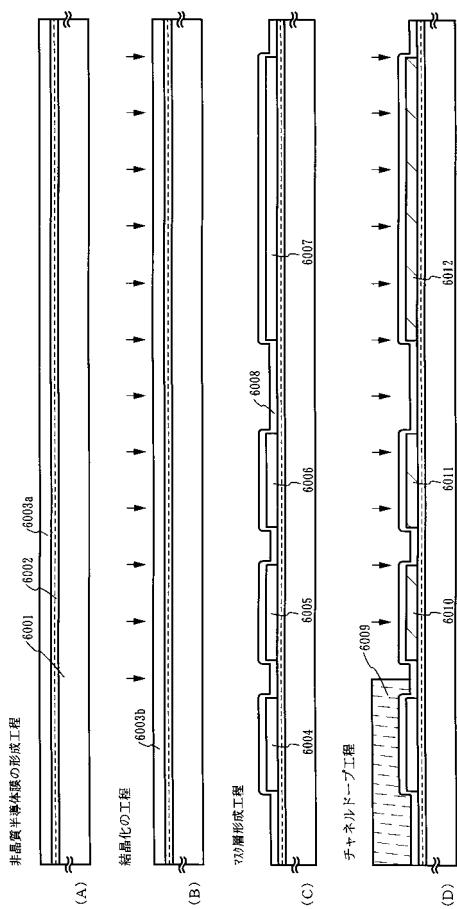

#### 【0073】

図13(A)において、基板6001には低アルカリガラス基板や石英基板を用いることができる。本実施例では低アルカリガラス基板を用いた。この場合、ガラス歪み点よりも10~20程度低い温度であらかじめ熱処理しておいても良い。この基板6001のTFTを形成する表面には、基板6001からの不純物拡散を防ぐために、酸化シリコン膜、窒化シリコン膜または酸化窒化シリコン膜などの下地膜6002を形成する。例えば、プラズマCVD法でSiH<sub>4</sub>、NH<sub>3</sub>、N<sub>2</sub>Oから作製される酸化窒化シリコン膜を100nm、同様にSiH<sub>4</sub>、N<sub>2</sub>Oから作製される酸化窒化シリコン膜を100nmの厚さに積層形成する。

30

#### 【0074】

次に、20~150nm(好ましくは30~80nm)の厚さで非晶質構造を有する半導体膜6003aを、プラズマCVD法やスパッタ法などの公知の方法で形成する。本実施例では、プラズマCVD法で非晶質シリコン膜を55nmの厚さに形成した。非晶質構造を有する半導体膜としては、非晶質半導体膜や微結晶半導体膜があり、非晶質シリコンゲルマニウム膜などの非晶質構造を有する化合物半導体膜を適用しても良い。また、下地膜6002と非晶質シリコン膜6003aとは同じ成膜法で形成することが可能であるので、両者を連続形成しても良い。下地膜を形成した後、一旦大気雰囲気に晒さないことでその表面の汚染を防ぐことが可能となり、作製するTFTの特性バラツキやしきい値電圧の変動を低減させることができる。(図13(A))

40

#### 【0075】

そして、公知の結晶化技術を使用して非晶質シリコン膜6003aから結晶質シリコン膜6003bを形成する。例えば、レーザー結晶化法や熱結晶化法(固相成長法)を適用すれば良いが、ここでは、特開平7-130652号公報で開示された技術に従って、触媒元素を用いる結晶化法で結晶質シリコン膜6003bを形成した。結晶化の工程に先立つて、非晶質シリコン膜の含有水素量にもよるが、400~500で1時間程度の熱処理

50

を行い、含有水素量を 5 atom% 以下にしてから結晶化させることが望ましい。非晶質シリコン膜を結晶化させると原子の再配列が起こり緻密化するので、作製される結晶質シリコン膜の厚さは当初の非晶質シリコン膜の厚さ（本実施例では 55 nm）よりも 1 ~ 15 % 程度減少した。（図 13 (B)）

#### 【0076】

そして、結晶質シリコン膜 6003b を島状に分割して、島状半導体層 6004 ~ 6007 を形成する。その後、プラズマ CVD 法またはスパッタ法により 50 ~ 100 nm の厚さの酸化シリコン膜によるマスク層 6008 を形成する。（図 13 (C)）

#### 【0077】

そしてレジストマスク 6009 を設け、n チャネル型 TFT を形成する島状半導体層 6005 ~ 6007 の全面にしきい値電圧を制御する目的で  $1 \times 10^{16} \sim 5 \times 10^{17}$  atoms/cm<sup>3</sup> 程度の濃度で p 型を付与する不純物元素としてボロン (B) を添加した。ボロン (B) の添加はイオンドープ法で実施しても良いし、非晶質シリコン膜を成膜するときに同時に添加しておくこともできる。ここでボロン (B) 添加は必ずしも必要でないが、ボロン (B) を添加した半導体層 6010 ~ 6012 は n チャネル型 TFT のしきい値電圧を所定の範囲内に収めるために形成することが好ましかった。（図 13 (D)）

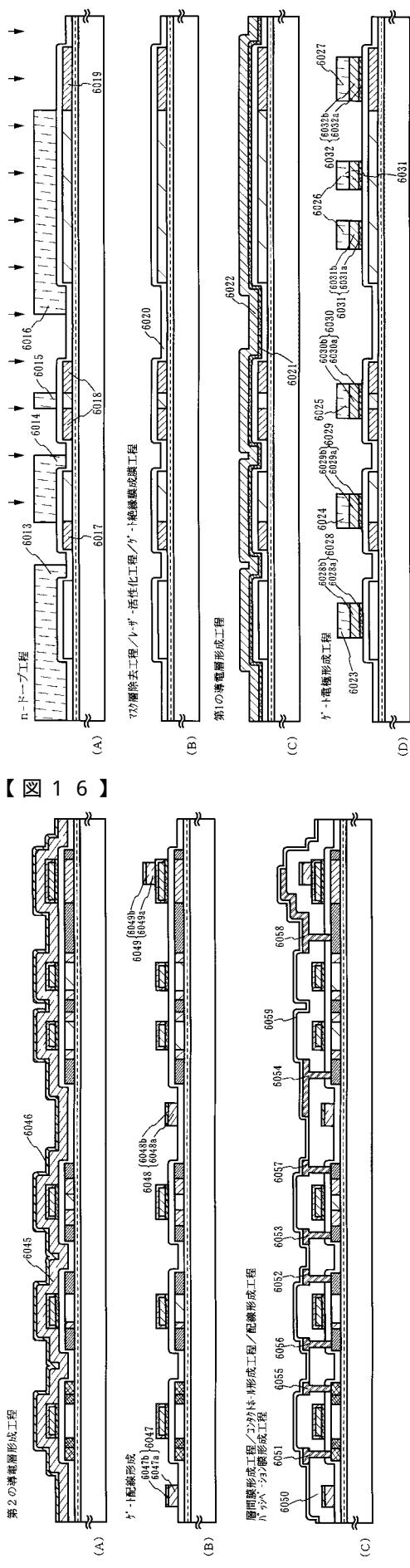

#### 【0078】

駆動回路の n チャネル型 TFT の LDD 領域を形成するために、n 型を付与する不純物元素を島状半導体層 6010、6011 に選択的に添加する。そのため、あらかじめレジストマスク 6013 ~ 6016 を形成した。n 型を付与する不純物元素としては、リン (P) や砒素 (As) を用いれば良く、ここではリン (P) を添加すべく、フォスフィン (PH<sub>3</sub>) を用いたイオンドープ法を適用した。形成された不純物領域 6017、6018 のリン (P) 濃度は  $2 \times 10^{16} \sim 5 \times 10^{19}$  atoms/cm<sup>3</sup> の範囲とすれば良い。本明細書中では、ここで形成された不純物領域 6017 ~ 6019 に含まれる n 型を付与する不純物元素の濃度を (n<sup>-</sup>) と表す。また、不純物領域 6019 は、画素部の保持容量を形成するための半導体層であり、この領域にも同じ濃度でリン (P) を添加した。（図 14 (A)）

#### 【0079】

次に、マスク層 6008 をフッ酸などにより除去して、図 13 (D) と図 14 (A) で添加した不純物元素を活性化させる工程を行う。活性化は、窒素雰囲気中で 500 ~ 600 で 1 ~ 4 時間の熱処理や、レーザー活性化の方法により行うことができる。また、両者を併用して行っても良い。本実施例では、レーザー活性化の方法を用い、KrF エキシマレーザー光（波長 248 nm）を用い、線状ビームを形成して、発振周波数 5 ~ 50 Hz、エネルギー密度 100 ~ 500 mJ/cm<sup>2</sup> として線状ビームのオーバーラップ割合を 80 ~ 98 % として走査して、島状半導体層が形成された基板全面を処理した。尚、レーザー光の照射条件には何ら限定される事項はなく、実施者が適宜決定すれば良い。

#### 【0080】

そして、ゲート絶縁膜 6020 をプラズマ CVD 法またはスパッタ法を用いて 10 ~ 250 nm の厚さでシリコンを含む絶縁膜で形成する。例えば、120 nm の厚さで酸化窒化シリコン膜を形成する。ゲート絶縁膜には、他のシリコンを含む絶縁膜を単層または積層構造として用いても良い。（図 14 (B)）

#### 【0081】

次に、ゲート電極を形成するために第 1 の導電層を成膜する。この第 1 の導電層は単層で形成しても良いが、必要に応じて二層あるいは三層といった積層構造としても良い。本実施例では、導電性の窒化物金属膜から成る導電層 (A) 6021 と金属膜から成る導電層 (B) 6022 とを積層させた。導電層 (B) 6022 はタンタル (Ta)、チタン (Ti)、モリブデン (Mo)、タンゲステン (W) から選ばれた元素、または前記元素を主成分とする合金か、前記元素を組み合わせた合金膜（代表的には Mo-W 合金膜、Mo-Ta 合金膜）で形成すれば良く、導電層 (A) 6021 は窒化タンタル (Ta<sub>N</sub>)、窒化タンゲステン (WN)、窒化チタン (TiN) 膜、窒化モリブデン (MoN) で形成する

10

20

20

30

40

50

。また、導電層（A）6021は代替材料として、タンゲステンシリサイド、チタンシリサイド、モリブデンシリサイドを適用しても良い。導電層（B）は低抵抗化を図るために含有する不純物濃度を低減させると良く、特に酸素濃度に関しては30 ppm以下とすると良かった。例えば、タンゲステン（W）は酸素濃度を30 ppm以下とすることで20 μ cm以下の比抵抗値を実現することができた。

#### 【0082】

導電層（A）6021は10～50 nm（好ましくは20～30 nm）とし、導電層（B）6022は100～400 nm（好ましくは250～350 nm）とすれば良い。本実施例では、導電層（A）6021に30 nmの厚さの窒化タンタル膜を、導電層（B）6022には350 nmのTa膜を用い、いずれもスパッタ法で形成した。このスパッタ法による成膜では、スパッタ用のガスのArに適量のXeやKrを加えておくと、形成する膜の内部応力を緩和して膜の剥離を防止することができる。尚、図示しないが、導電層（A）6021の下に2～20 nm程度の厚さでリン（P）をドープしたシリコン膜を形成しておくことは有効である。これにより、その上に形成される導電膜の密着性向上と酸化防止を図ると同時に、導電層（A）または導電層（B）が微量に含有するアルカリ金属元素がゲート絶縁膜6020に拡散するのを防ぐことができる。（図14（C））

#### 【0083】

次に、レジストマスク6023～6027を形成し、導電層（A）6021と導電層（B）6022とを一括でエッチングしてゲート電極6028～6031と容量配線6032を形成する。ゲート電極6028～6031と容量配線6032は、導電層（A）から成る6028a～6032aと、導電層（B）から成る6028b～6032bとが一体として形成されている。この時、駆動回路に形成するゲート電極6029、6030は不純物領域6017、6018の一部と、ゲート絶縁膜6020を介して重なるように形成する。（図14（D））

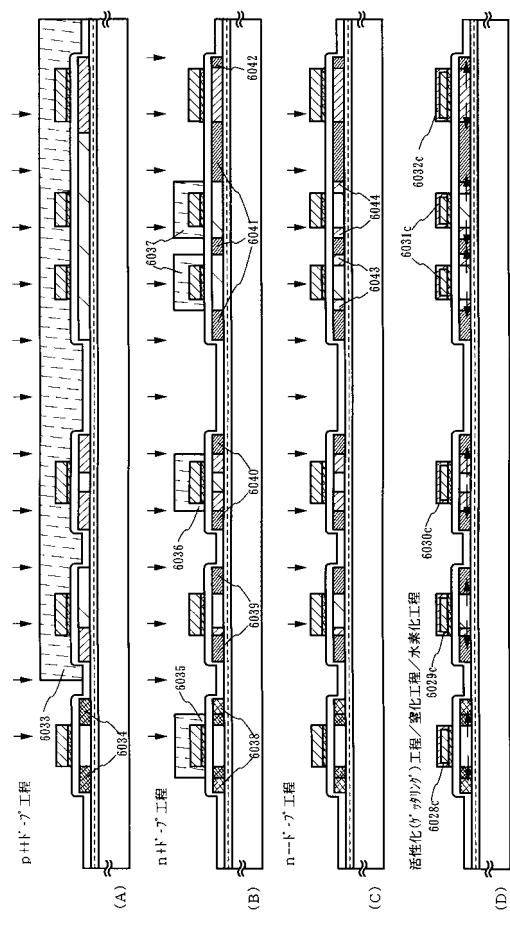

#### 【0084】

次いで、駆動回路のpチャネル型TFTのソース領域およびドレイン領域を形成するために、p型を付与する不純物元素を添加する工程を行う。ここでは、ゲート電極6028をマスクとして、自己整合的に不純物領域を形成する。このとき、nチャネル型TFTが形成される領域はレジストマスク6033で被覆しておく。そして、ジボラン（B<sub>2</sub>H<sub>6</sub>）を用いたイオンドープ法で不純物領域6034を形成した。この領域のボロン（B）濃度は $3 \times 10^{20} \sim 3 \times 10^{21}$  atoms/cm<sup>3</sup>となるようにする。本明細書中では、ここで形成された不純物領域6034に含まれるp型を付与する不純物元素の濃度を（p<sup>+</sup>）と表す。（図15（A））

#### 【0085】

次に、nチャネル型TFTにおいて、ソース領域またはドレイン領域として機能する不純物領域の形成を行った。レジストのマスク6035～6037を形成し、n型を付与する不純物元素が添加して不純物領域6038～6042を形成した。これは、フォスフィン（PH<sub>3</sub>）を用いたイオンドープ法で行い、この領域のリン（P）濃度を $1 \times 10^{20} \sim 1 \times 10^{21}$  atoms/cm<sup>3</sup>とした。本明細書中では、ここで形成された不純物領域6038～6042に含まれるn型を付与する不純物元素の濃度を（n<sup>+</sup>）と表す。（図15（B））

#### 【0086】

不純物領域6038～6042には、既に前工程で添加されたリン（P）またはボロン（B）が含まれているが、それに比して十分に高い濃度でリン（P）が添加されるので、前工程で添加されたリン（P）またはボロン（B）の影響は考えなくても良い。また、不純物領域6038に添加されたリン（P）濃度は図15（A）で添加されたボロン（B）濃度の1/2～1/3なのでp型の導電性が確保され、TFTの特性に何ら影響を与えることはなかった。

#### 【0087】

そして、画素部のnチャネル型TFTのLDD領域を形成するためのn型を付与する不純物添加の工程を行った。ここではゲート電極6031をマスクとして自己整合的にn型を

10

20

30

40

50

付与する不純物元素をイオンドープ法で添加した。添加するリン( P )の濃度は  $1 \times 10^{16} \sim 5 \times 10^{18}$  atoms / cm<sup>3</sup> であり、図 14 ( A ) および図 15 ( A ) と図 15 ( B ) で添加する不純物元素の濃度よりも低濃度で添加することで、実質的には不純物領域 6043 、 6044 のみが形成される。本明細書中では、この不純物領域 6043 、 6044 に含まれる n 型を付与する不純物元素の濃度を ( n<sup>-</sup> ) と表す。( 図 15 ( C ) )

#### 【 0088 】

その後、それぞれの濃度で添加された n 型または p 型を付与する不純物元素を活性化するために熱処理工程を行う。この工程はファーネスアニール法、レーザーアニール法、またはラピッドサーマルアニール法 ( R T A 法) で行うことができる。ここではファーネスアニール法で活性化工程を行った。熱処理は酸素濃度が 1 ppm 以下、好ましくは 0.1 ppm 以下の窒素雰囲気中で 400 ~ 800 、代表的には 500 ~ 600 で行うものであり、本実施例では 550 で 4 時間の熱処理を行った。また、基板 6001 に石英基板のような耐熱性を有するものを使用した場合には、 800 で 1 時間の熱処理としても良く、不純物元素の活性化と、該不純物元素が添加された不純物領域とチャネル形成領域との接合を良好に形成することができた。

#### 【 0089 】

この熱処理において、ゲート電極 6028 ~ 6031 と容量配線 6032 形成する金属膜 6028b ~ 6032b は、表面から 5 ~ 80 nm の厚さで導電層 ( C ) 6028c ~ 6032c が形成される。例えば、導電層 ( B ) 6028b ~ 6032b がタンゲステン ( W ) の場合には窒化タンゲステン ( WN ) が形成され、タンタル ( Ta ) の場合には窒化タンタル ( TaN ) を形成することができる。また、導電層 ( C ) 6028c ~ 6032c は、窒素またはアンモニアなどを用いた窒素を含むプラズマ雰囲気にゲート電極 6028 ~ 6031 を晒しても同様に形成することができる。さらに、 3 ~ 100 % の水素を含む雰囲気中で、 300 ~ 450 で 1 ~ 12 時間の熱処理を行い、島状半導体層を水素化する工程を行った。この工程は熱的に励起された水素により半導体層のダングリングボンドを終端する工程である。水素化の他の手段として、プラズマ水素化 ( プラズマにより励起された水素を用いる ) を行っても良い。

#### 【 0090 】

島状半導体層が、非晶質シリコン膜から触媒元素を用いる結晶化の方法で作製された場合、島状半導体層中には微量の触媒元素が残留した。勿論、そのような状態でも TFT を完成させることができると、残留する触媒元素を少なくともチャネル形成領域から除去する方がより好ましかった。この触媒元素を除去する手段の一つにリン( P )によるゲッタリング作用を利用する手段があった。ゲッタリングに必要なリン( P )の濃度は図 15 ( B ) で形成した不純物領域 ( n<sup>+</sup> ) と同程度であり、ここで実施される活性化工程の熱処理により、n チャネル型 TFT および p チャネル型 TFT のチャネル形成領域から触媒元素をゲッタリングすることができた。( 図 15 ( D ) )

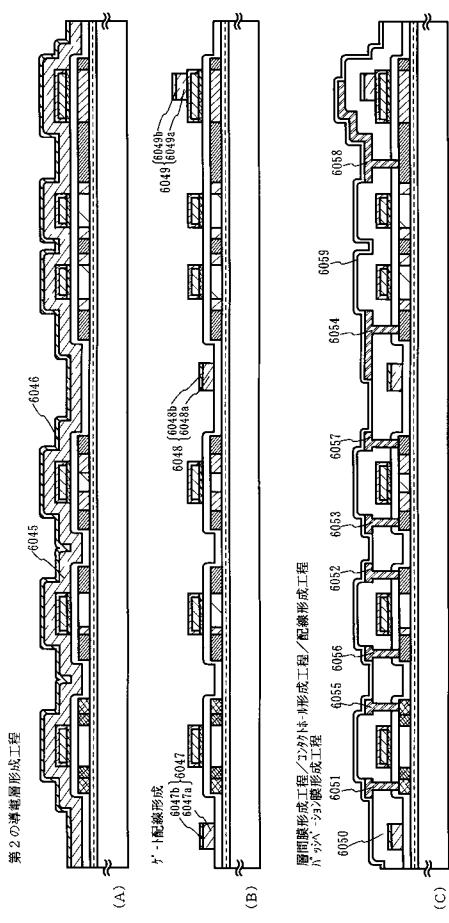

#### 【 0091 】

活性化および水素化の工程が終了したら、ゲート配線とする第 2 の導電膜を形成する。この第 2 の導電膜は低抵抗材料であるアルミニウム ( Al ) や銅 ( Cu ) を主成分とする導電層 ( D ) と、チタン ( Ti ) やタンタル ( Ta ) 、タンゲステン ( W ) 、モリブデン ( Mo ) から成る導電層 ( E ) とで形成すると良い。本実施例では、チタン ( Ti ) を 0.1 ~ 2 重量 % 含むアルミニウム ( Al ) 膜を導電層 ( D ) 6045 とし、チタン ( Ti ) 膜を導電層 ( E ) 6046 として形成した。導電層 ( D ) 6045 は 100 ~ 400 nm ( 好ましくは 250 ~ 350 nm ) とすれば良く、導電層 ( E ) 6046 は 50 ~ 200 ( 好ましくは 100 ~ 150 nm ) で形成すれば良い。( 図 16 ( A ) )

#### 【 0092 】

そして、ゲート電極に接続するゲート配線を形成するために導電層 ( E ) 6046 と導電層 ( D ) 6045 とをエッチング処理して、ゲート配線 6047 、 6048 と容量配線 6049 を形成した。エッチング処理は最初に SiCl<sub>4</sub> と Cl<sub>2</sub> と BC<sub>1</sub><sub>3</sub> との混合ガスを用いたドライエッチング法で導電層 ( E ) の表面から導電層 ( D ) の途中まで除去し、その

10

20

30

40

50

後リン酸系のエッティング溶液によるウエットエッティングで導電層（D）を除去することにより、下地との選択加工性を保ってゲート配線を形成することができた。

#### 【0093】

第1の層間絶縁膜6050は500～1500nmの厚さで酸化シリコン膜または酸化窒化シリコン膜で形成され、その後、それぞれの島状半導体層に形成されたソース領域またはドレイン領域に達するコンタクトホールを形成し、ソース配線6051～6054と、ドレイン配線6055～6058を形成する。図示していないが、本実施例ではこの電極を、Ti膜を100nm、Tiを含むアルミニウム膜300nm、Ti膜150nmをスパッタ法で連続して形成した3層構造の積層膜とした。

#### 【0094】

次に、パッシベーション膜6059として、窒化シリコン膜、酸化シリコン膜、または窒化酸化シリコン膜を50～500nm（代表的には100～300nm）の厚さで形成する。この状態で水素化処理を行うとTFTの特性向上に対して好ましい結果が得られた。例えば、3～100%の水素を含む雰囲気中で、300～450で1～12時間の熱処理を行うと良く、あるいはプラズマ水素化法を用いても同様の効果が得られた。なお、ここで後に画素電極とドレイン配線を接続するためのコンタクトホールを形成する位置において、パッシベーション膜6059に開口部を形成しておいても良い。（図16（C））

#### 【0095】

その後、有機樹脂からなる第2の層間絶縁膜6060を1.0～1.5μmの厚さに形成する。有機樹脂としては、ポリイミド、アクリル、ポリアミド、ポリイミドアミド、BCB（ベンゾシクロブテン）等を使用することができる。ここでは、基板に塗布後、熱重合するタイプのポリイミドを用い、300で焼成して形成した。そして、第2の層間絶縁膜6060にドレイン配線6058に達するコンタクトホールを形成し、画素電極6061、6062を形成する。画素電極は、透過型液晶表示装置とする場合には透明導電膜を用いれば良く、反射型の液晶表示装置とする場合には金属膜を用いれば良い。本実施例では透過型の液晶表示装置するために、酸化インジウム・スズ（ITO）膜を100nmの厚さにスパッタ法で形成した。（図17）

#### 【0096】

こうして同一基板上に、駆動回路のTFTと画素部の画素TFTとを有した基板を完成させることができた。駆動回路にはpチャネル型TFT6101、第1のnチャネル型TFT6102、第2のnチャネル型TFT6103、画素部には画素TFT6104、保持容量6105が形成した。本明細書では便宜上このような基板をアクティブマトリクス基板と呼ぶ。

#### 【0097】

駆動回路のpチャネル型TFT6101には、島状半導体層6004にチャネル形成領域6106、ソース領域6107a、6107b、ドレイン領域6108a、6108bを有している。第1のnチャネル型TFT6102には、島状半導体層6005にチャネル形成領域6109、ゲート電極6029と重なるLDD領域6110（以降、このようなLDD領域をLovと記す）、ソース領域6111、ドレイン領域6112を有している。このLov領域のチャネル長方向の長さは0.5～3.0μm、好ましくは1.0～1.5μmとした。第2のnチャネル型TFT6103には、島状半導体層6006にチャネル形成領域6113、LDD領域6114、6115、ソース領域6116、ドレイン領域6117を有している。このLDD領域はLov領域とゲート電極6030と重ならないLDD領域（以降、このようなLDD領域をLooffと記す）とが形成され、このLooff領域のチャネル長方向の長さは0.3～2.0μm、好ましくは0.5～1.5μmである。画素TFT6104には、島状半導体層6007にチャネル形成領域6118、6119、Looff領域6120～6123、ソースまたはドレイン領域6124～6126を有している。Looff領域のチャネル長方向の長さは0.5～3.0μm、好ましくは1.5～2.5μmである。さらに、容量配線6032、6049と、ゲート絶縁膜と同じ材料から成る絶縁膜と、画素TFT6104のドレイン領域6126に接続し、n型を付与する不

10

20

30

40

50

純物元素が添加された半導体層 6127 とから保持容量 6105 が形成されている。図 17 では画素 TFT 6104 をダブルゲート構造としたが、シングルゲート構造でも良いし、複数のゲート電極を設けたマルチゲート構造としても差し支えない。

#### 【0098】

次に、公知の方法を用いて、対向電極 6068 および配向膜 6069 が形成された基板 6067 とアクティブマトリクス基板とをシール剤（図示せず）で貼り合せる。その後、液晶 6070 を注入し、封止剤（図示せず）で封止する。本実施例では、ネマチック液晶を用いてツイストネマチックモード（TN モード）により表示を実現する。

#### 【0099】

以上をもって本実施例の液晶パネルが完成する。

10

#### 【0100】

以上の様に本実施例では、画素 TFT および駆動回路が要求する仕様に応じて各回路を構成する TFT の構造を最適化し、半導体装置の動作性能と信頼性を向上させた。さらにゲート電極を耐熱性を有する導電性材料で形成することにより LDD 領域やソース領域およびドレイン領域の活性化を容易とし、ゲート配線低抵抗材料で形成することにより、配線抵抗を十分低減できる。従って、画素部（画面サイズ）が 4 インチクラス以上の表示装置にも適用することができる。

#### 【0101】

また、本実施例で完成した液晶パネルを実施例 1 乃至 3 のいずれか一に用いることは可能である。

20

#### 【0102】

##### [実施例 5]

実施例 1 では 3 個の表示パネルを用いた表示装置の一例を示したが、本実施例では、1 個の表示パネルを用いた表示装置の一例を示す。

#### 【0103】

1 個の表示パネルにおいて座標 (m, n) の位置に欠陥画素が存在しているとする。

#### 【0104】

本実施例では、欠陥画素の座標 (m, n) に隣接して位置している座標 ( $m \pm 1, n \pm 1$ ) の画素における平均輝度をあげ、見かけの輝度がほぼ一定の値になるように補正する。また、欠陥画素に隣接して位置している座標 ( $m \pm 1, n \pm 1$ ) だけでなく、座標 ( $m \pm 2, n \pm 2$ ) に位置している画素における平均輝度をあげてもよい。

30

#### 【0105】

このように欠陥画素に隣接する画素の輝度を補正することによって、表示パネルに存在している欠陥画素を人の目では、ほとんど認識することができないようにすることができる。本実施例においては、画素サイズが微小である場合、特に効果的である。

#### 【0106】

##### 【発明の効果】

従来では、欠陥画素が数個あるだけで表示不良と見なされていた。また、微小かつ高精細であるため、欠陥画素の全くない表示パネルを作製することは非常に困難であり、歩留まりが非常に低かった。

40

#### 【0107】

しかし、本発明により欠陥画素がある表示パネルであっても、欠陥画素のまったくない表示パネルと同等の表示レベルを実現することができる。従って、作製プロセスを変更することなく製品歩留まりを大幅に向上させることができる。

#### 【0108】

例えば、60 インチのリアプロジェクターの場合、3H (2.2 m) で見えた画質劣化レベルが、本発明を利用することによって 4H (3 m) で見えた画質劣化レベルと同等のものが得られる。

#### 【0109】

また、直視パネルの表示装置の場合においても非常に近距離で見ても、画質劣化の少ない

50

ものが得られる。

【0110】

【図面の簡単な説明】

- 【図1】 本発明の概念を示す図である。

- 【図2】 本発明の概念を示す模式図である。

- 【図3】 本発明の概念を示す図である。

- 【図4】 本発明の概念を示す模式図である。

- 【図5】 本発明における欠陥画素補正システムの補正テーブル作成のフローチャートである。

- 【図6】 本発明の投射型表示装置のある実施形態の回路ブロック図である。 10

- 【図7】 リアプロジェクタの外観を示す図である。

- 【図8】 実施例1の投射型表示装置の回路ブロック図である。

- 【図9】 実施例1の液晶パネルの回路ブロック図である。

- 【図10】 本発明の投射型表示装置の構成を示す図である。

- 【図11】 本発明の投射型表示装置の外観を示す図である。

- 【図12】 実施例3における欠陥画素補正システムの補正テーブル作成のフローチャートである。 20

- 【図13】 AM-LCDの作製工程を示す図である。

- 【図14】 AM-LCDの作製工程を示す図である。

- 【図15】 AM-LCDの作製工程を示す図である。

- 【図16】 AM-LCDの作製工程を示す図である。

- 【図17】 アクティブマトリクス型液晶表示装置の断面構造図である。

- 【図18】 3板式の投射型表示装置の構成例である。

- 【図19】 3つの映像が合成されてカラー映像が形成される様子を示す図である。

- 【図20】 1つの表示パネルに1つの欠陥画素がある場合のカラー映像が形成される様子を示す図である。(従来例)

- 【図21】 1つの表示パネルに1つの欠陥画素がある場合のカラー映像が形成される様子を示す模式図である。(従来例)

- 【図22】 色度及び明度の空間周波数特性の一例を示す図である。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【 図 1 0 】

【 111 】

【习题 1 2】

【 义 1 3 】

【 図 1 4 】

【図15】

【 図 1 6 】

【図17】

【図18】

【図19】

青の映像

緑の映像

赤の映像

赤・緑・青の合成映像

【図20】

【図21】

【図22】

色度および明度の空間周波数特性の一例

---

フロントページの続き

| (51)Int.Cl. |       | F I       |         |              |

|-------------|-------|-----------|---------|--------------|

| G 0 3 B     | 21/14 | (2006.01) | G 0 3 B | 21/14 Z      |

| G 0 9 G     | 3/20  | (2006.01) | G 0 9 G | 3/20 6 4 1 P |

| H 0 4 N     | 9/12  | (2006.01) | G 0 9 G | 3/20 6 7 0 A |

|             |       |           | G 0 9 G | 3/20 6 8 0 C |

|             |       |           | H 0 4 N | 9/12 B       |

(56)参考文献 特表平05-506108(JP,A)

特開平08-054855(JP,A)

特開2001-109423(JP,A)

特開平05-134268(JP,A)

特開平07-261719(JP,A)

特開2001-188514(JP,A)

(58)調査した分野(Int.Cl., DB名)

G09G 3/00 - 3/38

G02F 1/133 505-580

G03B 21/14