(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5362985号

(P5362985)

(45) 発行日 平成25年12月11日(2013.12.11)

(24) 登録日 平成25年9月13日(2013.9.13)

(51) Int.Cl.

F 1

|              |           |             |      |

|--------------|-----------|-------------|------|

| HO1L 21/768  | (2006.01) | HO1L 21/90  | N    |

| HO1L 23/532  | (2006.01) | HO1L 21/302 | 101B |

| HO1L 21/3065 | (2006.01) | HO1L 21/302 | 104H |

| HO1L 21/312  | (2006.01) | HO1L 21/312 | A    |

| HO1L 21/316  | (2006.01) | HO1L 21/312 | N    |

請求項の数 5 (全 10 頁) 最終頁に続く

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2007-515228 (P2007-515228)  |

| (86) (22) 出願日 | 平成17年5月23日 (2005.5.23)        |

| (65) 公表番号     | 特表2008-502140 (P2008-502140A) |

| (43) 公表日      | 平成20年1月24日 (2008.1.24)        |

| (86) 国際出願番号   | PCT/US2005/018050             |

| (87) 国際公開番号   | W02005/117085                 |

| (87) 国際公開日    | 平成17年12月8日 (2005.12.8)        |

| 審査請求日         | 平成20年3月31日 (2008.3.31)        |

| 審判番号          | 不服2012-2811 (P2012-2811/J1)   |

| 審判請求日         | 平成24年2月14日 (2012.2.14)        |

| (31) 優先権主張番号  | 10/709722                     |

| (32) 優先日      | 平成16年5月25日 (2004.5.25)        |

| (33) 優先権主張国   | 米国(US)                        |

|           |                                                                                                                                        |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------|

| (73) 特許権者 | 390009531<br>インターナショナル・ビジネス・マシーンズ・コーポレーション<br>INTERNATIONAL BUSINESS MACHINES CORPORATION<br>アメリカ合衆国10504 ニューヨーク州 アーモンク ニュー オーチャード ロード |

| (74) 代理人  | 100108501<br>弁理士 上野 剛史                                                                                                                 |

| (74) 代理人  | 100112690<br>弁理士 太佐 稔一                                                                                                                 |

| (74) 代理人  | 100091568<br>弁理士 市位 嘉宏                                                                                                                 |

最終頁に続く

(54) 【発明の名称】空隙を有する半導体デバイスの形成方法および該方法によって形成された構造

## (57) 【特許請求の範囲】

## 【請求項 1】

基板上に第1の金属配線レベルを提供するステップであって、当該第1の金属配線レベルは、第1の誘電材料と第2の誘電材料とを交互に積層した第1の交互層を含むステップと、

前記第1の金属配線レベルに、当該第1の金属配線レベルの上面から前記基板の上面に至る、第1のトレンチおよび第2のトレンチを形成するステップと、

前記第1の金属配線レベルを選択的にエッチングして、前記第1のトレンチおよび前記第2のトレンチ内に露出する前記第1の交互層のうち前記第1の誘電材料を有する各層内の前記第1の誘電材料の全部でない少なくとも一部分を除去して当該各層に第1の空隙を形成し、前記第2の誘電材料を本質的にエッチングされていないままにしておくステップと、

前記第1の空隙の形成後の前記第1の金属配線レベルの表面を覆う第1の共形ライナを付着させて、前記第1の金属配線レベルの表面を密封するステップと、

前記第1の共形ライナの付着後の前記第1の金属配線レベルの表面を覆う導電材料を付着させて、前記第1のトレンチおよび前記第2のトレンチを当該導電材料で埋めるステップと、

前記第1の金属配線レベルの表面を研磨して、前記第1のトレンチおよび前記第2のトレンチ内の前記導電材料を残し、前記第1の金属配線レベルの表面の余分な導電材料を除去するステップと、

10

20

前記研磨後の第1の金属配線レベルの表面を覆う絶縁層を付着させるステップと、前記絶縁層上に第2の金属配線レベルを提供するステップであって、当該第2の金属配線レベルは、第3の誘電材料と第4の誘電材料とを交互に積層した第2の交互層を含むステップと、

前記第2の金属配線レベルに、当該第2の金属配線レベルの上面から前記第1のトレンチ内の前記導電材料の上面に至る、第3のトレンチを形成するステップであって、当該第3のトレンチは、前記第2の交互層内の開口が前記絶縁層内の開口よりも大きいデュアル・ダマシン構造を有するステップと、

前記第2の金属配線レベルを選択的にエッチングして、前記第3のトレンチ内に露出する前記第2の交互層のうち前記第3の誘電材料を有するそれぞれの層内の前記第3の誘電材料の全部でない少なくとも一部分を除去して当該それぞれの層に第2の空隙を形成し、前記第4の誘電材料を本質的にエッチングされていないままにしておくステップと、

前記第2の空隙の形成後の前記第2の金属配線レベルの表面を覆う第2の共形ライナを付着させて、前記第2の金属配線レベルの表面を密封するステップと、

前記第2の共形ライナの付着後の前記第2の金属配線レベルの表面を覆う導電材料を付着させて、前記第3のトレンチを当該導電材料で埋めるステップと、

前記第2の金属配線レベルの表面を研磨して、前記第3のトレンチ内の前記導電材料を残し前記第2の金属配線レベルの表面の余分な導電材料を除去するステップと、を含み、

前記第1の金属配線レベルの表面を覆う絶縁層を付着させるステップは、前記第2の金属配線レベルを選択的にエッチングするステップ中にエッチングされにくい、前記第1および第2の金属配線レベル間のバイアの高さを定める0.1~1.0ミクロンの厚さの多孔質層のみを付着させる、

半導体デバイスの形成方法。

#### 【請求項2】

前記第2の金属配線レベルを選択的にエッチングするステップから前記第2の金属配線レベルの表面を研磨するステップまでの代わりに、

前記第2の金属配線レベルに、当該第2の金属配線レベルの上面から前記絶縁層の上面に至る、第4のトレンチを形成するステップと、

前記第2の金属配線レベルを選択的にエッチングして、前記第3のトレンチおよび前記第4のトレンチ内に露出する前記第2の交互層のうち前記第3の誘電材料を有するそれぞれの層内の前記第3の誘電材料の全部でない少なくとも一部分を除去して当該それぞれの層に第2の空隙を形成し、前記第4の誘電材料を本質的にエッチングされていないままにしておくステップと、

前記第2の空隙の形成後の前記第2の金属配線レベルの表面を覆う第2の共形ライナを付着させて、前記第2の金属配線レベルの表面を密封するステップと、

前記第2の共形ライナの付着後の前記第2の金属配線レベルの表面を覆う導電材料を付着させて、前記第3のトレンチおよび前記第4のトレンチを当該導電材料で埋めるステップと、

前記第2の金属配線レベルの表面を研磨して、前記第3のトレンチおよび前記第4のトレンチ内の前記導電材料を残し、前記第2の金属配線レベルの表面の余分な導電材料を除去するステップと、を含む請求項1に記載の方法。

#### 【請求項3】

前記第1および前記第3の誘電材料が有機誘電材料を含み、前記第2および前記第4の誘電材料が無機誘電材料を含む、請求項1または2に記載の方法。

#### 【請求項4】

前記第1および前記第2の共形ライナが、SiCOH、SiO<sub>2</sub>、SiN、SiCおよびSiCNからなるグループから選択された材料を含む、請求項1~3のいずれか1項に記載の方法。

#### 【請求項5】

前記第1および前記第3の誘電材料が、ポリアリーレンエーテル(SiLK(商標))

10

20

30

40

50

、パリレン( N )、パリレン( F )、T e f l o n 、多孔質ポリアリーレンエーテル( S i L K (商標) )、多孔質パリレン( N )、多孔質パリレン( F )および多孔質 T e f l o n からなるグループから選択された有機誘電材料を含み、

前記第2および前記第4の誘電材料が、O S G 、S i O<sub>2</sub> 、F S G 、M S Q 、多孔質O S G 、多孔質S i O<sub>2</sub> 、多孔質F S G および多孔質M S Q からなるグループから選択された無機誘電材料を含む、請求項1、2または4のいずれか1項に記載の方法。

**【発明の詳細な説明】**

**【技術分野】**

**【0 0 0 1】**

本発明は一般に半導体デバイスに関し、詳細には、配線レベル(配線高さ)内に空隙を有する半導体デバイスの形成方法および該方法によって形成された構造に関する。 10

**【背景技術】**

**【0 0 0 2】**

半導体デバイスが縮小し続けるにつれデバイス・フィーチャ間の距離は短くなる。金属配線層内においてフィーチャ間の距離が短くなると静電容量が増大する。したがって半導体デバイス業界では、デバイス・フィーチャ間の距離を短くしても低い静電容量を維持することができ、上記の問題およびその他の問題を解決する、半導体デバイスの形成方法が求められている。

**【発明の開示】**

**【発明が解決しようとする課題】**

**【0 0 0 3】**

本発明は、金属配線レベル内に空隙を有し上述の問題を解決する半導体デバイスの形成方法および該方法によって形成された構造に関する。 20

**【課題を解決するための手段】**

**【0 0 0 4】**

本発明の第1の態様は、第1の誘電材料と第2の誘電材料の交互層を付着させるステップであって、第1の誘電材料と第2の誘電材料が異なる速度で選択的にエッチング可能であるステップと、誘電材料の交互層内に第1のフィーチャを形成するステップと、誘電材料の交互層を選択的にエッチングして、第1の誘電材料を有するそれぞれの層内の第1の誘電材料の全部でなくとも一部分を除去し、第2の誘電材料を本質的にエッチングされていないままにしておくステップとを含む、半導体デバイスの形成方法を提供する。 30

**【0 0 0 5】**

本発明の第2の態様は、第1の絶縁材料と第2の絶縁材料の交互層を付着させるステップと、ダマシン・フィーチャを形成するステップと、第1の絶縁材料の層内に開口を形成するステップとを含む、半導体デバイスの形成方法を提供する。

**【0 0 0 6】**

本発明の第3の態様は、第1の誘電材料と第2の誘電材料の交互層を有し、第1の誘電材料と第2の誘電材料の交互層内に形成された第1のフィーチャを有する金属配線レベルと、第1の誘電材料内の複数の開口とを含む半導体デバイスを提供する。

**【0 0 0 7】**

本発明の第4の態様は、交互層をなす複数の第1および第2の絶縁層であって、第1の絶縁層と第2の絶縁層のエッチング速度が異なる複数の絶縁層と、第1および第2の絶縁層内に形成された第1のフィーチャと、選択エッチング中に形成された複数の第1の絶縁層内の複数の開口とを含む半導体デバイスを提供する。 40

**【0 0 0 8】**

本発明の上記の特徴および利点ならびに他の特徴および利点は、本発明の実施形態の以下のより詳細な説明から明白となろう。

**【0 0 0 9】**

次に、図面を参照して本発明の実施形態を詳細に説明する。それらの図面では同様の符号が同様の要素を指示する。 50

【発明を実施するための最良の形態】

【0010】

次に、本発明のあるいくつかの実施形態を示し詳細に説明するが、それらの実施形態には、添付の請求項の範囲を逸脱しないさまざまな変更および修正を加えることができるこ<sup>10</sup>とを理解されたい。本発明の範囲は、本明細書に記載された構成要素の数、構成要素の材料、構成要素の形状、構成要素の相対的な配置等に限定されない。図面は本発明を例示することを目的としているが、それらの図面は一様な尺度で描かれているわけではない。

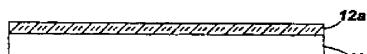

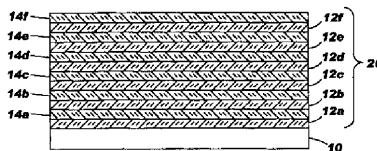

【0011】

図1に、その上に第1の絶縁層12aが形成されたプリメタル誘電体(p r e - m e t a l d i e l e c t r i c : PMD)10の断面図を示す。<sup>10</sup> PMD10はSiO<sub>2</sub>ベースの材料などの1種または数種の誘電材料、すなわちSiO<sub>2</sub>、PSG、BPSG、SiCOH(OSG)、SiLK(商標)(Dow Chemical Corp.)、SiN、SiC、SiCN、C-H等を含む。第1の絶縁層12aは誘電材料を含み、この例ではポリアリーレンエーテル(SiLK(商標))、パリレン(NまたはF)、Teflon、これらの膜の多孔質膜などの有機誘電材料を含む。使用する有機誘電材料のタイプは、使用する付着技法に応じて決定することができる。例えば、化学蒸着(CVD)またはプラズマ化学蒸着(PECVD)を使用して第1の絶縁層12aを形成する場合には、パリレン(NまたはF)、Teflonまたはこれらの膜の多孔質膜を使用することができる。しかし、スピノン付着を使用して第1の絶縁層12aを形成する場合には、SiLK(商標)を使用することができる。第1の絶縁層12aは5~<sup>20</sup> 10nmの厚さに形成することができる。

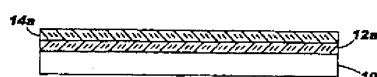

【0012】

次いで、図2に示すように、第1の絶縁層12a上に第2の絶縁層14aを形成する。<sup>20</sup> 第2の絶縁層14aは誘電材料を含み、この例ではSiCOH(OSG)、SiO<sub>2</sub>、フッ素化SiO<sub>2</sub>(FSG)、メチルシルセスキオキサン(MSQ)、これらの材料の多孔質膜などの無機誘電材料を含む。第1の絶縁層12aと同様に、第2の絶縁層14aは、CVD、PECVD、スピノン付着または他の同様の付着技法を使用して形成することができる。第2の絶縁層14aは5~10nmの厚さに形成することができる。

【0013】

図3に示すように、第2の絶縁層14a上に第3の絶縁層12bを形成する。<sup>30</sup> 第3の絶縁層12bは第1の絶縁層12aと同様の有機誘電材料を含む。第3の絶縁層12bは第1の絶縁層12aと同様の技法を使用して形成され、第1の絶縁層12aと同様の厚さを有する。

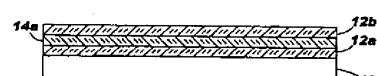

【0014】

図4に示すように、第3の絶縁層12b上に第4の絶縁層14bを形成する。<sup>30</sup> 第4の絶縁層14bは第2の絶縁層14aと同様の無機誘電材料を含む。第4の絶縁層14bは第2の絶縁層14aと同様の技法を使用して形成され、第2の絶縁層14aと同様の厚さを有する。

【0015】

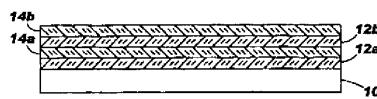

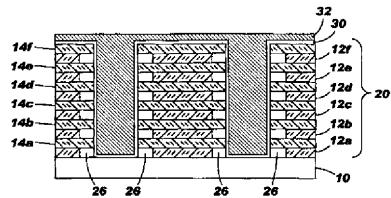

このようにして、基板10上に、図5に示すような有機誘電材料と無機誘電材料の交互層を、第1の金属配線レベル20として望ましい厚さに形成することができる。この例では層12c~12fが、第1および第3の絶縁層12a、12bと同様の有機誘電材料を含む。同様に層14c~14fは、第2および第4の絶縁層14a、14bと同様の無機誘電材料を含む。本発明において描かれる層の数は単に例示のためのものであって、限定を意図したものではなく、少なくとも1つの有機層と少なくとも1つの無機層が存在すればよい。同様に、この例において有機誘電材料を最初に付着させたのは単に例示のためにあることに留意されたい。最初に付着させるのは無機誘電材料でもまたは有機誘電材料でもよい。

【0016】

また、この有機絶縁材料と無機絶縁材料の交互層をin-situで付着させることが<sup>50</sup>

望ましい場合があることにも留意されたい。例えば、単一の P E C V D 室を使用し、この室から外に出すことなく、無機層と有機層の両方を付着させることができる。また、スピニ塗布トラックを使用し、この交互層の付着と硬化の両方を同じ室内で実施することもできる。あるいは、いずれかの技法を使用して、所望の厚さの 2 倍の厚さを有する第 1 の絶縁層 1 2 a を付着させることもできる。その後、第 1 の絶縁層 1 2 a をプラズマ処理または熱処理にかけ、第 1 の絶縁層 1 2 a の上部を、第 2 の絶縁層 1 4 a において必要な材料に転化させる。これらの方法は、有機絶縁層と無機絶縁層の間の厚さの不ぞろいを低下させるのに役立ち、有機絶縁層と無機絶縁層の間の付着力を増大させることができる。

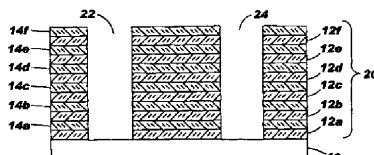

#### 【 0 0 1 7 】

第 1 の配線レベル 2 0 として望ましい厚さを達成した後、図 6 に示すように、第 1 の配線レベル 2 0 内に、第 1 のフィーチャ 2 2 およびこの例では第 2 のフィーチャ 2 4 を形成する。第 1 および第 2 のフィーチャ 2 2 、 2 4 は配線ライン用のワイヤ・トレチであり、従来のパターン形成技法および従来のエッティング技法を使用して形成することができる。

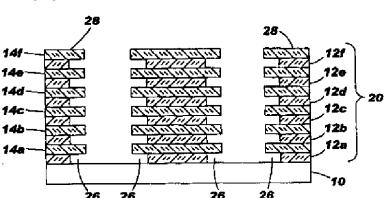

#### 【 0 0 1 8 】

第 1 および第 2 のフィーチャ 2 2 、 2 4 の形成に続いて、第 1 の配線レベル 2 0 内の有機誘電材料の少なくとも一部分、この例では層 1 2 a ~ 1 2 f 内の有機誘電材料の少なくとも一部分を除去するための選択エッティングを実行する（図 7）。有機誘電材料が p - S i L K (商標) を含み、無機誘電材料が p - O S G を含むこの例では、 N<sub>2</sub> プラズマ、 H<sub>2</sub> プラズマまたは他の同様のプラズマ・エッティングを使用して、この有機誘電材料を選択的に除去することができる。この N<sub>2</sub> または H<sub>2</sub> エッティングは、約 3 ~ 2 0 0 mT の圧力範囲において、平行プレートまたは高密度プラズマの一般的なパワーおよびフロー条件で実施することができる。あるいは、 1 0 0 : 1 D H F などの湿式エッティング剤を使用して無機誘電材料 ( p - O S G ) の部分をエッティングし、層 1 2 a ~ 1 2 f 内の S i L K (商標) 材料を残してもよい。

#### 【 0 0 1 9 】

層 1 2 a ~ 1 2 f 内の有機誘電材料の選択エッティングの結果、図 7 に示すように開口ないし空隙 2 6 が形成される。層 1 2 a ~ 1 2 f の有機誘電材料のエッティング速度は層 1 4 a ~ 1 4 f の無機誘電材料のエッティング速度よりも大きいため、空隙 2 6 は、層 1 2 a ~ 1 2 f の有機誘電材料内に形成され、層 1 4 a ~ 1 4 f の無機誘電材料内には形成されない。第 1 の配線レベル 2 0 内の空隙 2 6 はデバイス全体の静電容量を低減させる。空隙 2 6 のサイズは、有機誘電材料の全部でない一部分を除去するようにこの選択エッティングを調整することによって決定する。デバイスの機械的破損、例えば無機誘電層 1 4 a ~ 1 4 f の崩壊を防ぐため、この選択エッティング後に少なくとも一部の有機誘電材料が残っていなければならない。

#### 【 0 0 2 0 】

下表 1 に、さまざまな有機および無機材料を使用したデバイスの、空隙 2 6 がある場合との場合の静電容量値の推定による比較を示す。具体的にはこれらのデータは、ワイヤ幅が約 1 0 0 n m 、ワイヤ間隔が約 1 0 0 n m であり、このワイヤ間隔内の 1 0 0 n m の有機誘電体のうち約 3 3 n m が除去された第 1 の配線レベル 2 0 を有するサンプルからモデル化したものである。この比較によれば K e f f (デバイスの有効誘電率) は約 2 0 % 低減し、 K e f f はデバイスの静電容量に比例するため、この値はデバイスの静電容量の約 2 0 % の低減に相当する。

#### 【 0 0 2 1 】

10

20

30

40

## 【表1】

表1：空隙がある場合のK<sub>e f f</sub>と空隙がない場合のK<sub>e f f</sub>の比較

| 無機誘電体                     | 有機誘電体          | K <sub>e f f</sub><br>(空隙なし) | K <sub>e f f</sub><br>(空隙あり) | K <sub>e f f</sub> の低減% |

|---------------------------|----------------|------------------------------|------------------------------|-------------------------|

| SiO <sub>2</sub> (K=4)    | SiLK(K=2.6)    | 3.30                         | 2.70                         | 18%                     |

| SiCOH(K=3)                | SiLK(K=2.6)    | 2.80                         | 2.24                         | 20%                     |

| p-SiCOH*(K=2.5)           | SiLK(K=2.6)    | 2.55                         | 1.99                         | 22%                     |

| p-SiO <sub>2</sub> *(K=2) | p-SiLK*(K=2.2) | 2.10                         | 1.68                         | 20%                     |

(\*「p-」はその誘電体が多孔質誘電体であることを示す)

10

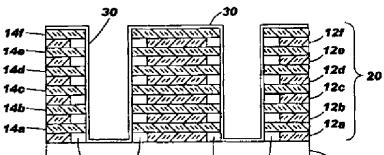

## 【0022】

空隙26を形成した後、次のステップで付着させる金属が空隙26内へ漏れることを防ぐため、第1の金属配線層20の表面28を密封する。これは異なるいくつかの方法で実施することができる。例えば、低誘電率を有する誘電体などの共形ライナ30、すなわちSiCOH、SiO<sub>2</sub>、SiN、SiC、およびSiCNなどを付着させて第1の金属配線レベル20の表面28を覆う(図8)。ライナ30は、PECVD、HDP CVD、SACVD、APCVD、THCVDまたは他の同様の付着技法を使用して、約1~10nmの厚さに付着させることができる。

## 【0023】

あるいは、空隙26が小さい場合、例えば空隙26が約1~10nmである場合、空隙26を密封する目的には、次のステップで付着させる金属で十分である。物理蒸着(PVD)、化学蒸着(CVD)、原子層付着(ALD)、または他の同様の付着技法を使用して、空隙26に実際に侵入する金属イオンがごくわずかとなるように金属を付着させることもできる。

20

## 【0024】

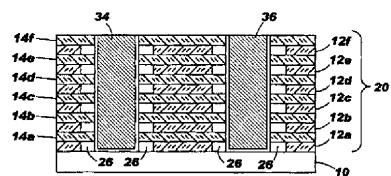

上記のとおりに別個の密封プロセスを使用した場合には、空隙26を密封した後に、第1の配線レベル20の表面28を覆う導電材料32を付着させて、第1および第2のフィーチャ22、24を埋める(図9)。導電材料32は、当技術分野で知られているタンタルなどの薄い耐熱性金属ライナで内張りされた銅、または同様に使用される他の材料を含むことができる。従来の技法を使用して第1の配線レベル20の表面28を研磨して、第1および第2のフィーチャ22、24内の導電材料32を残し余分な導電材料32を除去し、第1のワイヤ34および第2のワイヤ36を形成する(図10)。

30

## 【0025】

この例に示された第1の金属配線レベル20はシングル・ダマシン配線レベルである。図11~17に示すように、本発明は、デュアル・ダマシン配線レベルと共に使用するようにも設計される。図11に示すように、第1の配線レベル20の表面28を覆う絶縁層38を付着させることができる。絶縁層38は、(後に形成する)空隙を形成するために使用する後続のエッチング・プロセス中に除去されにくい低誘電率の1種または数種の誘電材料を含むことができる。例えば絶縁層38は、多孔質SiCOH(p-O SG)、SiO<sub>2</sub>、フッ素化SiO<sub>2</sub>(FSG)、SiCOH(OSG)、メチルシリセスキオキサン(MSQ)、またはこれらの全ての材料の多孔質膜を含む。絶縁層38は、CVD、PECVD、スピノン付着または他の同様の付着技法を使用して形成することができ、SiN、SiC、FSGなどの複数の層からなることができる。絶縁層38は、最終的なバイアの高さにほぼ等しい厚さ、例えば0.1から1.0ミクロンの厚さに形成することができる。

40

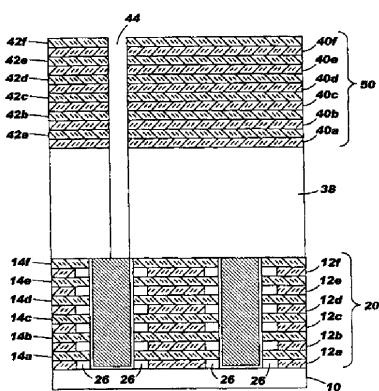

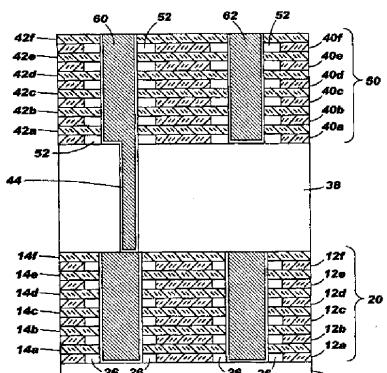

## 【0026】

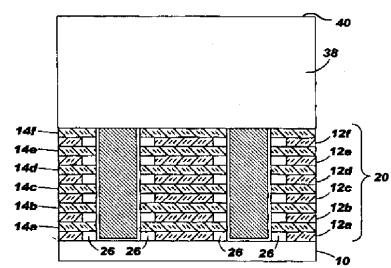

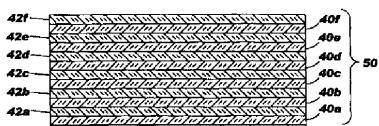

絶縁層38の表面40に、有機誘電材料40a~40fと無機誘電材料42a~42fの交互層を図12に示すように付着させて、第2の配線レベル50を形成する。この交互層は、第1の金属配線レベル20内に形成された交互層と同様の交互層(すなわち有機誘電材料、無機誘電材料、有機誘電材料、無機誘電材料等)であり、同様の方法で形成され

50

る。

#### 【0027】

第2の配線レベル50を形成した後、有機誘電材料40a～40fと無機誘電材料42a～42fの交互層および絶縁層38内に、第1のデュアル・ダマシン・フィーチャ44を形成する。図13に示すように、第1のデュアル・ダマシン・フィーチャ44はバイア・トレンチである。バイア・トレンチ44は、従来のパターン形成技法および従来のエッティング技法を使用して、第1の金属配線レベル20まで形成する。

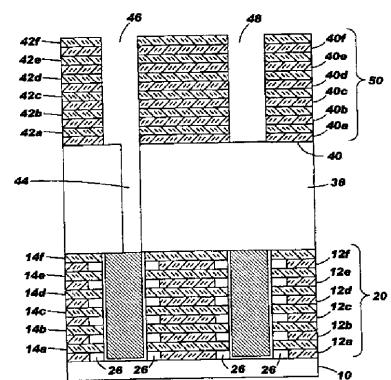

#### 【0028】

図14に示すように、有機誘電材料40a～40fと無機誘電材料42a～42fの交互層内に、第2のデュアル・ダマシン・フィーチャ46および第2のトレンチ48を形成する。第2のデュアル・ダマシン・フィーチャ46もワイヤ・トレンチであり、従来のパターン形成技法および従来のエッティング技法を使用して絶縁層38の表面40まで形成する。あるいは、当技術分野で知られているトレンチ・ファースト・バイア・セカンド・プロセス(trench first-via second process)を使用してもよい。同様に、上部ハードマスク内に第1のダマシン・フィーチャをパターン形成しこれをエッティングする、当技術分野で知られている多層ハードマスクを使用してもよい。

10

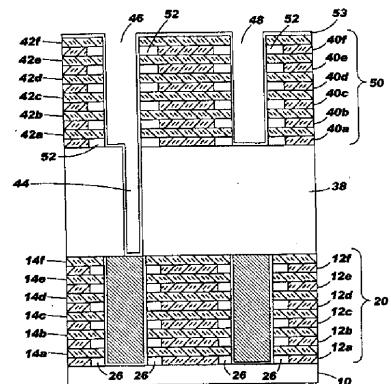

#### 【0029】

第1および第2のデュアル・ダマシン・フィーチャ44、46、48を形成した後、第2の配線レベル50内の有機誘電材料40a～40fの少なくとも一部分を除去する選択エッティングを実行する。前述のとおり、有機誘電材料がp-SiLK(商標)を含み、無機誘電材料がp-OSGを含む場合には、N<sub>2</sub>プラズマ、H<sub>2</sub>プラズマまたは他の同様のプラズマ・エッティングを使用して、この有機誘電材料を選択的に除去することができる。このN<sub>2</sub>またはH<sub>2</sub>エッティングは、約3～200mTの圧力範囲において、平行プレートまたは高密度プラズマの一般的なパワーおよびフロー条件で実施することができる。

20

#### 【0030】

この選択エッティングの結果、図15に示すように、第2の配線レベル50内に開口ないし空隙52が形成される。デバイス全体に機械強度および安定性を追加するため、この例の絶縁層38内には空隙52が形成されないように留意されたい。次いで、次のステップで付着させる金属が空隙52内へ漏れることを防ぐため、第2の金属配線レベル50の表面に共形ライナ53を形成して、第2の金属配線レベル50を密封する。

30

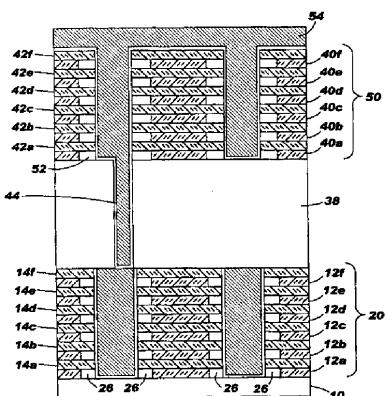

#### 【0031】

第2の配線レベル50の表面を覆う導電材料54を付着させて、バイア・トレンチ44およびトレンチ46、48を埋める(図16)。導電材料54は、薄い耐熱性金属ライナ、例えばタンタルで内張りされた銅、または同様に使用される他の材料を含むことができる。従来の技法を使用して第2の配線レベル50の表面を研磨して、バイア・トレンチ44およびワイヤ・トレンチ46、48内の導電材料54を残し余分な導電材料54を除去し、導電性デュアル・ダマシン・フィーチャ60および導電性シングル・ダマシン・フィーチャ62を形成する(図17)。

#### 【産業上の利用可能性】

#### 【0032】

金属配線レベル内に空隙を形成する本発明の方法はデバイスの全体的な静電容量を低減させる。デバイスはますます小型化し、デバイス・フィーチャ間の距離は短くなり続いているため、このことは特に有用である。

40

#### 【図面の簡単な説明】

#### 【0033】

【図1】プリメタル誘電層およびその上の第1の絶縁層を含む、本発明の実施形態に基づくデバイスの断面図である。

【図2】第2の絶縁層をその上に有する図1のデバイスを示す図である。

【図3】第3の絶縁層をその上に有する図2のデバイスを示す図である。

【図4】第4の絶縁層をその上に有する図3のデバイスを示す図である。

50

【図5】第1の金属配線レベルを形成する複数の絶縁層をその上に有する図4のデバイスを示す図である。

【図6】一対のダマシン・フィーチャがその中に形成された図5のデバイスを示す図である。

【図7】選択された絶縁層内に複数の空隙が形成された図6のデバイスを示す図である。

【図8】それを覆う共形ライナが形成された図7のデバイスを示す図である。

【図9】導電層をその上に付着させた図8のデバイスを示す図である。

【図10】研磨後の図9のデバイスを示す図である。

【図11】第1の金属配線レベルを覆う絶縁層が形成された図10のデバイスを示す図である。

10

【図12】第2の金属配線レベルを形成する複数の絶縁層を有する図11のデバイスを示す図である。

【図13】第1のダマシン・フィーチャがその中に形成された図12のデバイスを示す図である。

【図14】第2のダマシン・フィーチャがその中に形成された図13のデバイスを示す図である。

【図15】選択された絶縁層内に複数の空隙が形成された図14のデバイスを示す図である。

【図16】導電層をその上に付着させた図15のデバイスを示す図である。

【図17】研磨後の図16のデバイスを示す図である。

20

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【 図 1 2 】

【图 1-3】

【図14】

【図15】

【 四 1 6 】

〔 図 17 〕

---

フロントページの続き

(51)Int.CI.

F I

H 0 1 L 21/316

G

H 0 1 L 21/316

M

(72)発明者 アンソニー・ケー・スタンパー

アメリカ合衆国 0 5 4 9 5 バーモント州ウィリストン エバーグリーン・ドライブ 4 6

合議体

審判長 藤原 敬士

審判官 川端 修

審判官 井上 茂夫

(56)参考文献 特開2003-209166 (JP, A)

米国特許第6090698 (U.S., A)

(58)調査した分野(Int.CI., DB名)

H01L 21/3205,3213,768

H01L 23/52,522