## (12) 发明专利

(10) 授权公告号 CN 109308891 B

(45) 授权公告日 2023.08.15

(21) 申请号 201810832678.4

G10H 7/02 (2006.01)

(22) 申请日 2018.07.26

## (56) 对比文件

(65) 同一申请的已公布的文献号

CN 104867487 A, 2015.08.26

申请公布号 CN 109308891 A

CN 101170705 A, 2008.04.30

(43) 申请公布日 2019.02.05

JP 2000163050 A, 2000.06.16

(30) 优先权数据

CN 1398394 A, 2003.02.19

2017-146126 2017.07.28 JP

CN 103531193 A, 2014.01.22

(73) 专利权人 卡西欧计算机株式会社

JP 2007073182 A, 2007.03.22

地址 日本东京都

US 5519684 A, 1996.05.21

(72) 发明人 佐藤博毅 川岛肇

JP 2013148603 A, 2013.08.01

(74) 专利代理机构 永新专利商标代理有限公司

US 2006137515 A1, 2006.06.29

72002

EP 1580729 A1, 2005.09.28

专利代理人 吕文卓

CN 103310780 A, 2013.09.18

(51) Int. Cl.

CN 1674090 A, 2005.09.28

G06F 17/00 (2019.01)

JP H0519766 A, 1993.01.29

G10H 1/00 (2006.01)

CN 1447962 A, 2003.10.08

审查员 谢建军

权利要求书3页 说明书15页 附图20页

## (54) 发明名称

乐音发生装置、乐音发生方法、存储介质及

电子乐器

## (57) 摘要

乐音发生装置、乐音发生方法、存储介质及电子乐器。乐音发生装置的第1处理器能够将第1存储器内的波形数据向第2存储器良好地转送，第2处理器能够将第2存储器内的波形数据良好地读入。在从大容量闪存存储器的音色波形区域向RAM的波形缓存转送波形数据的情况下，判断是否能将波形数据向RAM内的多个波形缓存中的不包括环形缓存区域的第1区域转送。将判断为能向第1区域转送的波形数据向第1区域转送。判断是否能将判断为不能向第1区域转送的波形数据向多个区域中的包括环形缓存区域的第2区域转送。将判断为能向第2区域转送的波形数据向第2区域转送。

CN 109308891 B

1. 一种乐音发生装置,其特征在于,

包括:

演奏操作件;

第1存储器,存储有多个波形数据;

第2存储器,具有包括第1区域和第2区域的多个区域,上述第1区域具有能够容纳从上述多个波形数据中指定的波形数据的整体的容量,并且不是环形缓存区域,上述第2区域不具有能够容纳所指定的上述波形数据的整体的容量,并且是环形缓存区域;

处理器,执行决定处理和写入处理,上述决定处理决定将从上述第1存储器中存储的上述多个波形数据中指定的上述波形数据向上述第2存储器中的上述第1区域及上述第2区域中的哪个进行转送,上述写入处理向通过上述决定处理决定的区域转送并写入所指定的上述波形数据;以及

波形读出装置,读出被转送到上述第2存储器的所决定的上述区域中的所指定的上述波形数据。

2. 如权利要求1所述的乐音发生装置,其特征在于,

上述处理器执行以下处理:

第1判断处理,判断是否能够将从上述第1存储器中存储的上述多个波形数据中指定的波形数据的整体向上述第2存储器的上述第1区域转送;

第1转送处理,将在上述第1判断处理中判断为能够向上述第1区域转送的所指定的上述波形数据的整体向上述第1区域转送;

第2判断处理,判断是否能够将在上述第1判断处理中判断为不能向上述第1区域转送的所指定的上述波形数据通过环形缓存方式向上述第2区域转送;以及

第2转送处理,将在上述第2判断处理中判断为能够通过上述环形缓存方式向上述第2区域转送的上述波形数据通过上述环形缓存方式向上述第2区域转送。

3. 如权利要求2所述的乐音发生装置,其特征在于,

上述处理器,在上述第1判断处理之前执行第3判断处理,该第3判断处理判断从上述第1存储器中存储的上述多个波形数据中指定的波形数据是否已存储在上述第2存储器内的上述第1区域,在由上述第3判断处理判断为所指定的上述波形数据存储在上述第2存储器内的情况下,不执行上述第1转送处理。

4. 如权利要求2所述的乐音发生装置,其特征在于,

上述处理器,在由上述第2判断处理判断为不能将所指定的上述波形数据向上述第2区域转送的情况下,执行转送区域确保处理和第3转送处理,上述转送区域确保处理将上述第2存储器内的上述多个区域中的已存储有其他波形数据的区域确保为可转送上述波形数据的可转送区域,上述第3转送处理将所指定的上述波形数据向由上述转送区域确保处理确保的上述可转送区域转送。

5. 如权利要求1所述的乐音发生装置,其特征在于,

上述第1区域不包括作为环形缓存发挥功能的区域。

6. 如权利要求1所述的乐音发生装置,其特征在于,

上述第1区域包括2个以上的连续的可转送区域相结合而成的结合区域。

7. 如权利要求1所述的乐音发生装置,其特征在于,

上述第2区域包括作为环形缓存发挥功能的区域。

8. 如权利要求1所述的乐音发生装置,其特征在于,

上述第2区域与上述第1区域相比区域的尺寸较小。

9. 一种乐音发生方法,使乐音发生装置的计算机执行处理,其特征在于,

上述乐音发生装置包括:

演奏操作件;

第1存储器,存储有多个波形数据;以及

第2存储器,具有包括第1区域和第2区域的多个区域,上述第1区域具有能够容纳从上述多个波形数据中指定的波形数据的整体的容量,并且不是环形缓存区域,上述第2区域不具有能够容纳所指定的上述波形数据的整体的容量,并且是环形缓存区域;

上述乐音发生方法使乐音发生装置的计算机执行以下处理:

决定处理,决定将从上述第1存储器中存储的上述多个波形数据中指定的上述波形数据向上述第2存储器中的上述第1区域及上述第2区域中的哪个进行转送;

写入处理,向通过上述决定处理决定的区域转送并写入所指定的上述波形数据;以及

波形读出处理,读出被转送到上述第2存储器的所决定的上述区域中的所指定的上述波形数据。

10. 一种存储介质,存储使乐音发生装置的计算机执行处理的程序,其特征在于,

上述乐音发生装置包括:

演奏操作件;

第1存储器,存储有多个波形数据;以及

第2存储器,具有包括第1区域和第2区域的多个区域,上述第1区域具有能够容纳从上述多个波形数据中指定的波形数据的整体的容量,并且不是环形缓存区域,上述第2区域不具有能够容纳所指定的上述波形数据的整体的容量,并且是环形缓存区域;

上述程序使乐音发生装置的计算机执行以下处理:

决定处理,决定将从上述第1存储器中存储的上述多个波形数据中指定的上述波形数据向上述第2存储器中的上述第1区域及上述第2区域中的哪个进行转送;

写入处理,向通过上述决定处理决定的区域转送并写入所指定的上述波形数据;以及

波形读出处理,读出被转送到上述第2存储器的所决定的上述区域中的所指定的上述波形数据。

11. 一种电子乐器,其特征在于,

包括:

演奏操作件;

第1存储器,存储有多个波形数据;

第2存储器,具有包括第1区域和第2区域的多个区域,上述第1区域具有能够容纳从上述多个波形数据中指定的波形数据的整体的容量,并且不是环形缓存区域,上述第2区域不具有能够容纳所指定的上述波形数据的整体的容量,并且是环形缓存区域;

处理器,执行决定处理和写入处理,上述决定处理决定将从上述第1存储器中存储的上述多个波形数据中指定的上述波形数据向上述第2存储器中的上述第1区域及上述第2区域中的哪个进行转送,上述写入处理向通过上述决定处理决定的区域转送并写入所指定的上

述波形数据；

波形读出装置，读出被转送到上述第2存储器的所决定的上述区域中的所指定的上述波形数据；以及

扬声器，基于由上述波形读出装置读出的波形数据进行发音。

## 乐音发生装置、乐音发生方法、存储介质及电子乐器

[0001] 本申请基于2017年7月28日提出的日本专利申请第2017-146126号主张优先权，这里引用其全部内容。

### 技术领域

[0002] 本发明涉及乐音发生装置、乐音发生方法、存储介质及电子乐器。

### 背景技术

[0003] 在通过波形读入方式产生乐音波形的音源装置中，有采用以下这样的系统的技术：为了能够利用更多的、更长时间的波形数据，将不使用的波形数据预先保存到例如ROM (Read Only Memory)、闪存存储器或硬盘存储装置等二次存储装置（第1存储器）的音色波形区域，将其中使用的波形数据向作为音源装置能够直接访问的高速波形缓存而发挥功能的例如RAM (Random Access Memory) 等一次存储装置（第2存储器）转送并使其发音。即，将高价的RAM具有的存储容量以上的存储容量的波形数据预先保存到廉价的ROM等中，仅在需要的情况下将其移动到波形缓存中而用于发音，可以说这是在成本方面有效的方法。

[0004] 此外，乐音波形数据的尺寸是各种各样的，理想的是优选在第2存储器的波形缓存上准备能够将全部的发音声道量的各个波形数据原样保存的区域，但在现实中，为了抑制成本，在第2存储器的波形缓存上并没有准备充分的区域。为此，使波形缓存作为不需要在意乐音波形数据的尺寸的所谓“环形缓存（ring buffer）”发挥功能，在发音部的发音中，音源将对象发音声道的波形缓存（环形缓存区域）的规定区间反复读出，与之并行地，CPU向波形缓存依次补充波形数据。

[0005] 作为以往技术，已知例如在专利文献1中记载的技术。

[0006] 专利文献1：日本特开2000-122668号公报

[0007] 但是，上述的方法中，虽然波形缓存的容量可以较少，但是有转送数据的输送量较多的缺点。特别是在必须将波形的循环（loop）区间的转送进行到发音结束为止等情况下，还可能发生比原波形的容量更多的数据转送。例如，在波形缓存（环形缓存）的尺寸是16K（千）字节、波形数据的容量是30K字节、循环区间的容量是20K字节的情况下，如果由按键引起的发音长时间持续，则需要将循环区间多次反复转送，所以转送30K字节+（循环回数-1） $\times$ 20K字节的数据，会发生远比波形数据的容量多的数据转送。结果，CPU、存储器系统的总线的占用率变高，导致同时发音数的减少、演奏延时性的变差等性能下降。此外，如果为了减少该性能下降而使用高性能的CPU、总线系统，则成本增大。

### 发明内容

[0008] 因此，本发明的目的在于，提供由第1处理器将第1存储器内的波形数据向第2存储器良好地转送、由第2处理器将第2存储器内的波形数据良好地读入的乐音发生装置等。

[0009] 一种乐音发生装置，其特征在于，包括：演奏操作件；第1存储器，存储有多个波形数据；第2存储器，具有包括第1区域和第2区域的多个区域，上述第1区域具有能够容纳从上

述多个波形数据中指定的波形数据的整体的容量,并且不是环形缓存区域,上述第2区域不具有能够容纳所指定的上述波形数据的整体的容量,并且是环形缓存区域;处理器,执行决定处理和写入处理,上述决定处理决定将从上述第1存储器中存储的上述多个波形数据中指定的上述波形数据向上述第2存储器中的上述第1区域及上述第2区域中的哪个进行转送,上述写入处理向通过上述决定处理决定的区域转送并写入所指定的上述波形数据;以及波形读出装置,读出被转送到上述第2存储器的所决定的上述区域中的所指定的上述波形数据。

[0010] 一种乐音发生方法,使乐音发生装置的计算机执行处理,其特征在于,上述乐音发生装置包括:演奏操作件;第1存储器,存储有多个波形数据;以及第2存储器,具有包括第1区域和第2区域的多个区域,上述第1区域具有能够容纳从上述多个波形数据中指定的波形数据的整体的容量,并且不是环形缓存区域,上述第2区域不具有能够容纳所指定的上述波形数据的整体的容量,并且是环形缓存区域;上述乐音发生方法使乐音发生装置的计算机执行以下处理:决定处理,决定将从上述第1存储器中存储的上述多个波形数据中指定的上述波形数据向上述第2存储器中的上述第1区域及上述第2区域中的哪个进行转送;写入处理,向通过上述决定处理决定的区域转送并写入所指定的上述波形数据;以及波形读出处理,读出被转送到上述第2存储器的所决定的上述区域中的所指定的上述波形数据。

[0011] 一种存储介质,存储使乐音发生装置的计算机执行处理的程序,其特征在于,上述乐音发生装置包括:演奏操作件;第1存储器,存储有多个波形数据;以及第2存储器,具有包括第1区域和第2区域的多个区域,上述第1区域具有能够容纳从上述多个波形数据中指定的波形数据的整体的容量,并且不是环形缓存区域,上述第2区域不具有能够容纳所指定的上述波形数据的整体的容量,并且是环形缓存区域;上述程序使乐音发生装置的计算机执行以下处理:决定处理,决定将从上述第1存储器中存储的上述多个波形数据中指定的上述波形数据向上述第2存储器中的上述第1区域及上述第2区域中的哪个进行转送;写入处理,向通过上述决定处理决定的区域转送并写入所指定的上述波形数据;以及波形读出处理,读出被转送到上述第2存储器的所决定的上述区域中的所指定的上述波形数据。

[0012] 一种电子乐器,其特征在于,包括:演奏操作件;第1存储器,存储有多个波形数据;第2存储器,具有包括第1区域和第2区域的多个区域,上述第1区域具有能够容纳从上述多个波形数据中指定的波形数据的整体的容量,并且不是环形缓存区域,上述第2区域不具有能够容纳所指定的上述波形数据的整体的容量,并且是环形缓存区域;处理器,执行决定处理和写入处理,上述决定处理决定将从上述第1存储器中存储的上述多个波形数据中指定的上述波形数据向上述第2存储器中的上述第1区域及上述第2区域中的哪个进行转送,上述写入处理向通过上述决定处理决定的区域转送并写入所指定的上述波形数据;波形读出装置,读出被转送到上述第2存储器的所决定的上述区域中的所指定的上述波形数据;以及扬声器,基于由上述波形读出装置读出的波形数据进行发音。

## 附图说明

[0013] 图1是本发明的电子键盘乐器的一实施方式的外观图。

[0014] 图2是表示电子键盘乐器的一实施方式的硬件例的图。

[0015] 图3是表示音源LSI的框图。

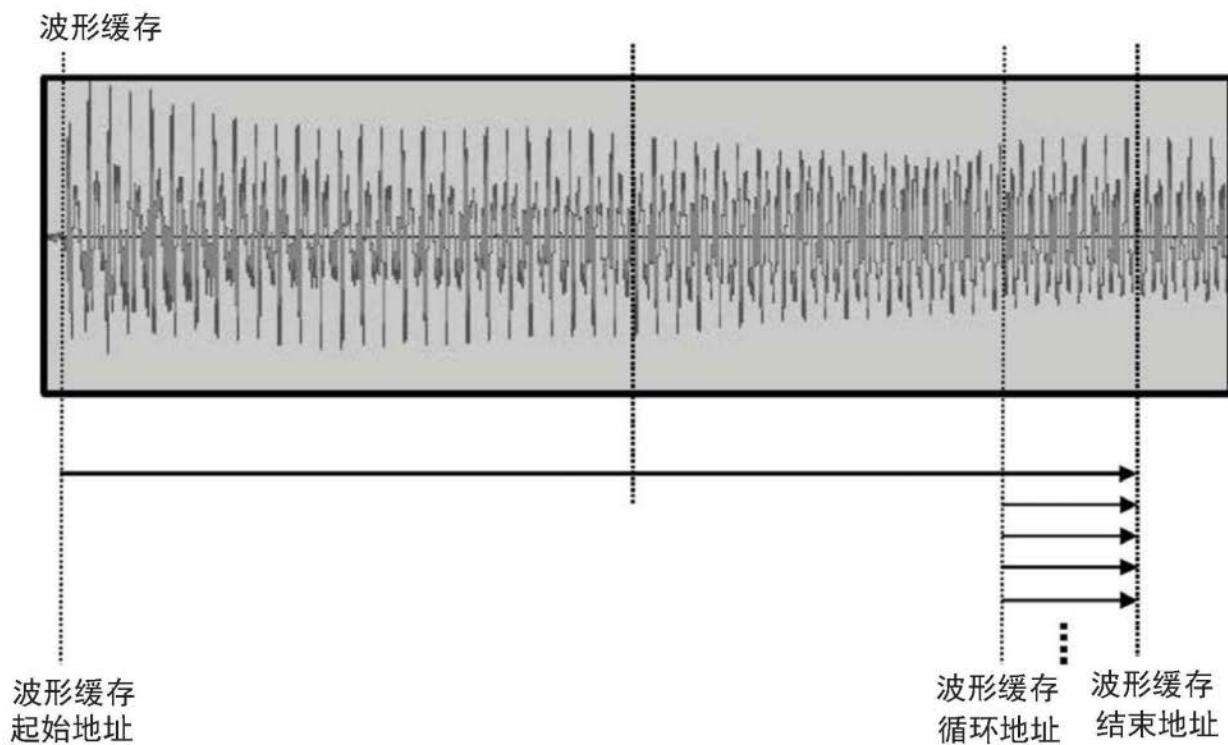

- [0016] 图4是波形读出循环的动作的说明图。

- [0017] 图5是表示“闪存存储器音色波形目录”的数据例的图。

- [0018] 图6是表示“RAM波形缓存目录”的数据例的图。

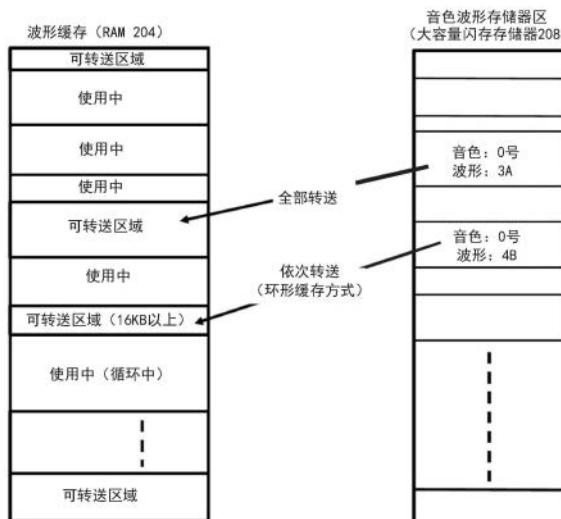

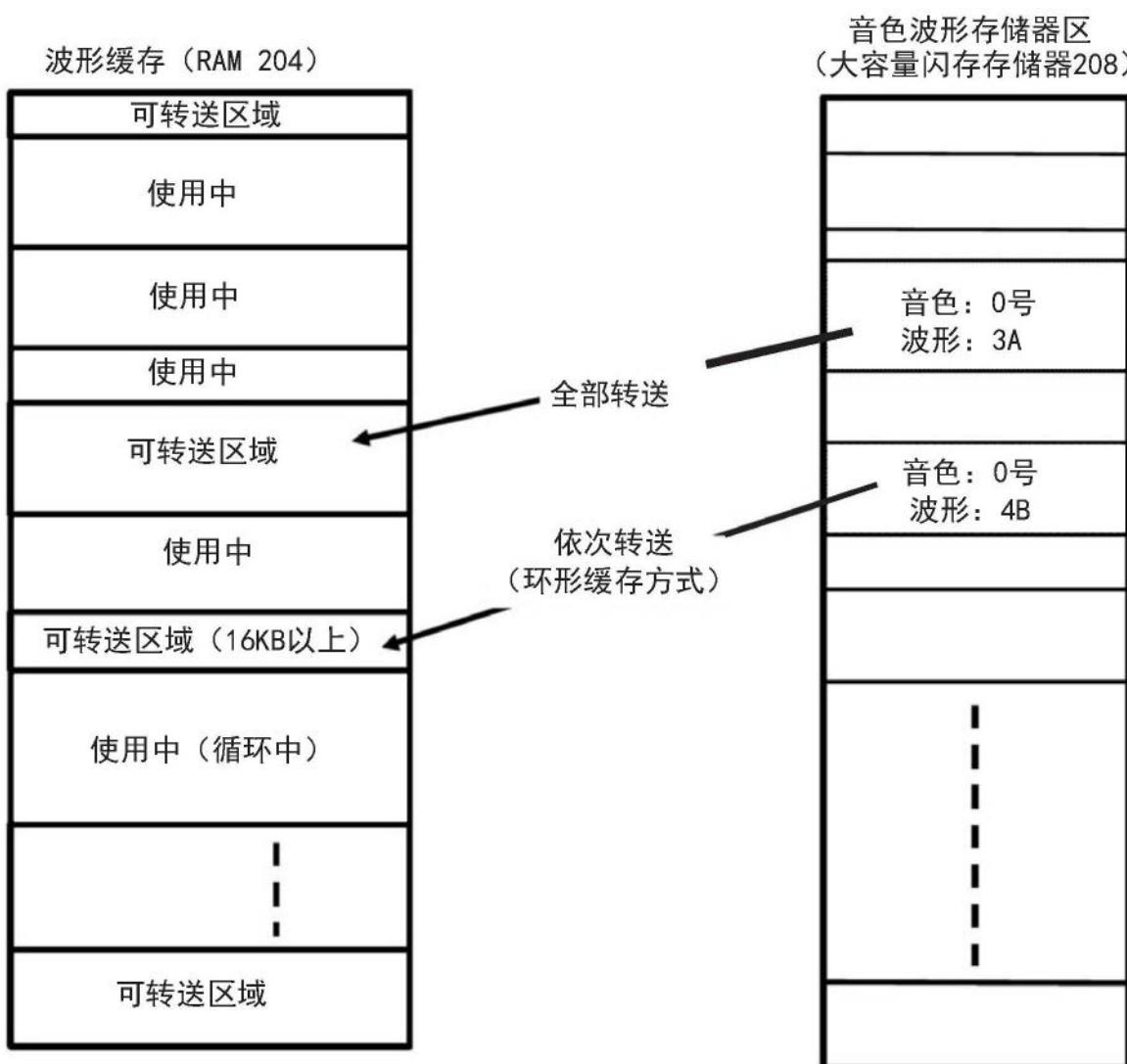

- [0019] 图7是从大容量闪存存储器上的音色波形区域向RAM上的波形缓存的音色波形转送动作的说明图。

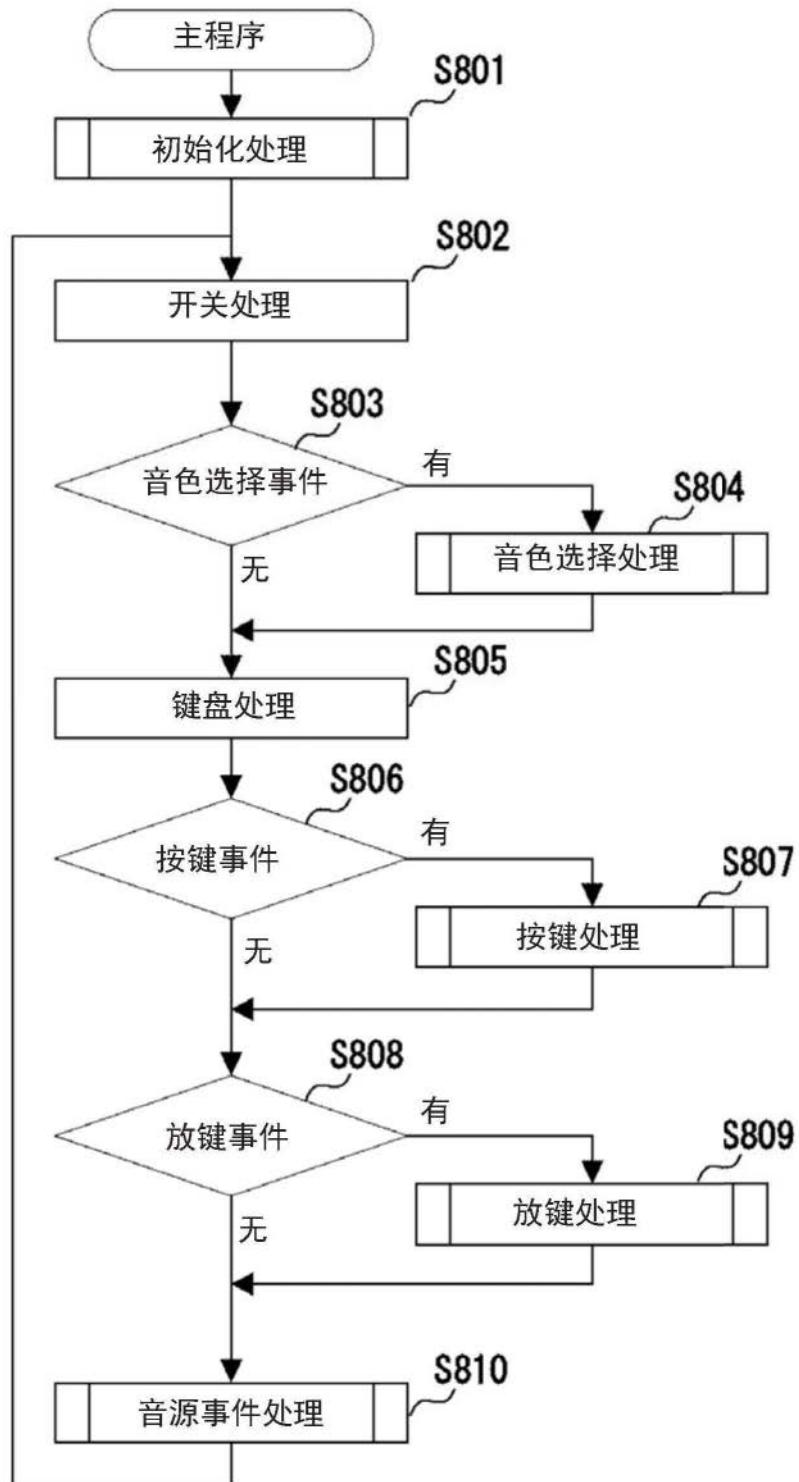

- [0020] 图8是表示主程序的处理例的流程图。

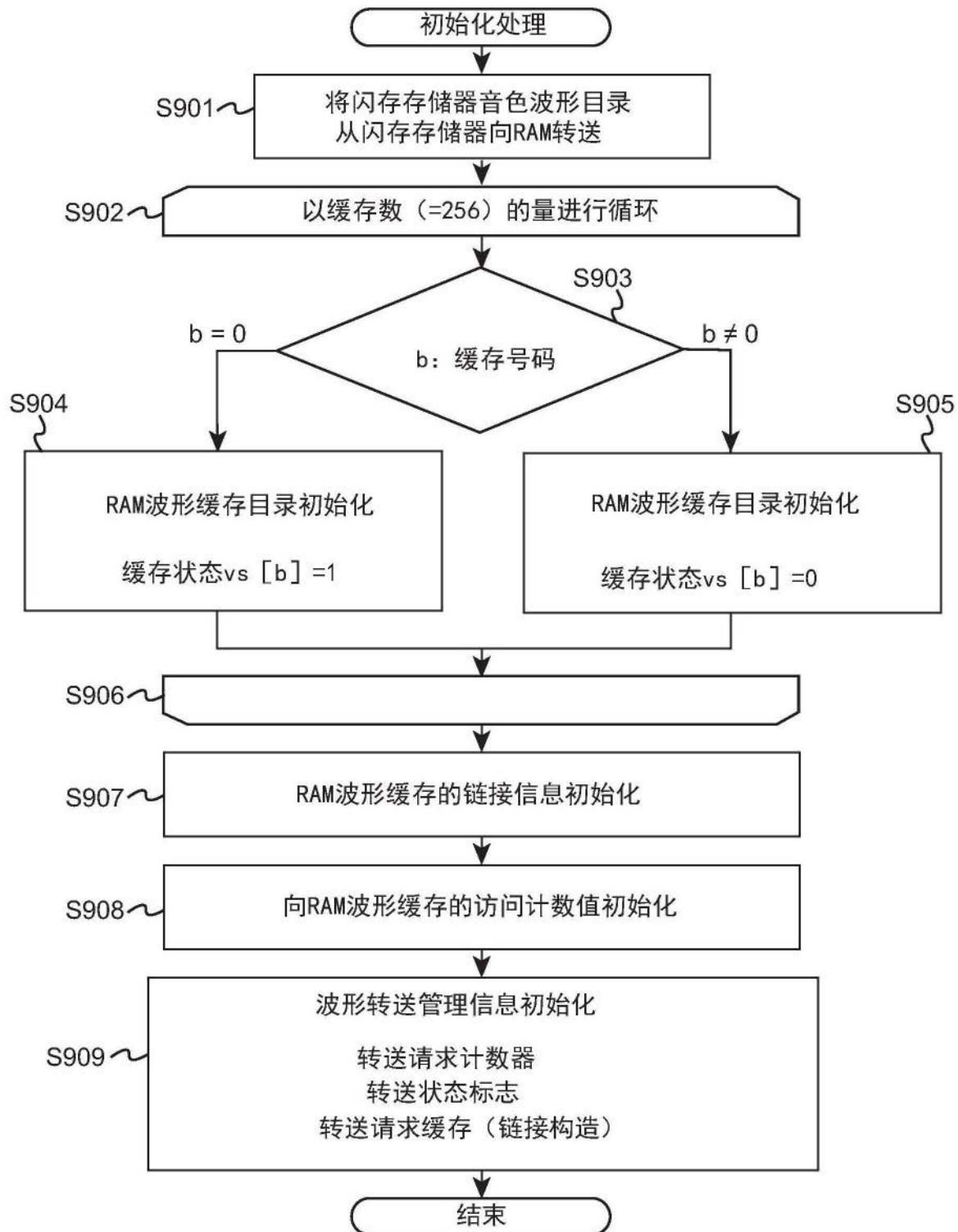

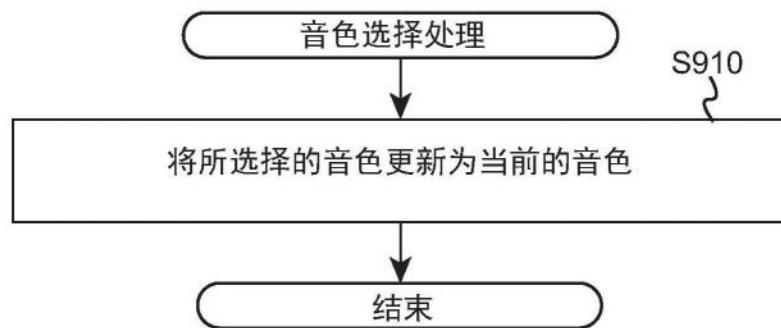

- [0021] 图9A～图9B是表示初始化处理及音色选择处理的详细例的流程图。

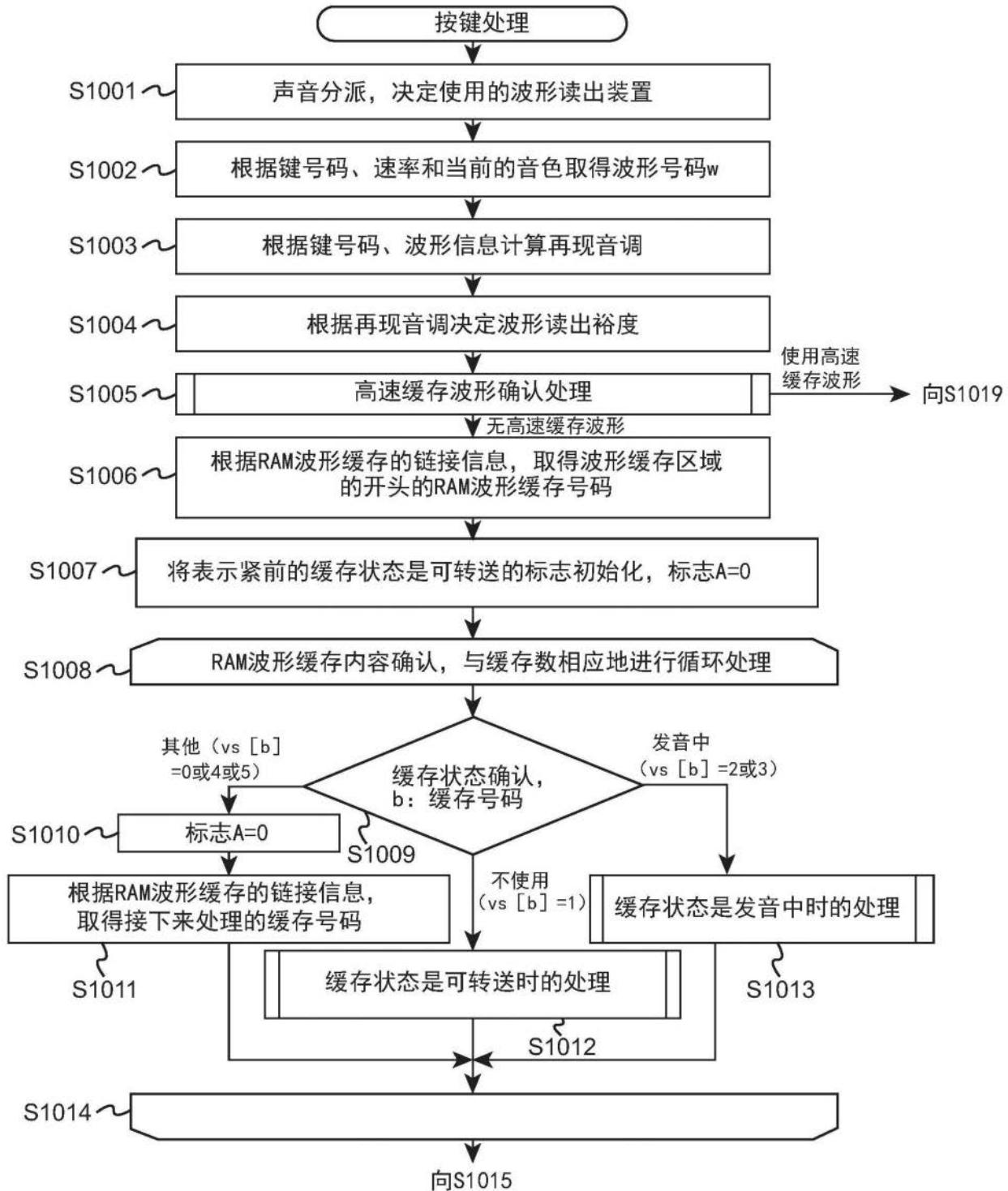

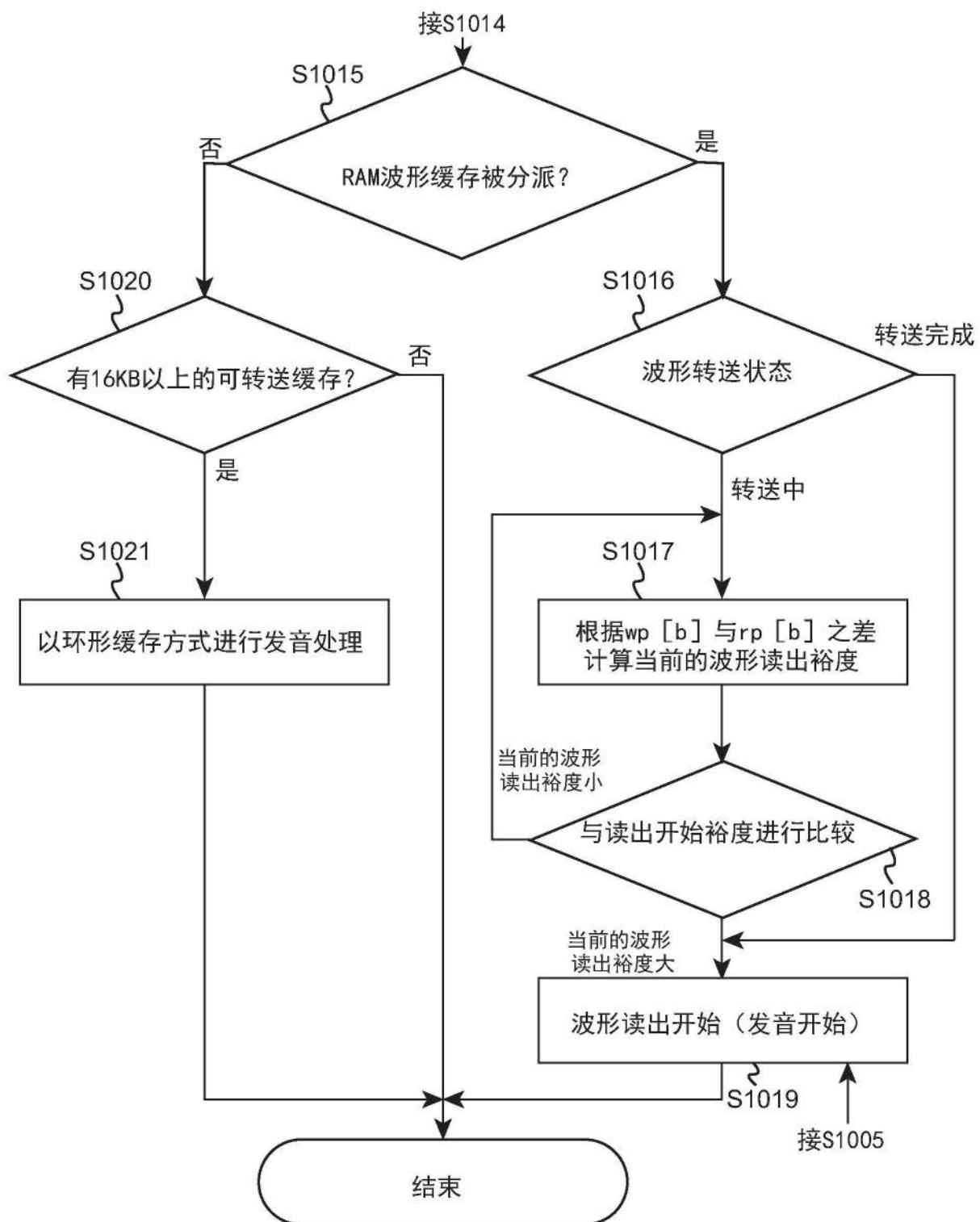

- [0022] 图10是表示按键处理的详细例(其一)的流程图。

- [0023] 图11是表示按键处理的详细例(其二)的详细例的流程图。

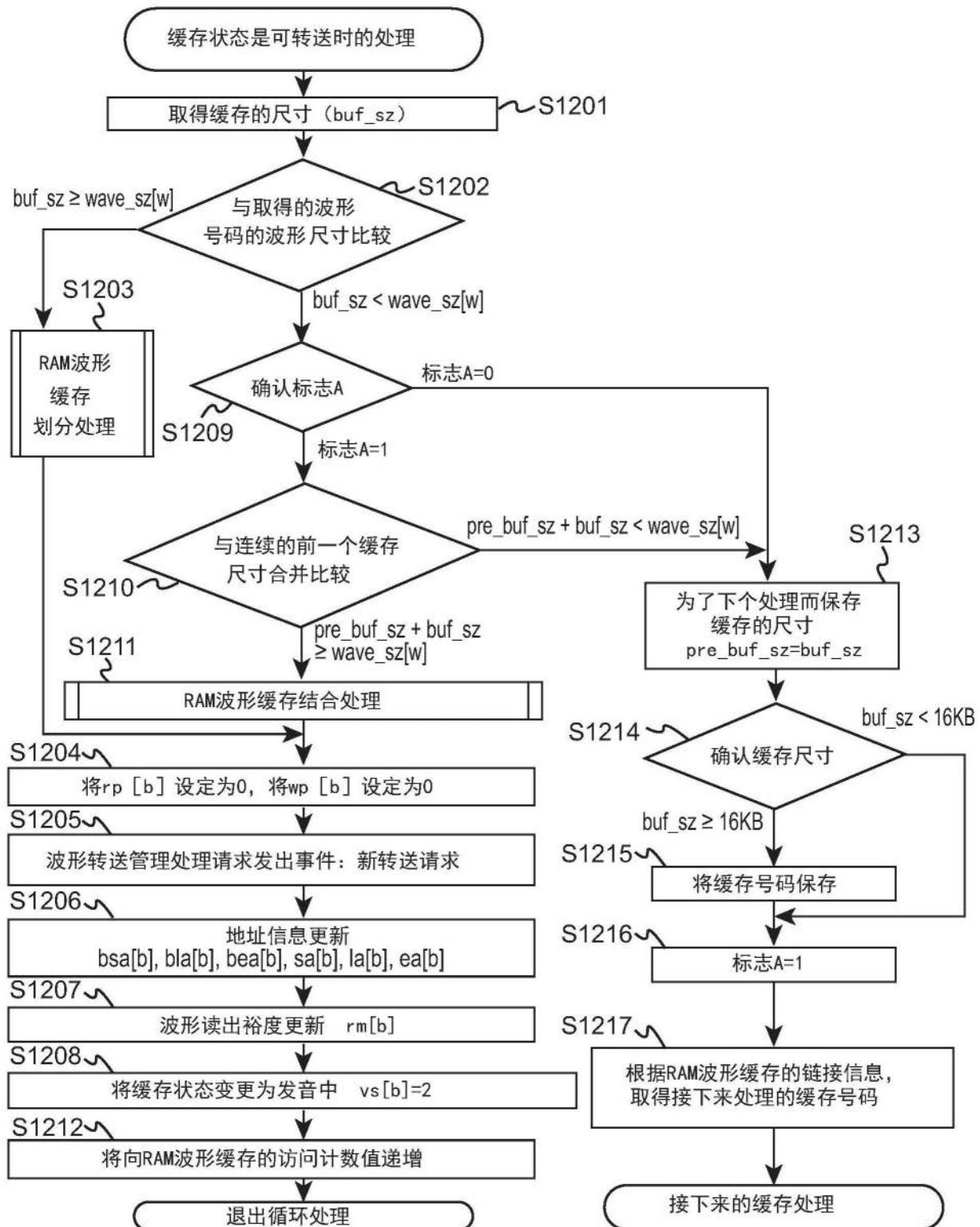

- [0024] 图12是表示缓存状态(buffer status)为可转送时的处理的详细例的流程图。

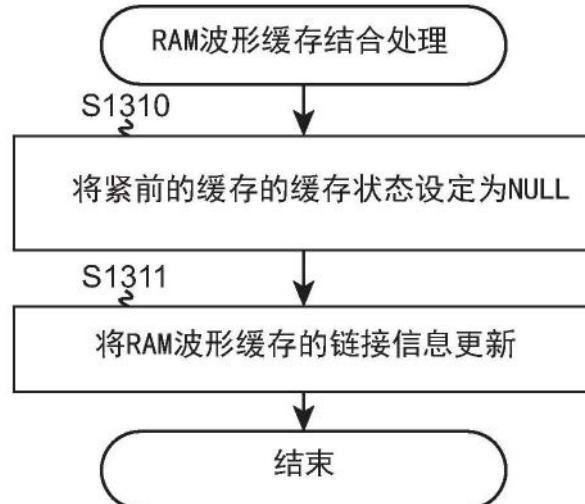

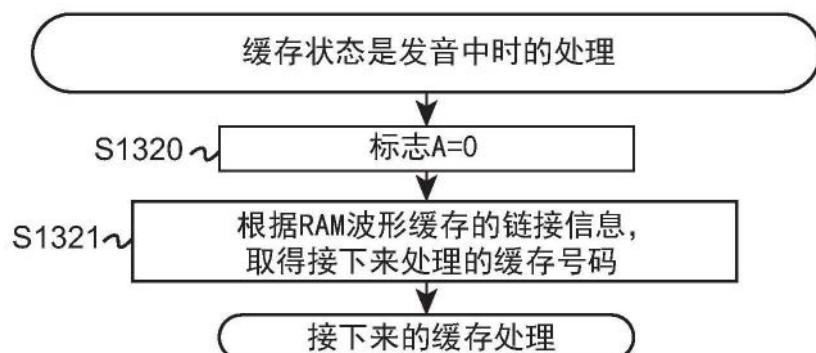

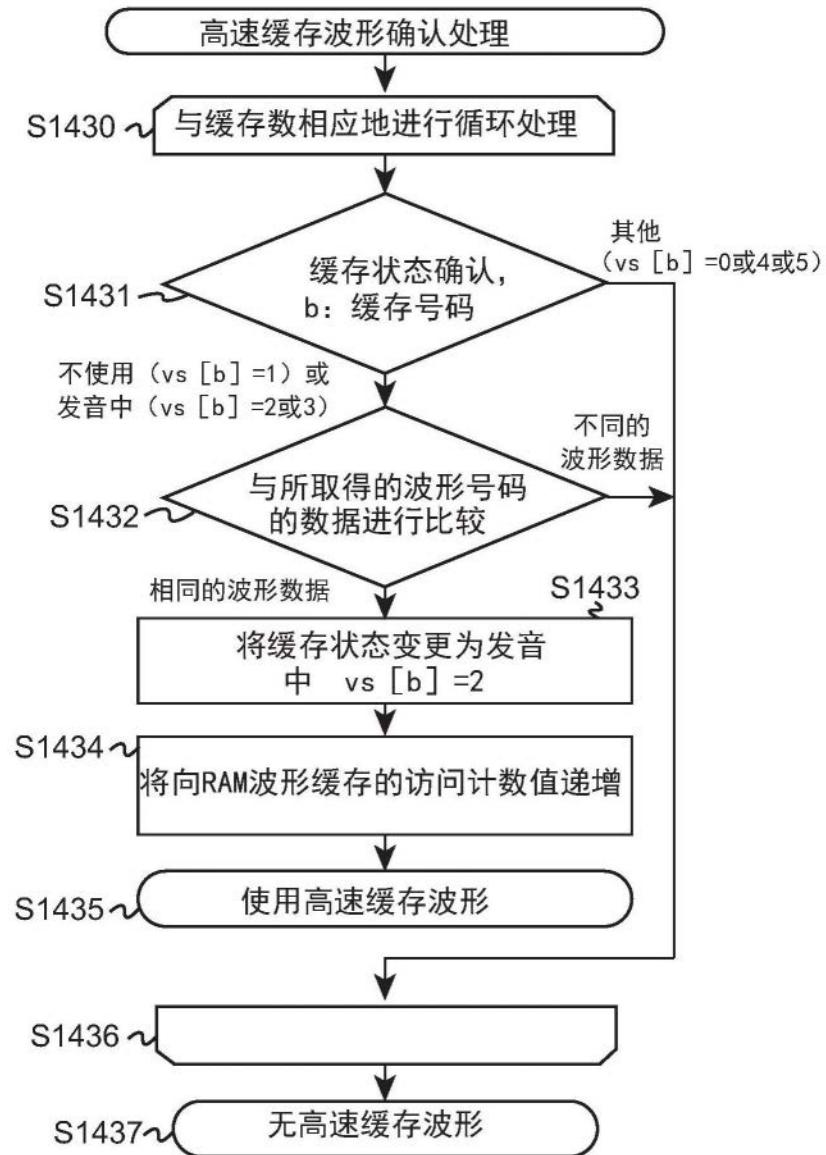

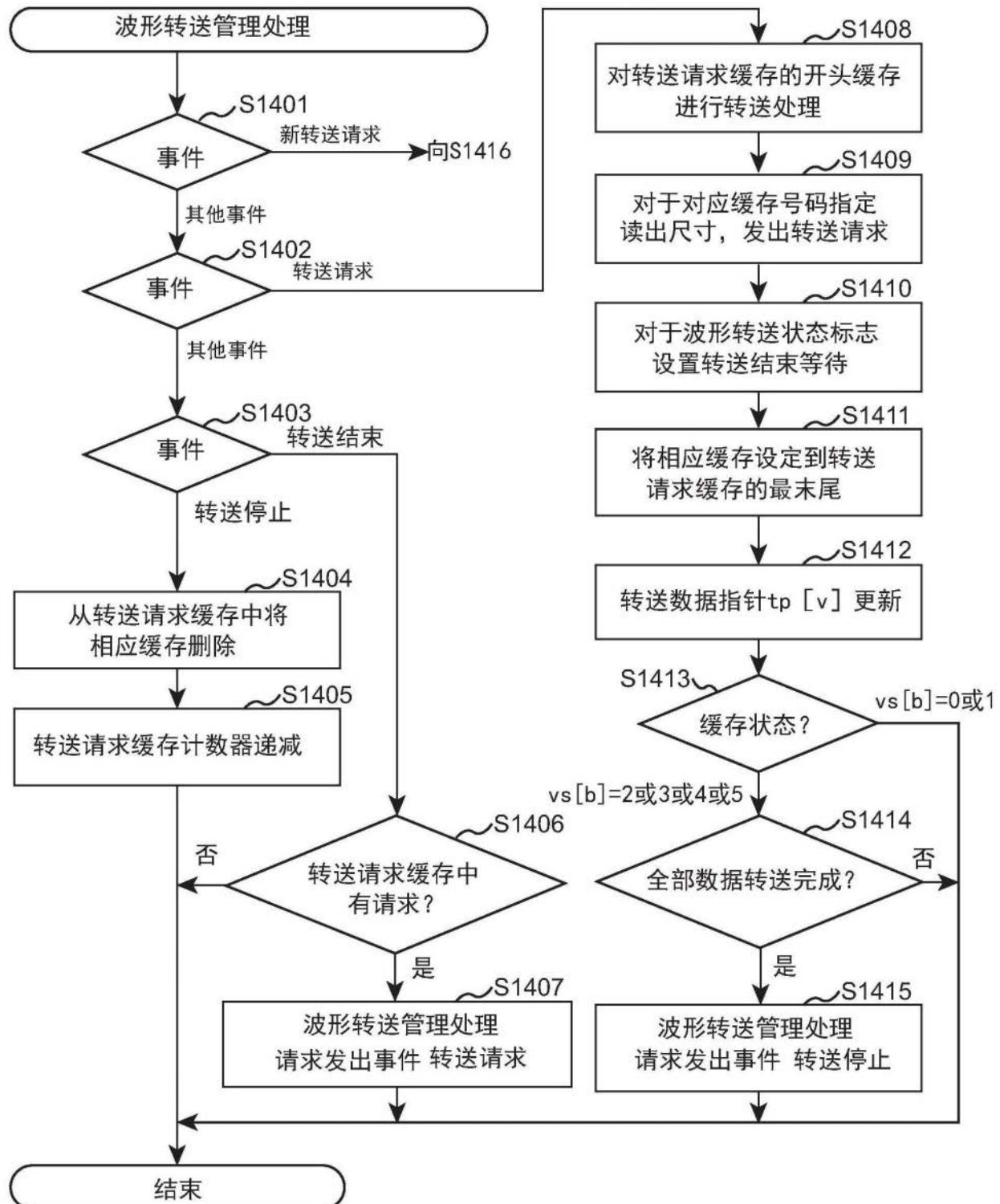

- [0025] 图13A～图13D是表示RAM波形缓存划分处理、RAM波形缓存结合处理、缓存状态为发音中时的处理、高速缓存(cache)波形确认处理的各详细例的流程图。

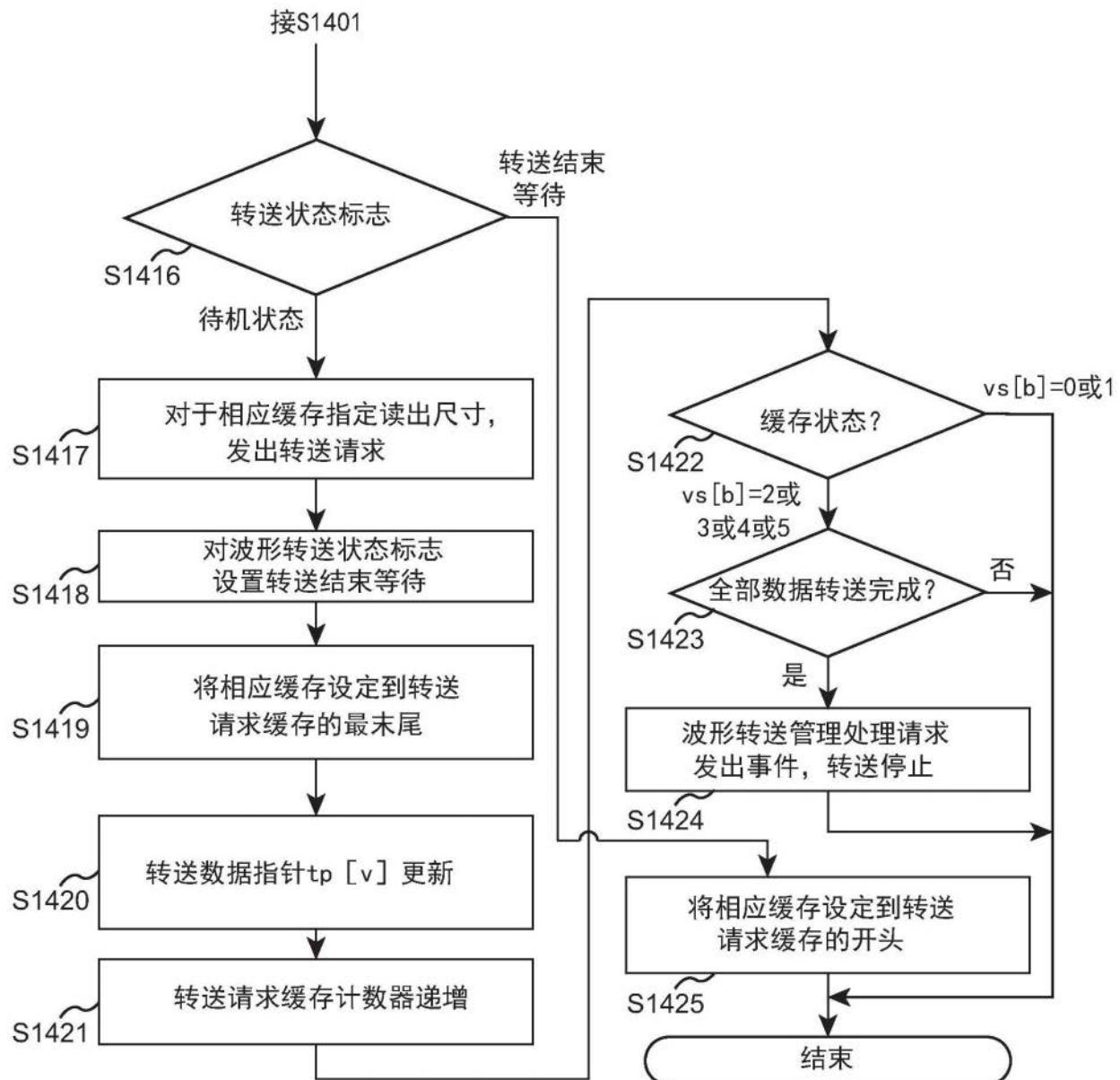

- [0026] 图14是表示波形转送管理处理的例子的流程图(其一)。

- [0027] 图15是表示波形转送管理处理的例子的流程图(其二)。

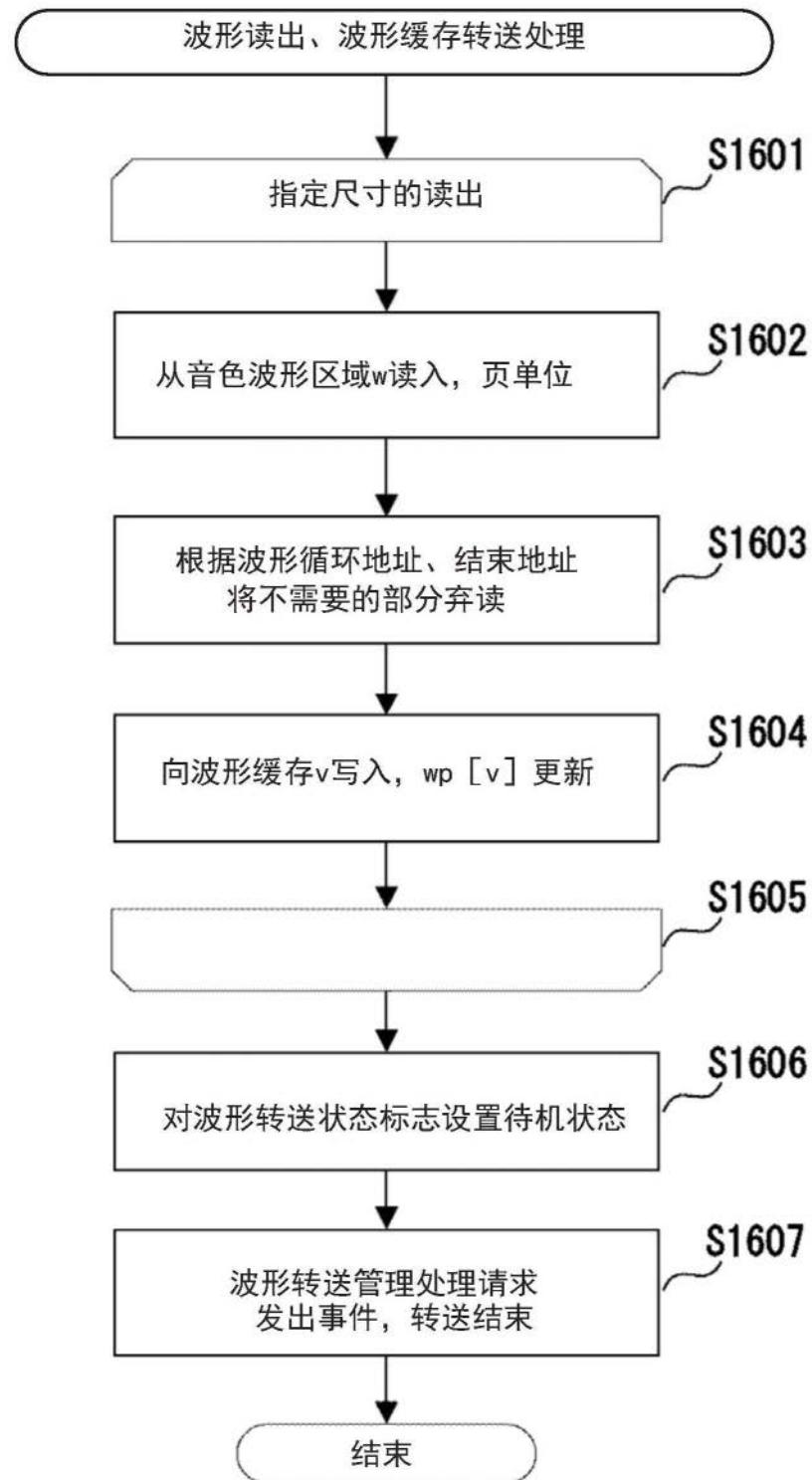

- [0028] 图16是表示波形读出、波形缓存转送处理的例子的流程图。

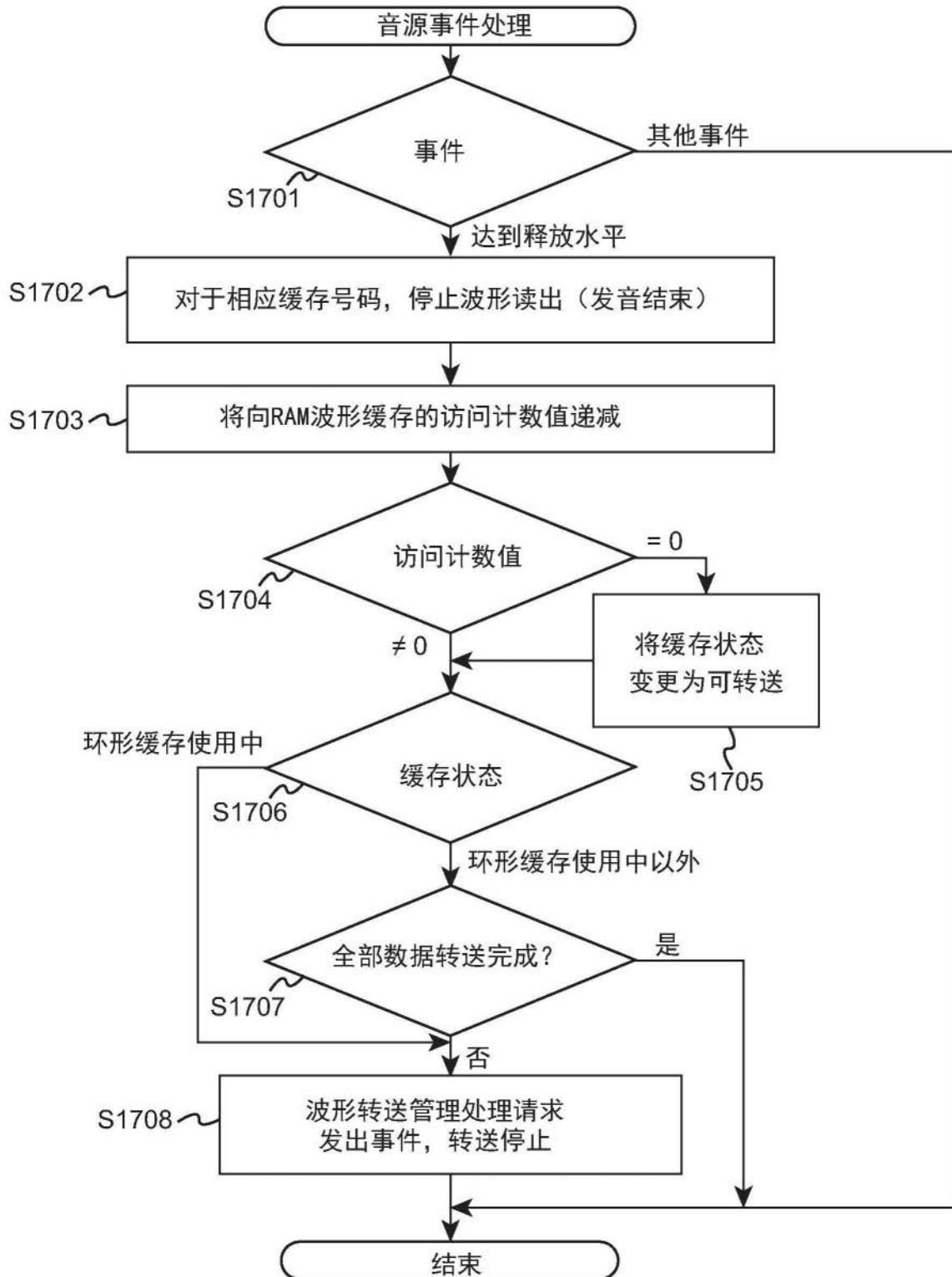

- [0029] 图17是表示音源事件处理的例子的流程图。

## 具体实施方式

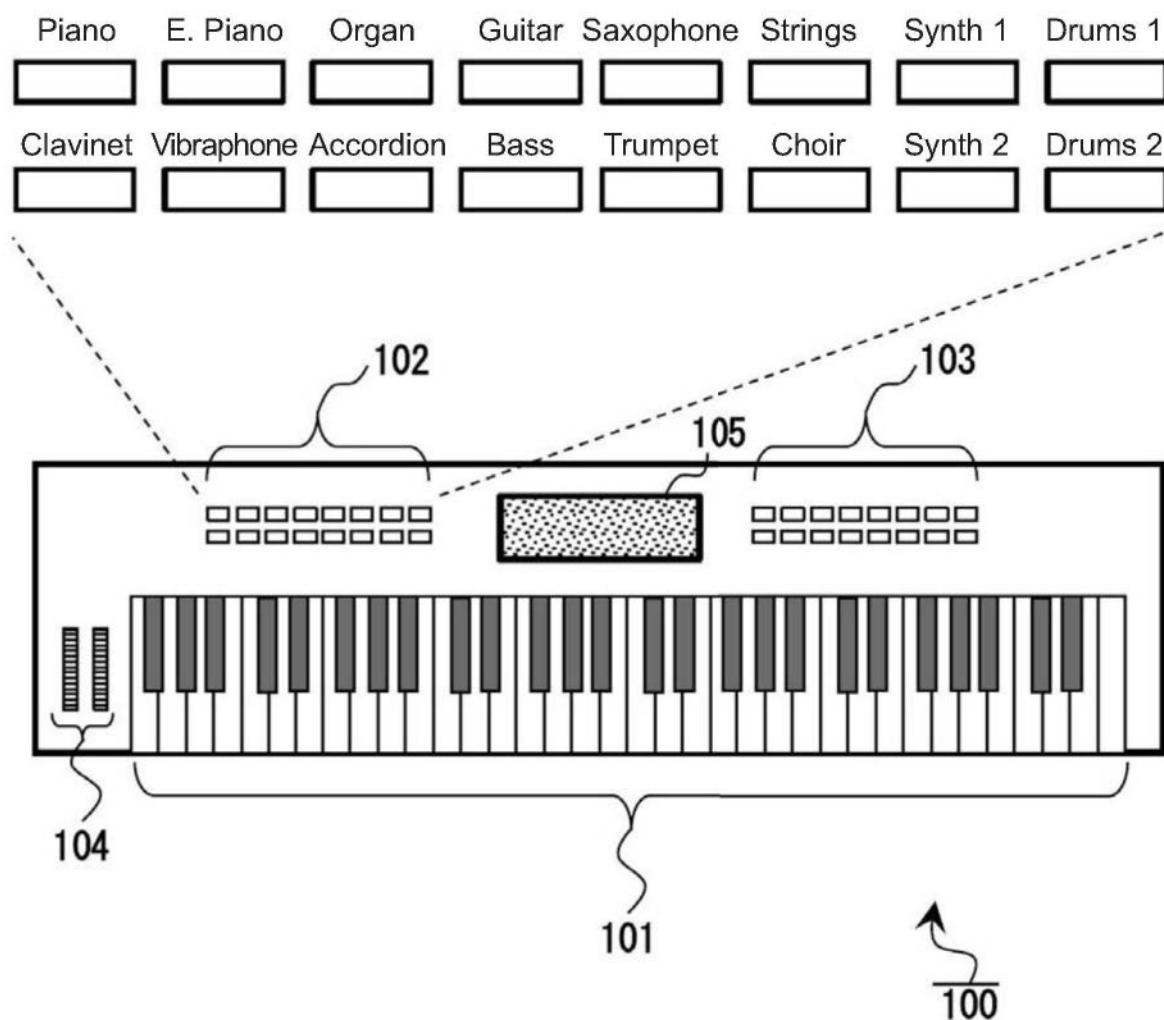

[0030] 以下,参照附图对用来实施本发明的一实施方式详细地进行说明。本实施方式以应用于例如电子键盘乐器的乐音发生装置为对象,所述乐音发生装置为了通过音高(键域)、音量(速率:敲键的快慢)等演奏信息来对音色的变化进行再现,从例如作为大容量闪存存储器的第1存储器的音色波形区域向例如作为RAM的第2存储器的波形缓存转送每个音高或音量的波形数据(以下将其称作“拆分(split)波形”)。本实施方式中,在这样的乐音发生装置中,一边由例如CPU将例如作为大容量闪存存储器的第1存储器内的波形数据向例如作为RAM的第2存储器进行转送,一边由例如音源LSI(大规模集成电路)执行将由上述转送处理转送来的第2存储器内的波形数据读入的读入处理。在这样的结构中,例如作为CPU的控制部执行第1判断处理,判断是否能够将第1存储器内的波形数据向第2存储器的多个区域中的不包含环形缓存区域的第1区域转送。此外,控制部执行第1转送处理,将在第1判断处理中判断为能够向第1区域转送的波形数据向第1区域转送。进而,控制部执行第2判断处理,判断是否能够将在第1判断处理中判断为不能向第1区域转送的波形数据向多个区域中的包含环形缓存区域的第2区域转送。并且,控制部执行第2转送处理,将在第2判断处理中判断为能够向第2区域转送的波形数据向第2区域转送。在本实施方式中,不是将波形缓存的区域等分而分配固定尺寸,而是将1个连续区域动态地划分使用,尽可能以1次的读出将1个波形的全部数据向缓存转送而进行发音,由此,使波形循环区间的转送以1次结束,减轻了总体的波形转送负荷。

[0031] 图1是本发明的电子键盘乐器的一实施方式的外观图。本实施方式作为电子键盘乐器100而被实施。电子键盘乐器100具备以下等部件:键盘101,由作为演奏操作件的多个键构成;开关面板,由作为音色选择操作件的来进行音色选择的音色选择按钮102及进行音色以外的各种功能选择的功能选择按钮103构成;变调器/调制轮(bender/modulation

wheels) 104, 附加变调(pitch bending)、震音(tremolo)、颤音(vibrato)等各种调制(演奏效果); LCD(Liquid Crystal Display: 液晶显示器) 105, 显示音色及音色以外的各种设定信息。此外, 虽然没有特别图示, 但电子键盘乐器100在里面部、侧面部或背部等具备将通过演奏生成的乐音放音的扬声器。

[0032] 音色选择按钮102如图1所示, 是用来选择钢琴(图中“Piano”)、电子钢琴(图中“E.piano”)、风琴(图中“Organ”)、吉他(图中“Guitar”)等各种音色的类别的按钮群。用户通过将该音色选择按钮102按下, 能够选择例如16个音色中的某个。

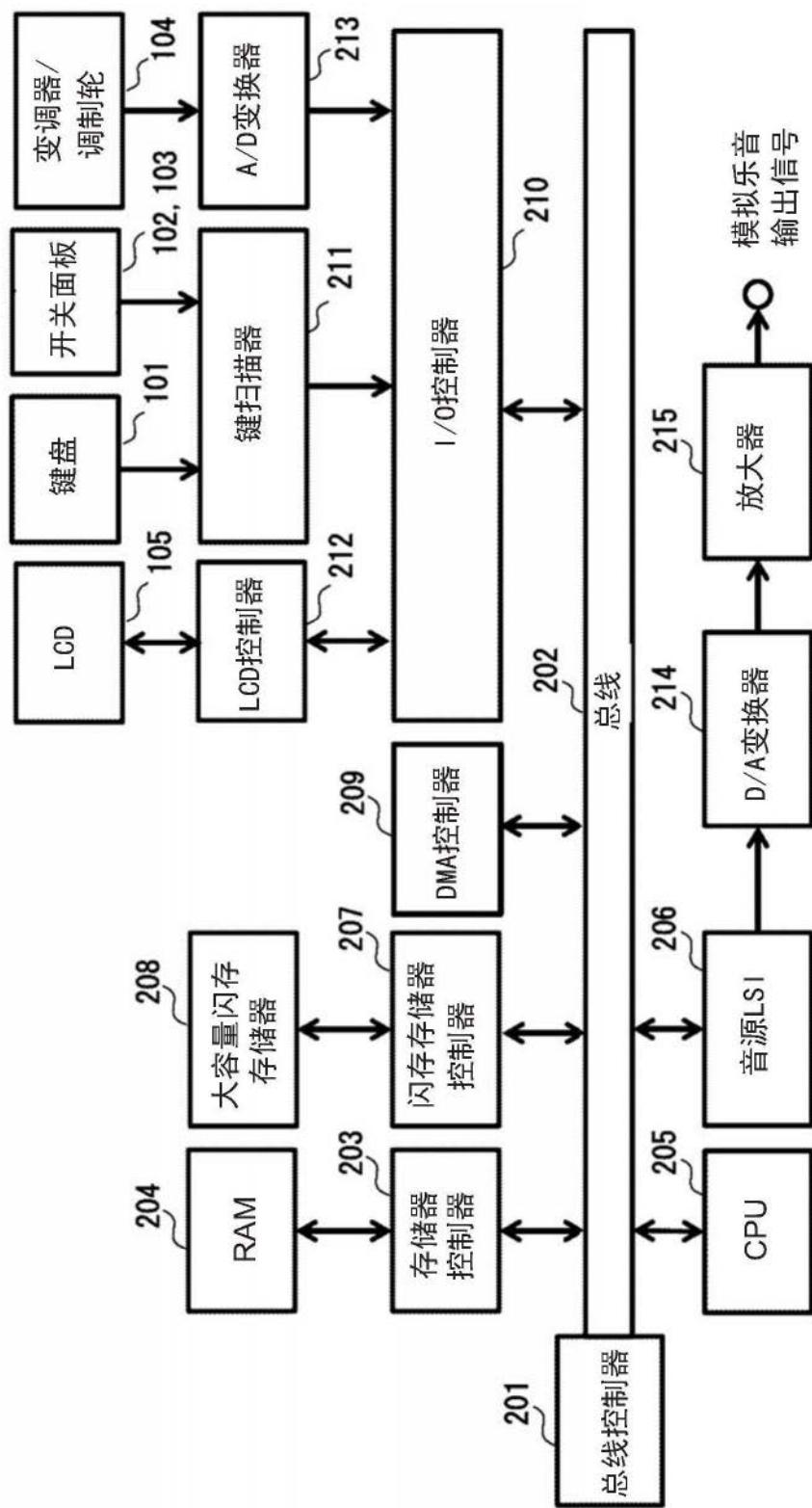

[0033] 图2是表示图1的电子键盘乐器100的实施方式的硬件例的图。在图2的电子键盘乐器100中, 系统整体被总线控制器201控制。总线控制器201控制总线202上的数据的流动, 其作用是与总线202连接的器件的优先位次的控制。例如, 经由存储器控制器203而与总线202连接的RAM204由CPU205和音源LSI206共用, 但进行发音的音源LSI206由于不允许数据的缺失而优先级被设定为最高, 根据需要而限制CPU205的访问。

[0034] 在总线202上, 连接着CPU205、音源LSI206、闪存存储器控制器207、存储器控制器203、DMA(直接存储器访问)控制器209、I/O(输入输出)控制器210、经由I/O控制器210连接的键扫描器(key scanner)211和LCD控制器212和A/D(模拟/数字)变换器213。

[0035] CPU205是执行电子键盘乐器100的整体的控制处理的第1处理器。音源LSI206是乐音发音专用的作为大规模集成电路的第2处理器。

[0036] 闪存存储器控制器207是将大容量闪存存储器208与总线202连接的接口电路。大容量闪存存储器208保存波形数据、控制程序、固定数据等。

[0037] 存储器控制器203是将RAM204与总线202连接的接口电路。RAM204根据需要而配置波形数据、控制程序、数据。RAM204还被作为CPU205或音源LSI206中内置的DSP(数字信号处理器)的工作区域而使用。

[0038] I/O控制器210是将总线202与图1的键盘101、音色选择按钮102、功能选择按钮103、变调器/调制轮104、或LCD105等周边器件进行连接的接口电路。与I/O控制器210连接的键扫描器211对图1的键盘101、音色选择按钮102或功能选择按钮103等开关面板的状态进行扫描, 将扫描结果经由I/O控制器210及总线202向CPU205通知。与I/O控制器210连接的LCD控制器212控制图1的LCD105的器件。A/D变换器213检测图1的变调器/调制轮104的操作位置。

[0039] DMA控制器209控制大容量闪存存储器208与RAM204间的DMA转送。

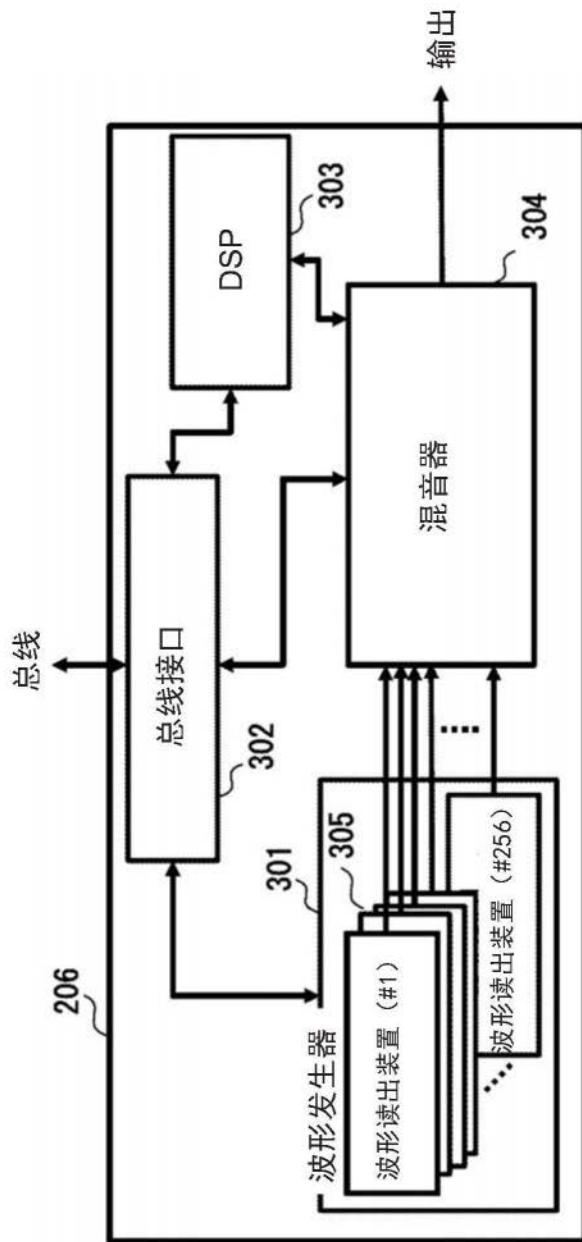

[0040] 图3是表示音源LSI206的框图。音源LSI206包括波形发生器301、总线接口302、DSP303及混音器(mixer)304。波形发生器301具备波形读出装置305, 该波形读出装置305是从图2的RAM204将波形数据读出而产生乐音波形的从#1到#256的256组振荡器。总线接口302是进行总线202与波形发生器301、DSP303及混音器304之间的连接的总线接口电路, 控制这些各部与图2的CPU205与RAM204之间的通信。DSP303是对乐音信号带来音响效果的数字信号处理电路。混音器304通过将波形发生器301输出的乐音信号混合、向DSP303发送、或接受来自DSP303的音响信号, 来控制整体的乐音信号的流动, 向外部进行输出。来自混音器304的数字乐音信号被图2的D/A变换器214变换为模拟乐音信号。该模拟乐音信号在被放大器215放大后, 被作为模拟乐音输出信号输出。

[0041] 接着, 图2的大容量闪存存储器208是NAND型闪存存储器等大容量且便宜的存储器

器件。另外,也可以代替该大容量闪存存储器208而使用硬盘存储装置、网络上或云上的盘装置。在大容量闪存存储器208中,主要保存有以下这样的数据。

- [0042] • 全部的音色的波形数据

- [0043] • 全部的音色的参数数据

- [0044] ■CPU205、DSP303执行的程序,程序的使用数据

- [0045] ■音乐数据

- [0046] ■用户的设定数据

- [0047] 波形数据例如是1个字长为16比特的线性PCM格式数据。

- [0048] 关于上述的大容量闪存存储器208的内容,能够从CPU205进行向任意的地址的访问,但不能从音源LSI206访问,所以需要将大容量闪存存储器208中的波形数据向RAM204转送。但是,由于RAM204的存储容量比大容量闪存存储器208小,所以无法将全部数据转送给RAM204中的每个发音声道的缓存区域。因而,RAM204的存储内容需要根据需要而依次替换。在需要替换的数据之中,本实施方式特别作为对象的是波形数据,关于波形数据的控制的详细情况在后面叙述。

- [0049] 以下对图1至图3的本实施方式的动作的概要进行说明。首先,在本实施例中,演奏者通过将图1的音色选择按钮102中的一个按下,能够选择图1中表示的16个音色中的某个。关于各音色,每1个音色分别最大由32种波形构成,波形数据被保存在大容量闪存存储器208中。1个音色的音域(键号码)和速率域被二维地划分,对于各个拆分(划分)区,分配了上述的最大32个波形。即,实施如下这样的控制:根据按键时的快慢(速率)和键号码(键盘101的号码)这2个因素,仅决定1个要读出的波形。

[0050] 本实施例的音源LSI206在波形读出时能够执行循环处理。图4是波形读出循环的动作的说明图。基于以下的3个地址信息执行循环处理的控制。

- [0051] 1. 波形缓存起始地址:音源LSI206开始读出所用到的地址

- [0052] 2. 波形缓存结束地址:音源LSI206进行读出的最后方的地址

- [0053] 3. 波形缓存循环地址:存在于波形缓存起始地址与波形缓存结束地址之间,在波形读出到达了波形缓存结束地址的情况下,接着被读出的是该波形缓存循环地址。

[0054] 如图4所示,波形缓存由非循环区间(第1区域)和循环区间(第2区域)构成,非循环区间(第1区域)从波形缓存起始地址到波形缓存循环地址的紧前,不作为环形缓存发挥功能,循环区间(第2区域)从波形缓存循环地址到波形缓存结束地址,作为环形缓存发挥功能。当存储在波形缓存中的从波形缓存起始地址到波形缓存结束地址的波形数据被读出时,在从波形缓存循环地址到波形缓存结束地址的循环区间中,反复执行读出动作。另外,在波形缓存循环地址与波形缓存结束地址相等的情况下,不进行循环处理,在读出指针(read pointer)到达波形缓存结束地址的时点,发音停止。

[0055] 图5是表示“闪存存储器音色波形目录”的数据例的图。闪存存储器音色波形目录是将保存在大容量闪存存储器208上的全部的波形数据的信息汇总而成的表。具体而言,该表是将以下信息汇总而成的表,即:表示由“音色号码”及“音色内波形号码”决定的各音色的各波形分别被使用的键域的“最低键号码”和“最高键号码”、作为上述各波形分别被使用的速率域信息的“最低速率”和“最高速率”、表示实际被配置在大容量闪存存储器208的哪个地址的“距波形区域开头的地址”、表示波形的长度的“波形尺寸”、在读出中使用的“起始

地址”、“循环地址”及“结束地址”。该表在接通电源时被展开到RAM204上。

[0056] 图6是表示“RAM波形缓存目录”的数据例的图。RAM波形缓存目录是将保存在RAM204的波形缓存上的波形数据的信息汇总而成的表。该表上的由缓存号码b决定的缓存目录之一所具有的信息中,保存有以下信息:表示波形缓存b的使用状态的“缓存状态vs[b]”;分别表示波形缓存b自身的起始位置、循环位置、结束位置的“波形缓存起始地址bsa[b]”、“波形缓存循环地址bla[b]”及“波形缓存结束地址bea[b]”;分别表示与波形缓存b对应的转送源的大容量闪存存储器208的音色波形区域的起始位置、循环位置、结束位置的“起始地址sa[b]”、“循环地址1a[b]”及“结束地址ea[b]”;CPU205在大容量闪存存储器208上的当前的转送波形的读出地址即“转送数据指针”;CPU205向RAM204的转送写入地址即“写入指针”;音源LSI206在RAM204上的当前的读出地址即“读出指针”;以及写入指针与读出指针最新值之间的差分即“波形读出裕度(margin)”。

[0057] 在图6的例子中,表的缓存信息的数量准备了256个。这并不是实际上RAM204上的波形缓存总是被划分为256个,在初始状态下表示连续的可转送区域的缓存信息仅存在1个,该缓存的缓存状态vs[b]是1。该缓存的缓存起始地址和缓存结束地址保存缓存区域的全部的开头和最末尾。其以外的缓存的信息的缓存状态由于不指示具体的RAM空间(RAM204的地址空间),所以具有NULL值。

[0058] 图7是从大容量闪存存储器208上的音色波形区域向RAM204上的波形缓存的音色波形转送动作的说明图。首先,如果被演奏,则调查应被转送的波形的号码。首先,不论该号码的波形是使用中还是可转送状态,都调查所希望的波形是否保留在RAM204上。如果存在,则不进行波形转送,保留着的波形被用作高速缓存波形。

[0059] 如果没有高速缓存波形,则接下来检索是否有比波形尺寸大的空闲区域,如果找到,则将该可转送区域作为波形缓存,开始波形转送。这里,如果1个可转送区域的尺寸足够则其被使用。在没有找到尺寸足够的可转送区域的情况下,搜索2个以上的连续的可转送区域,如果其合计尺寸足够则其被使用。在此情况下,波形缓存的目录信息被归纳为1个,空着的目录信息的状态被设为NULL。

[0060] 在即便这样也没有找到的情况下,在本实施例中,搜索环形缓存的所需容量即16KB的空闲区域,找到的区域以环形缓存方式被使用从而进行发音。在环形缓存方式下,是通过将波形缓存作为环来处理从而确保看起来为无限的存储器空间的方法。在此情况下,实施控制,以使CPU205的写入指针的地址值既不会超出音源LSI206的读出指针的地址值也不会被其赶超。在连该环形缓存区域也找不到的情况下,放弃发音。

[0061] 此外,如果波形缓存v的写入指针wp[v]超越了音源LSI206的读出指针rp[v],则音源LSI206读出的波形数据突然不连续地回到过去的数据,导致产生噪声。这是在音乐上不能容许的。

[0062] 因此,在本实施例中,将表示在不填补波形数据的状态下波形缓存v中的读出指针rp[v]能读出多少的数据的字数(地址)即写入指针wp[v]的值与读出指针rp[v]的值的差分,作为波形读出裕度来管理。在本实施方式中,在该波形读出裕度达到规定的值以下的情况下,对于产生该乐音的声音声道(voice channel1)执行减弱处理(damping process)(平缓的消音处理),在该处理后发音停止的时点从该声音声道的波形缓存v的读出中止,由此能够防止噪声的产生。

[0063] 在本实施例中,该波形读出裕度的阈值不是固定值,考虑再现音调,当在基音音调的再现时成为不到1K字、在升1个八度音的音调下的再现时成为不到2K字、在降1个八度音的音调下的再现时成为不到512字,则减弱处理的执行被决定。

[0064] 关于减弱处理的速度,只要是即使保持原样而不补充波形地进行读取、在已经被转送到波形缓存v中的读入裕度量的波形数据被读完之前能够消音的速度就可以。该速度依存于当前的再现音调。

[0065] 图8是表示图2的CPU205执行的控制处理的主程序的处理例的流程图。在图1的电子键盘乐器100中,当通过功能选择按钮103将装置电源接通,则CPU205启动由图8的流程图表示的主程序,首先执行将装置各部初始化的初始化处理(步骤S801)。当步骤S801的初始化处理完成,则反复执行以下处理:开关处理(步骤S802),由用户取得图1的音色选择按钮102或功能选择按钮103的操作状态;基于步骤S802的处理结果的音色选择按钮102被操作时的音色选择事件的检测及音色选择处理(步骤S803→S804);键盘处理(步骤S805),取得当用户弹奏了图1的键盘101时的按键事件、放键事件;基于步骤S805的处理结果的按键事件的检测及按键处理(步骤S806→S807);基于步骤S805的处理结果的放键事件的检测及放键处理(步骤S808→S809);以及音源事件处理(步骤S810),进行来自音源LSI206的事件的处理。

[0066] 图9A是表示图8的步骤S801的初始化处理的详细例的流程图。首先,CPU205从大容量闪存存储器208将闪存存储器音色波形目录(参照图5)的表数据向RAM204上的指定的地址转送(步骤S901)。

[0067] 接着,通过步骤S902和步骤S906的反复控制处理,执行缓存信息数(=256)的量的循环处理。在该循环处理中的步骤S903中,判定缓存号码b(参照图6的RAM波形缓存目录)的值。

[0068] CPU205在缓存号码b=0时,将存储在RAM204中的图6中例示的RAM波形缓存目录初始化后,将该目录内的缓存号码b=0所对应的缓存状态设定为可转送(=1)(步骤S903→S904)。然后,CPU205继续进行循环处理(步骤S904→S906)。

[0069] 另一方面,CPU205在缓存号码b≠0时,将RAM波形缓存目录初始化后,将该目录内的上述缓存号码b所对应的缓存状态设定为NULL(=0)(步骤S903→S905)。然后,CPU205继续进行循环处理(步骤S905→S906)。

[0070] 在上述步骤S902至S906的循环处理结束后,CPU205将RAM204上的波形缓存的链接信息(link information)初始化(步骤S907)。所谓链接信息,是对于RAM204上的波形缓存区域、从开头起依次使用哪个RAM波形缓存的能够取得缓存号码的信息。在初始化时,由于波形区域是1个,所以链接信息的开头号码被设定为0。

[0071] 接着,CPU205将向RAM204上的波形缓存的访问计数值进行初始化(步骤S908)。所谓访问计数值,是表示波形读出装置305(参照图3)对于由RAM波形缓存目录(参照图6)的缓存号码b指定的波形数据访问了多少的信息。

[0072] 接着,CPU205将用来管理从大容量闪存存储器208的音色波形区域向波形缓存的波形转送的转送请求计数器、转送状态标志、转送请求缓存(链接构造)初始化(S909)。转送请求计数器是对于RAM204上的波形缓存、管理由RAM波形缓存目录表示的缓存中的处于波形数据转送中的缓存当前有几个的信息。转送状态标志是判断是否正在从音色波形区域向

波形缓存转送波形数据的标志信息。转送请求缓存是用来管理接下来对哪个波形缓存进行从音色波形区域向波形缓存的波形转送的缓存。然后,CPU205结束由图9A的流程图表示的图8的步骤S801的初始化处理。

[0073] 图9B是表示图8的步骤S804的音色选择处理的详细例的流程图。CPU205为了在按键处理等中使用而将由图1的音色选择按钮102的操作指定的音色号码保存到CPU205内的工作存储器等中(步骤S910)。

[0074] 图10及图11是表示图8的步骤S807的按键处理的详细例的流程图。CPU205将由键被弹奏时的按键带来的演奏信息(键位置、被按下的强度)变换为键号码、速率,基于它们执行控制处理。

[0075] CPU205首先执行决定对该按键下的发音使用音源LSI206内的哪个波形读出装置305(图3)的声音分派(voice assignment) (步骤S1001)。

[0076] 接着,CPU205根据键号码、速率、当前的音色号码,取得应从音色波形区域向波形缓存进行转送的波形号码w(步骤S1002)。

[0077] 接着,CPU205根据从键号码、波形号码w得到的波形信息,计算再现音调(步骤S1003)。

[0078] 接着,CPU205根据再现音调,决定波形读出裕度(参照图6) (步骤S1004)。

[0079] 接着,CPU205执行高速缓存波形确认处理,即:确认从按键信息取得的波形号码的波形数据是否已经存在于RAM204上的波形缓存(步骤S1005)。关于该处理的详细情况,使用图13D在后面叙述。

[0080] 在步骤S1005的高速缓存波形确认处理的结果是波形数据已经存在于RAM204上的某个波形缓存中的情况下,CPU205使用该波形数据作为高速缓存波形,开始由音源LSI206内的波形读出装置305(图3)进行的波形读出(图10的步骤S1005→图11的步骤S1019)。然后,CPU205结束在图10和图11的流程图中表示的图8的步骤S807的按键处理。

[0081] 在步骤S1005的高速缓存波形确认处理的结果是高速缓存波形数据不存在于RAM204上的情况下,CPU205如下这样进行可转送波形数据的波形缓存的确认处理。CPU205根据RAM204上的波形缓存的链接信息,取得RAM204上的波形缓存区域对应的开头的缓存号码(步骤S1005→S1006)。

[0082] 接着,CPU205在对于RAM204上的波形缓存的循环处理时,将表示对于紧前的缓存号码的缓存状态是可转送的标志(以下记作“标志A”)初始化为0(步骤S1007)。

[0083] 接着,CPU205通过步骤S1008和S1014的循环控制处理,与RAM波形缓存目录(图6)的缓存信息数相应地,反复执行以下的步骤S1009至S1013的一系列处理。

[0084] 在该一系列处理中,CPU205首先对于从链接信息取得的缓存号码b,判定缓存状态(图6) (步骤S1009)。

[0085] CPU205在缓存状态的值是NULL(=0)、减衰中(=4)或环形缓存使用中(=5) (参照图6)的情况下,将标志A设定为0(步骤S1010)。

[0086] 接着,CPU205根据RAM204上的波形缓存的链接信息,取得接下来处理的缓存号码(步骤S1011)。然后,CPU205继续反复处理(步骤S1011→S1014)。

[0087] CPU205在缓存状态的值是可转送(=1) (参照图6)的情况下,执行缓存状态是可转送时的处理(步骤S1012)。关于该处理的详细情况,使用图12在后面叙述。然后,CPU205继续

反复处理(步骤S1012→S1014)。

[0088] CPU205在缓存状态的值是发音中(=2或3)(参照图6)的情况下,执行缓存状态是发音中时的处理(步骤S1013)。关于该处理的详细情况,使用图13C在后面叙述。然后,CPU205继续反复处理(步骤S1013→S1014)。

[0089] CPU205在上述的步骤S1008至S1014的反复处理结束的时点,判定RAM波形缓存目录(图6)所示的某个缓存号码是否已被分派(图11的步骤S1015)。

[0090] CPU205在通过步骤S1015判定为某个缓存号码b已被分派的情况下,对于与缓存号码b对应的波形缓存,判定是否处于波形数据转送中(图11的步骤S1015→S1016)。

[0091] CPU205在通过步骤S1016判定为转送完成的情况下,开始由音源LSI206内的波形读出装置305(图3)进行的波形读出(步骤S1016→S1019)。然后,CPU205结束由图10和图11的流程图表示的图8的步骤S807的按键处理。

[0092] CPU205在通过步骤S1016判定为处于转送中的情况下,反复执行根据与缓存号码b对应的写入指针wp[b]与读出指针rp[b]的差分进行的波形读出裕度的计算(步骤S1017)、和当前的波形读出裕度是否变得比波形读出开始裕度的阈值大的判定(步骤S1018)。如果最终在步骤S1018中判定为当前的波形读出裕度变得比波形读出开始裕度的阈值大,则CPU205开始由音源LSI206的波形读出装置305(图3)进行的波形读出(步骤S1018→S1019)。然后,CPU205结束由图10和图11的流程图表示的图8的步骤S807的按键处理。

[0093] CPU205在通过步骤S1015判定为哪个缓存号码都没有被分派的情况下,从CPU205内的工作存储器等中,判定是否有16KB以上的可转送缓存(步骤S1015→S1020)。

[0094] 如果步骤S1020的判定为“是”,则CPU205执行环形缓存方式下的发音处理(步骤S1020→S1021)。然后,CPU205结束由图10和图11的流程图例示的图8的步骤S807的按键处理。

[0095] 如果步骤S1020的判定也为“否”,则CPU205放弃发音处理,结束由图10和图11的流程图例示的图8的步骤S807的按键处理。

[0096] 图13D是表示图10的步骤S1005的高速缓存波形确认处理的详细例的流程图。

[0097] CPU205首先通过步骤S1430和S1436的反复控制处理,与RAM波形缓存目录(图6)的缓存信息数相应地,反复执行以下的步骤S1431至S1435的一系列处理。

[0098] 在上述一系列处理中,CPU205首先对于从链接信息取得的缓存号码b,判定缓存状态(图6)(步骤S1431)。

[0099] CPU205在缓存状态的值是NULL(=0)、减衰中(=4)或环形缓存使用中(=5)(参照图6)的情况下,直接结束对于当前的缓存号码b的处理,转移到对于下个缓存号码的处理(步骤S1431→S1436)。

[0100] CPU205在缓存状态的值是可转送(=1)或发音中(=2或3)(参照图6)的情况下,判定根据按键信息取得的波形号码的波形数据是否与由RAM波形缓存目录表示的当前的缓存号码b的波形缓存的波形数据相同(步骤S1432)。

[0101] CPU205在通过步骤S1432判定为上述各波形数据不同的情况下,直接结束对于当前的缓存号码b的处理,转移到对于下个缓存号码的处理(步骤S1432→S1436)。

[0102] CPU205在通过步骤S1432判定为上述各波形数据相同的情况下,将缓存状态变更发音中(步骤S1433)。

[0103] 接着,CPU205将向RAM波形缓存的访问计数值递增(步骤S1434)。

[0104] 并且,CPU205使得使用处于当前的缓存号码b的高速缓存波形,结束由图13D的流程图例示的图10的步骤S1005的高速缓存波形确认处理。

[0105] 在通过步骤S1436全部的反复处理结束的情况下,CPU205设为无高速缓存波形,结束由图13D的流程图例示的图10的步骤S1005的高速缓存波形确认处理。

[0106] 图12是表示图10的步骤S1012的缓存状态为可转送时的处理的详细例的流程图。

[0107] 首先,CPU205取得当前的缓存号码b的波形缓存的尺寸buf\_sz(步骤S1201)。buf\_sz能够作为RAM波形缓存目录内的缓存号码b对应的波形缓存结束地址与波形缓存起始地址之差来算出。

[0108] 接着,CPU205将上述buf\_sz与从按键信息取得的波形号码w的波形数据的尺寸(wave\_sz[w])进行比较(步骤S1202)。wave\_sz[w]能够作为图5的闪存存储器音色波形目录中的相应波形号码w所对应的波形尺寸来算出。

[0109] CPU205在通过步骤S1202判定为波形缓存的尺寸buf\_sz是与按键对应的波形数据的尺寸wave\_sz[w]以上的情况下,执行RAM波形缓存划分处理。关于该处理的详细情况,使用图13A在后面叙述。

[0110] CPU205在通过步骤S1202判定为波形缓存的尺寸buf\_sz比与按键对应的波形数据的尺寸wave\_sz[w]小的情况下,判定标志A的值(步骤S1209)。

[0111] CPU205在通过步骤S1209判定为标志A的值是1的情况下,比较将存储在CPU205的工作存储器中的连续的紧前的波形缓存尺寸pre\_buf\_sz(参照步骤S1213)和当前的波形缓存的尺寸buf\_sz相加后的波形缓存尺寸pre\_buf\_sz+buf\_sz、与波形数据的尺寸wave\_sz[w](步骤S1210)。

[0112] CPU205在通过步骤S1210判定为pre\_buf\_sz+buf\_sz是wave\_sz[w]以上的情况下,执行RAM波形缓存结合处理。关于该处理的详细情况,使用图13A在后面叙述。

[0113] 在步骤S1203的RAM波形缓存划分处理或步骤S1211的RAM波形缓存结合处理后,CPU205将对于缓存号码b的缓存的写入指针wp[b]和读出指针rp[b]设定为0(步骤S1204)。

[0114] 接着,CPU205对于后述的波形转送管理处理,发出新转送请求事件(步骤S1205)。

[0115] 然后,CPU205更新由当前的缓存号码b表示的缓存的地址信息(参照图6)即波形缓存起始地址bsa[b]、波形缓存循环地址bla[b]、波形缓存结束地址bea[b]、起始地址sa[b]、循环地址1a[b]、结束地址ea[b](步骤S1206)。

[0116] 接着,CPU205更新由当前的缓存号码b表示的波形缓存的波形读出裕度(参照图6)(步骤S1207)。

[0117] 进而,CPU205将由当前的缓存号码b表示的缓存状态(参照图6)变更为发音中(步骤S1208)。

[0118] 并且,CPU205将向RAM204上的波形缓存的访问计数值递增(步骤S1212)。然后,CPU205结束由图12的流程图例示的图10的步骤S1012的缓存状态为可转送时的处理,并退出图10的步骤S1008至S1014的循环处理。

[0119] CPU205在通过步骤S1209判定为标志A的值是0的情况下,或者在通过步骤S1210判定为pre\_buf\_sz+buf\_sz比wave\_sz[w]小的情况下,执行步骤S1213至S1217的一系列处理。

[0120] 在该一系列处理中,CPU205首先将当前的波形缓存的尺寸buf\_sz作为pre\_buf\_sz

保存到CPU205内的工作存储器等中,以便能够在接下来的循环处理中使用(步骤S1213)。

[0121] 接着,CPU205判定波形缓存尺寸buf\_sz(步骤S1214)。

[0122] CPU205在通过步骤S1214判定为buf\_sz是16KB以上的情况下,将缓存号码b保存到CPU205内的工作存储器等中(步骤S1215)。CPU205在通过步骤S1214判定为buf\_sz比16KB小的情况下,将上述步骤S1215的处理跳过。

[0123] 然后,CPU205将标志A的值设定为1(步骤S1216)。

[0124] 进而,CPU205根据RAM波形缓存的链接信息,取得接下来处理的缓存号码(步骤S1217)。然后,CPU205结束由图12的流程图例示的图10的步骤S1012的缓存状态为可转送时的处理,继续图10的步骤S1008至S1014的反复处理。

[0125] 图13A是表示图12的步骤S1203的RAM波形缓存划分处理的详细例的流程图。

[0126] 首先,CPU205将缓存尺寸buf\_sz与根据按键信息取得的波形号码w的波形数据的尺寸(wave\_sz[w])进行比较(步骤S1301)。

[0127] CPU205在通过步骤S1301判定为波形缓存的尺寸buf\_sz是与按键对应的波形数据的尺寸wave\_sz[w]以下的情况下,直接结束由图13的流程图例示的图12的步骤S1203的RAM波形缓存划分处理。

[0128] CPU205在通过步骤S1301判定为波形缓存的尺寸buf\_sz比与按键对应的波形数据的尺寸wave\_sz[w]大的情况下,进行仅使用波形数据的量并将其余设为可转送的波形缓存的划分。首先,CPU205将当前的缓存号码的波形缓存的尺寸设定为与波形数据相同的尺寸(步骤S1302)。

[0129] 接着,CPU205根据RAM波形缓存的链接信息,取得缓存状态是NULL的缓存的缓存号码。接着,CPU205设定从上述缓存尺寸buf\_sz减去波形数据的尺寸wave\_sz[w]后的剩余尺寸,将缓存状态设定为可转送(以上是步骤S1303)。

[0130] 最后,CPU205对于RAM波形缓存的链接信息进行更新,以使得将缓存状态设为了可转送的缓存在当前缓存的紧后(步骤S1304)。然后,CPU205结束由图13A的流程图表示的图12的步骤S1203的RAM波形缓存划分处理。

[0131] 图13B是表示图12的步骤S1211的RAM波形缓存结合处理的详细例的流程图。

[0132] 首先,CPU205将与紧前的缓存号码对应的缓存状态变更为NULL(步骤S1310)。

[0133] 并且,CPU205对于RAM波形缓存的链接信息进行更新,以使得对于紧前的缓存号码和当前的缓存号码而言紧前的缓存号码变成最末尾(步骤S1311)。然后,CPU205结束由图13B的流程图表示的图12的步骤S1211的RAM波形缓存结合处理。

[0134] 图13C是表示图10的步骤S1013的缓存状态为发音中的处理的详细例的流程图。

[0135] CPU205首先将标志A设定为0(步骤S1320)。

[0136] 并且,CPU205根据RAM波形缓存的链接信息,取得接下来处理的缓存号码(步骤S1321)。然后,CPU205结束由图13C的流程图例示的图10的步骤S1013的缓存状态为发音中的处理,继续图10的步骤S1008至S1014的反复处理。

[0137] 图14及图15是表示波形转送管理处理的流程图。CPU205通过图14的步骤S1401、S1402及S1403,分别判定对于波形转送管理处理发出的事件是新转送请求、转送请求、转送结束或转送停止中的哪个,执行与各个事件对应的处理。

[0138] 在发出了新转送请求事件的情况下(参照图12的步骤S1205),图14的步骤S1401的

判定为“是”，执行图15的步骤S1416的处理。在步骤S1416中，CPU205确认转送状态标志。

[0139] 在通过步骤S1416判定为转送状态标志是转送结束等待的情况下，由于处在对于其他缓存进行从音色波形区域向波形缓存的波形转送的过程中，所以CPU205将相应缓存设定到转送请求缓存的开头，以使得通过基于其他缓存的转送结束事件的转送请求事件进行处理(图15的步骤S1425)。然后，CPU205结束由图14及图15的流程图表示的波形转送管理处理。

[0140] 在通过步骤S1416判定为转送状态标志是待机状态的情况下，CPU205首先对于相应缓存号码，指定每1次转送的读出尺寸(这里是2页)，向后述的波形读出、波形缓存转送处理(图16)发出转送请求(图15的步骤S1417)。

[0141] 接着，CPU205将转送状态标志设定为转送结束等待(图15的步骤S1418)，将相应缓存设定到转送请求缓存的最末尾(图15的步骤S1419)。

[0142] 接着，CPU205将转送数据指针tp[v]更新(图15的步骤S1420)，将转送请求缓存计数器递增(图15的步骤S1421)。

[0143] 接着，CPU205判定缓存状态(图15的步骤S1422)。在判定为缓存状态是vs[b]=2或3或4或5的情况下，由于在波形缓存内全部的波形为可转送，所以判定是否全部数据转送完成(图15的步骤S1423)。该判定能够根据转送数据指针是否到达结束地址来判断。

[0144] 在全部数据的转送完成的情况下，由于不需要进一步的转送，所以对于波形转送管理处理发出转送停止事件(图15的步骤S1424)。然后，CPU205结束由图14及图15的流程图表示的波形转送管理处理。

[0145] 在通过步骤S1422判定为缓存状态是vs[b]=2或3或4或5以外的情况下，或者在通过步骤S1423判定为不是全部数据的转送已完成的情况下，CPU205结束由图14及图15的流程图表示的波形转送管理处理。

[0146] 在后述的波形读出、波形缓存转送处理中指定尺寸量的波形数据的转送结束、对于波形转送管理处理发出了转送结束的请求事件的情况下(图16的步骤S1607)，图14的步骤S1401及S1402的判定为“否”(其他事件)，步骤S1403的判定为“是”(转送结束)，执行图14的步骤S1406的处理。在步骤S1406中，CPU205判定在转送请求缓存中是否有转送等待的缓存，即，判定转送请求缓存计数器是否是0。

[0147] 如果步骤S1406的判定为“否”，则是从音色波形区域向波形缓存的全部的转送结束的状态，所以CPU205什么都不做，结束由图14及图15的流程图例示的当前的波形转送管理处理。

[0148] 如果步骤S1406的判定为“是”，则CPU205对于波形转送管理处理发出转送请求事件，以使得处理接下来的缓存(步骤S1407)，结束由图14及图15的流程图例示的当前的波形转送管理处理。

[0149] 当通过上述图14的步骤S1407的处理、对于波形转送管理处理发出了转送请求事件，则图14的步骤S1401的判定为“否”(其他事件)，步骤S1402的判定为“是”(转送请求)，执行图14的步骤S1408的处理。在步骤S1408中，CPU205对于转送请求缓存的开头的缓存执行转送处理。确认写入指针wp[v]和读出指针rp[v]，进行向波形缓存v的转送，从而在写入指针wp[v]超越读出指针rp[v]的情况下，关于该缓存v，设定到转送请求缓存的最末尾，对于从开头起第2个的缓存进行处理。

[0150] 接着,CPU205对相应缓存号码指定每1次转送的读出尺寸(这里是2页),向后述的波形读出、波形缓存转送处理(图16)发出转送请求(图14的步骤S1409)。

[0151] 接着,CPU205将转送状态标志设定为转送结束等待(图14的步骤S1410),将相应缓存设定到转送请求缓存的最末尾(图14的步骤S1411)。

[0152] 接着,CPU205将转送数据指针tp[v]更新(图14的步骤S1412)。

[0153] 接着,CPU205判定缓存状态(图14的步骤S1413)。在判定为缓存状态是vs[b]=2或3或4或5的情况下,判定在波形缓存内是否波形的全部数据转送完成(图14的步骤S1414)。该判定能够根据转送数据指针是否到达了结束地址来判断。

[0154] 在全部数据的转送完成的情况下,由于不需要进一步的转送,所以对于波形转送管理处理发出转送停止事件(图14的步骤S1415)。然后,CPU205结束由图14及图15的流程图表示的波形转送管理处理。

[0155] 在通过步骤S1413判定为缓存状态是vs[b]=2或3或4或5以外的情况下,或者在通过步骤S1414判定为不是全部数据的转送完成的情况下,CPU205结束由图14及图15的流程图表示的波形转送管理处理。

[0156] 在图15的步骤S1424、图14的步骤S1415、或后述的音源事件处理(图17的步骤S1708)中对于波形转送管理处理发出了转送停止事件的情况下,图14的步骤S1401、S1402及S1403的判定都为“否”(其他事件或转送停止),执行步骤S1404。在此情况下,CPU205从转送请求缓存将相应缓存删除(步骤S1404),将转送请求缓存计数器递减(步骤S1405)。然后,CPU205结束由图14及图15的流程图表示的波形转送管理处理。

[0157] 图16是表示波形读出、波形缓存转送处理的流程图。该流程图的处理通过来自图15的步骤S1417或图14的步骤S1409的转送请求事件而起动。

[0158] CPU205通过步骤S1601和S1605的循环控制处理,与由波形转送管理处理(图15的步骤S1417或图14的步骤S1409)指定的指定尺寸的量相应地,反复执行以下的步骤S1602至S1604的一系列处理。

[0159] 首先,在步骤S1602中,CPU205基于转送数据指针tp[v],从大容量闪存存储器208的音色波形区域w以页单位将波形数据读入。

[0160] 接着,在步骤S1603中,CPU205考虑波形缓存循环地址及波形缓存结束地址,在循环读出的情况下,将不需要的部分弃读。

[0161] 并且,在步骤S1604中,CPU205向与波形缓存v的写入指针wp[v]对应的地址,进行在步骤S1602及S1603中从音色波形区域w读出的波形数据的写入。CPU205对应于写入的尺寸的量而将写入指针wp[v]更新。

[0162] 当上述步骤S1601至S1605的反复处理结束,则CPU205对于转送状态标志设定待机状态(步骤S1606),对于上述的波形转送管理处理发出转送结束事件(步骤S1607)。然后,CPU205结束由图16的流程图表示的波形读出、波形缓存转送处理。

[0163] 图17是表示图8的步骤S810的音源事件处理的详细例的流程图。CPU205判定通过图8的步骤S809的放键处理、转变为释放状态的缓存是否达到了释放水平(release level)(步骤S1701)。

[0164] CPU205在步骤S1701的判定中没有判定为达到释放水平的情况下,直接结束由图17的流程图表示的图8的步骤S810的音源事件处理。

[0165] CPU205在步骤S1701的判定中判定了达到释放水平的情况下,对于与该判定对应的音源LSI206内的波形读出装置305(图3),指示波形读出的停止(发音结束)(步骤S1702)。

[0166] 接着,CPU205将向RAM上的波形缓存的访问计数值递减(步骤S1703)。

[0167] CPU205判定步骤S1703中的递减处理后的访问计数值的值(步骤S1704)。

[0168] CPU205在步骤S1704的判定中判定为访问计数值的值是0的情况下,将对应的波形缓存的缓存状态设定为可转送(步骤S1705)。

[0169] CPU205在步骤S1704的判定中判定为访问计数值的值不是0的情况下,将步骤S1705的处理跳过。

[0170] 接着,CPU205判定缓存状态(步骤S1706)。

[0171] CPU205在步骤S1706的判定中判定为环形缓存不是使用中的情况下,进一步判定是否全部数据的转送完成(步骤S1707)。

[0172] CPU205在步骤S1706的判定中判定为环形缓存是使用中的情况下,或者在步骤S1707的判定中判定为没有完成全部数据的转送的情况下,对于上述的波形转送管理处理发出转送停止事件(步骤S1708)。然后,CPU205结束由图17的流程图例示的图8的步骤S810的音源事件处理。

[0173] CPU205在步骤S1707的判定中判定为全部数据的转送完成的情况下,直接结束由图17的流程图例示的图8的步骤S810的音源事件处理。

[0174] 如以上说明的那样,在本发明的一实施方式中,在具有保存音源LSI206读出的波形数据的高速小容量的RAM204、和保持设备全部的音色波形数据的NAND闪存等低速大容量闪存存储器208、在演奏时从大容量闪存存储器208内的音色波形区域向RAM204内的波形缓存开始转送、在规定容量转送后音源开始读出的依次转送型乐音发生装置中,不是将波形缓存的区域等分而分配固定尺寸,而是将1个连续区域动态地划分使用,以1次的读出将1个波形的全部的数据向缓存转送而进行发音,由此,使波形循环区间的转送进行1次即可,能够减轻总体的波形转送负荷。此外,在本实施方式中,如果在波形缓存上保留有新的发音所需要的波形,则能够作为高速缓存波形再利用。进而,在本实施方式中,在不能确保将波形数据读出的波形缓存的情况下,将剩余的区域用作环形缓存,由此,能够进行以往那样的循环读出。通过这些控制,在本实施方式中,能够实现能够改善同时发音数的乐音发生装置、或使用这样的乐音发生装置的电子乐器。或者,能够实现能够削减用来改善性能下降的硬件的成本的乐音发生装置、或使用这样的乐音发生装置的电子乐器。

[0175] 也可以是,除了以上说明的实施方式的动作以外,还实施以下这样的控制动作。在上述的实施方式中,在连能够用作环形缓存的区域(第2区域)都无法确保的情况下,不是放弃发音,而是执行以下这样的处理。执行将波形缓存(第2存储器)内的多个区域中的已存储有其他波形数据的区域确保为可转送波形数据的可转送区域的转送区域确保处理、和将波形数据向通过转送区域确保处理确保的可转送区域转送的第3转送处理。由此,能够使发音几乎结束的波形数据或发音音量变小的波形数据消音,开始新的波形数据的发音,能够尽可能降低放弃发音的可能性。

[0176] 以上,对本发明的具体的实施方式进行了说明,但本发明并不限定于上述的实施方式,在不脱离本发明的主旨的范围中能够进行各种各样的变更。对于本领域技术人员,显然能够不脱离本发明的主旨或范围而对本发明进行各种各样的变更及变形。因而,本发明

意味着包含权利要求书及其等价范围中的改变及变形。特别是,清楚地意味着可以将上述实施方式及其变形中的任意2个以上的任意一部分或全部组合而考虑为本发明的范围。

图1

图2

图3

图4

|            |             |          |          |     |          |     |             |          |          |     |           |

|------------|-------------|----------|----------|-----|----------|-----|-------------|----------|----------|-----|-----------|

| 波形号码       | w           | 0        | 1        | ... | 10       | ... | 31          | 32       | 33       | ... | 511       |

| 音色号码       | tonen[w]    | 0        | 0        | ... | 0        | ... | 0           | 1        | 1        | ... | 15        |

| 音色内波形号码    | twnl[w]     | 0(1A)    | 1(2A)    | ... | 10(5B)   | ... | 31<br>(不使用) | 0(1A)    | 1(1B)    | ... | 31(9C)    |

| 最低速率       | vmin[w]     | 0        | 61       | ... | 80       | ... | 0           | 0        | 51       | ... | 122       |

| 最大速率       | vmax[w]     | 60       | 127      | ... | 127      | ... | 0           | 50       | 100      | ... | 127       |

| 最低键号码      | kmin[w]     | 0        | 0        | ... | 100      | ... | 0           | 0        | 0        | ... | 96        |

| 最高键号码      | kmax[w]     | 40       | 40       | ... | 127      | ... | 0           | 20       | 20       | ... | 127       |

| 距波形区域开头的地址 | wave_ad[w]  | 0000000H | 0000A00H | ... | 00F2000H | ... | 00FA000H    | 00FA000H | 0103200H | ... | 98000000H |

| 波形尺寸       | wave_sz[w]  | 00BA00H  | 00C100H  | ... | 013800H  | ... | 000000H     | 009200H  | 01A000H  | ... | 02C500H   |

| 起始地址       | start_ad[w] | 000080H  | 000004H  | ... | 000243H  | ... | 000000H     | 000042H  | 000115H  | ... | 00115AH   |

| 循环地址       | loop_ad[w]  | 00040AH  | 00BB9EH  | ... | 0112A0H  | ... | 000000H     | 008720H  | 0114E5H  | ... | 024856H   |

| 结束地址       | end_ad[w]   | 0006BFH  | 00C0E5H  | ... | 011ED2H  | ... | 000000H     | 0091E8H  | 019AE0H  | ... | 02C4CEH   |

图5

| 缓存号码          | b      | 0        | 1        | ... | 255      |

|---------------|--------|----------|----------|-----|----------|

| 缓存状态          | ,      |          |          |     |          |

| 0...NULL      | vs[b]  | 1        | 2        | ... | 0        |

| 1...可转送       |        |          |          |     |          |

| 2...发音中循环前    |        |          |          |     |          |

| 3...发音中循环中    |        |          |          |     |          |

| 4...衰减中       |        |          |          |     |          |

| 5...环形缓存使用中   |        |          |          |     |          |

| 波形缓存起始地址 (绝对) | bsa[b] | 0000000H | 0023C0AH | ... | 0000000H |

| 波形缓存循环地址 (绝对) | bla[b] | 0000EF4H | 002824CH | ... | 0000000H |

| 波形缓存结束地址 (绝对) | bea[b] | 000109AH | 002AA40H | ... | 0000000H |

| 起始地址 (绝对)     | sa[b]  | 0000A04H | 008422AH | ... | 0000000H |

| 循环地址 (绝对)     | la[b]  | 00C59EH  | 0089E8CH | ... | 0000000H |

| 结束地址 (绝对)     | ea[b]  | 00CAE5H  | 008E2F4H | ... | 0000000H |

| 转送数据指针 (绝对)   | tp[b]  | 000C724H | 008897FH | ... | 0000000H |

| 写入指针 (缓存相对)   | wp[b]  | 004722H  | 01320AH  | ... | 000000H  |

| 读出指针 (缓存相对)   | rp[b]  | 00484EH  | 012D89H  | ... | 000000H  |

| 波形读出裕度        | rm[b]  | 0FFED4H  | 000481H  | ... | 000000H  |

图6

图7

图8

图9A

图9B

图10

图11

图12

图13A

图13B

图13C

图13D

图14

图15

图16

图17