(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6053474号

(P6053474)

(45) 発行日 平成28年12月27日(2016.12.27)

(24) 登録日 平成28年12月9日(2016.12.9)

(51) Int.Cl.

F 1

|              |           |      |       |      |

|--------------|-----------|------|-------|------|

| HO1L 21/336  | (2006.01) | HO1L | 29/78 | 371  |

| HO1L 29/788  | (2006.01) | HO1L | 27/10 | 434  |

| HO1L 29/792  | (2006.01) | HO1L | 27/10 | 381  |

| HO1L 21/8247 | (2006.01) | G11C | 17/00 | 621B |

| HO1L 27/115  | (2006.01) | G11C | 17/00 | 623A |

請求項の数 9 (全 23 頁) 最終頁に続く

(21) 出願番号

特願2012-259128 (P2012-259128)

(22) 出願日

平成24年11月27日(2012.11.27)

(65) 公開番号

特開2014-107406 (P2014-107406A)

(43) 公開日

平成26年6月9日(2014.6.9)

審査請求日

平成27年9月9日(2015.9.9)

前置審査

(73) 特許権者 511229547

株式会社フローディア

東京都小平市小川東町1丁目30番9号

(74) 代理人 100137800

弁理士 吉田 正義

(72) 発明者 谷口 泰弘

東京都小平市小川東町1丁目29番9号

株式会社フローディア内

(72) 発明者 奥山 幸祐

東京都小平市小川東町1丁目29番9号

株式会社フローディア内

審査官 加藤 俊哉

最終頁に続く

(54) 【発明の名称】不揮発性半導体記憶装置

(57) 【特許請求の範囲】

【請求項 1】

フローティングゲートを備えた単層ゲート構造のメモリトランジスタと、スイッチゲート電極を備えた単層ゲート構造のスイッチトランジスタとを有するメモリセルを備え、前記メモリセルは、

前記メモリトランジスタの一端のメモリセルトランジスター端側ソースドレイン領域にソース線が接続されるとともに、前記スイッチトランジスタの一端のスイッチトランジスター端側ソースドレイン領域にビット線が接続されており、前記メモリトランジスタの他端と前記スイッチトランジスタの他端とが他端側ソースドレイン領域を介して電気的に接続され、該メモリトランジスタおよび該スイッチトランジスタが直列に配置された構成を有し、

前記メモリトランジスタは、

前記フローティングゲートの下部領域と前記他端側ソースドレイン領域との間に、前記フローティングゲートの下部領域と前記メモリセルトランジスター端側ソースドレイン領域との間の抵抗値よりも高い抵抗値を有する高抵抗領域を備え、

前記メモリトランジスタには、前記フローティングゲートの下部領域の両側にエクステンション領域が形成されており、前記高抵抗領域として、前記一端側のエクステンション領域よりも不純物濃度が低い低濃度不純物エクステンション領域が形成されている

ことを特徴とする不揮発性半導体記憶装置。

【請求項 2】

10

20

前記フローティングゲートの下部の活性領域上面には、

前記エクステンション領域と接してデブリート型チャネル領域が形成されている

ことを特徴する請求項1記載の不揮発性半導体記憶装置。

**【請求項3】**

前記フローティングゲートの電位を調整するカップリングキャパシタを備え、

前記フローティングゲートは、前記メモリトランジスタおよび前記カップリングキャパシタに延在している

ことを特徴とする請求項1記載の不揮発性半導体記憶装置。

**【請求項4】**

前記スイッチトランジスタは、

前記スイッチゲート電極の下部に形成されたゲート酸化膜の膜厚が、前記メモリトランジスタの前記フローティングゲートの下部に形成されたゲート酸化膜の膜厚よりも薄く形成されている

ことを特徴とする請求項1～3のうちいずれか1項記載の不揮発性半導体記憶装置。

**【請求項5】**

前記フローティングゲートから電荷を引き抜くイレーストランジスタを備えており、

前記フローティングゲートは、前記メモリトランジスタおよび前記イレーストランジスタに延在している

ことを特徴とする請求項1～4のうちいずれか1項記載の不揮発性半導体記憶装置。

**【請求項6】**

前記フローティングゲートは、前記メモリトランジスタとの対向領域がN型で形成され、前記イレーストランジスタとの対向領域がP型で形成されている

ことを特徴とする請求項5記載の不揮発性半導体記憶装置。

**【請求項7】**

前記メモリセルが行列状に配置されており、

前記ソース線は、前記メモリセル毎に設けた前記メモリトランジスタに共通の電圧を一律に印加する

ことを特徴とする請求項1～6のうちいずれか1項記載の不揮発性半導体記憶装置。

**【請求項8】**

S R A Mセルと、一の前記メモリセルおよび他の前記メモリセルとで1ビットを構成し

、

前記一のメモリセルに接続された一のビット線がS R A Mセルの一のストレージノードに接続され、前記他のメモリセルに接続された他のビット線が前記S R A Mセルの前記一のストレージノードと相補的な他のストレージノードに接続されている、

ことを特徴とする請求項1～6のうちいずれか1項記載の不揮発性半導体記憶装置。

**【請求項9】**

前記メモリセル毎に設けられた各前記スイッチトランジスタには個別にゲート線が接続されており、各前記スイッチトランジスタが独立にオンオフ制御される

ことを特徴とする請求項8記載の不揮発性半導体記憶装置。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、不揮発性半導体記憶装置に関し、例えばデータを書き込む際にソースサイド注入(S S I : Source Side Injection)によりフローティングゲートに電荷を注入する不揮発性半導体記憶装置に適用して好適なものである。

**【背景技術】**

**【0002】**

近年、標準的なCMOS(Complementary Metal Oxide Semiconductor)プロセスにより容易に製造できる不揮発性半導体記憶装置の研究が盛んに行われている。このような不揮発性半導体記憶装置は、データを書き込む際の書き込み手法により大きく分類することがで

10

20

30

40

50

き、主なものとして、FN (Fowler Nordheim) トンネル注入と、チャネルホットエレクトロン注入と、ソースサイド注入とが知られている。

### 【0003】

これらの書き込み手法の中でソースサイド注入は、チャネルのソース領域でホットキャリアを得てこれをフローティングゲートに注入する方式であり、例えば特許文献1に示すものが知られている。このようなソースサイド注入によるデータの書き込みは、比較的低電圧で行うことができ、書き込み時における消費電力も低減できることが知られており、LSIにおいて混載によるメリットが期待されている。

### 【先行技術文献】

#### 【特許文献】

10

#### 【0004】

#### 【特許文献1】特公平7-60864号公報

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0005】

しかしながら、ソースサイド注入によってデータを書き込む不揮発性半導体記憶装置としては、特許文献1に示すように、ゲートとなるポリシリコンを重ねた2層ポリシリコン構造が一般的であり、例えば単層ポリシリコン構造でソースサイド注入によるデータ書き込みを行う不揮発性半導体記憶装置については未だ研究段階にある。

#### 【0006】

20

そこで、本発明は以上の点を考慮してなされたもので、単層ゲート構造でもソースサイド注入によってフローティングゲートに電荷を注入し得る不揮発性半導体記憶装置を提案することを目的とする。

#### 【課題を解決するための手段】

#### 【0007】

かかる課題を解決するため本発明の不揮発性半導体記憶装置は、フローティングゲートを備えた単層ゲート構造のメモリトランジスタと、スイッチゲート電極を備えた単層ゲート構造のスイッチトランジスタとを有するメモリセルを備え、前記メモリセルは、前記メモリトランジスタの一端のメモリセルトランジスター端側ソースドレイン領域にソース線が接続されているとともに、前記スイッチトランジスタの一端のスイッチトランジスター端側ソースドレイン領域にビット線が接続されており、前記メモリトランジスタの他端と前記スイッチトランジスタの他端とが他端側ソースドレイン領域を介して電気的に接続され、該メモリトランジスタおよび該スイッチトランジスタが直列に配置された構成を有し、前記メモリトランジスタは、前記フローティングゲートの下部領域と前記他端側ソースドレイン領域との間に、前記フローティングゲートの下部領域と前記メモリセルトランジスター端側ソースドレイン領域との間の抵抗値よりも高い抵抗値を有する高抵抗領域を備えることを特徴とする。

30

#### 【発明の効果】

#### 【0008】

40

本発明によれば、メモリトランジスタおよびスイッチトランジスタを全て単層ゲート構造としつつも、データ書き込み時、ソース線からメモリトランジスタの一端に高電圧が印加され、かつビット線からスイッチトランジスタの一端に低電圧が印加されてオン状態になることで、ソース線およびビット線間にあるメモリトランジスタの高抵抗領域で電圧降下を生じさせて強電界を発生させ、この強電界を利用してソースサイド注入によって電荷をフローティングゲートに注入し得る。

#### 【図面の簡単な説明】

#### 【0009】

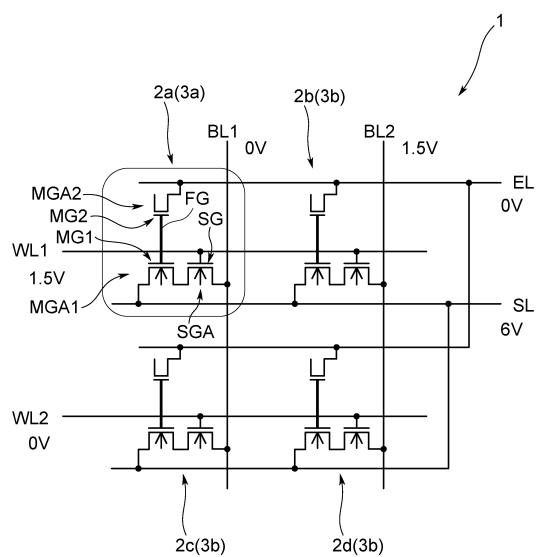

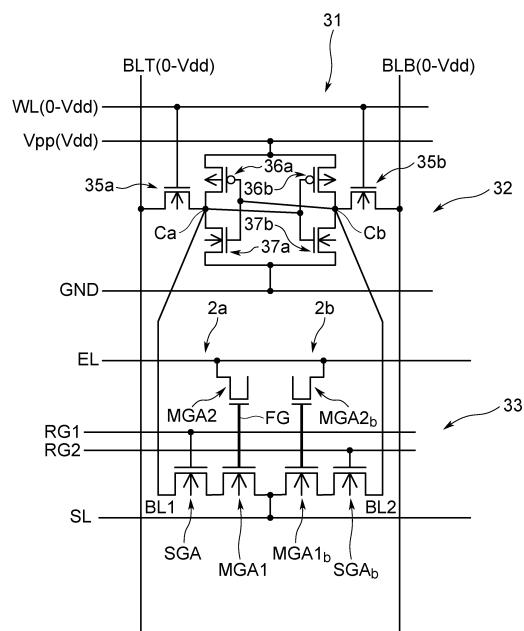

#### 【図1】本発明の不揮発性半導体記憶装置の回路構成を示す回路図である。

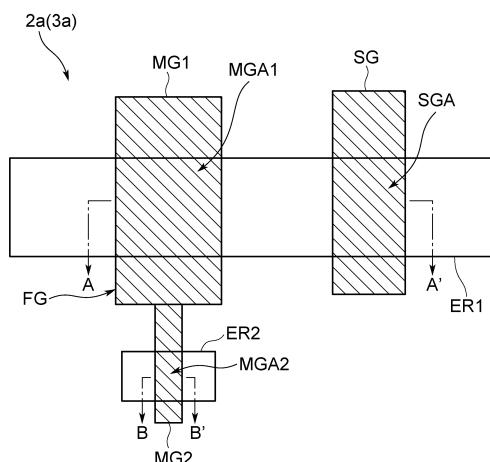

#### 【図2】図1に示したメモリセルの回路構成のレイアウトを示す概略図である。

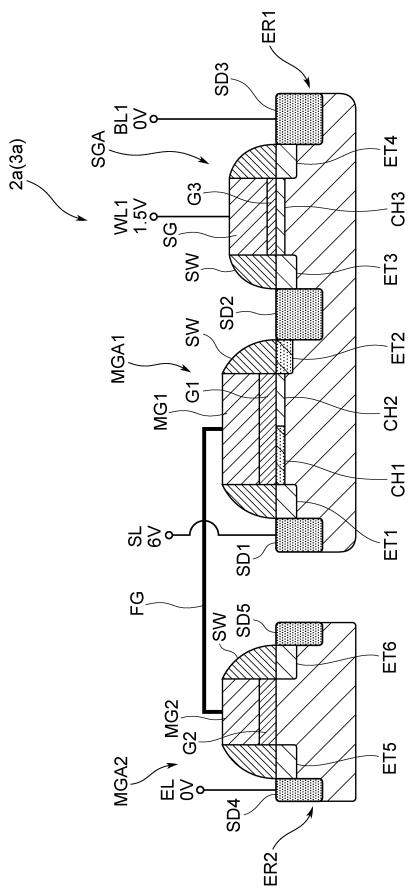

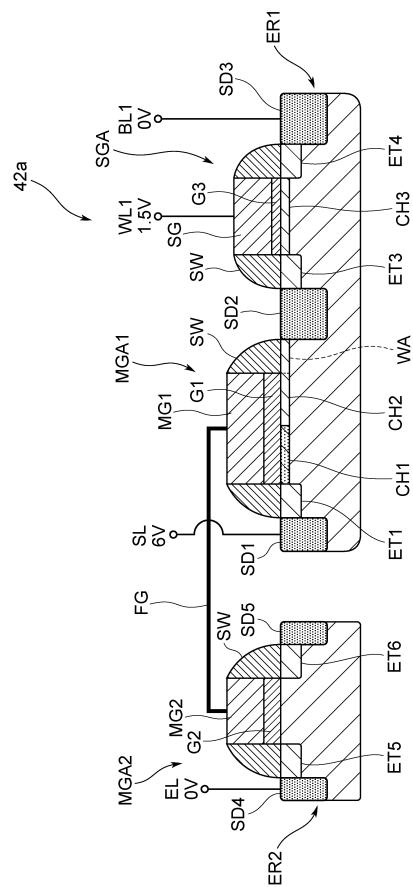

#### 【図3】図2に示すA-A'部分の断面構造、B-B'部分の断面構造を示す側断面図である。

50

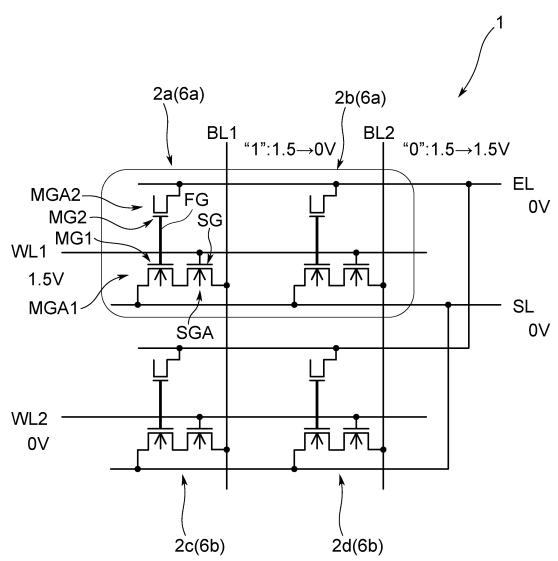

【図4】データの読み出し時における各部位の電圧値を示す回路図である。

【図5】データの消去時における各部位の電圧値を示す回路図である。

【図6】他の実施の形態による不揮発性半導体記憶装置の回路構成を示す回路図である。

【図7】図6に示したメモリセルの回路構成のレイアウトを示す概略図である。

【図8】図7に示すA-A'部分の断面構造、C-C'部分の断面構造を示す側断面図である。

【図9】SRAMセルを備えたメモリセルの回路構成を示す回路図である。

【図10】図9に示すメモリセルにおいて、データのプログラム時、消去時、データロード時、書き込み時、読み出し時、およびVthモニターロード時における各部位の電圧値を示す表である。

【図11】他の実施の形態による不揮発性半導体記憶装置の断面構造を示す側断面図である。 10

#### 【発明を実施するための形態】

##### 【0010】

以下図面に基づいて本発明の実施の形態を詳述する。

##### 【0011】

###### (1) 不揮発性半導体記憶装置の回路構成

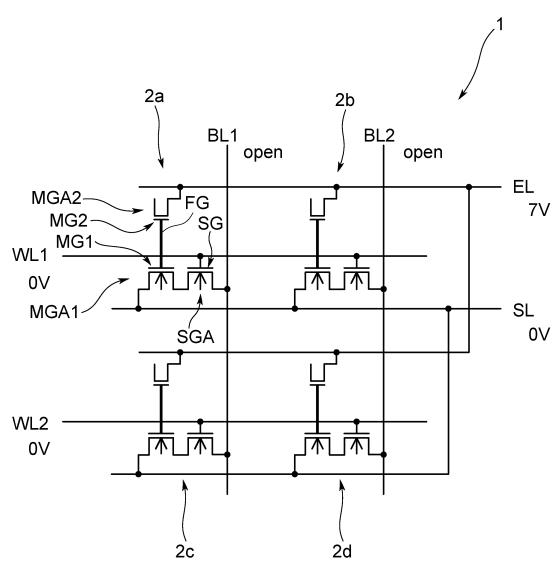

図1において、1は例えば4つのメモリセル2a,2b,2c,2dが2行2列に配置された不揮発性半導体記憶装置を示し、これらメモリセル2a,2b,2c,2dのうち例えば任意に選択されたメモリセル2aに対しソースサイド注入によってデータを書き込み得るようになされている。この場合、不揮発性半導体記憶装置1は、2本のビット線BL1,BL2が設けられるとともに、2本のワード線WL1,WL2が設けられており、ビット線BL1,BL2およびワード線WL1,WL2が交差する位置にメモリセル2a,2b,2c,2dが配置されている。 20

##### 【0012】

また、不揮発性半導体記憶装置1は、イレース線(消去線)ELがメモリセル2a,2b,2c,2dに接続されており、当該イレース線ELによって各メモリセル2a,2b,2c,2dに所定の電圧を一律に印加し得るようになされている。さらに、不揮発性半導体記憶装置1は、ソース線SLがメモリセル2a,2b,2c,2dに接続されており、当該ソース線SLによって各メモリセル2a,2b,2c,2dに所定の電圧を一律に印加し得るようになされている。

##### 【0013】

この実施の形態の場合、これらメモリセル2a,2b,2c,2dは全て同一構成を有していることから、説明の重複を避けるため、以下1つのメモリセル2aに着目して説明する。メモリセル2aは、N型MOSのメモリMOSトランジスタ(以下、メモリトランジスタと呼ぶ)MGA1と、P型MOSのイレース(消去)MOSトランジスタ(以下、イレーストランジスタと呼ぶ)MGA2と、N型MOSのスイッチMOSトランジスタ(以下、スイッチトランジスタと呼ぶ)SGAとを備えており、メモリトランジスタMGA1およびイレーストランジスタMGA2で1つのフローティングゲートFGを共有している。 30

##### 【0014】

フローティングゲートFGは、メモリトランジスタMGA1およびイレーストランジスタMGA2の各活性領域(後述する)に延在しており、メモリトランジスタMGA1のゲート電極MG1と、イレーストランジスタMGA2のイレースゲート電極MG2となり得る。また、メモリセル2aは、他のメモリセル2b,2c,2dにも接続されているソース線SLがメモリトランジスタMGA1の一端に接続されるとともに、同じく他のメモリセル2b,2c,2dにも接続されているイレース線ELがイレーストランジスタMGA2の一端に接続されている。 40

##### 【0015】

スイッチトランジスタSGAには、一方向に並ぶ他のメモリセル2cにも接続されたビット線BL1が一端に接続され、他方向に並ぶ他のメモリセル2bにも接続されたワード線WL1がスイッチゲート電極SGに接続されており、ビット線BL1およびワード線WL1の電圧差によりオンオフ動作し得るようになされている。また、スイッチトランジスタSGAは、他端がメモリトランジスタMGA1の他端と電気的に接続されており、メモリトランジスタMGA1と直列に配置されている。 50

## 【0016】

なお、イレーストランジスタMGA2の他端は後述する第2活性領域と短絡（ショート）している。また、図1では、メモリトランジスタMGA1のゲート電極MG1の面積が、イレーストランジスタMGA2のイレースゲート電極MG2の面積よりも大きく形成されており、メモリトランジスタMGA1のゲート電極MG1の面積を大きくした分だけ、メモリトランジスタMGA1からの電位がフローティングゲートFGへ伝わり易くなり、データを書き込む際、当該メモリトランジスタMGA1にて大容量の電流を発生させ、活性領域からフローティングゲートFGへ多くの電荷を注入し得るようになされている。

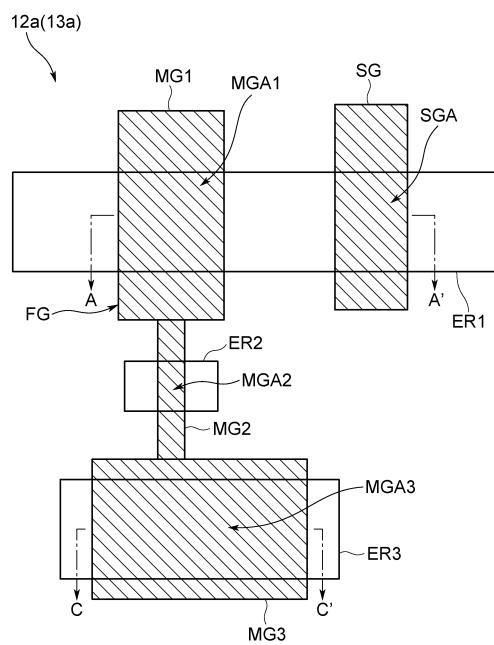

## 【0017】

ここで、図2は、図1に示したメモリセル2aの回路構成を実現するレイアウトの一例を示す概略図である。この場合、メモリセル2aには、例えばP型の第1活性領域ER1が形成されており、フローティングゲートFGを構成するメモリトランジスタMGA1のゲート電極MG1と、スイッチトランジスタSGAのスイッチゲート電極SGとが第1活性領域ER1に配置され、これらメモリトランジスタMGA1およびスイッチトランジスタSGAが直列に配置されている。また、メモリセル2aには、例えばN型の第2活性領域ER2が形成されており、メモリトランジスタMGA1のゲート電極MG1に接続されたイレーストランジスタMGA2のイレースゲート電極MG2が第2活性領域ER2に配置されている。

10

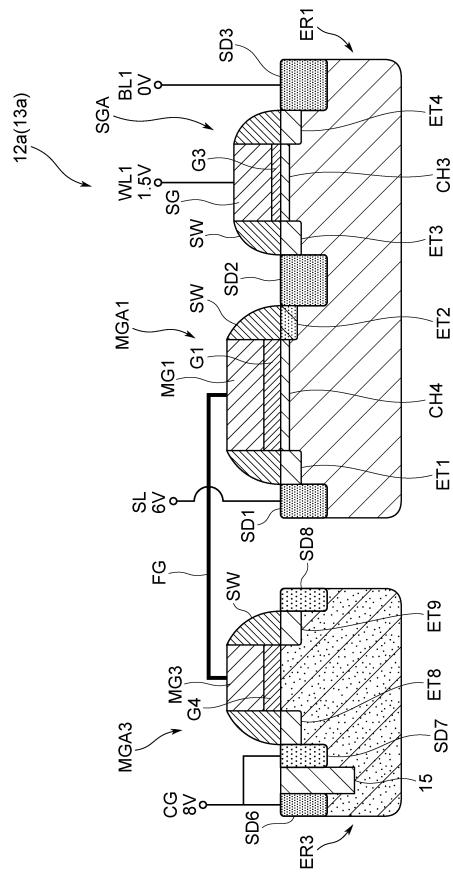

## 【0018】

ここで、図3は、図2のA-A'部分（図3中、右側）およびB-B'部分（図3中、左側）の側断面構成を示す断面図である。スイッチトランジスタSGAは、第1活性領域ER1にソースドレイン領域SD2, SD3が間隔を空けて形成された構成を有し、このうち一端となるソースドレイン領域SD3にピット線BL1が接続されている。また、ソースドレイン領域SD2, SD3間の第1活性領域ER1上面には、これらソースドレイン領域SD2, SD3の側面と接するようにエクステンション領域ET3, ET4が形成され、エクステンション領域ET3, ET4間にチャネル領域CH3が形成されている。スイッチトランジスタSGAは、エクステンション領域ET3, ET4間のチャネル領域上にゲート酸化膜G3を介してスイッチゲート電極SGを有しており、当該スイッチゲート電極SGにワード線WL1が接続された構成を有する。また、各エクステンション領域ET3, ET4の上面には、スイッチゲート電極SGの側面を覆うサイドウォールSWが形成されている。

20

## 【0019】

一方、メモリトランジスタMGA1は、ソースドレイン領域SD2をスイッチトランジスタSGAと共有しており、隣接するスイッチトランジスタSGAと直列に配置されている。また、メモリトランジスタMGA1は、このソースドレイン領域SD2と所定間隔を空けて第1活性領域ER1に形成されたソースドレイン領域SD1を有し、この一端のソースドレイン領域SD1にソース線SLが接続された構成を有しており、当該ソース線SLを介してソースドレイン領域SD1に書き込み電圧等が印加され得る。

30

## 【0020】

これに加えて、このメモリトランジスタMGA1には、一端のソースドレイン領域SD1の側面に接したエクステンション領域ET1と、他端のソースドレイン領域SD2の側面に接したエクステンション領域（以下、低濃度不純物エクステンション領域と呼ぶ）ET2とが第1活性領域ER1の上面に形成されている。また、メモリトランジスタMGA1には、エクステンション領域ET1および低濃度不純物エクステンション領域ET2間の第1活性領域ER1上面にゲート酸化膜G1を介してフローティングゲートFGとなるゲート電極MG1が形成されており、エクステンション領域ET1および低濃度不純物エクステンション領域ET2の各上面にゲート電極MG1の両側面を覆うサイドウォールSWが形成されている。

40

## 【0021】

ここで本発明は、メモリトランジスタMGA1において、スイッチトランジスタSGA側のサイドウォール下部領域（フローティングゲートFGの下部領域と、他端側のソースドレイン領域SD2との間の領域）に形成された低濃度不純物エクステンション領域ET2が、フローティングゲートFGの下部領域および一端側のソースドレイン領域SD1間にあるエクステンシ

50

ヨン領域ET1よりも不純物濃度が低濃度に選定され、低濃度不純物エクステンション領域ET2がソース線SL側のエクステンション領域ET1の抵抗値よりも高い抵抗値を有している点に特徴を有する。この実施の形態の場合、高抵抗領域としての低濃度不純物エクステンション領域ET2は、不純物ドープ量が $1E18/cm^3$ 以下であることが好ましい。

#### 【0022】

このような構成を有するメモリトランジスタMGA1は、後述するデータ書き込み時に、ソース線SLおよびビット線BL1間で大きな電位差が生じたとき、抵抗値を高くした低濃度不純物エクステンション領域ET2で最も大きな電位降下が生じ得るようになされている。

#### 【0023】

また、これに加えてこの実施の形態の場合、エクステンション領域ET1および低濃度不純物エクステンション領域ET2間の第1活性領域ER1上面には、エクステンション領域ET1の側面と接するデブリート型チャネル領域CH1と、このデブリート型チャネル領域CH1および低濃度不純物エクステンション領域ET2に両端が接するエンハンスメント型のチャネル領域CH2とが形成されている点にも特徴を有する。デブリート型チャネル領域CH1は、例えはヒ素やリン等の不純物がドープされてデブリート状態となっている。一方、このデブリート型チャネル領域CH1と隣接するチャネル領域CH2はボロン等の不純物がドープされてエンハンスメント状態になっている。このような構成を有するメモリトランジスタMGA1は、後述するデータ書き込み時に、ソース線SLからソースドレイン領域SD1に書き込み電圧が印加されたとき、デブリート型チャネル領域CH1およびゲート電極MG1の電圧が相乗的に上昇してゆき、最終的に低濃度不純物エクステンション領域ET2の末端に印加される電圧値をソース線SLに印加された電圧値まで上昇させ得るようになされている（詳細については後述する）。

10

#### 【0024】

因みに、イレーストランジスタMGA2は、図3に示すように、第1活性領域ER1とは別に形成された第2活性領域ER2にソースドレイン領域SD4, SD5が間隔を空けて形成された構成を有し、このうち少なくとも一端側のソースドレイン領域SD4にイレース線ELが接続されている。ソースドレイン領域SD4, SD5間の第2活性領域ER2上面には、当該ソースドレイン領域SD4の側面と接するようにエクステンション領域ET5が形成されるとともに、他端のソースドレイン領域SD5にも側面と接するようにエクステンション領域ET6が形成されている。また、イレーストランジスタMGA2には、エクステンション領域ET5, ET6間のチャネル領域上にゲート酸化膜G2を介してフローティングゲートFGとなるイレースゲート電極MG2が形成されており、当該イレースゲート電極MG2がメモリトランジスタMGA1のゲート電極MG1と接続されている。なお、これらエクステンション領域ET5, ET6の上面には、イレースゲート電極MG2の両側面を覆うようにしてサイドウォールSWが形成されている。

20

30

#### 【0025】

##### (2) データの書き込み動作

次に本発明の不揮発性半導体記憶装置1においてデータの書き込み動作について以下説明する。図1は、複数のメモリセル2a, 2b, 2c, 2dのうち、1行1列目のメモリセル2aにのみデータを書き込む際の各部位の電圧値を示している。なお、ここでは、データの書き込みが行われるメモリセル2aを選択メモリセル3aと呼び、データの書き込みを行わないメモリセル2b, 2c, 2dを非選択メモリセル3bと呼ぶ。

40

#### 【0026】

この場合、図1に示すように、不揮発性半導体記憶装置1は、データ書き込み時、イレース線ELに0[V]の低電圧が印加されるとともに、ソース線SLに高電圧の6[V]の書き込み電圧が印加され得る。これにより不揮発性半導体記憶装置1は、メモリセル2a, 2b, 2c, 2dの各イレーストランジスタMGA2にイレース線ELから0[V]の電圧が一律に印加されるとともに、メモリセル2a, 2b, 2c, 2dの各メモリトランジスタMGA1にソース線SLから6[V]の書き込み電圧が一律に印加され得る。

#### 【0027】

一方、選択メモリセル3aのスイッチトランジスタSGAには、ワード線WL1からスイッチゲ

50

ート電極SGに1.5[V]が印加されるとともに、ビット線BL1から一端に0[V]の書き込み電圧が印加されてオン状態となり得る。図3に示すように、スイッチトランジスタSGAは、オン状態になると、メモリトランジスタMGA1と共有しているソースドレイン領域SD2がビット線BL1と同じ0[V]となる。この際、スイッチトランジスタSGAと直列に配置されたメモリトランジスタMGA1では、ソース線SLから一端のソースドレイン領域SD1に6[V]の書き込み電圧が印加され、チャネル電位が上昇してゆき、チャネル領域CH2が書き込み電圧まで上昇し得る。

#### 【0028】

実際に、この実施の形態の場合、メモリトランジスタMGA1は、エクステンション領域ET1の側面と接するようにデブリート型チャネル領域CH1が形成されていることから、データ書き込み時、デブリート型チャネル領域CH1においてデブリート状態の閾値電圧V<sub>th</sub>(V<sub>th</sub><0)までチャネル電圧が上昇し得るようになされている。例えばフローティングゲートFGとなるゲート電極MG1に電荷がなく、デブリート型チャネル領域CH1の濃度が閾値電圧V<sub>th</sub>で2[V]とした場合には、データ書き込み時、ソース線SLに6[V]が印加されると、先ずデブリート型チャネル領域CH1が2[V]まで上昇し得る。そのときゲート電極MG1の電位は、容量結合によりデブリート型チャネル領域CH1の電位に比例して上昇する。

#### 【0029】

例えば、ゲート電極MG1の全容量に対する容量比(ゲート電極MG1およびデブリート型チャネル領域CH1間の容量比)が0.5とした場合、ゲート電極MG1は、デブリート型チャネル領域CH1が電圧2[V]まで上昇することで、その電位が0[V]から1[V]に上昇する。なお、この際、容量比が大きいほどゲート電極MG1の電圧上昇の効率が良くなることからメモリトランジスタMGA1のゲート電極MG1の面積を、イレーストランジスタMGA2のイレースゲート電極MG2よりも大きく形成することが望ましい。

#### 【0030】

次いで、メモリトランジスタMGA1では、ゲート電極MG1の電位が上昇して1[V]となると、デブリート型チャネル領域CH1に印加できる許容電位も上昇し、デブリート型チャネル領域CH1の電位が更に1[V]上昇して3[V]となる。これによりメモリトランジスタMGA1のゲート電極MG1の電位は、容量結合によりデブリート型チャネル領域CH1の電位に比例して変化し、デブリート型チャネル領域CH1が電圧3[V]となることで、電位が1[V]から1.5[V]に上昇する。

#### 【0031】

メモリトランジスタMGA1では、デブリート型チャネル領域CH1がゲート電極MG1の電位に相乗して上昇してゆき、更にチャネル領域CH2もオン状態となればその電位も容量結合に寄与し、ゲート電極MG1の電位が更に上昇して、最終的にはチャネル領域CH2の電位がソース線SLに印加された6[V]に近い値にまで到達し得る。

#### 【0032】

これにより低濃度不純物エクステンション領域ET2では、チャネル領域CH2と接する端部が書き込み電圧である6[V]となるとともに、ソースドレイン領域SD2と接する端部が0[V]となり、両端に6[V]の高い電圧差が生じて強電界が発生する。これによりメモリトランジスタMGA1では、低濃度不純物エクステンション領域ET2で発生した強電界により低濃度不純物エクステンション領域ET2内の電荷を加速させ、当該電荷から発生した2次電荷の一部をフローティングゲートFGとなるゲート電極MG1に注入させ得る。その結果、選択メモリセル3aでは、フローティングゲートFG中に電荷が蓄積して、データが書き込まれた状態となり得る。

#### 【0033】

このように選択メモリセル3aでは、メモリトランジスタMGA1のゲート電極MG1や、イレーストランジスタMGA2のイレースゲート電極MG2、スイッチトランジスタSGAのスイッチゲート電極SGを全て単層で設けた単層ゲート構造としつつ、データ書き込み時、低濃度不純物エクステンション領域ET2にて強電界を発生させることで、この強電界によって電荷をフローティングゲートFGに注入し得、単層ゲート構造でソースサイド注入によるデータ書

10

20

30

40

50

き込みを実現し得る。

**【0034】**

また、低濃度不純物エクステンション領域ET2では、不純物濃度を低濃度として高い抵抗値を有しており、データ書き込み時、大きな電圧降下が生じるもの、隣接するソースドレイン領域SD2を0[V]近くまで抑えることができ、スイッチトランジスタSGAに高電圧の書き込み電圧が印加されることを防止し得るようになされている。かくして、スイッチトランジスタSGAは、ゲート酸化膜G3の膜厚を、メモリトランジスタMGA1のゲート酸化膜G1（膜厚7[nm]程度）のように厚くする必要がなく、例えば膜厚を3~4[nm]と薄く形成し得、不揮発性メモリで一般的に用いられているゲート酸化膜が薄いコアMOSをそのまま用いることができる。

10

**【0035】**

因みにこのとき、図1に示したように、不揮発性半導体記憶装置1では、非選択メモリセル3bだけが接続されているビット線BL2に1.5[V]の書き込み禁止電圧が印加されるとともに、非選択メモリセル3bだけが接続されているワード線WL2に0[V]の電圧が印加される。これによりこのビット線BL2に接続された非選択メモリセル3b（メモリセル2b,2d）では、スイッチトランジスタSGAのスイッチゲート電極SGにワード線WL1,WL2から1.5[V]または0[V]が印加され、ビット線BL2からスイッチトランジスタSGAの一端に1.5[V]が印加されることで当該スイッチトランジスタSGAがオフ状態となり、メモリトランジスタMGA1の低濃度不純物エクステンション領域ET2において電荷が加速されることはなく、電荷がフローティングゲートFGに注入され得ない。

20

**【0036】**

また、0[V]の書き込み電圧が印加されるビット線BL1に接続された非選択メモリセル3b（メモリセル2c）でも、スイッチトランジスタSGAのスイッチゲート電極SGにワード線WL2から0[V]が印加されることからスイッチトランジスタSGAがオフ状態となり、メモリトランジスタMGA1の低濃度不純物エクステンション領域ET2において電荷が加速されることはなく、電荷がフローティングゲートFGに注入され得ない。

30

**【0037】**

かくして、この不揮発性半導体記憶装置1では、非選択メモリセル3bのスイッチトランジスタSGAをオフさせることで非選択メモリセル3bのフローティングゲートFGに電荷が注入されることはなく、所望の選択メモリセル3aのフローティングゲートFGにだけソースサイド注入により電荷を注入してデータを書き込むことができる。

**【0038】**

ここで、上述した実施の形態においては、メモリトランジスタMGA1のチャネル層に、デブリート型チャネル領域CH1の他、エンハンスマント型のチャネル領域CH2をも形成するようにした場合について述べたが、本発明はこれに限らず、例えばメモリトランジスタMGA1のチャネル層全てをデブリート型チャネル領域CH1で形成するようにしてもよい。但し、デブリート型チャネル領域CH1をチャネル層全域に形成した場合には、短チャネル効果を考慮して、ゲート電極MG1のゲート長を長くする必要がある。

**【0039】**

またチャネル全体をデブリート型にする場合においても、エクステンション領域ET1に近い側のチャネル濃度と、低濃度不純物エクステンション領域ET2に近い側のチャネル濃度を変更してもよい。

40

**【0040】**

なお、デブリート型チャネル領域CH1とエンハンスマント型のチャネル領域CH2とを形成する場合には、デブリート型チャネル領域CH1をチャネル領域CH2よりもチャネル長方向に長く選定することが好ましく、例えばゲート全長においてデブリート型チャネル領域CH1：チャネル領域CH2が、X：1（X > 1）が望ましい。このようにデブリート型チャネル領域CH1をチャネル領域CH2よりもチャネル長方向に長く選定した場合には、書き込み動作時のフローティング電位がより上昇するため、チャネル領域でのソース電位の下降が低減され、低濃度不純物エクステンション領域ET2で発生する電界をより高めることによりイン

50

ジェクションの効率をより高めることができる。

#### 【0041】

##### (3) データの読み出し動作

次に、不揮発性半導体記憶装置1において、データを読み出す際の電圧印加について以下説明する。図1との対応部分に同一符号を付して示す図4は、メモリセル2a,2b,2c,2dのうち、1行目のメモリセル2a,2bのデータを読み出す際の各部位の電圧値を示している。なお、ここでは、データを読み出すメモリセル2a,2bを読み出しメモリセル6aと呼び、データを読み出さないメモリセル2c,2dを非読み出しメモリセル6bと呼ぶ。また、この場合、メモリセル2a,2b,2c,2dのうちメモリセル2bにだけデータが書き込まれ、その他のメモリセル2a,2c,2dにはデータが書き込まれていないものとする。さらに、ここでは、フローティングゲートFGに電荷が蓄積された状態（データが書き込まれているとき）を例えば「0」とし、フローティングゲートFGに電荷が蓄積されてない状態（データが書き込まれていないとき）を「1」とする。

#### 【0042】

この場合、不揮発性半導体記憶装置1は、読み出しメモリセル6aに接続されたビット線BL1,BL2に、例えば1.5[V]の読み出し電圧を印加してプリチャージするとともに、読み出しメモリセル6aに接続されたワード線WL1に1.5[V]を印加し、スイッチトランジスタSGAをオン状態とし、これらビット線BL1,BL2の読み出し電圧の変化を基にデータの書き込み有無を判断し得る。

#### 【0043】

例えれば、フローティングゲートFGに電荷が蓄積された（データが書き込まれた）読み出しメモリセル6a（メモリセル2b）では、メモリトランジスタMGA1がオフ動作し、ビット線BL2での読み出し電圧が1.5[V]のままとなる。一方、フローティングゲートFGに電荷が蓄積されていない（データが書き込まれていない）他方の読み出しメモリセル6a（メモリセル2a）では、メモリトランジスタMGA1がオン動作し、これによりビット線BL1の読み出し電圧が変化し1.5[V]よりも低い電圧値（例えば0[V]）になる。不揮発性半導体記憶装置1は、ビット線BL1,BL2の読み出し電圧の変化を検知し、読み出し電圧が変化しない1.5[V]のビット線BL2を「0」とし、読み出し電圧が変化した他方のビット線BL1を「1」とし、読み出し情報を確定し得る。

#### 【0044】

##### (4) データの消去動作

次に、この不揮発性半導体記憶装置1において、メモリセル2a,2b,2c,2dのデータを消去する際の電圧印加について以下説明する。不揮発性半導体記憶装置1におけるデータの消去動作としては、例えればバンド間トンネル電流に起因するホール注入を用いた消去方法や、フローティングゲートFGとなるメモリトランジスタMGA1のゲート電極MG1エッジおよびソースドレイン領域SD1,SD2（図3）間のエッジトンネル放出を用いた消去方法、チャネル層全面を用いたFNトンネル放出を用いた消去方法等、フローティングゲートFGから電子を放出させるか、或いはフローティングゲートFGに正孔（ホール）を注入する技術であれば種々の消去方法を用いても良い。

#### 【0045】

図1との対応部分に同一符号を付して示す図5は、このうちバンド間トンネル電流に起因するホール注入を用いた場合について各部位の電圧値を示しており、この場合、イレーストランジスタMGA2を用い、イレース線ELに正電圧の消去電圧7[V]を印加し、ソース線SLに低電圧の0[V]を印加し、さらにビット線BL1,BL2をオープンとする。

#### 【0046】

このように不揮発性半導体記憶装置1では、イレース線ELを介してメモリセル2a,2b,2c,2dの各イレーストランジスタMGA2にマット一括で消去電圧を印加し、例えればフローティングゲートに電荷が蓄積されたメモリセル2bにおいて、イレーストランジスタMGA2のチャネル層からフローティングゲートFG中にホールを注入し、マット一括処理でメモリセル2a,2b,2c,2dのデータ消去を行い得る。

10

20

30

40

50

## 【0047】

なお、この実施の形態の場合、メモリトランジスタMGA1のゲート電極MG1、およびイレーストランジスタMGA2のイレースゲート電極MG2は、通常、ポリシリコンにより形成しているが、本発明はこれに限らず、例えばメモリトランジスタMGA1のゲート電極MG1にリン等の不純物をドープしてN型のゲート電極MG1とし、その一方、バンド間トンネルを起こすイレーストランジスタMGA2のイレースゲート電極MG2にボロン等の不純物をドープしてP型のイレースゲート電極MG2としてもよい。

## 【0048】

この場合、N型のゲート電極MG1と、P型のイレースゲート電極MG2とでは、仕事関数の差が1[V]以上あることから、フローティングゲートFGにおいてN型のゲート電極MG1とP型のイレースゲート電極MG2との間で約1[V]の電位降下を生むことができ、N型のゲート電極だけでフローティングゲートを構成する場合に比して、イレーストランジスタMGA2にてバンド間トンネル電流の発生効率が向上し、フローティングゲートFGに対するホール注入を行い易くなる。10

## 【0049】

## (5)動作及び効果

以上の構成において、メモリセル2aでは、フローティングゲートFGを備えた単層ゲート構造のメモリトランジスタMGA1と、スイッチゲート電極SGを備えた単層ゲート構造のスイッチトランジスタSGAとを有し、メモリトランジスタMGA1の一端にソース線SLが接続され、スイッチトランジスタSGAの一端にビット線BL1が接続されており、メモリトランジスタMGA1の他端と、スイッチトランジスタの他端とでソースドレイン領域SD2を共有させ、当該メモリトランジスタMGA1と当該スイッチトランジスタSGAとを直列に配置させるようにした。また、メモリトランジスタMGA1では、一端のソースドレイン領域SD1の側面にエクステンション領域ET1を形成し、スイッチトランジスタSGAと電気的に接続した他端側のソースドレイン領域SD2の側面に低濃度不純物エクステンション領域ET2を形成し、この低濃度不純物エクステンション領域ET2の不純物濃度をエクステンション領域ET1よりも低くして、低濃度不純物エクステンション領域ET2の抵抗値を高くした。20

## 【0050】

これにより選択メモリセル3aでは、データの書き込み時、ソース線SLからメモリトランジスタMGA1の一端に6[V]の書き込み電圧が印加され、かつビット線BL1からスイッチトランジスタSGAの一端に0[V]が印加されてオン状態になることで、メモリトランジスタMGA1において、当該スイッチトランジスタSGAと隣接する側の低濃度不純物エクステンション領域ET2で6[V]の電圧降下を生じさせて強電界を発生させ、この強電界により電荷をフローティングゲートFGに注入する、いわゆるソースサイド注入によってデータを書き込むことができる。30

## 【0051】

特にこの実施の形態の場合、メモリトランジスタMGA1は、エクステンション領域ET1および低濃度不純物エクステンション領域ET2間にデブリート型チャネル領域CH1が形成されており、データの書き込み時、一端に6[V]の書き込み電圧を印加されると、フローティングゲートFGとなるゲート電極MG1の電圧と、デブリート型チャネル領域CH1の電圧とが相乗的に上昇してゆき、最終的に他端側の低濃度不純物エクステンション領域ET2に対し、ソース線SLに印加された書き込み電圧と同じ6[V]を印加することができ、低濃度不純物エクステンション領域ET2にてソースサイド注入に必要な高い電圧降下を発生させることができる。40

## 【0052】

このようにしてメモリセル2aでは、低濃度不純物エクステンション領域ET2だけに高い電圧降下が生じ、メモリトランジスタMGA1に隣接したスイッチトランジスタSGAを低電圧に抑えることができ、かくしてスイッチトランジスタSGAのゲート酸化膜G3を膜厚3~4[nm]程度に薄くし得、ゲート酸化膜の薄い一般的なコアMOSの構成をそのまま用いることができる。50

## 【 0 0 5 3 】

また、この不揮発性半導体記憶装置1では、データの書き込み時、ビット線BL1,BL2およびワード線WL1,WL2にそれぞれ印加される電圧を1.5[V]以下に抑えることができるので、これらビット線BL1,BL2およびワード線WL1,WL2を制御する行列選択回路(図示せず)を、低電圧を前提としたコアMOS(1.5V MOS)で設計することができ、またスイッチトランジスタSGAのゲート酸化膜G3も薄くできる分、高速動作が図れ、回路面積も小さくし得る。

## 【 0 0 5 4 】

以上の構成によれば、メモリセル2aでは、メモリトランジスタMGA1およびスイッチトランジスタSGAを全て単層ゲート構造としつつも、データ書き込み時、ソース線SLからメモリトランジスタMGA1の一端に高電圧が印加され、かつビット線BL1からスイッチトランジスタSGAの一端に低電圧が印加されてオン状態になることで、ソース線SLおよびビット線B L1間にあるメモリトランジスタMGA1の低濃度不純物エクステンション領域ET2で電圧降下を生じさせて強電界を発生させ、この強電界を利用してソースサイド注入によって電荷をフローティングゲートFGに注入し得る。10

## 【 0 0 5 5 】

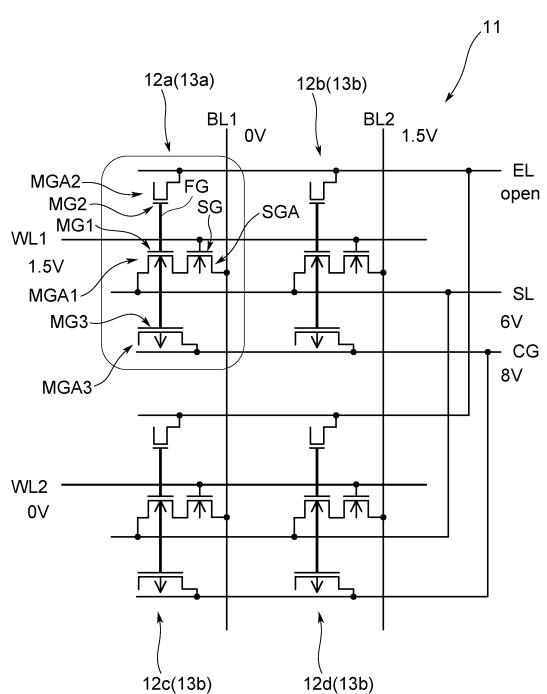

## ( 6 ) 他の実施の形態

なお、上述した実施の形態においては、メモリトランジスタMGA1のチャネル層にデブリート型チャネル領域CH1を形成し、フローティングゲートFGとデブリート型チャネル領域CH1との相乗効果でチャネル層の電圧を次第に上昇させてゆく場合について述べたが、本発明はこれに限らず、図1との対応部分に同一符号を付して示す図6のように、フローティングゲートFGが延在するカップリングキャパシタMGA3を設け、カップリングキャパシタMGA3を高電位にすることによってフローティングゲートFGの電位を上昇させ、これによりメモリトランジスタMGA1のチャネル層をオンさせるようにしても良い。この場合、メモリトランジスタMGA1のチャネル層には、図3に示すようなデブリート型チャネル領域CH1を形成することなく、単なるエンハンスマント型のチャネル領域CH4(図8にて後述する)のみとしても、カップリングキャパシタMGA3からの高電位によりメモリトランジスタMGA1のチャネル領域CH4をオン状態にし得る。20

## 【 0 0 5 6 】

実際に、このような構成を有する不揮発性半導体記憶装置11は、図6に示すように、カップリングゲート線CGが各メモリセル12a,12b,12c,12dのカップリングキャパシタMGA3の一端に接続されており、当該カップリングゲート線CGによって各カップリングキャパシタMGA3に所定の電圧が一律に印加され得る。ここで、図2との対応部分に同一符号を付して示す図7は、図6に示したメモリセル12aの回路構成を実現するレイアウトの一例を示す概略図である。この場合、メモリセル12aには、N型の第3活性領域ER3が形成されており、カップリングキャパシタMGA3のカップリングゲート電極MG3が第3活性領域ER3に形成されているとともに、当該カップリングゲート電極MG3がイレーストランジスタMGA2のイレースゲート電極MG2に連接され、ゲート電極MG1、イレースゲート電極MG2、およびカップリングゲート電極MG3によりフローティングゲートFGが形成されている。30

## 【 0 0 5 7 】

図3との対応部分に同一符号を付して示す図8は、図7のA-A'部分(図8中、右側)およびC-C'部分(図8中、左側)の側断面構成を示す断面図である。但し、この図8は、図7の各部位の面積に合わせ各部位を表記しておらず(例えば、カップリングゲート電極MG3はゲート電極MG1よりも大きいが、図8では小さく表記されている)、あくまで各部位の側断面構成を概略的に示したものである。40

## 【 0 0 5 8 】

図8に示すように、この場合、メモリトランジスタMGA1には、上述した実施の形態と異なり、エクステンション領域ET1および低濃度不純物エクステンション領域ET2間に、デブリート型チャネル領域CH1(図3)が形成されておらず、チャネル層が全てエンハンスマント型のチャネル領域CH4のみで形成されている。なお、カップリングキャパシタMGA3は50

、例えばN型の第3活性領域ER3にP型のソースドレイン領域SD7, SD8が間隔を空けて形成され、一端のソースドレイン領域SD7にカップリングゲート線CGが接続されている。なお、このカップリングゲート線CGは、素子分離層15を介して形成された隣接する他のカップリングキャパシタ(図示せず)のソースドレイン領域SD7にも接続されている。因みに、SD6は、N型であり、ウェルへの給電領域である。

#### 【0059】

なお、カップリングキャパシタMGA3は、ソースドレイン領域SD7, SD8間の第3活性領域ER3上面に、一端のソースドレイン領域SD7の側面と接したエクステンション領域ET8と、他端のソースドレイン領域SD8の側面と接したエクステンション領域ET9とが形成されている。また、カップリングキャパシタMGA3には、P型のエクステンション領域ET8, ET9間のチャネル層上にフローティングゲートFGとなるカップリングゲート電極MG3がゲート酸化膜G4を介して形成され、エクステンション領域ET8, ET9の上面に、ゲート電極MG3の両側面を覆うようにしてサイドウォールSWが形成されている。10

#### 【0060】

次にこの不揮発性半導体記憶装置11においてデータの書き込み動作について以下説明する。図6は、複数のメモリセル12a, 12b, 12c, 12dのうち、1行1列目のメモリセル12aにのみデータを書き込む際の各部位の電圧値を示している。実際上、この不揮発性半導体記憶装置11は、データの書き込み時、カップリングゲート線CGによって各メモリセル12a, 12b, 12c, 12dのカップリングキャパシタMGA3に8[V]の書き込み電圧を一律に印加し、イレース線ELをオーブンにする。20

#### 【0061】

これにより、図8に示すように、データが書き込まれる選択メモリセル13aは、カップリングゲート線CGに8[V]の書き込み電圧が印加されると、カップリングキャパシタMGA3およびフローティングゲートFG間に生じる容量結合によってフローティングゲートFGの電位が容量比だけ上昇し、これによってソース線SLが接続されたメモリトランジスタMGA1がオン状態となり、ソース線SLの電位をメモリトランジスタMGA1のチャネル領域CH4に伝える。その結果、ビット線BL1から0[V]が印加されているスイッチトランジスタSGAに隣接したメモリトランジスタMGA1では、上述した実施の形態と同様に、低濃度不純物エクステンション領域ET2にソースサイド注入に必要な強電界が発生し、この強電界により電荷をフローティングゲートFGに注入させ、データの書き込みを行い得る。30

#### 【0062】

なお、カップリングキャパシタMGA3のカップリングゲート電極MG3は、図7に示すように、メモリトランジスタMGA1のゲート電極MG1やイレーストランジスタMGA2のイレースゲート電極MG2よりも面積が大きく形成することにより容量比を上げることができる。これによりメモリセル12aでは、カップリングゲート線CGの電位を低減しても、メモリトランジスタMGA1において低濃度不純物エクステンション領域ET2と接するチャネル領域CH4端部の電位をソース線SLの電位と同程度まで高めることが可能となる。

#### 【0063】

以上の構成において、このメモリトランジスタMGA1でも、データの書き込み時、ソース線SLから一端に6[V]の書き込み電圧が印加され、かつビット線BL1からスイッチトランジスタSGAの一端に0[V]が印加されてオン状態になり、さらにカップリングゲート線CGからカップリングキャパシタMGA3に8[V]の書き込み電圧が印加されることで、ソース線SLおよびビット線BL1間のメモリトランジスタMGA1の低濃度不純物エクステンション領域ET2で6[V]の電圧降下を生じさせて強電界を発生させ、この強電界を利用してソースサイド注入により電荷をフローティングゲートFGに注入してデータを書き込むことができる。40

#### 【0064】

##### (7) S R A M セルを備える不揮発性半導体記憶装置について

次にS R A M (Static Random Access Memory) セルとメモリセルとを組み合わせた不揮発性半導体記憶装置について以下説明する。図1との対応部分に同一符号を付して示す図9は、本発明による不揮発性半導体記憶装置31を示し、メモリセル2a, 2bからなる不揮

10

20

30

40

50

発メモリ部33にS R A Mセル32が接続されている点に特徴を有する。この場合、不揮発メモリ部33は、メモリセル2aおよびメモリセル2bにより、2セル/1ビットの相補型セルを構成している。

#### 【 0 0 6 5 】

ここでS R A Mセル32は、N型M O Sトランジスタからなるアクセストランジスタ35a, 35bと、P型M O Sトランジスタからなるロードトランジスタ36a, 36bと、N型M O Sトランジスタからなるドライブトランジスタ37a, 37bとを備え、合計6個のM O Sトランジスタで構成されている。ロードトランジスタ36a(36b)は、ドレインがドライブトランジスタ37a(37b)のドレインに接続され、ソースが電源線Vppに接続されており、さらにゲートがドライブトランジスタ37a(37b)のゲートに接続されている。また、ドライブトランジスタ37a(37b)はソースがグランド線GNDに接続されている。10

#### 【 0 0 6 6 】

アクセストランジスタ35aは、相補型第1ビット線BLTにドレインが接続され、ロードトランジスタ36aおよびドライブトランジスタ37a間のストレージノードCaと、ロードトランジスタ36bおよびドライブトランジスタ37bのゲートとにソースが接続されている。一方、他方のアクセストランジスタ35bも同様に、相補型第2ビット線BLBにドレインが接続され、ロードトランジスタ36bおよびドライブトランジスタ37b間のストレージノードCbと、ロードトランジスタ36aおよびドライブトランジスタ37aのゲートとにソースが接続されている。さらに、これらアクセストランジスタ35a, 35bは共通のワード線WLにゲートが接続され、相補型第1ビット線BLTおよび相補型第2ビット線BLB間には、図示しないラッチタイプのセンスアンプが接続されている。20

#### 【 0 0 6 7 】

かかる構成に加えてS R A Mセル32には、一方のストレージノードCaに一方のメモリセル2aのビット線BL1が接続されるとともに、他方のストレージノードCbに他方のメモリセル2bのビット線BL2が接続されている。なお、ここで不揮発メモリ部33は、上述した実施の形態で説明した図1に示すメモリセル2a, 2bとほぼ同一構成を有するが、ここではスイッチトランジスタSGA, SGA<sub>b</sub>毎にそれぞれ個別のスイッチゲート線RG1, RG2を設けており、各スイッチトランジスタSGA, SGA<sub>b</sub>をそれぞれ別々にオンオフ制御し得るように構成されている。

#### 【 0 0 6 8 】

不揮発性半導体記憶装置31では、S R A Mセル32と不揮発メモリ部33間をスイッチトランジスタSGA, SGA<sub>b</sub>により遮断できるため、外部からS R A Mセル32への書き込み動作時や読み出し動作時に不揮発メモリ部33をスイッチトランジスタSGA, SGA<sub>b</sub>により切り離し、一般的なS R A Mセル32として使用することもできる。また、このS R A Mセル32はVddのみで動作でき、通常のコアM O Sを用いて構築できるため、高速動作が可能である。30

#### 【 0 0 6 9 】

このような構成を有する不揮発性半導体記憶装置31は、外部からのデータの書き込みや読み出しをS R A Mセル32で行うようになされている。不揮発メモリ部33へのデータ書き込み時には、メモリセル2a, 2bに書き込むデータが、当該メモリセル2a, 2bと直結したS R A Mセル32に格納されているので、データが格納された先をアドレス等で選択する必要がなく、また、不揮発メモリ部33で行うソースサイド注入は消費電力が小さいため、書き込み電位制御をマット一括で行うことができる。因みに、不揮発性半導体記憶装置31において消費電力を一段と低減させる場合には、スイッチゲート線RG1, RG2に印加する電圧を変えてスイッチトランジスタSGA, SGA<sub>b</sub>のいずれか一方だけをオン状態とすることで、消費電力を低減させることができる。更には、不揮発性半導体記憶装置31が行列状に配置された記憶装置において、選択した行のみ、スイッチゲート線RG1およびスイッチゲート線RG2、もしくはスイッチゲート線RG1またはスイッチゲート線RG2に印加する電圧を必要に応じて変え、オン状態となるスイッチトランジスタSGA, SGA<sub>b</sub>の数を減らし、書き込み時の消費電力を低減することもできる。40

#### 【 0 0 7 0 】

ここで、図10は、不揮発性半導体記憶装置31において、S R A Mセル32から不揮発メモリ部33へデータを取り込むプログラム時（図10中、「プログラム」と表記）、不揮発メモリ部33でのデータ消去時（図10中、「消去」と表記）、不揮発メモリ部33からS R A Mセル32へのデータを再び取り込むデータロード時（図10中、「データロード」と表記）、S R A Mセル32へのデータ書き込み時（図10中、「書き込み」と表記）、S R A Mセル32からのデータ読み出し時（図10中、「読み出し」と表記）、メモリセル2aまたはメモリセル2bのV<sub>th</sub>モニター時（図10中、「V<sub>th</sub>モニターロード」と表記）の各部位の電圧値をそれぞれ示す。なお、図10中、任意の電圧値に設定できる部位には「Don't care」と表記している。

## 【0071】

10

因みに、メモリセル2aおよびメモリセル2bでは、2セル/1ビットの相補型セルで構成されているため、各スイッチトランジスタSGA, SGA<sub>b</sub>を双方ともオン動作させると、相補側のセルの状態によって相補側のビット線の電位が変化することから、図示しないラッチ回路によって、例えば、より早く電圧が下がった側のビット線BL1を「1」とし、これに伴い他方のビット線BL2側を強制的に「0」としてしまい、メモリトランジスタMGA1, MGA1<sub>b</sub>のV<sub>th</sub>の正常なモニターを行えないという問題がある。

## 【0072】

そこで、本発明では、図9に示すように、相補型セルを構成するメモリセル2a, 2bにおいて、各スイッチトランジスタSGA, SGA<sub>b</sub>毎にスイッチゲート線RG1, RG2を設け、各スイッチトランジスタSGA, SGA<sub>b</sub>を個別にオンオフ動作させ、メモリセル2aおよびメモリセル2bの各メモリトランジスタMGA1, MGA1<sub>b</sub>のV<sub>th</sub>を個別にモニターし得るようになされている。

20

## 【0073】

## （7 1）S R A Mセルへのデータ書き込み

この場合、S R A Mセル32へのデータ書き込みは、ワード線WLにVddの所定電圧が印加され、ワード線WLに接続されたアクセストランジスタ35a, 35bを双方ともオン動作させる。また、この際、電源線VppにもVddの所定電圧が印加され得る。S R A Mセル32は、例えば一方の相補型第1ビット線BLTに書き込み電圧としてVddが印加されると、他方の相補型第2ビット線BLBに書き込み禁止電圧として0[V]が印加され得る。

## 【0074】

30

これにより、一方のロードトランジスタ36aおよびドライブトランジスタ37aでは、他方のアクセストランジスタ35bを介して相補型第2ビット線BLBとゲートが電気的に接続することによりゲートに0[V]が印加され、その結果、ロードトランジスタ36aがオン動作するとともに、ドライブトランジスタ37aがオフ動作する。かくして、これらロードトランジスタ36aおよびドライブトランジスタ37a間のストレージノードCaは、ロードトランジスタ36aを介して電源線Vppと電気的に接続して電圧がHigh（「1」）となる。

## 【0075】

40

このとき、他方のロードトランジスタ36bおよびドライブトランジスタ37bでは、一方のアクセストランジスタ35aを介して相補型第1ビット線BLTとゲートが電気的に接続することによりゲートにVddが印加され、その結果、ロードトランジスタ36bがオフ動作するとともに、ドライブトランジスタ37bがオン動作する。かくして、これらロードトランジスタ36bおよびドライブトランジスタ37b間のストレージノードCbは、ドライブトランジスタ37bを介してグランド線GNDと電気的に接続して電圧がLow（「0」）となる。以上によりS R A Mセル32データが書き込まれた状態となる。

## 【0076】

## （7 2）S R A Mセルからのデータ読み出し

S R A Mセル32のデータを読み出す際は、ワード線WLにVddの所定電圧が印加され、ワード線WLに接続されたアクセストランジスタ35a, 35bを双方ともオン動作する。これにより不揮発性半導体記憶装置31では、相補型第1ビット線BLTを介して一方のストレージノードCaの電位を読み出すとともに、相補型第2ビット線BLBを介して他方のストレージノードCbの電位を読み出すことで、センスアンプによってストレージノードCa, Cbに記録された

50

データの「0」「1」を判定し得る。

【0077】

(7 3) 不揮発メモリ部へのプログラム

本発明では、上述したS R A Mセル32に記録したデータを、上述した「(2)データの書き込み動作」の原理を基に、マット一括処理で不揮発メモリ部33に取り込むことができる。なお、ここでの説明では、S R A Mセル32において一方のストレージノードCaの電位が高いHigh状態にあり、他方のストレージノードCbの電位が低いLow状態にあるとする。

【0078】

この場合、不揮発メモリ部33では、イレース線ELに0[V]が印加され、ソース線SLに6[V]が印加され、さらにスイッチゲート線RG1,RG2にそれぞれVddが印加されて各スイッチトランジスタSGA,SGA<sub>b</sub>がオン状態となっている。不揮発メモリ部33は、データが書き込まれた一方のストレージノードCaに、一方のビット線BL1を介してメモリセル2aのスイッチトランジスタSGAが電気的に接続されていることから、スイッチトランジスタSGAの一端がストレージノードCaと同じHighの電位になる。これによりメモリトランジスタMGA1では、スイッチトランジスタSGA側とソース線SL側との電位差が小さくなることから強電界が発生することなく、フローティングゲートFGに電荷が注入され得ない。

【0079】

一方、この不揮発メモリ部33は、データが書き込まれていない他方のストレージノードCbに、他方のビット線BL2を介して他方のメモリセル2bのスイッチトランジスタSGA<sub>b</sub>が電気的に接続されていることから、スイッチトランジスタSGA<sub>b</sub>の一端がストレージノードCbと同じLowの電位になる。これによりメモリトランジスタMGA1<sub>b</sub>では、スイッチトランジスタSGA<sub>b</sub>側とソース線SL側との電位差が大きくなることから強電界が発生してフローティングゲートFGに電荷が注入され得る。

【0080】

このようにして不揮発性半導体記憶装置31では、S R A Mセル32に記録したデータを、マット一括処理で不揮発メモリ部33に取り込むことができ、かくして周辺回路の制御を簡素化させることもできる。

(7 4) 不揮発メモリ部からのデータロード

【0081】

また、本発明では、上述したように不揮発メモリ部33に一旦取り込んだデータを、上述した「(3)データの読み出し動作」の原理を基に、マット一括処理でS R A Mセル32に再び書き込むことができる。ここでは、不揮発メモリ部33においてメモリセル2bのフローティングゲートFGに電荷が蓄積してデータが書き込まれた状態とし、メモリセル2aのフローティングゲートFGに電荷が蓄積されておらずデータが書き込まれていない状態とする。また、この際、ストレージノードCa,Cbにはデータが書き込まれていないものとする。

【0082】

この場合、S R A Mセル32では、ワード線WLに0[V]が印加され、アクセストランジスタ35a,35bがオフ状態となっている。また、不揮発メモリ部33では、イレース線ELに0[V]が印加され、ソース線SLに3[V]が印加され、さらにスイッチゲート線RG1,RG2にそれぞれVddが印加されて各スイッチトランジスタSGA,SGA<sub>b</sub>がオン状態となっている。

【0083】

これにより不揮発メモリ部33は、メモリトランジスタMGA1およびビット線BL1間が電気的に接続され、フローティングゲートFGの高電位（電子が蓄積されていない状態）に伴ってS R A Mセル32の一方のストレージノードCaを高電位にしてデータが書き込まれた状態（「1」）に復元し得る。

【0084】

また、不揮発メモリ部33は、メモリトランジスタMGA<sub>b</sub>およびビット線BL2間も電気的に接続され、フローティングゲートFGの低電位（電子が蓄積されている状態）に伴ってS R A Mセル32の他方のストレージノードCbを低電位にしてデータが書き込まれない状態（「0」）に復元し得る。さらに、この不揮発メモリ部33では、S R A Mセル32へのデータロ

10

20

30

40

50

ードをマット一括処理で行うことができるところから、周辺回路の制御も簡素化させることができる。

#### 【0085】

##### (7 5) 不揮発メモリ部におけるデータ消去

さらに、本発明では、上述した「(4) データの消去動作」の原理を基に、不揮発メモリ部33においてデータを消去させることもできる。この場合、不揮発メモリ部33では、イレース線ELに7[V]のイレース電圧が印加され、ソース線SL、スイッチゲート線RG1, RG2に0[V]が印加され得る。不揮発メモリ部33は、イレース線ELに接続されたイレーストランジスタMGA2, MGA2<sub>b</sub>のゲート電極にのみ強い電界が印加されることで、イレーストランジスタMGA2, MGA2<sub>b</sub>のチャネル層によって各フローティングゲートFG中の電荷を引き抜き、マット一括処理で不揮発メモリ部33のデータ消去を行い得る。10

#### 【0086】

##### (7 6) 不揮発メモリ部に1つのメモリセルだけを設けた場合

因みに、上述した実施の形態においては、相補型の不揮発性半導体記憶装置31において2セル/1ビットの相補型セルとして2つのメモリセル2a, 2bを設けるようにした場合について述べたが、本発明はこれに限らず、相補型の不揮発性半導体記憶装置において例えば1つのメモリセル2aだけを設けるようにしてもよい。以下、図9において、他のメモリセル2bが設けられておらず、一のメモリセル2aだけが設けられているとして以下説明する。

#### 【0087】

例えば、S R A Mセル32において一方のストレージノードCaの電位が高いHigh状態にあり、他方のストレージノードCbの電位が低いLow状態にあるとした場合、不揮発メモリ部3へのプログラムは以下のようにして行われる。1つのメモリセル2aだけが設けられた不揮発メモリ部33では、イレース線ELに0[V]が印加され、ソース線SLに6[V]が印加され、さらにスイッチゲート線RG1にVddが印加されてスイッチトランジスタSGAがオン状態となっている。20

#### 【0088】

不揮発メモリ部33は、データが書き込まれた一方のストレージノードCaに、一方のビット線BL1を介してメモリセル2aのスイッチトランジスタSGAが電気的に接続されていることから、スイッチトランジスタSGAの一端がストレージノードCaと同じHighの電位になる。これによりメモリトランジスタでは、スイッチトランジスタSGA側とソース線SL側との電位差が小さくなることから強電界が発生することなく、フローティングゲートFGに電荷が注入され得ない。このようにして不揮発メモリ部33では、S R A Mセル32に記録したデータを1つのメモリセル2aだけに取り込む。30

#### 【0089】

次に、このようにしてデータを取り込んだ不揮発メモリ部33からS R A Mセル32へのデータロードについて以下説明する。この際、メモリセル2aには、フローティングゲートFGに電荷が蓄積されておらずデータが書き込まれていない状態となっており、また、ストレージノードCa, Cbにはデータが書き込まれていないものとする。

#### 【0090】

この場合、S R A Mセル32では、ワード線WLに0[V]が印加され、アクセストランジスタ35a, 35bがオフ状態となっている。また、不揮発メモリ部33では、イレース線ELに0[V]が印加され、ソース線SLに3[V]が印加され、さらにスイッチゲート線RG1にVddが印加されてスイッチトランジスタSGAがオン状態となっている。40

#### 【0091】

これによりメモリセル2aは、メモリトランジスタMGA1およびビット線BL1間が電気的に接続され、フローティングゲートFGの高電位（電子が蓄積されていない状態）に伴ってS R A Mセル32の一方のストレージノードCaを高電位にしてデータが書き込まれた状態（「1」）に復元し得る。また、この際、S R A Mセル32では、ストレージノードCaが高電位であることから、このストレージノードCaに接続されたロードトランジスタ36aがオフ状態となり、一方、ドライブトランジスタ37bがオン状態となることでストレージノードCa50

がゲート線GNDと接続して低電位となり、ストレージノードCbをデータが書き込まれない状態（「0」）に復元し得る。

#### 【0092】

このように、相互型の不揮発性半導体記憶装置では、S R A Mセル32の一方のストレージノードCaについてデータの書き込みの状態が決まれば、他方のストレージノードCbについてもデータの書き込み状態が決まることから、不揮発メモリ部33に設けた1つのメモリセル2aだけでS R A Mセル32へのデータロードを行うことができ、かくして他方のメモリセル2bを設けない分、さらに一段と回路構成を簡素化させることができる。

#### 【0093】

なお、本発明は、本実施の形態に限定されるものではなく、本発明の要旨の範囲内で種々の変形実施が可能である。例えば、図8に示した他の実施の形態によるメモリセルにおいて、メモリトランジスタMGA1のチャネル層に、図3に示したようなデブリート型チャネル領域CH1と、エンハンスマント型のチャネル領域CH2とを形成するようにしてもよい。10

#### 【0094】

また、図9に示す不揮発性半導体記憶装置31では、図1に示したメモリセル2a,2bを適用した不揮発メモリ部33を設けるようにした場合について述べたが、本発明はこれに限らず、図6に示したカップリングキャパシタMGA3を設けたメモリセル12a,12bを適用した不揮発メモリ部を設けるようにしてもよい。

#### 【0095】

なお、図1、図3～6、図8～図10において、データ書き込み時や、データ消去時、データ読み出し時等における各電圧値をそれぞれ明記しているが、本発明はこれに限らず、種々の電圧値を適用してもよい。例えば、上述した実施の形態においては、スイッチトランジスタSGAをオンオフ制御するために、ビット線BL1,BL2およびワード線WL1,WL2に1.5[V]の電圧を印加するようにした場合について述べたが、本発明はこれに限らず、スイッチトランジスタSGAをオンオフ制御できればよいことから、ビット線BL1,BL2およびワード線WL1,WL2に1.2[V]を印加しても、この場合、1.2[V]用のコアM O S (1.2V MOS)をスイッチトランジスタSGAとして用いることができる。20

#### 【0096】

さらに、上述した実施の形態においては、イレーストランジスタMGA2をP型の第2活性領域に形成し、メモリトランジスタMGA1およびスイッチトランジスタSGAをP型の第1活性領域に形成した場合について述べたが、本発明はこれに限らず、イレーストランジスタMGA2をN型の第2活性領域に形成し、メモリトランジスタMGA1およびスイッチトランジスタSGAをN型の第1活性領域に形成してもよく、また、図7に示すカップリングキャパシタMGA3をP型の第3活性領域に形成するようにしてもよい。30

#### 【0097】

また、上述した実施形態においては、メモリセル2aがイレーストランジスタMGA2を備えており、メモリセル2aのデータを消去可能な構成とした場合について述べたが、本発明はこれに限らず、例えば、メモリセル2aにイレーストランジスタMGA2を設げずに、スイッチトランジスタSGAおよびメモリトランジスタMGA1のみで構成したメモリセルとしてもよい。このようなメモリセルを備えた不揮発性半導体記憶装置は、メモリトランジスタMGA1に対して一回のみ書き込み可能な不揮発性素子となり得る。40

#### 【0098】

(8) 低濃度不純物エクステンション領域を設げずに高抵抗領域を有するメモリセル

上述した実施の形態においては、フローティングゲートFGの下部領域と、スイッチトランジスタSGAに電気的に接続された他端側のソースドレイン領域SD2との間に高抵抗領域として、低濃度不純物エクステンション領域ET2を設けた場合について述べたが、本発明はこれに限らず、メモリセルにおいてデータの読み出し動作が可能であれば、図3との対応部分に同一符号を付した図11のように、メモリセル42aにおいて、フローティングゲートFGの下部領域と、他端側のソースドレイン領域SD2との間に低濃度不純物エクステンション領域ET2を設げずに、エンハンスマント型のチャネル領域CH2をそのままソースドレイ

50

ン領域SD2まで形成し、フローティングゲートFGの下部領域と、他端側のソースドレイン領域SD2との間にあるチャネル領域CH2の一部を高抵抗領域WAとしてもよい。

#### 【0099】

このような構成を有するメモリセル42aでも、上述した実施の形態と同様に、データの書き込み時、ソース線SLからメモリトランジスタMGA1の一端に6[V]の書き込み電圧が印加され、かつビット線BL1からスイッチトランジスタSGAの一端に0[V]が印加されてオン状態になることで、メモリトランジスタMGA1において、当該スイッチトランジスタSGAと隣接する側の高抵抗領域WAで6[V]の電圧降下を生じさせて強電界を発生させ、この強電界により電荷をフローティングゲートFGに注入する、いわゆるソースサイド注入によってデータを書き込むことができる。

10

#### 【0100】

なお、サイドウォールSWの下部領域まで延びたチャネル領域CH2を設けた場合には、当該チャネル領域CH2の不純物濃度を $1E18/cm^3$ 以下とするのが望ましい。

#### 【0101】

因みに、このように低濃度不純物エクステンション領域ET2を設けずにチャネル領域をソースドレイン領域SD2まで形成し、サイドウォールSWの下部領域にあるチャネル領域を高抵抗領域WAとした構成については、図8に示すメモリトランジスタMGA1においても適用でき、この場合、チャネル領域CH4がそのままソースドレイン領域SD2まで延在した構成となり得る。

20

#### 【0102】

また、他のメモリトランジスタMGA1としては、上述したようにフローティングゲートFGの下部領域からソースドレイン領域SD2までチャネル領域CH2を形成した構成に加え、このような他端側と同様に、一端側のエクステンション領域ET1を設けずにデブリート型チャネル領域CH1をそのままソースドレイン領域SD1まで形成した構成としてもよい。

#### 【0103】

また、チャネル領域CH2をエンハンス型ではなくデブリート型のチャネル領域とし、このデブリート型のチャネル領域をそのままソースドレイン領域SD2まで形成して、フローティングゲートFGの下部領域と、他端側のソースドレイン領域SD2との間にあるデブリート型のチャネル領域の一部を高抵抗領域WAとしても良い。

#### 【0104】

30

このとき高抵抗領域WAの抵抗値は、一端側のエクステンション領域ET1が形成されている場合、当該エクステンション領域ET1の抵抗値よりも高くなるように形成され得る。また、一端側のエクステンション領域ET1を設けずにデブリート型チャネル領域CH1をフローティングゲートFGの下部領域からそのままソースドレイン領域SD1まで形成した場合でも、フローティングゲートFGの下部領域およびソースドレイン領域SD2間のデブリート型のチャネル領域の抵抗値は、一端側のデブリート型チャネル領域CH1の抵抗値よりも高くなるように形成され得る。

#### 【符号の説明】

#### 【0105】

1,11,31 不揮発性半導体記憶装置

40

2a,2b,2c,2d メモリセル

BL1,BL2 ビット線

CH1 デブリート型チャネル領域

ET1,ET3,ET4,ET5,ET6 エクステンション領域

ET2 低濃度不純物エクステンション領域（高抵抗領域）

FG フローティングゲート

MGA1 メモリトランジスタ

MGA2 イレーストランジスタ

MGA3 カップリングキャパシタ

MG1 ゲート電極

50

SGA スイッチトランジスタ

SG スイッチゲート電極

SL ソース線

WL1, WL2 ワード線

WA 高抵抗領域

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図11】

## 【図10】

|                            | EL         | RG1       | RG2       | SL         | Vpp | WL    |

|----------------------------|------------|-----------|-----------|------------|-----|-------|

| プログラム<br>(SRAMから不揮発メモリ部へ)  | 0          | Vdd       | Vdd       | 6          | Vdd | 0     |

| 消去<br>(不揮発メモリ部でデータ消去)      | 7          | 0         | 0         | 0          | Vdd | 0     |

| データロード<br>(不揮発メモリ部からSRAMへ) | 0          | Vdd       | Vdd       | 3          | Vdd | 0     |

| 書き込み<br>(SRAMへの書き込み)       | Don't care | 0         | 0         | Don't care | Vdd | Vdd/0 |

| 読み出し<br>(SRAMから読み出し)       | Don't care | 0         | 0         | Don't care | Vdd | Vdd/0 |

| Vthモニターロード                 | 0          | Vdd/<br>0 | 0/<br>Vdd | 0 or<br>3  | Vdd | Vdd   |

---

フロントページの続き

(51)Int.Cl. F I

H 01 L 21/8244 (2006.01) G 11 C 17/00 6 2 5

H 01 L 27/11 (2006.01)

G 11 C 16/04 (2006.01)

(56)参考文献 特開昭64-014798(JP,A)

特開2009-267185(JP,A)

特開2004-031920(JP,A)

特開2009-081181(JP,A)

特開2009-194140(JP,A)

(58)調査した分野(Int.Cl., DB名)

H 01 L 21 / 336

G 11 C 16 / 04

H 01 L 21 / 8244

H 01 L 21 / 8247

H 01 L 27 / 11

H 01 L 27 / 115

H 01 L 29 / 788

H 01 L 29 / 792