(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6037491号

(P6037491)

(45) 発行日 平成28年12月7日(2016.12.7)

(24) 登録日 平成28年11月11日(2016.11.11)

(51) Int.Cl.

G 11 C 11/15 (2006.01)

F 1

G 11 C 11/15 150

請求項の数 38 (全 24 頁)

(21) 出願番号 特願2016-501448 (P2016-501448)

(86) (22) 出願日 平成26年3月12日 (2014.3.12)

(65) 公表番号 特表2016-511502 (P2016-511502A)

(43) 公表日 平成28年4月14日 (2016.4.14)

(86) 國際出願番号 PCT/US2014/024245

(87) 國際公開番号 WO2014/150791

(87) 國際公開日 平成26年9月25日 (2014.9.25)

審査請求日 平成28年9月7日 (2016.9.7)

(31) 優先権主張番号 13/835,251

(32) 優先日 平成25年3月15日 (2013.3.15)

(33) 優先権主張国 米国(US)

早期審査対象出願

(73) 特許権者 507364838

クアルコム、インコーポレイテッド

アメリカ合衆国 カリフォルニア 921

21 サンディエゴ モアハウス ドラ

イブ 5775

(73) 特許権者 513262676

インダストリーアカデミック・コーポレ

ーション・ファウンデーション・ヨンセイ

・ユニヴァーシティ

大韓民国・ソウル・120-743・ソテ

ムング・シンチョンドン・ヨンセイ

ロ・50・ヨンセイ・ユニヴァーシティ

(74) 代理人 100108453

弁理士 村山 靖彦

最終頁に続く

(54) 【発明の名称】メモリセルを検知するシステムおよび方法

## (57) 【特許請求の範囲】

## 【請求項1】

データ電圧を生成するために第1の検知経路を用いてデータセルの状態を検知するステップであって、前記データセルの前記状態が前記データセルのプログラマブル抵抗ベースメモリ素子の状態に対応する、ステップと、

第1の基準電圧を生成するために基準セルの第1の状態を、第1の検知経路を用いて検知するステップと、

前記第1の基準電圧および前記基準セルに関連付けられた第2の基準電圧に基づいて、共有基準電圧を生成するための電荷共有動作を実施するステップと、

前記データ電圧および前記共有基準電圧に基づいて前記データセルの論理値を求めるステップと

を備える、方法。

## 【請求項2】

前記データセルの状態と前記基準セルの状態は共通検知経路を介して検知され、前記共通検知経路内の1つまたは複数の構成要素のプロセス変動に起因する前記データ電圧への影響が、前記1つまたは複数の構成要素の前記プロセス変動に起因する前記共有基準電圧への影響により少なくとも部分的に相殺される、請求項1に記載の方法。

## 【請求項3】

前記第2の基準電圧を生成するために前記基準セルの第2の状態を検知するステップと、前記データ電圧を前記共有基準電圧と比較するステップと、

10

20

をさらに備える、請求項1に記載の方法。

**【請求項4】**

前記データセルの前記論理値が、前記データ電圧が前記共有基準電圧よりも低い場合、第1の値に対応し、前記データセルの前記論理値が、前記データ電圧が前記共有基準電圧よりも高い場合、第2の値に対応する、請求項3に記載の方法。

**【請求項5】**

前記データセルの状態は第1の検知段階で検知され、前記基準セルの第1の状態は第2の検知段階で検知され、前記方法は、前記第2の基準電圧を生成するために前記基準セルの第2の状態を第3の検知段階の間に検知するステップをさらに備える、請求項1に記載の方法。 10

**【請求項6】**

前記基準セルの前記第1の状態が前記基準セルの第1の抵抗ベースメモリ素子の状態に対応し、前記基準セルの前記第2の状態が前記基準セルの第2の抵抗ベースメモリ素子の状態に対応する、請求項5に記載の方法。

**【請求項7】**

前記電荷共有動作を実施するステップは、前記共有基準電圧を生成するためにスイッチトキャパシタ回路の第1のキャパシタと第2のキャパシタの間の電荷共有を可能とし、前記共有基準電圧は前記第1の基準電圧と前記第2の基準電圧の平均に基づく、請求項1に記載の方法。 20

**【請求項8】**

前記第1の検知段階が第1の期間に相当し、かつ前記第2の検知段階が第2の期間に相当し、前記第3の検知段階が第3の期間に相当する、請求項5に記載の方法。

**【請求項9】**

前記プログラマブル抵抗ベースメモリ素子が磁気トンネル接合(MTJ)デバイスである、請求項1に記載の方法。

**【請求項10】**

前記プログラマブル抵抗ベースメモリ素子の前記状態が前記プログラマブル抵抗ベースメモリ素子の抵抗に対応する、請求項1に記載の方法。

**【請求項11】**

前記第1の検知経路がクランプトランジスタ、負荷トランジスタ、およびソース縮退トランジスタを含む、請求項2に記載の方法。 30

**【請求項12】**

前記データセルの前記状態を検知するステップ、前記基準セルの前記第1の状態を検知するステップ、および前記データセルの前記論理値を求めるステップが電子デバイスに統合されるプロセッサによって開始される、請求項1に記載の方法。

**【請求項13】**

前記第2の基準電圧を生成するために、前記基準セルの第2の抵抗ベースメモリ素子の状態を検知するステップをさらに備える、請求項1に記載の方法。

**【請求項14】**

前記データセルの前記状態は第1の検知段階の間に取得され、前記基準セルの前記第1の状態は第2の検知段階の間に取得され、前記方法は、 40

前記第2の基準電圧を生成するために、第2の検知経路を用いて前記第1の検知段階の間に前記基準セルの第2の状態を検知するステップと、

第2のデータ電圧を生成するために、前記第2の検知経路を用いて前記第2の検知段階の間に前記データセルの第2の状態を検知するステップであって、前記第1の検知経路と前記第2の検知経路は共通検知経路を含み、前記データセルの前記論理値はさらに前記データセルの前記第2のデータ電圧に基づく、ステップと、

をさらに備える、請求項1に記載の方法。

**【請求項15】**

前記データセルの平均データ電圧を生成するために、前記データセルの前記データ電圧 50

と前記第2のデータ電圧を平均するステップであって、前記データセルの前記論理値はさらに前記データセルの前記平均データ電圧に基づく、ステップをさらに備える、請求項14に記載の方法。

**【請求項16】**

前記データセルの前記平均データ電圧を生成するために前記データセルの前記データ電圧と前記データセルの前記第2のデータ電圧を平均するステップは、第3のキャパシタと第4のキャパシタの間の電荷を共有するステップを含む、請求項15に記載の方法。

**【請求項17】**

データ電圧を生成するためにデータセルの状態を検知し、第1の基準電圧を生成するために基準セルの第1の状態を検知するように構成される検知回路と、

10

前記第1の基準電圧および前記基準セルに関連付けられた第2の基準電圧に基づいて共有基準電圧を生成するために、第1のキャパシタと第2のキャパシタの間の電荷を共有するように構成されるスイッチトキャパシタ回路と、

前記データ電圧を前記共有基準電圧と比較し、前記比較に基づいて比較出力を生成するように構成されるセンスアンプと、

を備え、

前記データセルの前記状態が前記データセルのプログラマブル抵抗ベースメモリ素子の状態に対応する、

装置。

**【請求項18】**

20

前記検知回路が、

第1のデータ電圧を生成するために前記データセルの第1の状態を第1の検知段階の間に第1の検知経路を用いて検知し、

第2のデータ電圧を生成するために前記データセルの第2の状態を第2の検知段階の間に第2の検知経路を用いて検知する

ように構成され、

ことであって、前記データ電圧が前記第1のデータ電圧および前記第2のデータ電圧の平均に基づいて生成され、前記第1の検知経路と前記第2の検知経路が共通検知経路を含む、

請求項17に記載の装置。

**【請求項19】**

30

前記スイッチトキャパシタ回路は、前記データセルの前記データ電圧を生成するために第3のキャパシタと第4のキャパシタの間の電荷を共有するようにさらに構成される、請求項18に記載の装置。

**【請求項20】**

前記第1の検知経路および前記第2の検知経路がそれぞれ、ソース縮退トランジスタ、負荷トランジスタ、およびクランプトランジスタを含む、請求項18に記載の装置。

**【請求項21】**

前記比較出力が前記データセルの論理値に対応する、請求項17に記載の装置。

**【請求項22】**

前記データセルの状態と前記基準セルの前記第1の状態は共通検知経路を介して検知され、前記共通検知経路内の1つまたは複数の構成要素のプロセス変動に起因する前記データ電圧への影響が、前記1つまたは複数の構成要素の前記プロセス変動に起因する前記共有基準電圧への影響により少なくとも部分的に相殺される、請求項17に記載の装置。

40

**【請求項23】**

前記共通検知経路が、ソース縮退トランジスタ、負荷トランジスタ、およびクランプトランジスタを含む、請求項22に記載の装置。

**【請求項24】**

前記検知回路および前記センスアンプが少なくとも1つの半導体ダイに統合される、請求項17に記載の装置。

**【請求項25】**

50

前記検知回路および前記センスアンプが統合されるセットトップボックス、音楽プレーヤ、ビデオプレーヤ、娛樂ユニット、ナビゲーションデバイス、通信デバイス、携帯情報端末(PDA)、固定位置データユニット、およびコンピュータから選択されるデバイスをさらに備える、請求項17に記載の装置。

**【請求項 26】**

前記検知回路が、電源に接続されたソース縮退トランジスタを含む、請求項17に記載の装置。

**【請求項 27】**

データ電圧を生成するためにデータセルの状態を検知するための手段であって、前記データセルの前記状態が前記データセルのプログラマブル抵抗ベースメモリ素子の状態に対応する、手段と、

第1の基準電圧を生成するために基準セルの第1の状態を検知するための手段と、

前記第1の基準電圧および前記基準セルに関連付けられた第2の基準電圧に基づいて共有基準電圧を生成するために、前記第1の基準電圧を格納するための手段と前記第2の基準電圧を格納するための手段の間の電荷を共有するための手段と、

前記データ電圧および前記共有基準電圧に基づいて前記データセルの論理値を求めるための手段と、

を備える、装置。

**【請求項 28】**

前記データ電圧を前記共有基準電圧と比較するための手段をさらに備える、請求項27に記載の装置。

**【請求項 29】**

前記データセルの前記論理値を求めるための前記手段が前記データ電圧を前記共有基準電圧と比較するための前記手段に基づく、請求項28に記載の装置。

**【請求項 30】**

前記データセルの前記状態を検知するための前記手段、前記基準セルの前記状態を検知するための前記手段、および前記データセルの前記論理値を求めるための前記手段が統合されるセットトップボックス、音楽プレーヤ、ビデオプレーヤ、娯楽ユニット、ナビゲーションデバイス、通信デバイス、携帯情報端末(PDA)、固定位置データユニット、およびコンピュータから選択されるデバイスをさらに備える、請求項27に記載の装置。

**【請求項 31】**

プロセッサによって実行されると、前記プロセッサに、

データセルへの検知回路の結合を可能にさせ、

基準セルへの前記検知回路の結合を可能にさせ、

第1の基準電圧および前記基準セルに関連付けられた第2の基準電圧に基づいて、共有基準電圧を生成するための電荷共有動作の実施を可能にさせ、

データ電圧および前記共有基準電圧に基づいて前記データセルの論理値を求める

前記データ電圧および前記共有基準電圧に基づいて前記データセルの論理値を求めさせる

命令を備え、

前記データセルの状態が、前記データセルへの前記検知回路の前記結合に基づいて前記データ電圧を生成するために第1の検知経路を用いて検知され、前記データセルの前記状態が前記データセルのプログラマブル抵抗ベースメモリ素子の状態に対応し、

前記基準セルの第1の状態が、前記基準セルへの前記検知回路の前記結合に基づいて前記第1の基準電圧を生成するために前記第1の検知経路を用いて検知される、

非一時的コンピュータ可読記憶媒体。

**【請求項 32】**

前記データセルへの前記検知回路の前記結合を可能にさせることが、

前記検知回路と前記プログラマブル抵抗ベースメモリ素子とに結合される第1の選択トランジスタを第1の検知段階の間、有効化すること

10

20

30

40

50

を含む、請求項31に記載の非一時的コンピュータ可読記憶媒体。

**【請求項 3 3】**

前記データセルへの前記検知回路の前記結合を可能にさせることができ、

前記第1の基準電圧を生成するために、前記検知回路と前記基準セルの第1の抵抗ベースメモリ素子とに結合される第2の選択トランジスタを第2の検知段階の間、有効化することと、

前記第2の基準電圧を生成するために、前記検知回路と前記基準セルの第2の抵抗ベースメモリ素子とに結合される第3の選択トランジスタを第3の検知段階の間、有効化することと

を含む、請求項32に記載の非一時的コンピュータ可読記憶媒体。

10

**【請求項 3 4】**

前記データセルへの前記検知回路の前記結合を可能にさせることができ、

第1のデータ電圧を生成するために、前記第1の検知経路と前記データセルとに結合される第1の選択トランジスタを第1の検知段階の間、有効化することと、

第2のデータ電圧を生成するために、第2の検知経路と前記データセルとに結合される第2の選択トランジスタを第2の検知段階の間、有効化することと、

を含む、請求項31に記載の非一時的コンピュータ可読記憶媒体。

**【請求項 3 5】**

前記基準セルへの前記検知回路の前記結合を可能にさせることができ、

前記第1の基準電圧を生成するために、前記第2の検知経路と前記基準セルとに結合される第3の選択トランジスタを前記第1の検知段階の間、有効化することと、

前記第2の基準電圧を生成するために、前記第1の検知経路と前記基準セルとに結合される第4の選択トランジスタを前記第2の検知段階の間、有効化することとを含む、請求項34に記載の非一時的コンピュータ可読記憶媒体。

20

**【請求項 3 6】**

前記データ電圧が前記第1のデータ電圧と前記第2のデータ電圧の平均に相当し、かつ前記共有基準電圧が前記第1の基準電圧と前記第2の基準電圧の平均に相当する、請求項35に記載の非一時的コンピュータ可読記憶媒体。

**【請求項 3 7】**

データ電圧を生成するために第1の検知経路を用いてデータセルの状態を検知するためのステップであって、前記データセルの前記状態が前記データセルのプログラマブル抵抗ベースメモリ素子の状態に対応する、ステップと、

第1の基準電圧を生成するために基準セルの第1の状態を、前記第1の検知経路を用いて検知するためのステップと、

前記第1の基準電圧および前記基準セルに関連付けられた第2の基準電圧に基づいて、共有基準電圧を生成するための電荷共有動作を実施するためのステップと、

前記データ電圧および前記共有基準電圧に基づいて前記データセルの論理値を求めるためのステップとを備える、方法。

30

**【請求項 3 8】**

前記データセルの前記論理値を求めるための前記ステップが電子デバイスに統合されるプロセッサで行われる、請求項37に記載の方法。

40

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

関連出願の相互参照

本出願は、2013年3月15日に出願した所有者が共通の米国非仮出願第13/835,251号の優先権を主張し、その内容が全体として参照により本明細書に明示的に組み込まれる。

**【0002】**

本開示は一般にメモリセルを検知することに関する。

**【背景技術】**

50

**【0003】**

技術の進歩はより小型でより強力なコンピューティングデバイスをもたらした。たとえば現在、小型で、軽量で、ユーザが持ち運び容易な携帯型ワイヤレス電話機、携帯情報端末(PDA)、およびペーディングデバイスなどのワイヤレスコンピューティングデバイスを含めて、様々な携帯型パーソナルコンピューティングデバイスが存在する。より具体的には、セルラー電話機やインターネットプロトコル(IP)電話機などの携帯型ワイヤレス電話機はワイヤレスネットワーク上で音声およびデータパケットを通信できる。さらに、多くのそのようなワイヤレス電話機はその内部に組み込まれる他の種類のデバイスを含む。たとえばワイヤレス電話機はデジタルスチルカメラ、デジタルビデオカメラ、デジタルレコーダ、およびオーディオファイルプレーヤをも含み得る。またそのようなワイヤレス電話機は、インターネットにアクセスするために使用できる、ウェブブラウザアプリケーションなどのソフトウェアアプリケーションを含む、実行可能命令を処理できる。このように、これらのワイヤレス電話機はかなりのコンピューティング能力を含み得る。

10

**【0004】**

ワイヤレス電話機や他の電子デバイス内の回路はメモリストレージのためにスピントランスマルク磁気抵抗ランダムアクセスメモリ(STT-MRAM)を使用してよい。STT-MRAM内の各メモリセルは磁気トンネル接合(MTJ)素子に流れるスピニ偏極電流によってプログラムしてよい。たとえばスイッチング電流がMTJ素子に流れると、MTJ素子の自由層の磁化方向がMTJ素子の固定層の磁化方向に関して変化してよい(たとえば、平行状態から反平行状態へ)。MTJ素子は、自由層の磁化方向が固定層の磁化方向と平行であるときのより低い抵抗と比較して、自由層の磁化方向が固定層の磁化方向と反平行であるときにより高い抵抗を有してよい。自由層の磁化方向の変化はメモリセルの論理値の論理「0」から論理「1」への変化に対応してよい。

20

**【0005】**

読み出し動作の間にメモリセルの論理値を読み出す(すなわち、検知する)場合、センス電流がスイッチング電流と同じ経路を用いてMTJ素子に流れる。センス電流とスイッチング電流は同じ経路を用いてMTJ素子に流れるので、センス電流は、読み出し動作の間にメモリセルの論理値の何らの障害(すなわち、読み出しディスクエーブ)も引き起こさないように、MTJ素子に段階変化させる最小スイッチング電流(「臨界」スイッチング電流)よりも十分に低いべきである。たとえばセンス電流は自由層の磁化方向にはほとんど、または全く影響を有しないように十分に小さいべきである。

30

**【0006】**

しかしながら、小さいセンス電流はメモリセルと基準セルとの間の検知マージンを減少させ得る。たとえば検知回路は、メモリセルに対応する出力電圧をデータ分岐を用いて検知し、同時に基準セルに対応する出力電圧を基準分岐を用いて検知してよい。メモリセルに対応する出力電圧は、メモリセルの論理値を求めるために基準セルに対応する出力電圧と比較してよい。データ分岐と基準分岐内の素子のプロセス変動が、メモリセルと基準セルとの間の検知マージンを減少させ得る、したがってメモリセルに対応する出力電圧を基準セルに対応する出力電圧と比較する際の誤差を引き起こし得る、データ分岐と基準分岐との間のオフセット電圧をもたらし得る。

40

**【発明の概要】****【課題を解決するための手段】****【0007】**

多段検知を用いてメモリセルを検知するシステムおよび方法を開示する。スピントランスマルク磁気抵抗ランダムアクセスメモリ(STT-MRAM)はメモリセルと基準セルを含む。検知経路内の構成要素のプロセス変動によりもたらされ得る電圧オフセットは複数の検知段階の結果を組み合わせるときに相殺してよい。たとえば検知回路は、メモリセルの状態を検知するためと基準セルの状態を検知するために共通の検知経路を使用してよい。メモリセルの状態は特定の段階の間に検知経路を介して検知してよく、基準セルの状態は別の段階の間に同じ検知経路を介して検知してよい。メモリセルの状態に対応する出力電圧

50

は、メモリセルの論理値を求めるために基準セルの状態に対応する出力電圧と比較してよい。

#### 【0008】

特定の実施形態において、方法はデータ電圧を生成するためにデータセルの状態を検知することを含む。データセルの状態はデータセルのプログラマブル抵抗ベースメモリ素子の状態に対応する。方法はさらに、基準電圧を生成するために基準セルの状態を検知することを含む。データセルの状態と基準セルの状態は共通の検知経路を介して検知される。方法はさらに、データ電圧および基準電圧に基づいてデータセルの論理値を求めることを含む。

#### 【0009】

別の特定の実施形態において、装置は検知回路とセンスアンプを含む。検知回路は、データ電圧を生成するためにデータセルの状態を検知するように構成される。データセルの状態はデータセルのプログラマブル抵抗ベースメモリ素子の状態に対応する。検知回路はさらに、基準電圧を生成するために基準セルの状態を検知するように構成される。データセルの状態と基準セルの状態は共通の検知経路を介して検知される。センスアンプは、データ電圧を基準電圧と比較し、比較に基づいて比較出力を生成するように構成される。

#### 【0010】

開示する実施形態のうちの少なくとも1つによって提供される1つの特定の利点は、メモリセルの状態を検知するためと基準セルの状態を検知するための複数の段階の間に共通の検知経路を利用することによって、検知経路内の構成要素のプロセス変動によってもたらされるオフセット電圧を低減または排除する能力である。本開示の他の態様、利点、および特徴は、以下の各部：図面の簡単な説明、発明を実施するための形態、および特許請求の範囲を含めて、本出願全体を概観した後明らかになるであろう。

#### 【図面の簡単な説明】

#### 【0011】

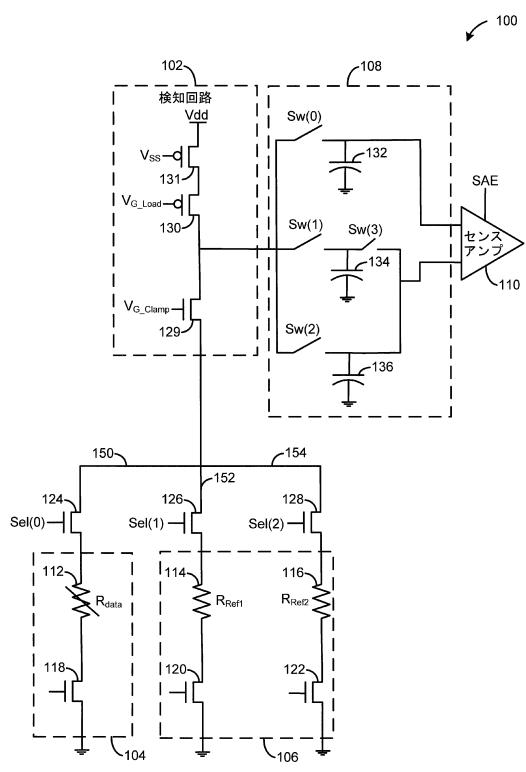

【図1】3段階プロセスを用いてデータセルの値を読み出すように動作可能であるメモリシステムの特定の例示的な実施形態の回路図である。

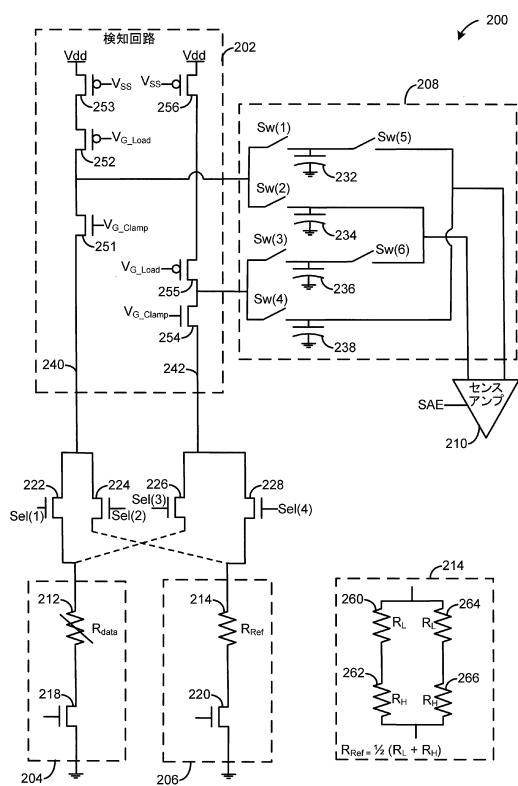

【図2】2段階プロセスを用いてデータセルの値を読み出すように動作可能であるメモリシステムの他の特定の例示的な実施形態の回路図である。

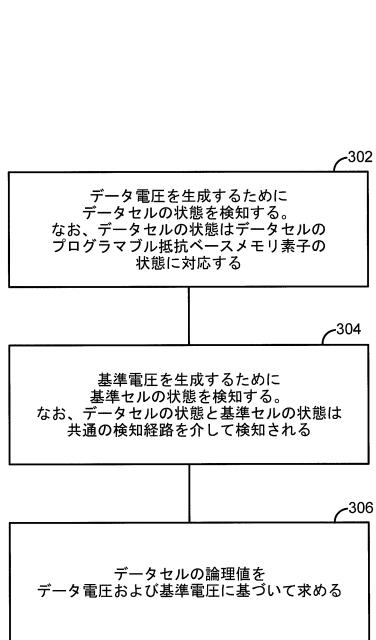

【図3】多段階プロセスを用いてデータセルの値を読み出す方法の特定の実施形態のフローチャートである。

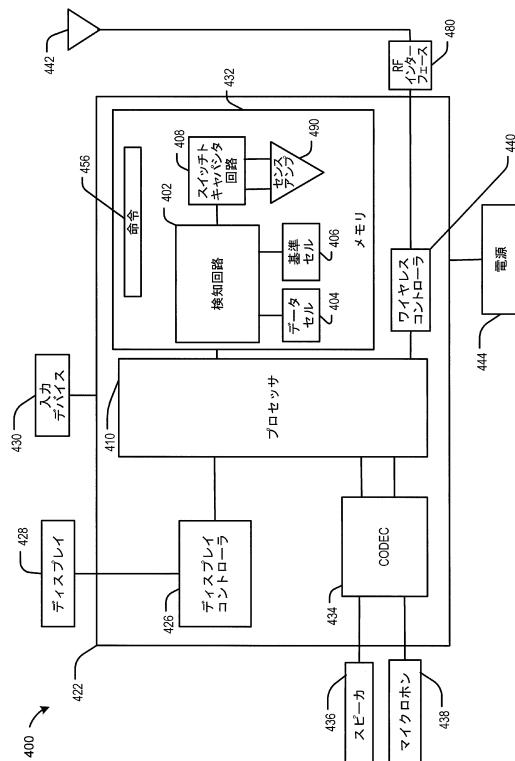

【図4】電圧オフセットを低減するために多段階プロセスを用いてデータセルの値を読み出すように動作可能である構成要素を含むワイヤレスデバイスのブロック図である。

【図5】電圧オフセットを低減するために多段階プロセスを用いてデータセルの値を読み出すように動作可能である構成要素を含む電子デバイスを製造する製造プロセスの特定の例示的な実施形態のデータフロー図である。

#### 【発明を実施するための形態】

#### 【0012】

図1を参照すると、3段階プロセスを用いてデータセルの値を読み出すように動作可能であるメモリシステム100の特定の例示的な実施形態を示す。メモリシステム100は検知回路102、データセル104、基準セル106、スイッチトキャパシタ回路108、およびセンスアンプ110を含む。データセル104は磁気抵抗ランダムアクセスメモリ(MRAM)、相変化ランダムアクセスメモリ(PRAM)、またはスピントランスマルク磁気抵抗ランダムアクセスメモリ(STT-MRAM)内のメモリセルであってよい。メモリシステム100は、データセル104の状態を検知するためと基準セル106の状態を検知するために共通の検知経路を使用することによって検知動作の間の電圧オフセットを低減または相殺してよい。たとえばメモリシステム100は、共通の検知経路を用いてデータセル104の状態を検知するためと基準セル106の状態を検知するために3段階プロセスを使用してよい。

#### 【0013】

データセル104はプログラマブル抵抗ベースメモリ素子112とデータセルアクセストラン

10

20

30

40

50

ジスタ118を含む。プログラマブル抵抗ベースメモリ素子112はデータセルアクセストランジスタ118のドレインに結合してよく、データセルアクセストランジスタ118のソースは接地に結合してよい。特定の実施形態において、プログラマブル抵抗ベースメモリ素子112は磁気トンネル接合(MTJ)素子を含む。プログラマブル抵抗ベースメモリ素子112の抵抗( $R_{data}$ )は、プログラマブル抵抗ベースメモリ素子112に提供される電流を介してプログラマブル抵抗ベースメモリ素子112に書き込まれるデータ値に基づいてよい。

#### 【0014】

たとえばプログラマブル抵抗ベースメモリ素子112は固定層と自由層を有してよい。プログラマブル抵抗ベースメモリ素子112に印加される電流の大きさがスイッチング電流( $I_C$ )よりも小さければ、電流はプログラマブル抵抗ベースメモリ素子112の抵抗( $R_{data}$ )を検知する(すなわち、データセル104の状態(たとえば、論理「1」または論理「0」)を検知する)ために使用してよい。たとえば電流の大きさがスイッチング電流未満の場合、電流は固定層および自由層の磁化方向が平行で、低抵抗状態に対応するか、または固定層および自由層の磁化方向が反平行で、高抵抗状態に対応するかを検知するために使用してよい。電流の大きさがスイッチング電流以上であれば、電流は電流の方向に基づいてプログラマブル抵抗ベースメモリ素子112をプログラムする(すなわち、データセル104の状態をプログラムする)ために使用してよい。

#### 【0015】

基準セル106は第1の抵抗ベースメモリ素子114、第1のアクセストランジスタ120、第2の抵抗ベースメモリ素子116、および第2のアクセストランジスタ122を含む。第1の抵抗ベースメモリ素子114は第1のアクセストランジスタ120のドレインに結合してよく、第1のアクセストランジスタ120のソースは接地に結合してよい。第2の抵抗ベースメモリ素子116は第2のアクセストランジスタ122のドレインに結合してよく、第2のアクセストランジスタ122のソースは接地に結合してよい。特定の実施形態において、第1の抵抗ベースメモリ素子114と第2の抵抗ベースメモリ素子116はMTJ素子である。第1の抵抗ベースメモリ素子114は「低」抵抗( $R_{Ref1}$ )を有してよく、第2の抵抗ベースメモリ素子116は「高」抵抗( $R_{Ref2}$ )を有してよい。たとえば、第1の抵抗ベースメモリ素子114の抵抗は論理「0」を表す状態に対応してよく、第2の抵抗ベースメモリ素子116の抵抗は論理「1」を表す状態に対応してよい。

#### 【0016】

検知回路102は、プロセス変動による電圧オフセットに寄与してよい、クランプトランジスタ129、負荷トランジスタ130、およびソース縮退トランジスタ131などの1つまたは複数の構成要素を含んでよい。ソース縮退トランジスタ131はシステム電源(Vdd)に結合してよい。特定の実施形態において、クランプトランジスタ129はn型金属酸化膜半導体(NMOS)トランジスタであり、負荷トランジスタ130とソース縮退トランジスタ131はp型金属酸化膜半導体(PMOS)トランジスタである。データセル選択トランジスタ124、第1の選択トランジスタ126、および第2の選択トランジスタ128もメモリシステム100に含めてよい。

#### 【0017】

データセル選択トランジスタ124、プログラマブル抵抗ベースメモリ素子112、およびデータセルアクセストランジスタ118はメモリシステム100のデータ分岐150に含めてよい。第1の選択トランジスタ126、第1の抵抗ベースメモリ素子114、および第1のアクセストランジスタ120はメモリシステム100の第1の基準分岐152に含めてよい。第2の選択トランジスタ128、第2の抵抗ベースメモリ素子116、および第2のアクセストランジスタ122はメモリシステム100の第2の基準分岐154に含めてよい。データ分岐150、第1の基準分岐152、および第2の基準分岐154は、データセル選択トランジスタ124、第1の選択トランジスタ126、および第2の選択トランジスタ128でそれぞれ受信する制御信号Sel(0)、Sel(1)、Sel(2)を介して、選択的に検知回路102に結合してよい。特定の実施形態において、データセル選択トランジスタ124、第1の選択トランジスタ126、および第2の選択トランジスタ128は分岐選択マルチプレクサ(図示せず)に含まれる。

#### 【0018】

10

20

30

40

50

検知回路102は、データ電圧を生成するためにデータセル104の状態を検知するように構成される。たとえば検知回路102は、データセル104のプログラマブル抵抗ベースメモリ素子112に流れる電流を検知し、負荷トランジスタ130を用いて電流に基づいてデータ電圧を生成してよい。データ電圧は、プログラマブル抵抗ベースメモリ素子112の抵抗( $R_{data}$ )に反比例してよいプログラマブル抵抗ベースメモリ素子112に流れる電流に反比例してよい。検知回路102はデータセル104の状態を第1の検知段階の間に(すなわち、第1の期間の間に)検知してよい。第1の検知段階は、制御信号Sel(0)がプログラマブル抵抗ベースメモリ素子112を検知回路102に結合するためにデータセル選択トランジスタ124を有効化するときに対応してよい。特定の実施形態において、第1検知段階はおよそ2ナノ秒の持続時間を有する。

10

#### 【0019】

検知回路102はさらに、基準電圧を生成するために基準セル106の状態を検知するように構成される。たとえば検知回路102は、第1の基準電圧を生成するために基準セル106の第1の状態を第2の検知段階の間に(すなわち、第2の期間の間に)検知してよい。第2の検知段階は、制御信号Sel(1)が第1の抵抗ベースメモリ素子114を検知回路102に結合するために第1の選択トランジスタ126を有効化するときに対応してよい。検知回路102は、基準セル106の第1の抵抗ベースメモリ素子114に流れる電流を検知し、負荷トランジスタ130を用いて電流に基づいて第1の基準電圧を生成してよい。第1の基準電圧は、第1の抵抗ベースメモリ素子114の抵抗( $R_{Ref1}$ )に反比例してよい第1の抵抗ベースメモリ素子114に流れる電流に反比例してよい。同様に、検知回路102はさらに、制御信号Sel(2)が第2の抵抗ベースメモリ素子116を検知回路102に結合するために第2の選択トランジスタ128を有効化するとき、第2の基準電圧を生成するために基準セル106の第2の状態を第3の検知段階の間に検知するように構成される。第2の基準電圧は、第2の抵抗ベースメモリ素子116の抵抗( $R_{Ref2}$ )に反比例してよい第2の抵抗ベースメモリ素子116に流れる電流に反比例してよい。特定の実施形態において、第2および第3の検知段階の持続時間は各々およそ2ナノ秒である。

20

#### 【0020】

スイッチトキャパシタ回路108はデータコンデンサ132、第1のコンデンサ134、および第2のコンデンサ136を含む。データコンデンサ132の正端子はセンスアンプ110の第1の入力に結合してよく、また検知回路102にデータセルスイッチSw(0)を介して選択的に結合してよい。データコンデンサ132の負端子は接地に結合してよい。第1のコンデンサ134の正端子はセンスアンプ110の第2の入力に第3のスイッチSw(3)を介して選択的に結合され、また検知回路102に第1のスイッチSw(1)を介して選択的に結合される。第1のコンデンサ134の負端子は接地に結合してよい。第2のコンデンサ136の正端子はセンスアンプ110の第2の入力に結合してよく、また検知回路102に第2のスイッチSw(2)を介して選択的に結合してよい。第2のコンデンサ136の負端子は接地に結合してよい。

30

#### 【0021】

データコンデンサ132は、データセル104の状態(すなわち、プログラマブル抵抗ベースメモリ素子112の抵抗( $R_{data}$ ))が検知されるときに検知回路102で生成されるデータ電圧を記憶するように構成される。たとえば第1の検知段階の間、データセルスイッチSw(0)は有効化してよく、第1および第2のスイッチSw(1)、Sw(2)は無効化してよい。データセルスイッチSw(0)を有効化することに応じて、検知回路102はデータコンデンサ132をデータ電圧に基づいて充電してよい。第1のコンデンサ134は、基準セル106の第1の状態(すなわち、第1の抵抗ベースメモリ素子114の抵抗( $R_{Ref1}$ ))が検知されるときに検知回路102で生成される第1の基準電圧を記憶するように構成される。たとえば第2の検知段階の間、第1のスイッチSw(1)は有効化してよく、データセルスイッチSw(0)と第2のスイッチSw(2)は無効化してよい。第1のスイッチSw(1)を有効化することに応じて、検知回路102は第1のコンデンサ134を第1の基準電圧に基づいて充電してよい。第2のコンデンサ136は、基準セル106の第2の状態(すなわち、第2の抵抗ベースメモリ素子116の抵抗( $R_{Ref2}$ ))が検知されるときに検知回路102で生成される第2の基準電圧を記憶するように構成される。たとえば第3の検知段階の間、第2のスイッチSw(2)は有効化してよく、データセルスイッチSw(0)と第1のス

40

50

イッチSw(1)は無効化してよい。第2のスイッチSw(2)を有効化することに応じて、検知回路102は第2のコンデンサ136を第2の基準電圧に基づいて充電してよい。

#### 【0022】

第1の基準電圧と第2の基準電圧の平均を、基準電圧を生成するために求めてよい。たとえば第1および第2のコンデンサ134、136がそれぞれ第1および第2の基準電圧に基づいて充電された後、第3のスイッチSw(3)が有効化する。第1および第2の基準電圧の平均(すなわち、基準電圧)は、第3のスイッチSw(3)が有効化されるときに電荷共有によって生成してよい。基準電圧はセンスアンプ110の第2の入力に提供されるが、一方データ電圧はセンスアンプ110の第1の入力に提供される。

#### 【0023】

センスアンプ110はデータ電圧および基準電圧に基づいてデータセル104の論理値を求めるように構成される。たとえばセンスアンプイネーブル信号(SAE)に応じて、センスアンプ110はデータ電圧を基準電圧と比較してよい。データセル104の論理値は、データ電圧が基準電圧よりも低い場合、第1の値(すなわち、論理「0」値)に対応してよい。データセル104の論理値は、データ電圧が基準電圧よりも高い場合、第2の値(すなわち、論理「1」値)に対応してよい。

#### 【0024】

動作の間メモリシステム100は、データセル104の状態と基準セル106の状態を検知するために同じ負荷トランジスタ130およびクランプトランジスタ129(すなわち、共通の検知経路)を使用する。たとえば第1の検知段階の間、分岐選択マルチプレクサはデータセル選択トランジスタ124を有効化し、検知回路102はデータセル104の状態を検知し、状態に基づいてデータ電圧を生成する。データ分岐150(ならびに負荷トランジスタ130およびクランプトランジスタ129(すなわち、検知経路))はデータセル104の状態を検知するために使用される。第2の検知段階の間、分岐選択マルチプレクサは第1の選択トランジスタ126を有効化し、検知回路102は基準セル106の第1の状態を検知し、第1の状態に基づいて第1の基準電圧を生成する。第1の基準分岐152、および検知経路は、基準セルの第1の状態を検知するために使用される。第3の検知段階の間、分岐選択マルチプレクサは第2の選択トランジスタ128を有効化し、検知回路102は基準セル106の第2の状態を検知し、第2の状態に基づいて第2の基準電圧を生成する。第2の基準分岐154、および検知経路は、基準セル106の第2の状態を検知するために使用される。

#### 【0025】

データセルスイッチSw(0)はデータコンデンサ132をデータ電圧に基づいて充電するために第1の検知段階の間有効化され、第1のスイッチSw(1)は第1のコンデンサ134を第1の基準電圧に基づいて充電するために第2の検知段階の間有効化され、第2のスイッチSw(2)は第2のコンデンサ136を第2の基準電圧に基づいて充電するために第3の検知段階の間有効化される。第3の検知段階の後、第3のスイッチSw(3)は第1および第2のコンデンサ134、136の電荷間の電荷共有を引き起こすように有効化される。基準電圧は共有電荷に基づいて生成される。データセル104の論理値はセンスアンプ110によってデータ電圧(すなわち、データコンデンサの電荷)および基準電圧(すなわち、第1および第2のコンデンサ134、136の共有電荷)に基づいて求められる。

#### 【0026】

図1のメモリシステム100は、データセル104の状態と基準セル106の状態を検知するときに、同じ負荷トランジスタ130およびクランプトランジスタ129(すなわち、共通の検知経路)を利用することによって、データ分岐150および基準分岐152、154から不整合を除去し得ることが認識されるであろう。たとえばデータ分岐150および各基準分岐152、154のために別の負荷トランジスタおよびクランプトランジスタを利用することは、別の負荷トランジスタおよびクランプトランジスタのプロセス変動によって検知回路102の検知マージンを制限し得る。共通の負荷トランジスタ130およびクランプトランジスタ129を3つの異なる段階で利用することによって、データ電圧と基準電圧を生成してよく、そうでなければ別の負荷およびクランプトランジスタを使用することから発生するであろう電圧オフセ

10

20

30

40

50

ットは低減または相殺し得る。電圧オフセットを相殺することは検知回路102の検知マージンを増大し得るので、データセル104と基準セル106に提供されるセンス電流量を低減し得る。例示として、検知マージンを増大させる結果として、センス電流はおよそ200マイクロアンペアからおよそ20マイクロアンペアへ低減し得る。より小さいセンス電流を利用することは、検知動作の間のプログラマブル抵抗ベースメモリ素子112の読み出しディストラーブを低減または排除し得る。

#### 【0027】

図2を参照すると、2段階プロセスを用いてデータセルの値を読み出すように動作可能であるメモリシステム200の別の特定の例示的な実施形態を示す。メモリシステム200は検知回路202、データセル204、基準セル206、スイッチトキャパシタ回路208、およびセンスアンプ210を含む。データセル204は磁気抵抗ランダムアクセスメモリ(MRAM)、相変化ランダムアクセスメモリ(PRAM)、またはスピントランスマagnetic抵抗トルクランダムアクセスメモリ(STT-MRAM)内のメモリセルであってよい。メモリシステム200は、データセル204の状態を検知するためと基準セル206の状態を検知するために共通の検知経路を使用することによって検知動作の間の電圧オフセットを低減または相殺してよい。たとえばメモリシステム200は、共通の検知経路を用いてデータセル204の状態を検知するためと基準セル206の状態を検知するために2段階プロセスを使用してよい。

#### 【0028】

データセル204はプログラマブル抵抗ベースメモリ素子212とデータセルアクセストランジスタ218を含む。プログラマブル抵抗ベースメモリ素子212はデータセルアクセストランジスタ218のドレインに結合してよく、データセルアクセストランジスタ218のソースは接地に結合してよい。プログラマブル抵抗ベースメモリ素子212は図1のプログラマブル抵抗ベースメモリ素子112に対応してよく、また実質的に同様の方法で動作してよい。

#### 【0029】

基準セル206は基準抵抗ベースメモリ素子214と基準セルアクセストランジスタ220を含む。基準抵抗ベースメモリ素子214は基準セルアクセストランジスタのドレインに結合してよく、基準セルアクセストランジスタ220のソースは接地に結合してよい。基準抵抗ベースメモリ素子214は、「低」抵抗( $R_L$ )を有する第1の抵抗器260を、「高」抵抗( $R_H$ )を有する第2の抵抗器262と直列に含んでよい。低抵抗( $R_L$ )は論理「0」値に対応してよく、高抵抗は論理「1」値に対応してよい。基準抵抗ベースメモリ素子214は、「低」抵抗( $R_L$ )を有する第3の抵抗器264も、「高」抵抗( $R_H$ )を有する第4の抵抗器266と直列に含んでよい。第1および第2の抵抗器260、262は第3および第4の抵抗器264、266と並列に結合してよく、基準抵抗ベースメモリ素子214の全抵抗( $R_{Ref}$ )は低抵抗( $R_L$ )と高抵抗( $R_H$ )の合計の半分にほぼ等しくなる。

#### 【0030】

検知回路202は第1のクランプトランジスタ251、第1の負荷トランジスタ252、第1のソース縮退トランジスタ253、第2のクランプトランジスタ254、第2の負荷トランジスタ255、および第2のソース縮退トランジスタ256などの、プロセス変動による電圧オフセットに寄与してよい1つまたは複数の構成要素を含んでよい。第1および第2のソース縮退トランジスタ253、256はシステム電源(Vdd)に結合してよい。特定の実施形態において、クランプトランジスタ251は、254はNMOSトランジスタであり、負荷およびソース縮退トランジスタ252、253、255、256はPMOSトランジスタである。第1の検知経路240は第1のクランプトランジスタ251、第1の負荷トランジスタ252、および第1のソース縮退トランジスタ253を含んでよい。第2の検知経路242は第2のクランプトランジスタ254、第2の負荷トランジスタ255、および第2のソース縮退トランジスタ256を含んでよい。

#### 【0031】

選択トランジスタ222～228は、第1の検知段階の間、第1の検知経路240をプログラマブル抵抗ベースメモリ素子212に結合するようにかつ第2の検知経路242を基準抵抗ベースメモリ素子214に結合するように構成可能である。たとえば選択信号Sel(1)～Sel(4)は、第1および第2の検知経路240、242をそれぞれプログラマブルおよび基準抵抗ベースメモリ素

10

20

30

40

50

子212、214に結合するために、選択トランジスタ222～228を選択的に有効化および無効化してよい。同様に、選択トランジスタ222～228はさらに、第2の検知段階の間、第1の検知経路240を基準抵抗ベースメモリ素子214に結合するようにかつ第2の検知経路242をプログラマブル抵抗ベースメモリ素子212に結合するように構成可能である。特定の実施形態において、選択トランジスタ222～228は検知経路選択マルチプレクサ(図示せず)に含まれる。

### 【 0 0 3 2 】

検知回路202は、データ電圧を生成するためにデータセル204の状態を検知するように構成される。検知回路202はデータセル204の第1の状態を第1の検知段階の間に第1の検知経路240を用いて検知してよい。たとえば検知回路202は、データセル204のプログラマブル抵抗ベースメモリ素子212に流れる電流を検知し、第1の負荷トランジスタ252を用いて電流に基づいて第1のデータ電圧を生成してよい。検知回路202はデータセル204の第2の状態も第2の検知段階の間に第2の検知経路242を用いて検知してよい。たとえば検知回路202は、データセル204のプログラマブル抵抗ベースメモリ素子212に流れる電流を検知し、第2の負荷トランジスタ255を用いて電流に基づいて第2のデータ電圧を生成してよい。以下に説明するように、データ電圧は第1のデータ電圧と第2のデータ電圧の平均に基づいてよい。

### 【 0 0 3 3 】

検知回路202はさらに、基準電圧を生成するために基準セル206の状態を検知するように構成される。検知回路202は基準セル206の第1の状態を第1の検知段階の間に第2の検知経路242を用いて検知してよい。たとえば検知回路202は、基準セル206の基準抵抗ベースメモリ素子214に流れる電流を検知し、第2の負荷トランジスタ255を用いて電流に基づいて第1の基準電圧を生成してよい。検知回路202は基準セル206の第2の状態も第2の検知段階の間に第1の検知経路240を用いて検知してよい。たとえば検知回路202は、基準セル206の基準抵抗ベースメモリ素子214に流れる電流を検知し、第1の負荷トランジスタ252を用いて電流に基づいて第2の基準電圧を生成してよい。以下に説明するように、基準電圧は第1の基準電圧と第2の基準電圧の平均に基づいてよい。

### 【 0 0 3 4 】

スイッチトキャパシタ回路208は第1のコンデンサ232、第2のコンデンサ234、第3のコンデンサ236、および第4のコンデンサ238を含む。第1のコンデンサ232の正端子は検知回路202に第1のスイッチSw(1)を介して選択的に結合し、センスアンプ210の第1の入力に第5のスイッチSw(5)を介して選択的に結合してよい。第1のコンデンサ232の負端子は接地に結合してよい。第2のコンデンサ234の正端子は検知回路202に第2のスイッチSw(2)を介して選択的に結合し、センスアンプ210の第2の入力に結合してよい。第2のコンデンサ234の負端子は接地に結合してよい。第1および第2のスイッチSw(1)、Sw(2)は検知回路202の第1の検知経路240に結合してよい。第3のコンデンサ236の正端子は検知回路202に第3のスイッチSw(3)を介して選択的に結合し、センスアンプ210の第2の入力に第6のスイッチSw(6)を介して選択的に結合してよい。第3のコンデンサ236の負端子は接地に結合してよい。第4のコンデンサ238の正端子は検知回路202に第4のスイッチSw(4)を介して選択的に結合し、センスアンプ210の第1の入力に結合してよい。第4のコンデンサ238の負端子は接地に結合してよい。第3および第4のスイッチSw(3)、Sw(4)は検知回路202の第2の検知経路242に結合してよい。

### 【 0 0 3 5 】

第1のコンデンサ232は、データセル204の第1の状態(すなわち、プログラマブル抵抗ベースメモリ素子212の抵抗( $R_{data}$ ))が第1の検知経路240を用いて検知されるときに検知回路202で生成される第1のデータ電圧を記憶するように構成される。たとえば第1の検知段階の間、第1のスイッチSw(1)は有効化してよく、第2のスイッチSw(2)は無効化してよい。第1のスイッチSw(1)を有効化することに応じて、検知回路202は第1のコンデンサ232を第1のデータ電圧に基づいて充電してよい。第2のコンデンサ234は、基準セル206の第2の状態(すなわち、基準抵抗ベースメモリ素子214の抵抗( $R_{ref}$ )))が第1の検知経路240を用いて検

10

20

30

40

50

知されるときに検知回路202で生成される第2の基準電圧を記憶するように構成される。たとえば第2の検知段階の間、第2のスイッチSw(2)は有効化してよく、第1のスイッチSw(1)は無効化してよい。第2のスイッチSw(2)を有効化することに応じて、検知回路202は第2のコンデンサ234を第2の基準電圧に基づいて充電してよい。

#### 【 0 0 3 6 】

第3のコンデンサ236は、基準セル206の第1の状態(すなわち、基準抵抗ベースメモリ素子214の抵抗( $R_{Ref}$ ))が第2の検知経路242を用いて検知されるときに検知回路202で生成される第1の基準電圧を記憶するように構成される。たとえば第1の検知段階の間、第3のスイッチSw(3)は有効化してよく、第4のスイッチSw(4)は無効化してよい。第3のスイッチSw(3)を有効化することに応じて、検知回路202は第3のコンデンサ236を第1の基準電圧に基づいて充電してよい。第4のコンデンサ238は、データセル204の第2の状態(すなわち、プログラマブル抵抗ベースメモリ素子212の抵抗( $R_{data}$ ))が第2の検知経路242を用いて検知されるときに検知回路202で生成される第2のデータ電圧を記憶するように構成される。たとえば第2の検知段階の間、第4のスイッチSw(4)は有効化してよく、第3のスイッチSw(3)は無効化してよい。第4のスイッチSw(4)を有効化することに応じて、検知回路202は第4のコンデンサ238を第2のデータ電圧に基づいて充電してよい。10

#### 【 0 0 3 7 】

第1および第2のデータ電圧の平均を、データ電圧を生成するために求めてよい。たとえば第1および第4のコンデンサ232、238がそれぞれ第1および第2のデータ電圧に基づいて充電された後、第5のスイッチSw(5)が有効化する。第1および第2のデータ電圧の平均(すなわち、データ電圧)は、第5のスイッチSw(5)が有効化されるときに電荷共有によって生成してよい。データ電圧はセンスアンプ210の第1の入力に提供される。同様に、第1および第2の基準電圧の平均を、基準電圧を生成するために求めてよい。たとえば第2および第3のコンデンサ234、236がそれぞれ第2および第1の基準電圧に基づいて充電された後、第6のスイッチSw(6)が有効化する。第1および第2の基準電圧の平均(すなわち、基準電圧)は、第6のスイッチSw(6)が有効化されるときに電荷共有によって生成してよい。基準電圧はセンスアンプ210の第2の入力に提供される。20

#### 【 0 0 3 8 】

センスアンプ210はデータ電圧および基準電圧に基づいてデータセル204の論理値を求めるように構成される。たとえばセンスアンプイネーブル信号(SAE)に応じて、センスアンプ210はデータ電圧を基準電圧と比較してよい。データセル204の論理値は、データ電圧が基準電圧よりも低い場合、第1の値(すなわち、論理「0」値)に対応してよい。データセル204の論理値は、データ電圧が基準電圧よりも高い場合、第2の値(すなわち、論理「1」値)に対応してよい。30

#### 【 0 0 3 9 】

動作の間メモリシステム200は、データセル204の状態と基準セル206の状態を検知するために共通の検知経路(すなわち、第1の検知経路240および第2の検知経路242)を使用する。たとえば第1の検知段階の間、検知経路選択マルチプレクサは第1の選択トランジスタ222と第4の選択トランジスタ228を有効化し、検知回路202はデータセル204の第1の状態と基準セル206の第1の状態をそれぞれ検知する。第1の検知経路240はデータセル204の第1の状態を検知するために使用され、第2の検知経路242は基準セル206の第1の状態を検知するために使用される。第2の検知段階の間、検知経路選択マルチプレクサは第2の選択トランジスタ224と第3の選択トランジスタ226を有効化し、検知回路202は基準セル206の第2の状態とデータセル204の第2の状態をそれぞれ検知する。第1の検知経路240は基準セル206の第2の状態を検知するために使用され、第2の検知経路242はデータセル204の第2の状態を検知するために使用される。40

#### 【 0 0 4 0 】

第1および第3のコンデンサ232、236は第1の検知段階の間、それぞれ第1のデータ電圧および第1の基準電圧に基づいて充電される。第2および第4のコンデンサ234、238は第2の検知段階の間、それぞれ第2の基準電圧および第2のデータ電圧に基づいて充電される。第250

の検知段階の後、第5および第6のスイッチSw(5)、Sw(6)はそれぞれ第1および第4のコンデンサ232、238の電荷間の電荷共有および第2および第3のコンデンサ234、236の電荷間の電荷共有を引き起こすように有効化される。データ電圧と基準電圧は共有電荷に基づいて生成される。データセル204の論理値はセンスアンプ210によってデータ電圧および基準電圧に基づいて求められる。

#### 【0041】

図2のメモリシステム200は第1および第2の検知経路240、242の構成要素のプロセス変動による電圧オフセットを除去または低減し得ることが認識されるであろう。たとえばデータ電圧と基準電圧を求めるために第1の検知経路240を利用するることは、そうでなければ、もっぱらデータ電圧を求めるために第1の検知経路240を使用する場合に存在するであろう電圧オフセットを排除または低減し得る。適用の際、第1の検知段階の間に第1および第2の検知経路240、242の構成要素のプロセス変動による任意の電圧オフセットは第2の検知段階の間に低減または相殺し得るので、データセル204の論理値を求める際の誤差を低減し得る。電圧オフセットを相殺することは検知回路202の検知マージンを増大し得るし、より小さいセンス電流の利用を可能にし得る。例示として、検知マージンを増大させる結果として、センス電流はおよそ200マイクロアンペアからおよそ20マイクロアンペアへ低減し得る。より小さいセンス電流を利用することは、検知動作の間のプログラマブル抵抗ベースメモリ素子212の読み出しディスタンスを低減または排除し得る。

10

#### 【0042】

図3を参照すると、多段階プロセスを用いてデータセルの値を読み出す方法300の特定の実施形態のフローチャートを示す。例示的な実施形態において、方法300は図1のメモリシステム100、図2のメモリシステム200、またはそれらの任意の組合せを用いて実施してよい。

20

#### 【0043】

方法300は、302で、データ電圧を生成するためにデータセルの状態を検知することを含む。たとえば図1では、検知回路102はデータセル104のプログラマブル抵抗ベースメモリ素子112に流れる電流を検知し、負荷トランジスタ130を用いて電流に基づいてデータ電圧を生成してよい。電流はプログラマブル抵抗ベースメモリ素子112の抵抗( $R_{data}$ )に反比例してよい。データセル104の状態はプログラマブル抵抗ベースメモリ素子112の抵抗( $R_{data}$ )(すなわち、状態)に対応してよい。別の例として図2では、検知回路202はデータセル204の第1の状態を第1の検知段階の間に第1の検知経路240を用いて検知してよい。たとえば検知回路202は、データセル204のプログラマブル抵抗ベースメモリ素子212に流れる電流を検知し、第1の負荷トランジスタ252を用いて電流に基づいて第1のデータ電圧を生成してよい。検知回路202はデータセル204の第2の状態も第2の検知段階の間に第2の検知経路242を用いて検知してよい。たとえば検知回路202は、データセル204のプログラマブル抵抗ベースメモリ素子212に流れる電流を検知し、第2の負荷トランジスタ255を用いて電流に基づいて第2のデータ電圧を生成してよい。データセル204の状態はプログラマブル抵抗ベースメモリ素子212の抵抗( $R_{data}$ )に対応してよい。

30

#### 【0044】

304で、基準電圧を生成するために基準セルの状態を検知してよい。たとえば図1では、検知回路102は、第1の基準電圧を生成するために基準セル106の第1の状態を第2の検知段階の間に検知してよい。検知回路102は、基準セル106の第1の抵抗ベースメモリ素子114に流れる電流を検知し、負荷トランジスタ130を用いて電流に基づいて第1の基準電圧を生成してよい。検知回路102は第2の基準電圧を生成するために基準セル106の第2の状態も第3の検知段階の間に検知する。たとえば検知回路102は、基準セル106の第2の抵抗ベースメモリ素子116に流れる電流を検知し、負荷トランジスタ130を用いて電流に基づいて第2の基準電圧を生成してよい。データセル104の状態と基準セル106の状態は共通の検知経路を介して検知される。基準電圧は第1の基準電圧と第2の基準電圧の平均に基づいてよい。

40

#### 【0045】

別の例として図2では、検知回路202は基準セル206の第1の状態を第1の検知段階の間に

50

第2の検知経路242を用いて検知してよい。たとえば検知回路202は、基準セル206の基準抵抗ベースメモリ素子214に流れる電流を検知し、第2の負荷トランジスタ255を用いて電流に基づいて第1の基準電圧を生成してよい。検知回路202は基準セル206の第2の状態も第2の検知段階の間に第1の検知経路240を用いて検知してよい。たとえば検知回路202は、基準セル206の基準抵抗ベースメモリ素子214に流れる電流を検知し、第1の負荷トランジスタ252を用いて電流に基づいて第2の基準電圧を生成してよい。データセル204の状態と基準セル206の状態は共通の検知経路240、242を介して検知される。基準電圧は第1の基準電圧と第2の基準電圧の平均に基づいてよい。

#### 【 0 0 4 6 】

306で、論理値をデータ電圧および基準電圧に基づいて求めてよい。たとえば図1では、センスアンプ110はデータ電圧および基準電圧に基づいてデータセル104の論理値を求めてよい。たとえばセンスアンプ110はデータ電圧を基準電圧と比較してよい。データセル104の論理値は、データ電圧が基準電圧よりも低い場合、第1の値(すなわち、論理「0」値)に対応してよい。データセル104の論理値は、データ電圧が基準電圧よりも高い場合、第2の値(すなわち、論理「1」値)に対応してよい。図2のセンスアンプ210は図1のセンスアンプ110と実質的に同様の方法で動作する。

#### 【 0 0 4 7 】

図3の方法300は、検知経路の1つまたは複数の構成要素のプロセス変動によるデータ電圧への影響を、論理値を求める際のプロセス変動による基準電圧への影響によって、少なくとも部分的に相殺し得ることが認識されるであろう。たとえば図1では、共通の負荷トランジスタ130およびクランプトランジスタ129を3つの異なる段階で利用することによって、データ電圧と基準電圧を生成してよく、そうでなければ別の負荷およびクランプトランジスタを使用することから発生するであろう電圧オフセットは低減または相殺し得る。別の例として図2では、第1の検知段階の間の第1および第2の検知経路240、242の構成要素のプロセス変動による任意の電圧オフセットは第2の検知段階の間に低減または相殺し得るので、データセル204の論理値を求める際の誤差を低減し得る。

#### 【 0 0 4 8 】

図4を参照すると、電圧オフセットを低減するために多段階プロセスを用いてデータセルの値を読み出すように動作可能である構成要素を含むワイヤレスデバイス400のプロック図を示す。デバイス400は、メモリ432に結合される、デジタル信号プロセッサ(DSP)などのプロセッサ410を含む。

#### 【 0 0 4 9 】

図4また、プロセッサ410とディスプレイ428とに結合されるディスプレイコントローラ426を示す。コーダ/デコーダ(CODEC)434もプロセッサ410に結合できる。スピーカ436とマイクロホン438をCODEC434に結合できる。図4はまた、ワイヤレスコントローラ440がプロセッサ410に、およびワイヤレスコントローラ440とアンテナ442との間に設けられる無線周波数(RF)インターフェース490を介してアンテナ442に結合できることを示す。

#### 【 0 0 5 0 】

メモリ432は検知回路402、データセル404、基準セル406、スイッチトキャパシタ回路408、およびセンスアンプ(SA)490を含んでよい。検知回路402は図1の検知回路102または図2の検知回路202に相当してよい。データセル404は検知回路402に結合してよい。データセル404は図1のデータセル104または図2のデータセル204に相当してよい。基準セル406も検知回路402に結合してよい。基準セル406は図1の基準セル106または図2の基準セル206に相当してよい。スイッチトキャパシタ回路408は図1のスイッチトキャパシタ回路108または図2のスイッチトキャパシタ回路208に相当してよい。センスアンプ(SA)490はスイッチトキャパシタ回路408に結合してよい。センスアンプ(SA)490は図1のセンスアンプ110または図2のセンスアンプ210に相当してよい。

#### 【 0 0 5 1 】

メモリ432は実行可能命令456を含む記憶デバイスであってよい。特定の実施形態において

10

20

30

40

50

て、命令456は有形の非一時的プロセッサ可読記憶媒体に記憶されてよく、データセルへの検知回路の結合を可能にするためにプロセッサ410などのプロセッサによって実行されてよい。たとえばプロセッサ410は、第1の検知段階の間、検知回路102とプログラマブル抵抗ベースメモリ素子112とに結合される図1のデータ選択トランジスタ124のゲートに選択的にバイアスをかけてよい。データセル104の状態は、データ電圧を生成するために検知回路102とデータセル104との間の導通に基づいて検知してよい。別の例として、プロセッサ410は、第1のデータ電圧を生成するために第1の検知段階の間、第1の検知経路240とデータセル204とに結合される図2の第1の選択トランジスタ222のゲートに選択的にバイアスをかけてよい。プロセッサ410はまた、第2のデータ電圧を生成するために第2の検知段階の間、第2の検知経路242とデータセル204とに結合される第3の選択トランジスタ226のゲートに選択的にバイアスをかけてよい。10

#### 【 0 0 5 2 】

命令456はまた、基準セルへの検知回路の結合を可能にするためにプロセッサ410によって実行可能であってよい。たとえばプロセッサ410は、第1の基準電圧を生成するために第2の検知段階の間、検知回路102と基準セル106の第1の抵抗ベースメモリ素子114とに結合される図1の第1の選択トランジスタ126のゲートに選択的にバイアスをかけてよい。プロセッサ410はまた、第2の基準電圧を生成するために第3の検知段階の間、検知回路102と基準セル106の第2の抵抗ベースメモリ素子116とに結合される第2の選択トランジスタ128のゲートに選択的にバイアスをかけてよい。別の例として、プロセッサ410は、第1の基準電圧を生成するために第1の検知段階の間、第2の検知経路242と基準セル206とに結合される図2の第4の選択トランジスタ228のゲートに選択的にバイアスをかけてよい。20 プロセッサ410はまた、第2の基準電圧を生成するために第2の検知段階の間、第1の検知経路240と基準セル206とに結合される第2の選択トランジスタ224のゲートに選択的にバイアスをかけてよい。

#### 【 0 0 5 3 】

命令456はまた、データ電圧および基準電圧に基づいてデータセルの論理値を求めるためにプロセッサ410によって実行可能であってよい。たとえば図1では、プロセッサ410は、センスアンプ110を有効化するためにセンスアンプイネーブル信号(SAE)にバイアスをかけてよい。有効化時にセンスアンプ110はデータ電圧および基準電圧に基づいてデータセル104の論理値を求めてよい。たとえばセンスアンプイネーブル信号(SAE)に応じて、センスアンプ110はデータ電圧を基準電圧と比較してよい。別の特定の実施形態において、プロセッサ410は、センスアンプ110とは独立してデータ電圧および基準電圧に基づいてデータセル104の論理値を求めてよい。プロセッサ410は図2のデータセル204の論理値を求めるときに、実質的に同様に機能してよい。30

#### 【 0 0 5 4 】

命令456はプロセッサ410に結合される代替のプロセッサ(図示せず)によって実行可能であってもよい。非限定的な例として、命令456は、図1の分岐選択マルチブレクサまたは図2の経路選択マルチブレクサに結合される、メモリ432のメモリコントローラ内などのプロセッサによって実行可能であってよい。

#### 【 0 0 5 5 】

特定の実施形態において、プロセッサ410、ディスプレイコントローラ426、メモリ432、CODEC434、およびワイヤレスコントローラ440はシステムインパッケージまたはシステムオンチップデバイス422に含まれる。特定の実施形態において、入力デバイス430と電源444がシステムオンチップデバイス422に結合される。その上特定の実施形態において、図4に例示するように、ディスプレイ428、入力デバイス430、スピーカ436、マイクロホン438、アンテナ442、および電源444はシステムオンチップデバイス422の外部である。しかしながら、ディスプレイ428、入力デバイス430、スピーカ436、マイクロホン438、アンテナ442、および電源444の各々は、インターフェースまたはコントローラなどのシステムオンチップデバイス422の構成要素に結合できる。

#### 【 0 0 5 6 】

10

20

30

40

50

説明した実施形態に関連して、装置は、データ電圧を生成するためにデータセルの状態を検知するための手段を含む。たとえばデータセルの状態を検知するための手段は、図1の検知回路102、図1のデータセル選択トランジスタ124、図1のデータセル104、図2の検知回路202、図2の第1の選択トランジスタ222、図2の第3の選択トランジスタ226、図2のデータセル204、図4の命令456を実行するようにプログラムされるプロセッサ410、またはデータセルの状態を検知する1つまたは複数の他のデバイス、回路、モジュール、もしくは命令を含んでよい。

#### 【 0 0 5 7 】

装置はまた、基準電圧を生成するために基準セルの状態を検知するための手段を含んでよい。たとえば基準セルの状態を検知するための手段は、図1の検知回路102、図1の第1の選択トランジスタ126、図1の基準セル106、図2の検知回路202、図2の第2の選択トランジスタ224、図2の第4の選択トランジスタ228、図2の基準セル206、図4の命令456を実行するようにプログラムされるプロセッサ410、または基準セルの状態を検知する1つまたは複数の他のデバイス、回路、モジュール、もしくは命令を含んでよい。10

#### 【 0 0 5 8 】

装置はまた、データ電圧および基準電圧に基づいてデータセルの論理値を求めるための手段を含んでよい。たとえばデータセルの論理値を求めるための手段は、図1の検知回路102、図1のスイッチトキャパシタ回路108、図1のセンスアンプ110、図2の検知回路202、図2のスイッチトキャパシタ回路208、図2のセンスアンプ210、図4の命令456を実行するようにプログラムされるプロセッサ410、またはデータセルの論理値を求める1つまたは複数の他のデバイス、回路、モジュール、もしくは命令を含んでよい。20

#### 【 0 0 5 9 】

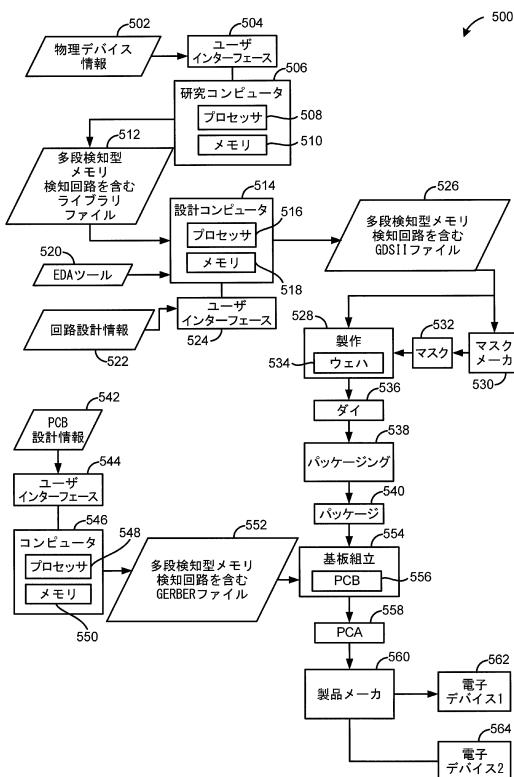

上記開示したデバイスや機能性は、コンピュータ可読媒体上に記憶されるコンピュータファイル(たとえばRTL、GDSII、GERBERなど)へ設計および構成してよい。一部のまたはすべてのそのようなファイルは、そのようなファイルに基づいてデバイスを製作する製作関係者に提供されてよい。得られる製品としては、次いで半導体ダイに切断されて半導体チップへパッケージングされる半導体ウェハが含まれる。チップは次いで上述のデバイスに採用される。図5は、電子デバイス製造プロセス500の特定の例示的な実施形態を描く。

#### 【 0 0 6 0 】

物理デバイス情報502が製造プロセス500にて、たとえば研究コンピュータ506で受入れられる。物理デバイス情報502は、図1のメモリシステム100の構成要素、図2のメモリシステム200の構成要素、またはそれらの任意の組合せを含むデバイスなどの半導体デバイスの少なくとも1つの物理的性質を表す設計情報を含んでよい。たとえば物理デバイス情報502は、研究コンピュータ506に結合されるユーザインターフェース504を介して入力される物理パラメータ、材料特性、および構造情報を含んでよい。研究コンピュータ506は、メモリ510などのコンピュータ可読媒体に結合される、1つまたは複数の処理コアなどのプロセッサ508を含む。メモリ510は、プロセッサ508に物理デバイス情報502をファイル形式に準拠して変換させ、ライブラリファイル512を生成させるように実行可能であるコンピュータ可読命令を記憶してよい。30

#### 【 0 0 6 1 】

特定の実施形態において、ライブラリファイル512は、変換された設計情報を含む少なくとも1つのデータファイルを含む。たとえばライブラリファイル512は、電子設計自動化(EDA)ツール520とともに用いるように提供される、図1のメモリシステム100の構成要素、図2のメモリシステム200の構成要素、またはそれらの任意の組合せを含む半導体デバイスのライブラリを含んでよい。40

#### 【 0 0 6 2 】

ライブラリファイル512は、メモリ518に結合される、1つまたは複数の処理コアなどのプロセッサ516を含む設計コンピュータ514で、EDAツール520に関連して使用してよい。EDAツール520は、設計コンピュータ514のユーザがライブラリファイル512のうちの、図1のメモリシステム100の構成要素、図2のメモリシステム200の構成要素、またはそれらの任50

意の組合せを含むデバイスを設計できるようにするために、プロセッサ実行可能命令としてメモリ518に記憶されてよい。たとえば設計コンピュータ514のユーザは、回路設計情報522を設計コンピュータ514に結合されるユーザインターフェース524を介して入力してよい。

#### 【 0 0 6 3 】

回路設計情報522は、図1のメモリシステム100の構成要素、図2のメモリシステム200の構成要素、またはそれらの任意の組合せを含む半導体デバイスの少なくとも1つの物理的性質を表す設計情報を含んでよい。例示として、回路設計性質としては、特定の回路および回路設計内の他の要素との関係の同定、位置情報、特徴サイズ情報、相互接続情報、または半導体デバイスの物理的性質を表す他の情報が含まれてよい。

10

#### 【 0 0 6 4 】

設計コンピュータ514は回路設計情報522を含む設計情報をファイル形式に準拠して変換するように構成してよい。例示として、ファイル形成は、グラフィックデータシステム(GDSII)ファイル形式などの、平面の幾何学的形状、テキストラベル、および他の回路レイアウトに関する情報を階層形式で表すデータベースバイナリファイル形式を含んでよい。設計コンピュータ514は変換された設計情報を含むデータファイル、たとえば図1のメモリシステム100の構成要素、図2のメモリシステム200の構成要素、またはそれらの任意の組合せを含み、かつSOC内の追加の電子回路および構成要素も含むデバイスを記述する情報を含むGDSIIファイル526を生成するように構成してよい。

#### 【 0 0 6 5 】

GDSIIファイル526は、図1のメモリシステム100の構成要素、図2のメモリシステム200の構成要素、またはそれらの任意の組合せを含む半導体デバイスをGDSIIファイル526内の変換された情報に従って製造する製作プロセス528で受入れられてよい。たとえばデバイス製造プロセスは、GDSIIファイル526を、代表的なマスク532として例示するフォトリソグラフィ処理で使用されるマスクなどの、1つまたは複数のマスクを作成するマスクメーカー530に提供することを含んでよい。マスク532は、試験されて代表的なダイ536などのダイに分離されてよい1つまたは複数のウェハ534を生成するために製作プロセスの間に使用してよい。ダイ536は、図1のメモリシステム100の構成要素、図2のメモリシステム200の構成要素、またはそれらの任意の組合せを含む回路を含む。

20

#### 【 0 0 6 6 】

ダイ536は、ダイ536が代表的なパッケージ540に組み込まれるパッケージングプロセス538に提供されてよい。たとえばパッケージ540は単一のダイ536、またはシステムインパッケージ(SiP)配置などの複数のダイを含んでよい。パッケージ540は電子素子技術連合評議会(JEDEC)規格などの1つまたは複数の規格または仕様に適合するように構成してよい。

30

#### 【 0 0 6 7 】

パッケージ540に関する情報は、コンピュータ546で記憶されるコンポーネントライブラリを介するなどして様々な製品設計者に配布されてよい。コンピュータ546は、メモリ550に結合される、1つまたは複数の処理コアなどのプロセッサ548を含んでよい。プリント回路基板(PCB)ツールが、コンピュータ546のユーザからユーザインターフェース544を介して受信されるPCB設計情報542を処理するために、プロセッサ実行可能命令としてメモリ550に記憶されてよい。PCB設計情報542は、回路基板上のパッケージングされる半導体デバイスの物理的位置決め情報を含んでよく、パッケージングされる半導体デバイスは、図1のメモリシステム100の構成要素、図2のメモリシステム200の構成要素、またはそれらの任意の組合せを含むデバイスを含むパッケージ540に相当する。

40

#### 【 0 0 6 8 】

コンピュータ546は、PCB設計情報542を変換して、回路基板上のパッケージングされる半導体デバイスの物理的位置決め情報、およびトレースやビアなどの電気的接続のレイアウトを含むデータを備えるGERBERファイル552などのデータファイルを生成するように構成してよく、ここでパッケージングされる半導体デバイスは、図1のメモリシステム100の構成要素、図2のメモリシステム200の構成要素、またはそれらの任意の組合せを含むパッ

50

ケージ540に相当する。他の実施形態において、変換されるPCB設計情報によって生成されるデータファイルはGERBER形式以外の形式を有してよい。

#### 【 0 0 6 9 】

GERBERファイル552は基板組立プロセス554で受け入れられ、GERBERファイル552内に記憶される設計情報に従って製造される、代表的なPCB556などのPCBを作成するために使用されてよい。たとえばGERBERファイル552は、PCB生産プロセスの様々なステップを行うために1つまたは複数の機械にアップロードされてよい。PCB556は、代表的なプリント回路アセンブリ(PCA)558を形成するために、パッケージ540を含む電子構成要素が装着されてよい。

#### 【 0 0 7 0 】

PCA558は製品製造プロセス560で受け入れられ、第1の代表的な電子デバイス562や第2の代表的な電子デバイス564などの1つまたは複数の電子デバイスに統合されてよい。例示的な非限定的な例として、第1の代表的な電子デバイス562、第2の代表的な電子デバイス564、または両者は、図1のメモリシステム100の構成要素、図2のメモリシステム200の構成要素、またはそれらの任意の組合せが統合されるセットトップボックス、音楽プレーヤ、ビデオプレーヤ、娛樂ユニット、ナビゲーションデバイス、通信デバイス、携帯情報端末(PDA)、固定位置データユニット、およびコンピュータの群から選択されてよい。別の例示的な非限定的な例として、電子デバイス562および564の1つまたは複数は、モバイル電話機などの遠隔ユニット、ハンドヘルドパーソナル通信システム(PCS)ユニット、携帯情報端末などの携帯型データユニット、全地球側位システム(GPS)対応デバイス、ナビゲーションデバイス、検針機器などの固定位置データユニット、またはデータもしくはコンピュータ命令を記憶もしくは取得する任意の他のデバイス、またはそれらの任意の組合せであってよい。本開示の教示に係る遠隔ユニットに加えて、本開示の実施形態はメモリとオンチップ回路とを含むアクティブ集積回路を含む任意のデバイスに適宜採用してよい。

#### 【 0 0 7 1 】

図1のメモリシステム100の構成要素、図2のメモリシステム200の構成要素、またはそれらの任意の組合せを含むデバイスが、例示的なプロセス500で説明したように、製作され、処理され、かつ電子デバイスに組み込まれてよい。図1～図4に関して開示した実施形態の1つまたは複数の態様が、ライブラリファイル512、GDSIIファイル526、およびGERBERファイル552内など様々な処理段階で含まれてよいのと同様に、研究コンピュータ506のメモリ510、設計コンピュータ514のメモリ518、コンピュータ546のメモリ550、基板組立プロセス554でなど様々な段階で使用される1つまたは複数の他のコンピュータまたはプロセッサ(図示せず)のメモリに記憶され、さらにマスク532、ダイ536、パッケージ540、PCA558、プロトタイプ回路もしくはデバイス(図示せず)などの他の製品、またはそれらの任意の組合せなどの、1つまたは複数の他の物理的な実施形態に組み込まれてよい。物理デバイス設計から最終製品まで生産の様々な代表的な段階が描かれるが、他の実施形態においてより少ない段階を使用してよいし、または追加の段階が含まれてよい。同様に、プロセス500は単一の実体によってまたはプロセス500の様々な段階を行う1つまたは複数の実体によって行われてよい。

#### 【 0 0 7 2 】

当業者は、本明細書に開示した実施形態に関する説明した様々な例示的な論理プロック、構成、モジュール、回路、およびアルゴリズムステップは、電子ハードウェア、プロセッサによって実行されるコンピュータソフトウェア、または両者の組合せとして実装されてよいことをさらに理解するであろう。様々な例示的な構成要素、プロック、構成、モジュール、回路、およびステップを概してこれらの機能性の観点から上記に説明した。そのような機能性がハードウェアまたはプロセッサ実行可能命令として実装されるかはシステム全体に課される特定の用途および設計制約に依存する。当業者は説明した機能性を各特定の用途のために様々な方法で実装してよいが、そのような実装の決定は本開示の範囲からの逸脱を引き起こすと解釈されるべきではない。

#### 【 0 0 7 3 】

10

20

30

30

40

50

本明細書に開示した実施形態に関連して説明した方法またはアルゴリズムのステップは、直接ハードウェアで、プロセッサによって実行されるソフトウェアモジュールで、またはその2つの組合せで具現化されてよい。ソフトウェアモジュールはランダムアクセスメモリ(RAM)、フラッシュメモリ、リードオンリーメモリ(ROM)、プログラマブルリードオンリーメモリ(PROM)、消去可能プログラマブルリードオンリーメモリ(EPROM)、電気的消去可能プログラマブルリードオンリーメモリ EEPROM)、レジスタ、ハードディスク、リムーバブルディスク、コンパクトディスククリードオンリーメモリ(CD-ROM)、または当該技術分野で公知の任意の他の形態の非一時的記憶媒体に常駐してよい。例示的な記憶媒体は、プロセッサが記憶媒体から情報を読み取り、そこに情報を書き込めるようにプロセッサに結合される。代替策では、記憶媒体はプロセッサと一体であってよい。プロセッサおよび記憶媒体は特定用途向け集積回路(ASIC)に常駐してよい。ASICはコンピューティングデバイスまたはユーザ端末に常駐してよい。代替策では、プロセッサおよび記憶媒体は別個の構成要素としてコンピューティングデバイスまたはユーザ端末に常駐してよい。

#### 【0074】

開示した実施形態の先の説明は、当業者が開示した実施形態を作製または使用できるようするために提供される。これらの実施形態への様々な変更は当業者には容易に明らかであろうし、本明細書に定めた原理は本開示の範囲から逸脱することなく他の実施形態に適用してよい。したがって本開示は本明細書に示した実施形態に限定されることを意図するものではなく、以下の特許請求の範囲によって定められる原理および新規な特徴と一致する可能限りの広範囲を与えられるべきである。

#### 【符号の説明】

#### 【0075】

|     |                   |    |

|-----|-------------------|----|

| 100 | メモリシステム           |    |

| 102 | 検知回路              |    |

| 104 | データセル             |    |

| 106 | 基準セル              |    |

| 108 | スイッチトキャバシタ回路      |    |

| 110 | センスアンプ            |    |

| 112 | プログラマブル抵抗ベースメモリ素子 |    |

| 114 | 第1の抵抗ベースメモリ素子     | 30 |

| 116 | 第2の抵抗ベースメモリ素子     |    |

| 118 | データセルアクセストランジスタ   |    |

| 120 | 第1のアクセストランジスタ     |    |

| 122 | 第2のアクセストランジスタ     |    |

| 124 | データセル選択トランジスタ     |    |

| 126 | 第1の選択トランジスタ       |    |

| 128 | 第2の選択トランジスタ       |    |

| 129 | クランプトランジスタ        |    |

| 130 | 負荷トランジスタ          |    |

| 131 | ソース縮退トランジスタ       | 40 |

| 132 | データコンデンサ          |    |

| 134 | 第1のコンデンサ          |    |

| 136 | 第2のコンデンサ          |    |

| 150 | データ分岐             |    |

| 152 | 第1の基準分岐           |    |

| 154 | 第2の基準分岐           |    |

| 200 | メモリシステム           |    |

| 202 | 検知回路              |    |

| 204 | データセル             |    |

| 206 | 基準セル              | 50 |

|                 |                             |    |

|-----------------|-----------------------------|----|

| 208             | スイッチトキャパシタ回路                |    |

| 210             | センスアンプ                      |    |

| 212             | プログラマブル抵抗ベースメモリ素子           |    |

| 214             | 基準抵抗ベースメモリ素子                |    |

| 218             | データセルアクセストランジスタ             |    |

| 220             | 基準セルアクセストランジスタ              |    |

| 222             | 第1の選択トランジスタ                 | 10 |

| 224             | 第2の選択トランジスタ                 |    |

| 226             | 第3の選択トランジスタ                 |    |

| 228             | 第4の選択トランジスタ                 |    |

| 232             | 第1のコンデンサ                    |    |

| 234             | 第2のコンデンサ                    |    |

| 236             | 第3のコンデンサ                    |    |

| 238             | 第4のコンデンサ                    |    |

| 240             | 第1の検知経路                     |    |

| 242             | 第2の検知経路                     |    |

| 251             | 第1のクランプトランジスタ               |    |

| 252             | 第1の負荷トランジスタ                 |    |

| 253             | 第1のソース縮退トランジスタ              |    |

| 254             | 第2のクランプトランジスタ               | 20 |

| 255             | 第2の負荷トランジスタ                 |    |

| 256             | 第2のソース縮退トランジスタ              |    |

| 260             | 第1の抵抗器                      |    |

| 262             | 第2の抵抗器                      |    |

| 264             | 第3の抵抗器                      |    |

| 266             | 第4の抵抗器                      |    |

| 400             | ワイヤレスデバイス                   |    |

| 402             | 検知回路                        |    |

| 404             | データセル                       |    |

| 406             | 基準セル                        | 30 |

| 408             | スイッチトキャパシタ回路                |    |

| 410             | プロセッサ                       |    |

| 422             | システムインパッケージまたはシステムオンチップデバイス |    |

| 426             | ディスプレイコントローラ                |    |

| 428             | ディスプレイ                      |    |

| 430             | 入力デバイス                      |    |

| 432             | メモリ                         |    |

| 434             | コーダ/デコーダ(CODEC)             |    |

| 436             | スピーカ                        |    |

| 438             | マイクロホン                      | 40 |

| 440             | ワイヤレスコントローラ                 |    |

| 442             | アンテナ                        |    |

| 444             | 電源                          |    |

| 456             | 実行可能命令                      |    |

| 490             | 無線周波数(RF)インターフェース           |    |

| 490             | センスアンプ(SA)                  |    |

| Vdd             | システム電源                      |    |

| Sel(0) ~ Sel(4) | 選択信号                        |    |

| Sw(0)           | データセルスイッチ                   |    |

| Sw(1)           | 第1のスイッチ                     | 50 |

- Sw(2) 第2のスイッチ

- Sw(3) 第3のスイッチ

- Sw(4) 第4のスイッチ

- Sw(5) 第5のスイッチ

- Sw(6) 第6のスイッチ

【図1】

【図2】

【図3】

【図4】

【図5】

---

フロントページの続き

(74)代理人 100163522

弁理士 黒田 晋平

(72)発明者 ソン・ウク・ジュン

大韓民国・ソウル・120-749・ソデムン・グ・シンチョン・ドン・134

(72)発明者 テフィ・ナ

大韓民国・ソウル・120-749・ソデムン・グ・シンチョン・ドン・134

(72)発明者 ジス・キム

大韓民国・ソウル・120-749・ソデムン・グ・シンチョン・ドン・134

(72)発明者 スン・エイチ・カン

アメリカ合衆国・カリフォルニア・92121-1714・サン・ディエゴ・モアハウス・ドライヴ・5775

(72)発明者 ジュン・ビル・キム

アメリカ合衆国・カリフォルニア・92121-1714・サン・ディエゴ・モアハウス・ドライヴ・5775

審査官 後藤 彰

(56)参考文献 特開2009-252276(JP,A)

特開2002-32983(JP,A)

米国特許出願公開第2009/0021976(US,A1)

(58)調査した分野(Int.Cl., DB名)

G 11 C 11/15 - 11/16

G 11 C 13/00