(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5911434号

(P5911434)

(45) 発行日 平成28年4月27日(2016.4.27)

(24) 登録日 平成28年4月8日(2016.4.8)

(51) Int.Cl.

H03F 3/50 (2006.01)

H03M 1/12 (2006.01)

F 1

H03F 3/50

H03M 1/12

A

請求項の数 19 (全 9 頁)

(21) 出願番号 特願2012-554996 (P2012-554996)

(86) (22) 出願日 平成22年12月22日 (2010.12.22)

(65) 公表番号 特表2013-531398 (P2013-531398A)

(43) 公表日 平成25年8月1日 (2013.8.1)

(86) 國際出願番号 PCT/US2010/061823

(87) 國際公開番号 WO2011/106071

(87) 國際公開日 平成23年9月1日 (2011.9.1)

審査請求日 平成25年12月12日 (2013.12.12)

(31) 優先権主張番号 482/CHE/2010

(32) 優先日 平成22年2月24日 (2010.2.24)

(33) 優先権主張国 インド (IN)

(31) 優先権主張番号 12/763,945

(32) 優先日 平成22年4月20日 (2010.4.20)

(33) 優先権主張国 米国 (US)

(73) 特許権者 390020248

日本テキサス・インスツルメンツ株式会社

東京都新宿区西新宿六丁目24番1号

(73) 特許権者 507107291

テキサス インスツルメンツ インコーポ

レイテッド

アメリカ合衆国 テキサス州 75265

-5474 ダラス メイル ステイショ

ン 3999 ピーオーボックス 655

474

(74) 上記1名の代理人 100098497

弁理士 片寄 恒三

最終頁に続く

(54) 【発明の名称】ソースフォロワ入力バッファ

## (57) 【特許請求の範囲】

## 【請求項 1】

バイアス回路であって、

信号電流を受け取るために入力信号の第1の部分(INM)を受け取る第1の静電容量

を有する第1のキャパシタと、

一対のカスコード接続トランジスタであって、前記第1のキャパシタが前記カスコード

接続トランジスタ間のノードに結合され、前記一対のカスコード接続トランジスタの第1

のカスコード接続トランジスタが第1のバイアス電圧を受け取り、前記一対のカスコード

接続トランジスタの第2のカスコード接続トランジスタが第2のバイアス電圧を受け取る

、前記一対のカスコード接続トランジスタと、

を有する、前記バイアス回路、

第2の静電容量を有するスイッチド・キャパシタ回路、及び

前記バイアス回路及び前記スイッチド・キャパシタ回路に結合されるソースフォロワバ

ッファであって、前記ソースフォロワバッファが、前記第2のバイアス電圧を受け取り、

前記入力信号の第2の部分(INP)を受け取り、前記ソースフォロワバッファが第3の

静電容量を有する第2のキャパシタを含み、第1の静電容量の組み合わされた前記第2及

び第3の静電容量に対する比が少なくとも1以上であり、前記ソースフォロワバッファが

前記信号電流をミラーする、前記ソースフォロワバッファ、

を含む、装置。

## 【請求項 2】

10

20

請求項 1 に記載の装置であって、

前記ソースフォロワバッファが、各々が前記バイアス回路に結合され、各々が前記入力信号の前記第 2 の部分 (I N P) を受け取る、複数のソースフォロワバッファを更に含む、装置。

【請求項 3】

請求項 1 に記載の装置であって、

前記第 1 のカスコード接続トランジスタが、そのゲートで前記第 1 のバイアス電圧を受け取る第 1 の N M O S トランジスタを更に含み、前記第 2 のカスコード接続トランジスタが、そのドレインで前記第 1 の N M O S トランジスタのソースに及びそのゲートで前記第 1 の N M O S トランジスタのドレインに結合される第 2 の N M O S トランジスタであり、

前記第 1 のキャパシタが前記第 2 の N M O S トランジスタのドレインに結合される、装置。

。

【請求項 4】

請求項 3 に記載の装置であって、

前記バイアス回路が、前記第 1 の N M O S トランジスタのドレインに結合される電流源を更に含む、装置。

【請求項 5】

請求項 4 に記載の装置であって、

前記ソースフォロワバッファが、

そのゲートで前記入力信号の前記第 2 の部分 (I N P) を受け取り、そのソースで前記第 2 のキャパシタに結合される第 3 の N M O S トランジスタ、及び

そのゲートで前記第 2 の N M O S トランジスタのゲートに結合され、そのドレインで前記第 3 の N M O S トランジスタのソースに結合される第 4 の N M O S トランジスタ、

を更に含む、装置。

【請求項 6】

請求項 5 に記載の装置であって、

前記第 3 の N M O S トランジスタのボディが前記第 2 のキャパシタに結合される、装置。

。

【請求項 7】

請求項 6 に記載の装置であって、

前記比が 10 : 1 である、装置。

【請求項 8】

請求項 1 に記載の装置であって、

前記スイッチド・キャパシタ回路がサンプルアンドホールド (S / H) 回路である、装置。

【請求項 9】

バイアス回路であって、

信号電流を受け取るために入力信号の第 1 の部分 (I N M) を受け取る第 1 の静電容量を有する第 1 のキャパシタと、

一対のカスコード接続トランジスタであって、前記第 1 のキャパシタが、前記カスコード接続トランジスタ間のノードに結合され、前記一対のカスコード接続トランジスタの第 1 のカスコード接続トランジスタが第 1 のバイアス電圧を受け取り、前記一対のカスコード接続トランジスタの第 2 のカスコード接続トランジスタが第 2 のバイアス電圧を受け取る、前記一対のカスコード接続トランジスタと、

を有する、前記バイアス回路、

前記第 2 のバイアス電圧を受け取るために前記バイアス回路に結合され、前記入力信号の第 2 の部分 (I N P) を受け取るソースフォロワバッファであって、第 2 の静電容量を有する第 2 のキャパシタを含み、前記信号電流をミラーする、前記ソースフォロワバッファ、

第 3 の静電容量を有する前記ソースフォロワバッファに結合される S / H 回路であって

10

20

30

40

50

、第1の静電容量の組み合わされた前記第2及び第3の静電容量に対する比が少なくとも1以上である、前記S/H回路、

前記S/H回路に結合されるアナログ・デジタル・コンバータ(ADC)パイプライン及び

前記S/H回路及び前記ADCパイプラインに結合されるクロック回路、

を含む、装置。

【請求項10】

請求項9に記載の装置であって、

前記ソースフォロワバッファが、各々が前記バイアス回路に結合され、各々が前記入力信号の前記第2の部分(INP)を受け取る複数のソースフォロワバッファを更に含み、

前記S/H回路が、各々が前記ソースフォロワバッファの少なくとも1つに結合される複数のS/H回路を更に含み、前記ADCパイプラインが、各々が前記S/H回路の少なくとも1つに結合される複数のADCパイプラインを更に含む、装置。 10

【請求項11】

請求項10に記載の装置であって、

前記装置が、各ADCパイプラインに結合されるマルチプレクサを更に含む、装置。

【請求項12】

請求項9に記載の装置であって、

前記第1のカスコード接続トランジスタが、そのゲートで前記第1のバイアス電圧を受け取る第1のN MOSトランジスタを更に含み、前記第2のカスコード接続トランジスタが、そのドレインで前記第1のN MOSトランジスタのソースに及びそのゲートで前記第1のN MOSトランジスタのドレインに結合される第2のN MOSトランジスタであり、

前記第1のキャパシタが前記第2のN MOSトランジスタのドレインに結合される、装置。

。

【請求項13】

請求項12に記載の装置であって、

前記バイアス回路が、前記第1のN MOSトランジスタのドレインに結合される電流源を更に含む、装置。

【請求項14】

請求項13に記載の装置であって、

前記ソースフォロワバッファが、

そのゲートで前記入力信号の前記第2の部分(INP)を受け取り、そのソースで前記第2のキャパシタに結合される第3のN MOSトランジスタ、及び

そのゲートで前記第2のN MOSトランジスタのゲートに結合され、そのドレインで前記第3のN MOSトランジスタのソースに結合される第4のN MOSトランジスタ、

を更に含む、装置。

【請求項15】

請求項14に記載の装置であって、

前記第3のN MOSトランジスタのボディが前記第2のキャパシタに結合される、装置。

。

【請求項16】

請求項15に記載の装置であって、

前記比が10:1である、装置。

【請求項17】

バイアス回路であって、

電流源と、

そのドレインで前記電流源に結合され、そのゲートでバイアス電圧を受け取る第1のN MOSトランジスタと、

そのドレインで前記第1のN MOSトランジスタのソースに結合され、そのゲートで前記第1のN MOSトランジスタのドレインに結合される第2のN MOSトランジスタと、 50

信号電流を受け取るために入力信号の第1の部分(INM)を受け取り、前記第2のN

MOSトランジスタのドレインに結合される第1の静電容量を有する第1のキャパシタと

、

を有する、前記バイアス回路、

複数のソースフォロワバッファであって、各ソースフォロワバッファが、

そのゲートで前記入力信号の第2の部分(INP)を受け取る第3のN MOSトランジ

スタと、

そのドレインで前記第3のN MOSトランジスタのソースに結合され、そのゲートで前

記第2のN MOSトランジスタのゲートに結合される第4のN MOSトランジスタと、

前記第3のN MOSキャパシタのソースに結合される第2の静電容量を有する第2のキ

ヤパシタと、

10

を含む、前記複数のソースフォロワバッファ、

複数のS / H回路であって、各S / H回路が、その第3のN MOSトランジスタのソ

ースで前記ソースフォロワバッファの少なくとも1つに結合され、各S / H回路が第3の静

電容量を有し、前記第1の静電容量の、各S / H回路及びその対応するソースフォロワバ

ッファにおける組み合わされた前記第2及び第3の静電容量に対する比が少なくとも1以

上であり、前記ソースフォロワバッファが前記信号電流をミラーする、前記複数のS / H

回路、

各ADCパイプラインが前記S / H回路の少なくとも1つに結合される、複数のADC

パイプライン、

20

各ADCパイプラインに結合されるマルチプレクサ、及び

各S / H回路及び各ADCパイプラインに結合されるクロック回路、

を含む、装置。

#### 【請求項18】

請求項17に記載の装置であって、

前記第3のN MOSトランジスタのボディが前記第2のキャパシタに結合される、装置

。

#### 【請求項19】

請求項18に記載の装置であって、

前記比が各々10:1である、装置。

30

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本願は、全般的にバッファに関し、更に特定して言えば、入力静電容量負荷が低減され

たソースフォロワバッファに関連する。

##### 【背景技術】

##### 【0002】

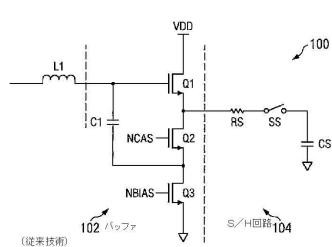

図1を参照すると、参考符号100はアナログ・デジタル・コンバータ(ADC)のため

の従来の入力回路を全般的に示す。回路100は、同時継続中の米国特許出願番号12

/199,804に全般的に説明されており、これはあらゆる目的のため参考としてここ

に組み込む。図示するように、回路100は全体として、送信媒体(インダクタL1で表

わす)、バッファ102、及びサンプルアンドホールド(S / H)回路104を含む。バ

ッファ102は、全体として、N MOSトランジスタQ1(これはインダクタL1に結合

される)、カスコード接続N MOSトランジスタQ2及びQ3(これらは、それぞれのゲ

ートでバイアス電圧N CAS及びN BIASを受け取る)、及びキャパシタC1を含む。

S / H回路102は全般的に(説明を簡潔にするため)、レジスタRS、サンプリングス

イッチSS、及びサンプリングキャパシタCSとして表される。

40

##### 【0003】

多くの従来のバッファでは、トランジスタQ1(これは一般的にソースフォロワである

)を駆動する「オフチップ」ドライバは、スイッチング負荷(これらはS / H回路104

50

の利用と共に存在する)ではなく継続的時間負荷を駆動する(和らげる)ことができる。この構成において、キャパシタC1(これは、一般的にキャパシタCSと同じ寸法である)は、(トランジスタQ2を用いて)負荷のための信号電流を供給し、ソースフォロワ(トランジスタQ1)は一般的にスイッチング負荷(S/H回路104)のための電圧を定めることができる。キャパシタC1は、それが「オフチップ」ドライバに負荷をかけるため、を小さく保つことが望ましい。これはトランジスタQ1も信号電流の一部を提供し得ることを意味し得る。小さなキャパシタC1の制約が加えられたこの構成は、スイッチング負荷を駆動することができない点で問題となり得るのみならず、更に、多数のS/H回路を駆動するため多くのバッファを用いる、インターリープされたADCに用いられるとき、インターリープされたADCのスプリアスフリーダイナミックレンジ(SFDR)に著しくかつ悪い影響を与える恐れがある。従って、性能が改善された回路が求められている。

#### 【0004】

幾つかの他の従来の回路は、米国特許番号第4,634,993号、米国特許番号第5,764,175号、米国特許番号第5,872,469号、米国特許番号第6,255,865号、米国特許番号第7,385,427号、米国特許公開番号20090206885、及びPCT公開番号WO07/093475に記載されている。

#### 【発明の概要】

#### 【0005】

従って、本発明の例示の一実施例は或る装置を提供する。この装置は、入力信号の第1の部分を受け取る第1の静電容量を有する第1のキャパシタと、一対のカスコード接続トランジスタであって、第1のキャパシタがカスコード接続トランジスタ間のノードに結合され、カスコード接続トランジスタ対の第1のカスコード接続トランジスタが第1のバイアス電圧を受け取り、カスコード接続トランジスタ対の第2のカスコード接続トランジスタが第2のバイアス電圧を受け取る、カスコード接続トランジスタ対とを有するバイアス回路、第2の静電容量を有するスイッチド・キャパシタ回路、及びバイアス回路及びスイッチド・キャパシタ回路に結合されるソースフォロワバッファであって、ソースフォロワバッファが、第2のバイアス電圧を受け取り、入力信号の第2の部分を受け取り、ソースフォロワバッファが、第3の静電容量を有する第2のキャパシタを含み、第1の静電容量に対する組み合わされた第2及び第3の静電容量の比が少なくとも1である、ソースフォロワバッファを含む。

#### 【0006】

本発明の例示の一実施例に従って、ソースフォロワバッファが、各々がバイアス回路に結合され、各々が入力信号の第2の部分を受け取る複数のソースフォロワバッファを更に含む。

#### 【0007】

本発明の例示の一実施例に従って、第1のカスコード接続トランジスタが、そのゲートで第1のバイアス電圧を受け取る第1のN MOSトランジスタを更に含み、第2のカスコード接続トランジスタが、そのドレインで第1のN MOSトランジスタのソースに及びそのゲートで第1のN MOSトランジスタのドレインに結合される第2のN MOSトランジスタであり、第1のキャパシタが第2のN MOSトランジスタのドレインに結合される。

#### 【0008】

本発明の例示の一実施例に従って、バイアス回路が、第1のN MOSトランジスタのドレインに結合される電流源を更に含む。

#### 【0009】

本発明の例示の一実施例に従って、ソースフォロワバッファが、そのゲートで入力信号の第2の部分を受け取り、そのソースで第2のキャパシタに結合される第3のN MOSトランジスタ、及びそのゲートで第2のN MOSトランジスタのゲートに結合され、そのドレインで第3のN MOSトランジスタのソースに結合される第4のN MOSトランジスタを更に含む。

10

20

30

40

50

## 【0010】

本発明の例示の一実施例に従って、第3のN M O Sトランジスタの本体(ボディ)が第2のキャパシタに結合される。

## 【0011】

本発明の例示の一実施例に従って、前記比が10:1である。

## 【0012】

本発明の例示の一実施例に従って、スイッチド・キャパシタ回路がサンプルアンドホールド(S/H)回路である。

## 【0013】

本発明の例示の一実施例に従って、或る装置が提供される。この装置は、入力信号の第1の部分を受け取る第1の静電容量を有する第1のキャパシタと、一対のカスコード接続トランジスタであって、第1のキャパシタがカスコード接続トランジスタ間のノードに結合され、カスコード接続トランジスタ対の第1のカスコード接続トランジスタが第1のバイアス電圧を受け取り、カスコード接続トランジスタ対の第2のカスコード接続トランジスタが第2のバイアス電圧を受け取る、カスコード接続トランジスタ対とを有するバイアス回路、第2のバイアス電圧を受け取り、入力信号の第2の部分を受け取るようにバイアス回路に結合されるソースフォロワバッファであって、第2の静電容量を有する第2のキャパシタを含むソースフォロワバッファ、第3の静電容量を有するソースフォロワバッファに結合されるS/H回路であって、第1の静電容量に対する組み合わされた第2及び第3の静電容量の比が少なくとも1であるS/H回路、S/H回路に結合されるアナログ・デジタル・コンバータ(ADC)パイプライン、及びS/H回路及びADCパイプラインに結合されるクロック回路を含む。10

## 【0014】

本発明の例示の一実施例に従って、ソースフォロワバッファが、各々がバイアス回路に結合され、各々が入力信号の第2の部分を受け取る複数のソースフォロワバッファを更に含み、S/H回路が、各々がソースフォロワバッファの少なくとも1つに結合される複数のS/H回路を更に含み、ADCパイプラインが、各々がS/H回路の少なくとも1つに結合される複数のADCパイプラインを更に含む。20

## 【0015】

本発明の例示の一実施例に従って、この装置が、各ADCパイプラインに結合されるマルチプレクサを更に含む。30

## 【0016】

本発明の例示の一実施例に従って或る装置が提供される。この装置は、電流源と、そのドレインで電流源に結合され、そのゲートでバイアス電圧を受け取る第1のN M O Sトランジスタと、そのドレインで第1のN M O Sトランジスタのソースに結合され、そのゲートで第1のN M O Sトランジスタのドレインに結合される第2のN M O Sトランジスタと、入力信号の第1の部分を受け取り、第2のN M O Sトランジスタのドレインに結合される第1の静電容量を有する第1のキャパシタとを有するバイアス回路、複数のソースフォロワバッファであって、各ソースフォロワバッファが、そのゲートで入力信号の第2の部分を受け取る第3のN M O Sトランジスタと、そのドレインで第3のN M O Sトランジスタのソースに結合され、そのゲートで第2のN M O Sトランジスタのゲートに結合される第4のN M O Sトランジスタと、第3のN M O Sキャパシタのソースに結合される第2の静電容量を有する第2のキャパシタとを含む、複数のソースフォロワバッファ、複数のS/H回路であって、各S/H回路が、その第3のN M O Sトランジスタのソースでソースフォロワバッファの少なくとも1つに結合され、各S/H回路が第3の静電容量を有し、各S/H回路及びその対応するソースフォロワバッファの、第1の静電容量に対する組み合わされた第2及び第3の静電容量の比が少なくとも1である、複数のS/H回路、各ADCパイプラインがS/H回路の少なくとも1つに結合される複数のADCパイプライン、各ADCパイプラインに結合されるマルチプレクサ、及び各S/H回路及び各ADCパイプラインに結合されるクロック回路を含む。40

## 【0017】

本発明の例示の一実施例に従って、第3のN M O Sトランジスタの本体が第2のキャパシタに結合される。

## 【0018】

例示の実施例を添付の図面を参照して説明する。

## 【図面の簡単な説明】

## 【0019】

【図1】図1は、A D Cのための従来の入力回路の回路図である。

## 【0020】

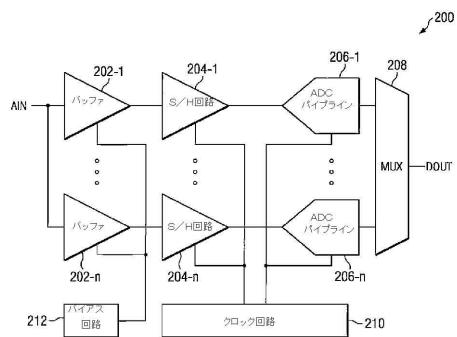

【図2】図2は、本発明の例示の一実施例に従ったインターリープされたA D Cのプロック図である。 10

## 【0021】

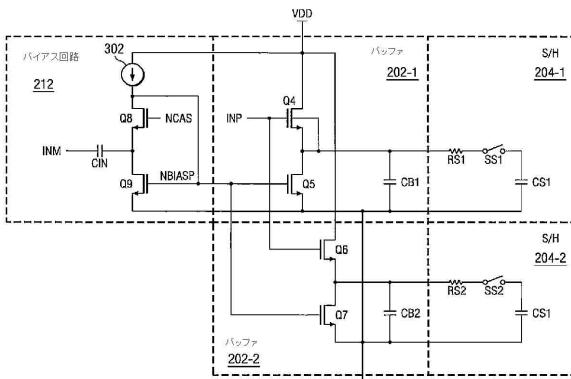

【図3】図3は、図2のA D Cの一部の回路図である。

## 【発明を実施するための形態】

## 【0022】

図2は、本発明の例示の一実施例に従った、インターリープされたアナログ・デジタル・コンバータ(A D C)200を図示する。オペレーションにおいて、アナログ入力信号A I Nが、バッファ202-1～202-n(これらは各々バイアス回路212に結合される)に供給される。各バッファ202-1～202-nからの出力は、対応するサンプルアンドホールド(S/H)回路204-1～204-nに結合され、入力信号A I Nがサンプリングされかつ変換のため対応するA D Cパイプライン206-1～206-nに供給され得るようにする。S/H回路204-1～204-n及びA D Cパイプライン206-1～206-nに結合されるクロック回路210が、入力信号A I Nをサンプリングし、それをデジタル信号に変換するため、タイミング信号を供給する。A D Cパイプライン206-1～206-nからのインターリープされたデジタル出力信号は、その後、マルチプレクサ(又はm u x)208により多重化されて、デジタル出力信号D O U Tを生成する。 20

## 【0023】

図3は、バイアス回路212、バッファ202-1及び202-2、及びS/H回路204-1及び204-2の更に詳細な図を提供する。簡潔にするため、2つのA D Cパイプラインに対する入力回路が示されている。また、簡潔にするため、S/H回路204-1及び204-2は、レジスタR1及びR2、サンプリングスイッチS S 1及びS S 2、及びサンプリングキャパシタC S 1及びC S 2で表す。バイアス回路212は、一般的にキャパシタC I N、N M O SトランジスタQ 8及びQ 9、及び電流源302を含む。バッファ202-1は、一般的にN M O SトランジスタQ 4及びQ 5、及びキャパシタC B 1を含み、バッファ202-2は、一般的にN M O SトランジスタQ 6及びQ 7、及びキャパシタC B 2を含む。 30

## 【0024】

オペレーションにおいて、入力信号A I Nの一部(I N P及びI N M)が、バイアス回路212及びバッファ202-1及び202-2に供給されて、入力信号A I NがS/H回路204-1及び204-2によりサンプリングされ得るようにする。電流源302は、N M O Sトランジスタ(これはそのゲートでバイアス電圧N C A Sを受け取る)のドレンに電流を供給し、N M O SトランジスタQ 9のゲートにバイアス電圧N B I A S Pを供給する。カスコード接続N M O SトランジスタQ 8及びQ 9間のノードにキャパシタC I Nを介して部分I N Mが供給される。これにより、接地からトランジスタQ 9及びキャパシタC I Nを介して信号電流が流れ得る。この信号電流は、キャパシタC B 1及びC B 2に供給され得るように、N M O SトランジスタQ 5及びQ 7の各々によりミラーされる。また、部分I N Pが、(各々ソースフォロワとして動作し)一般的に信号電流は供給しないN M O SトランジスタQ 4及びQ 6のゲートに供給される。そのため、この入力回路は、改善された線形性を備えてS/H回路204-1及び204-2に電圧及び電流を供 40

給することができる。

【0025】

キャパシタCIN、CB1、CB2、CS1、及びCS2の静電容量も全般的にスケーリングされる。典型的にキャパシタCB1及びCS1及びキャパシタCB2及びCS2の各々の組み合わされた静電容量は、キャパシタCIN（これは補償キャパシタとして動作する）の静電容量と少なくとも同じであるかそれより小さい。例えば、キャパシタCB1及びCS1の組み合わされた静電容量とキャパシタCINの静電容量との比は1:10であり得る。キャパシタCINは、他の従来の回路より非線形性の源を全般的になくすように、非常に低いインピーダンスノード（これは小さな非線形電圧を有する）に結合されることにも注意されたい。また、入力を介する信号電流が低減され、これは、高速で制約要件となり得る電磁干渉を低減するのにも役立つ。

10

【0026】

例示の実施例の文脈で説明したような特徴又は工程のすべて又はその幾つかを有する例示の実施例の文脈で説明した1つ又はそれ以上の特徴又は工程の異なる組み合わせを有する実施例も、本明細書に包含されることも意図している。当業者であれば、他の多くの実施例及び変形も特許請求の範囲に包含されることが理解されるであろう。

【図1】

【図2】

【図3】

---

フロントページの続き

(72)発明者 ニティン アガーワル

インド 560075 バンガロール, ジェイ ピー ナガール, ティンマ レディ コロニー, アシュラヤ アパートメント 206

(72)発明者 ヴィスヴェスヴァラヤ エイ ペンタコタ

インド 560093 バンガロール, ハル サード ステージ, サード クロス, ファースト メイン 2380

審査官 柳下 勝幸

(56)参考文献 特開平9-266419 (JP, A)

特開平11-177352 (JP, A)

米国特許出願公開第2009/0315594 (US, A1)

H. Rapakko, J. Kostamovaara, "On the Performance and Use of an Improved Source-Follower Buffer", IEEE Transactions on Circuits and Systems I: Regular Papers, 米国, IEEE, 2007年3月, Vol.54, No.3, pp.504-517

S.M. Louwsma, A.J.M. van Tuijl, M. Vertregt, B. Nauta, "A 1.35 GS/s, 10 b, 175 mW Time-Interleaved AD Converter in 0.13 μm CMOS", IEEE Journal of Solid-State Circuits, 米国, IEEE, 2008年4月, Vol. 43, No. 4, pp.778-786

(58)調査した分野(Int.Cl., DB名)

H 03 F 1/00 - 3/72

H 03 M 1/12

I E E E X p l o r e