(19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11)特許番号

特許第3612913号 (P3612913)

(45) 発行日 平成17年1月26日(2005.1.26)

(24) 登録日 平成16年11月5日 (2004.11.5)

(51) Int. C1. <sup>7</sup> F 1

HO1 L

21/8242

HO1 L

27/10

62 1 C

HO1 L

21/768

HO1 L

21/90

D

HO1 L

27/108

HO1 L

27/10

68 1 F

請求項の数 3 (全 20 頁)

(21) 出願番号 特願平8-358126

(22) 出願日 平成8年12月29日 (1996.12.29)

(65) 公開番号 特開平10-200065

(43) 公開日 平成10年7月31日 (1998.7.31) 審査請求日 平成15年2月21日 (2003.2.21) (73) 特許権者 000002185

ソニー株式会社

東京都品川区北品川6丁目7番35号

||(74) 代理人 100094053

弁理士 佐藤 隆久

(72) 発明者 黒田 英明

東京都品川区北品川6丁目7番35号 ソ

二一株式会社内

審査官 安田 雅彦

|(56) 参考文献 特開平O8-O3195O(JP,A)

特開平08-203997 (JP, A) 特開平10-178160 (JP, A) 特開平09-135005 (JP, A)

最終頁に続く

(54) 【発明の名称】半導体装置の製造方法

### (57)【特許請求の範囲】

#### 【請求項1】

層間絶縁膜に配線用溝を形成する工程と、

該配線用溝を導電性材料で埋める工程と、

前記導電性材料が埋められた前記配線溝中に第1の開口部を形成する工程と、

該第1の開口部の内周壁に導電性材料で構成されるサイドウオールを形成する工程と、

該サイドウオールをマスクとして第2の開口部を前記層間絶縁膜に形成する工程と、

該第2の開口部を導電性材料で埋め込む工程と、

該層間絶縁膜と該配線用溝を埋める導電性材料を平坦化して埋込配線層を形成する工程と

該埋込配線層を被覆する層間絶縁膜を形成する工程と

を有することを特徴とする半導体装置の製造方法。

## 【請求項2】

上記配線用溝が形成される層間絶縁膜がトランジスタ上に形成されている

請求項1記載の半導体装置の製造方法。

### 【請求項3】

上記埋込配線層がダイナミックランダムアクセスメモリのビット線を構成する 請求項1記載の半導体装置の製造方法。

#### 【発明の詳細な説明】

[0001]

### 【発明の属する技術分野】

本発明は、DRAM (Dynamic Random Access Memory)等の<u>半導体装置の製造方法</u>に関する。

#### [0002]

### 【従来の技術】

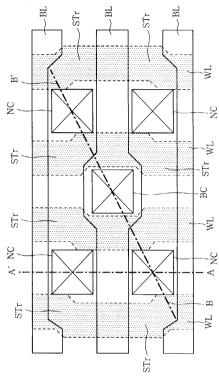

図23にCOB(Capacitor Over Bitline)型のDRAMセルの平面図を示す。選択トランジスタSTrのゲート電極WLが平行に配線され、これらの選択トランジスタSTrの拡散層とビットコンタクトBCで接続されたビット線BLがゲート電極WLと直交して配線されている。各選択トランジスタSTrの拡散層には図示しないキャパシタと接続されたノードコンタクトNCが設けられている。図のA-A'線に沿った断面図を図24に、図のB-B'線に沿った断面図を図38に示す。これらの断面図からわかるようにノードコンタクトNCは、いわゆる座布団付プラグで途中取り出しコンタクトを採用していると共に、このDRAMは、選択トランジスタSTrとキャパシタCAPとの間の層間絶縁膜にビット線が埋め込まれたCOB型である。また、図38の断面図は、DRAMセル部と一部周辺回路も示している。

#### [0003]

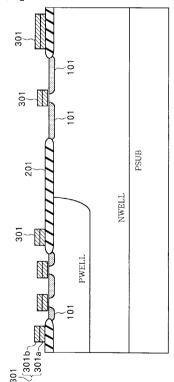

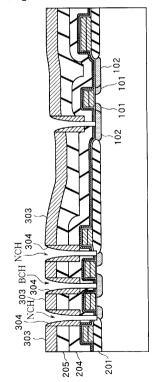

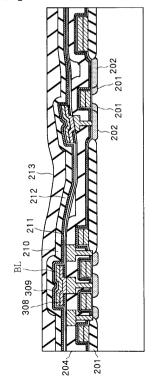

次に、従来の図38に示したCOB型のDRAMセルの製造方法について、図25~図38を参照して簡単に説明する。まず、図25に示すように、P型シリコン基板にNウエルとPウエルが形成された基板に素子分離酸化膜201を形成して素子分離を行い、その後、図示しないゲート絶縁膜を熱酸化法で形成した後、ポリシリコン301a、タングステンシリサイド301bを積層した後パターニングしてゲート電極301を形成する。このゲート電極301をマスクとしてイオン注入を行い、LDD(Lightly Doped Drain)101を形成する。

#### [0004]

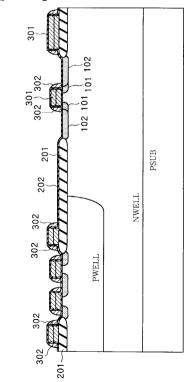

次に、図26に示すように、全面にエッチングストッパー用の薄いシリコン酸化膜202を形成する。次いで、ポリシリコンを堆積した後エッチバックすることにより、ゲート電極側壁にポリシリコンで構成されるサイドウオール302を形成する。そして、このサイドウオール302をマスクとしてイオン注入を行い、ソース・ドレイン102を形成する

#### [0005]

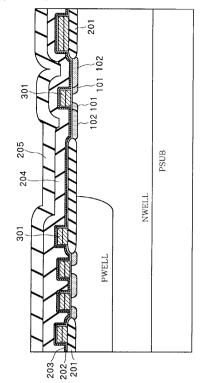

サイドウオール 3 0 2 を取り除いた後、図 2 7 に示すように、エッチングストッパー用のシリコン室化膜 2 0 3 を低圧 C V D により全面に形成する。その後、N S G (Natural Si licate Glass)膜 2 0 4 を  $O_3$  - T E O S (テトラエトキシシラン)で形成した後、B P S G (Boro-Phospho-Silicate-Glass )膜 2 0 5 を  $O_3$  - T E O S で形成する。

### [0006]

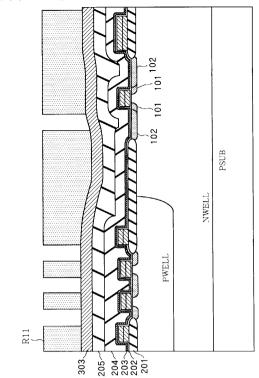

次に、図28に示すように、BPSG205をフローして平坦化する。その後、ポリシリコン303を堆積した後、ビットコンタクト及びノードコンタクトの開口を行うためのレジストパターニングR11を行う。

### [0007]

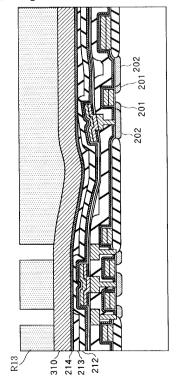

次に、図29に示すように、ポリシリコン膜303、BPSG膜205、NSG膜204をエッチングし、途中でエッチングを停止して開口部(あるいは、予備コンタクト孔と記載する)を形成し、更にポリシリコンを堆積した後エッチバックすることにより、この予備コンタクト孔の側壁にポリシリコンで構成されるサイドウオール304を形成する。次に、このサイドウオール304とポリシリコン膜303をマスクとしてエッチングすることにより、基板に達するコンタクトホールを開口し、シュリンクされたビット線コンタクトホールBCH及びノードコンタクトホールNCHを開口する。

#### [0008]

コンタクトホール開口後、図 3 0 に示すように、ポリシリコン膜 3 0 5 を堆積してコンタクトホール B C H 、N C H を埋める。

### [0009]

40

20

(3)

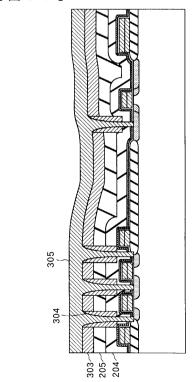

次に、図31に示すように、ポリシリコン膜305、303、サイドウオール304をエッチバックして予備コンタクト孔よりポリシリコン膜305(サイドウオール304も含まれる)の表面が低くなるようにする。これにより、各コンタクトには途中取り出し用のいわゆる座布団付ポリプラグ306が形成される。

#### [0010]

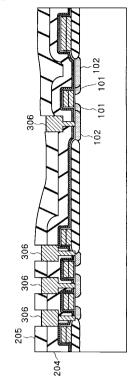

次に、図32に示すように、BPSG膜205をエッチングしてポリプラグ306と面一化した後、LP-TEOSにより酸化シリコン膜207、次いで低圧CVD法により窒化シリコン膜208を全面に形成する。その上にビット線形成用のコンタクト開口用のレジストR12をパターニングする。

#### [0011]

次に、図33に示すように、レジスト膜R12をマスクとして窒化シリコン膜208、酸化シリコン膜209をエッチングしてビット線コンタクトのプラグ表面を露出させる。レジスト膜R12を除去した後、ビット線形成用のポリシリコン膜308、タングステンシリサイド309を堆積し、ビット線用のレジストパターンを形成し、これをマスクとしてエッチングしてビット線BLをパターニングする。その後、LP-TEOSで酸化シリコン膜210、低圧CVD法により窒化シリコン膜211をそれぞれ薄く形成した後、NSG膜212、BPSG213を堆積して、BPSG213をフローして平坦化する。

#### [0012]

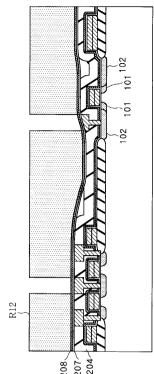

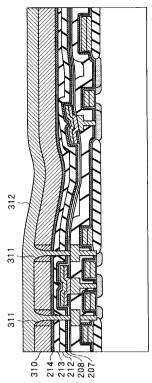

次に、図34に示すように、エッチング等により表面を削って平坦化した後、キャパシタ 形成時のエッチングストッパーとなる窒化シリコン膜214を堆積する。その上にポリシ リコン膜310を堆積した後、ノードコンタクトプラグに対するコンタクトを開口するレ ジストパターニングR13を行う。

#### [0013]

そして、図35に示すように、レジストR13をマスクとしてエッチングし、ポリシリコン膜310に予備コンタクト孔を形成する。次に、ポリシリコンを堆積した後エッチバックすることにより、予備コンタクト孔の側壁にポリシリコンで構成されるサイドウオール311を形成し、サイドウオール311とポリシリコン膜310をマスクとして窒化シリコン膜214、BPSG膜213、NSG膜212、窒化シリコン膜208、酸化シリコン膜207を順次エッチングして、いわゆる座布団に達するシュリンクされたノードコンタクト孔を開口し、次にポリシリコン312を堆積してコンタクト孔を埋める。

#### [0014]

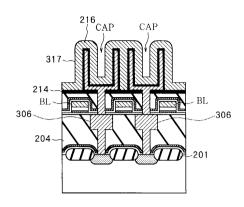

次に、図36に示すように、ポリシリコン膜312、ポリシリコン膜310、サイドウオール311をエッチバックすることにより、ポリプラグ314を残してポリシリコン膜を除去し、更に、ノード電極のためのポリシリコン膜315を堆積する。その上に、シリンダー型キャパシタを形成するための酸化シリコン膜215を厚く堆積し、キャパシタの底壁電極用のパターンでレジスト膜R14を形成する。

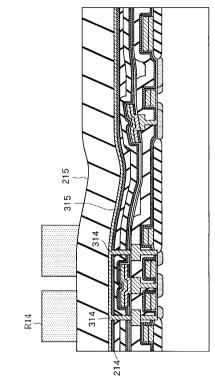

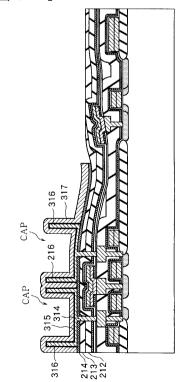

## [ 0 0 1 5 ]

次に、図37に示すように、レジスト膜R14をマスクとして異方性エッチングを行い、酸化シリコン膜215とポリシリコン膜315をパターニングした後、レジスト膜R14を除去する。その後、ポリシリコン膜を堆積した後、エッチバックすることにより酸化シリコン膜の側部にポリシリコンで構成されるサイドウオール316を形成する。酸化シリコン215をウエットエッチングにより除去してシリンダー型のノード電極を形成する。その後、ONO膜(酸化シリコンを窒化シリコン膜で挟んだ構造)216をノード電極上に形成した後、プレート電極となるポリシリコン膜317を堆積し、次にプレート電極317及び窒化シリコン膜214をパターニングしてプレート電極を形成してキャパシタCAPが形成される。これにより、DRAMが完成する。

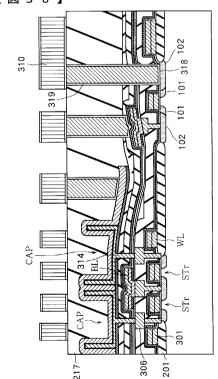

#### [0016]

その後、図38に示したように、層間絶縁膜217を堆積してキャパシタを埋め込み、平 坦化した後、プレート電極、周辺回路と配線層を接続するためのコンタクト孔を開口する 。次いで、コンタクト孔内壁を覆って密着層としてのTi/TiN膜318を形成した後 10

20

30

40

、タングステンを堆積した後エッチバックすることにより、ブランケットタングステン3 19を形成する。その後配線層310をパターニングして図38に示した断面構造のCO B型のDRAMを得る。

### [0017]

### 【発明が解決しようとする課題】

この従来の工程で製造されるCOB型DRAMセルでは、配線層がゲート電極、ビット線及びキャパシタの3層、層間絶縁膜が3層あることから、メモリセル部の高さは1μm程度になり、周辺回路の層間絶縁膜が厚くなって周辺回路のコンタクトのアスペクト比が大きくなるため、周辺回路のコンタクト径を小さくできず、集積度を上げることができないという問題がある。

#### [0018]

本発明は、上記事情に鑑みなされたもので、周辺回路部における層間絶縁膜を薄くし、コンタクト径を小さくできるCOB型DRAM等の<u>半導体装置の製造方法</u>を提供することを目的とする。

#### [0019]

#### 【課題を解決するための手段】

本発明の半導体装置の製造方法は、層間絶縁膜に配線用溝を形成する工程と、該配線用溝を導電性材料で埋める工程と、<u>前記導電性材料が埋められた前記配線溝中に第1の開口部</u>を形成する工程と、該<u>第1の開口部</u>内壁に導電性材料で構成されるサイドウオールを形成する工程と、該サイドウオールをマスクとして<u>第2の開口部を前記</u>層間絶縁膜に<u>形成</u>する工程と、該<u>第2の開口部</u>を導電性材料で埋め込む工程と、該層間絶縁膜と該配線用溝を埋める導電性材料を平坦化して埋込配線層を形成する工程と、該埋込配線層を被覆する層間絶縁膜を形成する工程とを有することを特徴とする。

### [0020]

本発明の半導体装置の製造方法は、上記埋込配線層とその下方の接続領域とを接続するプラグとを形成する方法であり、層間絶縁膜に配線用溝を形成してこれを導電材料で埋め込み、導電性材料中に第1の開口部を形成し、その第1の開口部に導電性サイドウオールを形成してそのサイドウオールをマスクとしてシュリンクされた第2の開口部を形成する。従って、確実に<u>開口部</u>を形成できると共に、埋込配線層により半導体の高さを減少させることができ、<u>開口部(コンタクト)</u>径を小さくできる。

#### 【発明の実施の形態】

以下、本発明の実施の形態について具体的に説明するが、本発明は、下記の実施の形態に 限定されるものではない。

### [ 0 0 2 1 ]

本発明の半導体装置の製造方法によって形成した半導体装置は、層間絶縁膜に掘られた配線用溝を埋める埋込配線層と、その層間絶縁膜を貫通しその埋込配線層とその下方の接続領域とを接続する導電性プラグとを有し、その埋込配線層が覆間絶縁膜で被覆された構造を有し、好適には上記COB型DRAMのビット線に適用することができる。

### [0022]

本発明の半導体装置の製造方法によって形成した半導体装置をCOB型DRAMに適用した形態の平面的な構成は、従来と同様であり、図23に示した平面図がそのまま適用される。即ち、選択トランジスタSTrのゲート電極WLが平行に配線され、これらの選択トランジスタSTrの拡散層とビットコンタクトBCで接続されたビット線BLがゲート電極WLと直交して配線されている。各選択トランジスタSTrの拡散層には図示しないキャパシタと接続されたノードコンタクトNCが設けられている。

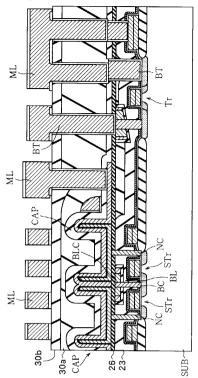

## [0023]

図23のB-B'線に沿った本発明にかかるCOB型DRAMの断面図の一形態を図15に示した。なお、この断面図は、周辺回路の一部を含んでいる。このDRAMは、シリコン基板SUB面に選択トランジスタSTr及び周辺回路のトランジスタTrが形成されている。ビット線BLは基板SUBとキャパシタCAPとの間の層間絶縁膜中に配線され、

10

20

30

40

ビット線コンタクトBCで選択トランジスタSTrの拡散層と接続されている。また、キャパシタCAPはノードコンタクトNCで選択トランジスタSTrの拡散層に接続されている。

### [0024]

ビット線BLは、トランジスタSTrを覆っている層間絶縁膜23に掘られたビット線用溝BLCを埋める例えばタングステンシリサイドとポリシリコンの2層の導電性材料で構成されている。ビット線コンタクトBCはビット線BLを貫通して基板SUBと接続されている。また、ビット線BLの上面は平坦化されて、絶縁膜26で被覆され、キャパシタCAPと分離されている。

#### [0025]

次に、このような断面構造の半導体装置の製造工程を説明する。

### [0026]

#### 「第1実施形態]

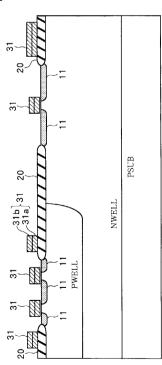

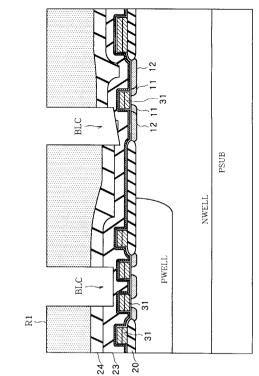

まず、図1に示すように、例えば、基板としてP型基板にNウエルを形成した後、そのNウエル内にPウエルを形成したシリコン基板を用いる。そのシリコン基板に例えばパッド酸化膜と窒化シリコン膜を堆積した後、レジスト膜を形成し、レジスト膜に素子分離形成領域の開口部のパターニングを露光、現像により形成し、レジスト膜の開口部の窒化シリコン膜をエッチングで除去する。レジスト膜を除去後、基板を酸化してLOCOS20を形成し、素子分離を行う。窒化珪素膜とパッド酸化膜を除去した後、シリコン基板表面を酸化して活性領域に図示しないゲート酸化膜を形成する。その後、例えば不純物導入ポリシリコン膜31aをCVD法により、更に、タングステンシリサイドWSi×31bをCVD法により数百nm程度の膜厚でそれぞれ堆積する。次に、ゲート電極パターンにレジストパターニングを行い、タングステンシリサイド31b、ポリシリコン膜31aをエッチングによりパターニングしてゲート電極31を形成する。次に、ゲート電極31とLOCOS20をマスクとして、砒素又はリンを例えばエネルギー数十keV、ドーズ量1×10 $^{12}$ ~1×10 $^{14}$ 4程度の条件でイオン注入して、LDD11を形成する。

### [0027]

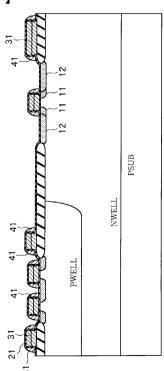

## [0028]

その後、図 3 に示すように、ポリシリコンで構成されるサイドウオール 4 1 を除去した後、低圧 C V D 法により、窒化シリコン膜 2 2 を例えば数十 n m程度の膜厚で堆積し、 O<sub>3</sub> - T E O S 法 C V D により、 N S G 膜 2 3 を数百 n m の 膜厚で堆積 し、 次に、 O<sub>3</sub> - T E O S 法 C V D により、 B P S G 膜 2 4 を数百 n m 程度の膜厚で堆積する。

#### [0029]

その後、図4に示すように、BPSG膜24をリフローして平坦化した後、通常のビット線パターンの反転パターンでレジストパターニングR1を行い、これをマスクとしてBPSG膜24、NSG膜23を順次エッチングし、NSG膜23のゲート電極31の上でエッチングを停止する。この場合、ゲート電極31を被覆してシリコン窒化膜22を形成しているため、ゲート電極31がエッチングにより露出することはない。これにより、ビット線のパターンでビット線用溝BLCが選択トランジスタSTr上に形成されて直接覆う層間絶縁膜23中に形成される。

### [0030]

10

20

30

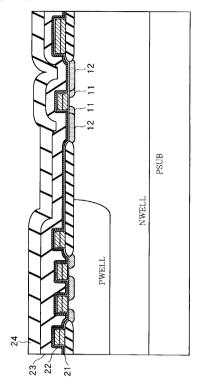

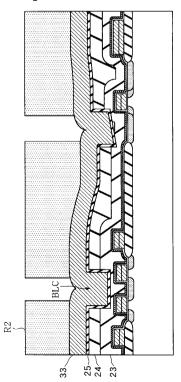

次に、図 5 に示すように、レジスト膜 R 1 を除去した後、例えば窒化シリコン膜(酸化シリコンでもよい) 2 5 を低圧 C V D 法により数十 n m の 膜厚で堆積し、次に、例えばW F  $_6$  / S  $_1$  H  $_2$  C l  $_2$  = 3 . 6 s c c m / 1 0 0 s c c m 、温度 5 9 5 、 1 3 3 P a の 条件でタングステンシリサイドW S  $_1$  x 膜 3 2 を数十 n m の 膜厚で C V D 法により堆積し、更に不純物導入ポリシリコン膜 3 3 を数十 n m ~ 百数十 n m 程度の 膜厚で C V D 法により堆積し、ビット線用溝 B L C を埋める。なお、タングステンシリサイド膜形成前に、下地の酸化シリコンとの密着性を確保するため、薄いポリシリコン膜を数十 n m 程度の 膜厚で形成してもよい。その後、ビット線用溝 B L C 中の 導電材料中に <u>開口部(あるいは、予備コンタクト孔と記載する)</u>を形成するためのパターンでレジストパターニング R 2 を行う

10

20

30

40

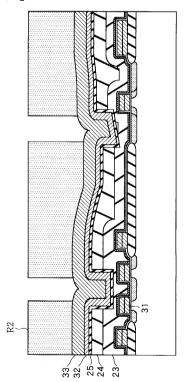

### [0031]

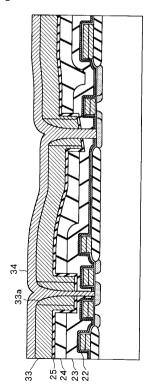

次に、図6に示すように、レジストR2をマスクとしてポリシリコン膜33とタングステンシリサイド膜34を順次異方性エッチングすることにより、ビット線用溝BLC中の導電材料中に開口部(予備コンタクト孔)PBCHを形成する。

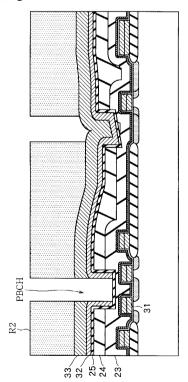

#### [0032]

次に、図7に示すように、レジストR2を除去した後、数百nmの厚さで不純物導入ポリシリコン膜を堆積した後、エッチバックすることにより、予備孔PBCHの側壁にポリシリコンで構成されるサイドウオール33aを形成する。その後、ポリシリコン膜33とサイドウオール33aをマスクとして窒化シリコン膜25、酸化シリコン膜23、窒化シリコン膜22を順次エッチングして基板に達するビットコンタクトホールを形成する。このビットコンタクトホールはサイドウオール33aをマスクとしているためシュリンクされている。不純物導入ポリシリコン膜34をCVD法により堆積し、ビットコンタクトホールをポリシリコン34で埋める。

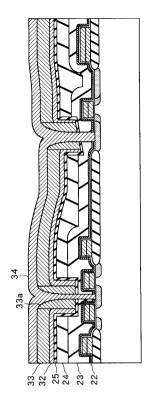

[0033]

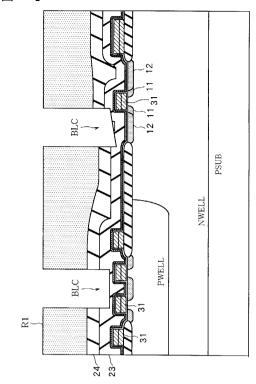

次に、図8に示すように、ポリシリコン膜34、33、サイドウオール33a、タングステンシリサイド層32を順次エッチングにより除去又はCMP(Chemical Mechanical Po lishing )法により研磨し、続いて層間絶縁膜25、24を順次CMP法により研磨して平坦化する。これにより、ビット線用溝BLCを埋め込んだビット線BLが形成される。このように、本実施形態では、ビット線BLの形成と平坦化を併用しているプロセスを採用しているため、従来より工程が短縮化されている。このとき同時に、ビット線BLを貫通するビット線コンタクトBCのポリプラグ34が形成される。次に、ノード電極形成時のエッチングストッパー及びビット線を埋め込むための窒化シリコン膜26を数十nmの膜厚でCVD法により堆積する。

[ 0 0 3 4 ]

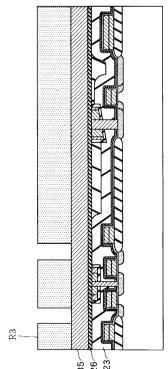

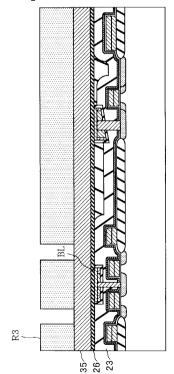

次に、キャパシタと基板を接続するノードコンタクトの形成工程に入り、図9に示すように、不純物導入ポリシリコン膜を数百nmの膜厚でCVD法により堆積し、ノードコンタクトのレジストパターニングR3を行う。

[0035]

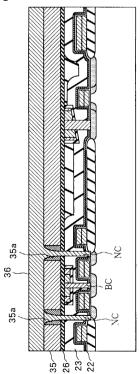

次に、図10に示すように、レジストR3をマスクとして異方性エッチングによりポリシリコン膜に予備コンタクト孔を形成し、レジストR3を除去した後、不純物導入ポリシリコン膜をCVD法により形成し、これをエッチバックすることによりポリシリコン膜35の予備コンタクト孔の側壁にサイドウオール35aを形成する。そして、サイドウオール35aとポリシリコン膜35とをマスクとして窒化シリコン膜26,NSG膜23、窒化シリコン膜22を順次エッチングし、基板に達するシュリンクされたノードコンタクトホールを形成する。次に、不純物導入ポリシリコン膜36をCVDで堆積し、ノードコンタクトホールを埋め込む。

[0036]

次に、図11に示すように、ポリシリコン膜36、35、サイドウオールをエッチングで除去して、ノードコンタクトNCのポリプラグを形成する。その後は、キャパシタ形成工程に入り、ノード電極のための不純物導入ポリシリコン膜37をCVD法により数百nm

20

30

40

50

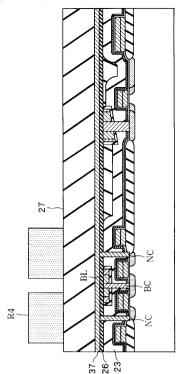

の膜厚で堆積する。その上に、シリンダー型キャパシタを形成するための酸化シリコン膜27を厚くCVD法により堆積し、キャパシタの底壁電極用のパターンでレジストパターニングR4を形成する。

### [0037]

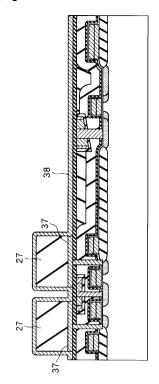

次に、図12に示すように、レジスト膜R4をマスクとして異方性エッチングを行い、酸化シリコン膜27とポリシリコン膜37をパターニングした後、レジスト膜R4を除去する。その後、ポリシリコン膜38を堆積する。

### [0038]

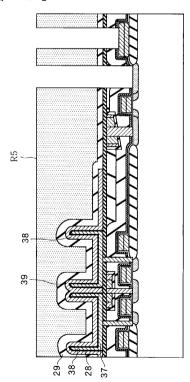

次に、図13に示すように、ポリシリコン膜38をエッチバックすることにより酸化シリコン膜27の側部にポリシリコンで構成されるサイドウオール38を形成し、シリンダー型記憶ノードの立設する側壁を形成する。酸化シリコン27をウエットエッチングにより除去してシリンダー型のノード電極を形成する。その後、記憶ノード37、38表面のRTA(Rapid Thermal Anneal)をアンモニア雰囲気下で行い、次に窒化ケイ素膜をCVDで形成し、続いて窒化ケイ素膜を例えば熱酸化して誘電体膜(ONO膜)28を形成し、誘電体膜28で記憶ノード37、38を被覆する。その後、プレート電極となるポリシリコン膜39をCVD法により数百nm程度の膜厚で堆積した後、プレート電極のパターンでレジストパターニングし、レジストをマスクとして異方性エッチングを行い、プレート電極39を形成する。その後、プレート電極保護のための酸化シリコン膜29をCVD法により堆積する。この後、周辺回路部のコンタクト開口パターン(溝状の場合もある)でレジストR5をパターニングし、これをマスクとして異方性エッチングを行い、コンタクト孔を開口する。

### [0039]

次に、図14に示すように、レジストを除去した後、コンタクト孔内壁を覆って密着層としてのTi/TiN膜を形成する。その後、タングステンを数百nmの膜厚で堆積した後エッチバックすることにより、ブランケットタングステンBTを形成し、途中取り出し用のタングステンプラグを形成する。その後、酸化シリコン膜30aを数百nm程度の膜厚で堆積する。

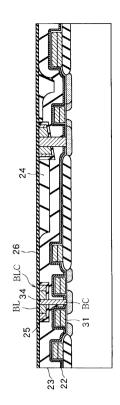

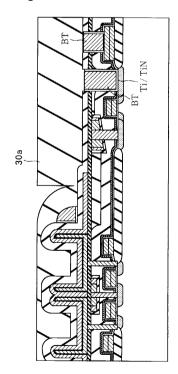

### [0040]

次に、図15に示すように、BPSG膜30bをCVD法により堆積した後平坦化する。次に、周辺回路部のコンタクト、プレート電極の取り出し用コンタクト等を開口するパターンでレジストパターニングを行い、レジストをマスクとして異方性エッチングにより層間絶縁膜30a、30bにコンタクト孔を開口した後、レジスト膜を除去する。タングステンを数百nm程度の膜厚でCVD法により堆積してコンタクト孔を埋め、その後、エッチバックすることによりタングステンプラグBTを形成する。次に、アルミニウムなどの金属をスパッタリング等により成膜し、配線パターンでレジストパターニングし、レジストをマスクとして異方性エッチングすることにより金属配線層MLを形成してCOB型のDRAMが完成する。

### [0041]

以上の工程で得られたCOB型DRAMセルは、従来のビット線が層間絶縁膜上に乗った構造と異なり、ビット線BLが層間絶縁膜23に掘られた溝の底部を埋める構造となっている。そのため、ビット線の厚さ及びビット線を埋める層間絶縁膜の厚さの分、基板表面上の層間絶縁膜の高さが従来のCOB型のDRAMより減少する。具体的には、シリンダー型のキャパシタを有するCOB型のDRAMでは、キャパシタ上端までの高さは約1μm(1000nm)程度あるが、本実施形態によれば300~400nm程度の高さの減少が可能であり、3~4割程度DRAMの高さを減らすことができる。その結果、周辺回路部における層間絶縁膜の膜厚も300~400nm程度減少する。それによって周辺回路部のコンタクト孔形成時のアスペクト比が低下し、コンタクト径の縮小化が可能であり、集積度を向上させることが可能である。

#### [0042]

また、ビット線上の平坦化プロセスとビット線形成プロセスを併用しているため、工程の

10

20

30

40

50

短縮が可能であり、コスト低下が可能である。

### [0043]

#### 「第2実施形態]

第1実施形態では、ビット線用溝をタングステンシリサイド膜とポリシリコン膜で埋めて、ビット線を2層構成としているが、第2実施形態ではタングステンシリサイドを後工程でポリシリコンとタングステンとを反応させることによって形成する。以下の図面では、第1実施形態と同じ部材には同じ符号を付す。

### [0044]

図16は、第1実施形態の図4と同じであり、ビット線用溝BLCを形成する工程までは同じでよい。

### [0045]

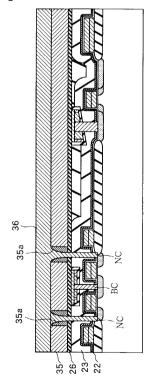

次に、図17に示すように、レジスト膜 R 1を除去した後、例えば窒化シリコン膜(酸化シリコンでもよい)25をCVD法により数十nmの膜厚で堆積し、次に、不純物導入ポリシリコン膜33を数百nm程度の膜厚でCVD法により堆積し、ビット線用溝BLCを埋める。なお、ポリシリコン膜33形成前に、下地の酸化シリコンとの密着性を確保するため、薄いポリシリコン膜を数十nm程度の膜厚で形成してもよい。その後、ビット線用溝BLC中のポリシリコン33中に予備コンタクト孔を形成するためのパターンでレジストパターニング R 2を行う。

### [0046]

次に、図18に示すように、レジストR2をマスクとしてポリシリコン膜33に予備コンタクト孔を開口し、その後レジストR2を除去する。その後、ポリシリコン膜を厚く堆積した後エッチバックし、予備コンタクト孔の側壁にポリシリコンで構成されるサイドウオール33aを形成する。その後、ポリシリコン膜33とサイドウオール33aをマスクとして窒化シリコン膜25、酸化シリコン膜23、窒化シリコン膜22を順次エッチングして基板に達するビットコンタクトホールを形成する。このビットコンタクトホールはサイドウオール33aをマスクとしているためシュリンクされている。不純物導入ポリシリコン膜34をCVD法により堆積し、ビットコンタクトホールをポリシリコン34で埋める

## [0047]

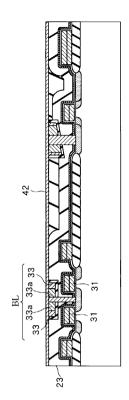

次に、図19に示すように、ポリシリコン膜34、33、サイドウオール33a、タングステンシリサイド層32を順次エッチングにより除去又はCMP法により研磨し、続いて層間絶縁膜25、24を順次CMP法により研磨して平坦化する。これにより、ビット線用溝BLCを埋め込んだポリシリコンで構成されるビット線BLが形成される。同時に、ビット線BLを貫通するビット線コンタクトBCのポリプラグが形成される。次に、例えばTi、Co等の高融点金属42を数十nmの膜厚でスパッタリングにより堆積する。

#### [0048]

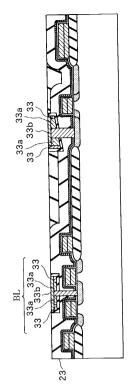

そして、図20に示すように、例えばランプアニール法で、650 ~700 の熱処理を加え、高融点金属42とポリシリコン33、33aとを反応させ、高融点金属シリサイド膜を形成する。その後、未反応高融点金属膜を硫酸過水等でエッチオフして高融点金属シリサイド膜33bをビット線BL表面に残す。

## [0049]

その後は、図21、図22に示すように、第1実施形態と同様の工程でノードコンタクト 形成、キャパシタ形成後COB型DRAMを製造することができる。

## [0050]

上記態様では、本発明をCOB型DRAMに適用した形態を説明しているが、本発明は、例えばSRAM等にも適用でき、DRAMに限定されるものではない。また、埋込配線層は基板と接続された例を示したが、中間配線層との接続でもよい。更に、ノードコンタクトとビット線コンタクトは共に、ポリシリコンで埋めてポリプラグとしているが、キャパシタのONO膜形成時の熱に耐えるものであれば、高融点金属で構成してもよい。その他、例えばキャパシタは、何れの形態でもよく、その他本発明の要旨を逸脱しない範囲で種

50

々変更することができる。

## [0051]

#### 【発明の効果】

本発明の半導体装置は、層間絶縁膜の厚さを減らし、コンタクトホールのアスペクト比を 小さくすることができる。

### [0052]

また、本発明の半導体装置の製造方法によれば、コンタクトホールの開口径を小さくして 集積度の向上した半導体装置を得ることができる。

#### 【図面の簡単な説明】

- 【図1】本発明にかかる第1実施形態のCOB型DRAMを製造する最初の工程を説明す 10る断面図である。

- 【図2】本発明にかかる第1実施形態のCOB型DRAMを製造する図1に続く工程を説明する断面図である。

- 【図3】本発明にかかる第1実施形態のCOB型DRAMを製造する図2に続く工程を説明する断面図である。

- 【図4】本発明にかかる第1実施形態のCOB型DRAMを製造する図3に続く工程を説明する断面図である。

- 【図5】本発明にかかる第1実施形態のCOB型DRAMを製造する図4に続く工程を説明する断面図である。

- 【図6】本発明にかかる第1実施形態のCOB型DRAMを製造する図5に続く工程を説 20 明する断面図である。

- 【図7】本発明にかかる第1実施形態のCOB型DRAMを製造する図6に続く工程を説明する断面図である。

- 【図8】本発明にかかる第1実施形態のCOB型DRAMを製造する図7に続く工程を説明する断面図である。

- 【図9】本発明にかかる第1実施形態のCOB型DRAMを製造する図8に続く工程を説明する断面図である。

- 【図10】本発明にかかる第1実施形態のCOB型DRAMを製造する図9に続く工程を 説明する断面図である。

- 【図11】本発明にかかる第1実施形態のCOB型DRAMを製造する図10に続く工程 30を説明する断面図である。

- 【図12】本発明にかかる第1実施形態のCOB型DRAMを製造する図11に続く工程 を説明する断面図である。

- 【図13】本発明にかかる第1実施形態のCOB型DRAMを製造する図12に続く工程を説明する断面図である。

- 【図14】本発明にかかる第1実施形態のCOB型DRAMを製造する図13に続く工程を説明する断面図である。

- 【図15】本発明にかかる第1実施形態のCOB型DRAMを製造する最終工程を説明する断面図であり、図23のB-B'線に沿った断面図である。

- 【図16】本発明にかかる第2実施形態のCOB型DRAMを製造する工程を説明する断 40面図であり、第1実施形態の図4に相当する。

- 【図17】本発明にかかる第2実施形態の図16に続くCOB型DRAMを製造する工程を説明する断面図である。

- 【図18】本発明にかかる第2実施形態の図17に続くCOB型DRAMを製造する工程を説明する断面図である。

- 【図19】本発明にかかる第2実施形態の図18に続くCOB型DRAMを製造する工程を説明する断面図である。

- 【図20】本発明にかかる第2実施形態の図19に続くCOB型DRAMを製造する工程を説明する断面図である。

- 【図21】本発明にかかる第2実施形態の図20に続くCOB型DRAMを製造する工程

を説明する断面図である。

【図22】本発明にかかる第2実施形態の図21に続くCOB型DRAMを製造する工程を説明する断面図である。

【図23】従来のCOB型DRAMの平面構成を示す配置図である。

【図24】図23のA-A'線に沿った断面図である。

【図25】従来のCOB型DRAMの製造工程の最初の段階を説明する断面図である。

【図26】図25に続く従来のCOB型DRAMの製造工程を説明する断面図である。

【図27】図26に続く従来のCOB型DRAMの製造工程を説明する断面図である。

【図28】図27に続く従来のCOB型DRAMの製造工程を説明する断面図である。

【図29】図28に続く従来のCOB型DRAMの製造工程を説明する断面図である。

【図30】図29に続く従来のCOB型DRAMの製造工程を説明する断面図である。

【図31】図30に続く従来のCOB型DRAMの製造工程を説明する断面図である。

【図32】図31に続く従来のCOB型DRAMの製造工程を説明する断面図である。

【図33】図32に続く従来のCOB型DRAMの製造工程を説明する断面図である。

【図34】図33に続く従来のCOB型DRAMの製造工程を説明する断面図である。

【図35】図34に続く従来のCOB型DRAMの製造工程を説明する断面図である。

【図36】図35に続く従来のCOB型DRAMの製造工程を説明する断面図である。

【図37】図36に続く従来のCOB型DRAMの製造工程を説明する断面図である。

【図38】従来のCOB型DRAMを製造する最終工程を説明する断面図であり、図23のB-B'線に沿った断面図である。

#### 【符号の説明】

S T r … 選択トランジスタ、W L … ゲート電極、 B L … ビット線、 B C … ビットコンタクト、 B C H … ビットコンタクトホール、 N C … ノードコンタクト、 N C H … ノードコンタクトホール、 B L C … ビット線用溝、 C A P … キャパシタ、 予備コンタクト孔 … P B C H

### 【図1】

### 【図2】

10

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

【図31】

【図32】

【図33】

【図34】

【図35】

【図36】

【図37】

【図38】

# フロントページの続き

(58)調査した分野(Int.CI.<sup>7</sup>, DB名)

H01L 27/108 H01L 21/8242 H01L 21/768