(12)

## Patentschrift

(21) Aktenzeichen: 11 2012 007 296.0

(51) Int Cl.: G11C 14/00 (2006.01)

(22) Anmelddatum: 12.03.2012

G11C 7/10 (2006.01)

(45) Veröffentlichungstag

der Patenterteilung: 20.04.2017

G11C 11/4074 (2006.01)

Innerhalb von neun Monaten nach Veröffentlichung der Patenterteilung kann nach § 59 Patentgesetz gegen das Patent Einspruch erhoben werden. Der Einspruch ist schriftlich zu erklären und zu begründen. Innerhalb der Einspruchsfrist ist eine Einspruchsgebühr in Höhe von 200 Euro zu entrichten (§ 6 Patentkostengesetz in Verbindung mit der Anlage zu § 2 Abs. 1 Patentkostengesetz).

(30) Unionspriorität:

2011-065210 24.03.2011 JP

2011-108886 14.05.2011 JP

(72) Erfinder:

Maehashi, Yukio, Atsugi-shi, Kanagawa-ken, JP;

Kobayashi, Hidetomo, Atsugi-shi, Kanagawa-ken,

JP

(62) Teilung aus:

11 2012 001 395.6

(56) Ermittelter Stand der Technik:

US 7 394 717 B2

US 2008 / 0 071 972 A1

US 2010 / 0 077 244 A1

US 2010 / 0 141 322 A1

(73) Patentinhaber:

SEMICONDUCTOR ENERGY LABORATORY CO.,

LTD., Atsugi-shi, Kanagawa-ken, JP

(74) Vertreter:

Grünecker Patent- und Rechtsanwälte PartG

mbB, 80802 München, DE

(54) Bezeichnung: **Signalverarbeitungsschaltung**

(57) Hauptanspruch: Signalverarbeitungsschaltung, umfassend:

einen arithmetischen Teil;

einen Speicher (2005); und

einen Steuerteil zum Steuern des arithmetischen Teils und

des Speichers,

wobei der Steuerteil eine erste Speicherschaltung (200)

und eine zweite Speicherschaltung (100) zum Speichern

von Daten, die in der ersten Speicherschaltung (200) ge-

halten werden, umfasst,

wobei die zweite Speicherschaltung (100) einen ersten

Transistor (101; 101a) und einen ersten Kondensator (102;

102a) umfasst,

wobei eine erste Elektrode des ersten Kondensators (102;

102a) elektrisch mit einem ersten Knoten verbunden ist, der

in einen potenzialfreien Zustand versetzt wird, wenn der

erste Transistor (101; 101a) ausgeschaltet ist,

wobei der Speicher (2005) eine Vielzahl von dritten Spei-

cherschaltungen umfasst, welche in einer Matrix (400) ange-

ordnet sind,

wobei die Vielzahl von dritten Speicherschaltungen jeweils

einen zweiten Transistor (101b, 101d) und einen zweiten

Kondensator (102b, 102d) umfassen,

wobei eine erste Elektrode des zweiten Kondensators (102b;

102d) elektrisch mit einem zweiten Knoten verbun-

den ist, der in einen potenzialfreien Zustand versetzt wird,

wenn der zweite Transistor (101b, 101d) ausgeschaltet ist,

und

wobei der erste Transistor (101; 101a) und der zweite Transistor (101b, 101d) jeweils einen Kanalbildungsbereich in

einer Oxidhalbleiterschicht aufweisen.

**Beschreibung****TECHNISCHES GEBIET**

**[0001]** Eine Ausführungsform der vorliegenden Erfindung bezieht sich auf eine Signalverarbeitungsschaltung, die eine Speicherschaltung für nichtflüchtigen Speicher aufweist, die einen gespeicherten logischen Zustand bewahren kann, selbst wenn die Stromversorgung ausgeschaltet wird. Ferner bezieht sich eine Ausführungsform der vorliegenden Erfindung auf eine elektronische Vorrichtung, welche die Signalverarbeitungsschaltung umfasst.

**STAND DER TECHNIK**

**[0002]** Eine Signalverarbeitungsschaltung, wie z. B. eine zentrale Verarbeitungseinheit (CPU), hat eine Vielzahl von Konfigurationen, je nach ihrer Anwendung, ist aber in der Regel mit irgendeiner Art von Speicherschaltungen, wie etwa einem Register und einem Cache-Speicher zusätzlich zu einem Hauptspeicher zum Speichern von Daten oder eines Programms ausgestattet.

**[0003]** In einer Speicherschaltung, wie z. B. einem Register oder einem Cache-Speicher, muss das Lesen und Schreiben von Daten mit einer höheren Geschwindigkeit durchgeführt werden als in einem Hauptspeicher. So wird in der Regel ein Flipflop oder dergleichen als ein Register verwendet, und ein statischer Direktzugriffspeicher (SRAM) oder dergleichen wird als ein Cache-Speicher verwendet. Das heißt, für das Register, den Cache-Speicher und dergleichen werden Speicherschaltungen für flüchtigen Speicher verwendet, in denen Daten verloren gehen, wenn die Bereitstellung einer Versorgungsspannung unterbrochen ist.

**[0004]** Um die benötigte Leistung zu reduzieren, wurde ein Verfahren zum vorübergehenden Unterbrechen der Zufuhr einer Versorgungsspannung zu einer Signalverarbeitungsschaltung für einen Zeitraum vorgeschlagen, in dem Daten weder eingegeben noch ausgegeben werden. In dem Verfahren wird eine Speicherschaltung für nichtflüchtigen Speicher im Umfeld einer Speicherschaltung für flüchtigen Speicher, wie z. B. einem Register oder einem Cache-Speicher, angeordnet, so dass die Daten vorübergehend in der Speicherschaltung für nichtflüchtigen Speicher gespeichert werden. Somit bewahrt das Register, der Cache-Speicher oder dergleichen Daten auch, während die Bereitstellung von Versorgungsspannung an der Signalverarbeitungsschaltung gestoppt wird (siehe z. B. Patentschrift 1).

**[0005]** Zusätzlich werden in dem Fall, in dem die Bereitstellung der Versorgungsspannung an einer Signalverarbeitungsschaltung für eine lange Zeit gestoppt wird, Daten in einer Speicherschaltung für flüchtigen Speicher in eine externe Speichervorrichtung, wie z. B. eine Festplatte oder einem Flash-Speicher, übertragen, bevor die Bereitstellung der Versorgungsspannung beendet wird, so dass verhindert werden kann, dass die Daten gelöscht werden. US 2010/0141322 A1 zeigt eine Latch-Schaltung mit einer Magnetic Tunnel Junction (MTJ) Struktur. US 2010/0077244 A1 zeigt ein Computersystem mit einem Funktionsblock und einem MRAM-Block, der den funktionalen Zustand des Funktionsblocks hält, während der Funktionsblock abgeschaltet ist. US 7,394,717 B2 zeigt einen Dünnschichtmagnetspeicher mit einem großenvariablen ROM-Bereich und einem großenvariablen RAM-Bereich. US 2008/0071972 A1 zeigt eine Datenverarbeitungsvorrichtung mit einem Kontrollabschnitt, der alle Daten zum Wiederherstellen des Zustands eines Schaltkreisabschnitts in einem nicht-flüchtigen Speicher speichert.

**[Referenz]****[0006]**

[Patentschrift 1] Veröffentlichte japanische Patentanmeldung JP H10-078836 A

**BESCHREIBUNG DER ERFINDUNG**

**[0007]** In einer solchen Signalverarbeitungsschaltung wie in Patentschrift 1 offenbart wird ein Ferroelektrikum für ein Speicherelement, das in einer Speicherschaltung für nichtflüchtigen Speicher enthalten ist, verwendet. In dem Speicherelement, welches ein Ferroelektrikum umfasst, ändert ein ferroelektrisches Material durch wiederholtes Schreiben von Daten, was ein Problem, wie z. B. einen Schreibfehler, verursacht. Entsprechend ist die Anzahl der Male für nochmaliges Schreiben begrenzt. Darüber hinaus ist die Geschwindigkeit der Datenverarbeitung (im Folgenden auch als Zugriffsgeschwindigkeit bezeichnet), zum Beispiel, die Geschwindigkeit des Lesens und Schreibens von Daten gering.

**[0008]** In dem Fall, dass ein Flash-Speicher als Speicherschaltung für nichtflüchtigen Speicher verwendet wird, wird eine hohe Spannung angelegt, um einen Tunnelstrom zu erzeugen, wobei eine Injektion oder Freisetzung von Elektronen durchgeführt wird. Daher gibt es insofern Probleme, dass sich Speicherelemente durch wiederholtes Durchführen des Umschreibens von Daten massiv verschlechtern, so dass die Anzahl der Umschreibvorgänge begrenzt ist. Darüber hinaus ist die Zugriffsgeschwindigkeit gering.

**[0009]** In dem Fall, dass Daten in der Speicherschaltung für flüchtigen Speicher in der externen Speichervorrichtung gespeichert werden, während die Bereitstellung der Versorgungsspannung an der Signalverarbeitungsschaltung unterbrochen ist, dauert es eine lange Zeit, um Daten von der externen Speichervorrichtung an die Speicherschaltung für flüchtigen Speicher zurück zu übertragen. Daher ist solch eine Signalverarbeitungsschaltung nicht für den Fall geeignet, in dem die Stromversorgung für eine kurze Zeit unterbrochen wird, um den Stromverbrauch zu reduzieren.

**[0010]** In Anbetracht der obigen Probleme ist es eine Aufgabe einer Ausführungsform der vorliegenden Erfindung, eine Signalverarbeitungsschaltung zur Verfügung zu stellen, die eine Speicherschaltung mit einer neuartigen Struktur aufweist, in der ein gespeicherter logischer Zustand selbst dann nicht verloren geht, wenn die Stromversorgung unterbrochen wird.

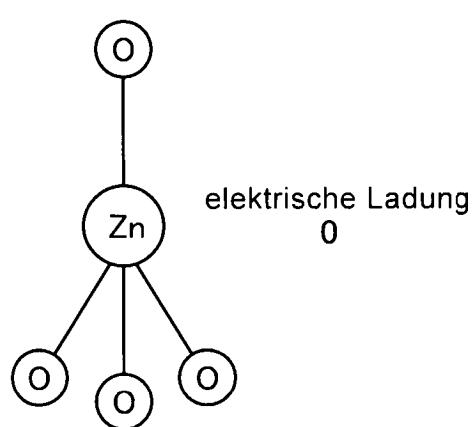

**[0011]** Eine Ausführungsform einer Signalverarbeitungsschaltung gemäß der vorliegenden Erfindung umfasst einen arithmetischen Teil, einen Speicher und einen Steuerteil zum Steuern des arithmetischen Teils und des Speichers. Der Steuerteil umfasst eine Gruppe aus einer ersten Speicherschaltung für flüchtigen Speicher und einer ersten Speicherschaltung für nichtflüchtigen Speicher zum Speichern von Daten, die in der ersten Speicherschaltung für flüchtigen Speicher gehalten werden, und der Speicher weist eine zweite Speicherschaltung für nichtflüchtigen Speicher auf. Man beachte, dass der Speicher die Vielzahl von zweiten Speicherschaltungen für nichtflüchtigen Speicher in einer Matrixanordnung umfassen kann. Die Daten, die in der ersten Speicherschaltung für flüchtigen Speicher gehalten werden, werden im Steuerteil in die erste Speicherschaltung für nichtflüchtigen Speicher eingegeben und dort gespeichert, während eine Versorgungsspannung bereitgestellt wird (im Folgenden auch als Datenspeichern bezeichnet). Daten können gleichzeitig zu dem Halten von vorbestimmten Daten in der ersten Speicherschaltung für flüchtigen Speicher oder nach dem Halten der Daten darin gespeichert werden. Dann wird bewirkt, dass sich die Daten, die in der ersten Speicherschaltung für nichtflüchtigen Speicher gespeichert sind, nicht in Reaktion auf ein Signal von der ersten Speicherschaltung für flüchtigen Speicher ändern (im Folgenden auch als Datenbereithaltung (Daten Standby) bezeichnet). In der ersten Speicherschaltung für nichtflüchtigen Speicher wird insbesondere ein Knoten, in welchem ein Potenzial eines Signals entsprechend den Daten gespeichert ist, in einem potenzialfreien Zustand versetzt. Nach der Datenbereithaltung wird die Bereitstellung von Versorgungsspannung im gesamten Steuerteil (oder im größten Teil des Steuerteils) gestoppt. Selbst nachdem die Bereitstellung von Versorgungsspannung beendet ist, können die Daten in der ersten Speicherschaltung für flüchtigen Speicher in der ersten Speicherschaltung für nichtflüchtigen Speicher gehalten werden. Dann wird eine Versorgungsspannung, je nach Bedarf, selektiv an dem gesamten Steuerteil oder an einem Teil davon bereitgestellt. Danach werden die Daten, die in der ersten Speicherschaltung für nichtflüchtigen Speicher gehalten werden, in einem Teil des Steuerteils, für den die Versorgungsspannung selektiv bereitgestellt wird, in die erste Speicherschaltung für flüchtigen Speicher bewegt (im Folgenden auch als Bereitstellung von Daten bezeichnet). Somit kann die erste Speicherschaltung für flüchtigen Speicher in dem Teil des Steuerteils, der für die Bereitstellung der Versorgungsspannung ausgewählt wurde, eine vorbestimmte Operation durchführen.

**[0012]** Auf diese Weise kann der Energieverbrauch der Signalverarbeitungsschaltung durch Verwendung eines Steuerverfahrens, bei welchem eine Versorgungsspannung nur bei Bedarf bereitgestellt wird, (im Folgenden auch als Standard-Aus Steuerverfahren bezeichnet) wie oben beschrieben drastisch verringert werden. Außerdem ist die Schreibe- und Lesegeschwindigkeit von Daten in der ersten Speicherschaltung für flüchtigen Speicher höher als die in der ersten Speicherschaltung für nichtflüchtigen Speicher. So kann die Bearbeitungsgeschwindigkeit in dem Teil des Steuerteils, der für die Bereitstellung der Versorgungsspannung ausgewählt wird, erhöht werden. Daher kann die Signalverarbeitungsschaltung mit hoher Geschwindigkeit betrieben werden. Darüber hinaus kann der Speicher Daten auch, nachdem die Bereitstellung der Versorgungsspannung beendet ist, weiter halten.

(Konfiguration der Speicherschaltung für nichtflüchtigen Speicher)

**[0013]** Hier enthält die oben erwähnte Speicherschaltung für nichtflüchtigen Speicher (jede von der ersten Speicherschaltung für nichtflüchtigen Speicher und der zweiten Speicherschaltung für nichtflüchtigen Speicher) einen Transistor mit extrem niedrigem Sperrstrom und einen Kondensator, bei dem eine Elektrode ei-

nes Paars von Elektroden (im Folgenden als „eine Elektrode“ bezeichnet) elektrisch mit einem Knoten verbunden ist, der in einen potenzialfreien Zustand versetzt wird, wenn der Transistor ausgeschaltet ist. Daten werden in der Speicherschaltung für nichtflüchtigen Speicher durch Steuern des Potenzials (oder der Menge an elektrischer Ladung, die dem Potenzial entspricht) der einen Elektrode des Kondensators, in Abhängigkeit von den Daten, gespeichert (oder abgespeichert). Zum Beispiel wird ein Zustand, in dem eine vorbestimmte elektrische Ladung in dem Kondensator akkumuliert wurde (auch als „geladen“ bezeichnet), mit dem Wert „1“ gleichgesetzt und ein Zustand, in dem die vorbestimmte elektrische Ladung nicht in dem Kondensator akkumuliert wurde, mit dem Wert „0“ gleichgesetzt, wodurch 1-Bit-Daten gespeichert werden können. Hier ist es möglich, einen Transistor mit einem Kanal in einer Schicht oder einem Substrat mit einem Halbleiter, dessen Bandlücke größer als die von Silicium ist, als den Transistor mit extrem niedrigem Sperrstrom zu verwenden. Ein Verbindungshalbleiter ist ein Beispiel für den Halbleiter, dessen Bandlücke größer als die von Silicium ist. Beispiele für den Verbindungshalbleiter umfassen einen Oxidhalbleiter, einen Nitridhalbleiter, und dergleichen. Beispielsweise kann ein Transistor mit einem Kanal in einer Oxidhalbleiterschicht als ein Transistor mit extrem niedrigem Sperrstrom verwendet werden.

**[0014]** Wenn der Transistor mit extrem niedrigem Sperrstrom in einer solchen Speicherschaltung für nichtflüchtigen Speicher ausgeschaltet wird, kann das Potenzial einer Elektrode des Kondensators für eine lange Zeit gehalten werden, selbst nachdem die Bereitstellung einer Versorgungsspannung beendet ist. Daher wird in einem Speicher, der eine Speicherschaltung für nichtflüchtigen Speicher mit der obigen Konfiguration aufweist, ein regelmäßiges Datenrückschreiben (im Folgenden auch als Aktualisierungsoperation bezeichnet) nicht benötigt oder die Häufigkeit der Aktualisierungsoperation kann deutlich verringert werden.

**[0015]** Darüber hinaus ist eine Speicherschaltung für nichtflüchtigen Speicher dazu ausgelegt, Daten in einer solchen Weise zu speichern, dass ein Potenzial eines Signals, welches den Daten entspricht, an einen vorbestimmten Knoten (die eine Elektrode des Kondensators) eingegeben wird, der Transistor mit extrem niedrigem Sperrstrom ausgeschaltet wird und der Knoten in einen potenzialfreien Zustand versetzt wird. Daher kann in der Speicherschaltung für nichtflüchtigen Speicher ein Alter durch wiederholtes Schreiben von Daten vermindert werden, und die Anzahl der Male, dass Daten geschrieben werden können, kann erhöht werden.

**[0016]** Hierbei können der Transistor mit extrem niedrigem Sperrstrom, der in der ersten Speicherschaltung für nichtflüchtigen Speicher (der Speicherschaltung für nichtflüchtigen Speicher des Steuerteils) enthalten ist, und der Transistor mit extrem niedrigem Sperrstrom, der in der zweiten Speicherschaltung für nichtflüchtigen Speicher (der Speicherschaltung für nichtflüchtigen Speicher des Speichers) enthalten ist, in demselben Schritt gebildet werden. Beispielsweise können Gate-Elektroden dieser Transistoren durch Ätzen eines leitfähigen Films gebildet werden; Source-Elektroden und Drain-Elektroden dieser Transistoren können durch Ätzen eines leitfähigen Films gebildet werden; und aktive Schichten (Halbleiterschichten, in denen Kanäle gebildet werden) dieser Transistoren können durch Ätzen einer Halbleiterschicht gebildet werden.

**[0017]** Darüber hinaus können der Kondensator, der in der ersten Speicherschaltung für nichtflüchtigen Speicher (der Speicherschaltung für nichtflüchtigen Speicher des Steuerteils) enthalten ist, und der Kondensator, der in der zweiten Speicherschaltung für nichtflüchtigen Speicher (der Speicherschaltung für nichtflüchtigen Speicher des Speichers) enthalten ist, in demselben Schritt gebildet werden. Zum Beispiel kann jede eine Elektrode dieser Kondensatoren durch Ätzen eines leitfähigen Films gebildet werden; und dielektrische Schichten dieser Kondensatoren können durch Ätzen einer Isolierschicht gebildet werden. Man beachte, dass die dielektrischen Schichten dieser Kondensatoren gemeinsam, ohne voneinander getrennt zu sein, vorgesehen werden können. Ferner können beispielsweise die anderen Elektroden der Paare von Elektroden dieser Kondensatoren (im Folgenden als die andere Elektrode jedes der Kondensatoren bezeichnet) durch Ätzen eines leitfähigen Films gebildet werden. Man beachte, dass die andere Elektrode jedes dieser Kondensatoren gemeinsam, ohne voneinander getrennt zu sein, vorgesehen werden kann. In diesem Fall kann eine leitfähige Schicht, die gemeinsam, ohne voneinander getrennt zu sein, vorgesehen ist, als eine Abschirmschicht oder eine Licht blockierende Schicht verwendet werden. Wenn die leitfähige Schicht zum Beispiel so vorgesehen ist, dass sie ein Element wie etwa einen Transistor, der in der Signalverarbeitungsschaltung enthalten ist, bedeckt, kann die nachteilige Wirkung eines äußeren elektrischen Feldes oder dergleichen auf das Element, das in der Signalverarbeitungsschaltung enthalten ist, reduziert werden. Des Weiteren kann z. B., wenn die leitfähige Schicht so vorgesehen ist, dass sie eine Oberfläche (eine vordere Fläche oder eine hintere Fläche) eines Substrats, über dem ein Element wie etwa ein Transistor, der in der Signalverarbeitungsschaltung enthalten ist, gebildet wird, bedeckt, die nachteilige Wirkung eines externen elektrischen Feldes oder dergleichen auf das Element, das in der Signalverarbeitungsschaltung enthalten ist, reduziert werden. Wie oben beschrieben kann eine sehr zuverlässige Signalverarbeitungsschaltung zur Verfügung gestellt werden, ohne die Anzahl

von Herstellungsprozessen zu erhöhen, wenn die andere Elektrode jedes der Kondensatoren jeweils als eine Abschirmschicht oder eine Licht blockierende Schicht dient.

(Konfiguration einer Speicherschaltung für flüchtigen Speicher)

**[0018]** Die erste Speicherschaltung für flüchtigen Speicher (die Speicherschaltung für flüchtigen Speicher, die in dem Steuerteil enthalten ist) kann mindestens zwei arithmetischen Schaltungen aufweisen, die eine Rückkopplungsschleife bilden, in der eine Ausgabe von einer der arithmetischen Schaltungen in die andere der arithmetischen Schaltungen eingegeben wird und eine Ausgabe der anderen der arithmetischen Schaltungen in die eine der arithmetischen Schaltungen eingegeben wird. Eine Flipflop-Schaltung und eine Verriegelungsschaltung (Latch-Schaltung) können als Beispiele für die Speicherschaltung mit einer solchen Konfiguration gegeben werden.

**[0019]** Man beachte, dass die Signalverarbeitungsschaltung der vorliegenden Erfindung je nach Kategorie eine CPU, eine hochintegrierte Schaltung (LSI), wie ein Mikroprozessor, eine Bildverarbeitungsschaltung, ein digitaler Signalprozessor (DSP) oder ein feldprogrammierbares Gate-Array (FPGA) und dergleichen umfasst. Der arithmetische Teil kann auch als ein Rechenwerk (ALU) bezeichnet werden. Der Speicher kann als ein Hauptspeicher zum Speichern von Daten oder eines Programms dienen.

(Variante des arithmetischen Teils)

**[0020]** Der arithmetische Teil kann eine Gruppe aus einer zweiten Speicherschaltung für flüchtigen Speicher und einer dritten Speicherschaltung für nichtflüchtigen Speicher zum Speichern von Daten, die in der zweiten Speicherschaltung für flüchtigen Speicher gehalten werden, aufweisen. Die dritte Speicherschaltung für nichtflüchtigen Speicher kann einen ähnlichen Aufbau wie den der ersten Speicherschaltung für nichtflüchtigen Speicher und der zweiten Speicherschaltung für nichtflüchtigen Speicher haben. Hier kann z. B. eine Flipflop-Schaltung, die Daten in Synchronisation mit Taktsignalen ein- und ausgibt, als die zweite Speicherschaltung für flüchtigen Speicher (die Speicherschaltung für flüchtigen Speicher des arithmetischen Teils) verwendet werden.

**[0021]** Hierbei können ein Transistor mit extrem niedrigem Sperrstrom, der in der dritten Speicherschaltung für nichtflüchtigen Speicher (der Speicherschaltung für nichtflüchtigen Speicher des arithmetischen Teils) enthalten ist, der Transistor mit extrem niedrigem Sperrstrom, der in der ersten Speicherschaltung für nichtflüchtigen Speicher (der Speicherschaltung für nichtflüchtigen Speicher des Steuerteils) enthalten ist, und der Transistor mit extrem niedrigem Sperrstrom, der in der zweiten Speicherschaltung für nichtflüchtigen Speicher (der Speicherschaltung für nichtflüchtigen Speicher des Speichers) enthalten ist, in demselben Schritt gebildet werden. Beispielsweise können Gate-Elektroden dieser Transistoren durch Ätzen eines leitfähigen Films gebildet werden; Source-Elektroden und Drain-Elektroden dieser Transistoren können durch Ätzen eines leitfähigen Films gebildet werden, und aktive Schichten (Halbleiterschichten, in denen Kanäle gebildet werden) dieser Transistoren können durch Ätzen einer Halbleiterschicht gebildet werden.

**[0022]** Darüber hinaus können der Kondensator, der in der dritten Speicherschaltung für nichtflüchtigen Speicher (der Speicherschaltung für nichtflüchtigen Speicher des arithmetischen Teils) enthalten ist, der Kondensator, der in der ersten Speicherschaltung für nichtflüchtigen Speicher (der Speicherschaltung für nichtflüchtigen Speicher des Steuerteils) enthalten ist, und der Kondensator, der in der zweiten Speicherschaltung für nichtflüchtigen Speicher (der Speicherschaltung für nichtflüchtigen Speicher des Speichers) enthalten ist, in demselben Schritt gebildet werden. Zum Beispiel kann die eine Elektrode jedes dieser Kondensatoren durch Ätzen eines leitfähigen Films gebildet werden; und dielektrische Schichten dieser Kondensatoren können durch Ätzen einer Isolierschicht gebildet werden. Man beachte, dass die dielektrischen Schichten dieser Kondensatoren gemeinsam, ohne voneinander getrennt zu sein, vorgesehen sein können. Ferner kann beispielsweise die andere Elektrode jedes dieser Kondensatoren durch Ätzen eines leitfähigen Films gebildet werden. Man beachte, dass die andere Elektrode jedes dieser Kondensatoren gemeinsam, ohne voneinander getrennt zu sein, vorgesehen sein kann. In diesem Fall kann die leitfähige Schicht, die gemeinsam, ohne voneinander getrennt zu sein, vorgesehen ist, als eine Abschirmschicht oder eine Licht blockierende Schicht verwendet werden. Wenn die leitfähige Schicht zum Beispiel so vorgesehen ist, dass sie ein Element wie etwa einen Transistor, der in der Signalverarbeitungsschaltung enthalten ist, bedeckt, kann die nachteilige Wirkung eines äußeren elektrischen Feldes oder dergleichen auf das Element, das in der Signalverarbeitungsschaltung enthalten ist, reduziert werden. Des Weiteren kann z. B., wenn die leitfähige Schicht so vorgesehen ist, dass sie eine Oberfläche (eine vordere Fläche oder eine hintere Fläche) eines Substrats, über dem ein Element wie etwa ein Transistor, der in der Signalverarbeitungsschaltung enthalten ist, gebildet wird, bedeckt, die nachteilige Wirkung eines äußeren elektrischen Feldes oder dergleichen auf das Element, das in der Signal-

verarbeitungsschaltung enthalten ist, reduziert werden. Wie oben beschrieben kann eine sehr zuverlässige Signalverarbeitungsschaltung zur Verfügung gestellt werden, ohne die Anzahl der Herstellungsprozesse zu erhöhen, wenn die andere Elektrode jedes der Kondensatoren jeweils als eine Abschirmschicht oder eine Licht blockierende Schicht dient.

(Variante des Steuerteils)

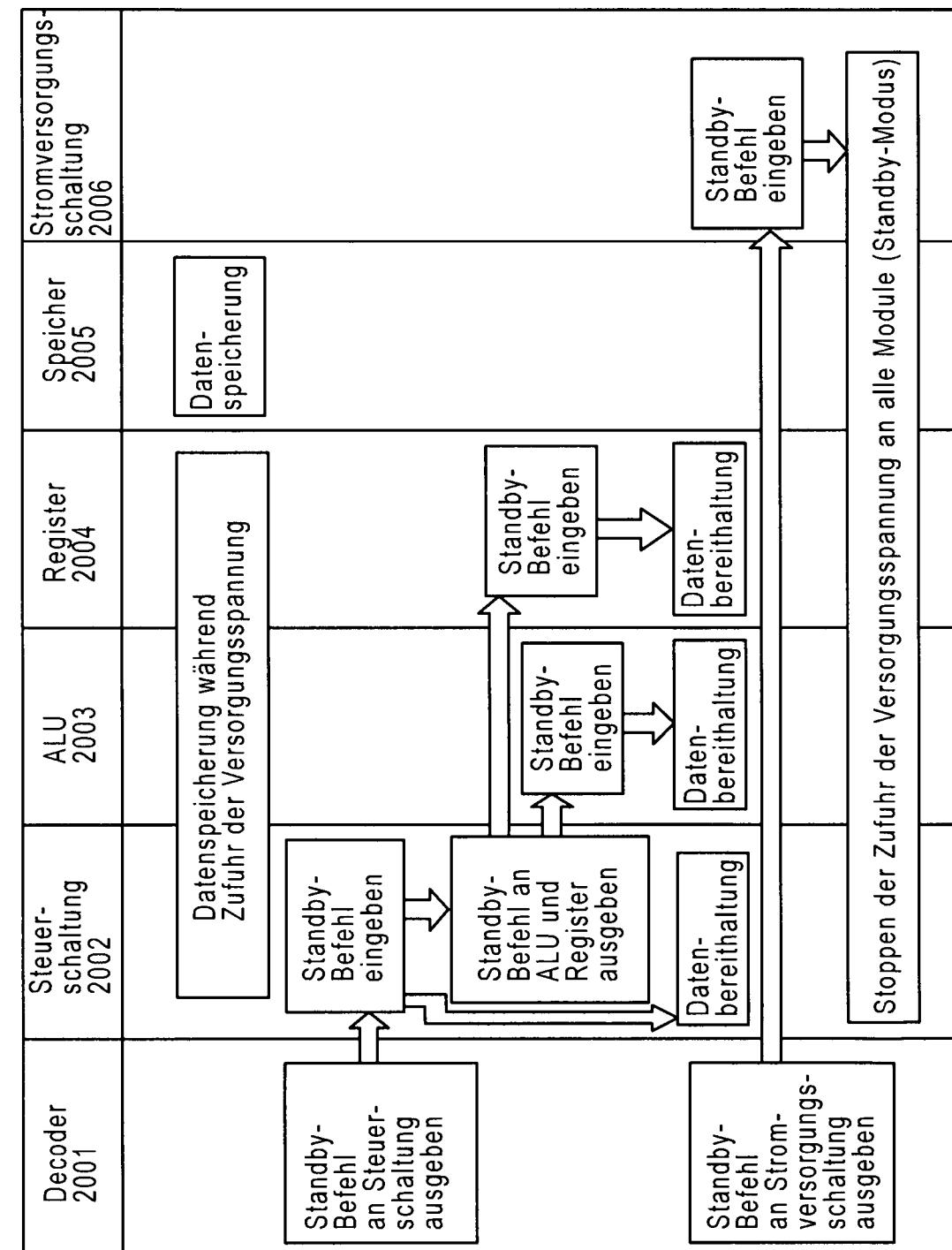

**[0023]** Der Steuerteil kann einen Decoder, eine Steuerschaltung, ein Register und eine Stromversorgungsschaltung aufweisen.

**[0024]** Der Decoder decodiert einen Befehl. Darüber hinaus kann der Decoder eine Funktion zum Eingeben eines Steuersignals an die Stromversorgungsschaltung oder die Steuerschaltung durch eine Eingabe von außen, wenn die Bereitstellung von Versorgungsspannung an den Speicher gestoppt wird, haben. Ferner kann der Decoder einen Zähler (ein Zeitzählwerk) haben und eine Funktion zum Eingeben eines Steuersignals an die Stromversorgungsschaltung oder die Steuerschaltung durch den Zähler (das Zeitzählwerk), wenn die Bereitstellung von Versorgungsspannung an den Speicher gestoppt wird, haben. Die Steuerschaltung steuert das Register, den arithmetischen Teil und den Speicher basierend auf dem decodierten Befehl. Das Register speichert vorübergehend Daten, welche an den arithmetischen Teil eingegeben werden, und Daten, welche von dem arithmetischen Teil ausgegeben werden. Die Stromversorgungsschaltung wird durch den Decoder gesteuert und die Stromversorgungsschaltung steuert die Bereitstellung von Versorgungsspannung an den arithmetischen Teil, die Steuerschaltung, das Register und den Speicher. Man beachte, dass der arithmetische Teil, die Steuerschaltung, das Register und der Speicher auch jeweils als Modul bezeichnet werden. Dabei kann die Stromversorgungsschaltung an jedem Modul selektiv die Versorgungsspannung bereitstellen oder stoppen. Das heißt, dass die Stromversorgungsschaltung Versorgungsspannung an alle Module (an den arithmetischen Teil, die Steuerschaltung, das Register und den Speicher) liefern kann und dass die Stromversorgungsschaltung selektiv Versorgungsspannung an einige der Module (wahlweise an den arithmetischen Teil, die Steuerschaltung, das Register und/oder den Speicher) liefern kann.

**[0025]** Das Register kann eine Gruppe aus einer dritten Speicherschaltung für flüchtigen Speicher und einer vierten Speicherschaltung für nichtflüchtigen Speicher zum Speichern von Daten, die in der dritten Speicherschaltung für flüchtigen Speicher gehalten werden, umfassen, und die Steuerschaltung kann eine Gruppe aus einer vierten Speicherschaltung für flüchtigen Speicher und einer fünften Speicherschaltung für nichtflüchtigen Speicher zum Speichern von Daten, die in der vierten Speicherschaltung für flüchtigen Speicher gehalten werden, umfassen. Die dritte Speicherschaltung für flüchtigen Speicher und die vierte Speicherschaltung für flüchtigen Speicher entsprechen jeweils der ersten Speicherschaltung für flüchtigen Speicher (der Speicherschaltung für flüchtigen Speicher des Steuerteils). Die vierte Speicherschaltung für nichtflüchtigen Speicher und die fünfte Speicherschaltung für nichtflüchtigen Speicher entsprechen jeweils der ersten Speicherschaltung für nichtflüchtigen Speicher (der Speicherschaltung für nichtflüchtigen Speicher des Steuerteils).

**[0026]** Hier kann z. B. eine Flipflop-Schaltung oder eine Verriegelungsschaltung (Latch-Schaltung), welche Daten in Synchronisation mit Taktsignalen ein- und ausgibt, als dritte Speicherschaltung für flüchtigen Speicher des Registers verwendet werden. Darüber hinaus kann beispielsweise eine Flipflop-Schaltung, die Daten in Synchronisation mit Taktsignalen ein- und ausgibt, als vierte Speicherschaltung für flüchtigen Speicher des Steuerteils verwendet werden.

**[0027]** Man beachte, dass die Vielzahl von vierten Speicherschaltungen für nichtflüchtigen Speicher zum Speichern von 1-Bit-Daten in dem Register für jede der dritten Speicherschaltungen für nichtflüchtigen Speicher zum Speichern von 1-Bit-Daten bereitgestellt werden können. Hier wird die Vielzahl von vierten Speicherschaltungen für nichtflüchtigen Speicher auch jeweils als eine (Speicher-)Bank bezeichnet. Auf diese Weise wird, wenn die Bereitstellung von Versorgungsspannung in dem Fall des Durchführens eines Standard-Aus Steuerverfahrens gewählt ist, eine vierte Speicherschaltung für nichtflüchtigen Speicher (eine Bank) aus der Vielzahl von vierten Speicherschaltungen für nichtflüchtigen Speicher (der Vielzahl von Bänken) ausgewählt, und 1-Bit-Daten, die in der ausgewählten vierten Speicherschaltung für nichtflüchtigen Speicher (der Bank) gehalten werden, werden für die dritte Speicherschaltung für flüchtigen Speicher bereitgestellt (Bereitstellung von Daten), so dass der Zustand des Registers aus einer Vielzahl von Zuständen ausgewählt werden kann.

**[0028]** Bei Verwendung der obigen Speicherschaltung für nichtflüchtigen Speicher, welche eine neuartige Konfiguration für die Signalverarbeitungsschaltung besitzt, kann die Signalverarbeitungsschaltung Daten für eine lange Zeit fortgesetzt halten, selbst nachdem die Bereitstellung der Versorgungsspannung beendet ist. Somit kann ein Standard-Aus (normally-off) Steuerverfahren durchgeführt werden. Dementsprechend kann der

Stromverbrauch der Signalverarbeitungsschaltung drastisch reduziert werden. Die Signalverarbeitungsschaltung kann eine vorbestimmte Verarbeitung von gehaltenen Daten beginnen, kurz nachdem die Bereitstellung der Versorgungsspannung ausgewählt wird. Daher kann die Zeit von der Auswahl der Bereitstellung der Versorgungsspannung bis zum Beginn einer vorbestimmten Verarbeitung in der Signalverarbeitungsschaltung verkürzt werden. Außerdem wird eine vorbestimmte Verarbeitung unter Verwendung einer Speicherschaltung für flüchtigen Speicher in einem Modul, das mit Versorgungsspannung versorgt wird, ausgeführt; deshalb kann die Zugriffsgeschwindigkeit der Signalverarbeitungsschaltung erhöht werden. Ferner wird eine sehr zuverlässige Schaltung, für die die Anzahl, wie oft Daten geschrieben werden können, hoch ist, als die Speicherschaltung für nichtflüchtigen Speicher für die Signalverarbeitungsschaltung verwendet; deshalb können die Haltbarkeit und die Zuverlässigkeit der Signalverarbeitungsschaltung verbessert werden.

**[0029]** Insbesondere können die folgenden vorteilhaften Auswirkungen in einer solchen Weise erzielt werden, dass je eine Gruppe aus der Speicherschaltung für flüchtigen Speicher und der Speicherschaltung für nichtflüchtigen Speicher zum Speichern von Daten, die in der Speicherschaltung für flüchtigen Speicher gehalten werden, für das Register und die Steuerschaltung des Steuerteils oder für das Register, die Steuerschaltung und den arithmetischen Teil des Steuerteils vorgesehen ist, dass die Speicherschaltung für nichtflüchtigen Speicher für den Speicher vorgesehen ist, und dass die Bereitstellung der Versorgungsspannung zu jedem Modul durch die Stromversorgungsschaltung gesteuert wird.

**[0030]** Ohne Verschieben von Daten zwischen den Modulen können Bereitstellung und Bereithaltung von Daten, bevor und nachdem die Bereitstellung der Versorgungsspannung gestoppt wird, durchgeführt werden. Daher ist es nicht notwendig, einen speziellen Signalweg (einen Weg oder einen Scanpfad) zum Durchführen von Bereitstellung und Bereithaltung von Daten zwischen den Modulen vorzusehen, und die Größe der Signalverarbeitungsschaltung kann leicht vergrößert werden.

#### KURZBESCHREIBUNG DER ZEICHNUNGEN

**[0031]** **Fig. 1A** bis **Fig. 1E** sind Diagramme, die Konfigurationen einer Signalverarbeitungsschaltung darstellen.

**[0032]** **Fig. 2A** und **Fig. 2B** sind Diagramme, die eine Konfiguration eines Speichers darstellen.

**[0033]** **Fig. 3A** bis **Fig. 3C** sind Diagramme, die Anordnungen eines Leseverstärkers und einer Vorladeschaltung darstellen.

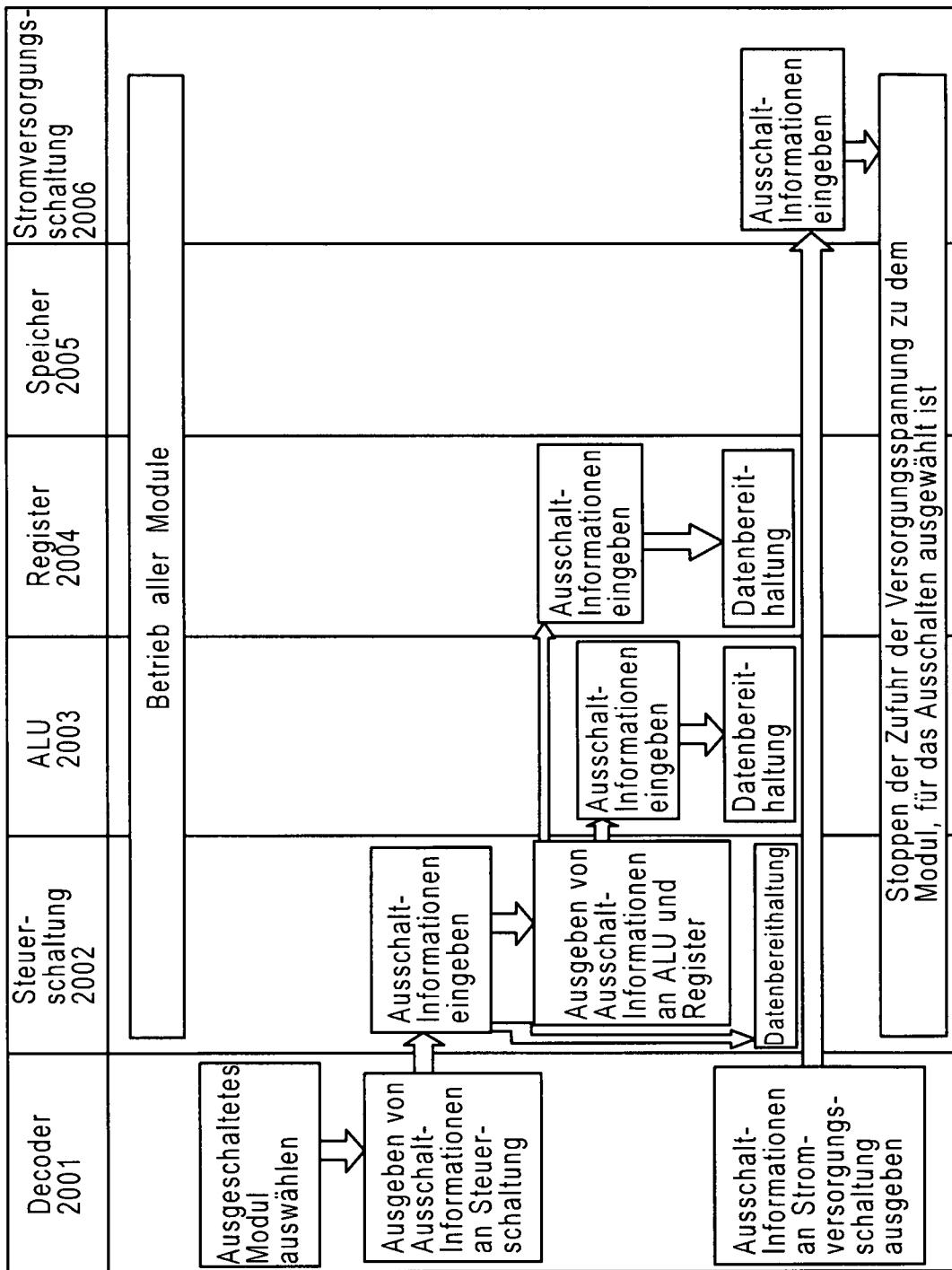

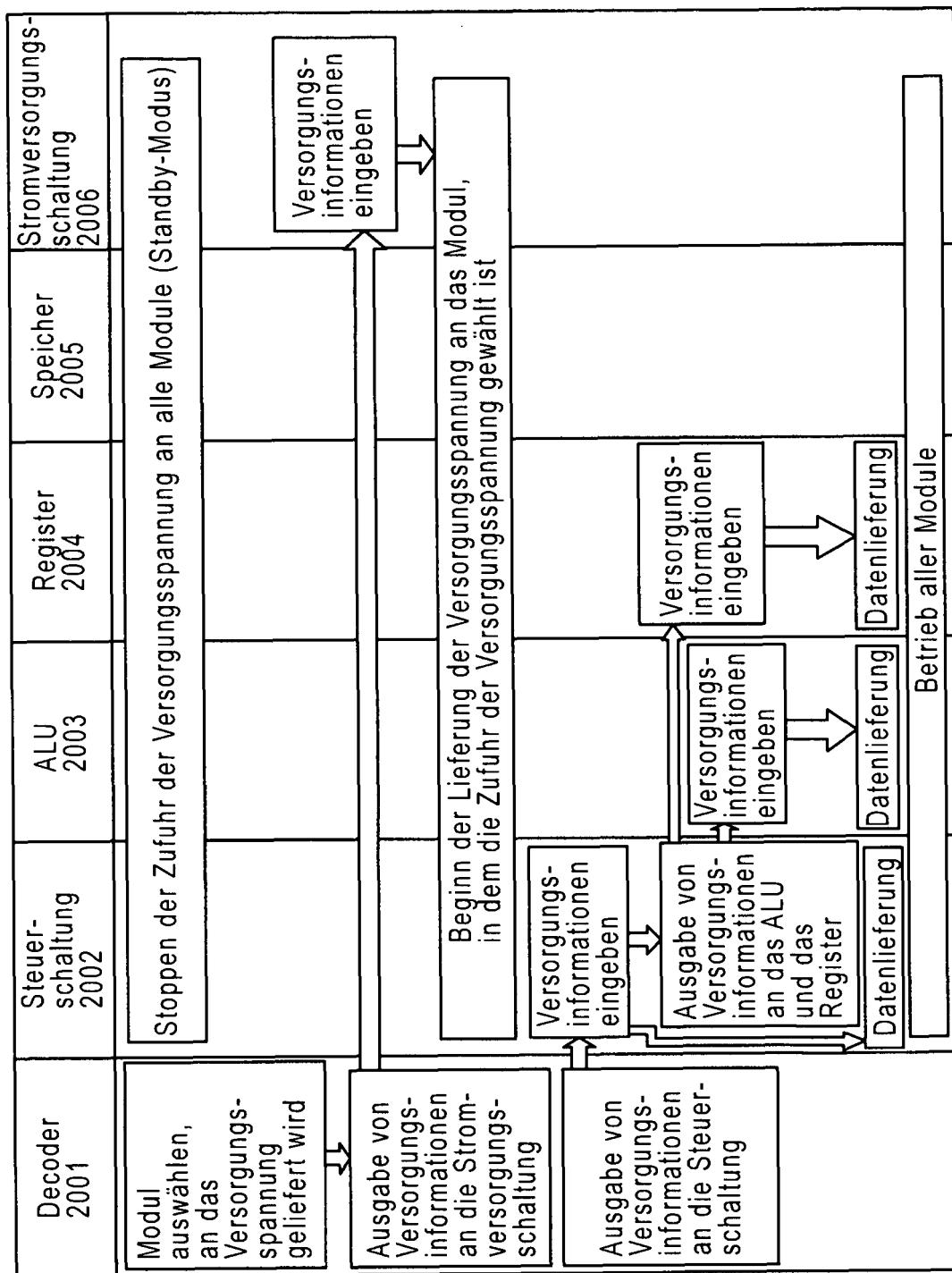

**[0034]** **Fig. 4** ist ein Flussdiagramm, das ein Verfahren zum Ansteuern einer Signalverarbeitungsschaltung darstellt.

**[0035]** **Fig. 5'** ist ein Flussdiagramm, das ein Verfahren zum Ansteuern einer Signalverarbeitungsschaltung darstellt.

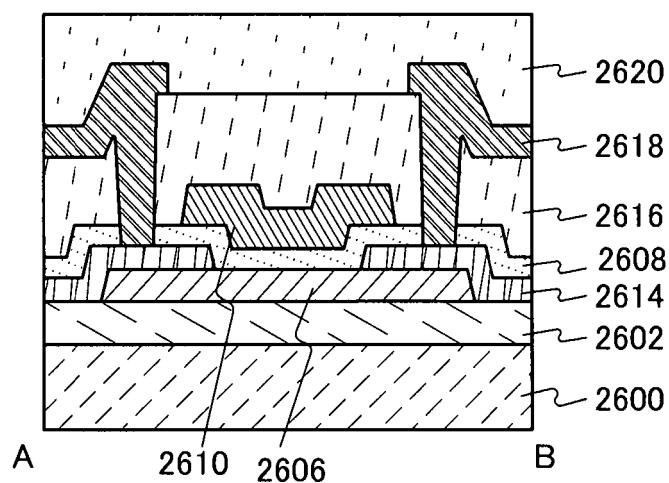

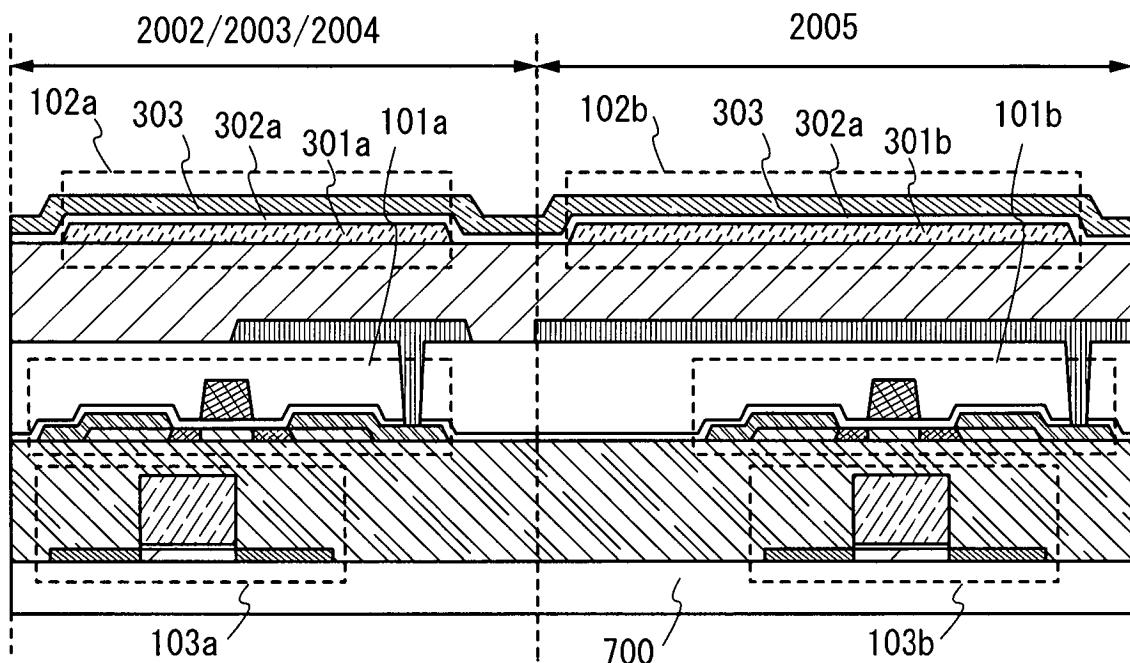

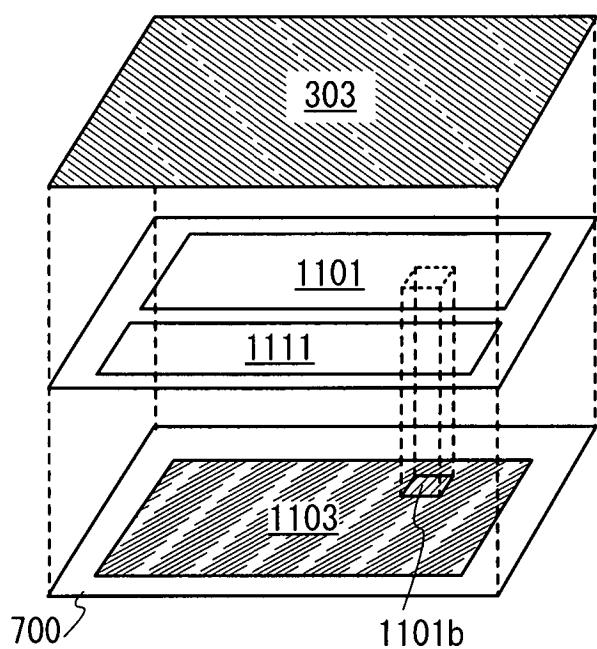

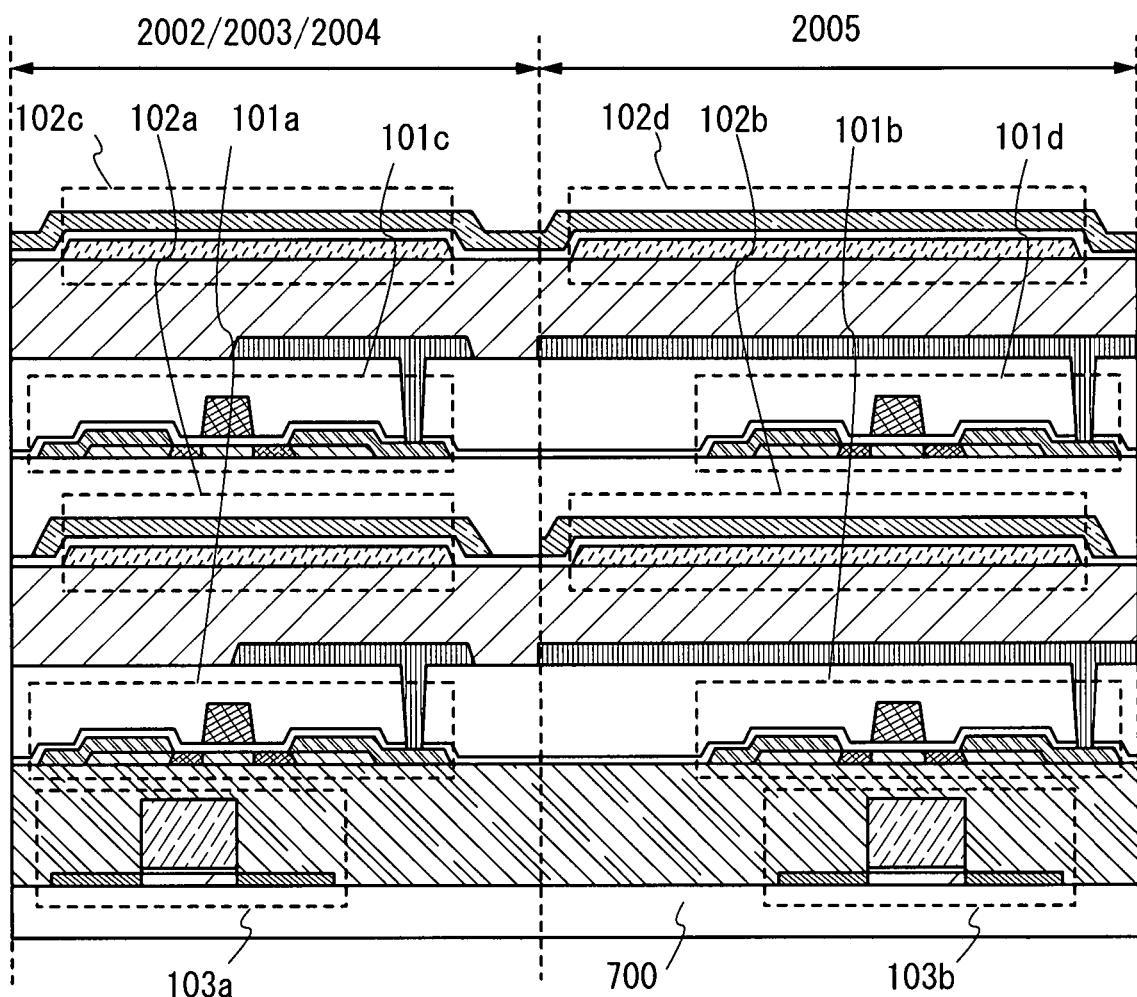

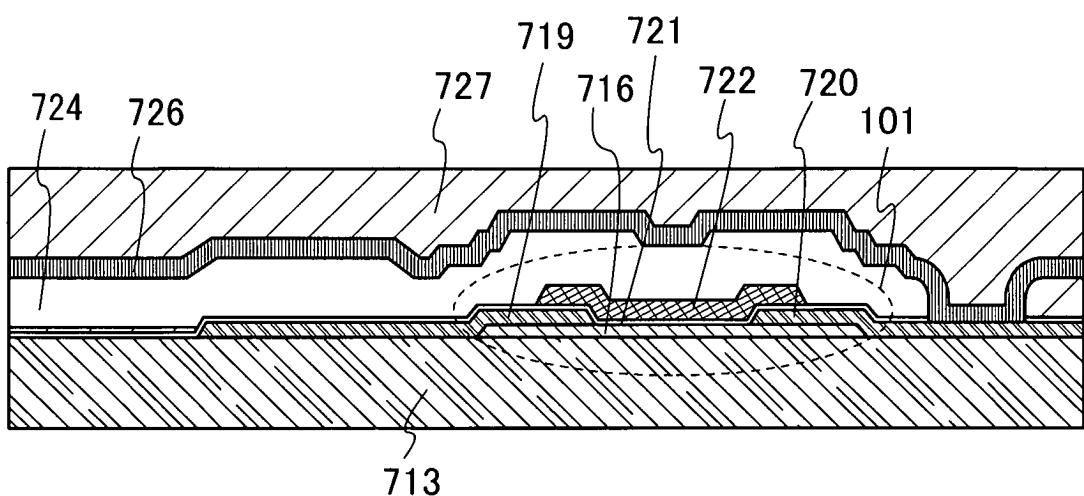

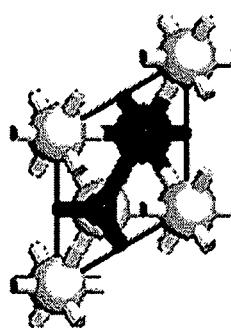

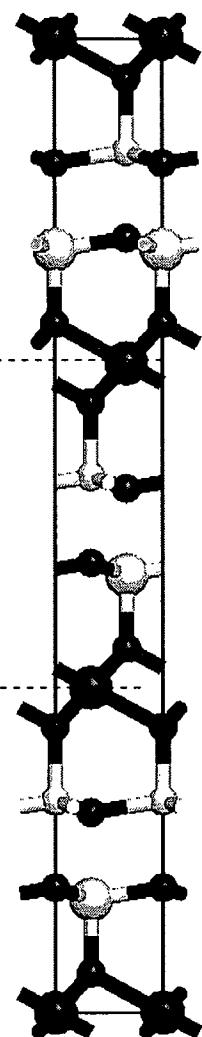

**[0036]** **Fig. 6A** und **Fig. 6B** sind eine Querschnittsansicht und eine perspektivische, schematische Ansicht, die eine Konfiguration einer Signalverarbeitungsschaltung darstellen.

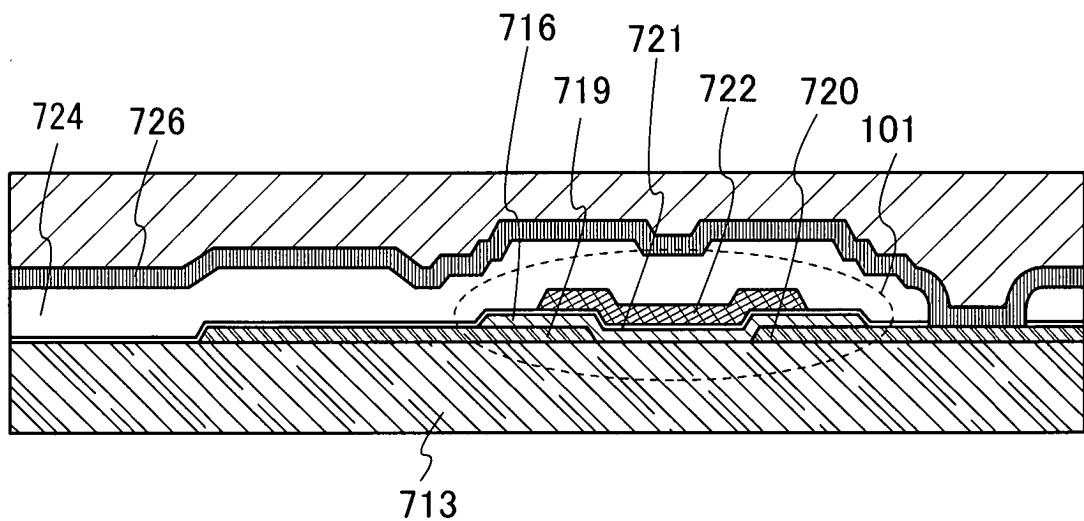

**[0037]** **Fig. 7** ist eine Querschnittsansicht, die eine Konfiguration einer Signalverarbeitungsschaltung darstellt.

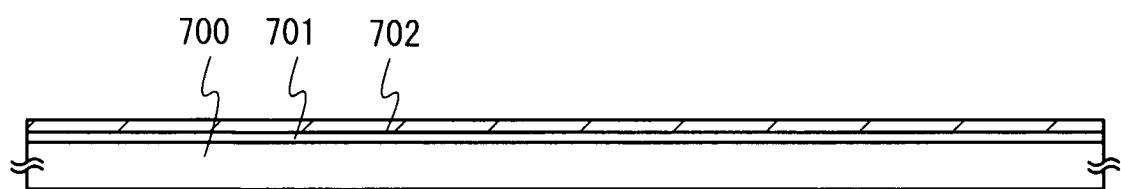

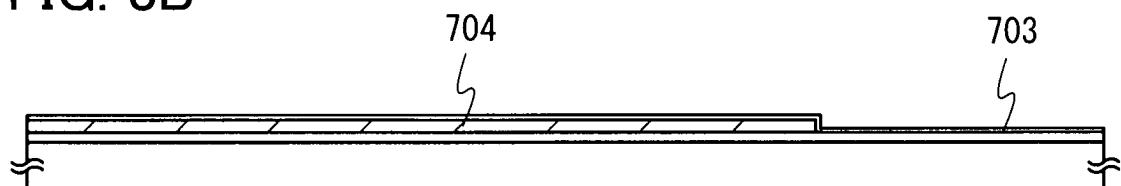

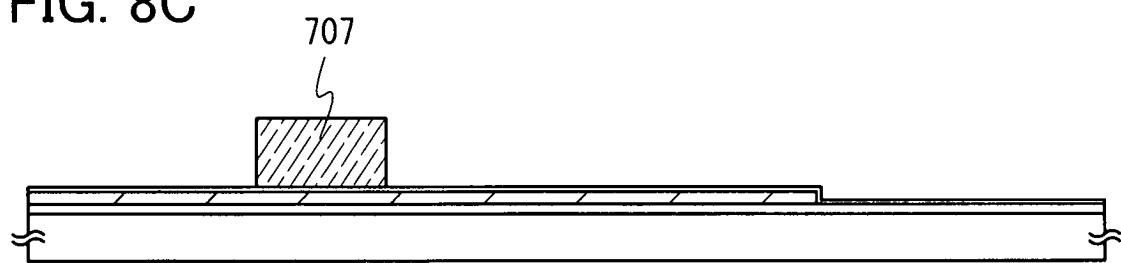

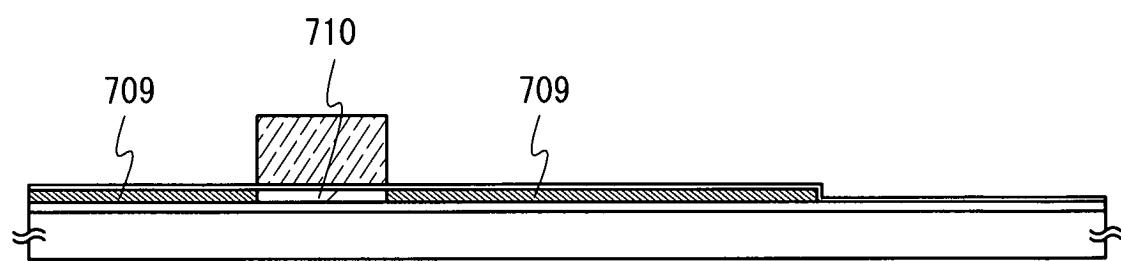

**[0038]** **Fig. 8A** bis **Fig. 8D** sind Querschnittsansichten, die einen Herstellungsprozess einer Signalverarbeitungsschaltung darstellen.

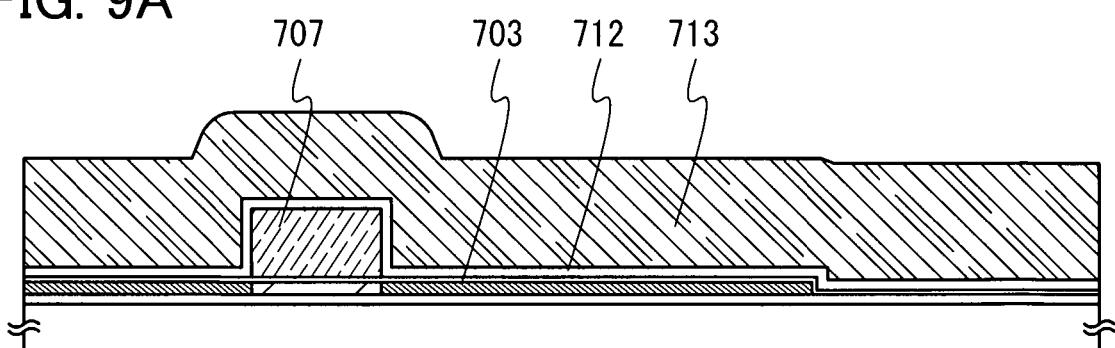

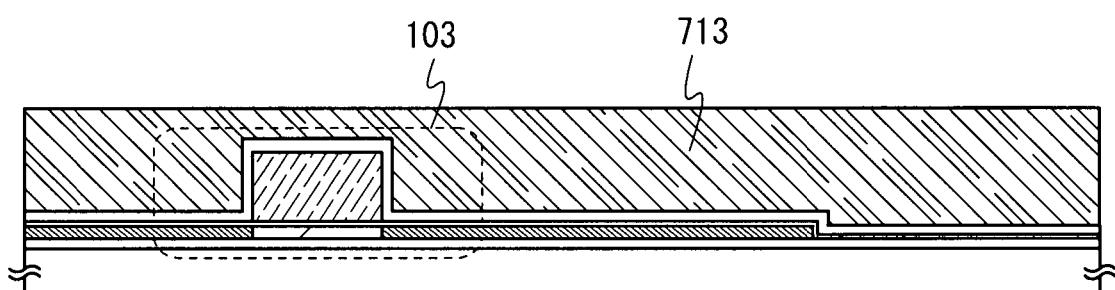

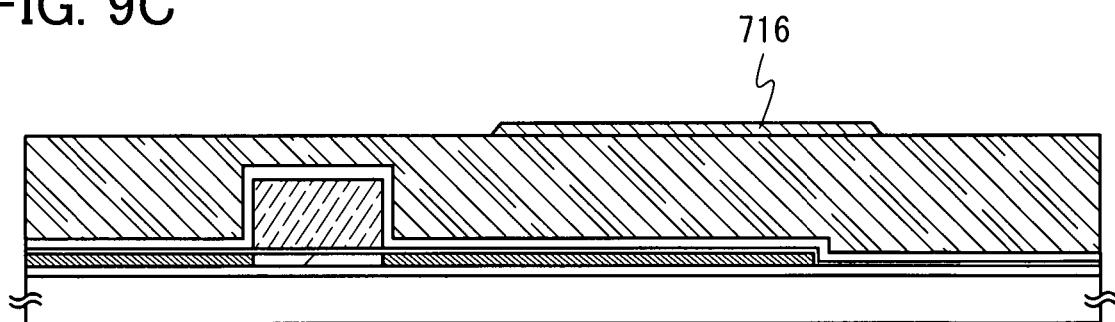

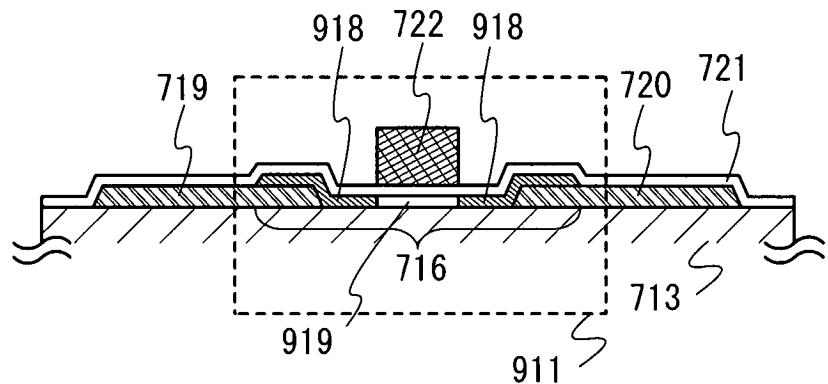

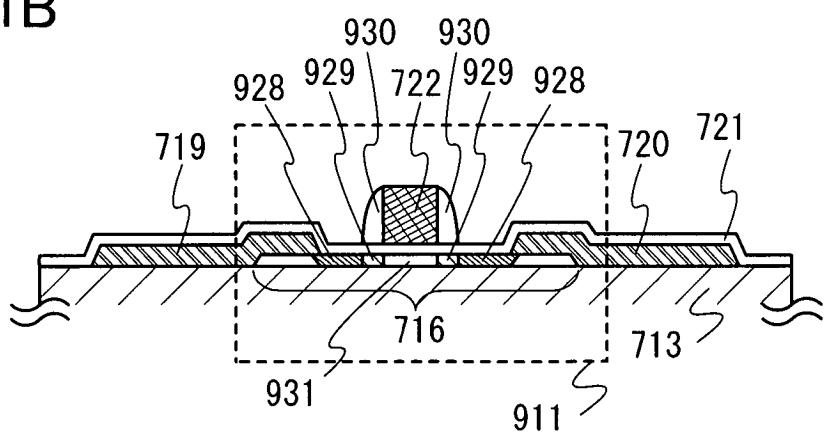

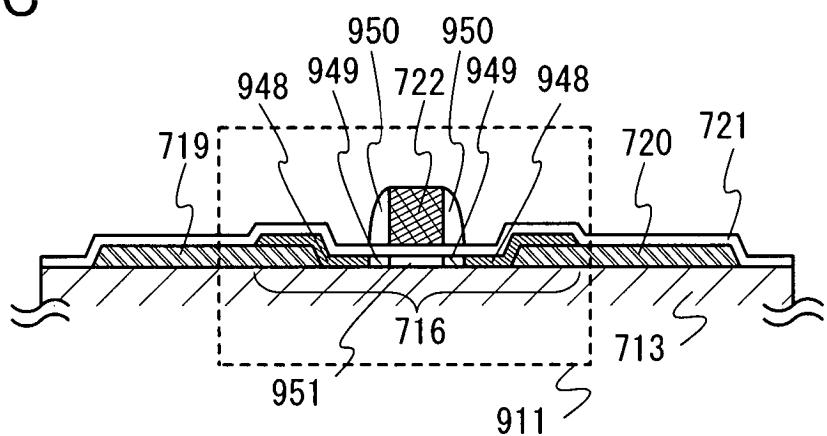

**[0039]** **Fig. 9A** bis **Fig. 9C** sind Querschnittsansichten, die einen Herstellungsprozess einer Signalverarbeitungsschaltung darstellen.

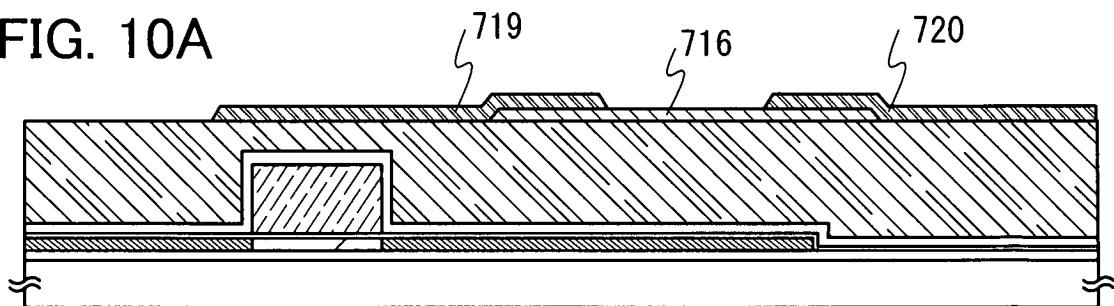

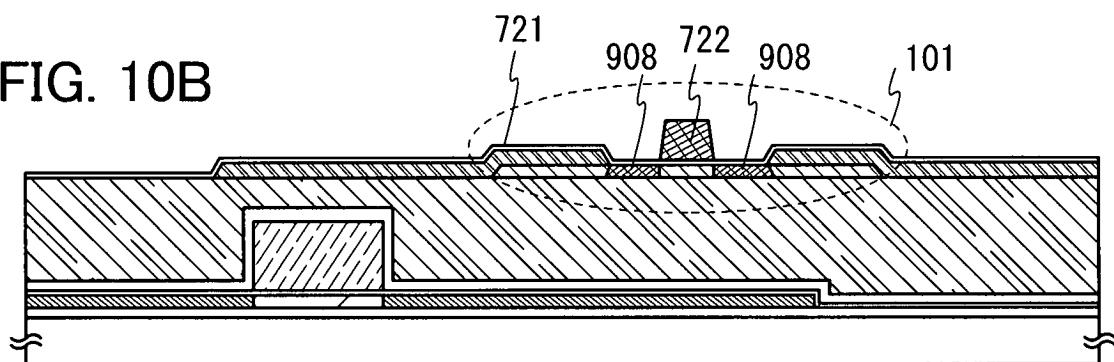

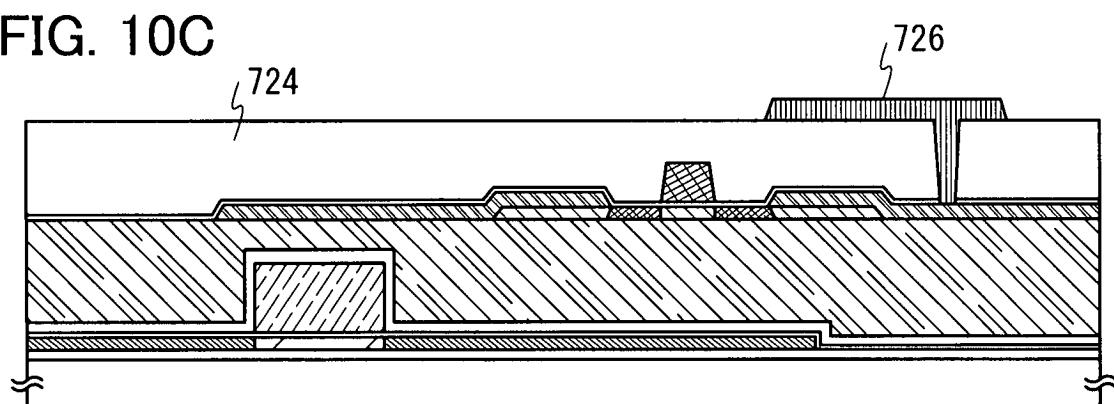

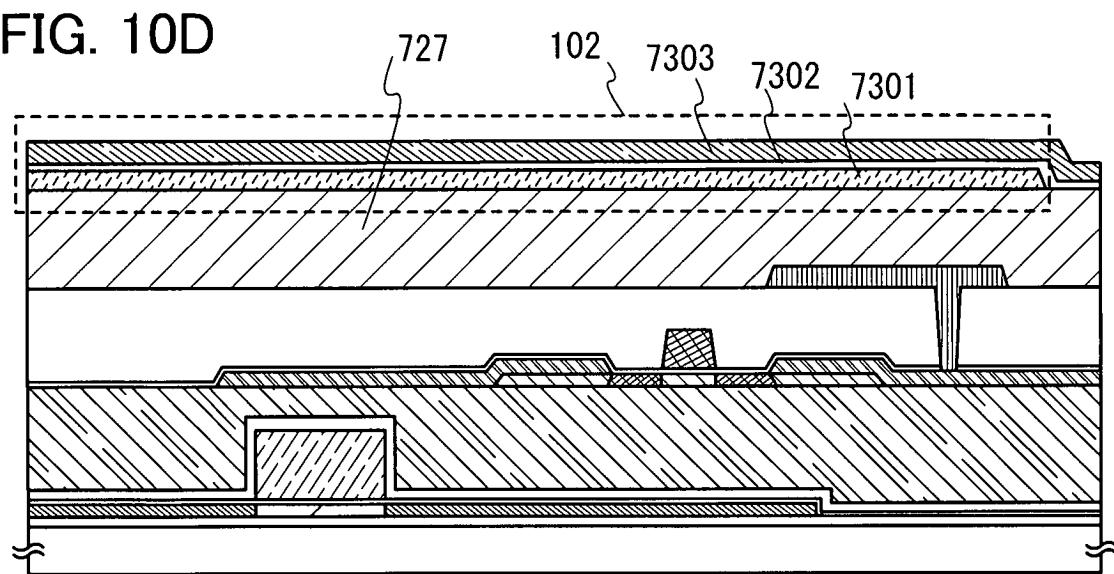

**[0040]** **Fig. 10A** bis **Fig. 10D** sind Querschnittsansichten, die einen Herstellungsprozess einer Signalverarbeitungsschaltung darstellen.

**[0041]** **Fig. 11A** bis **Fig. 11C** sind Querschnittsansichten, die jeweils eine Struktur eines Transistors mit einem Kanal in einer Oxidhalbleiterschicht darstellen.

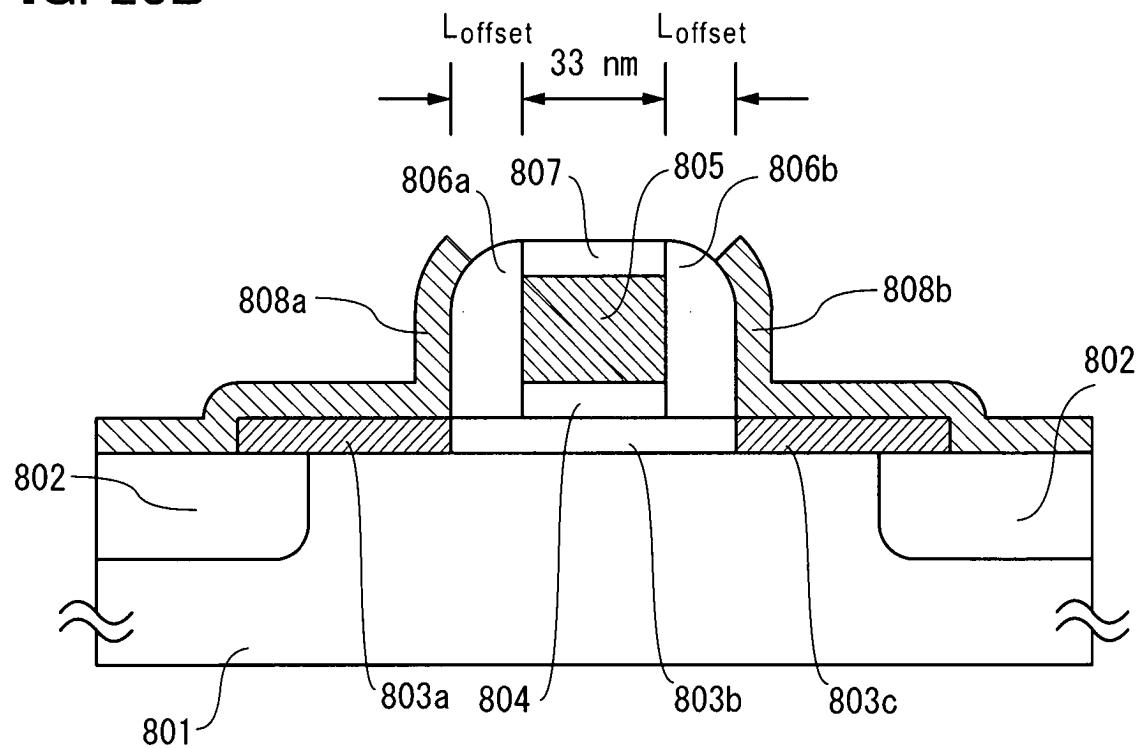

**[0042]** **Fig. 12A** und **Fig. 12B** sind Querschnittsansichten, die jeweils eine Struktur eines Transistors mit einem Kanal in einer Oxidhalbleiterschicht darstellen.

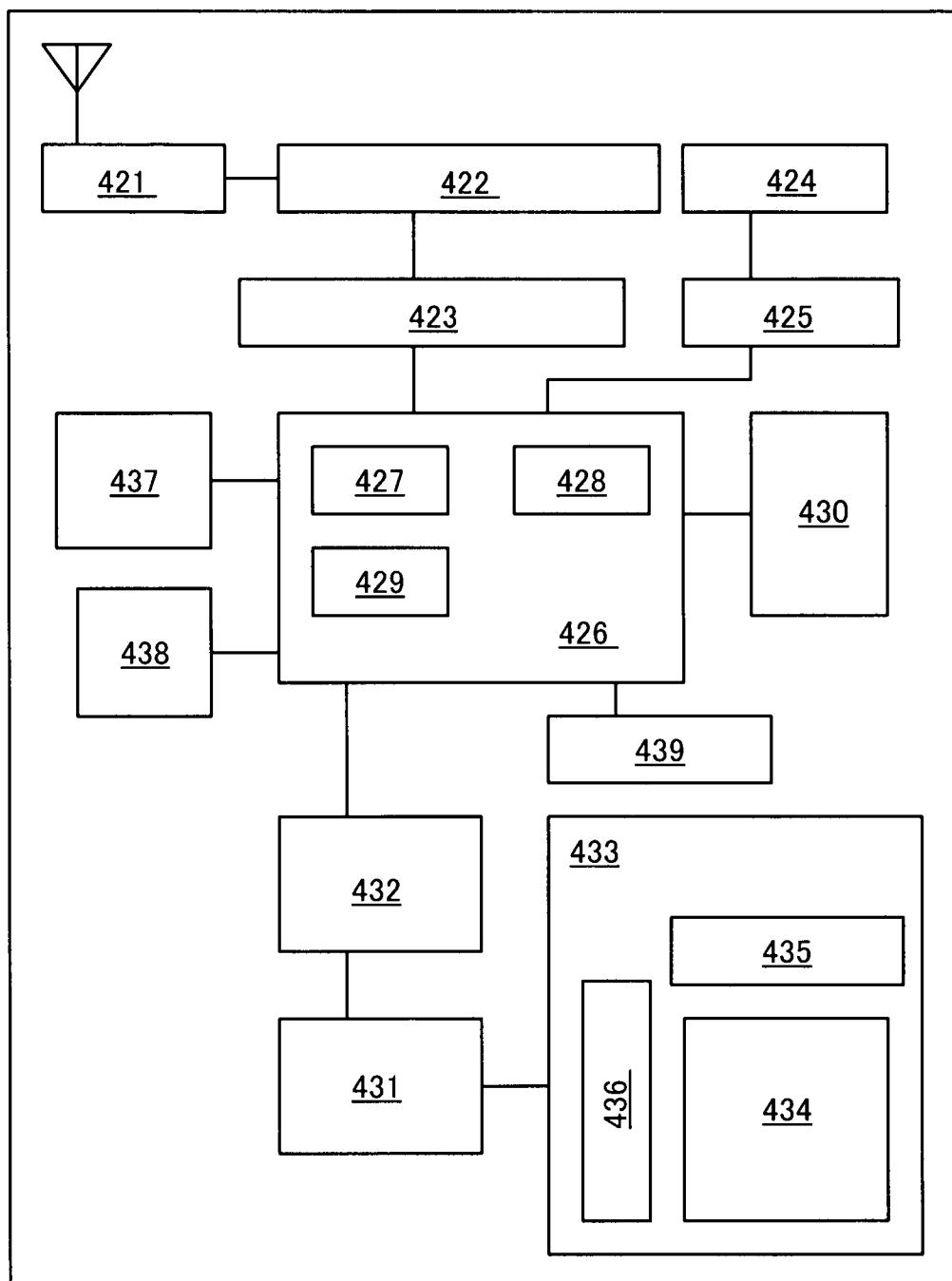

[0043] **Fig.** 13 ist ein Blockdiagramm einer tragbaren elektronischen Vorrichtung.

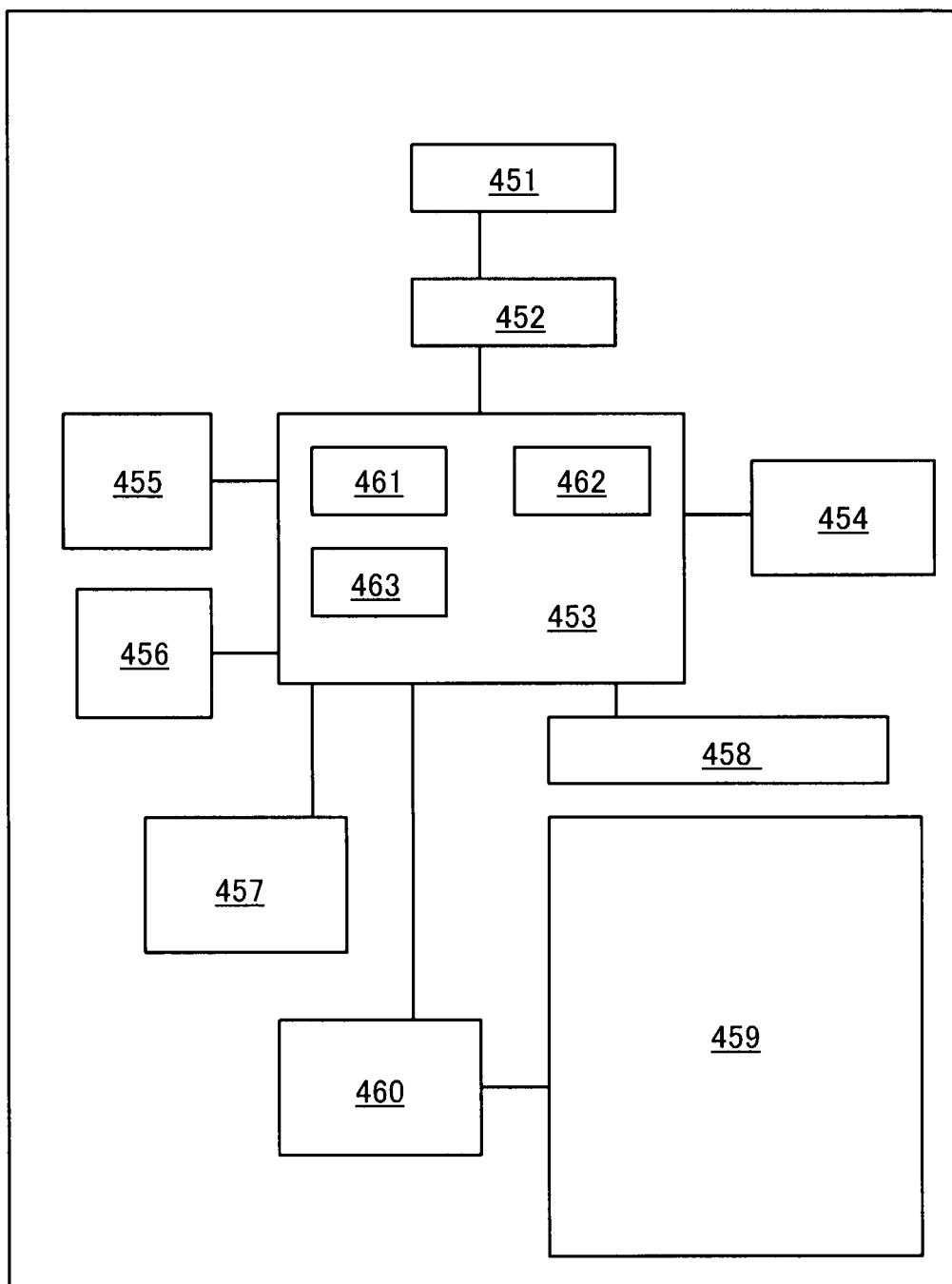

[0044] **Fig.** 14 ist ein Blockdiagramm eines E-Book-Lesegeräts.

[0045] **Fig.** 15 ist ein Flussdiagramm, das ein Verfahren zum Ansteuern einer Signalverarbeitungsschaltung darstellt.

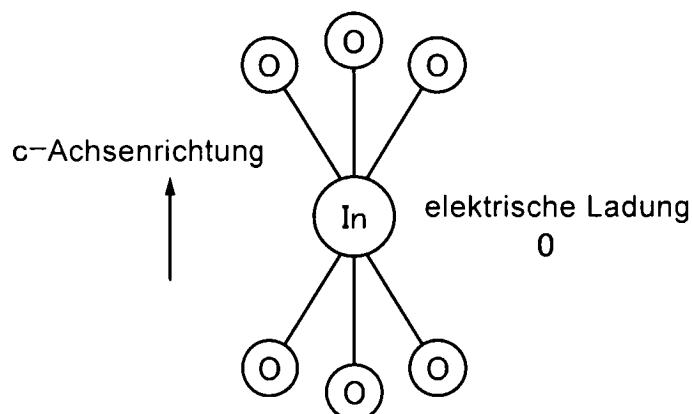

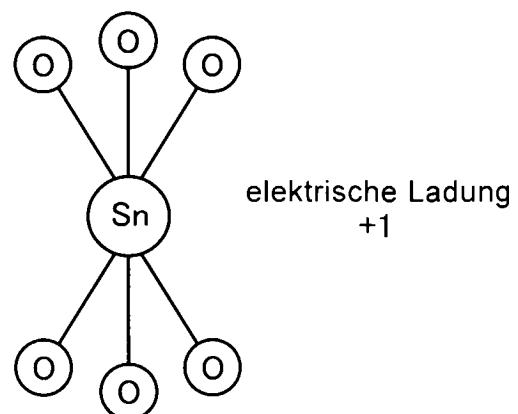

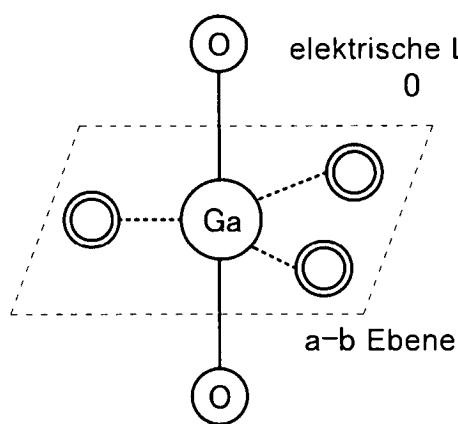

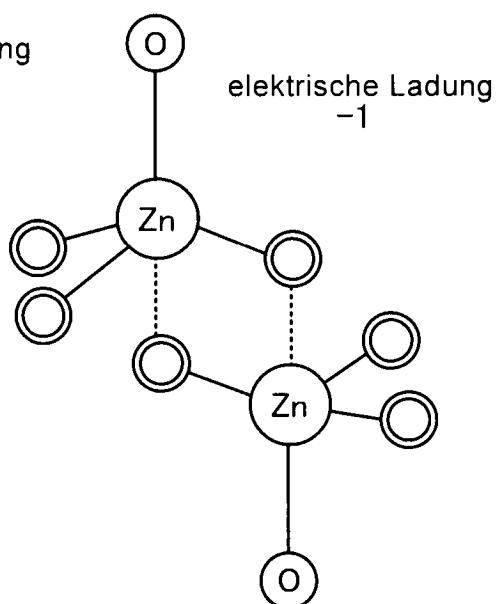

[0046] **Fig.** 16A bis **Fig.** 16E sind Diagramme, die jeweils eine Kristallstruktur eines Oxidmaterials darstellen.

[0047] **Fig.** 17A bis **Fig.** 17C sind Diagramme, die eine Kristallstruktur eines Oxidmaterials darstellen.

[0048] **Fig.** 18A bis **Fig.** 18C sind Diagramme, die eine Kristallstruktur eines Oxidmaterials darstellen.

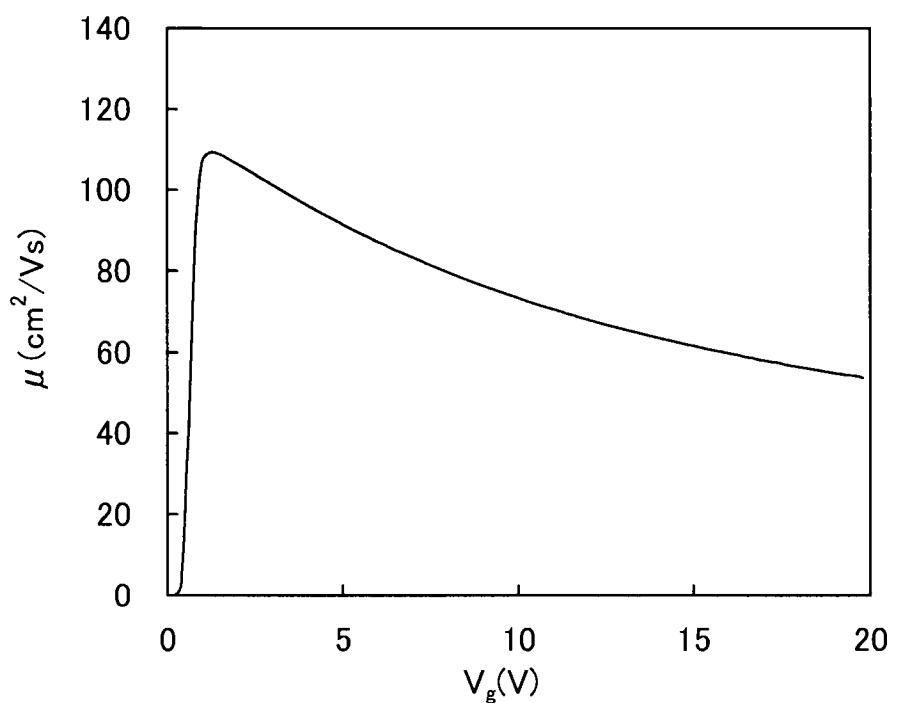

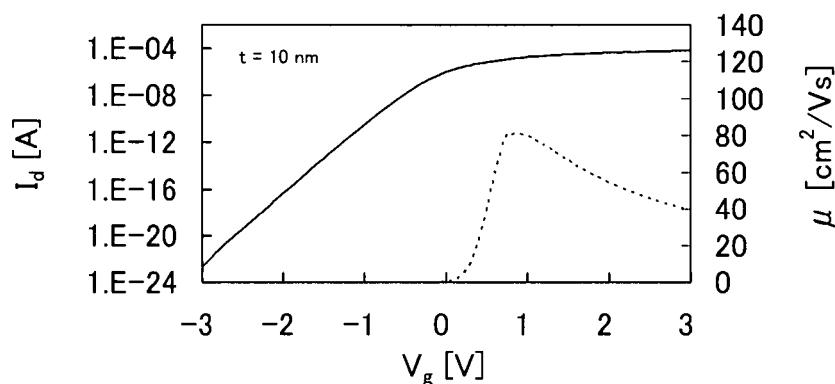

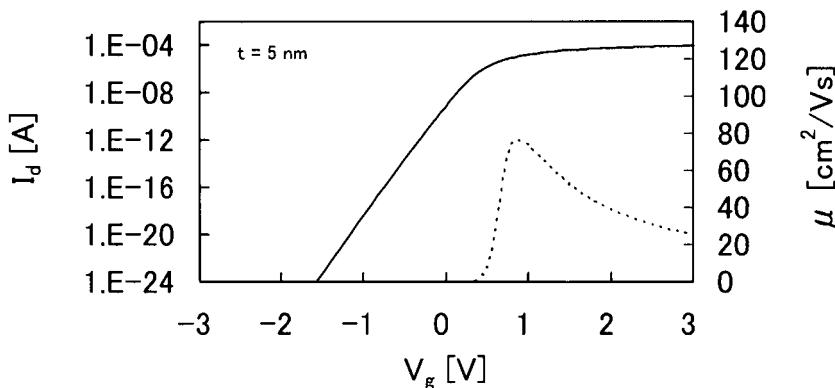

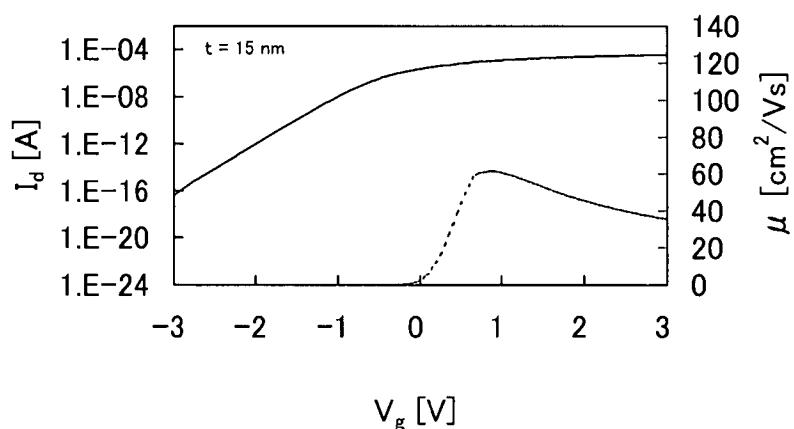

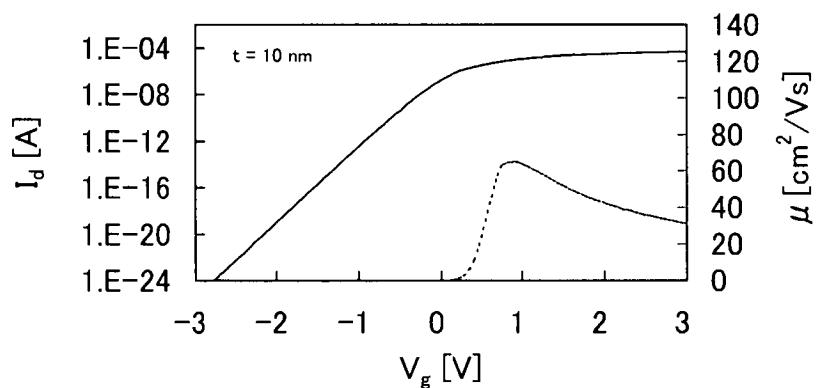

[0049] **Fig.** 19 zeigt die Mobilität in Abhängigkeit von der Gate-Spannung als Ergebnis einer Berechnung.

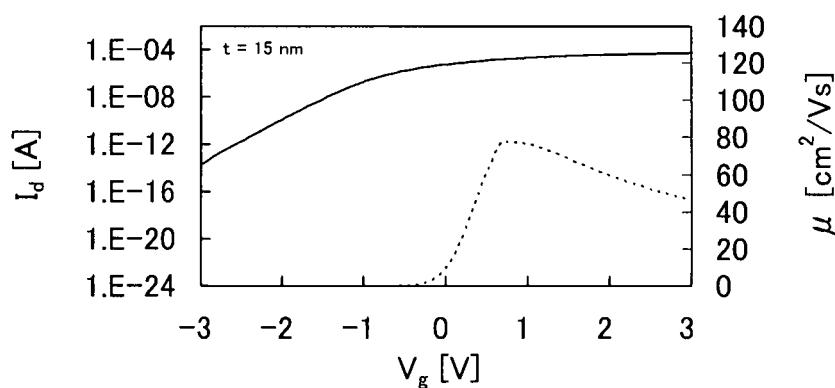

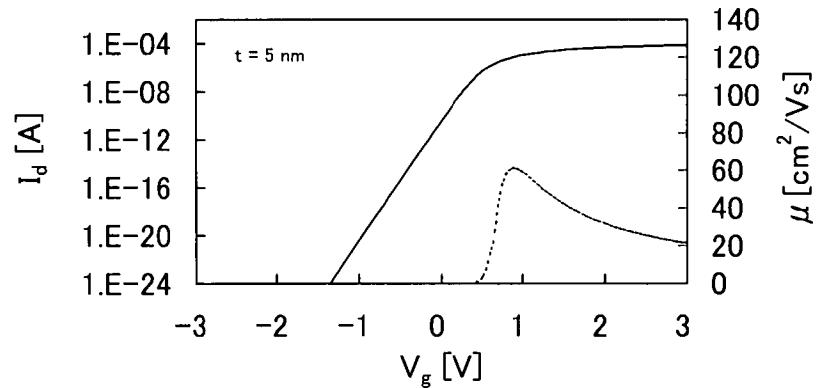

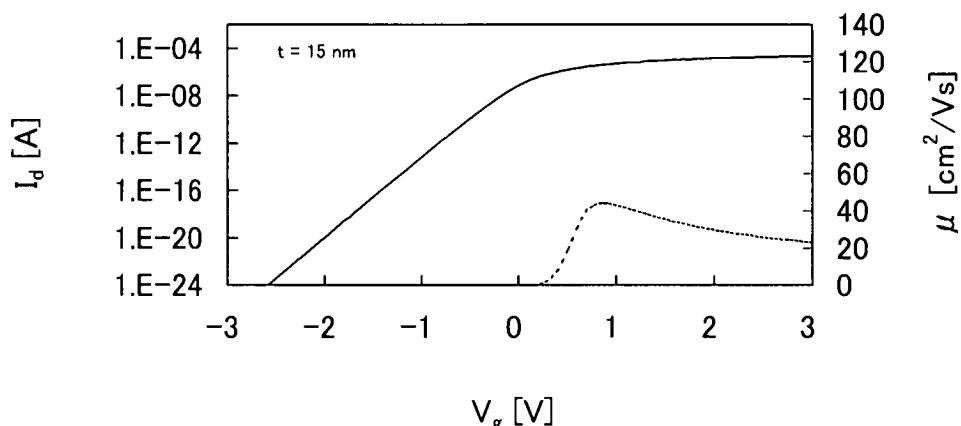

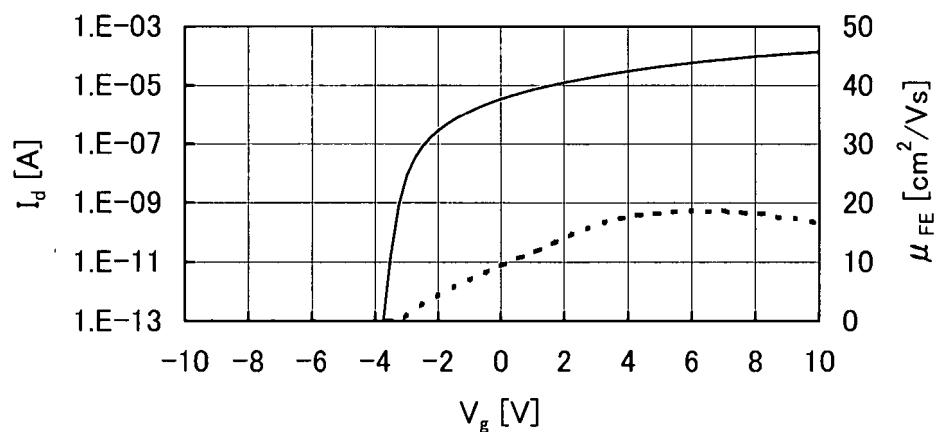

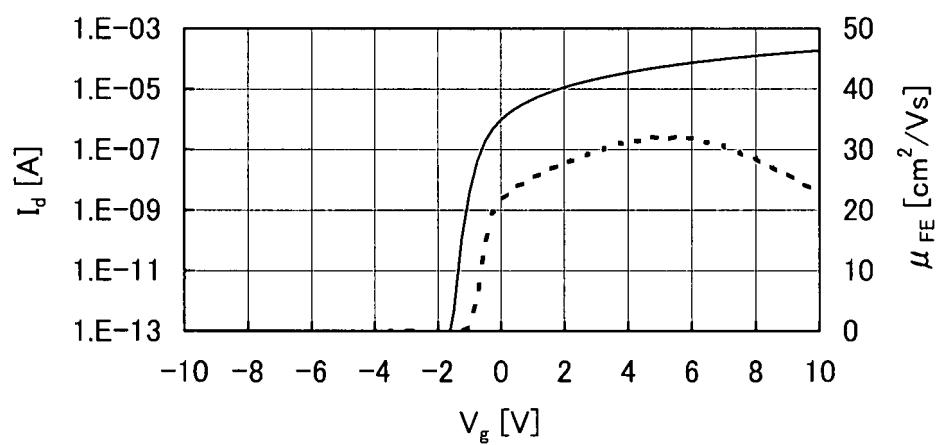

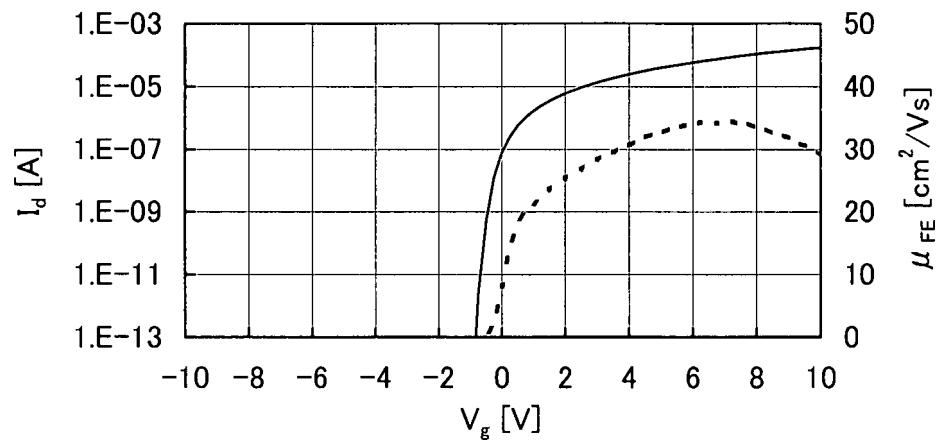

[0050] **Fig.** 20A bis **Fig.** 20C sind Diagramme, die jeweils den Drain-Strom und die Mobilität in Abhängigkeit von der Gate-Spannung als Ergebnis einer Berechnung zeigen.

[0051] **Fig.** 21A bis **Fig.** 21C sind Diagramme, die jeweils den Drain-Strom und die Mobilität in Abhängigkeit von der Gate-Spannung als Ergebnis einer Berechnung zeigen.

[0052] **Fig.** 22A bis **Fig.** 22C sind Diagramme, die jeweils den Drain-Strom und die Mobilität in Abhängigkeit von der Gate-Spannung als Ergebnis einer Berechnung zeigen.

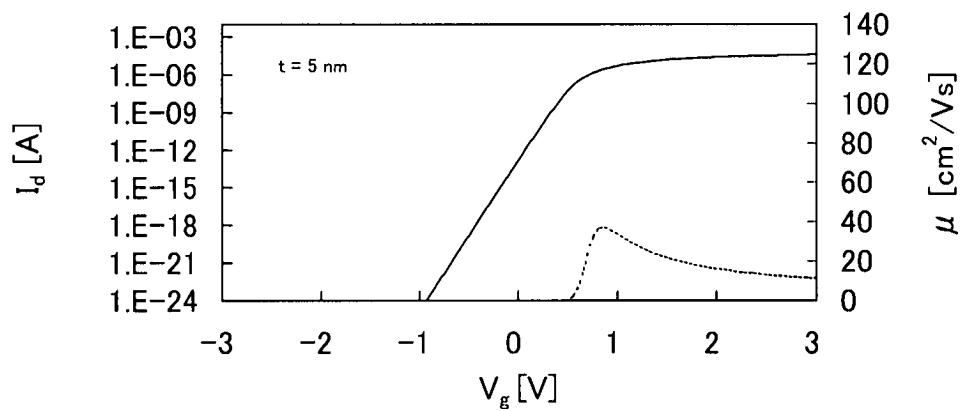

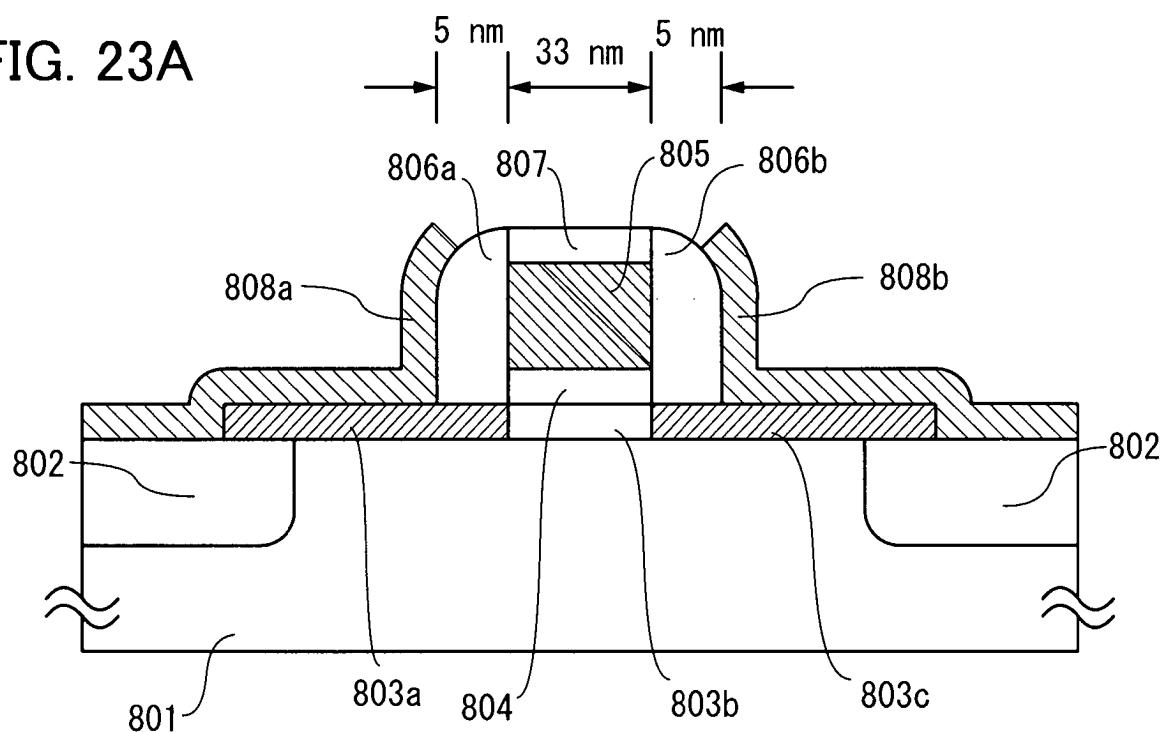

[0053] **Fig.** 23A und **Fig.** 23B sind Ansichten, die jeweils eine Querschnittsstruktur eines Transistors darstellen, der in der Berechnung verwendet wurde.

[0054] **Fig.** 24A bis **Fig.** 24C sind Diagramme, die jeweils Kennlinien eines Transistors mit einem Oxidhalbleiterfilm zeigen.

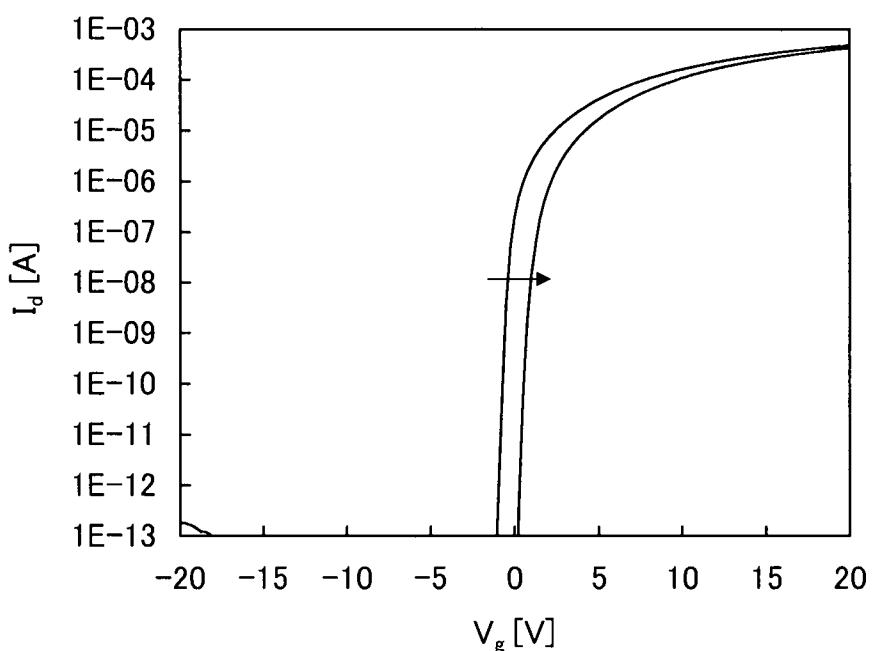

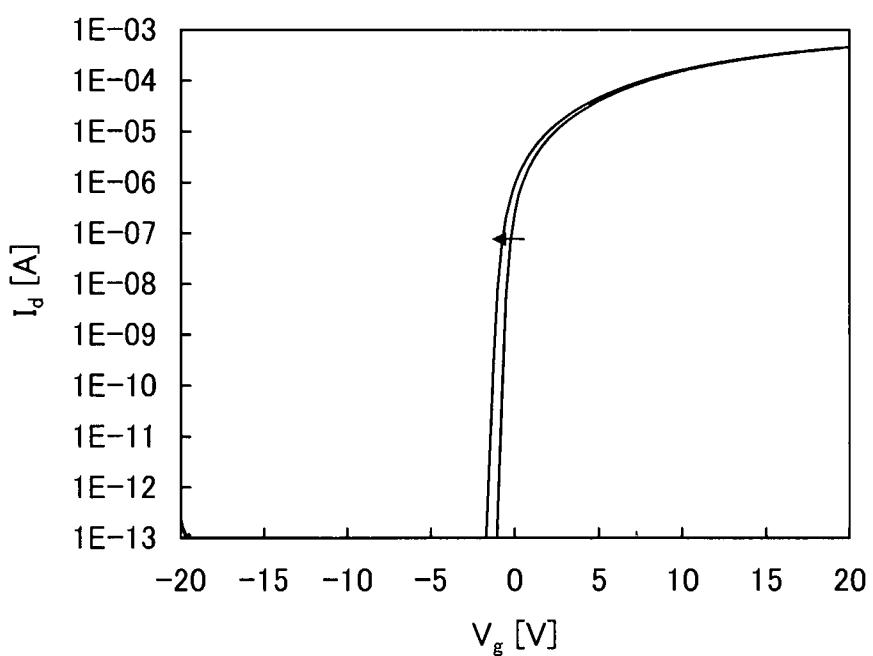

[0055] **Fig.** 25A und **Fig.** 25B sind Diagramme, die jeweils  $V_g$ - $I_d$  Kennlinien nach einem BT-Test eines Transistors der Probe 1 zeigen.

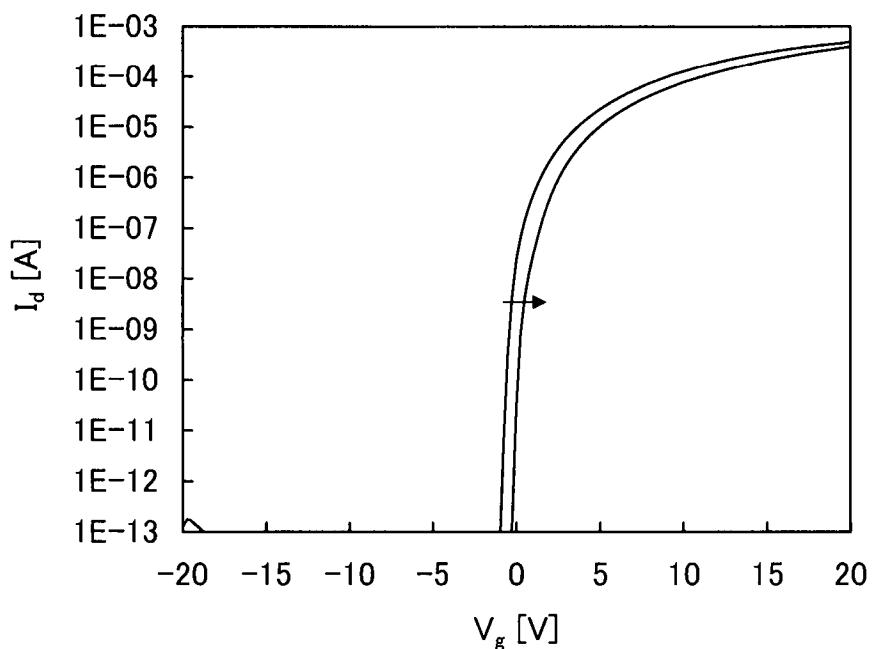

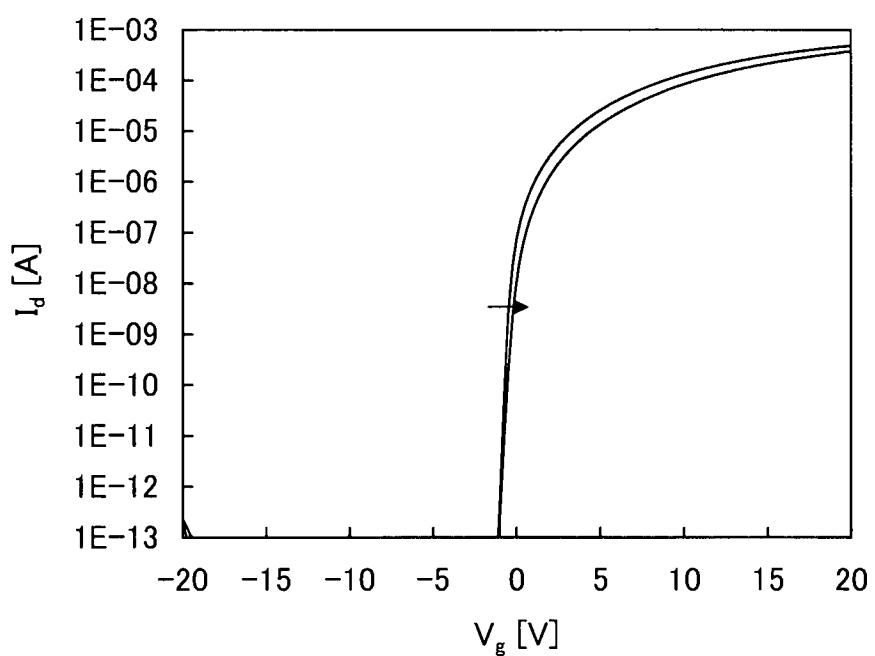

[0056] **Fig.** 26A und **Fig.** 26B sind Diagramme, die jeweils  $V_g$ - $I_d$  Kennlinien nach einem BT-Test eines Transistors der Probe 2 zeigen.

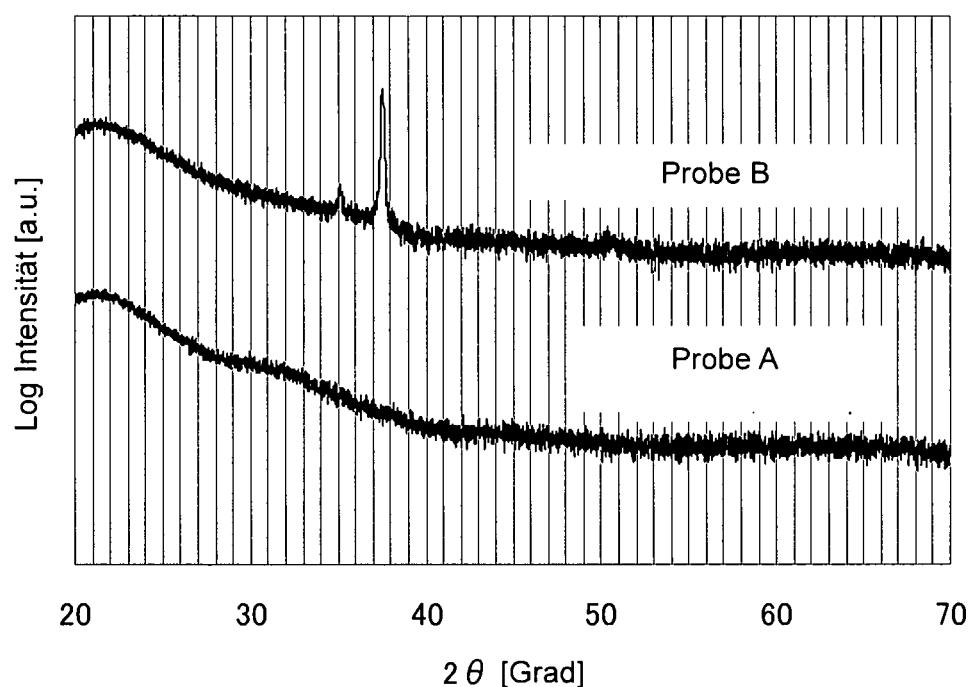

[0057] **Fig.** 27 zeigt XRD-Spektren von Probe A und Probe B.

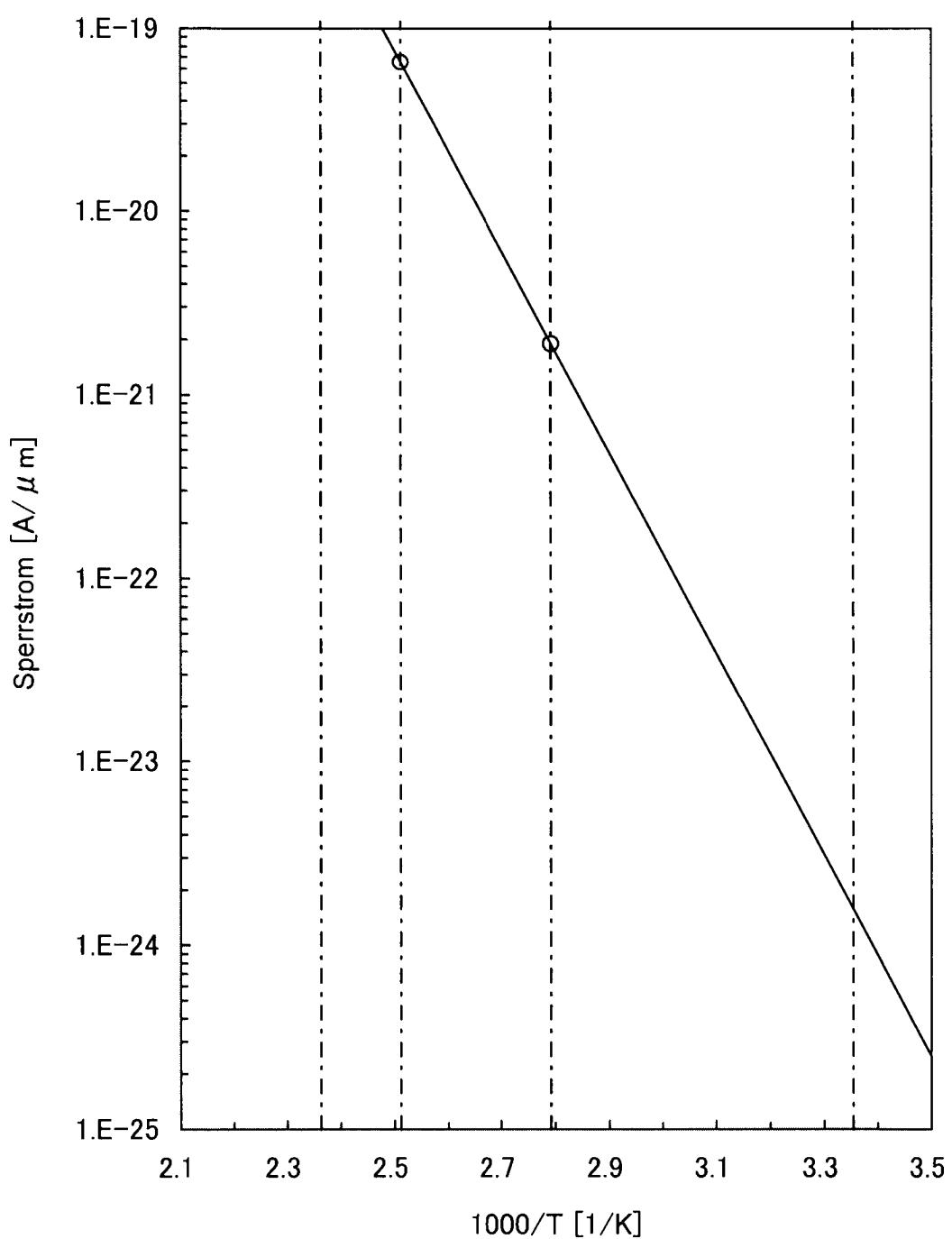

[0058] **Fig.** 28 ist ein Graph, der eine Beziehung zwischen Sperrstrom und Substrattemperatur bei Messung an einem Transistor zeigt.

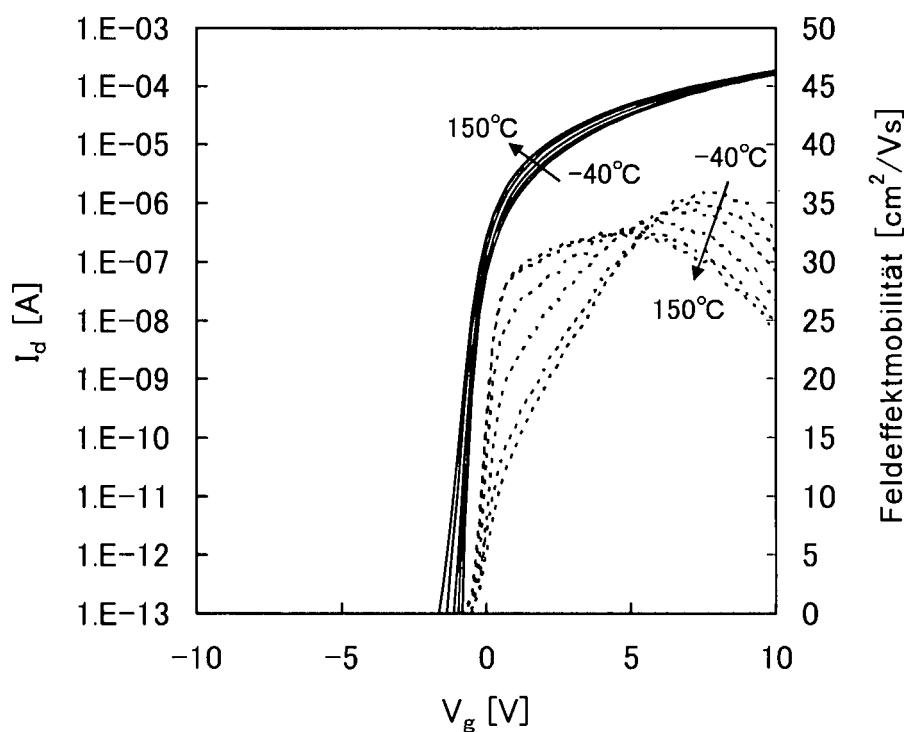

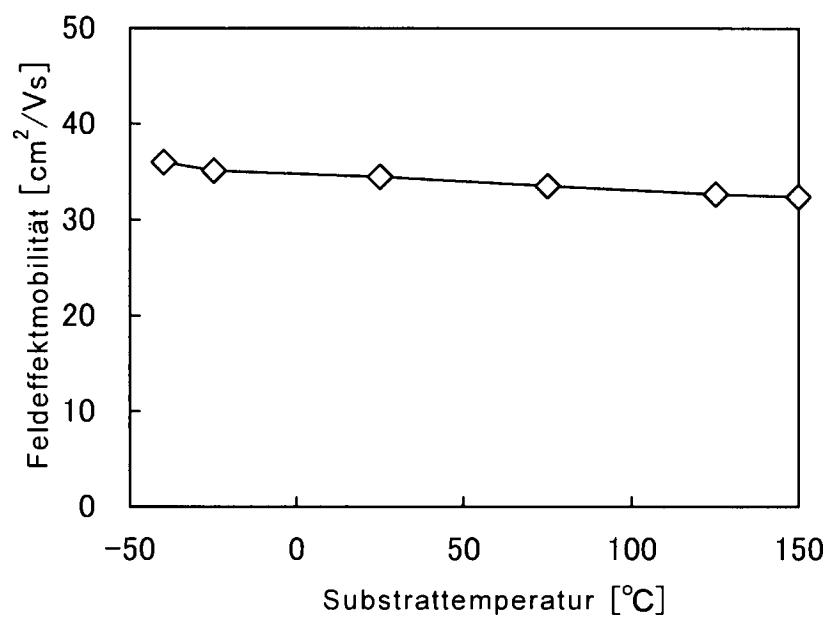

[0059] **Fig.** 29 ist ein Diagramm, das  $I_d$  und die Feldeffektmobilität in Abhängigkeit von  $V_g$  zeigt.

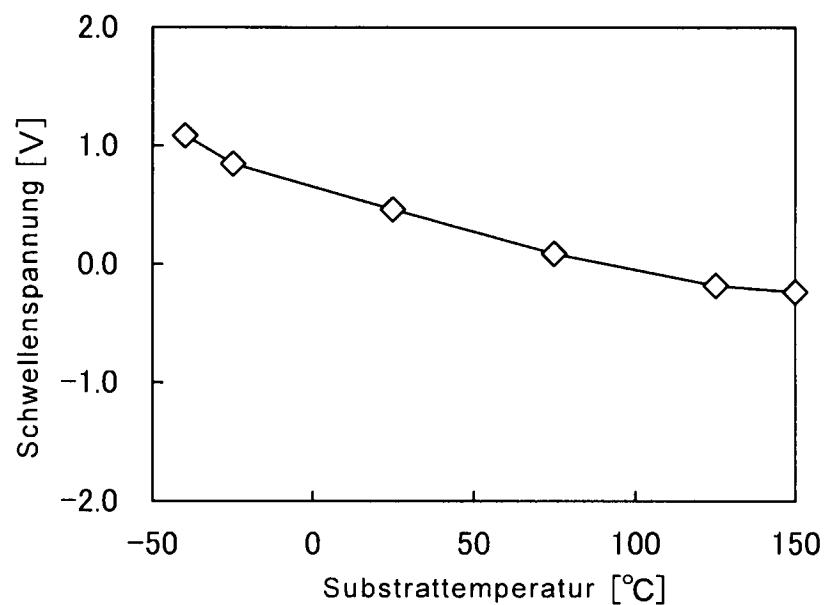

[0060] **Fig.** 30A ist ein Graph, der eine Beziehung zwischen Substrattemperatur und Schwellenspannung zeigt, und **Fig.** 30B ist ein Graph, der eine Beziehung zwischen Substrattemperatur und Feldeffektmobilität zeigt.

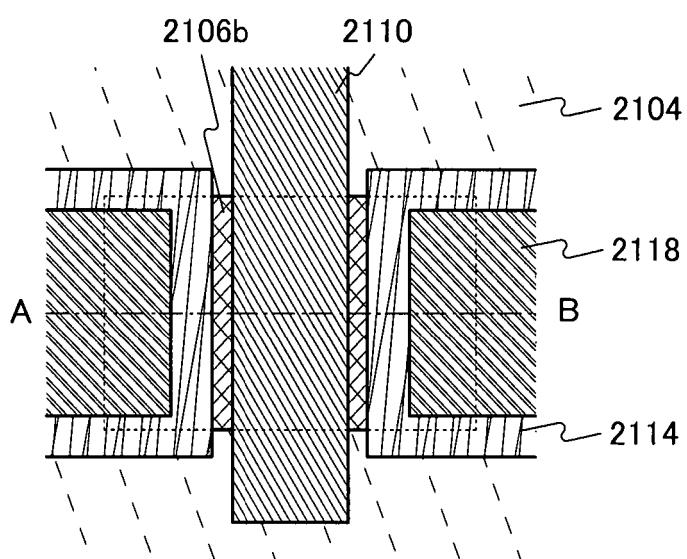

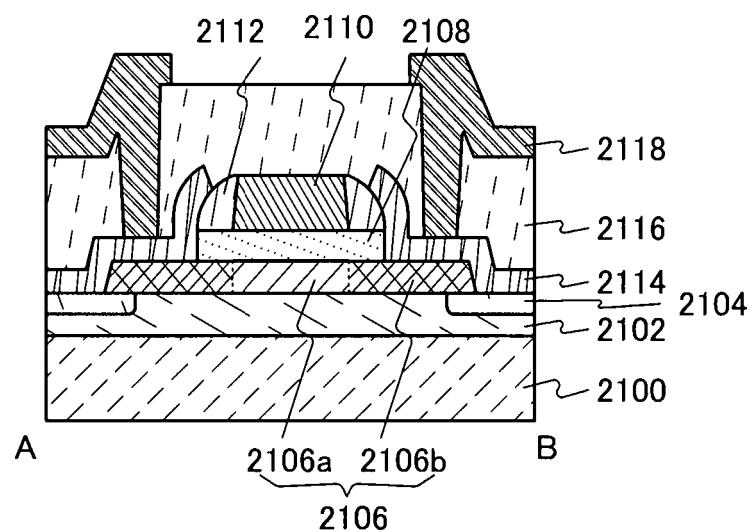

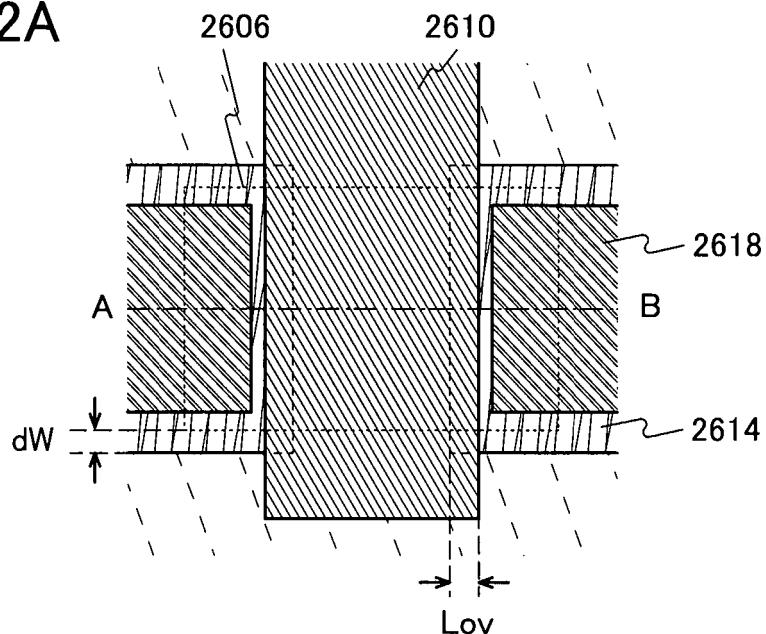

[0061] **Fig.** 31A und **Fig.** 31B sind eine Draufsicht und eine Querschnittsansicht, die eine beispielhafte Struktur eines Transistors darstellen.

[0062] **Fig.** 32A und **Fig.** 32B sind eine Draufsicht und eine Querschnittsansicht, die eine beispielhafte Struktur eines Transistors darstellen.

#### BEVORZUGTE AUSFÜHRUNG DER ERFINDUNG

[0063] Ausführungsformen und ein Beispiel der vorliegenden Erfindung werden nachfolgend unter Bezugnahme auf die beigelegten Zeichnungen beschrieben.

[0064] Man beachte, dass Funktionen der "Source" und der Drain beispielsweise in dem Fall, dass Transistoren unterschiedlicher Polaritäten eingesetzt werden, oder in dem Fall, dass die Richtung eines Stromflus-

ses sich während des Betriebs einer Schaltung ändert, vertauscht werden können. Daher können die Begriffe "Source" und "Drain" in dieser Beschreibung verwendet werden, um jeweils den Drain und die Source zu bezeichnen.

**[0065]** Man beachte, dass der Begriff "elektrisch verbunden" den Fall einschließt, in dem Komponenten durch ein "Objekt mit irgendeiner elektrischen Funktion" verbunden sind. Es gibt keine besondere Einschränkung für ein Objekt mit irgendeiner elektrischen Funktion, solange elektrische Signale zwischen Komponenten, die durch das Objekt verbunden sind, übertragen und empfangen werden können.

**[0066]** Darüber hinaus gibt es, auch wenn unabhängige Komponenten elektrisch miteinander in einem elektrischen Schaltplan verbunden sind, den Fall, in dem eine leitfähige Schicht die Funktionen einer Vielzahl von Komponenten besitzt, wie z. B. in dem Fall, in dem ein Teil einer elektrischen Leitung als eine Elektrode oder als ein Anschluss dient. Die "elektrische Verbindung" in dieser Beschreibung schließt in ihrer Kategorie einen solchen Fall ein, in dem eine leitfähige Schicht die Funktionen einer Vielzahl von Komponenten hat.

**[0067]** Die Begriffe "über" und "unter" bedeuten nicht zwingend "direkt auf" bzw. "direkt unter" in der Beschreibung einer physikalischen Beziehung zwischen den Komponenten. Zum Beispiel kann der Ausdruck "eine Gate-Elektrode über einem Gate-Isolierfilm" den Fall anzeigen, in dem eine zusätzliche Komponente zwischen dem Gate-Isolierfilm und der Gate-Elektrode vorliegt.

**[0068]** Man beachte, dass die Position, Größe, Ausdehnung oder dergleichen der einzelnen in den Zeichnungen dargestellten Komponenten und dergleichen in einigen Fällen zum besseren Verständnis nicht exakt dargestellt ist. Daher ist die offenbare Erfindung nicht notwendigerweise auf die Position, Größe, Ausdehnung oder dergleichen, wie in den Zeichnungen und dergleichen offenbart, beschränkt.

**[0069]** Die Ordinalzahlen wie z. B. "erste", "zweite" und "dritte" werden verwendet, um Verwechslungen zwischen Komponenten zu vermeiden.

[Ausführungsform 1]

**[0070]** Eine Weiterbildung einer Signalverarbeitungsschaltung wird beschrieben werden.

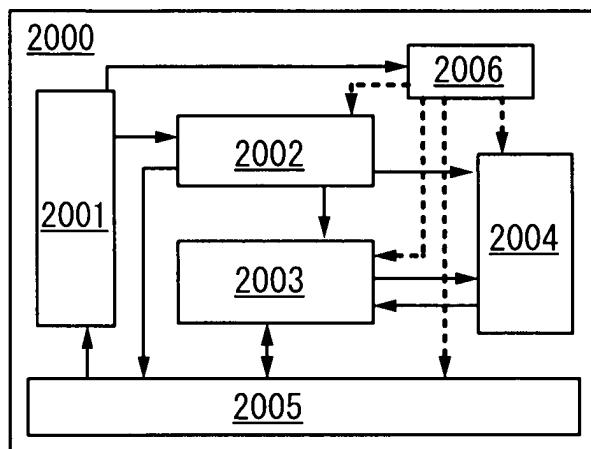

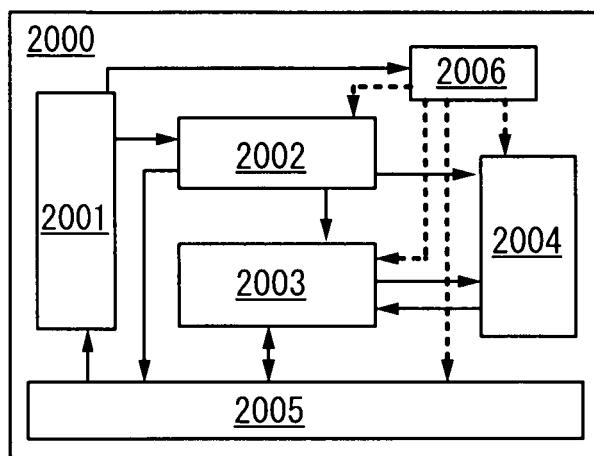

**[0071]** **Fig. 1A** ist ein Blockdiagramm, das schematisch eine Konfiguration einer Signalverarbeitungsschaltung darstellt. Eine Signalverarbeitungsschaltung **2000** enthält einen Decoder **2001**, eine Steuerschaltung **2002**, ein ALU **2003**, ein Register **2004**, einen Speicher **2005** und eine Stromversorgungsschaltung **2006**.

**[0072]** Der Decoder **2001** decodiert einen Befehl. Die Steuerschaltung **2002** steuert das Register **2004**, das ALU **2003** und den Speicher **2005** basierend auf dem decodierten Befehl. Das Register **2004** speichert vorübergehend Daten, die an das ALU **2003** eingegeben werden, und Daten, die von dem ALU **2003** ausgegeben werden. Dateneingabe/-ausgabe wird auch zwischen dem ALU **2003** und dem Speicher **2005** durchgeführt. Die Stromversorgungsschaltung **2006** wird von dem Decoder **2001** gesteuert, und die Stromversorgungsschaltung **2006** steuert die Bereitstellung von Versorgungsspannung an das ALU **2003**, die Steuerschaltung **2002**, das Register **2004** und den Speicher **2005**. Dabei kann die Stromversorgungsschaltung **2006** die Lieferung der Versorgungsspannung an alle Module (das ALU **2003**, die Steuerschaltung **2002**, das Register **2004** und den Speicher **2005**) stoppen und sie kann die Versorgungsspannung an alle Module liefern. Alternativ kann die Stromversorgungsschaltung **2006** selektiv Versorgungsspannung an einige der Module (wahlweise an das ALU **2003**, die Steuerschaltung **2002**, das Register **2004** und/oder den Speicher **2005**) liefern, und die Stromversorgungsschaltung **2006** kann die Bereitstellung von Versorgungsspannung an den anderen Modulen stoppen.

(Speicherschaltung für nichtflüchtigen Speicher)

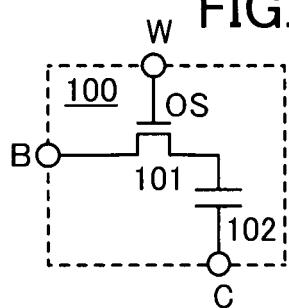

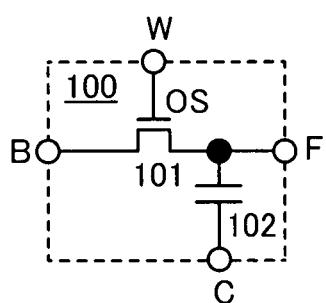

**[0073]** Die Steuerschaltung **2002**, das Register **2004** und der Speicher **2005** können jeweils eine Speicherschaltung für nichtflüchtigen Speicher **100** wie in **Fig. 1B** dargestellt aufweisen. Man beachte, dass das ALU **2003** ebenso die Speicherschaltung für nichtflüchtigen Speicher **100**, wie in **Fig. 1B** dargestellt, aufweisen kann. In der **Fig. 1B** umfasst die Speicherschaltung für nichtflüchtigen Speicher **100** einen Transistor **101** und einen Kondensator **102**. Ein Gate des Transistors **101** ist elektrisch mit einem Anschluss W verbunden. Ein Terminal aus Source und Drain des Transistors **101** ist elektrisch mit einem Anschluss B verbunden. Das andere Terminal aus Source und Drain des Transistors **101** ist elektrisch mit einer Elektrode des Kondensators **102** verbunden. Die andere Elektrode des Kondensators **102** ist elektrisch mit einem Anschluss C verbunden.

**[0074]** Hierbei kann ein Transistor mit extrem niedrigem Sperrstrom als der Transistor **101** verwendet werden. Die eine Elektrode des Kondensators **102** ist elektrisch mit einem Knoten verbunden, der in einen potenzialfreien (schwebenden) Zustand versetzt wird, wenn der Transistor **101** ausgeschaltet ist. Daten werden in der Speicherschaltung für nichtflüchtigen Speicher **100** durch Steuerung des Potenzials (oder der Menge an elektrischer Ladung, die dem Potenzial entspricht) der einen Elektrode des Kondensators **102** in Abhängigkeit von den Daten gespeichert. Zum Beispiel wird ein Zustand, in dem eine vorbestimmte elektrische Ladung in dem Kondensator **102** akkumuliert wurde, dem Wert "1" gleichgesetzt und ein Zustand, in dem die vorbestimmte elektrische Ladung nicht in dem Kondensator **102** akkumuliert wurde, dem Wert "0" gleichgesetzt, wodurch 1-Bit-Daten gespeichert werden können. Hierbei ist es möglich, einen Transistor mit einem Kanal in einer Schicht oder einem Substrat mit einem Halbleiter, dessen Bandlücke größer als die von Silicium ist, als den Transistor **101**, dessen Sperrstrom extrem niedrig ist, zu verwenden. Ein Verbindungshalbleiter ist ein Beispiel für einen Halbleiter, dessen Bandlücke größer als die von Silicium ist. Beispiele für den Verbindungshalbleiter umfassen einen Oxidhalbleiter, einen Nitridhalbleiter und dergleichen. Beispielsweise kann ein Transistor mit einem Kanal in einer Oxidhalbleiterschicht verwendet werden. **Fig. 1B** zeigt ein Beispiel, bei dem ein Transistor mit einem Kanal in einer Oxidhalbleiterschicht als der Transistor **101**, neben dem "OS" steht, verwendet wird.

(Verfahren zur Ansteuerung der Speicherschaltung für nichtflüchtigen Speicher **100**)

**[0075]** In der Speicherschaltung für nichtflüchtigen Speicher **100** wird der Transistor **101** in Reaktion auf ein Steuersignal, welches an dem Anschluss W eingegeben wird, angeschaltet, und ein Potenzial eines Signals, welches einem Datenwert entspricht, wird an dem Anschluss B eingegeben. Dann wird der Datenwert, wenn der Transistor **101** durch ein an dem Anschluss W eingegebenes Steuersignal ausgeschaltet wird, gehalten. Die Speicherschaltung für nichtflüchtigen Speicher **100** kann eine Konfiguration haben, in der ein vorgegebenes Potenzial an dem Anschluss C bereitgestellt wird. Zum Beispiel kann ein Massepotenzial an dem Anschluss C bereitgestellt werden. Da der Sperrstrom des Transistors **101** äußerst gering ist, kann das Potenzial der einen Elektrode des Kondensators **102** für eine lange Zeit gehalten werden, selbst nachdem die Bereitstellung der Versorgungsspannung beendet ist. Daten werden aus der Speicherschaltung für nichtflüchtigen Speicher **100** in der folgenden Weise gelesen: Der Transistor **101** wird in Reaktion auf das an dem Anschluß W eingegebene Steuersignal angeschaltet, und das Potenzial (oder die Menge an elektrischer Ladung, die dem Potenzial entspricht) der einen Elektrode des Kondensators **102** wird von dem Anschluss B registriert. Die Speicherschaltung für nichtflüchtigen Speicher **100** speichert Daten in einer Weise, dass ein Potenzial eines Signals, das den Daten entspricht, an einem vorbestimmten Knoten (der einen Elektrode des Paares der Elektroden des Kondensators **102**) eingegeben wird, der Transistor **101** mit extrem niedrigem Sperrstrom ausgeschaltet wird, und der Knoten in einen schwebenden Zustand versetzt wird. In der Speicherschaltung für nichtflüchtigen Speicher **100** können daher ein Altern der Speicherschaltung für nichtflüchtigen Speicher **100** durch wiederholtes Schreiben von Daten reduziert und die Anzahl der Male, die Daten geschrieben werden können, erhöht werden.

(Konfigurationen der Steuerschaltung **2002**, des Registers **2004** und des ALU **2003**)

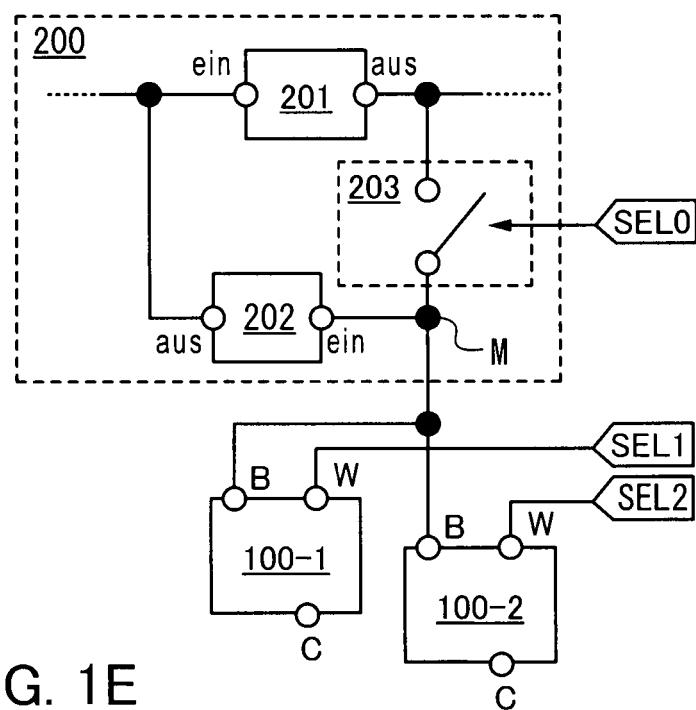

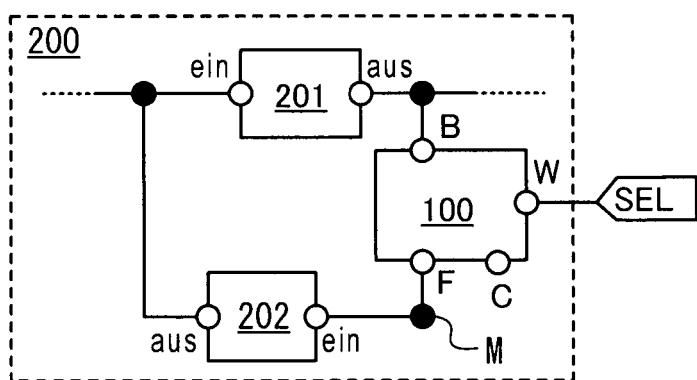

**[0076]** Hier können die Steuerschaltung **2002** und das Register **2004** oder die Steuerschaltung **2002**, das Register **2004** und das ALU **2003** jeweils eine Gruppe aus einer Speicherschaltung für flüchtigen Speicher und der Speicherschaltung für nichtflüchtigen Speicher **100**, die in **Fig. 1B** dargestellt ist, aufweisen. **Fig. 1C** ist ein Diagramm, das die Konfiguration der Gruppe darstellt. **Fig. 1C** zeigt ein Beispiel, in dem die zwei Speicherschaltungen für nichtflüchtigen Speicher **100** aus **Fig. 1B** (eine Speicherschaltung für nichtflüchtigen Speicher **100-1** und eine Speicherschaltung für nichtflüchtigen Speicher **100-2**) für eine Speicherschaltung für flüchtigen Speicher **200** zum Speichern von 1-Bit-Daten vorgesehen sind. Ohne Einschränkung des oben Gesagten können eine Speicherschaltung für nichtflüchtigen Speicher **100** aus **Fig. 1B** oder drei oder mehr Speicherschaltungen für nichtflüchtigen Speicher **100** aus **Fig. 1B** für die Speicherschaltung für flüchtigen Speicher **200** zum Speichern von 1-Bit-Daten bereitgestellt werden. Insbesondere kann in dem Register **2004** eine Anordnung, die eine Gruppe aus der Vielzahl von Speicherschaltungen für nichtflüchtigen Speicher **100** aufweist, die für die Speicherschaltung für flüchtigen Speicher **200** zum Speichern von 1-Bit-Daten vorgesehen sind, verwendet werden. In jedem von der Steuerschaltung **2002** und dem ALU **2003** kann eine Konfiguration mit einer Gruppe aus einer Speicherschaltung für nichtflüchtigen Speicher **100**, die für die Speicherschaltung für flüchtigen Speicher **200** zum Speichern von 1-Bit-Daten vorgesehen ist, verwendet werden.

**[0077]** Die Speicherschaltung für flüchtigen Speicher **200** kann mindestens zwei arithmetische Schaltungen aufweisen, die eine Rückkopplungsschleife bilden können, in der eine Ausgabe von einer der arithmetischen Schaltungen in die andere der arithmetischen Schaltungen eingegeben wird und eine Ausgabe der anderen der arithmetischen Schaltungen in die eine der arithmetischen Schaltungen eingegeben wird. In **Fig. 1C** sind

eine arithmetische Schaltung **201** und eine arithmetische Schaltung **202** enthalten, die eine Rückkopplungsschleife bilden, in der ein Ausgangssignal der arithmetischen Schaltung **201** in die arithmetische Schaltung **202** eingegeben wird und ein Ausgangssignal der arithmetischen Schaltung **202** in die arithmetische Schaltung **201** eingegeben wird. Beispiele für die arithmetische Schaltung umfassen eine Inverter-Schaltung und eine NAND-Schaltung. Eine Flipflop-Schaltung und eine Verriegelungsschaltung (Latch-Schaltung) können als Beispiele für die Speicherschaltung für nichtflüchtigen Speicher **200** mit einer solchen Anordnung angegeben werden.

**[0078]** Ein Anschluss B der Speicherschaltung für nichtflüchtigen Speicher **100-1** und ein Anschluss B der Speicherschaltung für nichtflüchtigen Speicher **100-2** sind jeweils elektrisch mit einem Knoten M verbunden, der zwischen einem Eingangsanschluss der arithmetischen Schaltung **202** und einem Ausgangsanschluss der arithmetischen Schaltung **201** vorliegt. Die Speicherschaltung für flüchtigen Speicher **200** enthält einen Schalter **203** für die Auswahl einer elektrischen Verbindung zwischen dem Knoten M und dem Ausgangsanschluss der arithmetischen Schaltung **201**. Ein leitender Zustand oder ein nicht leitender Zustand des Schalters **203** wird mittels eines Steuersignals SEL0 ausgewählt. Man beachte, dass der Schalter **203** in dem Fall, dass die arithmetische Schaltung **201** eine Schaltung zum selektiven Ausgeben eines Signals in Reaktion auf ein Steuersignal (z. B. ein Taktsignal) ist, nicht notwendigerweise vorgesehen ist und weggelassen werden kann. Ein Steuersignal SEL1 wird an einem Anschluss W der Speicherschaltung für nichtflüchtigen Speicher **100-1** eingegeben und ein Steuersignal SEL2 wird an einem Anschluss W der Speicherschaltung für nichtflüchtigen Speicher **100-2** eingegeben. Man beachte, dass das gleiche Potenzial an einem Anschluss C der Speicherschaltung für nichtflüchtigen Speicher **100-1** und an einem Anschluss C der Speicherschaltung für nichtflüchtigen Speicher **100-2** eingegeben wird.

**[0079]** Als nächstes wird ein Verfahren zum Ansteuern der Gruppe aus der Speicherschaltung für flüchtigen Speicher **200**, der Speicherschaltung für nichtflüchtigen Speicher **100-1** und der Speicherschaltung für nichtflüchtigen Speicher **100-2**, die in **Fig. 1C** dargestellt ist, beschrieben.

(Betrieb während der Bereitstellung der Versorgungsspannung)

**[0080]** Während eine Versorgungsspannung an die Gruppe geliefert wird, das heißt, während eine Versorgungsspannung an ein Modul, das die Gruppe enthält, geliefert wird, ist der Schalter **203** in einem leitenden Zustand aufgrund des Steuersignals SEL0. Auf diese Weise speichert die Speicherschaltung für flüchtigen Speicher **200** Daten mit Hilfe der Rückkopplungsschleife, die aus der arithmetischen Schaltung **201** und der arithmetischen Schaltung **202** gebildet wird. Das heißt, dass in der in **Fig. 1C** dargestellten Gruppe Eingabedaten durch die Rückkopplungsschleife der Speicherschaltung für flüchtigen Speicher **200** gehalten werden, und Daten von der Rückkopplungsschleife der Speicherschaltung für flüchtigen Speicher **200** ausgegeben werden. Daten können durch die Rückkopplungsschleife der Speicherschaltung für flüchtigen Speicher **200** gehalten und mit hoher Geschwindigkeit ausgegeben werden.

(Vorgang zur Datenspeicherung)

**[0081]** Wie oben beschrieben wird, während oder nachdem Daten mittels der Rückkopplungsschleife der Speicherschaltung für flüchtigen Speicher **200** gehalten werden, der Transistor **101** der Speicherschaltung für nichtflüchtigen Speicher **100-1** oder der Transistor **101** der Speicherschaltung für nichtflüchtigen Speicher **100-2** selektiv in Reaktion auf das Steuersignal SEL1 und das Steuersignal SEL2 eingeschaltet, wobei der Schalter **203** durch das Steuersignal SEL0 in einem leitenden Zustand gehalten wird. Zum Beispiel wird der Transistor **101** der Speicherschaltung für nichtflüchtigen Speicher **100-1** eingeschaltet, und der Transistor **101** der Speicherschaltung für nichtflüchtigen Speicher **100-2** wird ausgeschaltet. Auf diese Weise wird das Potenzial des Knotens M der Speicherschaltung für flüchtigen Speicher **200** an eine Elektrode des Kondensators **102** der Speicherschaltung für nichtflüchtigen Speicher **100-1** eingegeben, so dass die Daten, die in der Speicherschaltung für flüchtigen Speicher **200** gehalten werden, in der Speicherschaltung für nichtflüchtigen Speicher **100-1** gespeichert werden. Somit können die Daten gespeichert werden.

(Vorgang zur Datenbereithaltung)

**[0082]** Nachdem die Daten gespeichert sind, wird bewirkt, dass sich die Daten, die in der Speicherschaltung für nichtflüchtigen Speicher **100-1** gespeichert sind, nicht in Reaktion auf ein Signal von der Speicherschaltung für flüchtigen Speicher **200** ändern, indem der Transistor **101** der Speicherschaltung für nichtflüchtigen Speicher **100-1** ausgeschaltet wird. Somit kann ein Bereithalten der Daten durchgeführt werden.

**[0083]** In der Konfiguration, in der die Vielzahl von Speicherschaltungen für nichtflüchtigen Speicher **100** aus Fig. 1B für die Speicherschaltung für flüchtigen Speicher **200** zum Speichern von 1-Bit-Daten vorgesehen ist, kann in dem Fall, in dem die Speicherschaltung für flüchtigen Speicher **200** verschiedene Daten zu verschiedenen Zeiten hält, eine Vielzahl von Portionen von Daten, die den Zeiten entsprechen, in den verschiedenen Speicherschaltungen für nichtflüchtigen Speicher **100** gespeichert werden. Insbesondere kann jede der Vielzahl von Speicherschaltungen für nichtflüchtigen Speicher **100** in dem Register in dem Fall, dass eine Konfiguration verwendet wird, die eine Gruppe aus der Vielzahl von Speicherschaltungen für nichtflüchtigen Speicher **100** umfasst, die für die Speicherschaltung für flüchtigen Speicher **200** zum Speichern von 1-Bit-Daten vorgesehen ist, als eine (Speicher-)Bank bezeichnet werden. Auf diese Weise kann jeder der Zustände des Registers zu unterschiedlichen Zeiten in der Vielzahl von Bänken gespeichert werden.

**[0084]** Man beachte, dass sogar in dem Fall, in dem eine Anordnung verwendet wird, die eine Gruppe aus der einen Speicherschaltung für nichtflüchtigen Speicher **100** umfasst, die für die Speicherschaltung für flüchtigen Speicher **200** zum Speichern von 1-Bit-Daten vorgesehen ist, Daten, die in der Speicherschaltung für flüchtigen Speicher **200** gehalten werden, in der Speicherschaltung für nichtflüchtigen Speicher **100** durch einen Vorgang ähnlich dem oben beschriebenen Vorgang gespeichert werden können. Somit kann eine Datenbereithaltung durchgeführt werden.

**[0085]** Wie oben beschrieben wird Zufuhr der Versorgungsspannung nach der Bereithaltung der Daten gestoppt.

(Vorgang bei Bereitstellung der Daten)

**[0086]** Nachdem die Lieferung der Versorgungsspannung an die Gruppe gewählt ist, das heißt, nach dem Beginn der Zufuhr der Versorgungsspannung zu dem Modul, welches die Gruppe enthält, wird der leitende Zustand des Schalters **203** durch das Steuersignal SEL0 unterbrochen, und der Transistor **101** der Speicherschaltung für nichtflüchtigen Speicher **100-1** oder der Transistor **101** der Speicherschaltung für nichtflüchtigen Speicher **100-2** wird selektiv in Reaktion auf das Steuersignal SEL1 und das Steuersignal SEL2 eingeschaltet. Zum Beispiel wird der Transistor **101** der Speicherschaltung für nichtflüchtigen Speicher **100-1** eingeschaltet, und der Transistor **101** der Speicherschaltung für nichtflüchtigen Speicher **100-2** wird ausgeschaltet. Auf diese Weise wird das Potenzial (oder die Menge an elektrischer Ladung, die dem Potenzial entspricht) der einen Elektrode des Kondensators **102** der Speicherschaltung für nichtflüchtigen Speicher **100-1** an den Knoten M der Speicherschaltung für flüchtigen Speicher **200** eingegeben. Danach wird der Schalter **203** durch das Steuersignal SEL0 in den leitenden Zustand gebracht. Auf diese Weise können die Daten, die in der Speicherschaltung für nichtflüchtigen Speicher **100-1** gehalten werden, an die Speicherschaltung für flüchtigen Speicher **200** eingegeben und durch die Rückkopplungsschleife gehalten werden. Somit können die Daten der Speicherschaltung für flüchtigen Speicher **200** zugeführt werden. Dabei ist die Geschwindigkeit des Schreibens und Lesens von Daten in der Speicherschaltung für flüchtigen Speicher **200** höher als die in der Speicherschaltung für nichtflüchtigen Speicher **100-1** oder der Speicherschaltung für nichtflüchtigen Speicher **100-2**. Daher kann die Gruppe, für die die Zufuhr der Versorgungsspannung ausgewählt ist, eine höhere Bearbeitungsgeschwindigkeit haben.

**[0087]** In der Konfiguration, in der die Vielzahl von Speicherschaltungen für nichtflüchtigen Speicher **100** aus Fig. 1B für die Speicherschaltung für flüchtigen Speicher **200** zum Speichern von 1-Bit-Daten vorgesehen sind, können Daten, die in der Speicherschaltung für nichtflüchtigen Speicher **100**, die aus der Vielzahl von Speicherschaltungen für nichtflüchtigen Speicher **100** ausgewählt wird, gehalten werden, zu der Speicherschaltung für flüchtigen Speicher **200** geliefert werden. Insbesondere werden Daten in dem Register in dem Fall, in dem eine Anordnung verwendet wird, die eine Gruppe aus der Vielzahl von Speicherschaltungen für nichtflüchtigen Speicher **100** umfasst, die für die Speicherschaltung für flüchtigen Speicher **200** zum Speichern von 1-Bit-Daten vorgesehen ist, selektiv von der Vielzahl von Bänken an die Speicherschaltung für flüchtigen Speicher **200** geliefert, so dass der Zustand des Registers, nachdem die Bereitstellung der Versorgungsspannung ausgewählt wird, aus einer Vielzahl von Zuständen ausgewählt werden kann.

**[0088]** Man beachte, dass sogar in dem Fall, in dem eine Anordnung verwendet wird, die eine Gruppe aus der einen Speicherschaltung für nichtflüchtigen Speicher **100** umfasst, die für die Speicherschaltung für flüchtigen Speicher **200** zum Speichern von 1-Bit-Daten vorgesehen ist, Daten, die in der Speicherschaltung für nichtflüchtigen Speicher **100** gehalten werden, in die Speicherschaltung für flüchtigen Speicher **200** durch den Vorgang ähnlich dem oben beschriebenen Vorgang eingegeben werden können. Somit können die Daten der Speicherschaltung für flüchtigen Speicher **200** zugeführt werden.

**[0089]** Man beachte, dass die arithmetische Schaltung **201** in dem Fall, in dem eine Konfiguration verwendet wird, bei der die arithmetische Schaltung **201** als eine Schaltung zum selektiven Ausgeben eines Signals in Reaktion auf ein Steuersignal (z. B. ein Taktsignal) dient und der Schalter **203** weggelassen wird, derart gesteuert wird, dass es keine Ausgabe (d. h., ein Ausgang der arithmetischen Schaltung **201** stellt eine beschränkte Verbindung dar) von der arithmetischen Schaltung **201** gibt, wenn sich der Schalter **203** in der obigen Beschreibung in einem nicht leitenden Zustand befindet. Das Verfahren zum Ansteuern der Komponenten mit Ausnahme der arithmetischen Schaltung **201** kann dem obenstehenden Steuerverfahren ähneln.

**[0090]** Das Vorstehende ist die Beschreibung des Verfahrens zum Ansteuern der Gruppe aus der Speicherschaltung für flüchtigen Speicher **200**, der Speicherschaltung für nichtflüchtigen Speicher **100-1** und der Speicherschaltung für nichtflüchtigen Speicher **100-2**, die in **Fig. 1C** dargestellt ist.

(Variante der Gruppe aus einer Speicherschaltung für flüchtigen Speicher und einer Speicherschaltung für nichtflüchtigen Speicher)

**[0091]** Die Konfiguration einer Gruppe aus einer Speicherschaltung für flüchtigen Speicher und einer Speicherschaltung für nichtflüchtigen Speicher zum Speichern von Daten, die in der Speicherschaltung für flüchtigen Speicher gehalten werden, ist nicht auf die Konfiguration in **Fig. 1C** beschränkt. Zum Beispiel kann die Konfiguration, die in **Fig. 1E** dargestellt ist, verwendet werden. Man beachte, dass in **Fig. 1E** die gleichen Teile wie in **Fig. 1C** mit den gleichen Bezugszeichen bezeichnet werden und dass deren Beschreibung weggelassen wird. In einer Gruppe mit der Konfiguration in **Fig. 1E** ist eine Speicherschaltung für nichtflüchtigen Speicher **100** in einer Speicherschaltung für flüchtigen Speicher **200** enthalten. In **Fig. 1E** stellt ein Anschluss F der Speicherschaltung für nichtflüchtigen Speicher **100** einen Anschluss dar, der elektrisch mit einer Elektrode eines Kondensators **102** verbunden ist, wie in **Fig. 1D** dargestellt.

**[0092]** Ein Verfahren zum Ansteuern der Gruppe mit der Anordnung in **Fig. 1E** wird nun beschrieben.

(Betrieb während der Bereitstellung der Versorgungsspannung)

**[0093]** Während Versorgungsspannung an der Gruppe bereitgestellt wird, das heißt, während Versorgungsspannung zu einem Modul, welches die Gruppe umfasst, geliefert wird, wird ein Transistor **101** der Speicherschaltung für nichtflüchtigen Speicher **100** in Reaktion auf ein Steuersignal SEL eingeschaltet. Auf diese Weise speichert die Speicherschaltung für flüchtigen Speicher **200** Daten mittels einer Rückkopplungsschleife, die aus einer arithmetischen Schaltung **201** und einer arithmetischen Schaltung **202** besteht. Das heißt, dass Eingangsdaten in der in **Fig. 1E** dargestellten Gruppe durch die Rückkopplungsschleife der Speicherschaltung für flüchtigen Speicher **200** gehalten werden, und Daten von der Rückkopplungsschleife der Speicherschaltung für flüchtigen Speicher **200** ausgegeben werden. Daten können durch die Rückkopplungsschleife der Speicherschaltung für flüchtigen Speicher **200** gehalten und mit hoher Geschwindigkeit ausgegeben werden.

(Vorgang zur Datenspeicherung)

**[0094]** Wie oben beschrieben wird das Potenzial eines Knotens M der Speicherschaltung für flüchtigen Speicher **200**, während Daten durch die Rückkopplungsschleife der Speicherschaltung für flüchtigen Speicher **200** gehalten werden, an die eine Elektrode des Kondensators **102** der Speicherschaltung für nichtflüchtigen Speicher **100** eingegeben, so dass die Daten, die in der Speicherschaltung für flüchtigen Speicher **200** gehalten werden, in der Speicherschaltung für nichtflüchtigen Speicher **100** gespeichert werden können. Somit können die Daten gespeichert werden.

(Vorgang zur Datenbereithaltung)

**[0095]** Nachdem die Daten gespeichert sind, wird durch Ausschalten des Transistors **101** der Speicherschaltung für nichtflüchtigen Speicher **100** bewirkt, dass sich die Daten, die in der Speicherschaltung für nichtflüchtigen Speicher **100** gespeichert sind, nicht in Reaktion auf ein Signal von der arithmetischen Schaltung **201** der Speicherschaltung für flüchtigen Speicher **200** ändern. Somit kann ein Bereithalten der Daten durchgeführt werden.

**[0096]** Wie oben beschrieben wird eine Zufuhr der Versorgungsspannung nach der Bereithaltung der Daten gestoppt.

(Vorgang bei Bereitstellung der Daten)

**[0097]** Nachdem die Zufuhr der Versorgungsspannung zu der Gruppe gewählt ist, das heißt nach dem erneuten Beginn der Bereitstellung der Versorgungsspannung an dem Modul, das die Gruppe enthält, wird der Transistor **101** der Speicherschaltung für nichtflüchtigen Speicher **100** in Reaktion auf das Steuersignal SEL eingeschaltet. Auf diese Weise wird das Potenzial (oder die Menge an elektrischer Ladung, die dem Potenzial entspricht) der einen Elektrode des Kondensators **102** der Speicherschaltung für nichtflüchtigen Speicher **100** an den Knoten M der Speicherschaltung für flüchtigen Speicher **200** eingegeben. Auf solche Weise können die Daten, die in der Speicherschaltung für nichtflüchtigen Speicher **100** gehalten werden, durch die Rückkopplungsschleife der Speicherschaltung für flüchtigen Speicher **200** gehalten werden. Somit können die Daten zu der Speicherschaltung für flüchtigen Speicher **200** zugeführt werden. Dabei ist die Geschwindigkeit des Schreibens und Lesens von Daten in der Speicherschaltung für flüchtigen Speicher **200** höher als die in der Speicherschaltung für nichtflüchtigen Speicher **100**. Daher kann die Gruppe, für die die Zufuhr der Versorgungsspannung ausgewählt ist, eine höhere Bearbeitungsgeschwindigkeit haben.

**[0098]** Man beachte, dass die folgende Konfiguration vorteilhaft ist, wenn die Daten geliefert werden. In dem Fall, dass der Transistor **101** der Speicherschaltung für nichtflüchtigen Speicher **100** in Reaktion auf das Steuersignal SEL eingeschaltet wird, nachdem die Zufuhr der Versorgungsspannung ausgewählt wird, wird kein Signal von der arithmetischen Schaltung **201** ausgegeben (d. h. ein Ausgang der arithmetischen Schaltung **201** stellt eine beschränkte Verbindung dar). Zum Beispiel ist es vorteilhaft, eine Schaltung zum selektiven Ausgeben eines Signals in Reaktion auf ein Steuersignal (z. B. ein Taktsignal) als die arithmetische Schaltung **201** zu verwenden. Weiterhin ist beispielsweise ein Schalter oder dergleichen zwischen einem Ausgangsanschluss der arithmetischen Schaltung **201** und einem Anschluss B der Speicherschaltung für flüchtigen Speicher **100** vorgesehen. In diesem Fall ist es vorteilhaft, den leitenden Zustand des Schalters zu unterbrechen, wenn der Transistor **101** der Speicherschaltung für nichtflüchtigen Speicher **100** in Reaktion auf das Steuersignal SEL eingeschaltet wird, nachdem die Zufuhr der Versorgungsspannung ausgewählt wird.

**[0099]** Das Vorstehende ist die Beschreibung des Verfahrens zum Ansteuern der Gruppe aus der Speicherschaltung für flüchtigen Speicher **200** und der Speicherschaltung für nichtflüchtigen Speicher **100**, die in **Fig. 1E** dargestellt ist.

**[0100]** Die Gruppe mit der Konfiguration in **Fig. 1C** oder **Fig. 1E** kann jeweils für das Register **2004** und für die Steuerschaltung **2002** oder jeweils für das Register **2004**, für die Steuerschaltung **2002** und für das ALU **2003** vorgesehen werden, und die Zufuhr der Versorgungsspannung zu jedem Modul kann durch die Stromversorgungsschaltung **2006** gesteuert werden. Auf diese Weise kann der Energieverbrauch der Signalverarbeitungsschaltung drastisch durch Ausführen eines Standard-Aus Steuerverfahrens reduziert werden, bei dem Versorgungsspannung nur bei Bedarf bereitgestellt wird. Ohne Verschieben von Daten zwischen den Modulen können Bereitstellung und Bereithaltung von Daten vor und nach der Zufuhr der Versorgungsspannung ausgeführt werden. Daher ist es nicht notwendig, einen speziellen Signalweg (einen Weg oder einen Scanpfad) zum Durchführen von Bereitstellung und Bereithaltung von Daten zwischen den Modulen vorzusehen, und die Größe der Signalverarbeitungsschaltung kann leicht vergrößert werden.

(Konfiguration des Speichers **2005**).

(Konfiguration einer Speicherzellenmatrix)

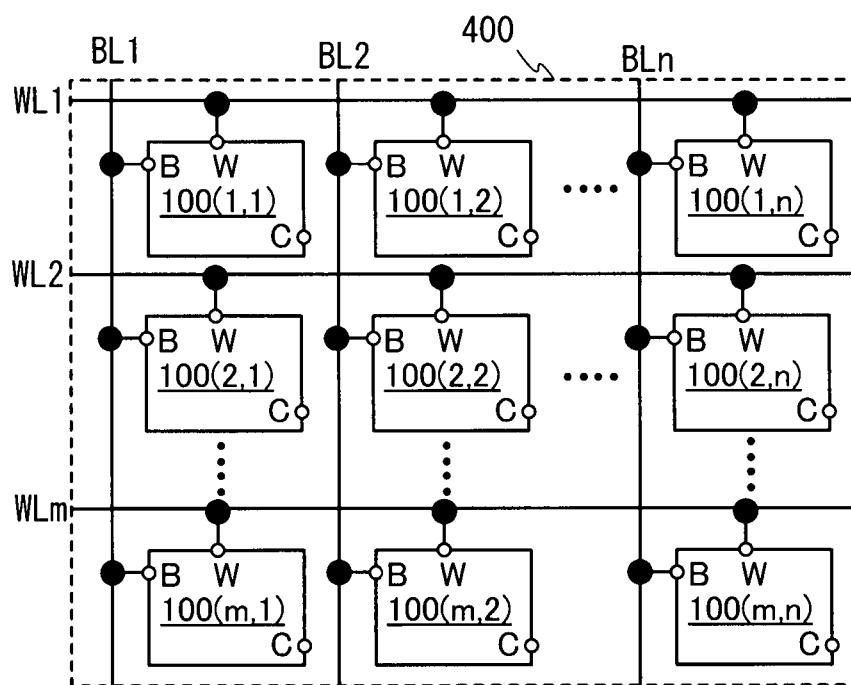

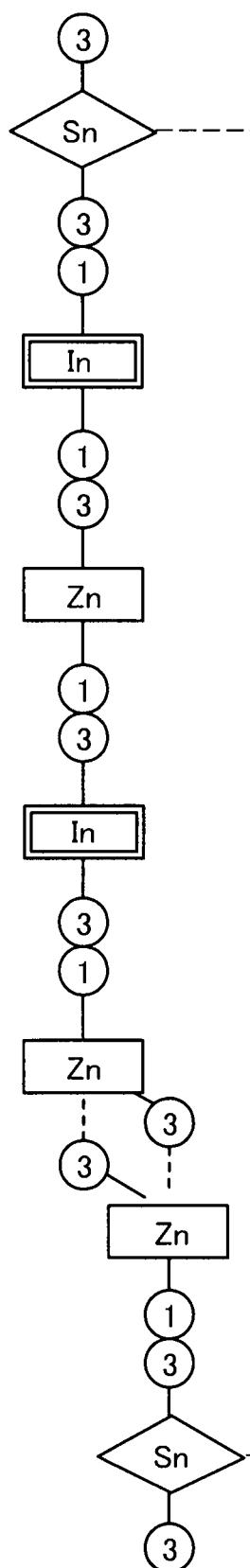

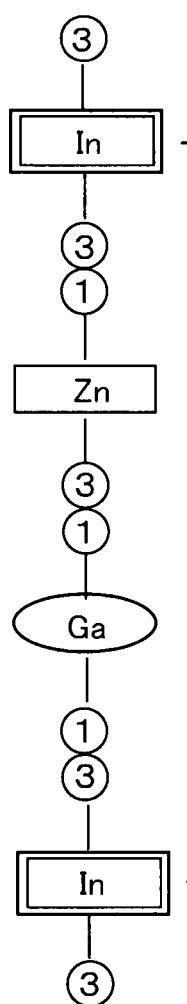

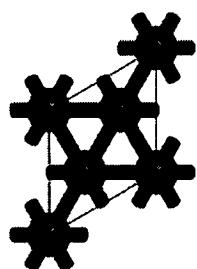

**[0101]** Der Speicher **2005** kann eine Speicherzellenmatrix aufweisen, die die Vielzahl von Speicherschaltungen für nichtflüchtigen Speicher **100** in **Fig. 1B** in einer Matrixanordnung umfasst. Zum Beispiel kann die Anordnung in **Fig. 2B** für die Speicherzellenmatrix verwendet werden. Eine Speicherzellenmatrix **400**, die in **Fig. 2B** dargestellt ist, umfasst  $m \times n$  ( $m$  ist eine natürliche Zahl und  $n$  ist eine natürliche Zahl) Speicherschaltungen für nichtflüchtigen Speicher **100** ( $i, j$ ) ( $i$  ist eine natürliche Zahl kleiner oder gleich  $m$  und  $j$  ist eine natürliche Zahl kleiner oder gleich  $n$ ). Die Speicherschaltung für nichtflüchtigen Speicher **100** ( $i, j$ ) kann die Speicherschaltung für nichtflüchtigen Speicher **100** in **Fig. 1B** sein. Im Folgenden wird die Speicherschaltung für nichtflüchtigen Speicher **100** ( $i, j$ ) auch als eine Speicherzelle bezeichnet.

**[0102]** In **Fig. 2B** wird eine Leitung (BL $j$ ), die elektrisch mit dem Anschluss B verbunden ist, gemeinsam von den Speicherzellen, die in einer Spalte angeordnet sind, genutzt. Zum Beispiel wird eine Leitung BL1, die elektrisch mit dem Anschluss B verbunden ist, gemeinsam von den Speicherzellen, die in einer ersten Spalte angeordnet sind, verwendet. Die Leitung BL $j$  kann als Bitleitung bezeichnet werden.

**[0103]** In **Fig. 2B** wird eine Leitung (WLi), die elektrisch mit dem Anschluss W verbunden ist, gemeinsam von den Speicherzellen, die in einer Zeile angeordnet sind, genutzt. Zum Beispiel wird eine Leitung WL1, die elektrisch mit dem Anschluss W verbunden ist, gemeinsam von den Speicherzellen, die in einer ersten Zeile angeordnet sind, verwendet. Die Leitung WL1 kann als Wortleitung bezeichnet werden.

**[0104]** Jedoch ist diese Ausführungsform nicht auf diese Konfiguration beschränkt. Die Vielzahl von Leitungen BLj können in den Speicherzellen, die in einer Spalte angeordnet sind, vorgesehen sein oder die Vielzahl von Leitungen WLj können in den Speicherzellen, die in einer Zeile angeordnet sind, vorgesehen sein. In den  $m \times n$  Speicherzellen können die Anschlüsse C elektrisch mit einer Elektrode oder einer Leitung verbunden sein oder elektrisch mit unterschiedlichen Elektroden oder unterschiedlichen Leitungen verbunden sein.

**[0105]** In der Speicherzellenmatrix **400**, die in **Fig. 2B** dargestellt ist, werden Daten selektiv geschrieben und gelesen in bzw. von der Speicherzelle in einer Zeile, die als Antwort auf ein Signal, welches in die Leitung WLj eingegeben wird, festgelegt wird. Genauer gesagt werden die Transistoren **101** in den Speicherzellen in den Zeilen mit Ausnahme der Speicherzellen in der i-ten Zeile, in welche Daten geschrieben werden, ausgeschaltet, und die Transistoren **101** in den Speicherzellen in der i-ten Zeile, in welche Daten geschrieben werden, werden in Reaktion auf ein Signal, das in die Leitung WLj eingegeben wird, eingeschaltet; somit werden die Daten selektiv geschrieben. Ferner werden die Transistoren **101** in den Speicherzellen in den Zeilen mit Ausnahme der Speicherzellen in der i-ten Zeile, von denen Daten gelesen werden, ausgeschaltet, und die Transistoren **101** in den Speicherzellen in der i-ten Zeile, von denen Daten gelesen werden, werden in Reaktion auf einen Signal, das in die Leitung WLj eingegeben wird, eingeschaltet; somit werden die Daten selektiv gelesen. Man beachte, dass ein Verfahren zum Schreiben und Lesen von Daten in bzw. von einer bestimmten Speicherzelle dem Verfahren zum Ansteuern der Speicherschaltung für nichtflüchtigen Speicher **100** ähnelt, das oben beschrieben ist; daher wird dessen Beschreibung weggelassen.

(Anordnung außer Speicherzellenmatrix)

**[0106]** Der Speicher **2005** kann irgendwelche oder alle von einem Zeilendecoder, einem Spaltendecoder, einer Vorladeschaltung, einem Leseverstärker und einer Speicherschaltung für temporären Speicher zusätzlich zu der Speicherzellenmatrix **400** umfassen. Man beachte, dass einige dieser Schaltungen in einer einzigen Schaltung zusammengefasst werden können. Zum Beispiel kann der Leseverstärker als Speicherschaltung für temporären Speicher dienen.

**[0107]** Der Zeilendecoder und der Spaltendecoder haben jeweils die Funktion, eine bestimmte Speicherzelle in der Speicherzellenmatrix **400** auszuwählen. Der Speicher **2005** schreibt und liest Daten in bzw. von der Speicherzelle, die durch den Zeilendecoder und den Spaltendecoder ausgewählt wird. Die Vorladeschaltung hat die Funktion, das Potenzial einer Bitleitung, die in der Speicherzellenmatrix **400** enthalten ist, auf ein vorbestimmtes Potenzial zu legen (vorzuladen), bevor Daten von der Speicherzelle gelesen werden. Da Daten aus der Speicherzelle gelesen werden können, nachdem das Potenzial der Bitleitung durch die Vorladeschaltung auf das vorbestimmten Potenzial gelegt (vorgeladenen) wird, kann die Geschwindigkeit des Lesens von Daten aus der Speicherzelle erhöht werden. Der Leseverstärker hat die Funktion, das Potenzial der Bitleitung, das den Daten, die in der Speicherzelle gehalten werden, entspricht, zu verstärken und das verstärkte Potenzial auszugeben. Daten können durch den Leseverstärker schneller und genauer gelesen werden. Die Speicherschaltung für temporären Speicher wird auch als Seitenpuffer oder als Verriegelungsschaltung (Latch-Schaltung) bezeichnet und hat die Funktion, Daten, die von außerhalb des Speichers **2005** eingegeben werden, vorübergehend zu halten. Die Speicherschaltung für temporären Speicher kann die Funktion haben, Daten, die von der Speicherzellenmatrix gelesen werden, zu halten.

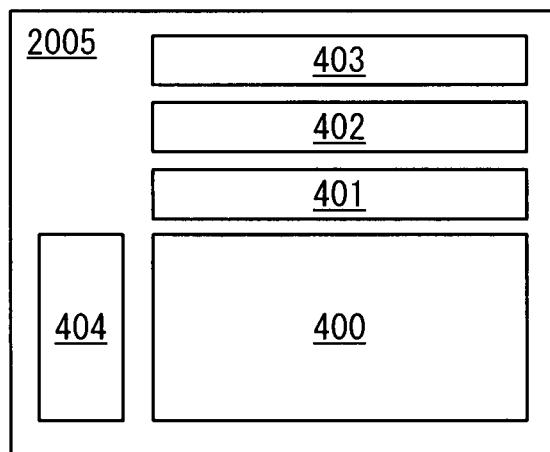

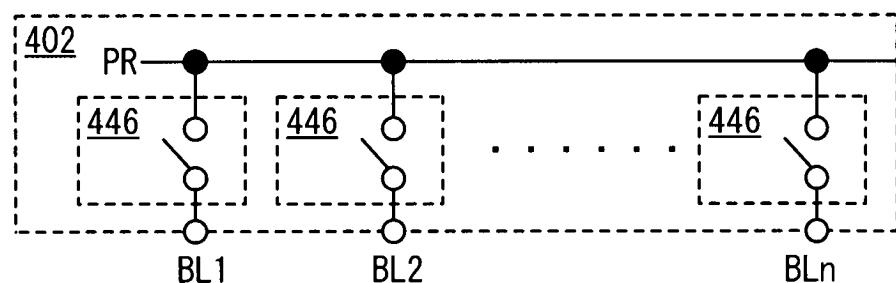

**[0108]** **Fig. 2A** zeigt schematisch eine Weiterbildung der Konfiguration des Speichers **2005**. In der **Fig. 2A** umfasst der Speicher **2005** die Speicherzellenmatrix **400**, einen Spaltendecoder **403**, einen Zeilendecoder **404**, eine Vorladeschaltung **402** und einen Leseverstärker **401**.

**[0109]** Man beachte, dass, obwohl **Fig. 2A** die Anordnung zeigt, bei der die Vorladeschaltung **402** und der Leseverstärker **401** auf einer Seite der Speicherzellenmatrix **400** angeordnet sind, wo der Spaltendecoder **403** vorgesehen ist, eine Weiterbildung der vorliegenden Erfindung nicht auf diese Anordnung beschränkt ist. Eines oder beide von der Vorladeschaltung **402** und dem Leseverstärker **401** können auf einer Seite angeordnet sein, die dem Spaltendecoder **403** gegenüberliegt, wobei die Speicherzellenmatrix **400** dazwischen angeordnet ist. Die Vorladeschaltung **402** und der Leseverstärker **401** können in einer einzigen Schaltung zusammengefasst werden.

**[0110]** Hierbei ist die Anordnung der Schaltungen nicht auf die Anordnung, die schematisch in **Fig. 2A** veranschaulicht ist und welche lediglich eine Weiterbildung für die Konfiguration des Speichers **2005** ist, beschränkt. Zum Beispiel können die anderen Schaltungen (der Spaltendecoder **403**, der Zeilendecoder **404**, die Vorladeschaltung **402** und der Leseverstärker **401**) in der Praxis so ausgebildet werden, dass sie mit der Speicherzellenmatrix **400** überlappen. Darüber hinaus kann die Speicherzellenmatrix **400** unterteilt werden und die unterteilten Speicherzellenmatrizen können mit Überlapp gestapelt werden (können mehrschichtig sein). Auf diese Weise kann der Speicherplatz erhöht werden, während die Fläche der Speicherzellenmatrix **400** verringert wird.

(Konfiguration des Leseverstärkers)

**[0111]** Als nächstes wird eine spezifische Ausführung der Konfiguration des Leseverstärkers **401** in **Fig. 2A** beschrieben. Der Leseverstärker **401** kann eine Vielzahl von Leseverstärkern enthalten. Jeder der Leseverstärker kann pro Bitleitung in der Speicherzellenmatrix **400** vorgesehen sein. Das Potenzial der Bitleitung kann von jedem der Leseverstärker verstärkt werden und kann an einem Ausgangsanschluss von jedem der Leseverstärker erfasst werden. Dabei beruht das Potenzial der Bitleitung auf einem Potenzial eines Signals, das in einer Speicherzelle gehalten wird, die elektrisch mit der Bitleitung verbunden ist und von welcher Daten gelesen werden. Somit entspricht ein Signal, das von dem Ausgangsanschluss von jedem der Leseverstärker ausgegeben wird, den Daten, die in der Speicherzelle gehalten werden, von welcher Daten gelesen werden. Auf diese Weise können Daten, die in jeder Speicherzelle in der Speicherzellenmatrix **400** gehalten werden, durch den Leseverstärker **401** erfasst werden.

**[0112]** Der Leseverstärker kann unter Verwendung eines Inverters oder eines Puffers gebildet werden. Zum Beispiel kann der Leseverstärker unter Verwendung einer Verriegelungsschaltung (ein Verriegelungsleseverstärker) gebildet werden. Der Verriegelungsleseverstärker kann ein Eingangssignal verstärken und das verstärkte Signal halten. Daher kann, selbst wenn die elektrische Ladung, die einem Potenzial eines Signals entspricht, das in dem Kondensator **102** gehalten wird, zum Zeitpunkt des Lesens von Daten aus der Speicherzelle (der Speicherschaltung für nichtflüchtigen Speicher **100**) geändert (beschädigt) wird, ein Signal, welches dem Potenzial des Signals entspricht, in dem Verriegelungsleseverstärker gehalten und erneut in die Speicherzelle (die Speicherschaltung für nichtflüchtigen Speicher **100**) geschrieben werden.

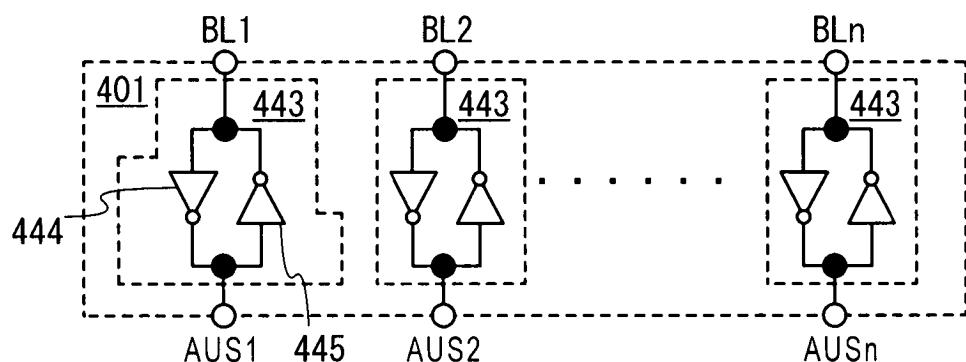

**[0113]** Eine weitere spezifische Ausführungsform des Leseverstärkers **401** wird unter Bezugnahme auf die **Fig. 3A** und **Fig. 3B** untenstehend beschrieben.

**[0114]** Der Leseverstärker **401**, der in den **Fig. 3A** und **Fig. 3B** dargestellt ist, ist ein Beispiel für einen Verriegelungsleseverstärker, der Verriegelungsschaltungen **443** umfasst (oder durch sie gebildet wird). Die Verriegelungsschaltung **443** kann zum Beispiel unter Verwendung eines Inverters **444** und eines Inverters **445** gebildet werden. Der Leseverstärker **401** umfasst n Verriegelungsschaltungen **443**, und jede der n Verriegelungsschaltungen **443** ist in den Bitleitungen BL1 bis BLn angeordnet, die in der Speicherzellenmatrix **400** vorgesehen sind. Die Potenziale der Bitleitungen BL1 bis BLn können durch die n Verriegelungsschaltungen **443** verstärkt und von den Ausgangsanschlüssen AUS1 bis AUSn ausgegeben werden. Dabei basiert das Potenzial der Bitleitung auf einem Potenzial eines Signals, das in einer Speicherzelle gehalten wird, die elektrisch mit der Bitleitung verbunden ist und von welcher Daten selektiv gelesen werden. Somit entspricht ein Signal (ein verstärktes Signal), das von dem Ausgangsanschluss der Verriegelungsschaltung **443** ausgegeben wird, den Daten, die in der Speicherzelle gehalten werden, von welcher Daten selektiv gelesen werden. Auf diese Weise können Daten, die in jeder Speicherzelle in der Speicherzellenmatrix **400** gehalten werden, von dem Leseverstärker **401**, der die n Verriegelungsschaltungen **443** enthält, erfasst werden.

**[0115]** Ferner kann jede der n Verriegelungsschaltungen **443** ein verstärktes Signal halten. Daher kann, selbst wenn Daten zum Zeitpunkt des Lesens der Daten aus der Speicherzelle in der Speicherzellenmatrix **400** beschädigt sind, ein entsprechendes Signal in den n Verriegelungsschaltungen **443** gehalten und erneut in die Speicherzelle geschrieben werden.

**[0116]** Da der Leseverstärker **401**, der die Verriegelungsschaltung **443** enthält, die in jeder der **Fig. 3A** und **Fig. 3B** dargestellt ist, die Funktion hat, ein Signal wie oben beschrieben zu halten, kann der Leseverstärker **401** als Speicherschaltung für temporären Speicher verwendet werden. Zum Beispiel kann der Leseverstärker **401**, der die Verriegelungsschaltung **443** enthält, als eine Schaltung (beispielsweise ein Seitenpuffer) zum temporären Halten von Daten verwendet werden, die außerhalb des Speichers **2005** eingegeben werden.

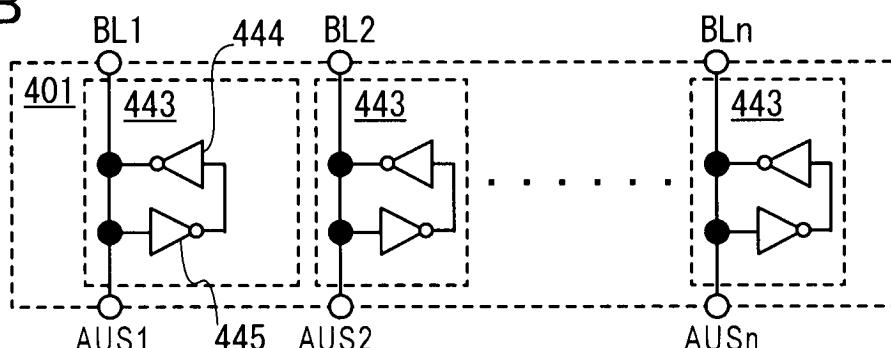

**[0117]** Als nächstes wird eine spezifische Ausführungsform der Konfiguration der Vorladeschaltung **402** in **Fig. 2A** unter Bezug auf **Fig. 3C** beschrieben. In **Fig. 3C** umfasst die Vorladeschaltung **402** eine Vorladeleitung PR und eine Vielzahl von Schaltern **446**. Jeder der Schalter **446** kann in den Bitleitungen BL1 bis BLn in der Speicherzellenmatrix **400** vorgesehen sein. Eine elektrische Verbindung zwischen jeder Bitleitung und der Vorladeleitung PR wird durch jeden Schalter **446** ausgewählt, und das Potenzial (das Vorladepotenzial) der Vorladeleitung PR kann in jede Bitleitung eingegeben werden. Zum Beispiel können ein analoger Schalter, ein Transistor oder dergleichen als der Schalter **446** verwendet werden. Alternativ kann eine arithmetische Schaltung, in die eines oder beide von einem Taktsignal und einem invertierten Signal des Taktsignals eingegeben werden, als der Schalter **446** verwendet werden.

**[0118]** Das Vorstehende ist die Beschreibung des Speichers **2005**.

**[0119]** Wie oben beschrieben wird in dem Speicher **2005**, der die Speicherschaltung für nichtflüchtigen Speicher **100** umfasst, ein regelmäßiges Datenrückschreiben (im Folgenden auch als Aktualisierungsoperation bezeichnet) nicht benötigt oder die Häufigkeit der Aktualisierungsoperation kann deutlich verringert werden. Bei Verwendung des Speichers **2005** kann ein Standard-Aus Steuerverfahren leicht durchgeführt werden und der Stromverbrauch der Signalverarbeitungsschaltung kann reduziert werden.