(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6012763号

(P6012763)

(45) 発行日 平成28年10月25日(2016.10.25)

(24) 登録日 平成28年9月30日(2016.9.30)

(51) Int.Cl.

F 1

H01L 21/3205 (2006.01)

H01L 21/88

J

H01L 21/768 (2006.01)

H01L 23/522 (2006.01)

請求項の数 12 (全 21 頁)

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2014-552358 (P2014-552358)  |

| (86) (22) 出願日 | 平成25年1月12日 (2013.1.12)        |

| (65) 公表番号     | 特表2015-505171 (P2015-505171A) |

| (43) 公表日      | 平成27年2月16日 (2015.2.16)        |

| (86) 國際出願番号   | PCT/US2013/021342             |

| (87) 國際公開番号   | W02013/106796                 |

| (87) 國際公開日    | 平成25年7月18日 (2013.7.18)        |

| 審査請求日         | 平成27年4月22日 (2015.4.22)        |

| (31) 優先権主張番号  | 61/586,463                    |

| (32) 優先日      | 平成24年1月13日 (2012.1.13)        |

| (33) 優先権主張国   | 米国(US)                        |

| (31) 優先権主張番号  | 61/671,607                    |

| (32) 優先日      | 平成24年7月13日 (2012.7.13)        |

| (33) 優先権主張国   | 米国(US)                        |

|           |                                                                                       |

|-----------|---------------------------------------------------------------------------------------|

| (73) 特許権者 | 507364838<br>クアルコム、インコーポレイテッド<br>アメリカ合衆国 カリフォルニア 921<br>21 サンディエゴ モアハウス ドラ<br>イブ 5775 |

| (74) 代理人  | 100108453<br>弁理士 村山 靖彦                                                                |

| (74) 代理人  | 100163522<br>弁理士 黒田 晋平                                                                |

| (72) 発明者  | ヴィディヤ・ラマチャンドラ<br>アメリカ合衆国・カリフォルニア・921<br>21・サン・ディエゴ・モアハウス・ドラ<br>イブ・5775                |

最終頁に続く

(54) 【発明の名称】基板貫通ビアを集積回路の中間工程層に組み込むこと

## (57) 【特許請求の範囲】

## 【請求項 1】

基板と、

前記基板の第1の側に形成された誘電体層と、

前記誘電体層および前記基板を貫通して延びる基板貫通ビアであって、前記基板貫通ビアが導電材料および絶縁層を含み、前記絶縁層が前記導電材料を少なくとも部分的に囲み、前記絶縁層がテーパ部分を備える、基板貫通ビアと

を備え、

前記基板貫通ビアが、前記導電材料の一部分を前記絶縁層から分離するフォトレジスト層の残部をさらに備える半導体ウェハ。

10

## 【請求項 2】

前記絶縁層が、実質的に一定の直径を有する一定部分を備え、前記テーパ部分が変動直径を有し、前記変動直径が前記実質的に一定の直径より大きい、請求項1に記載の半導体ウェハ。

## 【請求項 3】

前記導電材料が、実質的に一定の直径を有する第1の部分と、前記テーパ部分の前記変動直径に対応して変動する直径を有する第2の部分とを備える、請求項2に記載の半導体ウェハ。

## 【請求項 4】

前記絶縁層の前記テーパ部分が、能動デバイスおよび/または受動デバイスを有する前

20

記基板の前記第1の側に近接して配設される、請求項1に記載の半導体ウェハ。

**【請求項5】**

前記絶縁層の前記テープ部分が、前記基板の前記第1の側、および前記誘電体層に近接して配設される、請求項1に記載の半導体ウェハ。

**【請求項6】**

前記基板貫通ビアが、前記導電材料を前記絶縁層から分離する多層キャップ層をさらに備える、請求項1に記載の半導体ウェハ。

**【請求項7】**

前記半導体ウェハの一部分が、音楽プレーヤ、ビデオプレーヤ、娛樂ユニット、ナビゲーションデバイス、通信デバイス、携帯情報端末(PDA)、固定位置のデータユニット、およびコンピュータの内の少なくとも1つに組み込まれる、請求項1に記載の半導体ウェハ。10

**【請求項8】**

半導体基板と、

前記基板の第1の側に形成された誘電体層と、

前記誘電体層および前記基板を通って伝導するための手段と、

前記伝導手段を絶縁するための手段であって、前記伝導手段を囲み、テープ部分を備える絶縁手段と

を備え、20

前記基板貫通ビアが、前記導電材料の一部分を前記絶縁層から分離するフォトレジスト層の残部をさらに備える半導体ウェハ。

**【請求項9】**

前記伝導手段の一部分が、

前記絶縁手段の前記テープ部分に少なくとも部分的に基づいて直径が変動する、請求項8に記載の半導体ウェハ。

**【請求項10】**

前記絶縁手段の前記テープ部分が、能動デバイスおよび/または受動デバイスを有する前記基板の前記第1の側に近接して配設される、請求項8に記載の半導体ウェハ。30

**【請求項11】**

前記絶縁手段の前記テープ部分が、前記基板の前記第1の側、および前記誘電体層に近接して配設される、請求項8に記載の半導体ウェハ。

**【請求項12】**

前記半導体ウェハの一部分が、音楽プレーヤ、ビデオプレーヤ、娛樂ユニット、ナビゲーションデバイス、通信デバイス、携帯情報端末(PDA)、固定位置のデータユニット、およびコンピュータの内の少なくとも1つに組み込まれる、請求項8に記載の半導体ウェハ。30

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

関連出願40

本出願は、V. Ramachandranらの名義の2012年1月13日に出願された米国仮特許出願第61/586,463号および2012年7月13日に出願された米国仮特許出願第61/671,607号の利益を主張し、上記の仮出願の開示は、参照により全体が本明細書に明示的に組み込まれる。

**【0002】**

本開示は一般に、集積回路(IC)に関する。より詳細には、本開示は、基板貫通ビア(TSV)を先端CMOS(相補型金属酸化膜半導体)ノードにおける中間工程層に組み込むことに関する。

**【背景技術】**

**【0003】**

集積回路（I C）の半導体製造のプロセスフローは、基板工程（F E O L : front-end-of-line）、中間工程（M O L : middle-of-line）、および配線工程（B E O L : back-end-of-line）を含み得る。F E O L プロセスは、ウェハ作製、分離、ウェル形成、ゲートパターニング、スペーサ、エクステンションおよびソース／ドレインインプラント、シリサイド形成、ならびにデュアルストレスライナー形成を含み得る。M O L プロセスは、ゲートコンタクト形成を含み得る。B E O L プロセスは、F E O L およびM O L プロセス中に作成された半導体デバイスを相互接続するための一連のウェハ加工ステップを含み得る。成功を収めている現代の半導体チップ製品の製造および認定には、採用される材料とプロセスの間の相互作用が伴う。とりわけ、M O L プロセスにおけるゲートコンタクト形成は、特にリソグラフィパターニングに関して、プロセスフローのますます困難な部分となっている。

#### 【0004】

半導体ノードが進歩する（すなわち、ノードがより小さくなり、製造方法が高度化する）につれて、T S V（基板貫通ビア）をM O L 層に組み込むことがより難しくなる。中間工程層は、半導体デバイストランジスタまたは他の同様の能動デバイスに近接したM O L コンタクトまたは他の層を含むことができるが、これに限定されない。一般にM O L 層は厚さが薄いので、デバイストランジスタに対しM O L 層が近接することで、T S Vを首尾よく組み込むための狭いプロセスウィンドウがもたらされる。その結果、T S V組み込みプロセスによって生じるダイ／ウェハの厚さのばらつきは、T S Vプロセスが半導体デバイスの本体を貫通する縦接続を生成するので、M O L 層に、より重大な問題となる。その上、T S Vのサイズスケーリング能力が限られているため、さらにM O L 層に対するばらつきの影響が増大する。

#### 【0005】

ダイおよびウェハの厚さのばらつきに寄与するT S Vプロセスの1つは、T S V化学機械研磨（C M P）のオーバー研磨である。オーバー研磨は、T S V充填プロセスによってウェハ上に配置された（膜を含む）すべての層を完全に除去するために行われる。特に、T S V充填プロセスによってウェハ上に配置される層は、ウェハのM O L 層上に形成され得る。不都合なことに、オーバー研磨によるウェハからの層除去により、特に20ナノメータ（20nm）以下のプロセスについて、M O L 層の厚さがさらに薄くなるおそれがある。

#### 【発明の概要】

#### 【課題を解決するための手段】

#### 【0006】

本開示の一態様では、組み込まれた基板貫通ビア（T S V）を有する半導体ウェハが説明される。半導体ウェハは基板を備える。誘電体層は、基板の第1の側に形成され得る。基板貫通ビアは、誘電体層および基板を貫通して延びることができる。基板貫通ビアは、導電材料および絶縁層を含むことができる。絶縁層は、導電材料を少なくとも部分的に囲むことができる。絶縁層は、テーパ部分を備えることができる。

#### 【0007】

本開示の一態様では、基板貫通ビア（T S V）を先端C M O S（相補型金属酸化膜半導体）ノードに組み込むための方法が説明される。この方法は、基板の第1の側に形成された誘電体層を含む基板において基板貫通ビアキャビティを画成するステップを含む。この方法はまた、基板貫通ビアキャビティ内に絶縁層を堆積させるステップを含む。この方法は、絶縁層の一部分をエッチングするステップをさらに含む。エッチングするステップは、誘電体層に実質的に近接した絶縁層のテーパ部分を生成することができる。この方法はまた、基板貫通ビアキャビティ内に導電材料を堆積させるステップを含む。

#### 【0008】

本開示の一態様では、組み込まれた基板貫通ビア（T S V）を有する半導体ウェハが説明される。半導体ウェハは基板を備える。誘電体層は、基板の第1の側に形成され得る。半導体ウェハは、誘電体層および半導体基板を通って伝導するための手段を備える。半導

10

20

30

40

50

体ウェハはまた、伝導手段を絶縁するための手段を備える。絶縁手段は、伝導手段を囲むことができる。絶縁手段はまた、テーパ部分を備えることができる。

#### 【0009】

本開示の別の態様では、基板貫通ビア（T S V）を先端C M O S（相補型金属酸化膜半導体）ノードに組み込むための方法が説明される。この方法は、半導体基板において基板貫通ビアキャビティを画成するステップを含む。この方法はまた、基板貫通ビアキャビティ内および基板貫通ビアキャビティの外側に、絶縁層を堆積させるステップを含む。この方法は、基板貫通ビアキャビティにフォトレジストを堆積させるステップをさらに含む。この方法はまた、基板貫通ビアキャビティの外側の絶縁層をエッチングするステップを含む。この方法は、基板貫通ビアキャビティを覆うフォトレジストを除去するステップをさらに含む。この方法はまた、基板貫通ビアキャビティを導電材料で充填するステップを含む。この方法は、基板貫通ビアキャビティの外側の絶縁層の化学機械オーバー研磨で中間工程層を露出させるステップをさらに含む。

#### 【0010】

本開示の一態様では、組み込まれた基板貫通ビア（T S V）を有する半導体ウェハが説明される。半導体ウェハは半導体基板を備える。誘電体層は、半導体基板の表面に形成され得る。研磨停止層は、誘電体層の表面に形成され得る。基板貫通ビアは、研磨停止層、誘電体層、および半導体基板を貫通して延びることができる。基板貫通ビアは、導電材料および絶縁層を含むことができる。絶縁層は、導電材料を少なくとも部分的に囲むことができる。絶縁層はまた、研磨停止層の一部分を部分的に覆うこともできる。

#### 【0011】

本開示の別の態様では、組み込まれた基板貫通ビア（T S V）を有する半導体ウェハが説明される。半導体ウェハは半導体基板を備える。誘電体層は、半導体基板の表面に形成され得る。研磨停止層は、誘電体層の表面に形成され得る。半導体ウェハは、研磨停止層、誘電体層、および半導体基板を通って伝導するための手段を備える。半導体ウェハは、伝導手段を絶縁するための手段を備える。絶縁手段は、導電材料を少なくとも部分的に囲むことができる。絶縁層はまた、研磨停止層の一部分を部分的に覆うこともできる。

#### 【0012】

上記は、以下の詳細な説明がより良く理解され得るように、本開示の特徴および技術的な利点を、かなり大まかに概説したものである。本開示のさらなる特徴および利点は、以下で説明される。本開示と同じ目的を実行するための他の構造を修正または設計するための基礎として、本開示が容易に利用され得ることを当業者は諒解されたい。そのような等価な構成は、添付の特許請求の範囲に記載される本開示の教示から逸脱しないことも当業者は認識されたい。機構と動作方法の両方に関して本開示の特性であると考えられる新規の特徴は、添付の図面と併せて考慮されれば、さらなる目的および利点とともに、以下の説明からより良く理解されよう。しかしながら、図面の各々は例示および説明のみを目的として提供され、本開示の範囲を規定するものとして意図されないことを明確に理解されたい。

#### 【0013】

本開示のより完全な理解のために、ここで、添付の図面と併せて以下の説明を参照する。

#### 【図面の簡単な説明】

#### 【0014】

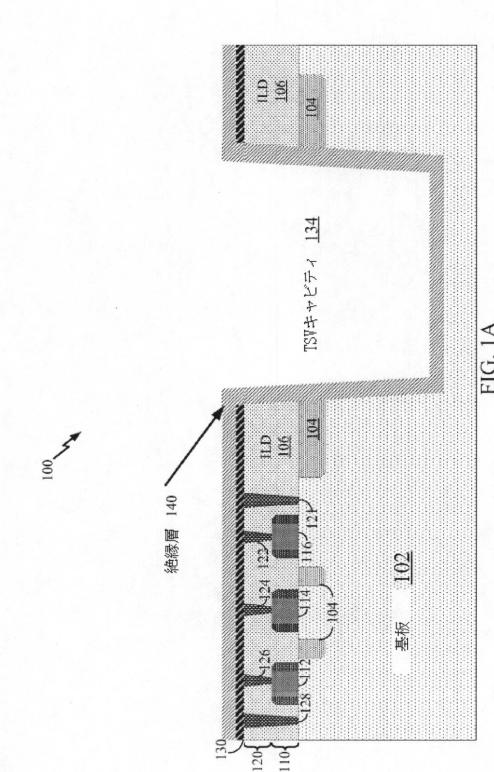

【図1A】本開示の一態様による、能動デバイスおよび絶縁層を含む集積回路（I C）デバイスを示す断面図である。

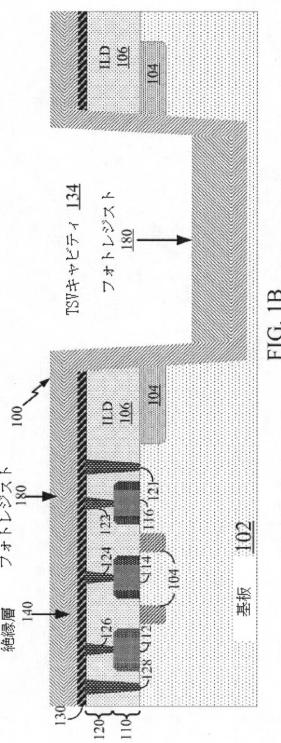

【図1B】本開示の一態様による絶縁層上に配設されたフォトレジストを含む、図1AのI Cデバイスを示す断面図である。

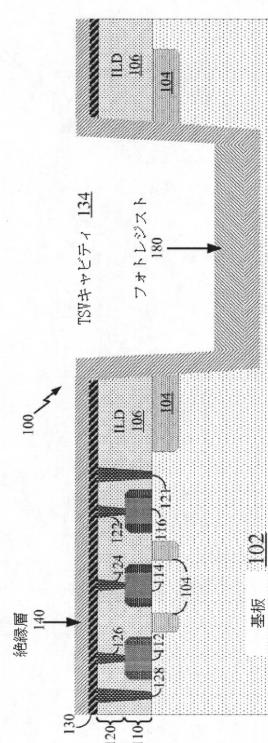

【図1C】本開示の一態様による絶縁層上に配設されたフォトレジストを含む、図1AのI Cデバイスを示す断面図である。

【図2A】本開示の一態様による絶縁層のテーパ部分を形成するための絶縁層のエッチ

10

20

30

40

50

グを示す、図 1 C の I C デバイスの断面図である。

【図 2 B】本開示の一態様による絶縁層のテーパ部分を形成するための絶縁層のエッチングを示す、図 1 A の I C デバイスの断面図である。

【図 2 C】本開示の一態様による絶縁層上の多層キャップ層の形成を示す、図 2 B の I C デバイスの断面図である。

【図 3 A】本開示の一態様による T S V バリアシードおよび銅充填プロセスの後の図 2 B の I C デバイスを示す断面図である。

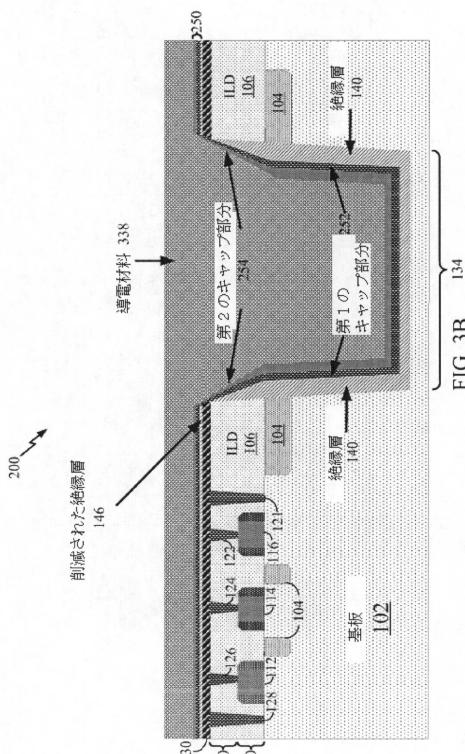

【図 3 B】本開示の一態様による T S V バリアシードおよび銅充填プロセスの後の図 2 C の I C デバイスを示す断面図である。

【図 4 A】本開示の一態様による銅化学機械研磨 (C M P) プロセスの後の図 3 A の I C デバイスを示す断面図である。 10

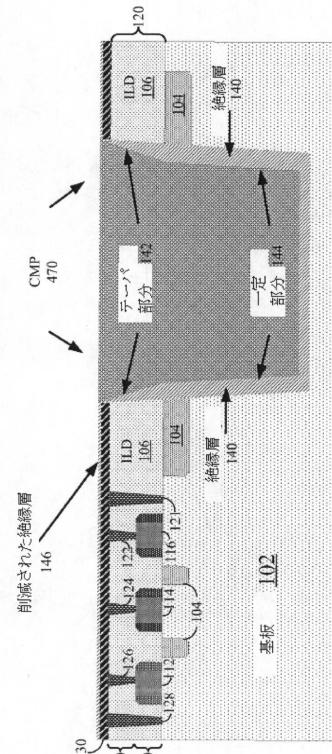

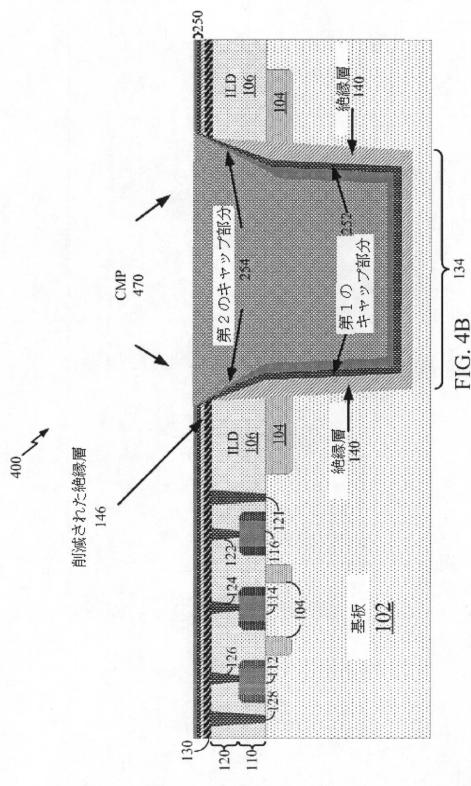

【図 4 B】本開示の一態様による銅化学機械研磨 (C M P) プロセスの後の図 3 B の I C デバイスを示す断面図である。

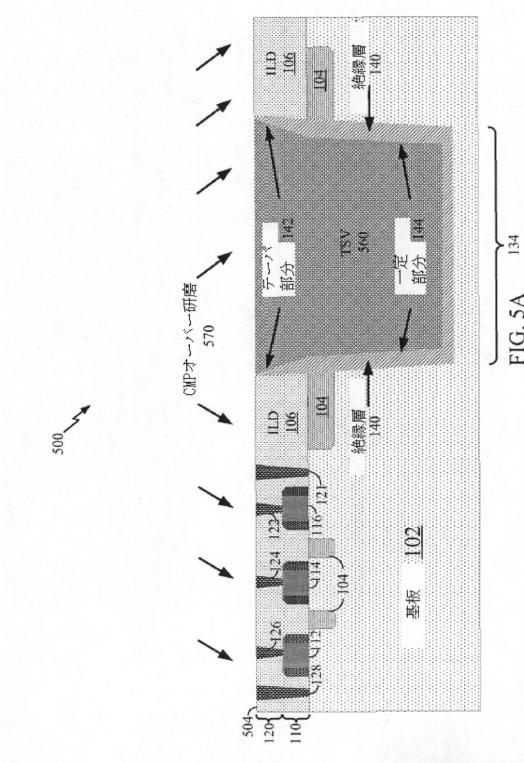

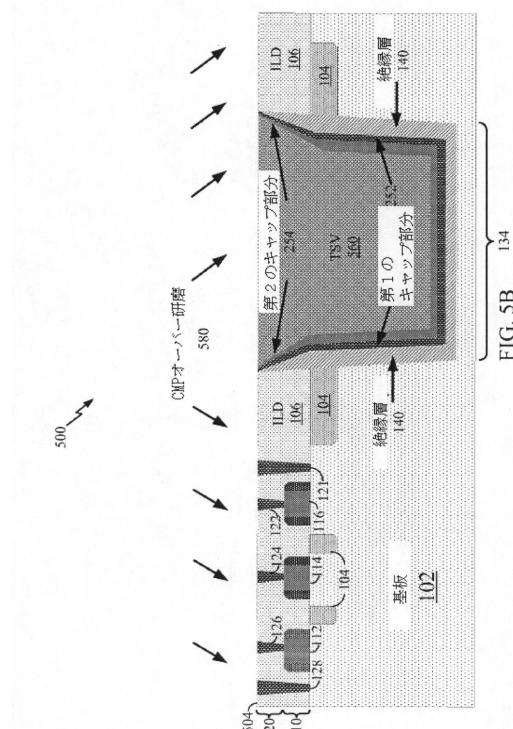

【図 5 A】本開示の一態様による I C デバイスの能動面近くでテーパ部分を有する絶縁層によって囲まれた T S V を有する、図 4 A の I C デバイスを示す断面図である。

【図 5 B】本開示の一態様による I C デバイスの能動面近くでテーパ部分を有する絶縁層上の多層キャップ層によって囲まれた T S V を有する、図 4 C の I C デバイスを示す断面図である。

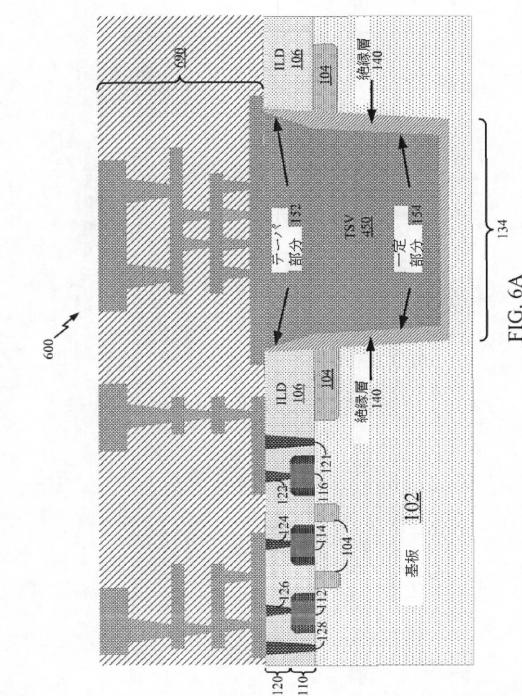

【図 6 A】本開示の一態様による配線工程 (B E O L) スタックの作製の後の図 5 A の I C デバイスを示す断面図である。 20

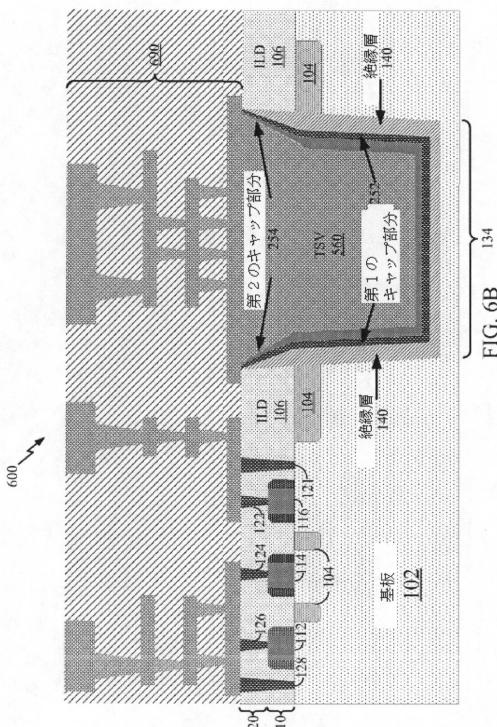

【図 6 B】本開示の一態様による配線工程 (B E O L) スタック作製の後の図 5 B の I C デバイスを示す断面図である。

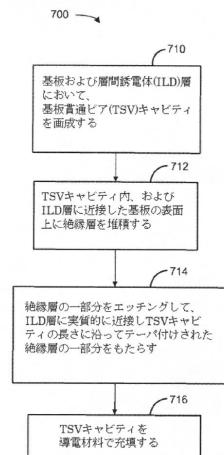

【図 7】本開示の一態様による、基板貫通ビア (T S V) を先端 C M O S (相補型金属酸化膜半導体) ノードに組み込むための方法を示すブロック図である。

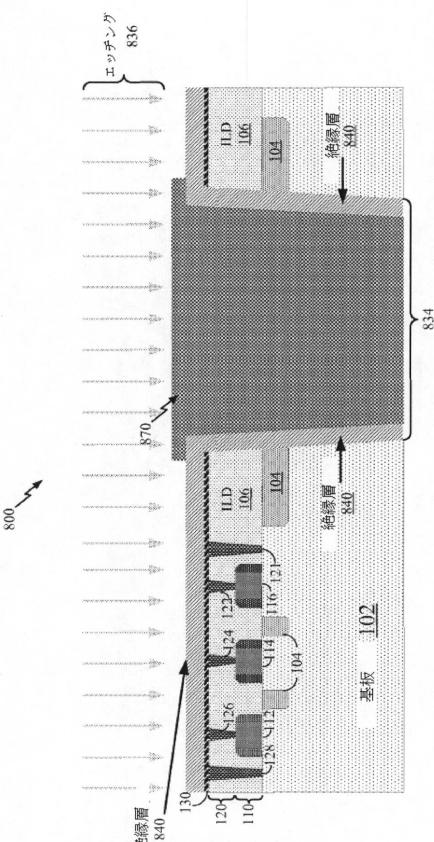

【図 8】本開示の一態様による T S V キャビティ上および T S V キャビティ内に形成されたストリップレジストを示す、図 1 A の I C デバイスの断面図である。

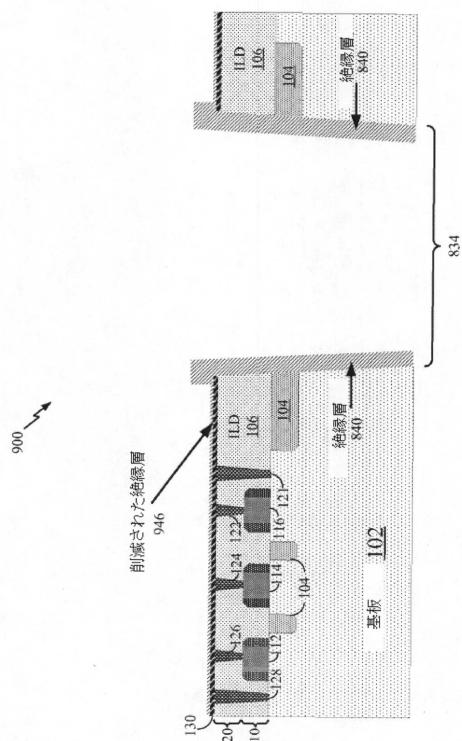

【図 9】本発明の一態様による削減された絶縁層を形成するためのフィールド酸化物層およびストリップレジストのエッチングの後の図 8 の I C デバイスを示す断面図である。

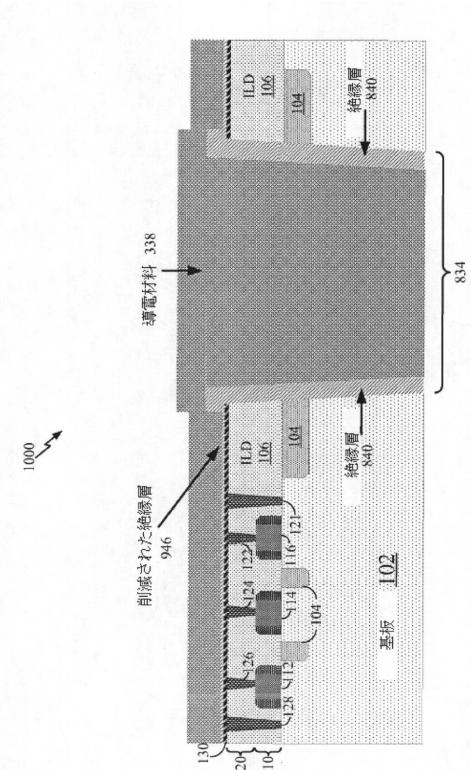

【図 10】本開示の一態様による T S V バリアシードおよび銅充填プロセスの後の図 9 の I C デバイスを示す断面図である。 30

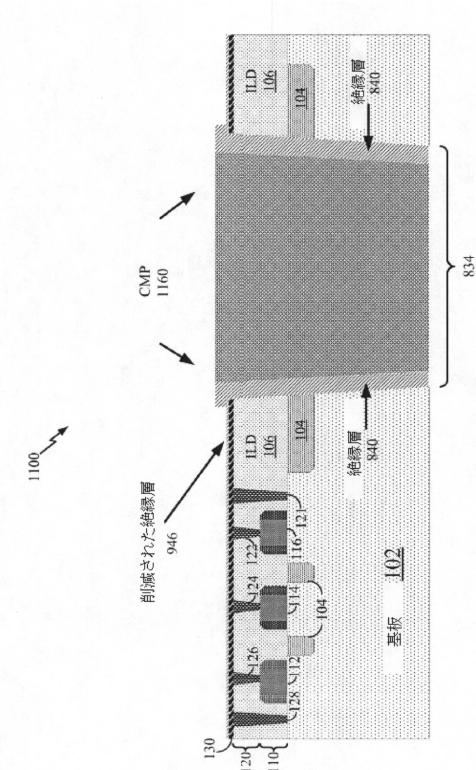

【図 11】本開示の一態様による銅化学機械研磨 (C M P) プロセスの後の図 10 の I C デバイスを示す断面図である。

【図 12】本開示の一態様による化学機械研磨 (C M P) オーバー研磨プロセスの後の図 11 の I C デバイスを示す断面図である。

【図 13】本開示の一態様による、基板貫通ビア (T S V) を先端 C M O S (相補型金属酸化膜半導体) ノードに組み込むための方法を示すブロック図である。

【図 14】本開示の構成が有利に採用され得るワイヤレス通信システムを示すブロック図である。

#### 【発明を実施するための形態】

##### 【0 0 1 5】

添付の図面に関する下記の詳細な説明は、様々な構成の説明として意図されており、本明細書で説明される概念が実施され得る唯一の構成を表すように意図されているわけではない。詳細な説明は、様々な概念の完全な理解をもたらす目的で、具体的な詳細を含んでいる。しかしながら、これらの概念はこれらの具体的な詳細なしに実施され得ることが当業者には明らかであろう。場合によっては、そのような概念を曖昧にするのを回避する目的で、周知の構造および構成要素がブロック図の形式で示されている。本明細書の説明では、「および / または」という用語の使用は、「包含的論理和」を表すことを意図し、「または」という用語の使用は、「排他的論理和」を表すことを意図する。

##### 【0 0 1 6】

本開示の様々な態様は、基板貫通ビア (T S V) を集積回路 (I C) における中間工程 50

層に組み込むための技法を実現する。集積回路（IC）の半導体製造のプロセスフローは、基板工程（FEOL：front-end-of-line）プロセス、中間工程（MOL：middle-end-of-line）プロセス、および配線工程（BEOL：back-end-of-line）プロセスを含み得る。「層」という用語は、膜を含み、特に指定のない限り、縦または横の厚さを示すものと解釈されるべきではない。本開示の一態様によれば、絶縁層は、基板貫通ビア（TSV）の導電性部分を、ウェハの基板（たとえば、シリコン）から、またウェハの層間誘電体層から分離する。一構成では、絶縁層は、ウェハの誘電体層に実質的に近接したテーパ部分を備える。絶縁層はまた、ウェハの基板の水平長に沿って配設された実質的に一定の部分を備える。別の構成では、基板貫通ビアの絶縁層は、第1の実質的に一定の直径を有する第1の部分と、より大きな実質的に一定の直径を有する第2の部分とを有する。さらなる構成では、多層キャップが、基板貫通ビアを充填する導電材料から絶縁層を分離する。

#### 【0017】

本開示の一態様では、方向性反応性イオン（DRI：directional reactive ion）エッチングにより、テーパ付けされた絶縁層の部分が得られる。本開示のこの態様では、DRIエッチングにより、CMP（化学機械研磨）の前にウェハの水平面から層の一部分を実質的に除去し、したがって、CMPオーバー研磨により除去する絶縁層の量が少なくなる。本開示のこの態様では、DRIエッチングが、TSV形成プロセスの前にウェハの水平面上に形成される絶縁層の厚さを実質的に減らす。本開示の別の態様では、TSV形成プロセスに続いて、ICデバイスを完成するために配線工程（BEOL）相互接続層がウェハ上に作製される。

#### 【0018】

有利なことに、TSV充填プロセス中にウェハ上に配置されたすべての層を除去するCMPオーバー研磨は、DRIエッチングを使用することによって削減される。すなわち、DRIエッチングがウェハの水平面から層のほとんどを除去するので、（TSV充填プロセス中に配置された）ウェハ上の残りの層を除去するために必要なCMPオーバー研磨プロセスが低減する。また、DRIエッチングは、TSVの側壁内に堆積された層のいくつかを除去して、テーパが付いた絶縁層をもたらす。除去の大部分はTSVの最上部付近である。CMPオーバー研磨を削減することによって、ウェハの中間工程（MOL）層がCMPオーバー研磨中により良く保存／保護される。TSVは、導電材料（たとえば金属）レベル（たとえばBEOL相互接続層）のようにMOL層より上に挿入することも可能である。

#### 【0019】

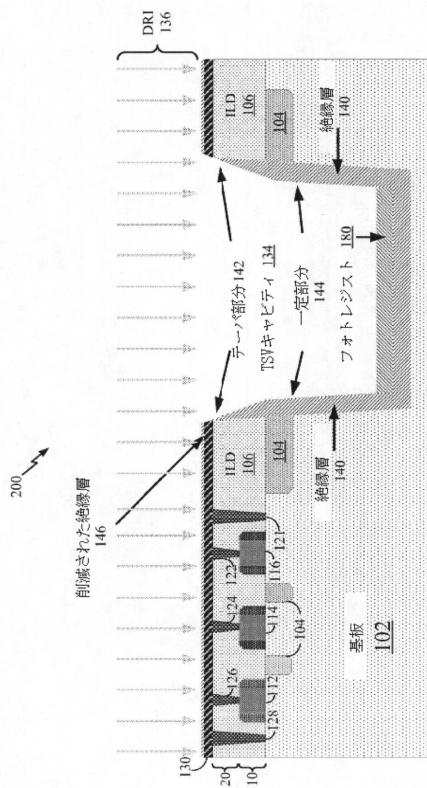

図1Aは、本開示の一態様による、能動デバイス112～126を含む集積回路（IC）デバイス100を示す断面図を示す。典型的には、ICパッケージ100は、シャロートレンチアイソレーション（STI）領域104を有する基板（たとえば、シリコンウェハ）102を含む。STI領域104および基板102の上に、層間誘電体（IDL）層106がある。また、（FEOL）相互接続層110も設けられる。また、中間工程（MOL）層120も設けられる。IDL層106は、FEOL相互接続層110の能動デバイス112～116、およびMOL層120の導電素子（たとえば、ビア）121～128を、後の処理による損傷から保護する。この構成では、IDL層106は、MOL層120の導電素子121～128間の短絡を防止するために酸化ケイ素または他の同様の材料で形成される。代替構成では、IDL層106は低誘電率誘電体または他の同様の材料である。

#### 【0020】

図1Aに示すように、TSVキャビティ134は、本開示の一態様による1つまたは複数の絶縁層およびTSV（基板貫通ビア）導電材料を収容するために拡大された寸法（たとえば、10～100ミクロンの深さ）を有する。図1Aに示すように、研磨ストップ層130を、IDL層106の表面上、および導電素子121～128を含むMOL層120の表面上に堆積した後、リソグラフィが、最終的なTSVの実際の導電性部分より若干

10

20

30

40

50

大きい T S V キャビティ 1 3 4 を画成する(図 4 および図 5 参照)。この構成では、T S V のサイズは 1 マイクロメートル(  $\mu\text{m}$  ) ~ 2 0 マイクロメートル程度である。さらに、研磨停止層 1 3 0 は、炭化ケイ素、窒化ケイ素、SiC ON、または他の同様の保護材料で形成されてよい。

#### 【 0 0 2 1 】

図 1 A は、本開示の一態様による絶縁層 1 4 0 を示す。この構成では、エッチングおよび / またはリソグラフィプロセスが、ILD 層 1 0 6 、および基板 1 0 2 の STI 領域 1 0 4 をエッチングする。このプロセスが T S V キャビティ 1 3 4 を形成する。エッチングの完了後、絶縁堆積により、研磨停止層 1 3 0 、側壁、および T S V キャビティ 1 3 4 の底部上に絶縁層 1 4 0 が形成される。保護誘電体層 1 4 0 は、非フッ素化石英ガラス( USG )、オルトケイ酸テトラエチル( TEOS )、酸化ケイ素、窒化ケイ素、または酸化物層もしくは電気的絶縁膜を形成するための他の同様の前駆体の層として形成されてよい。絶縁層 1 4 0 は、2 0 ~ 1 0 0 0 ナノメートル( nm )の範囲の厚さを有することができる。10

#### 【 0 0 2 2 】

図 1 B および図 1 C は、本開示の一態様による絶縁層 1 4 0 上に配設されたフォトレジスト 1 8 0 を含む、図 1 A の IC デバイスを示す断面図を示す。典型的には、フォトレジスト 1 8 0 は、研磨停止層 1 3 0 上に形成される絶縁層 1 4 0 の上面に堆積される。この構成では、フォトレジスト 1 8 0 は、T S V キャビティ 1 3 4 内の絶縁層 1 4 0 上にも堆積される。フォトレジスト 1 8 0 の薄層が、この構成では T S V 1 3 4 の側壁の上部分に堆積される。20

#### 【 0 0 2 3 】

図 1 C は、研磨停止層 1 3 0 上に形成された絶縁層 1 4 0 の上部水平面に堆積されたフォトレジスト 1 8 0 の部分を除去するためのエッチバックプロセス(たとえば、O 2 プラズマプロセス)を示す。この構成では、T S V キャビティ 1 3 4 の底部の絶縁層 1 4 0 上に形成されたフォトレジスト 1 8 0 の部分が完全には除去されない。この構成では、T S V キャビティ 1 3 4 の側壁の上部分のフォトレジスト 1 8 0 は完全に除去される。本開示のこの態様では、フォトレジスト 1 8 0 が、T S V キャビティ 1 3 4 の底部分上に堆積された絶縁層 1 4 0 の部分を保護する。この構成では、T S V キャビティ 1 3 4 の底部分上に堆積された完全な絶縁層 1 4 0 が、T S V 1 3 4 内の導電性充填材料(図 3 A ~ 図 6 B )と基板 1 0 2 との間の接触を防止する。30

#### 【 0 0 2 4 】

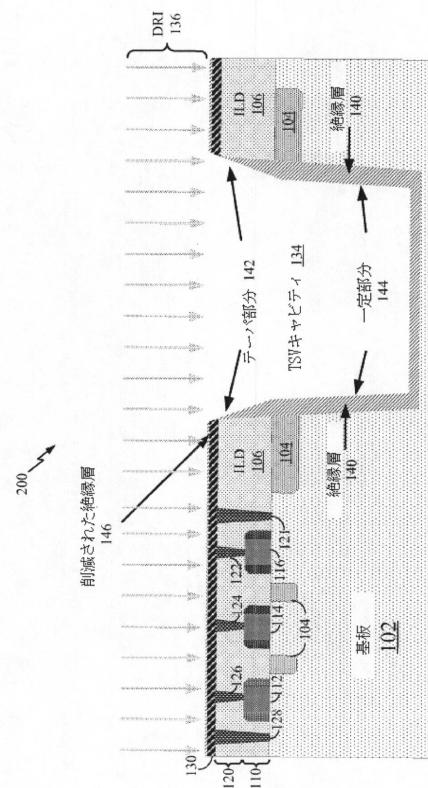

図 2 A は、本開示の一態様による T S V キャビティ 1 3 4 内に形成された絶縁層 1 4 0 のテーパ部分 1 4 2 を含む、IC デバイス 2 0 0 を示す断面図を示す。図 2 A に示すように、絶縁層 1 4 0 の方向性反応性イオン( D R I )エッチング 1 3 6 が行われる。D R I エッチング 1 3 6 は、研磨停止層 1 3 0 上に形成された絶縁層 1 4 0 の部分を削減して、削減された絶縁層 1 4 6 をもたらす。その上、この構成では、D R I エッチング 1 3 6 は、図 2 A に示すようにテーパ付けされている、側壁上に形成された絶縁層 1 4 0 の部分をもたらす。言い換えれば、T S V の側壁上に形成された絶縁層 1 4 0 の最上部分(すなわち、D R I エッチングプロセスに最も近接した T S V の側壁上の絶縁層 1 4 0 の部分)が、T S V の側壁上に形成された絶縁層 1 4 0 の下方部分と比べて減少した水平幅を有する。絶縁層 1 4 0 の一部分の水平幅の減少は、段階的または漸減的である。40

#### 【 0 0 2 5 】

T S V キャビティ 1 3 4 の上部の絶縁層 1 4 0 のテーパ部分 1 4 2 のテーパ形状は、T S V の上部の鋭角隅部の高電界を低減し得る。絶縁層 1 4 0 の(たとえば、垂直軸に沿った)テーパ部分 1 4 2 の長さは、トランジスタ技術に応じて決定され得る基板 1 0 2 内へ延びるデバイス(たとえば、能動デバイス 1 1 2 ~ 1 1 6 )の深さに基づく。D R I エッチング 1 3 6 が、絶縁層 1 4 0 の(たとえば、テーパ付けされない、減少しない)一定部分 1 4 4 に大きく影響しないことは理解されよう。その上、フォトレジスト 1 8 0 は、D R I エッチング 2 3 6 中に T S V キャビティ 1 3 4 の底部上の絶縁層 1 4 0 の部分を保護50

する。

**【0026】**

図2Bは、テーパ付けされている絶縁層140の部分をもたらす絶縁層のDRIエッチングを示す、ICデバイス200の断面図を示す。この例示的な構成では、図1B、図1C、および図2Aに示した例示的な構成で設けられたフォトレジスト180が設けられない。言い換えれば、図2Bの例示的な構成は、図2Aの例示的な構成が得られたプロセスに類似するプロセスによって得られるが、フォトレジスト層180を追加するプロセスが省かれている。TSVキャビティ134の底部に位置する絶縁層140を保護するためのフォトレジスト層がないので、絶縁層140のその部分は、DRIエッティング136によって削減される。いくつかの構成では、DRIエッティング136のプロセスパラメータが、DRIエッティング136がTSVキャビティ134の底部に到達するのを防止するよう10に調整される。これらの構成では、TSVキャビティ136の底部の絶縁層140は、フォトレジスト180の堆積なしに保護される。

**【0027】**

図2Aおよび図2Bに示すように、DRIエッティング136プロセスは、TSVキャビティ134の外側の基板102上の水平領域から絶縁層の一部を除去する。図2Bでは、TSVキャビティ134の内側の絶縁層140の一部も除去される。図2Aおよび図2Bに示すように、削減された絶縁層146は、CMPオーバー研磨の削減を可能にする。その後、CMPオーバー研磨が行われて、残りの削減された絶縁層146および研磨停止層130を除去し、中間工程プロセスによって形成されたMOL層120の導電素子121～128を露出する。本開示のこの態様では、削減された絶縁層146をエッティングすることで生じる誤り（すなわち、MOL層の潜在的除去）が、より厚い層をエッティングすることで生じる潜在的誤りより小さいので、CMPオーバー研磨の削減によって、基板102のMOL層120に対する影響が減少する。

20

**【0028】**

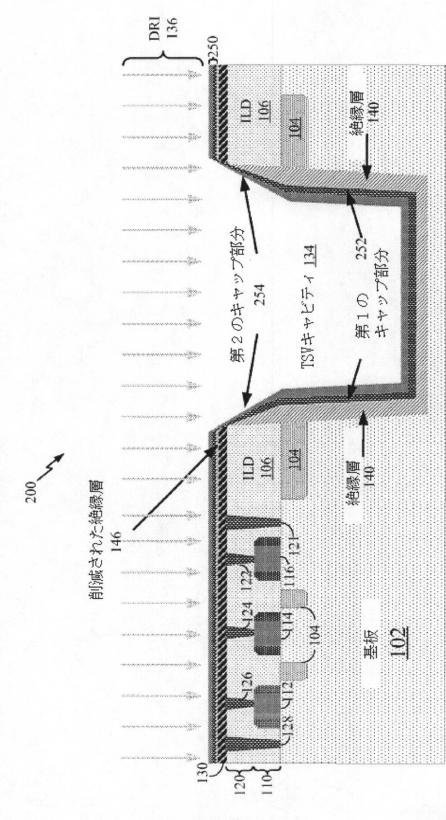

図2Cは、本開示の一態様による絶縁層140上の多層キャップ層250の形成を示す、図2BのICデバイス200の断面図を示す。典型的には、キャップ堆積が、絶縁層140上に多層キャップ層250を形成する。多層キャップ層250は、DRIエッティング136が後続する第1のキャップ層252の堆積によって形成され得る。DRIエッティング136は、削減された絶縁層146上に形成された第1のキャップ層252の部分を削減する。この構成では、DRIエッティング136は、テーパ付けされている（側壁上に形成された）第1のキャップ層252の部分がもたらす。すなわち、TSVの側壁上に形成された第1のキャップ層252の最上部分（すなわち、DRIエッティングプロセスに最も近接したTSVの側壁上に形成された第1のキャップ層252の部分）が、TSVの側壁上に形成された第1のキャップ層252の底部分と比べて減少した水平幅を有する。第1のキャップ層252の一部分の水平幅の減少は、段階的または漸減的である。

30

**【0029】**

図2Cにさらに示されるように、キャップ堆積およびDRIエッティングが第2のキャップ層254を形成するように繰り返される。この構成では、TSVの側壁上に形成された第2のキャップ層254の最上部分が、TSVの側壁上に形成された第1のキャップ層252の底部分と比べて減少した水平幅を有する。多層キャップ層250は、2つの層を有するように示されているが、単一膜を含む任意の数の層を備えることができる。さらに、多層キャップ層250は、テーパ部分を含むように示されているが、DRIエッティング136を省略して一定の水平幅で形成されてもよい。多層キャップ層250は、酸化ケイ素、窒化ケイ素、炭化ケイ素、酸窒化ケイ素、ポリイミド、もしくは同様の他の絶縁膜、または窒化チタン、窒化タンタル、タングステン、タンタル、もしくは他の同様の導電性膜を含むがこれらに限定されない、誘電体膜または導電性膜の複数の層を使用して形成され得る。多層キャップ層250は、2～1000ナノメートル(nm)の範囲の厚さを有することができる。

40

**【0030】**

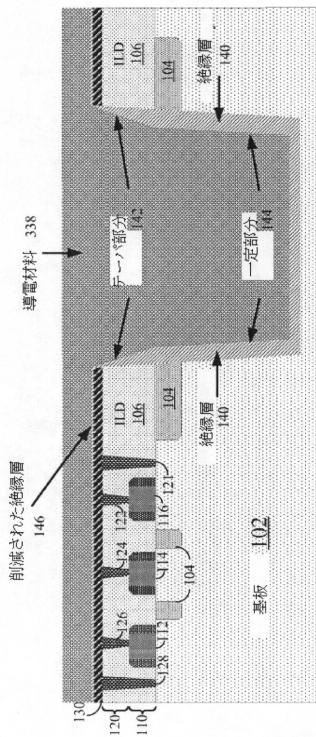

図3Aは、本開示の一態様によるTSVバリアシードおよび導電材料充填プロセスの後の図2BのICデバイス200を示す断面図を示す。図3Aに示すように、ICデバイス300は、ICデバイス200上に導電材料338を堆積するためのTSVバリアシードおよび導電材料充填プロセスを受ける。図3Aに示す導電材料338は、削減された絶縁層146を覆い、またTSVキャビティ134を充填する。絶縁層140のテーパ部分142および一定部分144は、TSVキャビティ134内の充填材料が基板102に接触するのを防止する。導電材料338は、銅、タングステン、または他の同様の導電材料を含み得るが、これらに限定されない。図示されていないが、フォトレジストは、TSVキャビティ134の底部分に位置する絶縁層140の部分上に残る場合、あるいはTSVキャビティ134を導電材料で充填する前に除去される場合がある。

10

#### 【0031】

図3Bは、本開示の一態様によるTSVバリアシードおよび銅充填プロセスの後の図2CのICデバイス200を示す断面図を示す。図3Bに示すように、ICデバイス300は、ICデバイス200上に導電材料338を堆積するためのTSVバリアシードおよび導電材料充填プロセスを受ける。図3Aに示す導電材料338は、削減された絶縁層146上の多層カップ層250を覆い、また、絶縁層140上の第1のカップ層252および第2のカップ層254を含むTSVキャビティ134を充填する。

#### 【0032】

図4Aは、本開示の一態様による図3AのICデバイス300に化学機械研磨(CMP)プロセス470が適用された後のICデバイス400を示す断面図を示す。図4Aに示すように、CMPプロセス470は、基板102の表面から導電材料338を除去する。たとえば、CMPプロセス470は、図3Aに示した研磨停止層130上に位置する導電材料338を除去する。図4Aに示すように、削減された絶縁層146および研磨停止層130は、CMPプロセス470後に基板102の表面上に残る。これらの層は、たとえば、図5Aに示すように、CMPオーバー研磨プロセッサによって除去される。

20

#### 【0033】

図4Bは、本開示の一態様による図3BのICデバイス300に化学機械研磨(CMP)プロセス470が適用された後のICデバイス400を示す断面図を示す。図4Bに示すように、CMPプロセス470は、基板102の表面から導電材料338を除去する。たとえば、CMPプロセス470は、図3Bに示したような削減された絶縁層146上の多層カップ層250に位置する導電材料338を除去する。図4Bに示すように、多層カップ層250の削減された部分、削減された絶縁層146、および研磨停止層130は、CMPプロセス470後に基板102の表面上に残る。これらの層は、たとえば、図5Bに示すように、CMPオーバー研磨プロセッサによって除去される。

30

#### 【0034】

図5Aは、本開示の一態様による絶縁層140によって囲まれたTSV560を含む、ICデバイス500を示す断面図を示す。図5Aに示すように、CMPオーバー研磨プロセス580は、基板102の表面504上の層の残りの部分を除去して、MOL層120の導電素子121～128を露出する。たとえば、CMPオーバー研磨プロセス580は、基板102のMOL層120の導電素子121～128に損傷を与えることなく、削減された絶縁層146および研磨停止層130(図4A参照)を除去する。すなわち、CMPオーバー研磨プロセス580の期間がより短く、したがって、図2A～図4Bに示すような削減された絶縁層146による基板102の下層のMOL層120に対する影響がより小さい。

40

#### 【0035】

図5Aに示すように、CMPオーバー研磨プロセス580がTSV560の形成を完了すると、TSV560では、その導電材料の直径が、TSVキャビティ134内の絶縁層140のテーパ部分142および一定部分144に応じて異なっている。典型的には、CMPオーバー研磨プロセス580は、図6Aに示すように、配線工程相互接続層の形成に備えて、削減された絶縁層146および研磨停止層130(図4A参照)を除去するため

50

に行われる。本開示のこの態様では、基板 102 は、ILD 層 106 から TSV560 を露出するためのプロセス（たとえば、研削）を受ける。

#### 【0036】

図 5B は、本開示の一態様による IC デバイス 500 の能動面近くでテーパ部分を有する絶縁層 140 上の多層キャップ層 250 によって囲まれた TSV560 を有する、図 4C の IC デバイス 400 を示す断面図を示す。典型的には、CMP オーバー研磨プロセス 580 は、図 6B に示すように、配線工程相互接続層の形成に備えて、多層キャップ層 250、削減された絶縁層 146 および研磨停止層 130（図 4B 参照）を除去するために行われる。

#### 【0037】

図 6A は、本開示の一態様による相互接続層を作製するために使用される配線工程（B E O L）プロセスの後の IC デバイス 600 を示す断面図を示す。典型的には、TSV 处理が完了した後、相互接続層 690 が B E O L プロセスによって基板 102 上に作製され、IC デバイス 600 の形成が完了する。この構成では、相互接続層 690 は、コンタクトレベルを含むように形成される。追加または代替の相互接続層が B E O L プロセスによって形成されてもよい。相互接続層 690 は、IC デバイス 600 を別の IC デバイス（図示せず）に電気的および／または熱的に結合する機構を提供する。

#### 【0038】

図 6B は、IC デバイス 600 を形成するための配線工程（B E O L）スタック作製の後の図 5B の IC デバイス 500 を示す断面図を示す。この構成では、IC デバイス 600 は、本開示の一態様による IC デバイス 500 の能動面近くでテーパ部分を有する絶縁層 140 上の多層キャップ層 250 によって囲まれた TSV560 を備える。相互接続層 690 は、IC デバイス 600 を別の IC デバイス（図示せず）に電気的および／または熱的に結合する機構を提供する。

#### 【0039】

図 7 は、本開示の一態様による、基板貫通ビア（TSV）を介して先端 CMOS（相補型金属酸化膜半導体）ノードに組み込むための方法 700 を示すブロック図である。ブロック 710 で、TSV キャビティ 134 が、たとえば、図 1A～図 5B に示すように、基板、および基板上の誘電体層（たとえば、層間誘電体層（ILD））を介して画成される。本明細書ではシリコン基板について述べているが、ガラス、サファイア、または任意の他の適切な材料を含む他の基板材料も企図される。ブロック 712 では、絶縁層が、たとえば、図 1A～図 1C に示すように、TSV キャビティ内および研磨停止層上に堆積される。

#### 【0040】

図 7 を再び参照すると、ブロック 714 では、絶縁層が、能動デバイスの上方に位置する絶縁層の部分（たとえば、停止研磨層上に位置する絶縁層の部分が除去される）を除去するためにエッティングされる。エッティングにより、テーパされている絶縁層の部分がもたらされる。たとえば、図 2A および図 2B に示すように、絶縁層 140 の方向性反応性イオン（DRI）エッティングが、TSV キャビティ 134 の側壁上の絶縁層 140 のテーパ部分 142 を生成する。ブロック 716 では、たとえば、図 2A～図 5B に示すように、TSV キャビティ 134 が導電材料によって充填される。本明細書では銅充填材について述べているが、他の導電材料も企図される。

#### 【0041】

一構成では、IC デバイス 600 が、誘電体層および基板を通じて伝導するための手段を備える。伝導手段は、導電性充填材料を有する。本開示の一態様では、伝導手段は、伝導手段によって列挙される機能を実行するように構成された図 5A～図 6B の TSV560 である。一構成では、IC デバイス 600 はまた、基板から伝導手段を絶縁するための手段を備える。絶縁するための手段は、導電材料を囲むことができ、ILD 層に実質的に近接したテーパ部分を備える。本開示の一態様では、絶縁手段は、絶縁手段によって列挙される機能を実行するように構成された図 4A～図 6B のテーパ部分 142 および一定部

分 144 を含む絶縁層 140 である。別の態様では、上記の手段は、上記の手段によって列挙される機能を実行するように構成されたデバイスまたは任意の層であってよい。

#### 【 0042 】

図 8 は、別のプロセスが採用される IC デバイス 800 を示す断面図を示す。本開示の一態様によれば、絶縁層の堆積の後、フォトレジスト 870 が、TSV キャビティ 834 内に、また TSV キャビティ 834 を覆って形成される。別の構成では、フォトレジストは、TSV キャビティ 834 を部分的に充填することができる。図 8 に示すように、絶縁層 840 と TSV キャビティ 834 上のフォトレジスト 870 とのエッチング 836 が行われる。エッチング 836 プロセスは、フォトレジスト 870 下ではない絶縁層 840 の一部（たとえば、図 9 に示すような TSV キャビティ 834 の外側の絶縁層）を除去する。TSV キャビティ 834 の側壁上の絶縁層 840 は、フォトレジスト 870 によって保護される。

10

#### 【 0043 】

図 9 は、本開示の一態様による削減された絶縁層 946 を形成する、図 8 に示したような絶縁層 840 の部分的エッチングおよびフォトレジスト 870 の除去の後の IC デバイス 900 を示す断面図を示す。図 9 に示すように、TSV キャビティ 834 内ではない絶縁層が基板 102 の表面上で削減されて、削減された絶縁層 946 を形成する。本開示の一態様では、削減された絶縁層 946 により、削減された絶縁層 946 および研磨停止層 130 を基板 102 の表面から除去するときに CMP オーバー研磨の削減が可能になる。本開示のこの態様では、CMP オーバー研磨の削減により、基板 102 の中間工程 (MOL) 層 120 の導電素子 121 ~ 128 に対する影響が限定される。

20

#### 【 0044 】

図 10 は、本開示の一態様による TSV バリアシードおよび導電材料充填プロセスの後の IC デバイス 1000 を示す断面図を示す。図 10 に示すように、TSV バリアシードおよび導電材料充填プロセスは、TSV キャビティ 834 を導電材料 338 で充填する。図示の例では、導電材料 338 は、削減された絶縁層 946 上にも形成される銅である。絶縁層 840 は、TSV キャビティ 834 内の導電材料 338 が基板 102 に接触するのを防止する。充填材料は、銅、タンゲステン、または他の同様の導電材料を含み得るが、これらに限定されない。

30

#### 【 0045 】

図 11 は、本開示の一態様による化学機械研磨 (CMP) プロセス 1160 の後の IC デバイス 1100 を示す断面図を示す。図 11 に示すように、CMP プロセス 1160 は、基板 102 の表面から導電材料 338 を除去する。図 11 に示すように、削減された絶縁層 946 および研磨停止層 130 は、基板 102 の表面上に残る。これらの層は、たとえば、図 12 に示すように、CMP オーバー研磨プロセスによって除去される。

30

#### 【 0046 】

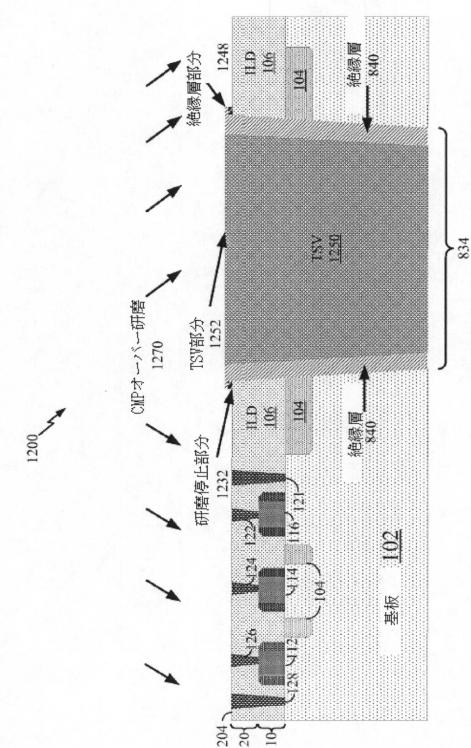

図 12 は、本開示の一態様による絶縁層 840 によって囲まれた TSV 1250 を含む、図 11 の IC デバイス 1200 を示す断面図を示す。図 12 に示すように、CMP オーバー研磨プロセス 1270 は、基板 102 の表面 1204 上の絶縁層の残りの部分を除去する。典型的には、CMP オーバー研磨プロセス 1270 は、基板 102 の MOL 部分に損傷を与えることなく、削減された絶縁層 946 および研磨停止層 130 (図 11 参照) を除去する。すなわち、CMP オーバー研磨プロセス 1270 はより短く、したがって、図 9 ~ 図 11 に示すような削減された絶縁層 946 による基板 102 の MOL 層 120 の導電素子 121 ~ 128 に対する影響がより小さい。

40

#### 【 0047 】

図 12 に示すように、CMP オーバー研磨プロセス 1270 は TSV 1250 の形成を完了し、TSV 1250 は、TSV キャビティ 834 の上へまた ILD 層 106 上に延びる TSV 部分 1252 を含む。典型的には、研磨停止部分 1232、および TSV 1250 の絶縁層部分 1248 は、TSV キャビティ 834 の外へ延びる。CMP オーバー研磨プロセス 1270 は、たとえば、図 6A に示したような BEOL プロセスを通して形成さ

50

れる相互接続層の形成に備えて、削減された絶縁層 946 および研磨停止層 130 (図 1 1 参照) を、基板 102 の表面 1204 から除去する。

#### 【0048】

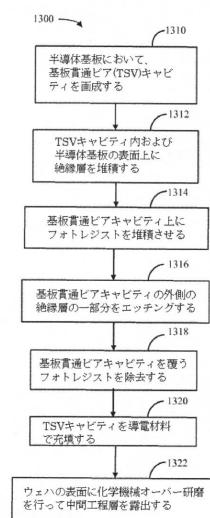

図 13 は、本開示の一態様による、基板貫通ビア (TSV) を介して先端 CMOS (相補型金属酸化膜半導体) ノードに組み込むための方法 1300 を示すブロック図である。ブロック 1310 で、TSV キャビティ 834 が、たとえば、図 8 ~ 図 12 に示すように、基板および ILD を介して画成される。本明細書ではシリコン基板について述べているが、他の適切な材料も企図される。ブロック 1312 では、絶縁層が、たとえば、図 8 に示すように、TSV キャビティ内および研磨停止層上に堆積される。

#### 【0049】

図 13 を再び参照すると、ブロック 1314 では、半導体基板がパターニングされて、基板貫通ビアキャビティだけを覆うフォトレジストを堆積させる。たとえば、図 8 に示すように、フォトレジスト 870 は、TSV キャビティ 834 の上へ、および TSV キャビティ 384 の側壁上に位置する絶縁層 840 を覆って形成される。ブロック 1316 では、TSV キャビティの外側の絶縁層の部分がエッチングされて、削減された絶縁層部分を形成する。たとえば、図 9 に示すように、エッチングが絶縁層 840 の一部分を除去して、削減された絶縁層 946 を形成する。ブロック 1318 では、TSV キャビティを覆うフォトレジストが除去される。ブロック 1320 では、たとえば、図 10 に示すように、TSV キャビティ 834 が導電材料 838 によって充填される。

#### 【0050】

図 13 を再び参照すると、ブロック 1322 では、化学機械オーバー研磨がウェハの表面に対して行われて、MOL プロセスによって生成された層を露出する。化学機械オーバー研磨は、図 11 および 12 に示すように、ウェハの基板の表面から、導電材料、絶縁層、および研磨停止層を除去する。たとえば、図 11 に示すように、導電材料、バリアシード、および CMP プロセス 1160 のエッチング停止が行われる。図 12 に見られるように、CMP オーバー研磨プロセス 1270 が行われ、絶縁層部分 1248、研磨停止部分 1232、および TSV 1250 の TSV 部分 1252 が残り、TSV キャビティ 834 の外側に突き出る。

#### 【0051】

一構成では、IC デバイス 1200 が、研磨停止層、層間誘電体 (IDL) 層、および基板を通じて伝導するための手段を備える。伝導手段は導電材料を有する。本開示の一態様では、伝導手段は、伝導手段によって列挙される機能を実行するように構成された図 12 の基板貫通ビア 1250 である。一構成では、IC デバイス 1200 はまた、半導体基板から伝導手段を絶縁するための手段を備える。この絶縁するための手段は、導電材料を囲み、研磨停止層の一部分を部分的に覆うことができる。本開示の一態様では、絶縁手段は、絶縁手段によって列挙される機能を実行するように構成された図 12 の研磨停止部分 1232 および絶縁層部分 1248 を含む絶縁層 840 である。別の態様では、上記の手段は、上記の手段によって列挙される機能を実行するように構成されたデバイスまたは任意の層であってよい。

#### 【0052】

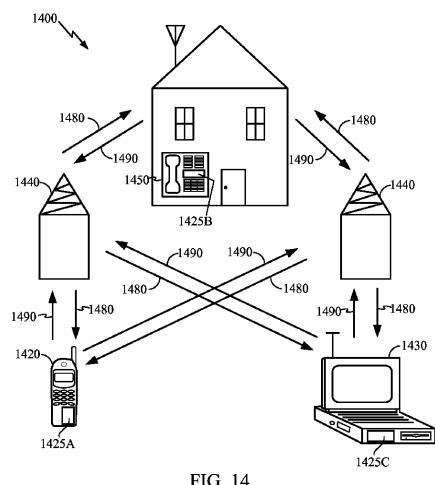

図 14 は、本開示の構成が有利に採用され得る例示的なワイヤレス通信システム 1400 を示すブロック図である。例示のために、図 14 は、3 つの遠隔ユニット 1420、1430 および 1450、ならびに 2 つの基地局 1440 を示す。ワイヤレス通信システムがこれよりも多くの遠隔ユニットおよび基地局を有してもよいことが認識されよう。遠隔ユニット 1420、1430、および 1450 は、IC デバイス 1425A、1425B、および 1425C を備え、これらの IC デバイスは、テーパ付けされた絶縁層 / 付加的研磨停止部分 / 絶縁層部分を有する本開示の基板貫通ビア (TSV) を備える。基地局、スイッチングデバイス、およびネットワーク機器を含む、IC を含む任意のデバイスは、本明細書で開示するテーパ付けされた絶縁層 / 付加的研磨停止部分 / 絶縁層部分によって囲まれた TSV も含み得ることが認識されよう。図 14 は、基地局 1440 から遠隔ユニ

10

20

30

40

50

ット 1420、1430 および 1450 への順方向リンク信号 1480、ならびに遠隔ユニット 1420、1430 および 1450 から基地局 1440 への逆方向リンク信号 1490 を示す。

#### 【0053】

図 14 では、遠隔ユニット 1420 は携帯電話として示され、遠隔ユニット 1430 はポータブルコンピュータとして示され、遠隔ユニット 1450 はワイヤレスローカルループシステム内の固定ロケーション遠隔ユニットとして示される。たとえば、遠隔ユニットは、携帯電話、ハンドヘルドパーソナル通信システム（P C S）ユニット、携帯情報端末などのポータブルデータユニット、G P S 対応デバイス、ナビゲーションデバイス、セットトップボックス、音楽プレーヤ、ビデオプレーヤ、娛樂ユニット、メータ読み取り機器などの固定ロケーションデータユニット、またはデータもしくはコンピュータ命令の記憶もしくは取り出しを行う任意の他のデバイス、またはそれらの任意の組合せであり得る。図 14 は、本開示の教示によるリモートユニットを示すが、本開示は、これらの例示的に示されたユニットには限定されない。本開示の態様は、テープ付けされた絶縁層／追加的研磨停止部分／絶縁層部分によって囲まれた T S V を含む任意のデバイスにおいて好適に採用され得る。10

#### 【0054】

ファームウェアおよび／またはソフトウェアの実装形態の場合、これら的方法を、本明細書に記載された機能を実行するモジュール（たとえば、プロシージャ、関数など）で実装することができる。本明細書に記載された方法を実装する際に、命令を有形に具現化する任意の機械可読媒体を使用することができます。たとえば、ソフトウェアコードはメモリに記憶され、プロセッサユニットにより実行され得る。メモリは、プロセッサユニット内に実装されてよく、またはプロセッサユニットの外部に実装されてよい。本明細書で使用される場合、「メモリ」という用語は、長期メモリ、短期メモリ、揮発性メモリ、不揮発性メモリ、または他のメモリのいずれかの種類を指し、メモリのいかなる特定の種類またはいかなる特定の数にも、あるいはメモリが記憶される媒体のいかなる特定の種類にも限定されない。20

#### 【0055】

本開示およびその利点が詳細に記載されたが、添付の特許請求の範囲によって規定される本開示の技術から逸脱することなく、本明細書において様々な変更、代用および改変が行われ得ることを理解されたい。たとえば、「上」および「下」などの関係用語が、基板または電子デバイスに関して使用される。もちろん、基板または電子デバイスが反転した場合、上は下に、下は上になる。加えて、横向きの場合、上および下は、基板または電子デバイスの側面を指す場合がある。さらに、本出願の範囲は、本明細書に記載されたプロセス、機械、製造、物質組成、手段、方法、およびステップの特定の実施形態に限定されるものではない。当業者が本開示から容易に諒解するように、本明細書に記載された対応する実施形態と実質的に同じ機能を実行するか、または実質的に同じ結果を実現する、既存または今後開発されるプロセス、機械、製造、物質組成、手段、方法、またはステップが、本開示に従って利用され得る。したがって、添付の特許請求の範囲は、そのようなプロセス、機械、製造、物質組成、手段、方法、またはステップをそれらの範囲内に含むものとする。30

#### 【符号の説明】

#### 【0056】

- 100 I C デバイス

- 102 基板

- 104 S T I 領域

- 106 I D L 層

- 110 F E O L 相互接続層

- 120 M O L 層

- 130 研磨ストップ層

|           |                  |    |

|-----------|------------------|----|

| 1 1 2     | 能動デバイス           |    |

| 1 1 4     | 能動デバイス           |    |

| 1 1 6     | 能動デバイス           |    |

| 1 2 1     | 導電素子             |    |

| 1 2 2     | 導電素子             |    |

| 1 2 4     | 導電素子             |    |

| 1 2 6     | 導電素子             |    |

| 1 2 8     | 導電素子             |    |

| 1 3 4     | T S V キャビティ      |    |

| 1 3 6     | D R I エッ칭ング      | 10 |

| 1 4 0     | 絶縁層              |    |

| 1 4 2     | テーパ部分            |    |

| 1 4 4     | 一定部分             |    |

| 1 4 6     | 削減された絶縁層         |    |

| 1 5 2     | テーパ部分            |    |

| 1 5 4     | 一定部分             |    |

| 2 0 0     | I C デバイス         |    |

| 2 5 0     | 多層キャップ層          |    |

| 2 5 2     | 第1のキャップ部分        |    |

| 2 5 4     | 第2のキャップ部分        | 20 |

| 3 0 0     | I C デバイス         |    |

| 3 3 8     | 導電材料             |    |

| 4 0 0     | I C デバイス         |    |

| 4 5 0     | T S V            |    |

| 4 7 0     | C M P プロセス       |    |

| 5 0 0     | I C デバイス         |    |

| 5 0 4     | 表面               |    |

| 5 6 0     | T S V            |    |

| 5 8 0     | C M P オーバー研磨プロセス |    |

| 6 0 0     | I C デバイス         | 30 |

| 6 9 0     | 相互接続層            |    |

| 8 0 0     | I C デバイス         |    |

| 8 3 4     | T S V キャビティ      |    |

| 8 3 6     | エッ칭ング            |    |

| 8 4 0     | 絶縁層              |    |

| 8 7 0     | フォトレジスト          |    |

| 9 0 0     | I C デバイス         |    |

| 9 4 6     | 削減された絶縁層         |    |

| 1 0 0 0   | I C デバイス         |    |

| 1 1 0 0   | I C デバイス         | 40 |

| 1 1 6 0   | C M P プロセス       |    |

| 1 2 0 0   | I C デバイス         |    |

| 1 2 3 2   | 研磨停止部分           |    |

| 1 2 4 8   | 絶縁層部分            |    |

| 1 2 5 2   | T S V 部分         |    |

| 1 2 7 0   | C M P オーバー研磨プロセス |    |

| 1 4 0 0   | ワイヤレス通信システム      |    |

| 1 4 2 0   | 遠隔ユニット           |    |

| 1 4 4 0   | 基地局              |    |

| 1 4 2 5 A | I C デバイス         | 50 |

1 4 2 5 B I C デバイス

1 4 2 5 C I C デバイス

1 4 3 0 遠隔ユニット

1 4 5 0 遠隔ユニット

1 4 8 0 順方向リンク信号

1 4 9 0 逆方向リンク信号

【図 14】

FIG. 14

【図 1 A】

FIG. 1A

【図 1 B】

【図 1 C】

【図 2 A】

【図 2 B】

【図2C】

FIG. 2C

【図3A】

FIG. 3A

【図3B】

FIG. 3B

【図4A】

FIG. 4A

【図4B】

【図5A】

【図 5 B】

【図 6 A】

【図 6 B】

【図7】

FIG. 7

【 四 8 】

【図9】

FIG. 9

【図10】

FIG. 10

【 図 1 1 】

FIG. 11

【図12】

FIG. 12

【図13】

FIG. 13

---

フロントページの続き

(31)優先権主張番号 13/724,038

(32)優先日 平成24年12月21日(2012.12.21)

(33)優先権主張国 米国(US)

早期審査対象出願

(72)発明者 シーチュン・グ

アメリカ合衆国・カリフォルニア・92121・サン・ディエゴ・モアハウス・ドライブ・577

5

審査官 佐藤 靖史

(56)参考文献 欧州特許出願公開第00926726(EP, A1)

米国特許出願公開第2007/0184654(US, A1)

(58)調査した分野(Int.Cl., DB名)

H01L 21/3205 - 21/3213

21/768

23/52 - 23/522