(12)

# Offenlegungsschrift

(21) Aktenzeichen: 10 2015 217 930.3

(22) Anmeldetag: 18.09.2015

(43) Offenlegungstag: 07.04.2016

(51) Int Cl.: **H01L 21/336** (2006.01)

H01L 29/78 (2006.01)

(30) Unionspriorität:

14/489,817

18.09.2014 US

(71) Anmelder:

Soitec, Bernin, FR

(74) Vertreter:

Grünecker Patent- und Rechtsanwälte PartG mbB, 80802 München, DE

(72) Erfinder:

Nguyen, Bich-Yen, Austin, Tex., US; Sadaka, Mariam, Austin, Tex., US; Malville, Christophe, La

Terrasse, FR

Die folgenden Angaben sind den vom Anmelder eingereichten Unterlagen entnommen

(54) Bezeichnung: Verfahren zur Herstellung von Halbleiterstrukturen mit Finnenstrukturen mit unterschiedlichen Spannungszuständen, und zugehörige Halbleiterstrukturen

(57) Zusammenfassung: Verfahren zum Bilden einer Halbleiterstruktur beinhalten das Bereitstellen eines Mehrschichtsubstrats mit einer epitaxialen Basisschicht, die über einer verspannten primären Halbleiterschicht über einer eingebetteten Oxidschicht liegt. Elemente in der epitaxialen Basisschicht werden zum Ändern eines Spannungszustands in der primären Halbleiterschicht in einer ersten Region des Mehrschichtsubstrats verwendet, ohne dabei einen Spannungszustand in der primären Halbleiterschicht in einer zweiten Region des Mehrschichtsubstrats zu ändern. Eine erste Vielzahl von Transistor-Kanalstrukturen wird ausgebildet, die jeweils einen Abschnitt der primären Halbleiterschicht in der ersten Region des Mehrschichtsubstrats umfassen, und eine zweite Vielzahl von Transistor-Kanalstrukturen wird ausgebildet, die jeweils einen Abschnitt der primären Halbleiterschicht in der zweiten Region des Mehrschichtsubstrats umfassen. Zu Halbleiterstrukturen, die mithilfe solcher Verfahren hergestellt werden, können Transistor-Kanalstrukturen mit unterschiedlichen Spannungszuständen zählen

### **Beschreibung**

#### **Technisches Gebiet**

**[0001]** Ausführungsbeispiele der vorliegenden Offenlegungsschrift betreffen Verfahren, die zur Herstellung von Metalloxid-Feldeffekttransistoren vom n-Typ (NMOS) und Metalloxid-Feldeffekttransistoren vom p-Typ (PMOS) verwendet werden können, die unterschiedliche Spannungszustände in einer gemeinsamen Schicht auf einem Halbleitersubstrat aufweisen, und Halbleiterstrukturen und Vorrichtungen, die unter Verwendung solcher Verfahren hergestellt werden.

#### Hintergrund

[0002] Halbleitervorrichtungen wie Mikroprozessoren und Speichergeräte verwenden Festkörpertransistoren als grundlegende primäre Betriebsstruktur für ihre integrierten Schaltungen. Ein häufig für Halbleiterstrukturen und -vorrichtungen verwendeter Transistortyp ist der Feldeffekttransistor (FET), der im Allgemeinen einen Source-Kontakt, einen Drain-Kontakt und einen oder mehrere Gate-Kontakte beinhaltet. Eine halbleitende Kanalregion erstreckt sich zwischen dem Source-Kontakt und dem Drain-Kontakt. Zwischen dem Source-Kontakt und dem Gate-Kontakt sind ein oder mehrere pn-Verbindungen definiert. Der Gate-Kontakt befindet sich neben mindestens einem Abschnitt der Kanalregion, und die Leitfähigkeit der Kanalregion wird durch die Anwesenheit eines elektrischen Feldes geändert. Somit wird ein elektrisches Feld in der Kanalregion durch Anlegen einer Spannung an den Gate-Kontakt bereitgestellt. So kann beispielsweise elektrischer Strom durch den Transistor von dem Source-Kontakt zu dem Drain-Kontakt durch die Kanalregion fließen, wenn eine Spannung an den Gate-Kontakt angelegt wird, kann jedoch nicht durch den Transistor von dem Source-Kontakt zu dem Drain-Kontakt in Abwesenheit einer an den Gate-Kontakt angelegten Spannung fließen.

**[0003]** In jüngster Zeit wurden Feldeffekttransistoren (FETs) entwickelt, die diskrete, langgestreckte Kanalstrukturen aufweisen, welche als "Finnen" bezeichnet werden. Solche Transistoren werden im Stand der Technik häufig als "FinFET" bezeichnet. Für FinFETs wurden im Stand der Technik viele verschiedene Konfigurationen vorgeschlagen.

**[0004]** Die langgestreckten Kanalstrukturen oder Finnen eines FinFETs umfassen ein Halbleitermaterial, das entweder n-Typ oder p-Typ dotiert sein kann. Außerdem wurde gezeigt, dass die Leitfähigkeit von n-Typ-dotierten Halbleitermaterialien verbessert werden kann, wenn sich das n-Typ-Halbleitermaterial in einem Zustand der Zugspannung befindet, und die Leitfähigkeit des p-Typ-Halbleitermaterials verbessert werden kann, wenn sich das p-Typ-

Halbleitermaterial in einem Zustand von Druckspannung befindet.

[0005] Aktuell verwendete FinFETs weisen einen Querschnitt von weniger als 22 nm auf. Solche FinFETs können vollständig verarmte (undotierte) Kanäle enthalten, welche die elektrostatische Leistung der Transistoren verbessern und Probleme im Zusammenhang mit zufälligen Dotierstofffluktuationen verhindern.

**[0006]** Es hat sich gezeigt, dass durch die Einführung von Zugspannung in die Kanalregion eines Transistors die Elektronenbeweglichkeit von n-Typ-FETs verbessert werden kann, und dass die Einführung von Druckspannung in die Kanalregion eines Transistors die Löcherbeweglichkeit von p-Typ-FETs verbessern kann.

## Kurze Zusammenfassung

[0007] Die nachfolgende Zusammenfassung soll eine Auswahl von Konzepten in vereinfachter Form vorstellen. Diese Konzepte werden unten in der ausführlichen Beschreibung von Ausführungsbeispielen der Offenbarung im Detail beschrieben. Die Zusammenfassung soll keine Hauptmerkmale oder wesentlichen Merkmale des beanspruchten Erfindungsgegenstands identifizieren oder den Geltungsbereich des beanspruchten Erfindungsgegenstands beschränken.

[0008] In einigen Ausführungsbeispielen beinhaltet die vorliegende Offenlegungsschrift ein Verfahren zum Herstellen einer Halbleiterstruktur. Es wird ein Mehrschichtsubstrat bereitgestellt, das ein Basissubstrat beinhaltet, eine eingebettete Oxidschicht über einer Oberfläche des Basissubstrats, eine verspannte primäre Halbleiterschicht über der eingebetteten Oxidschicht auf einer Seite gegenüber dem Basissubstrat, und eine epitaxiale Basisschicht über der verspannten Halbleiterschicht auf einer Seite gegenüber der eingebetteten Oxidschicht. Elemente diffundieren aus der epitaxialen Basisschicht in die verspannte primäre Halbleiterschicht in einer ersten Region des Mehrschichtsubstrats, ohne dass Elemente aus der epitaxialen Basisschicht in die verspannte primäre Halbleiterschicht in einer zweiten Region des Mehrschichtsubstrats diffundieren, und eine Konzentration der diffundierten Elemente wird in der primären Halbleiterschicht in der ersten Region so angereichert, dass ein Spannungszustand in der primären Halbleiterschicht in der ersten Region von einem Spannungszustand in der primären Halbleiterschicht in der zweiten Region abweicht. Eine erste Vielzahl von Transistor-Kanalstrukturen wird ausgebildet, die jeweils einen Abschnitt der primären Halbleiterschicht in der ersten Region des Mehrschichtsubstrats umfassen, und eine zweite Vielzahl von Transistor-Kanalstrukturen wird ausgebildet, die jeweils einen Abschnitt der primären Halbleiterschicht in der zweiten Region des Mehrschichtsubstrats umfassen.

[0009] In weiteren Ausführungsbeispiel beinhaltet die vorliegende Offenlegungsschrift ein Verfahren zum Herstellen einer Halbleiterstruktur, in der ein Mehrschichtsubstrat vorgesehen ist, das ein Basissubstrat beinhaltet, eine eingebettete Oxidschicht über einer Oberfläche des Basissubstrats, eine verspannte primäre Halbleiterschicht über der eingebetteten Oxidschicht auf einer Seite gegenüber dem Basissubstrat, und eine epitaxiale Basisschicht über der verspannten Halbleiterschicht auf einer Seite gegenüber der eingebetteten Oxidschicht. Eine erste Region des Mehrschichtsubstrats wird mit einer ersten Maskenschicht maskiert und ein Abschnitt der epitaxialen Basisschicht wird von einer zweiten Region des Mehrschichtsubstrats entfernt. Die erste Maskenschicht wird von der ersten Region des Mehrschichtsubstrats entfernt, und die zweite Region des Mehrschichtsubstrats wird mit einer zweiten Maskenschicht maskiert. Elemente diffundieren aus der epitaxialen Basisschicht in die verspannte primäre Halbleiterschicht in der ersten Region des Mehrschichtsubstrats, und ein Spannungszustand der primären Halbleiterstruktur in der ersten Region des Mehrschichtsubstrats ändert sich, ohne dass Elemente in die verspannte primäre Halbleiterschicht in der zweiten Region des Mehrschichtsubstrats diffundieren. Eine erste Vielzahl von Transistor-Kanalstrukturen wird ausgebildet, die jeweils einen Abschnitt der primären Halbleiterschicht in der ersten Region des Mehrschichtsubstrats umfassen, und eine zweite Vielzahl von Transistor-Kanalstrukturen wird ausgebildet, die jeweils einen Abschnitt der primären Halbleiterschicht in der zweiten Region des Mehrschichtsubstrats umfassen.

[0010] In weiteren Ausführungsbeispielen beinhaltet die vorliegende Offenlegungsschrift eine Halbleiterstruktur mit einem Mehrschichtsubstrat, das ein Basissubstrat umfasst, eine eingebettete Oxidschicht über einer Oberfläche des Basissubstrats und eine primäre Halbleiterschicht über der eingebetteten Oxidschicht auf einer Seite gegenüber dem Basissubstrat. Ein Abschnitt der primären Halbleiterschicht in einer ersten Region des Mehrschichtsubstrats umfasst Si<sub>v</sub>Ge<sub>1-v</sub>, wobei y zwischen etwa 0,20 und etwa 0,99 liegt, und ein Abschnitt der primären Halbleiterschicht in einer zweiten Region des Mehrschichtsubstrats zugverspanntes Si umfasst. Der Abschnitt der primären Halbleiterschicht in der ersten Region des Mehrschichtsubstrats weist eine kristallographische Spannung auf, die von einer kristallographischen Spannung des Abschnitts der primären Halbleiterschicht in der zweiten Region des Mehrschichtsubstrats abweicht.

Kurze Beschreibung der Zeichnungen

**[0011]** Zwar endet die Beschreibung mit Patentansprüchen, die speziell herausstellen und dezidiert beanspruchen, was als Ausführungsbeispiele der Erfindung anzusehen ist, doch gehen die Vorteile der Ausführungsbeispiele der Offenlegungsschrift besser aus der Beschreibung bestimmter Beispiele von Ausführungsbeispielen der Offenlegungsschrift hervor, wenn diese in Verbindung mit den begleitenden Zeichnungen gelesen wird, wobei:

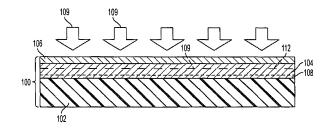

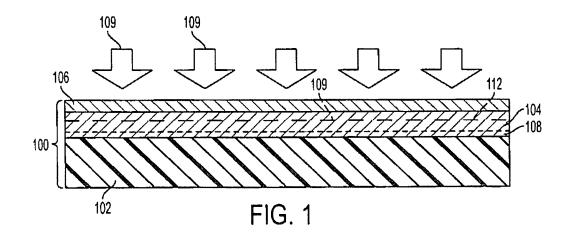

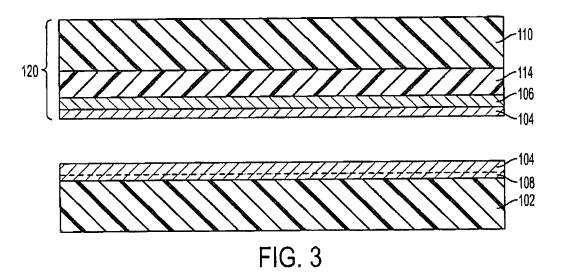

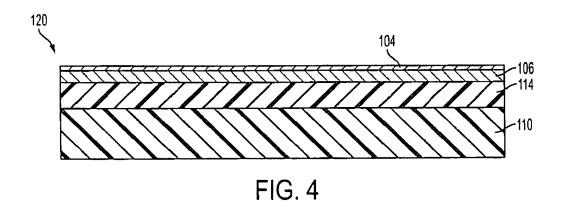

**[0012] Fig.** 1 bis **Fig.** 4 vereinfachte, schematische Querschnittdarstellungen sind, welche die Herstellung eines Mehrschichtsubstrats illustrieren, das gemäß Ausführungsbeispielen der vorliegenden Offenlegungsschrift verwendet werden kann.

**[0013] Fig.** 1 die Implantation von Ionen in ein Donatorsubstrat zeigt, das eine Halbleitermasse, eine epitaxiale Basisschicht und eine verspannte primäre Halbleiterschicht aufweist, wobei die implantierten Ionen eine geschwächte Zone in der epitaxialen Basisschicht bilden;

**[0014] Fig.** 2 das Bonden des Donatorsubstrats Aus **Fig.** 1 auf ein Empfängersubstrat darstellt;

**[0015] Fig.** 3 die Trennung des Donatorsubstrats entlang der geschwächten Zone darstellt;

[0016] Fig. 4 ein Mehrschichtsubstrat zeigt, das nach der Trennung des Donatorsubstrats entlang der geschwächten Zone aus Fig. 3 gebildet wird;

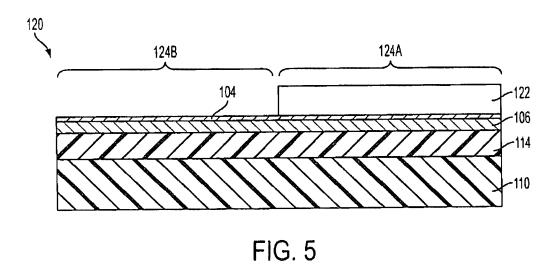

[0017] Fig. 5 eine erste Maskenschicht darstellt, die eine erste Region des Mehrschichtsubstrats aus Fig. 4 bedeckt, während eine weitere zweite Region des Mehrschichtsubstrats nicht durch die erste Maskenschicht abgedeckt wird und freiliegt;

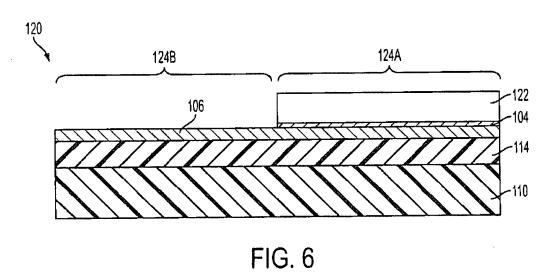

[0018] Fig. 6 die Halbleiterstruktur aus Fig. 5 nach dem Entfernen eines Abschnitts der epitaxialen Basisschicht von über der primären Halbleiterschicht in der zweiten Region des Mehrschichtsubstrats darstellt, während ein anderer Abschnitt der epitaxialen Basisschicht über der primären Halbleiterschicht unter der ersten Maskenschicht aus Fig. 5 in der ersten Region des Mehrschichtsubstrats verbleibt;

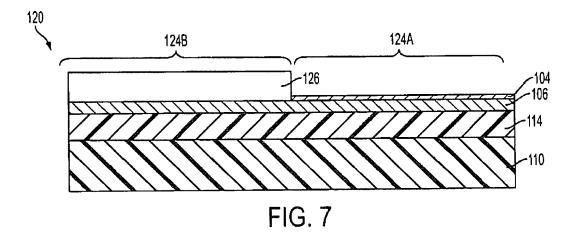

[0019] Fig. 7 eine Struktur darstellt, die durch Entfernen der ersten Maskenschicht aus der ersten Region des Mehrschichtsubstrats und durch Bereitstellen einer zweiten Maskenschicht über der primären Halbleiterschicht in der zweiten Region des Mehrschichtsubstrats gebildet wird;

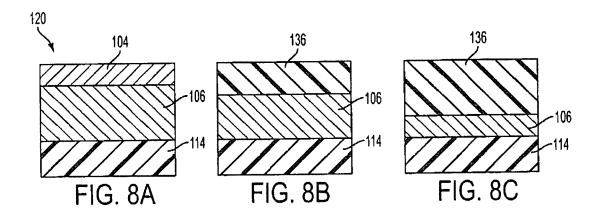

**[0020] Fig.** 8A bis **Fig.** 8C vergrößerte Darstellungen eines Abschnitts der ersten Region des Mehrschichtsubstrats sind, die einen Kondensationsprozess illus-

trieren, der zum Diffundieren von einem oder mehreren Elementen aus der epitaxialen Basisschicht in die primäre Halbleiterschicht in der ersten Region des Mehrschichtsubstrats verwendet wird, um einen Spannungszustand in der primären Halbleiterschicht in der ersten Region des Mehrschichtsubstrats zu ändern;

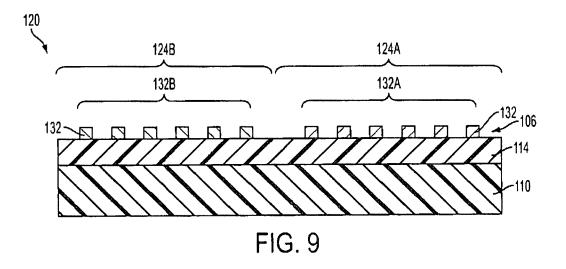

**[0021]** Fig. 9 eine Vielzahl von Finnenstrukturen darstellt, die durch Ätzen durch die primäre Halbleiterschicht der Struktur aus Fig. 7 gebildet werden; und

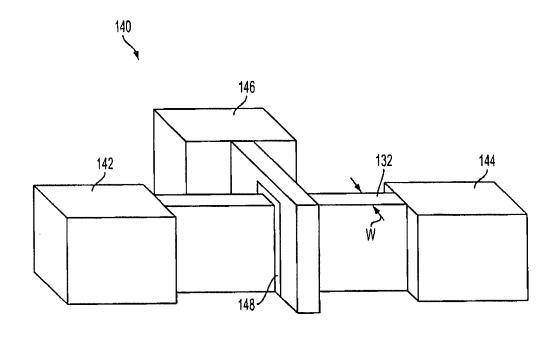

**[0022] Fig.** 10 eine beispielhafte Struktur eines Fin-FET-Transistors darstellt.

## Ausführliche Beschreibung

**[0023]** Die hier präsentierten Illustrationen sind nicht als tatsächliche Ansichten einer bestimmten Halbleiterstruktur, einer Vorrichtung, eines Systems oder Verfahrens aufzufassen, sondern sind lediglich idealisierte Darstellungen, die zur Veranschaulichung von Ausführungsbeispielen der Offenlegungsschrift dienen.

[0024] Die hier verwendeten Titel sind nicht als einschränkend für den Geltungsbereich der Ausführungsbeispiele der Erfindung zu verstehen, wie in den unten stehenden Ansprüchen und deren rechtlichen Äquivalenten definiert. Die in einem bestimmten Titel ausgedrückten Konzepte sind generell auf andere Abschnitte in der gesamten Beschreibung anwendbar.

**[0025]** Die Begriffe "erstes" und "zweites" in der Beschreibung und den Ansprüchen dienen zur Unterscheidung ähnlicher Elemente.

**[0026]** In der vorliegenden Beschreibung bezeichnen die Begriffe "Finne" und "Finnenstruktur" ein langgestrecktes, dreidimensionales, finites und begrenztes Volumen eines Halbleitermaterials mit einer Länge, einer Breite und einer Höhe, wobei die Länge größer als die Breite ist. Die Breite und Höhe der Finne kann entlang der Länge der Finne in einigen Ausführungsbeispielen variieren.

[0027] Die Verfahren, die zur Herstellung von Halbleitervorrichtungen verwendet werden können, sind unten unter Bezug auf die Figuren beschrieben. Wie unten noch ausführlicher beschrieben wird, beinhalten die Verfahren im Allgemeinen das Bereitstellen eines Mehrschichtsubstrats, das ein Basissubstrat beinhaltet, eine eingebettete Oxidschicht (buried oxide, BOX) über einer Oberfläche des Basissubstrats, eine verspannte primäre Halbleiterschicht über der BOX-Schicht auf einer Seite gegenüber dem Basissubstrat, und eine epitaxiale Basisschicht über der verspannten Halbleiterschicht auf einer Seite gegenüber der BOX-Schicht. Die epitaxiale Basisschicht kann ei-

ne Schicht umfassen, auf der zuvor die primäre Halbleiterschicht epitaxial gezüchtet wurde, wie nachstehend erläutert wird. Nach dem Bereitstellen des Mehrschichtsubstrats, kann das Mehrschichtsubstrat dahingehend verarbeitet werden, dass der Spannungszustand in einer Region der primären Halbleiterschicht geändert wird, ohne einen Spannungszustand in einer anderen Region der primären Halbleiterschicht zu ändern, so dass Regionen mit unterschiedlichen Spannungszuständen in der primären Halbleiterschicht vorhanden sind. Anschließend können n-Typ-Transistorstrukturen in einer Region oder in Regionen der primären Halbleiterschicht hergestellt werden, die einen Spannungszustand aufweisen, der für eine erhöhte Elektronenbeweglichkeit bevorzugt wird, und p-Typ-Transistorstrukturen können in einer Region oder in Regionen der primären Halbleiterschicht hergestellt werden, die einen Spannungszustand aufweisen, der für eine gesteigerte Löcherbeweglichkeit bevorzugt wird.

[0028] Ausführungsbeispiele für Verfahren, die zum Bereitstellen eines Mehrschichtsubstrats verwendet werden können, werden unten unter Bezug auf Fig. 1 bis Fig. 4 erläutert. Fig. 1 zeigt ein Donatorsubstrat 100, das eine Halbleitermasse 102 beinhaltet, eine epitaxiale Basisschicht 104 auf der Halbleitermasse 102 und eine verspannte Halbleiterschicht 106 auf einer Seite der epitaxialen Basisschicht 104 gegenüber der Halbleitermasse 102.

[0029] Die Halbleitermasse 102 kann einen Die oder Wafer umfassen, der beispielsweise aus einem Halbleitermaterial (z. B. Silizium, Siliziumkarbid, Germanium, einem III-V-Halbleitermaterial usw.), einem Keramikmaterial (z. B. Siliziumoxid, Aluminiumoxid, Siliziumkarbid usw.) oder einem Metallmaterial (z. B. Molybdän usw.) besteht. Die Halbleitermasse 102 kann in einigen Ausführungsbeispielen eine monokristalline oder polykristalline Mikrostruktur aufweisen. In anderen Ausführungsbeispielen kann die Halbleitermasse 102 amorph sein. Die Halbleitermasse 102 kann eine Dicke im Bereich von beispielsweise 400 µm bis etwa 900 µm aufweisen (z. B. etwa 750 µm).

[0030] Die Schichten über der Halbleitermasse 102, wie beispielsweise die epitaxiale Basisschicht 104 und die primäre Halbleiterschicht 106, können mit Hilfe verschiedener Prozesse aufgebracht oder "gezüchtet" werden, wie beispielsweise durch chemisches Aufdampfen (CVD), Atomlagenabscheidung (ALD), Vakuumaufdampfen (PLD), Gasphasenepitaxie (VPE) und Molekularstrahlepitaxie (MBE).

[0031] In einigen Ausführungsbeispielen kann die epitaxiale Basisschicht 104 ein Material umfassen, das die Erhaltung von Spannung in dem Kristallgitter der überlagernden primären Halbleiterschicht 106 in der nachfolgenden Verarbeitung unterstützt, wie unten noch ausführlicher erläutert wird. So kann

die epitaxiale Basisschicht **104** eine Zusammensetzung und/oder Schichtdicke aufweisen, die so gewählt wird, dass die epitaxiale Basisschicht **104** die Spannung in dem Kristallgitter der überlagernden primären Halbleiterschicht **106** in der nachfolgenden Verarbeitung erhalten kann, wie unten noch ausführlicher erläutert wird.

[0032] Die primäre Halbleiterschicht 106 kann beispielsweise eine Schicht aus verspanntem Silizium (Si), verspanntem Germanium (Ge), verspanntem Silizium-Germanium (SiGe) oder verspanntem III-V-Halbleitermaterial umfassen. So kann die verspannte primäre Halbleiterschicht 106 eine Kristallstruktur haben, die Gitterparameter aufweist, die entweder über (Zugspannung) oder unter (Druckspannung) den entspannten Gitterparametern liegen, welche die Kristallstruktur der entsprechenden verspannten Halbleiterschicht 106 normalerweise aufweisen würde, wenn die verspannte Halbleiterschicht 106 in freistehender Halbleitermasseform im Gleichgewichtszustand vorläge. Die primäre Halbleiterschicht 106 kann eine durchschnittliche Schichtdicke von etwa 50 nm oder weniger aufweisen, oder sogar 35 nm oder weniger, auch wenn in einigen Ausführungsbeispielen der vorliegenden Offenlegungsschrift dickere Schichten von verspanntem Halbleitermaterial verwendet werden.

[0033] Optional können eine oder mehrere Pufferschichten 108 zwischen der Halbleitermasse 102 und der epitaxialen Basisschicht 104 angeordnet werden, um das epitaxiale Wachstum der epitaxialen Basisschicht 104 und der primären Halbleiterschicht 106 über der Halbleitermasse 102 zu erleichtern.

[0034] Als nicht einschränkendes spezielles Beispiel kann die Halbleitermasse 102 des Donatorsubstrats 101 monokristallines Siliziumsubstrat umfassen, die epitaxiale Basisschicht 104 kann Si<sub>x</sub>Ge<sub>1-x</sub> umfassen (wobei x zwischen etwa 0,01 bis etwa 0,99 liegt oder spezieller zwischen etwa 0,20 bis etwa 0,80), und die primäre Halbleiterschicht 106 kann verspannte Silizium (sSi) oder verspanntes Si<sub>v</sub>Ge<sub>1-v</sub> umfassen (wobei y zwischen etwa 0,20 bis etwa 0,99 liegt). In einigen Ausführungsbeispielen kann das SixGe1-x der epitaxialen Basisschicht 104 zumindest im Wesentlichen entspanntes Si<sub>x</sub>Ge<sub>1-x</sub> umfassen. Mit anderen Worten kann das Si<sub>x</sub>Ge<sub>1-x</sub> der epitaxialen Basisschicht 104 in einigen Ausführungsbeispielen zumindest im Wesentlichen frei von kristallographischer Spannung sein.

**[0035]** Eine oder mehrere Pufferschichten **108**, die  $\mathrm{Si_zGe_{1-7}}$  umfassen (wobei der Wert von z stufenweise oder kontinuierlich mit zunehmendem Abstand von der Halbleitermasse **102** graduell zunimmt), können zwischen dem Silizium der Halbleitermasse **102** und der epitaxialen  $\mathrm{Si_xGe_{1-x}}$ -Basisschicht **104** angeordnet sein.

[0036] Der Wert von x in der epitaxialen  $\mathrm{Si_xGe_{1-x^-}}$ Basisschicht 104 kann so ausgewählt werden, dass er ein erwünschtes Maß an Spannung in dem überlagernden Si oder  $\mathrm{Si_yGe_{1-y}}$  der primären Halbleiterschicht 106 bewirkt. Wie im Stand der Technik bekannt, herrscht zwischen Si und Ge eine Gitterfehlanpassung von etwa 4,2%. Somit bestimmt der Gehalt an Ge in der epitaxialen  $\mathrm{Si_xGe_{1-x^-}}$ Basisschicht 104 zumindest zum Teil die Werte der Gitterparameter in der epitaxialen  $\mathrm{Si_xGe_{1-x^-}}$ Basisschicht 104 und damit die Größe der kristallographischen Spannung in der Gitterstruktur des Si oder  $\mathrm{Si_yGe_{1-y}}$  der überlagernden epitaxialen primären Halbleiterschicht 106.

[0037] Die epitaxiale Basisschicht 104 und die primäre Halbleiterschicht 106 können jeweils eine Dicke unterhalb ihrer jeweiligen kritischen Dicke aufweisen, um die anfängliche Entspannung und Bildung von lokalen Defekten in der Kristallstruktur zu vermeiden.

[0038] Nach dem Bilden oder anderweitigen Bereitstellen des Donatorsubstrats 100 aus Fig. 1, können die primäre Halbleiterschicht 106 und zumindest ein Teil der epitaxialen Basisschicht 104 auf ein Empfängersubstrat 110 (Fig. 2) übertragen werden, unter Verwendung von beispielsweise dem Verfahren. das im Stand der Technik als SMARTCUT®-Verfahren bezeichnet wird. Das SMARTCUT®-Verfahren ist beispielsweise in der US-Patentschrift Nr. RE 39,484 von Bruel (eingereicht am 6. Februar 2007), der US-Patentschrift Nr. 6,303,468 von Aspar u. a. (eingereicht am 16. Oktober 2001), der US-Patentschrift Nr. 6,335,258 von Aspar u. a. (eingereicht am 1. Januar 2002), der US-Patentschrift Nr. 6,756,286 von Moriceau u. a. (eingereicht am 29. Juni 2004), der US-Patentschrift Nr. 6,809,044 von Aspar u. a. (eingereicht am 26. Oktober 2004) und der US-Patentschrift Nr. 6,946,365 von Aspar u. a. (20. September 2005) beschrieben, deren Inhalte hierin vollumfänglich durch Bezugnahme eingeschlossen sind.

[0039] Eine Vielzahl von Ionen (z. B. Wasserstoff-, Helium- oder Inertgasionen) können in das Donatorsubstrat 100 implantiert werden. Die Ionen können beispielsweise aus einer Ionenquelle in das Donatorsubstrat 100 implantiert werden, die sich auf einer Seite des Donatorsubstrats 100 befindet, wie durch die Richtungspfeile 109 in Fig. 1 dargestellt. Die lonen können in das Donatorsubstrat 100 entlang einer Richtung implantiert werden, die im Wesentlichen lotrecht zu der Hauptoberfläche des Donatorsubstrats 100 verläuft. Wie im Stand der Technik bekannt, ist die Tiefe, mit der die Ionen in das Donatorsubstrat 100 implantiert werden, zumindest zum Teil eine Funktion der Energie, mit der die Ionen in das Donatorsubstrat 100 implantiert werden. Im Allgemeinen werden die mit weniger Energie implantierten lonen in eine relativ geringe Tiefe implantiert, wogegen Ionen, die mit höherer Energie implantiert werden, relativ in eine tiefere Tiefe implantiert werden.

[0040] Die Ionen können in das Donatorsubstrat 100 mit einer vorgegebenen Energie implantiert werden, die so gewählt wird, dass die Ionen in eine erwünschte Tiefe in das Donatorsubstrat 100 implantiert werden. In einem bestimmten nicht einschränkenden Beispiel können die Ionen in das Donatorsubstrat 100 auf einer ausgewählten Tiefe angeordnet werden, so dass eine geschwächte Zone in dem Donatorsubstrat 100 entsteht. Wie im Stand der Technik bekannt, werden unvermeidlich zumindest einige lonen auf anderen Tiefen als der erwünschten Implantationstiefe implantiert, und ein Graph der Ionenkonzentration als Funktion der Tiefe in dem Donatorsubstrat 100 von einer Oberfläche des Donatorsubstrats 100 kann im Allgemeinen eine Glockenkurve (symmetrisch oder asymmetrisch) mit einem Maximum auf einer erwünschten Implantationstiefe aufweisen.

[0041] Bei der Implantation in das Donatorsubstrat 100 können die Ionen eine geschwächte Zone 112 (mit der gestrichelten Linie in Fig. 1 dargestellt) in dem Donatorsubstrat 100 definieren. Die geschwächte Zone 112 kann eine Schicht oder Region in dem Donatorsubstrat 100 umfassen, die mit der Ebene der maximalen Ionenkonzentration in dem Donatorsubstrat 100 fluchtet (z. B. darüber zentriert ist). Die geschwächte Zone 100 kann eine Ebene in dem Donatorsubstrat 100 definieren, entlang der das Donatorsubstrat 100 in einem nachfolgenden Prozess abgetrennt oder gebrochen werden kann. Wie in Fig. 1 dargestellt, kann die geschwächte Zone 100 in einer im Wesentlichen homogenen Region des Donatorsubstrats angeordnet sein, welche die epitaxiale Basisschicht 104 umfasst.

[0042] Nach dem Bilden der geschwächten Zone 112 in dem Donatorsubstrat 100, kann das Donatorsubstrat 100 an das Empfängersubstrat 110 gebondet werden, wie in Fig. 2 dargestellt, unter Verwendung eines direkten molekularen Bonding-Verfahrens.

[0043] In dem direkten molekularen Bonding-Verfahren können direkte Atombindungen zwischen dem Donatorsubstrat 100 und dem Empfängersubstrat 110 gebildet werden. Die Art der Atombindungen zwischen dem Donatorsubstrat 100 und dem Empfängersubstrat 110 hängen von der Materialzusammensetzung an den jeweiligen Oberflächen des Donatorsubstrats 100 und des Empfängersubstrats 110 ab.

[0044] In einigen Ausführungsbeispielen kann die direkte Verbindung zwischen der Bonding-Fläche des Donatorsubstrats 110 und der Bonding-Fläche des Empfängersubstrats 110 durch Ausbilden der Bonding-Fläche des Donatorsubstrats 100 und der Bonding-Fläche des Empfängersubstrats 110 mit jeweils einer relativ glatten Oberfläche gebildet werden, und durch nachfolgendes Anordnen der Bonding-Flächen aneinander und Initiieren der Ausbreitung einer Bon-

ding-Welle dazwischen. So können die Bonding-Fläche des Donatorsubstrats 100 und die Bonding-Fläche des Empfängersubstrats 110 beispielsweise jeweils mit einer Oberflächenrauheit (RMS) mit einem quadratischen Mittelwert von etwa zwei Nanometern (2,0 nm) oder weniger, etwa einem Nanometer (1,0 nm) oder weniger oder sogar nur einem Viertel von einem Nanometer (0,25 nm) oder weniger ausgebildet werden. Die Bonding-Fläche des Donatorsubstrats 100 und die Bonding-Fläche des Empfängersubstrats 110 können jeweils unter Verwendung von mindestens einem aus einem mechanischen Polierverfahren und einem chemischen Ätzverfahren geglättet werden. So kann beispielsweise ein chemisch-mechanisches Polierverfahren (CMP) eingesetzt werden, um die Oberflächenrauheit der Bonding-Fläche des Donatorsubstrats 100 und der Bonding-Fläche des Empfängersubstrats 110 zu planarisieren und/oder zu reduzieren.

**[0045]** Nach dem Glätten der Bonding-Flächen, können die Bonding-Flächen unter Verwendung von im Stand der Technik bekannten Verfahren optional gereinigt und/oder aktiviert werden. Ein solcher Aktivierungsprozess kann verwendet werden, um die Oberflächenchemie der Bonding-Flächen auf eine Weise zu verändern, die den Bonding-Prozess erleichtert und/oder zur Bildung einer stärkeren Verbindung führt.

**[0046]** Die Bonding-Flächen können in direkten physischen Kontakt miteinander gebracht werden und in einem umgrenzten Bereich auf der Bonding-Grenzfläche kann Druck angewendet werden. Interatomare Bindungen können in der Nähe des umgrenzten Druckbereichs initiiert werden, und eine Bonding-Welle kann sich über die Grenzfläche zwischen den Bonding-Flächen ausbreiten.

[0047] Optional kann zur Verstärkung der Bindung ein Annealing-Verfahren eingesetzt werden. Ein solches Annealing-Verfahren kann das Erhitzen des gebondeten Donatorsubstrats 100 und Empfängersubstrats 110 in einem Ofen auf eine Temperatur von zwischen einhundert Grad Celsius (100°C) und etwa vierhundert Grad Celsius (400°C) für eine Zeit von zwischen zwei Minuten (2 Min.) und etwa fünfzehn Stunden (15 Std.) umfassen.

[0048] Eine Isolierschicht 114 (wie beispielsweise ein Oxid (z. B. SiO<sub>2</sub>, Al<sub>2</sub>O<sub>3</sub>, usw.), ein Nitrid oder ein Oxinitrid) kann auf einem oder beidem aus dem Donatorsubstrat 100 und dem Empfängersubstrat 110 vor dem Bonding-Verfahren angeordnet werden, so dass die Bonding-Fläche von einem oder beidem aus dem Donatorsubstrat 100 und dem Empfängersubstrat 110 eine Fläche mit der Isolierschicht 110 umfasst. So kann das direkte molekulare Bonding-Verfahren in solchen Ausführungsbeispielen ein direktes

molekulares Oxid-zu-Oxid oder Oxid-zu-Silizium oder Oxid-zu-SiGe-Bonding-Verfahren umfassen.

[0049] Die Isolierschicht 114 kann eine Schicht umfassen, die oft als "eingebettete Oxidschicht" oder "BOX" bezeichnet wird. Die Isolierschicht 114 kann kristallin oder amorph sein. Diese Isolierschicht 114 kann eine durchschnittliche Schichtdicke in der gebondeten Struktur (welche die Dicke der beiden Isolierschichten 114 umfassen kann, wenn diese vor dem Bonden auf das Donatorsubstrat 100 und das Empfängersubstrat 110 aufgebracht wurden) von beispielsweise zwischen etwa 10 nm und etwa 50 nm aufweisen, obwohl auch dickere oder dünnere Isolierschichten 114 in Ausführungsbeispielen der vorliegenden Offenlegungsschrift verwendet werden können.

[0050] Wie in Fig. 3 dargestellt, kann das Donatorsubstrat 100 nach dem Bonden des Donatorsubstrats 100 an das Empfängersubstrat 110 entlang der geschwächten Zone 112 (Fig. 1 und Fig. 2) abgetrennt werden. Das Donatorsubstrat 100 kann entlang der geschwächten Zone 112 durch Erhitzen des Donatorsubstrats 100 und/oder durch Anlegen einer mechanischen Kraft an das Donatorsubstrat 100 abgetrennt oder abgebrochen werden.

[0051] Beim Brechen des Donatorsubstrats 100 entsteht, wie in Fig. 3 dargestellt, ein Mehrschichtsubstrat 120, welches das Empfängersubstrat 110 beinhaltet, das ein Basissubstrat des Mehrschichtsubstrats 120 definiert, die Isolierschicht 114, die eine eingebettete Oxidschicht des Mehrschichtsubstrats 120 definiert, die primäre Halbleiterschicht 106 über der eingebetteten Oxidschicht 114 auf einer Seite gegenüber dem Basissubstrat 110, und mindestens einen Abschnitt der epitaxialen Basisschicht 104 über der primären Halbleiterschicht 106 auf einer Seite gegenüber der eingebetteten Oxidschicht 114.

**[0052]** Das Mehrschichtsubstrat **120** ist in **Fig.** 3 in umgekehrter Ausrichtung zu der Darstellung in **Fig.** 3 zur nachfolgenden Verarbeitung dargestellt.

[0053] Die Dicke der epitaxialen Basisschicht 104 des Mehrschichtsubstrats 120 kann selektiv durch Steuern der Position (das heißt Tiefe) der geschwächten Zone 112 in dem Donatorsubstrat 100 (Fig. 1) gesteuert werden, und/oder durch selektives Ausdünnen des Abschnitts der epitaxialen Basisschicht 104 des Mehrschichtsubstrats 120 nach dem Brechen des Donatorsubstrats 100 entlang der geschwächten Zone 112, wie zuvor unter Bezug auf Fig. 3 beschrieben. So kann die Dicke der epitaxialen Basisschicht 104 in einigen Ausführungsbeispielen beispielsweise selektiv unter Verwendung von beispielsweise mindestens einem aus einem mechanischen Polierverfahren und einem chemischen Ätzverfahren nach dem Brechen des Donatorsubstrats

100 entlang der geschwächten Zone 112 reduziert werden. So kann beispielsweise ein chemisch-mechanisches Polierverfahren (CMP) verwendet werden, um die Dicke der epitaxialen Basisschicht 104 auf eine vorgegebene und ausgewählte Dicke nach dem Brechen des Donatorsubstrats 100 entlang der geschwächten Zone 112 zu reduzieren. Eine solche Verarbeitung kann auch zu einer Reduktion der Oberflächenrauheit der freiliegenden Hauptfläche der epitaxialen Basisschicht 104 und einer gleichförmigeren Dicke der epitaxialen Basisschicht 104 führen, was ebenfalls wünschenswert sein kann.

[0054] Wie in Fig. 5 dargestellt, kann eine Maskenschicht 122 über der epitaxialen Basisschicht 104 und der primären Halbleiterschicht 106 in einer ersten Region 124A des Mehrschichtsubstrats 120 aufgebracht oder anderweitig bereitgestellt werden. Dabei bedeckt die Maskenschicht 122 die epitaxiale Basisschicht 104 und die primäre Halbleiterschicht 106 nicht in einer zweiten Region 124B des Mehrschichtsubstrats 120. Die erste Maskenschicht 122 kann zumindest im Wesentlichen durchgehend über dem Mehrschichtsubstrat 120 aufgebracht und dann anschließend strukturiert werden, um die Maskenschicht 122 in der zweiten Region 124B des Mehrschichtsubstrats 120 zu entfernen, so dass die epitaxiale Basisschicht 104 und die primäre Halbleiterschicht 106 durch die erste Maskenschicht 122 in der zweiten Region 124B des Mehrschichtsubstrats 120 freiliegen.

[0055] Die erste Maskenschicht 122 kann eine einzelne Schicht aus Maskenmaterial oder eine Vielzahl von Schichten aus Maskenmaterial umfassen. Die Zusammensetzung der ersten Maskenschicht 122 kann so gewählt werden, dass sie gegen das Ätzen durch Ätzmittel resistent ist, das nachfolgend verwendet wird, um die Maskenschicht 122 in der zweiten Region 124B des Mehrschichtsubstrats 120 zu ätzen und zu entfernen, wie unten erläutert wird. Die erste Maskenschicht 122 kann beispielsweise ein Oxid (z. B.  $SiO_2$ ,  $Al_2O_3$ , usw.), ein Nitrid (z. B.  $Si_3N_4$ ) oder ein Oxinitrid (z. B. Silizium-Oxinitrid) umfassen. Als nicht einschränkendes Beispiel kann die erste Maskenschicht 122 in Ausführungsbeispielen, in welchen die epitaxiale Basisschicht Si<sub>x</sub>Ge<sub>1-x</sub> umfasst und die primäre Halbleiterschicht 106 zugverspanntes Silizium (sSi) umfasst, eine Mehrschicht-Maskenstruktur mit einer ersten Oxidschicht (z. B. SiO<sub>2</sub>) umfassen, einer Nitridschicht (z. B. Si<sub>3</sub>N<sub>4</sub>) auf einer Seite der ersten Oxidschicht gegenüber der epitaxialen Basisschicht **104**, und einer zweiten Oxidschicht (z. B. SiO<sub>2</sub>) auf einer Seite der Nitridschicht gegenüber der ersten Oxidschicht, so dass sich die Nitridschicht zwischen der ersten und zweiten Oxidschicht befindet.

[0056] Wie in Fig. 6 dargestellt, kann nach dem Maskieren der epitaxialen Basisschicht 104 und der primären Halbleiterschicht 106 in der ersten Regi-

on 124A des Mehrschichtsubstrats 120 mit der ersten Maskenschicht 122 der freiliegende Abschnitt der epitaxialen Basisschicht 104 aus der zweiten Region 124B des Mehrschichtsubstrats 120 entfernt werden. Zum Entfernen der epitaxialen Basisschicht 104 über der primären Halbleiterschicht 106 in der zweiten Region 124B kann ein Ätzverfahren eingesetzt werden.

[0057] Als Ätzverfahren zum Entfernen der epitaxialen Basisschicht 104 von der primären Halbleiterschicht 106 in der zweiten Region 124B kann ein Nassätzverfahren oder ein Trockenätzverfahren eingesetzt werden (z. B. reaktives Ionenätzen (RIE)). Das Ätzverfahren kann ein isotropes oder anisotropes Ätzverfahren umfassen. Das Ätzmittel zum Ätzen der epitaxialen Basisschicht 104 kann selektiv relativ zu der primären Halbleiterschicht 106 gewählt werden, so dass die epitaxiale Basisschicht 104 vorzugsweise durch das Ätzverfahren entfernt wird und die primäre Halbleiterschicht 106 als eine Ätzstoppschicht dient. In anderen Ausführungsbeispielen kann das Ätzverfahren einfach beendet werden. sobald die epitaxiale Basisschicht 104 entfernt wurde, wenn kein Ätzmittel zur Verfügung steht, das nur selektiv die epitaxiale Basisschicht 104 entfernt, ohne im Wesentlichen die primäre Halbleiterschicht 106 zu entfernen.

[0058] Als nicht einschränkendes Beispiel kann in Ausführungsbeispielen, in welchen die epitaxiale Basisschicht 104 Si<sub>x</sub>Ge<sub>1-x</sub> umfasst und die primäre Halbleiterschicht 106 zugverspanntes Silizium (sSi) umfasst, ein trockenes reaktives Ionenätzverfahren (RIE) verwendet werden, um die epitaxiale Basisschicht 104 zu entfernen. Als Ätzmittel in einem solchen Trocken-RIE-Verfahren können halogenbasierte Chemikalien verwendet werden, darunter Chlor (z. B. Cl<sub>2</sub>), Fluor (z. B. CF<sub>4</sub> oder SF<sub>6</sub>) und/oder Brom (HBr). Die Ätzrate des RIE-Ätzverfahrens kann durch Anpassen von Vakuumfaktor, Druck und Vorspannung in der RIE-Ätzkammer selektiv gesteuert werden. Siehe dazu beispielsweise Marcelo S. B. Castro u. a., "Selective and Anisotropic Dry Etching of Ge over Si", Journal of Integrated Circuits and Systems 2013, Bd. 8, Nr. 2, S. 104-109, das ein solches RIE-Atzverfahren offenbart und hierin vollumfänglich durch Bezugnahme eingeschlossen ist.

[0059] Nach dem Entfernen der epitaxialen Basisschicht 104 von der darunterliegenden primären Halbleiterschicht 106 in der zweiten Region 124B des Mehrschichtsubstrats 120 kann anschließend die Maskenschicht 134 von dem Mehrschichtsubstrat 120 entfernt werden.

[0060] Wie in Fig. 7 dargestellt, kann eine zweite Maskenschicht 126 über der freiliegenden primären Halbleiterschicht 106 in einer zweiten Region 124B des Mehrschichtsubstrats 120 aufgebracht oder anderweitig bereitgestellt werden. Dabei bedeckt die

zweite Maskenschicht 126 die epitaxiale Basisschicht 104 und die primäre Halbleiterschicht 106 nicht in der ersten Region 124B des Mehrschichtsubstrats 120. Die zweite Maskenschicht 124 kann zumindest im Wesentlichen durchgehend über dem Mehrschichtsubstrat 120 aufgebracht und dann anschließend strukturiert werden, um die Maskenschicht 122 in der ersten Region 124B des Mehrschichtsubstrats 120 zu entfernen, so dass die epitaxiale Basisschicht 104 und die primäre Halbleiterschicht 106 durch die erste Maskenschicht 122 in der ersten Region 124B des Mehrschichtsubstrats 120 freiliegen.

[0061] Die zweite Maskenschicht 126 kann eine einzelne Schicht aus Maskenmaterial oder eine Vielzahl von Schichten aus Maskenmaterial umfassen. Die Zusammensetzung der zweiten Maskenschicht 126 kann so gewählt werden, dass sie gegenüber Umgebungsbedingungen resistent ist, welchen sie während des Atomdiffusionsverfahrens ausgesetzt werden kann, das nachfolgend an der epitaxialen Basisschicht 104 und der primären Halbleiterschicht 106 in der ersten Region 194A des Mehrschichtsubstrats 120 durchgeführt wird, wie nachfolgend unter Bezug auf Fig. 8A-Fig. 8C beschrieben. Die zweite Maskenschicht 126 kann beispielsweise ein Oxid (z. B. SiO<sub>2</sub>, Al<sub>2</sub>O<sub>3</sub> usw.), ein Nitrid (z. B. Si<sub>3</sub>N<sub>4</sub>) oder ein Oxinitrid (z. B. Silizium-Oxinitrid) umfassen. Als nicht einschränkendes Beispiel kann die zweite Maskenschicht 126 in den Ausführungsbeispielen, in welchen die epitaxiale Basisschicht 104 Si<sub>x</sub>Ge<sub>1-x</sub> umfasst und die primäre Halbleiterschicht 106 zugverspanntes Silizium (sSi) umfasst, eine Mehrschicht-Maskenstruktur mit einer Oxidschicht (z. B. SiO<sub>2</sub>) und einer Nitridschicht (z. B. Si<sub>3</sub>N<sub>4</sub>) auf einer Seite der Oxidschicht gegenüber der epitaxialen Basisschicht 104 umfassen.

[0062] Nach dem Maskieren der primären Halbleiterschicht 106 in der zweiten Region 124B des Mehrschichtsubstrats 120 mit der zweiten Maskenschicht 126 kann ein Kondensationsverfahren (oft als "thermisches Mischen" bezeichnet) oder eine andere Art von Prozess eingesetzt werden, um Elemente aus der epitaxialen Basisschicht 104 in der ersten Region in die darunterliegende primäre Halbleiterschicht 106 zu diffundieren und so selektiv die Zugspannung in der primären Halbleiterschicht 106 in der ersten Region 124A relativ zu dem Spannungsniveau in der primären Halbleiterschicht 106 in der zweiten Region 124B des Mehrschichtsubstrats 120 zu reduzieren und/oder die Druckspannung zu erhöhen. Die Anwesenheit der zweiten Maskenschicht 126 und die Abwesenheit der epitaxialen Basisschicht 104 in der zweiten Region 124B können die Diffusion von Elementen in die primäre Halbleiterschicht 106 in der zweiten Region 124B verhindern, so dass die Spannung in der Halbleiterschicht 106 während des Kondensationsverfahrens erhalten bleibt, das in der ersten Region 124A des Mehrschichtsubstrats 120

durchgeführt wird. Mit anderen Worten wird das Kondensationsverfahren nur in der ersten Region **124A** des Mehrschichtsubstrats **120** und nicht in der zweiten Region **124B** des Mehrschichtsubstrats **120** ausgeführt. Ein solches Kondensationsverfahren wird unten unter Bezug auf **Fig.** 8A–**Fig.** 8C beschrieben.

[0063] Fig. 8A ist eine vergrößerte Darstellung eines Abschnitts des Mehrschichtsubstrats 120 aus Fig. 6 in der ersten Region 124A. Das Kondensationsverfahren kann das Anwenden eines Oxidationsprozesses auf das Mehrschichtsubstrat 120, bei dem die primäre Halbleiterschicht 106 in der zweiten Region 124B maskiert ist, in einem Ofen bei erhöhten Temperaturen (z. B. zwischen etwa 900°C und etwa 1150°C) in einer Oxidationsatmosphäre (z. B. trockener O<sub>2</sub>) beinhalten. Wie in Fig. 8B dargestellt, kann das Oxidationsverfahren zur Bildung einer Oxidschicht 136 auf der Oberfläche des Mehrschichtsubstrats 120 führen und die Diffusion von Elementen aus der epitaxialen Basisschicht 104 in die primäre Halbleiterschicht 106 in der ersten Region 124A des Mehrschichtsubstrats 120 bewirken. Mit der Zeit wird die Grenze bzw. Grenzfläche zwischen der epitaxialen Basisschicht 104 und der primären Halbleiterschicht 106 zusammenhängend, da die Elemente der epitaxialen Basisschicht 104 in die wachsende Oxidschicht 136 integriert werden oder in die darunterliegende primäre Halbleiterschicht 106 diffundieren und darin integriert werden.

[0064] In Ausführungsbeispielen, in welchen die primäre Halbleiterschicht 106 zugverspanntes Silizium (sSi) umfasst und die epitaxiale Basisschicht 104 Six-Ge<sub>1-x</sub> umfasst, kann die Oxidschicht 136 Siliziumdioxid (SiO<sub>2</sub>) umfassen und das Germanium der epitaxialen Si<sub>x</sub>Ge<sub>1-x</sub>-Basisschicht 104 kann in das verspannte Silizium (sSi) der primären Halbleiterschicht 106 diffundieren, wodurch sich die verspannte sSi-Halbleiterschicht 106 zu einer verspannten primären Si<sub>v</sub>Ge<sub>1-v</sub>-Halbleiterschicht 106 ändert. Die Oxidschicht 136 kann sich an der Oberfläche der epitaxialen Basisschicht 104 bilden und durch das Auflösen der epitaxialen Basisschicht 104 in der Dickenrichtung in das Mehrschichtsubstrat 120 und in die primäre Halbleiterschicht 106 wachsen. Während die Dicke der Oxidschicht 136 während des Germanium-Kondensationsverfahrens zunimmt, nimmt die Dicke der Halbleiterschicht 106 ab und die Konzentration des Germaniums in der primären Halbleiterschicht 106 nimmt zu, bis eine primäre Halbleiterschicht 106 mit einer erwünschten Konzentration an Germanium in der verspannten primären Si<sub>v</sub>Ge<sub>1-v</sub>-Halbleiterschicht 106 erzielt wird, wie in Fig. 8C dargestellt. Die Diffusion von Germanium in die primäre Halbleiterschicht 106 kann zu einer Abnahme der Zugspannung in der primären Halbleiterschicht 106 und zur Entstehung von Druckspannung in der primären Halbleiterschicht 106 führen. Nach dem Kondensationsverfahren kann die primäre Halbleiterschicht 106 in der ersten Region 124A eine geringere Zugspannung als die Zugspannung in der primären Halbleiterschicht 106 in der zweiten Region 124B aufweisen, die primäre Halbleiterschicht 106 kann sich in der ersten Region 124A in einem zumindest im Wesentlichen entspannten Zustand frei von Zugspannung oder Druckspannung befinden, oder die primäre Halbleiterschicht 106 in der ersten Region 124A kann sich in einem Zustand der Druckspannung befinden.

[0065] Die Oxidschicht 136 kann optional über der primären Halbleiterschicht 106 in der ersten Region 124A des Mehrschichtsubstrats 120 nach dem Durchführen des Kondensationsverfahrens entfernt werden. Die Oxidschicht 136 kann beispielsweise unter Verwendung eines Nass- oder Trockenätzverfahrens entfernt werden.

[0066] Das Kondensationsverfahren kann zu einer Abnahme der Dicke der primären Halbleiterschicht 106 in der ersten Region 124A des Mehrschichtsubstrats 120 führen, wie aus dem Vergleich von Fig. 8A und Fig. 8C hervorgeht. In einigen Ausführungsbeispielen kann nach dem Durchführen des Kondensationsverfahrens und dem Entfernen der Oxidschicht 136 zusätzlich ein Halbleitermaterial selektiv epitaxial auf der primären Halbleiterschicht 106 in der ersten Region 124A des Mehrschichtsubstrats 120 ohne zusätzliches epitaxiales Wachstum von Halbleitermaterial auf der primären Halbleiterschicht 106 in der zweiten Region 124B des Mehrschichtsubstrats 120 gezüchtet werden. Das zusätzliche Halbleitermaterial kann dieselbe Zusammensetzung und denselben Spannungszustand wie das darunterliegende Halbleitermaterial der primären Halbleiterschicht 106 in der ersten Region 124A des Mehrschichtsubstrats 120 aufweisen. Das selektive epitaxiale Wachstum von zusätzlichem Halbleitermaterial kann zum Verdicken der primären Halbleiterschicht 106 in der ersten Region 124A des Mehrschichtsubstrats 120 verwendet werden, so dass eine Dicke der primären Halbleiterschicht 106 in der ersten Region 124A zumindest im Wesentlichen gleich einer Dicke der primären Halbleiterschicht 106 in der zweiten Region 124B ist, die dem Kondensationsverfahren nicht unterzogen wurde.

[0067] Das Kondensationsverfahren kann zu einer verbesserten Löcherbeweglichkeit in der primären Halbleiterschicht 106 in der ersten Region 124A das Mehrschichtsubstrats 120 führen, was zum Bilden von PMOS-Transistoren wünschenswert sein kann, wie beispielsweise von planaren FET-Transistoren oder FinFET-Transistoren mit Transistorkanalstrukturen, die Regionen der primären Halbleiterschicht 106 in der ersten Region 124A des Mehrschichtsubstrats 120 umfassen. Die primäre Halbleiterschicht 106 in der zweiten Region 124B des Mehrschichtsubstrats 120 kann in einem Zustand der Zugspannung bleiben, was zum Bilden von NMOS-Transis-

toren wünschenswert sein kann, wie beispielsweise von planaren FET-Transistoren oder FinFET-Transistoren mit Transistorkanalstrukturen, die Regionen der primären Halbleiterschicht 106 in der zweiten Region 124A des Mehrschichtsubstrats 120 umfassen.

[0068] So kann, bezogen auf Fig. 9, nach dem Bereitstellen des Mehrschichtsubstrats 120 das Mehrschichtsubstrat 120 so geätzt werden, dass Finnenstrukturen 132 definiert werden, die jeweils einen Abschnitt der primären Halbleiterschicht 106 umfassen. Die Finnenstrukturen 132 können jeweils zur Verwendung in einem FinFET bemessen und konfiguriert werden.

[0069] Das Ätzverfahren kann beispielsweise durch Aufbringen einer Maskenschicht auf das Mehrschichtsubstrat 120 ausgeführt werden, Strukturieren der Maskenschicht, so dass darin Öffnungen an Positionen entstehen, an welchen in und durch die epitaxiale Basisschicht 104 und die primäre Halbleiterschicht 106 geätzt werden soll, und durch anschließendes Ätzen der primären Halbleiterschicht 106 durch die strukturierte Maskenschicht. Es können auch andere im Stand der Technik bekannte Verfahren zum Bilden der Finnenstrukturen 132 eingesetzt werden, wie beispielsweise die Doppelstrukturierung mithilfe von Abstandhaltern (Spacer-Defined Double Patterning, SDDP), die im Stand der Technik auch als Seitenwand-Bildtransferverfahren bezeichnet werden.

[0070] Das Ätzverfahren kann ein Nassätzverfahren oder ein Trockenätzverfahren umfassen (z. B. ein reaktives Ionenätzverfahren (RIE)). Das Ätzverfahren kann ein anisotropes Ätzverfahren umfassen, um Finnenstrukturen 132 mit im Allgemeinen vertikalen Seitenwänden zu erhalten. Das Ätzmittel kann so gewählt werden, dass die epitaxiale Basisschicht 104 und die primäre Halbleiterschicht 106 selektiv relativ zu der darunterliegenden BOX-Schicht 114 geätzt werden, so dass die BOX-Schicht 114 als eine Ätzstoppschicht dienen kann.

**[0071]** Als nicht einschränkendes Beispiel kann in Ausführungsbeispielen, in welchen die primäre Halbleiterschicht **106** ein zugverspanntes Silizium (sSi) in der zweiten Region **124B** und ein druckverspanntes Si<sub>y</sub>Ge<sub>1-y</sub> in der ersten Region **124A** umfasst, einen trockenes reaktives Ionenätzverfahren unter Verwendung von halogenbasierten Chemikalien, darunter Chlor- (z. B. Cl<sub>2</sub>), Fluor- (z. B. CF<sub>4</sub> oder SF<sub>6</sub>) und/oder Brom-Reaktionsgase (z. B. HBr) als Ätzmittel eingesetzt werden.

[0072] Die Finnenstrukturen 132 können eine erste Vielzahl von Finnen 132A aufweisen, die als Finnen von p-Typ-FinFET-Transistoren vorgesehen sind, und eine zweite Vielzahl von Finnen 132B, die als Finnen von n-Typ-FinFET-Transistoren vorgese-

hen sind. Jede der ersten Vielzahl von Finnen 132A kann einen Abschnitt der primären Halbleiterschicht 106 in der ersten Region 124A des Mehrschichtsubstrats 120 umfassen, und jede der zweiten Vielzahl von Finnen 132B kann einen Abschnitt der primären Halbleiterschicht 106 in der zweiten Region 124B des Mehrschichtsubstrats 120 umfassen. Somit kann sich die erste Vielzahl von Finnenstrukturen 132A in einem anderen Spannungszustand relativ zu der zweiten Vielzahl von Finnenstrukturen 132B befinden. Insbesondere kann sich die zweite Vielzahl von Finnenstrukturen 133B in einem Zustand der Zugspannung befinden, und die erste Vielzahl von Finnenstrukturen 133A kann sich in einem Zustand von reduzierter Zugspannung (relativ zu der zweiten Vielzahl von Finnenstrukturen 132B) befinden, in einem entspannten Zustand, der zumindest im Wesentlichen frei von Zug- oder Druckspannung ist, oder in einem Zustand der Druckspannung.

[0073] In einigen Ausführungsbeispielen können die Finnenstrukturen 132 ein oder mehrere Maße (z. B. Länge, Breite oder Höhe) aufweisen, die unterhalb eines kritischen Maßes liegt, auf dem sich das Material der Finnenstrukturen 132 entweder spontan oder während der nachfolgenden Verarbeitung bei erhöhten Temperaturen entspannt. In einigen Ausführungsbeispielen können die Finnenstrukturen 132 mit einer durchschnittlichen Finnenbreite W (siehe Fig. 10) von etwa 30 nm oder weniger, etwa 20 nm oder weniger oder sogar 15 nm oder weniger ausgebildet sein.

[0074] Bei den oben beschriebenen Verfahren kann die epitaxiale Basisschicht 104 als eine Basisschicht verwendet werden, auf der zunächst die primäre Halbleiterschicht 106 epitaxial gezüchtet wird, so dass sich die primäre Halbleiterschicht 106 in einem verspannten Zustand befindet, wie unter Bezug auf Fig. 1 beschrieben, und kann dann anschließend verwendet werden, um einen Spannungszustand eines Abschnitts der primären Halbleiterschicht 106 in dem Kondensationsverfahren zu ändern, wie unter Bezug auf Fig. 8A–Fig. 8C beschrieben.

[0075] Wie oben stehend beschrieben, können die erste Vielzahl von Finnenstrukturen 132A und die zweite Vielzahl von Finnenstrukturen 132B zusammen in einem gemeinsamen Maskierungs- und Ätzverfahren gebildet werden, wie unter Bezug auf Fig. 9 beschrieben.

[0076] Die Struktur, die mithilfe der hier beschriebenen Verfahren gebildet wird, beinhaltet eine erste Vielzahl von Finnenstrukturen 132A und eine zweite Vielzahl von Finnenstrukturen 132B, die über der eingebetteten Oxidschicht 114 in einer gemeinsamen Ebene auf einer Seite davon gegenüber dem Basissubstrat 110 angeordnet sind.

[0077] Jede der ersten Vielzahl von Finnenstrukturen 132 umfasst eine kondensierte primäre Halbleiterschicht 106 mit zwei oder mehr Elementen (z. B. Silizium und Germanium). Jede der zweiten Vielzahl von Finnenstrukturen 132B umfasst eine nicht kondensierte primäre Halbleiterschicht 106. Außerdem haben die Finnenstrukturen 132 der zweiten Vielzahl von Finnenstrukturen 132B eine kristallographische Spannung, die von einer kristallographischen Spannung der Finnenstrukturen 132 der ersten Vielzahl von Finnenstrukturen 132A abweicht. So können sich beispielsweise die Finnenstrukturen 132 der zweiten Vielzahl von Finnenstrukturen 132B in einem Zustand der Zugspannung befinden, und die Finnenstrukturen 132 der ersten Vielzahl von Finnenstrukturen 132A können sich in einem Zustand von reduzierter Zugspannung befinden, einem entspannten Spannungszustand (d. h. keine Spannung) oder einem Zustand der Druckspannung.

[0078] Nach dem Bilden der ersten Vielzahl von Finnenstrukturen 132A und der zweiten Vielzahl von Finnenstrukturen 132B, wie oben beschrieben, kann eine erste Vielzahl von PMOS FinFET-Transistoren gebildet werden, welche die erste Vielzahl von Finnenstrukturen 132A umfassen, sowie eine zweite Vielzahl von NMOS FinFET-Transistoren, welche die zweite Vielzahl von Finnenstrukturen 132B umfassen

[0079] Fig. 10 illustriert ein nicht einschränkendes, vereinfachtes Ausführungsbeispiel einer Fin-FET-Transistorkonfiguration, die unter Verwendung der ersten Vielzahl von Finnenstrukturen 132A und/oder der zweiten Vielzahl von Finnenstrukturen 132B gemäß Ausführungsbeispielen der der vorliegenden Offenlegungsschrift hergestellt wird. Es sei angemerkt, dass verschiedene unterschiedliche Konfigurationen von FinFETs im Stand der Technik bekannt sind und entsprechend den Ausführungsbeispielen der Offenlegungsschrift verwendet werden können, und die FinFET-Struktur aus Fig. 10 lediglich als ein Beispiel für solche FinFET-Strukturen dient.

[0080] Wie in Fig. 10 dargestellt, umfasst ein Fin-FET-Transistor 140 eine Source-Region 142, eine Drain-Region 144 und einen Kanal, der sich zwischen der Source-Region 142 und der Drain-Region 144 erstreckt. Der Kanal wird von einer Finne 132 definiert und umfasst diese, wie beispielsweise eine erste Finnenstruktur 132A oder eine zweite Finnenstruktur 132B. In einigen Ausführungsbeispielen können die Source-Region 142 und die Drain-Region 144 langgestreckte Endabschnitte einer Finnenstruktur 132 beinhalten oder dadurch definiert werden. Ein leitendes Gate 146 erstreckt sich über und neben zumindest einem Abschnitt der Finnenstruktur 132 zwischen der Source-Region 142 und der Drain-Region 144. Das Gate 146 kann durch ein dielektrisches Material 148 von der Finnenstruktur 132 getrennt sein. Das Gate 146 kann eine Mehrschichtstruktur aufweisen und Halbleiter und/oder leitende Schichten beinhalten. Eine Schicht mit geringem Widerstand, die ein Metall, eine Metallverbindung oder beides beinhaltet, wie beispielsweise ein leitendes Silizid, kann über der Source-Region 142 und/oder der Drain-Region 144 angeordnet werden, um damit elektrische Kontakte zu bilden.

[0081] Vorzugsweise kann Zugspannung in dem Kanal die Leistung von NMOS FinFET-Transistoren erhöhen und die Schwellenspannung senken, während eine reduzierte Zugspannung (z. B. geringere Zugspannung, keine Zug- oder Druckspannung, oder Druckspannung) in dem Kanal die Leistung von PMOS FinFET-Transistoren erhöhen und die Schwellenspannung senken kann. Für manche Funktionen sind verspannte Vorrichtungen von Vorteil, da eine hohe Leistung erforderlich ist, und für andere Funktionen ist die Leistung weniger bedeutend, wird jedoch eine hohe Schwellenspannung benötigt. Bei den Ausführungsbeispielen der vorliegenden Offenlegungsschrift kann der Hersteller selektiv unterschiedliche Spannungen in die Kristallgitter von verschiedenen FinFET-Transistoren in derselben Vorrichtung in einer gemeinsamen FinFET-Transistorebene integrieren.

[0082] Zwar wurden die hier offenbarten Verfahren und Strukturen unter Bezug auf FinFET-Strukturen beschrieben, doch sei angemerkt, dass weitere Ausführungsbeispiele der Offenlegungsschrift das Bilden von konventionellen FET-Strukturen anstatt der FinFET Strukturen beinhalten können, und eine Vielzahl von konventionellen p-Typ-CMOS-FET-Transistoren unter Verwendung der primären Halbleiterschicht 106 in der ersten Region 124A des Mehrschichtsubstrats 120 hergestellt werden können, und eine Vielzahl von herkömmlichen n-Typ-CMOS-FET-Transistoren unter Verwendung der primären Halbleiterschicht 106 in der zweiten Region 124B des Mehrschichtsubstrats 120 hergestellt werden können.

[0083] Außerdem sind nicht einschränkende Ausführungsbeispiele der Offenlegungsschrift nachfolgend dargelegt.

[0084] Ausführungsbeispiel 1: Verfahren zum Herstellen einer Halbleiterstruktur, umfassend: Bereitstellen eines Mehrschichtsubstrats, das beinhaltet: ein Basissubstrat, eine eingebettete Oxidschicht über einer Oberfläche des Basissubstrats, eine verspannte primäre Halbleiterschicht über der eingebetteten Oxidschicht auf einer Seite davon gegenüber dem Basissubstrat, und eine epitaxiale Basisschicht über der verspannten Halbleiterschicht auf einer Seite davon gegenüber der eingebetteten Oxidschicht, Diffundieren von Elementen aus der epitaxialen Basisschicht in die verspannte primäre Halbleiterschicht

in einer ersten Region des Mehrschichtsubstrats, ohne dabei Elemente aus der epitaxialen Basisschicht in die verspannte primäre Halbleiterschicht in einer zweiten Region des Mehrschichtsubstrats zu diffundieren, und Anreichern einer Konzentration der diffundierten Elemente in der primären Halbleiterschicht in der ersten Region, so dass ein Spannungszustand in der primären Halbleiterschicht in der ersten Region von einem Spannungszustand in der primären Halbleiterschicht in der zweiten Region abweicht; und Bilden einer ersten Vielzahl von Transistor-Kanalstrukturen, die ieweils einen Abschnitt der primären Halbleiterschicht in der ersten Region des Mehrschichtsubstrats umfassen und einer zweiten Vielzahl von Transistor-Kanalstrukturen, die jeweils einen Abschnitt der primären Halbleiterschicht in der zweiten Region des Mehrschichtsubstrats umfassen.

**[0085]** Ausführungsbeispiel 2: Verfahren nach Ausführungsbeispiel 1, des Weiteren umfassend das Auswählen der verspannten Halbleiterschicht, so dass sie verspanntes Silizium umfasst.

**[0086]** Ausführungsbeispiel 3: Verfahren nach Ausführungsbeispiel 2, des Weiteren umfassend das Auswählen der verspannten Halbleiterschicht, so dass sie zugverspanntes Silizium umfasst.

**[0087]** Ausführungsbeispiel 4: Verfahren nach einem der Ausführungsbeispiele 1 bis 3, des Weiteren umfassend das Auswählen der epitaxialen Basisschicht, so dass sie Si<sub>x</sub>Ge<sub>1-x</sub> umfasst, wobei x zwischen etwa 0,01 bis etwa 0,99 liegt, und wobei das Diffundieren der Elemente aus der epitaxialen Basisschicht in die verspannte primäre Halbleiterschicht das Diffundieren von Germanium in die verspannte primäre Halbleiterschicht in der ersten Region des Mehrschichtsubstrats umfasst.

[0088] Ausführungsbeispiel 5: Verfahren nach einem der Ausführungsbeispiele 1 bis 4, wobei das Bilden einer ersten Vielzahl von Transistor-Kanalstrukturen und das Bilden der zweiten Vielzahl von Transistor-Kanalstrukturen das Ätzen durch die primäre Halbleiterschicht und das Definieren von Finnenstrukturen umfasst, wobei jede der Finnenstrukturen einen Abschnitt der primären Halbleiterschicht umfasst und jede der Finnenstrukturen zur Verwendung in einem FinFET bemessen und konfiguriert ist.

[0089] Ausführungsbeispiel 6: Verfahren nach einem der Ausführungsbeispiele 1 bis 5, wobei das Bereitstellen des Mehrschichtsubstrats umfasst: epitaxiales Züchten der verspannten Halbleiterschicht auf der epitaxialen Basisschicht über einem Donatorsubstrat, um eine Donatorstruktur zu bilden; Implantieren von Ionen in die Donatorstruktur und Bilden einer geschwächten Zone in der Donatorstruktur; Bonden der Donatorstruktur an ein Empfängersubstrat, welches das Basissubstrat umfasst; und Abtrennen der Donatorstruktur an ein Empfängersubstrat der Donatorstruktur

torstruktur entlang der geschwächten Zone, um die verspannte Halbleiterschicht und die epitaxiale Basisschicht auf das Basissubstrat zu übertragen.

[0090] Ausführungsbeispiel 7: Verfahren nach Ausführungsbeispiel 6, wobei das Bonden der Donatorstruktur an das Empfängersubstrat das Bereitstellen einer Oxidschicht auf einem oder beidem aus der Donatorstruktur und dem Empfängersubstrat und das Bonden der Donatorstruktur an das Empfängersubstrat unter Verwendung eines direkten Bonding-Verfahrens umfasst.

**[0091]** Ausführungsbeispiel 8: Verfahren nach Ausführungsbeispiel 6 oder Ausführungsbeispiel 7, des Weiteren umfassend das Anordnen der geschwächten Zone in einer im Wesentlichen homogenen Region des Donatorsubstrats, welche die epitaxiale Basisschicht umfasst.

[0092] Ausführungsbeispiel 9: Verfahren nach einem der Ausführungsbeispiele 1 bis 8, wobei das Diffundieren der Elemente aus der epitaxialen Basisschicht in die verspannte primäre Halbleiterschicht in der ersten Region des Mehrschichtsubstrats das Entspannen der Spannung in der primären Halbleiterschicht in der ersten Region des Mehrschichtsubstrats umfasst.

[0093] Ausführungsbeispiel 10: Verfahren nach einem der Ausführungsbeispiele 1 bis 9, wobei das Diffundieren der Elemente aus der epitaxialen Basisschicht in die verspannte primäre Halbleiterschicht in der ersten Region des Mehrschichtsubstrats das Induzieren von Druckspannung in der primären Halbleiterschicht in der ersten Region des Mehrschichtsubstrats umfasst.

[0094] Ausführungsbeispiel 11: Verfahren nach einem der Ausführungsbeispiele 1 bis 10, wobei das Diffundieren der Elemente aus der epitaxialen Basisschicht in die verspannte primäre Halbleiterschicht in der ersten Region des Mehrschichtsubstrats das Erhöhen einer Löcherbeweglichkeit in der primären Halbleiterschicht in der ersten Region umfasst.

[0095] Ausführungsbeispiel 12: Verfahren nach einem der Ausführungsbeispiele 1 bis 11, wobei das Diffundieren der Elemente aus der epitaxialen Basisschicht in die verspannte primäre Halbleiterschicht in der ersten Region des Mehrschichtsubstrats das Ausführen eines Kondensationsverfahrens an der primären Halbleiterschicht in der ersten Region des Mehrschichtsubstrats umfasst.

[0096] Ausführungsbeispiel 13: Verfahren nach Ausführungsbeispiel 12, wobei Ausführen eines Kondensationsverfahrens an der primären Halbleiterschicht in der ersten Region des Mehrschichtsubstrats das Oxidieren eines Abschnitts der primären Halbleiter-

schicht in der ersten Region des Mehrschichtsubstrats umfasst.

**[0097]** Ausführungsbeispiel 14: Verfahren nach einem der Ausführungsbeispiele 1 bis 13, des Weiteren umfassend das Bilden einer Vielzahl von p-Typ-FET-Transistoren, welche die erste Vielzahl von Transistor-Kanalstrukturen umfassen, und Bilden einer Vielzahl von n-Typ-FET-Transistoren, welche die zweite Vielzahl von Transistor-Kanalstrukturen umfassen.

[0098] Ausführungsbeispiel 15: Verfahren zum Herstellen einer Halbleiterstruktur, umfassend: Bereitstellen eines Mehrschichtsubstrats, das beinhaltet: ein Basissubstrat, eine eingebettete Oxidschicht über einer Oberfläche des Basissubstrats, eine verspannte primäre Halbleiterschicht über der eingebetteten Oxidschicht auf einer Seite davon gegenüber dem Basissubstrat, und eine epitaxiale Basisschicht über der verspannten Halbleiterschicht auf einer Seite davon gegenüber der eingebetteten Oxidschicht, Maskieren einer ersten Region des Mehrschichtsubstrats mit einer ersten Maskenschicht und Entfernen eines Abschnitts der epitaxialen Basisschicht von einer zweiten Region des Mehrschichtsubstrats; Entfernen der ersten Maskenschicht von der ersten Region des Mehrschichtsubstrats und Maskieren der zweiten Region des Mehrschichtsubstrats mit einer zweiten Maskenschicht; Diffundieren von Elementen aus der epitaxialen Basisschicht in die verspannte primäre Halbleiterschicht in der ersten Region des Mehrschichtsubstrats und Ändern eines Spannungszustands der primären Halbleiterschicht in der ersten Region des Mehrschichtsubstrats, ohne dabei Elemente in die verspannte primäre Halbleiterschicht in einer zweiten Region des Mehrschichtsubstrats zu diffundieren; und Bilden einer ersten Vielzahl von Transistor-Kanalstrukturen, die jeweils einen Abschnitt der primären Halbleiterschicht in der ersten Region des Mehrschichtsubstrats umfassen und einer zweiten Vielzahl von Transistor-Kanalstrukturen, die jeweils einen Abschnitt der primären Halbleiterschicht in der zweiten Region des Mehrschichtsubstrats umfassen.

**[0099]** Ausführungsbeispiel 16: Verfahren nach Ausführungsbeispiel 15, des Weiteren umfassend das Auswählen der verspannten Halbleiterschicht, so dass sie zugverspanntes Silizium umfasst.

**[0100]** Ausführungsbeispiel 17: Verfahren nach einem Ausführungsbeispiel 15 oder Ausführungsbeispiel 16, des Weiteren umfassend das Auswählen der epitaxialen Basisschicht, so dass sie zumindest im Wesentlichen entspanntes Si<sub>x</sub>Ge<sub>1-x</sub> umfasst, wobei x zwischen etwa 0,01 bis etwa 0,99 liegt, und wobei das Diffundieren der Elemente aus der epitaxialen Basisschicht in die verspannte primäre Halbleiterschicht in der ersten Region des Mehrschichtsubstrats das Diffundieren von Germanium in die verspannte primä-

re Halbleiterschicht in der ersten Region des Mehrschichtsubstrats umfasst.

**[0101]** Ausführungsbeispiel 18: Verfahren nach einem der Ausführungsbeispiele 15 bis 17, des Weiteren umfassend das Bilden einer Vielzahl von p-Typ-FET-Transistoren, welche die erste Vielzahl von Transistor-Kanalstrukturen umfassen, und Bilden einer Vielzahl von n-Typ-FET-Transistoren, welche die zweite Vielzahl von Transistor-Kanalstrukturen umfassen.

[0102] Ausführungsbeispiel 19: Halbleiterstruktur mit einem Mehrschichtsubstrat, umfassend: ein Basissubstrat, eine eingebettete Oxidschicht über einer Oberfläche des Basissubstrats, und eine primäre Halbleiterschicht über der eingebetteten Oxidschicht auf einer Seite davon gegenüber dem Basissubstrat, wobei ein Abschnitt der primären Halbleiterschicht in der ersten Region des Mehrschichtsubstrats Si<sub>v-</sub> Ge<sub>1-v</sub> umfasst, wobei y zwischen etwa 0,20 und etwa 0,99 liegt, ein Abschnitt der primären Halbleiterschicht in einer zweiten Region des Mehrschichtsubstrats zugverspanntes Si umfasst; wobei der Abschnitt der primären Halbleiterschicht in der ersten Region des Mehrschichtsubstrats eine kristallographische Spannung aufweist, die von einer kristallographischen Spannung des Abschnitts der primären Halbleiterschicht in der zweiten Region des Mehrschichtsubstrats abweicht.

**[0103]** Ausführungsbeispiel 20: Halbleiterstruktur nach Ausführungsbeispiel 19, des Weiteren umfassend eine erste Vielzahl von p-Typ-FET-Transistoren, die jeweils einen Abschnitt der primären Halbleiterschicht in der ersten Region des Mehrschichtsubstrats umfassen, und eine zweite Vielzahl von n-Typ-FET-Transistoren, die jeweils einen Abschnitt der primären Halbleiterschicht in der zweiten Region des Mehrschichtsubstrats umfassen.

[0104] Die oben beschriebenen Ausführungsbeispiele schränken den Geltungsbereich der Erfindung nicht ein, da diese Ausführungsbeispiele lediglich beispielhafte Ausführungsformen der Erfindung darstellen, die durch den Geltungsbereich der angehängten Ansprüche und deren gesetzliche Aquivalente definiert ist. Damit fallen auch alle äquivalenten Ausführungsbeispiele in den Geltungsbereich dieser Erfindung. Tatsächlich werden sich Fachleuten aus der Beschreibung verschiedene Modifikationen der Offenlegungsschrift, zusätzlich zu den aufgezeigten und beschriebenen Beispielen, sowie alternative nützliche Kombinationen der beschriebenen Elemente erschließen. Mit anderen Worten können ein oder mehrere Merkmale eines hier beschriebenen Ausführungsbeispiels mit einem oder mehreren Merkmalen eines anderen hier beschriebenen Ausführungsbeispiels kombiniert werden, um zusätzliche Ausführungsbeispiele der Offenlegungsschrift zu verwirkli-

chen. Auch diese Modifikationen und Ausführungsbeispiele fallen in den Geltungsbereich der angehängten Ansprüche.

## ZITATE ENTHALTEN IN DER BESCHREIBUNG

Diese Liste der vom Anmelder aufgeführten Dokumente wurde automatisiert erzeugt und ist ausschließlich zur besseren Information des Lesers aufgenommen. Die Liste ist nicht Bestandteil der deutschen Patent- bzw. Gebrauchsmusteranmeldung. Das DPMA übernimmt keinerlei Haftung für etwaige Fehler oder Auslassungen.

## **Zitierte Patentliteratur**

- US 39484 [0038]

- US 6303468 [0038]

- US 6335258 [0038]

- US 6756286 [0038]

- US 6809044 [0038]

- US 6946365 [0038]

#### **Zitierte Nicht-Patentliteratur**

Marcelo S. B. Castro u. a., "Selective and Anisotropic Dry Etching of Ge over Si", Journal of Integrated Circuits and Systems 2013, Bd. 8, Nr. 2, S. 104–109 [0058]

#### **Patentansprüche**

1. Verfahren zum Herstellen einer Halbleiterstruktur, umfassend:

Bereitstellen eines Mehrschichtsubstrats, das beinhaltet:

ein Basissubstrat,

eine eingebettete Oxidschicht über einer Oberfläche des Basissubstrats,

eine verspannte primäre Halbleiterschicht über der eingebetteten Oxidschicht auf einer Seite gegenüber dem Basissubstrat, und eine epitaxiale Basisschicht über der verspannten Halbleiterschicht auf einer Seite gegenüber der eingebetteten Oxidschicht;

Diffundieren von Elementen aus der epitaxialen Basisschicht in die verspannte primäre Halbleiterschicht in einer ersten Region des Mehrschichtsubstrats, ohne dass Elemente aus der epitaxialen Basisschicht in die verspannte primäre Halbleiterschicht in einer zweiten Region des Mehrschichtsubstrats diffundieren, und Anreichern einer Konzentration der diffundierten Elemente in der primären Halbleiterschicht in der ersten Region, so dass ein Spannungszustand in der primären Halbleiterschicht in der ersten Region von einem Spannungszustand in der primären Halbleiterschicht in der zweiten Region abweicht; und Bilden einer ersten Vielzahl von Transistor-Kanalstrukturen, die jeweils einen Abschnitt der primären Halbleiterschicht in der ersten Region des Mehrschichtsubstrats umfassen, und einer zweiten Vielzahl von Transistor-Kanalstrukturen, die jeweils einen Abschnitt der primären Halbleiterschicht in der zweiten Region des Mehrschichtsubstrats umfassen.

- 2. Verfahren nach Anspruch 1, des Weiteren umfassend das Auswählen der verspannten Halbleiterschicht, so dass sie verspanntes Silizium umfasst.

- 3. Verfahren nach Anspruch 2, des Weiteren umfassend das Auswählen der verspannten Halbleiterschicht, so dass sie zugverspanntes Silizium umfasst.

- 4. Verfahren nach Anspruch 2, des Weiteren umfassend das Auswählen der epitaxialen Basisschicht, so dass sie Si<sub>x</sub>Ge<sub>1-x</sub> umfasst, wobei x zwischen etwa 0,01 bis etwa 0,99 liegt, und wobei das Diffundieren der Elemente aus der epitaxialen Basisschicht in die verspannte primäre Halbleiterschicht das Diffundieren von Germanium in die verspannte primäre Halbleiterschicht in der ersten Region des Mehrschichtsubstrats umfasst.

- 5. Verfahren nach Anspruch 1, wobei das Bilden einer ersten Vielzahl von Transistor-Kanalstrukturen und das Bilden der zweiten Vielzahl von Transistor-Kanalstrukturen das Ätzen durch die primäre Halbleiterschicht und das Definieren von Finnenstrukturen umfasst, wobei jede der Finnenstrukturen einen Abschnitt der primären Halbleiterschicht umfasst und

jede der Finnenstrukturen zur Verwendung in einem FinFET bemessen und konfiguriert ist.

- 6. Verfahren nach Anspruch 1, wobei das Bereitstellen des Mehrschichtsubstrats umfasst: epitaxiales Züchten der verspannten Halbleiterschicht auf der epitaxialen Basisschicht über einem Donatorsubstrat, um eine Donatorstruktur zu bilden; Implantieren von Ionen in die Donatorstruktur und Bilden einer geschwächten Zone in der Donatorstruktur; Bonden der Donatorstruktur an ein Empfängersubstrat, welches das Basissubstrat umfasst; und Abtrennen der Donatorstruktur entlang der geschwächten Zone, um die verspannte Halbleiterschicht und die epitaxiale Basisschicht auf das Basissubstrat zu übertragen.

- 7. Verfahren nach Anspruch 6, wobei das Bonden der Donatorstruktur an das Empfängersubstrat das Bereitstellen einer Oxidschicht auf einem oder beidem aus der Donatorstruktur und dem Empfängersubstrat und das Bonden der Donatorstruktur eines Empfängersubstrats unter Verwendung eines direkten Bonding-Verfahrens umfasst.

- 8. Verfahren nach Anspruch 7, des Weiteren umfassend das Anordnen der geschwächten Zone in einer im Wesentlichen homogenen Region des Donatorsubstrats, welche die epitaxiale Basisschicht umfasst.

- 9. Verfahren nach Anspruch 1, wobei das Diffundieren der Elemente aus der epitaxialen Basisschicht in die verspannte primäre Halbleiterschicht in der ersten Region des Mehrschichtsubstrats das Entspannen der Spannung in der primären Halbleiterschicht in der ersten Region des Mehrschichtsubstrats umfasst.

- 10. Verfahren nach Anspruch 1, wobei das Diffundieren der Elemente aus der epitaxialen Basisschicht in die verspannte primäre Halbleiterschicht in der ersten Region des Mehrschichtsubstrats das Induzieren von Druckspannung in der primären Halbleiterschicht in der ersten Region des Mehrschichtsubstrats umfasst.

- 11. Verfahren nach Anspruch 1, wobei das Diffundieren der Elemente aus der epitaxialen Basisschicht in die verspannte primäre Halbleiterschicht in der ersten Region des Mehrschichtsubstrats das Erhöhen einer Löcherbeweglichkeit in der primären Halbleiterschicht in der ersten Region umfasst.

- 12. Verfahren nach Anspruch 1, wobei das Diffundieren der Elemente aus der epitaxialen Basisschicht in die verspannte primäre Halbleiterschicht in der ersten Region des Mehrschichtsubstrats das Ausführen eines Kondensationsverfahrens an der primä-

ren Halbleiterschicht in der ersten Region des Mehrschichtsubstrats umfasst.

- 13. Verfahren nach Anspruch 12, wobei Ausführen eines Kondensationsverfahrens an der primären Halbleiterschicht in der ersten Region des Mehrschichtsubstrats das Oxidieren eines Abschnitts der primären Halbleiterschicht in der ersten Region des Mehrschichtsubstrats umfasst.

- 14. Verfahren nach Anspruch 1, des Weiteren umfassend das Bilden einer Vielzahl von p-Typ-FET-Transistoren, welche die erste Vielzahl von Transistor-Kanalstrukturen umfassen, und Bilden einer Vielzahl von n-Typ-FET-Transistoren, welche die zweite Vielzahl von Transistor-Kanalstrukturen umfassen.

- 15. Verfahren zum Herstellen einer Halbleiterstruktur, umfassend:

Bereitstellen eines Mehrschichtsubstrats, das beinhaltet:

ein Basissubstrat,

eine eingebettete Oxidschicht über einer Oberfläche des Basissubstrats.

eine verspannte primäre Halbleiterschicht über der eingebetteten Oxidschicht auf einer Seite gegenüber dem Basissubstrat, und eine epitaxiale Basisschicht über der verspannten Halbleiterschicht auf einer Seite gegenüber der eingebetteten Oxidschicht;

Maskieren einer ersten Region des Mehrschichtsubstrats mit einer ersten Maskenschicht und Entfernen eines Abschnitts der epitaxialen Basisschicht von einer zweiten Region des Mehrschichtsubstrats:

Entfernen der ersten Maskenschicht von der ersten Region des Mehrschichtsubstrats und Maskieren der zweiten Regionen des Mehrschichtsubstrats mit einer zweiten Maskenschicht;

Diffundieren von Elementen aus der epitaxialen Basisschicht in die verspannte primäre Halbleiterschicht in der ersten Region des Mehrschichtsubstrats, und Ändern eines Spannungszustands der primären Halbleiterstruktur in der ersten Region des Mehrschichtsubstrats, ohne dass Elemente in die verspannte primäre Halbleiterschicht in der zweiten Region des Mehrschichtsubstrats diffundieren; und Bilden einer ersten Vielzahl von Transistor-Kanalstrukturen, die jeweils einen Abschnitt der primären Halbleiterschicht in der ersten Region des Mehrschichtsubstrats umfassen, und einer zweiten Vielzahl von Transistor-Kanalstrukturen, die jeweils einen Abschnitt der primären Halbleiterschicht in der zweiten Region des Mehrschichtsubstrats umfassen.

- 16. Verfahren nach Anspruch 15, des Weiteren umfassend das Auswählen der verspannten Halbleiterschicht, so dass sie zugverspanntes Silizium umfasst.

- 17. Verfahren nach Anspruch 16, des Weiteren umfassend das Auswählen der epitaxialen Basis-

schicht, so dass sie zumindest im Wesentlichen entspanntes  $\mathrm{Si_xGe_{1-x}}$  umfasst, wobei X zwischen etwa 0,01 bis etwa 0,99 liegt, und wobei das Diffundieren der Elemente aus der epitaxialen Basisschicht in die verspannte primäre Halbleiterschicht in der ersten Region des Mehrschichtsubstrats das Diffundieren von Germanium in die verspannte primäre Halbleiterschicht in der ersten Region des Mehrschichtsubstrats umfasst.

- 18. Verfahren nach Anspruch 17, des Weiteren umfassend das Bilden einer Vielzahl von p-Typ-FET-Transistoren, welche die erste Vielzahl von Transistor-Kanalstrukturen umfassen, und Bilden einer Vielzahl von n-Typ-FET-Transistoren, welche die zweite Vielzahl von Transistor-Kanalstrukturen umfassen.

- 19. Halbleiterstruktur mit einem Mehrschichtsubstrat, umfassend:

ein Basissubstrat,

eine eingebettete Oxidschicht über einer Oberfläche des Basissubstrats, und

eine primäre Halbleiterschicht über der eingebetteten Oxidschicht auf einer Seite davon gegenüber dem Basissubstrat, wobei ein Abschnitt der primären Halbleiterschicht in einer ersten Region des Mehrschichtsubstrats Si<sub>y</sub>Ge<sub>1-y</sub> umfasst, wobei y zwischen etwa 0,20 und etwa 0,99 liegt, und ein Abschnitt der primären Halbleiterschicht in einer zweiten Region des Mehrschichtsubstrats zugverspanntes Si umfasst:

wobei der Abschnitt der primären Halbleiterschicht in der ersten Region des Mehrschichtsubstrats eine kristallographische Spannung aufweist, die von einer kristallographischen Spannung des Abschnitts der primären Halbleiterschicht in der zweiten Region des Mehrschichtsubstrats abweicht.

20. Halbleiterstruktur nach Anspruch 19, des Weiteren umfassend eine erste Vielzahl von p-Typ-FET-Transistoren, die jeweils einen Abschnitt der primären Halbleiterschicht in der ersten Region des Mehrschichtsubstrats umfassen, und eine zweite Vielzahl von n-Typ-FET-Transistoren, die jeweils einen Abschnitt der primären Halbleiterschicht in der zweiten Region des Mehrschichtsubstrats umfassen.

Es folgen 4 Seiten Zeichnungen

# Anhängende Zeichnungen

FIG. 10