(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4406838号

(P4406838)

(45) 発行日 平成22年2月3日(2010.2.3)

(24) 登録日 平成21年11月20日(2009.11.20)

(51) Int.Cl.

G 1 O L 21/04 (2006.01)

F 1

G 1 O L 21/04 110 D

請求項の数 4 (全 27 頁)

(21) 出願番号 特願2005-38102 (P2005-38102)

(22) 出願日 平成17年2月15日 (2005.2.15)

(65) 公開番号 特開2006-227110 (P2006-227110A)

(43) 公開日 平成18年8月31日 (2006.8.31)

審査請求日 平成18年7月11日 (2006.7.11)

(73) 特許権者 000002185

ソニー株式会社

東京都港区港南1丁目7番1号

(74) 代理人 100082740

弁理士 田辺 恵基

(72) 発明者 岡田 慎也

東京都品川区北品川6丁目7番35号ソニー株式会社内

審査官 涌井 智則

最終頁に続く

(54) 【発明の名称】オーディオ入出力制御装置及びオーディオ入出力制御方法

## (57) 【特許請求の範囲】

## 【請求項 1】

外部から入力するオーディオデータを蓄積する所定スロット数分のリングバッファと、上記オーディオデータの上記リングバッファに対する書き込みアドレスと、上記リングバッファに蓄積された上記オーディオデータを一定速度で読み出す際の読み出しアドレスとの差分値に基づいて上記リングバッファに対する読み出しアドレスを強制的に変更するか否かを判定するアドレス変更判定手段と、

上記アドレス変更判定手段により上記読み出しアドレスを変更する判定がされたとき、上記オーディオデータの信号レベルがゼロクロス直前のアドレス位置となる変更前の読み出しアドレスからゼロクロス直後のアドレス位置となる変更予定の読み出しアドレスを設定する読み出アドレス設定手段と、

上記読み出アドレス設定手段により設定された上記変更予定の読み出しアドレスと上記変更前の読み出アドレスとの差に基づいて上記リングバッファに対する上記変更予定の読み出しアドレスと上記書き込みアドレスとの間に生じる初期ディレイを確保できると判断したとき、上記変更前の読み出しアドレスを上記変更予定の読み出しアドレスへアドレスジャンプさせるアドレス変更手段と

を具えることを特徴とするオーディオ入出力制御装置。

## 【請求項 2】

上記読み出アドレス設定手段は、

上記オーディオデータに不要な直流成分が重畠していることを検出したときは、当該直

流成分を除去した状態で上記変更後の読み出アドレスを設定する

請求項 1 に記載のオーディオ入出力制御装置。

**【請求項 3】**

上記読み出アドレス設定手段は、

上記オーディオデータの信号レベルがゼロレベル以下のときや、ゼロレベルを超えるときに符号ビットをセットし、その符号ビットに基づいて上記ゼロクロス直前又は上記ゼロクロス直後を判断する

請求項 1 に記載のオーディオ入出力制御装置。

**【請求項 4】**

外部から入力するオーディオデータを蓄積する所定スロット数分のリングバッファに対する書き込みアドレスと、上記リングバッファに蓄積された上記オーディオデータを一定速度で読み出す際の読み出アドレスとの差分値に基づいて上記リングバッファに対する読み出アドレスを強制的に変更するか否かをアドレス変更判定手段により判定するアドレス変更判定ステップと、

上記アドレス変更判定ステップにより上記読み出アドレスを変更する判定がされたとき、上記オーディオデータの信号レベルがゼロクロス直前のアドレス位置となる変更前の読み出アドレスからゼロクロス直後のアドレス位置となる変更予定の読み出アドレスを読み出アドレス設定手段により設定する読み出アドレス設定ステップと、

上記読み出アドレス設定ステップにより設定された上記変更予定の読み出アドレスと上記変更前の読み出アドレスとの差に基づいて上記リングバッファに対する上記変更予定の読み出アドレスと上記書き込みアドレスとの間に生じる初期ディレイを確保できると判断したとき、アドレス変更手段により上記変更前の読み出アドレスを上記変更予定の読み出アドレスへアドレスジャンプさせるアドレス変更ステップと

を有するオーディオ入出力制御方法。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、オーディオ入出力制御装置及びオーディオ入出力制御方法に関し、例えば放送局で用いられる業務用のビデオテープレコーダに適用して好適なものである。

**【背景技術】**

**【0002】**

従来、業務用のビデオテープレコーダにおいては、収録した通常の1時間番組にコマーシャルを入れて55分間の番組として放送したいときや、1時間5分の番組として放送したいといった要求に応えることができるようになされている。

**【0003】**

このような場合、ビデオテープレコーダでは当該番組のビデオに関しては人間に不自然な印象を与えない範囲でフレーム間引きやフレーム補間等によって55分間又は1時間5分となるような变速再生処理を行うようになされている（例えば、特許文献1参照）。

**【0004】**

しかしながらビデオテープレコーダでは、变速再生処理を行う場合、オーディオに関しては連續性が保たないのでデータ間引きやデータ補間を行なうことができず、ビデオの变速再生速度に合わせてオーディオ出力した場合には音程が変化しユーザーに不自然な印象を与えてしまう。

**【0005】**

このような場合に対応するべくビデオテープレコーダではいわゆるプログラムプレイと呼ばれる機能が設けられている。このプログラムプレイとは、番組のビデオに関してフレーム間引きやフレーム補間を行うことに対して、オーディオの連續性を保ったまま音程を変化させないようにするための調整機能である。

【特許文献1】特開2000-23105公報

**【発明の開示】**

10

20

30

40

50

**【発明が解決しようとする課題】****【0006】**

ところでかかる構成のビデオテープレコーダにおいては、プログラムプレイ機能を動作させる場合にオーディオの連続性を保ったまま音程を変化させないようにするために膨大な信号処理が必要となり、通常再生の場合に比べてオーディオデータの品位を保ち難いという問題があった。

**【0007】**

本発明は以上の点を考慮してなされたもので、オーディオデータの信号処理量を低減しつつ当該オーディオデータの品位を保持し得るオーディオ入出力制御装置及びオーディオ入出力制御方法を提案しようとするものである。

10

**【課題を解決するための手段】****【0008】**

かかる課題を解決するため本発明においては、外部から入力するオーディオデータを蓄積する所定スロット数分のリングバッファに対する書込アドレスと、リングバッファに蓄積されたオーディオデータを一定速度で読み出す際の読出アドレスとの差分値に基づいてリングバッファに対する読出アドレスを強制的に変更するか否かを判定し、読出アドレスを変更する判定がされたとき、オーディオデータの信号レベルがゼロクロス直前のアドレス位置となる変更前の読出アドレスからゼロクロス直後のアドレス位置となる変更予定の読出アドレスを設定し、変更予定の読出アドレスと変更前の読出アドレスとの差に基づいてリングバッファに対する変更予定の読出アドレスと書込アドレスとの間に生じる初期ディレイを確保できると判断したとき、変更前の読出アドレスを変更予定の読出アドレスへアドレスジャンプせざるようにしたことにより、ゼロクロス直前のアドレス位置からゼロクロス直後のアドレス位置となるように変更予定の読出アドレスを設定することができる。アドレスジャンプしたときでも、信号レベルの変化が極めて自然であってオーディオ出力の連続性を保ってオーディオデータの品位を保持しつつ、変更予定の読出アドレスと書込アドレスとの間に生じる初期ディレイを確保できるので、書込アドレスが変更予定の読出アドレスに追い越したり、変更予定の読出アドレスが書込アドレスを追い越すというリスクを予め回避することができる。

20

**【発明の効果】****【0009】**

30

本発明によれば、ゼロクロス直前のアドレス位置からゼロクロス直後のアドレス位置となるように変更予定の読出アドレスを設定することができるので、アドレスジャンプしたときでも、信号レベルの変化が極めて自然であってオーディオ出力の連続性を保ってオーディオデータの品位を保持しつつ、変更予定の読出アドレスと書込アドレスとの間に生じる初期ディレイを確保できるので、書込アドレスが変更予定の読出アドレスに追い越したり、変更予定の読出アドレスが書込アドレスを追い越すというリスクを予め回避することができ、かくしてオーディオデータの信号処理量を低減しつつ当該オーディオデータの品位を保持し得るオーディオ入出力制御装置及びオーディオ入出力制御方法を実現することができる。

40

**【発明を実施するための最良の形態】****【0010】**

以下、図面について、本発明の一実施の形態を詳述する。

**【0011】****(1) 本発明の原理**

本発明においては、ビデオテープレコーダでのプログラムプレイ機能を動作させる際に、ビデオテープから読み出した番組のビデオに関してはフレーム間引きやフレーム補間等による变速再生処理を行うにも拘らず、オーディオの音程を変えないためのオーディオ入出力制御装置の原理について最初に説明する。

**【0012】**

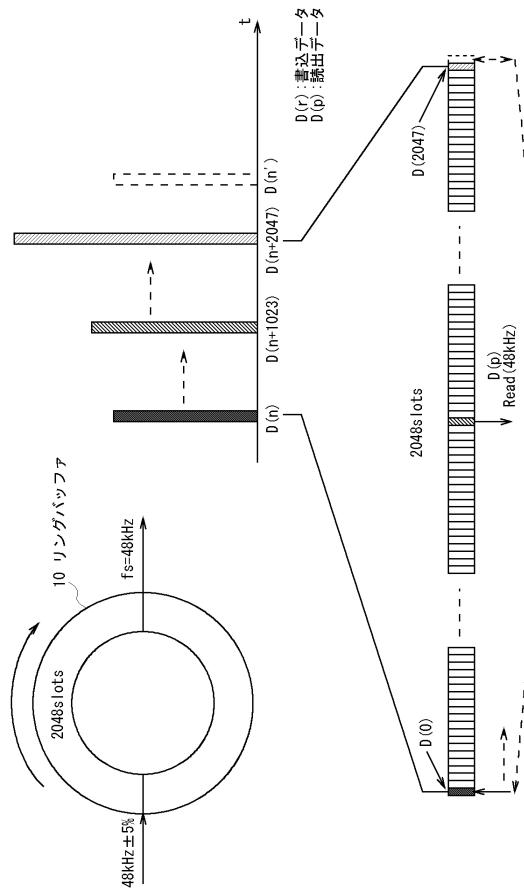

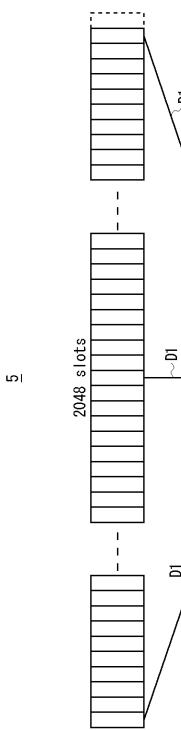

図1に示すように、オーディオ入出力制御装置においてはオーディオデータが計204

50

8スロットのリングバッファ10に例えれば書き速度48[kHz]で書き込まれ、当該リングバッファ10から一定の読み出速度48[kHz]で当該オーディオデータが読み出される標準再生処理の場合には、オーディオデータに基づいて出力されるオーディオの音程が変化することはない。

#### 【0013】

しかしながらオーディオ入出力制御装置では、ビデオテープレコーダのプログラムプレイ機能が動作した場合、ビデオの变速再生処理に合わせてオーディオデータを書き速度48[kHz]±5%でリングバッファ10に書き込み、当該リングバッファ10からは一定の48[kHz]で当該オーディオデータを読み出すようになされている。

#### 【0014】

ここでオーディオデータの読み出しを一定速度の48[kHz]で行うのは、当該読み出されたオーディオデータに基づいて出力されるオーディオの音程を変化させないようにするためである。

#### 【0015】

この場合のオーディオデータの読み出しは、当該オーディオデータの書き速度に±5%の変動があるため書きタイミングと読み出タイミングとの間でずれが生じ、書き速度48[kHz]-5%のときは読み出データが書き出データをいずれ追い越すことになり、書き速度48[kHz]+5%のときは書き出データが読み出データをいずれ追い越すことになる。

#### 【0016】

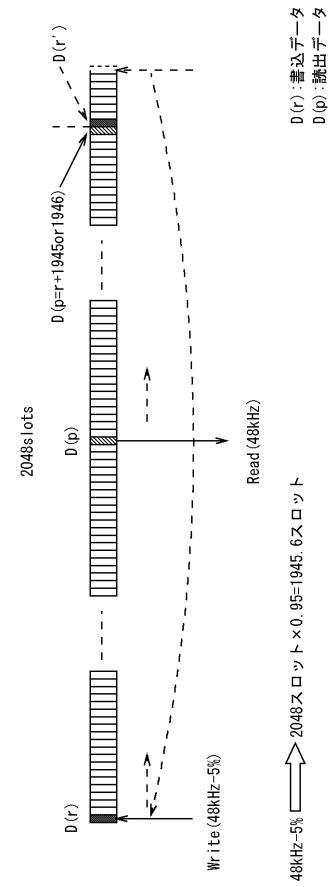

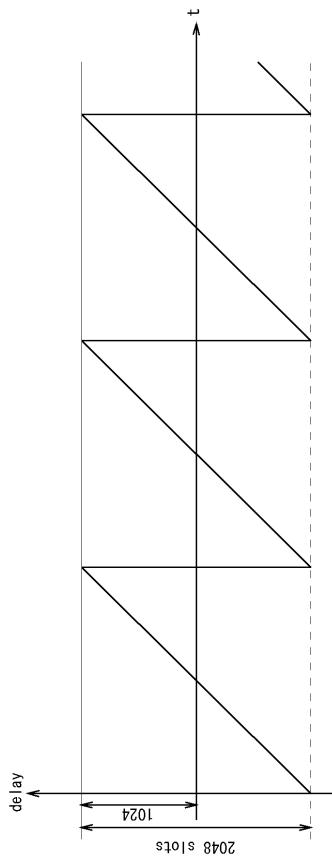

図2に示すように、オーディオデータが書き速度48[kHz]-5%のときは読み出速度48[kHz]が一定であるため書き速度よりも読み出速度の方が速くなり、読み出データD(p)が1周(2048スロット)進む間に書き出データD(r)が1945スロット又は1946スロット(2048スロット×0.95=1945.6スロット)進むため、約20周(2048÷(2048-1945.6)=20)毎に読み出データD(p)が書き出データD(r)に追い付き追い越すことになる。

#### 【0017】

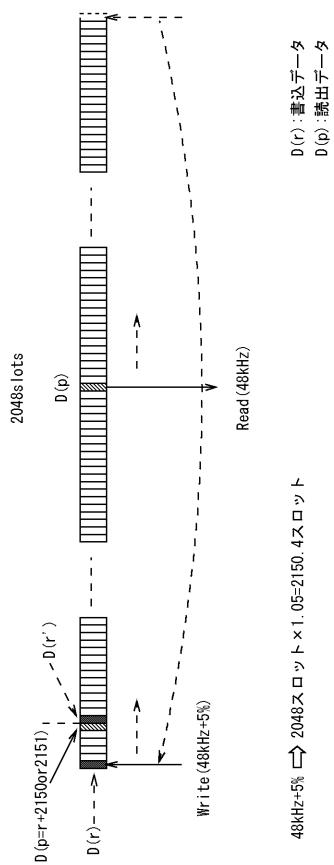

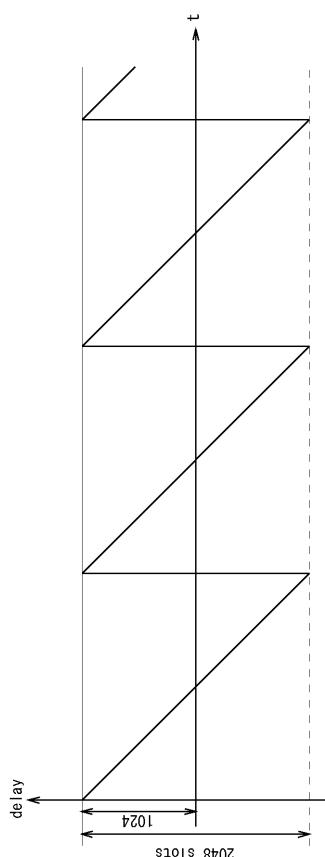

また図3に示すように、オーディオデータが書き速度48[kHz]+5%のときは読み出速度48[kHz]が一定であるため読み出速度よりも書き速度の方が速くなり、読み出データD(p)が一周(2048スロット)進む間に書き出データD(r)が2150スロット又は2151スロット(2048スロット×1.05=2150.4スロット)進むため、約20周(2048÷(2150.4-2048)=20周)毎に書き出データD(r)が読み出データD(p)に追い付き追い越すことになる。

#### 【0018】

このように読み出データD(p)が書き出データD(r)を追い越す場合や、書き出データD(r)が読み出データD(p)を追い越す場合には、その時点で読み出データD(p)の連続性が維持できなくなって出力する音声にノイズが発生してしまう。

#### 【0019】

そこで図4に示すように、オーディオ入出力制御装置では例えば書き出データD(r)が読み出データD(p)を追い越す場合、リングバッファ10の他に256ステップすなわち256スロット分のクロスフェードバッファを別に用意しておき、書き出データD(r)に追い付かれる前の読み出データD(p)を当該クロスフェードバッファに256ステップ分だけコピーし、書き出データD(r)に追い付かれたときから当該コピーした読み出データD(p)を次第にフェードアウトさせながら書き込まれた直後の読み出データD(p)をフェードインさせることにより、いわゆるクロスフェード処理を実行し得るようになされている。

#### 【0020】

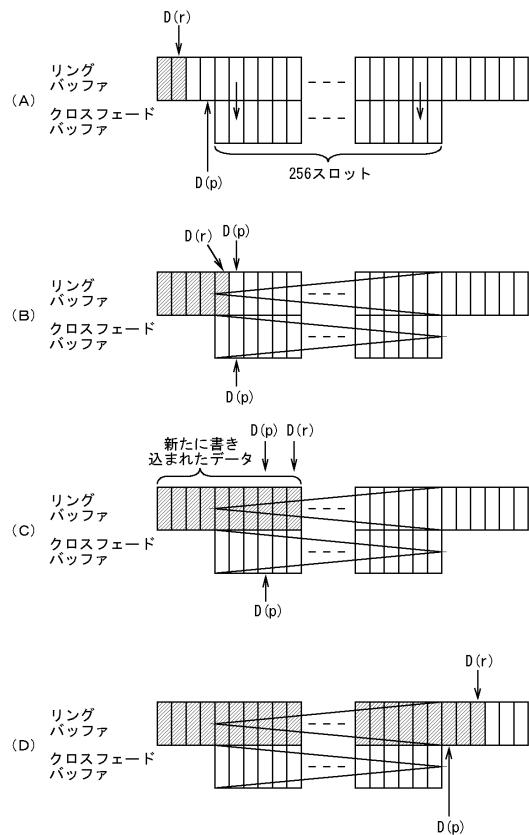

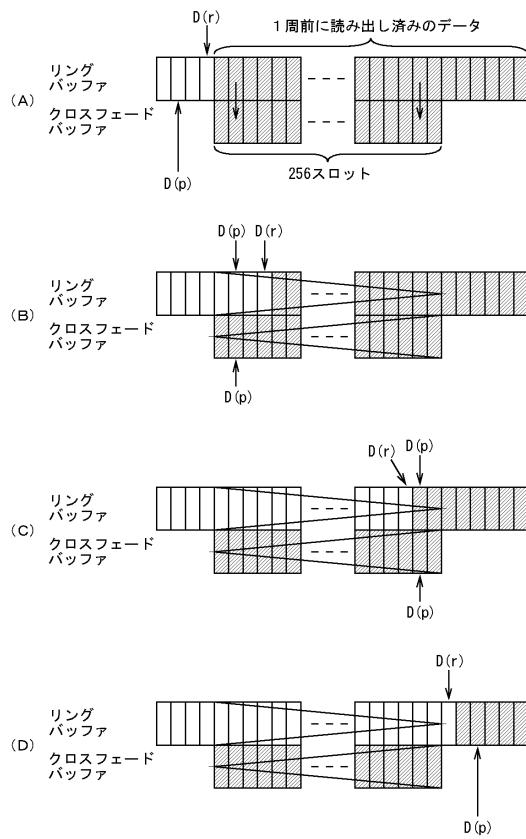

すなわち図5(A)～(D)に示すように書きアドレスが読み出アドレスを追い越すときのクロスフェード処理では、オーディオ入出力制御装置は、まず図5(A)に示すように読み出データD(p)が書き出データD(r)に追い付かれる直前に当該読み出データD(p)をクロスフェードバッファに256スロット分だけコピーする。

#### 【0021】

10

20

30

40

50

次にオーディオ入出力制御装置は、図5( B )に示すように、クロスフェードバッファから読み出す読出データD(p)の信号レベルを通常のレベルから徐々にフェードアウトしていくと共に、リングバッファ10から読み出す読出データD(p)の信号レベルを0から徐々にフェードインしていく。

#### 【0022】

ここでオーディオ入出力制御装置は、図5( C )に示すように、リングバッファ10において書きデータD(r)が読出データD(p)を追い抜き、この時点以降、リングバッファのまだ読み出されていない読出データD(p)を書きデータD(r)により上書きしていく(図中の斜線部分)。

#### 【0023】

このとき、リングバッファ10上の読出データD(p)は追い抜かれた箇所において不連続となるものの、この時点ではまだリングバッファ10から読み出した読出データD(p)の信号レベルが十分に小さく、また同時にクロスフェードバッファから読み出す連続した読出データD(p)の信号レベルが十分に大きいため、オーディオ入出力部はこのような不連続な読出データD(p)を読み出してもオーディオを聴取するユーザに違和感を与えることはない。

10

#### 【0024】

続いてオーディオ入出力制御装置は、これまでリングバッファ10から読み出していた読出データD(p)と連続したクロスフェードバッファの読出データD(p)を徐々にフェードアウトしながら、これまでリングバッファ10から読み出していた読出データD(p)と不連続となる、先ほど書き込まれた直後の書きデータD(r)を「1周先の」読出データD(p)として読み出して徐々にフェードインしていくことによりクロスフェード処理を進めていき、クロスフェードバッファの読出データD(p)から徐々にリングバッファ10の「1周先の」読出データD(p)に切り換えていく。

20

#### 【0025】

その後オーディオ入出力制御装置は、図5( D )に示すようにクロスフェード処理を完了し、書きデータD(r)により上書きされた直後の書きデータD(r)を読出データD(p)として通常の信号レベルで読み出す。

#### 【0026】

この場合、オーディオ入出力制御装置ではクロスフェード処理によって書きデータD(r)が読出データD(p)を追い越す際に生じるノイズを防止できるため、リングバッファ10に蓄積されたオーディオデータを1周分捨てる(データ間引きした)ことになるにも拘らず、ユーザの聴感的にはオーディオデータの連続性を維持し得るようになされている。

30

#### 【0027】

また図6( A )～( D )に示すように読出アドレスが書きアドレスを追い越すときのクロスフェード処理では、オーディオ入出力制御装置は、まず図6( A )に示すように書きデータD(r)が読出データD(p)に追い付かれる前に当該読出データD(p)をクロスフェードバッファに256スロット分だけコピーする。

#### 【0028】

次にオーディオ入出力制御装置は、図6( B )に示すように、リングバッファ10に書きデータD(r)として書き込まれた直後の読出データD(p)を読み出して出力する際の信号レベルを通常のレベルから徐々にフェードアウトしていくと共に、既に1回読み出している読出データD(p)(図中斜線で示す)をクロスフェードバッファから2回目に読み出して出力する際の信号レベルを0から徐々にフェードインしていく。

40

#### 【0029】

このときクロスフェードバッファ上の読出データD(p)は「1周前の」ものであるため、これまでリングバッファ10から読み出していた読出データD(p)とは不連続であるものの、この時点ではまだクロスフェードバッファから読み出す読出データD(p)の信号レベルが十分に小さく、またこれまでリングバッファ10から読み出していた読出データD(p)に連続した当該リングバッファ10から読み出す読出データD(p)の信号レベルが十分

50

に大きいため、オーディオ入出力部はこのような不連続な読み出データ D(p)を読み出してもオーディオを聴取するユーザに違和感を与えることはない。

#### 【 0 0 3 0 】

続いてオーディオ入出力制御装置は、これまでリングバッファ 10 から読み出していた読み出データ D(p)と連続した読み出データ D(p)を徐々にフェードアウトしながら、これまでリングバッファ 10 から読み出していた読み出データ D(p)とは不連続な「1周前の」読み出データ D(p)を徐々にフェードインしていくことによりクロスフェード処理を進めていく、リングバッファ 10 の読み出データ D(p)から徐々にクロスフェードバッファの「1周前の読み出データ D(p)」に切り換えていく。

#### 【 0 0 3 1 】

10

その後オーディオ入出力制御装置は、図 6 (C) に示すように、リングバッファ 10において読み出データ D(p)が書き込みデータ D(r)を追い抜き、この時点以降、当該リングバッファ 10 の既に 1 回読み出した読み出データ D(p)を 2 回目に読み出す。(図中の斜線部分)。

#### 【 0 0 3 2 】

このとき、リングバッファ 10 上の読み出データ D(p)は追い抜かれた箇所において不連続となるものの、この時点では既にリングバッファ 10 から読み出した読み出データ D(p)の信号レベルが十分に小さく、また同時にクロスフェードバッファから読み出す「1周前の」読み出データ D(p)の信号レベルが既に十分に大きいため、オーディオ入出力部はこのような不連続な読み出データ D(p)を読み出してもオーディオを聴取するユーザに違和感を与えることはない。

20

#### 【 0 0 3 3 】

このクロスフェード処理の完了後、オーディオ入出力制御装置は、図 6 (D) に示すように、2 回目の読み出しとなる読み出データ D(p)をリングバッファ 10 から通常の信号レベルで読み出していく。

#### 【 0 0 3 4 】

この場合、オーディオ入出力制御装置ではクロスフェード処理によって読み出データ D(p)が書き込みデータ D(r)を追い越す際に生じるノイズを防止できるため、リングバッファ 10 に蓄積された同一のオーディオデータを再度読み出してデータ補間することになるにも拘らず、ユーザの聴感的にはオーディオデータの連続性を維持し得るようになされている。

30

#### 【 0 0 3 5 】

なお、この場合には読み出データ D(p)が書き込みデータ D(r)を追い越すので、256ステップのクロスフェード処理が終了した時点では、書き込みデータ D(r)が読み出データ D(p)の直後に位置することになって、書き込みデータ D(r)がリングバッファ 10 を約 20 周進む間は読み出データ D(p)に追い付かれることはない。

#### 【 0 0 3 6 】

このようにビデオテープレコーダでは、書き込みデータ D(r)が読み出データ D(p)に追い越される場合や、読み出データ D(p)が書き込みデータ D(r)に追い越される場合、クロスフェード処理を行うようになされているが、12 個のオーディオトラックを用いてオーディオデータの信号処理を行っているためクロスフェード処理に応じた信号処理量が膨大となり効率的ではない。またクロスフェード処理では、2 種類のオーディオデータを重ね合わせるため、どうしてもオーディオの品位が低下してしまう。

40

#### 【 0 0 3 7 】

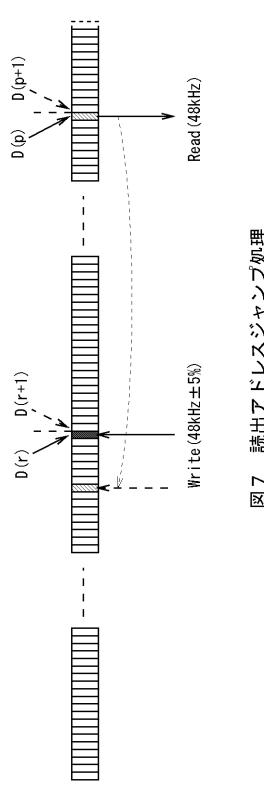

そこで図 7 に示すように、オーディオ入出力制御装置では書き込み速度と読み出速度との速度差によって、例えば書き込みデータ D(r)が読み出データ D(p)に追い付くことになった場合、読み出アドレスを書き込みアドレスの後ろへ強制的に変更することにより、読み出アドレスジャンプ処理を実行するようになされている。

#### 【 0 0 3 8 】

このときオーディオ入出力制御装置では、読み出アドレスを書き込みアドレスの後ろへ強制的に変更するのだが、何ら考慮せずに読み出アドレスジャンプ処理を実行した場合、アドレス

50

変更前の読み出アドレス時におけるオーディオデータとアドレス変更後の読み出アドレス時におけるオーディオデータとの間では信号レベルに大きな差が生じ、当該オーディオデータの連続性が保てずノイズを発生させかねない。

#### 【0039】

そこでオーディオ入出力制御装置では、アドレス変更前の読み出アドレス時におけるオーディオデータとアドレス変更後の読み出アドレス時におけるオーディオデータとの間で、当該オーディオデータの信号レベル差が少ない位置を変更後の読み出アドレスとして決定するようになされている。

#### 【0040】

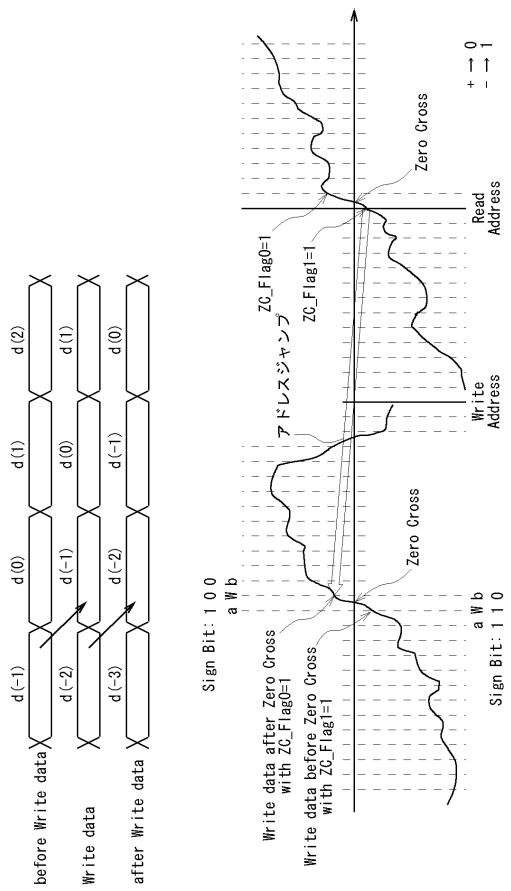

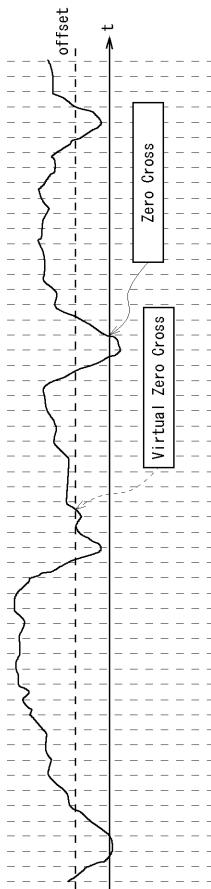

具体的には、図8に示すようにオーディオ入出力制御装置は、オーディオデータの信号レベルがゼロレベルをクロスするゼロクロス近傍のとき、現在の読み出アドレスを書きアドレスの後ろへ強制的にアドレスジャンプさせるようになされている。 10

#### 【0041】

すなわちオーディオ入出力制御装置は、例えば書きアドレスが読み出アドレスに追い付いてくると、現時点におけるアドレス変更前の読み出アドレスからリングバッファ10の約1周分先の書きアドレスの後ろであって、当該オーディオデータの信号レベルがゼロクロス近傍となる位置をアドレス変更後の読み出アドレスとして決定する。

#### 【0042】

このときオーディオ入出力制御装置では、ゼロクロス直前の読み出アドレスから、ゼロクロス直後の読み出アドレスへとアドレスジャンプさせるようになされており、これによりアドレスジャンプ前とアドレスジャンプ後との間においてオーディオデータの連続性を維持してオーディオの品位を低下させないようになされている。 20

#### 【0043】

但しオーディオ入出力制御装置では、必ずしもこれに限る必要はなく、ゼロクロス直前の読み出アドレスからゼロクロス直前の読み出アドレスへアドレスジャンプさせ、又はゼロクロス直後の読み出アドレスからゼロクロス直後の読み出アドレスへアドレスジャンプさせ、或いはゼロクロス直後の読み出アドレスからゼロクロス直前の読み出アドレスへアドレスジャンプさせるようにしても良い。

#### 【0044】

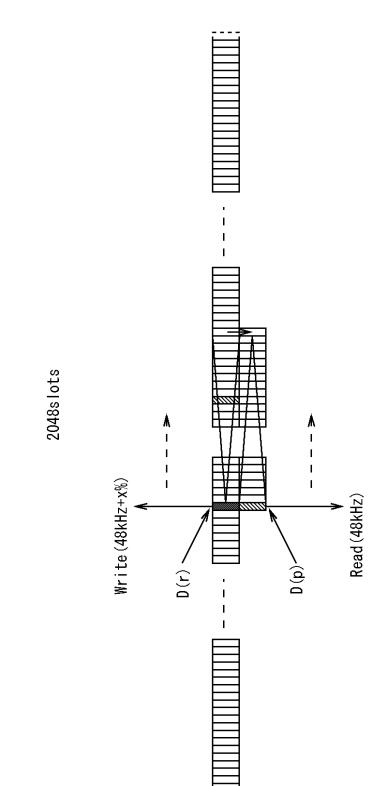

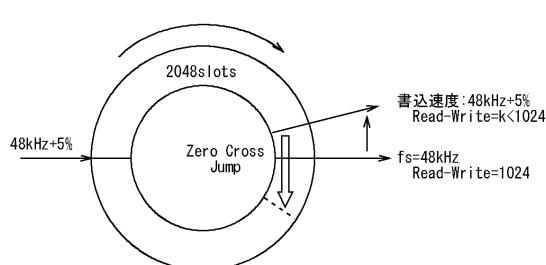

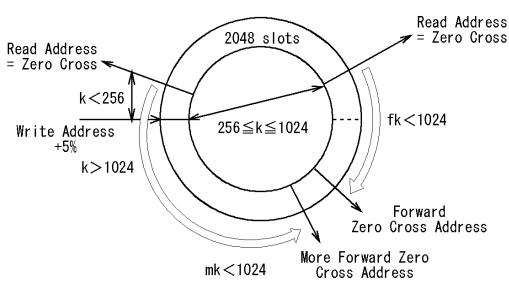

ところで図9に示すようにオーディオ入出力制御装置は、2048スロットを有するリングバッファ10を用いているため、例えばオーディオデータの書き速度が読み出速度よりも速い場合には書きデータが読み出データを追い越した瞬間に最小ディレイとなり、その後次第にディレイ量が増えていく。 30

#### 【0045】

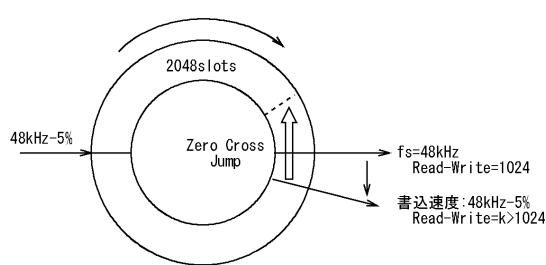

また図10に示すようにオーディオ入出力制御装置は、例えばオーディオデータの読み出速度が書き速度よりも速い場合には読み出データが書きデータを追い越した瞬間に最小ディレイとなり、その後次第にディレイ量が増えていく。

#### 【0046】

そのためオーディオ入出力制御装置では、オーディオデータの書きアドレスに対して読み出アドレスをリングバッファ10の半分の値(1024スロット分)だけ離した位置に設定し、書きデータD(r)の書きタイミングと読み出データD(p)の読み出タイミングとの間でリングバッファ10の半周分に相当する1024スロットの初期ディレイ(21.3msec)をディレイ量として保持するようにしたい。 40

#### 【0047】

しかしながらオーディオ入出力制御装置は、例えば書き速度が読み出速度よりも速い場合には読み出データが書きデータに追い付かれる前に読み出アドレスを書きアドレスの後ろへアドレスジャンプさせるが、このときはディレイ量が最も大きくなってしまうので1024スロットの初期ディレイから大きく外れることのない一定範囲(例えば1024スロット±100スロット)に制御するようになされている。

#### 【0048】

50

具体的には図11(A)に示すようにオーディオ入出力制御装置は、書込速度が読出速度よりも速い場合、読出アドレスがいずれ書込アドレスに追い付かれてしまうので、読出アドレスと書込アドレスとの差分値kを算出し、 $k < 1024$ となった場合に読出アドレスを少し先に進めた位置へ強制的にアドレスジャンプさせるようになされている。

#### 【0049】

これによりオーディオ入出力制御装置は、書込速度が読出速度よりも速い場合であっても読出アドレスと書込アドレスとの差分値kをある程度一定に保つことができるため、1024スロットの初期ディレイから大きく外れることがない一定範囲のディレイ量を維持し得るようになされている。

#### 【0050】

また図11(B)に示すようにオーディオ入出力制御装置は、読出速度が書込速度よりも速い場合、読出アドレスと書込アドレスとの差が拡がって、いずれ書込アドレスが読出アドレスに追い付かれるので、読出アドレスと書込アドレスとの差分値kを算出し、 $k > 1024$ となった場合に読出アドレスを現時点よりも少し戻した位置へ強制的にアドレスジャンプさせるようになされている。

#### 【0051】

これによりオーディオ入出力制御装置は、読出速度が書込速度よりも速い場合であっても読出アドレスと書込アドレスとの差分値kをある程度一定に保つことができるため、1024スロットの初期ディレイから大きく外れることがない一定範囲のディレイ量を維持し得るようになされている。

#### 【0052】

因みにオーディオ入出力制御装置は、アドレスジャンプ前の読出アドレスと、アドレスジャンプ後の読出アドレスとの間で、オーディオデータの信号レベル差が少ないゼロクロス近傍同士でアドレスジャンプさせるようになされている。

#### 【0053】

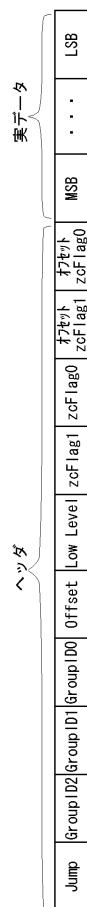

ところで、リングバッファ10にスロット単位で書き込まれるオーディオデータは、図12に示すように、MSB(Most Significant Bit)からLSB(Least Significant Bit)で示される実データと、当該実データの前段に記述されたヘッダとから構成されている。

#### 【0054】

オーディオデータのヘッダにおいては、「Jump」としてゼロクロス近傍であるか否かに基づいてアドレスジャンプすべきオーディオデータがあるときは現在のアドレスがジャンプアドレス(詳しくは後述する)であることを表すフラグ情報が記述され、「GroupId2」、「GroupId1」、「GroupId0」として12トラックのうち所望のトラック同士を関連付けて1つのグループとした際のグループを識別するグループIDが記述され、「Offset」としてアナログディジタル変換後のオーディオデータに重畠している直流成分を除去するためのオフセット量が記述される。

#### 【0055】

図13に示すようにオーディオデータに直流成分が重畠している場合、波形全体の信号レベルが直流成分によって上がり、直流成分が重畠されていない本来のオーディオデータにおけるゼロクロスが検出できなくなってしまう。

#### 【0056】

そこでオーディオ入出力制御装置は、直流成分を除去するためのオフセット量を予め検出し、それをオーディオデータのヘッダ情報における「Offset」に記述するようになされている。従ってオーディオ入出力制御装置は、直流成分が重畠しているオーディオデータについては当該直流成分を予め除去したバーチャルゼロクロスを検出することにより、直流成分が重畠していない本来のオーディオデータにおけるゼロクロスを検出し得るようになされている。

#### 【0057】

またオーディオデータのヘッダ(図12)においては、「Low level」としてオーディオデータが例えば-60[dB]以下のローレベルであるときにその旨が記述され、「zcFlag

10

20

30

40

50

1」としてオーディオデータがゼロクロス直前(図8)であるときにフラグ情報が記述され、「zcFlag0」としてオーディオデータがゼロクロス直後(図8)であるときにフラグ情報が記述されるようになされている。

#### 【0058】

従ってオーディオ入出力制御装置では、2048スロット毎のオーディオデータにおけるヘッダを参照して「zcFlag1」や「zcFlag0」のフラグ情報を確認することにより、オーディオデータの信号レベルがゼロクロス直前であるのか、ゼロクロス直後であるのかを瞬時に判別し得るようになされている。

#### 【0059】

またオーディオデータのヘッダでは、直流成分の重畠されているオーディオデータについては、「オフセットzcFlag1」として直流成分が重畠されていない本来のオーディオデータがゼロクロス直前であるときにフラグ情報が記述され、「オフセットzcFlag0」として直流成分が重畠していない本来のオーディオデータがゼロクロス直後であるときにフラグ情報が記述されるようになされている。

#### 【0060】

ところでオーディオ入出力制御装置は、図8に示したように、オーディオデータの信号レベルをリングバッファ10のスロット単位で監視しており、その結果、オーディオデータの信号レベルがゼロレベル以下のときは符号ビットとして「1」をセットし、ゼロレベルを超えるときには符号ビットとして「0」をセットするようになされている。

#### 【0061】

従ってオーディオ入出力制御装置は、例えばゼロクロス直前の時点(記号Wで示す)で書き込まれたオーディオデータの信号レベルがゼロレベル以下であるため符号ビットとして「1」をセットし、その1時点前(記号aで示す)のオーディオデータの信号レベルもゼロレベル以下であるため符号ビットとして「1」をセットし、そのゼロクロス直前の時点に対して1時点後(記号bで示す)のオーディオデータの信号レベルがゼロレベルを超えるため符号ビットとして「0」をセットする。

#### 【0062】

また同様にオーディオ入出力制御装置は、例えばゼロクロス直後の時点(記号Wで示す)で書き込まれたオーディオデータの信号レベルがゼロレベルを超えるため符号ビットとして「0」をセットし、その1時点前(記号aで示す)のオーディオデータの信号レベルはゼロレベル以下であるため符号ビットとして「1」をセットし、そのゼロクロス直後の時点に対して1時点後(記号bで示す)のオーディオデータの信号レベルがゼロレベルを超えるため符号ビットとして「0」をセットする。

#### 【0063】

従ってオーディオ入出力制御装置は、この符号ビットをスロット毎に監視しておくことにより、符号ビットが「1」「0」に変化するタイミングをゼロクロス時と判断することができ、そのときの符号ビットが「1」を示しているスロットをゼロクロス直前のオーディオデータとして把握し得ると共に「zcFlag1」のフラグ情報として「1」をセットし、符号ビットが「0」を示しているスロットをゼロクロス直後のオーディオデータとして把握し得ると共に「zcFlag0」のフラグ情報として「0」をセットするようになされている。

#### 【0064】

なおオーディオ入出力制御装置は、「オフセットzcFlag1」及び「オフセットzcFlag0」のフラグ情報についても、「zcFlag1」及び「zcFlag0」と同様に符号ビットに基づいて「1」又は「0」をセットするようになされている。

#### 【0065】

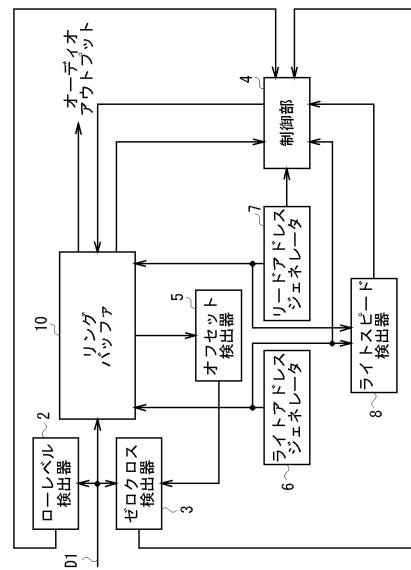

##### (2) オーディオ入出力制御装置の構成

実際上、図14に示すようにオーディオ入出力制御装置1は、2048スロット構成のリングバッファ10に合わせて2048サンプル毎のオーディオデータD1をローレベル検出器2、ゼロクロス検出器3及びリングバッファ10に入力する。

10

20

30

40

50

**【 0 0 6 6 】**

ローレベル検出器 2 は、 C P U (Central Processing Unit) 構成でなる制御部 4 でゼロクロスを判断するために、オーディオデータ D 1 の信号レベルが - 60 [dB] 以下のローレベルであることを検出するようになされており、検出結果を制御部 4 へ出力する。

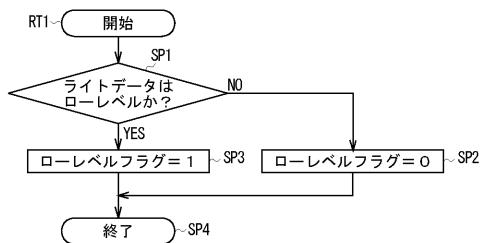

**【 0 0 6 7 】**

実際上、ローレベル検出器 2 は、図 15 に示すようにルーチン R T 1 の開始ステップから入って次のステップ S P 1 へ移り、リングバッファ 1 0 に書き込むオーディオデータ D 1 の信号レベルがローレベルであるか否かを判定する。

**【 0 0 6 8 】**

ここで否定結果が得られるとローレベル検出器 2 は、次のステップ S P 2 へ移り、ローレベルフラグとして「 0 」をセットし、次のステップ S P 4 へ移って処理を終了する。一方、ステップ S P 1 で肯定結果が得られると、ローレベル検出器 2 は次のステップ S P 3 へ移り、ローレベルフラグとして「 1 」をセットし、次のステップ S P 4 へ移って処理を終了する。10

**【 0 0 6 9 】**

ゼロクロス検出器 3 は、オーディオデータ D 1 の信号レベルを監視することにより、当該オーディオデータの信号レベルが「 0 」レベルをクロスするか否かを検出し、その検出結果を制御部 4 へ出力する。

**【 0 0 7 0 】**

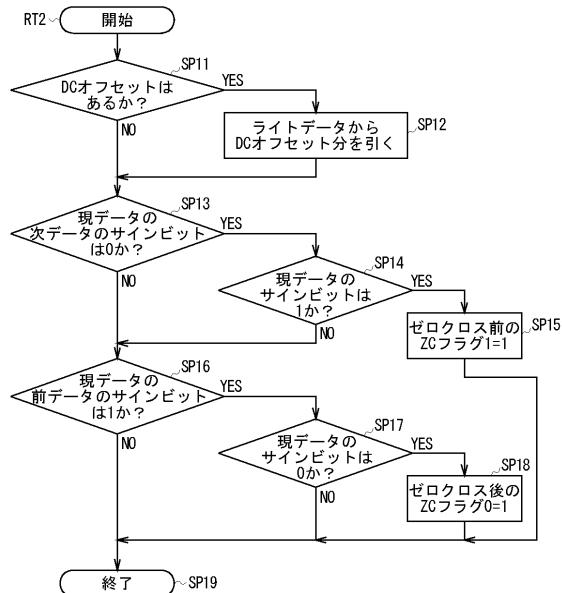

実際上、ゼロクロス検出器 3 は図 16 に示すようにルーチン R T 2 の開始ステップから入って次のステップ S P 1 1 へ移り、オーディオデータ D 1 に直流成分が重畠しているか否かをオフセット検出器 5 の検出結果に基づいて判別する。20

**【 0 0 7 1 】**

ここで図 17 に示すようにオフセット検出器 5 は、リングバッファ 1 0 の 2 0 4 8 スロットに順次書き込むオーディオデータ D 1 の信号レベルの合計値を 2 0 4 8 で除算することにより平均値を算出し、当該平均値を直流成分のオフセット量として検出するようになされている。

**【 0 0 7 2 】**

ステップ S P 1 1 で否定結果が得られると、ゼロクロス検出器 5 はオーディオデータ D 1 に直流成分が重畠していないので何ら処理を施すことなく次のステップ S P 1 3 へ移る。30

**【 0 0 7 3 】**

一方ステップ S P 1 1 で肯定結果が得られると、ゼロクロス検出器 5 はオーディオデータ D 1 に直流成分が重畠しているのでリングバッファ 1 0 に書き込むオーディオデータ D 1 から直流成分がないものと仮定したバーチャルゼロクロスを基準にして以降判断し、次のステップ S P 1 3 へ移る。

**【 0 0 7 4 】**

ステップ S P 1 3 においてゼロクロス検出器 5 は、図 8 に示したように、現時点（記号 W で示す）におけるオーディオデータ D 1 の次の時点（記号 b で示す）における符号ビットが「 0 」であるか否かを判定し、否定結果が得られると、次のステップ S P 1 6 へ移るのに対し、肯定結果が得られると次のステップ S P 1 4 へ移る。40

**【 0 0 7 5 】**

ステップ S P 1 4 においてゼロクロス検出器 5 は、現時点（記号 W で示す）におけるオーディオデータ D 1 の符号ビットが「 1 」であるか否かを判定し、否定結果が得られる記号 W b の並びとなる符号ビットが「 0 0 」となっていること、すなわちゼロクロスしていないことを表しており、このとき次のステップ S P 1 6 へ移る。

**【 0 0 7 6 】**

一方ステップ S P 1 4 で肯定結果が得られると、記号 W b の並びとなる符号ビットが「 1 0 」となっていること、すなわちゼロクロスしていることを表しており、このときゼロクロス検出器 5 は次のステップ S P 1 5 へ移り、ゼロクロス直前における「 zcFlag1 」の50

フラグ情報として「1」をセットした後、ステップSP19へ移って処理を終了する。

**【0077】**

ステップSP16においてゼロクロス検出器5は、現時点(記号Wで示す)におけるオーディオデータD1の前時点(記号aで示す)における符号ビットが「1」であるか否かを判定し、否定結果が得られると、ステップSP19へ移って処理を終了するのに対し、肯定結果が得られると次のステップSP17へ移る。

**【0078】**

ステップSP17においてゼロクロス検出器5は、現時点(記号Wで示す)におけるオーディオデータD1の符号ビットが「0」であるか否かを判定し、否定結果が得られる記号aWの並びとなる符号ビットが「11」となっていること、すなわちゼロクロスしていないことを検出し、ステップSP19へ移って処理を終了する。10

**【0079】**

一方ステップSP17で肯定結果が得られると、記号aWの並びとなる符号ビットが「10」となっていること、すなわちゼロクロスしていることを表しており、このときゼロクロス検出器5は次のステップSP18へ移り、ゼロクロス直後における「zcFlag0」のフラグ情報として「1」をセットした後、ステップSP19へ移って処理を終了する。

**【0080】**

ところでリングバッファ10は、上述した通り、2048スロット構成であり、入力されたオーディオデータD1をライトアドレスジェネレータ6から供給される書込アドレスに従い書込速度48[kHz]±5%でスロット毎に書き込み、当該オーディオデータD1をリードアドレスジェネレータ7から供給される読出アドレスに従い一定の読出速度48[kHz]で読み出して出力するようになされている。20

**【0081】**

このときライトアドレスジェネレータ6及びリードアドレスジェネレータ7は、書込アドレス及び読出アドレスをライトスピード検出器8へ送出すると共に、制御部4へ送出するようになされている。

**【0082】**

ライトスピード検出器8は、読出アドレスと書込アドレスとの差分値kを算出することにより、書込速度と読出速度との速度差を検出するようになされており、その差分値kを制御部4へ送出する。30

**【0083】**

制御部4は、書込アドレス、読出アドレス及び当該読出アドレスと当該書込アドレスとの差分値kに基づいて、現時点におけるアドレス変更前の読出アドレスを何処にアドレスジャンプさせるべきかを判断してアドレスジャンプ先となるアドレス変更後の読出アドレスを決定し、当該アドレス変更後の読出アドレスをリングバッファ10に指示するようになされている。

**【0084】**

(3) アドレスジャンプ処理手順

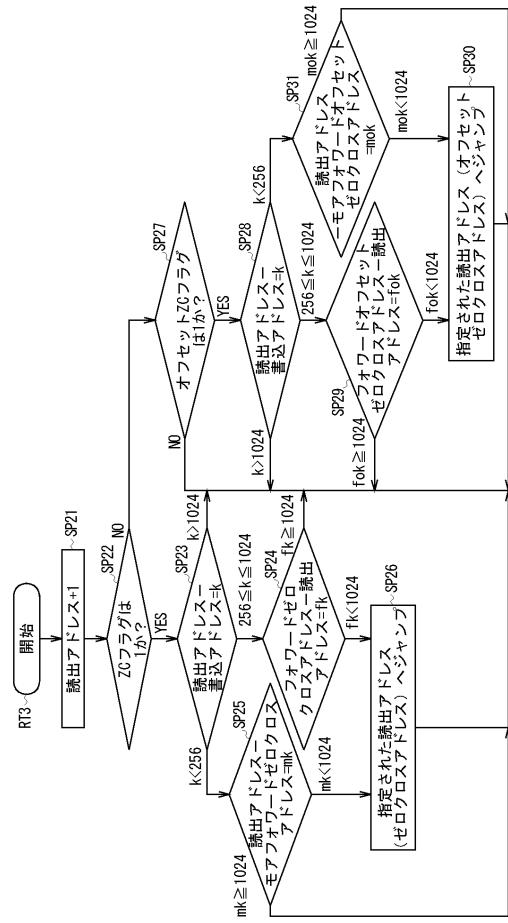

次に、オーディオ入出力制御装置1の制御部4がリングバッファ10に対する書込速度と読出速度との速度差に応じて読出アドレスをアドレスジャンプさせるアドレスジャンプ処理手順について、書込速度が読出速度よりも速い場合と、読出速度が書込速度よりも速い場合とに分けて説明する。40

**【0085】**

(3-1) 書込速度が読出速度よりも速い場合の読出アドレスジャンプ処理手順

オーディオ入出力制御装置1の制御部4は、アプリケーションプログラムであるアドレスジャンプ処理プログラムに従い、ビデオテープレコーダのプログラムプレイ機能が動作する際にビデオの变速再生処理に応じてオーディオデータの書込速度が読出速度よりも速い場合にオーディオの音程変化を起こさせることなく、かつオーディオの連続性を維持するための読出アドレスジャンプ処理手順について図18のフローチャートを用いて具体的に説明する。50

**【0086】**

実際に、オーディオ入出力制御装置1の制御部4は、ルーチンR T 3の開始ステップから入ってステップS P 2 1へ移り、リングバッファ10から読み出すべき現時点における読み出アドレスに「1」を加算することにより次の読み出アドレスへ移行し、次のステップS P 2 2へ移る。

**【0087】**

ステップS P 2 2において制御部4は、次の読み出アドレスに相当するリングバッファ10のスロットに書き込まれているオーディオデータD 1のヘッダを参照し、当該ヘッダの「zcFlag1」又は「zcFlag0」のフラグ情報として「1」がセットされているか否かを判定する。

10

**【0088】**

ここで肯定結果を得られると、このことは「zcFlag1」又は「zcFlag0」のフラグ情報として「1」がセットされていること、すなわち次の読み出アドレスから読み出すべきオーディオデータD 1がゼロクロス直前又はゼロクロス直後のデータであることを表しており、このとき制御部4は次のステップS P 2 3へ移る。

**【0089】**

ステップS P 2 3において制御部4は、ライトスピード検出器8により読み出アドレスと書込アドレスとの差分値kを算出し、その差分値kが256(スロット)未満であるか、差分値kが1024(スロット)よりも大きいか、或いは差分値kが256(スロット)以上1024(スロット)以下の範囲であるかを判定する。

20

**【0090】**

ここで図19に示すように、差分値kが1024(スロット)よりも大きい場合、このことは読み出アドレスが書込アドレスに追い付かれるまでには相当の時間的余裕があることを表しており、このとき制御部4はステップS P 3 2へ移って読み出アドレスジャンプ処理を行うことなく終了する。

**【0091】**

また差分値kが256(スロット)以上1024(スロット)以下の範囲である場合、このことは読み出アドレスに書込アドレスが次第に追い付いており、読み出アドレスと書込アドレスとの差が初期ディレイの一定範囲(例えば1024スロット±100スロット)から外れる可能性が出てきたことを表しており、このとき制御部4は次のステップS P 2 4へ移る。

30

**【0092】**

ステップS P 2 4において制御部4は、読み出アドレスをアドレスジャンプさせる際に、オーディオデータD 1の信号レベル変化が少ないゼロクロス近傍で、かつ読み出アドレスから近い先に位置するアドレスジャンプ予定の読み出アドレスをフォワードゼロクロスアドレスとし、当該フォワードゼロクロスアドレスと読み出アドレスとの差f kを算出する。

**【0093】**

そして制御部4は、その差f kが1024(スロット)以上の場合、フォワードゼロクロスアドレスへ読み出アドレスをアドレスジャンプさせてしまうと、初期ディレイの一定範囲(例えば1024スロット±100スロット)から外れる可能性が高いのでステップS P 3 2へ移って読み出アドレスジャンプ処理を行うことなく終了する。

40

**【0094】**

一方、制御部4は差f kが1024(スロット)よりも小さい場合、フォワードゼロクロスアドレスへ読み出アドレスをアドレスジャンプさせても、初期ディレイの一定範囲(例えば1024スロット±100スロット)に収まる可能性が高いので読み出アドレスジャンプ処理を行なべく次のステップS P 2 6へ移る。

**【0095】**

ステップS P 2 3において差分値kが256(スロット)よりも小さい場合、このことは読み出アドレスが書込アドレスに追い付かれる直前の状態にあることを表しており、このとき制御部4は次のステップS P 2 5へ移る。

50

**【 0 0 9 6 】**

ステップ S P 2 5において制御部 4は、読出アドレスをアドレスジャンプさせる際に、オーディオデータ D 1の信号レベル変化が少ないゼロクロス近傍で、かつ読出アドレスから遠い先に位置するアドレスジャンプ予定の読出アドレスをモアフォワードゼロクロスアドレスとし、読出アドレスと当該モアフォワードゼロクロスアドレスとの差 $m_k$ を算出する。

**【 0 0 9 7 】**

そして制御部 4は、その差 $m_k$ が 1 0 2 4 (スロット) 以上の場合、モアフォワードゼロクロスアドレスへ読出アドレスをアドレスジャンプさせてしまうと、初期ディレイの一定範囲(例えば 1 0 2 4 スロット ± 1 0 0 スロット)から外れる可能性が高いのでステップ S P 3 2へ移って読出アドレスジャンプ処理を行うことなく終了する。 10

**【 0 0 9 8 】**

一方、制御部 4は差 $m_k$ が 1 0 2 4 (スロット) よりも小さい場合、モアフォワードゼロクロスアドレスへ読出アドレスをアドレスジャンプさせても、初期ディレイの一定範囲(例えば 1 0 2 4 スロット ± 1 0 0 スロット)に収まる可能性が高いので読出アドレスジャンプ処理を行うべく次のステップ S P 2 6へ移る。

**【 0 0 9 9 】**

ステップ S P 2 6において制御部 4は、読出アドレスをフォワードゼロクロスアドレス若しくはモアフォワードゼロクロスアドレスへアドレスジャンプさせることによりオーディオデータ D 1をデータ間引きして読出アドレスが書込アドレスに追い付かれることを予め防止すると共に、アドレスジャンプ前に読み出したオーディオデータ D 1とアドレスジャンプ後に読み出すオーディオデータ D 1との連続性を保持し、次のステップ S P 3 2へ移って処理を終了する。 20

**【 0 1 0 0 】**

これに対してステップ S P 2 2で否定結果が得られると、このことは「zcFlag1」又は「zcFlag0」のフラグ情報として「0」がセットされていること、すなわちゼロクロスとは無関係のオーディオデータ D 1であることを表しており、このとき制御部 4は次のステップ S P 2 7へ移る。

**【 0 1 0 1 】**

ここで制御部 4は、例えオーディオデータ D 1がゼロクロスとは無関係であっても当該オーディオデータ D 1に直流成分が重畠しているためにゼロクロスを検出できていない可能性もあるため、次のステップ S P 2 7以降の処理へ移るようになされている。 30

**【 0 1 0 2 】**

ステップ S P 2 7において制御部 4は、当該オーディオデータ D 1のヘッダを参照し、当該ヘッダの「オフセットzcFlag1」又は「オフセットzcFlag0」のフラグ情報として「1」がセットされているか否かを判定する。

**【 0 1 0 3 】**

ここで否定結果が得られると、このことは「zcFlag1」又は「zcFlag0」と、「オフセットzcFlag1」又は「オフセットzcFlag0」のフラグ情報として何れも「0」がセットされていること、すなわち直流成分が重畠していないオーディオデータ D 1及び直流成分が重畠しているオーディオデータ D 1の双方共にゼロクロスしていないため、読出アドレスジャンプ処理を行うタイミングではないことを表しており、このとき制御部 4はステップ S P 3 2へ移って処理を終了する。 40

**【 0 1 0 4 】**

一方ステップ S P 2 7で肯定結果が得られると、このことは直流成分が重畠しているオーディオデータ D 1について、直流成分が除去されたオーディオデータ D 1として考えた場合にバーチャルゼロクロス(図 1 3)を検出し得たことを表しており、このとき制御部 4は次のステップ S P 2 8へ移る。

**【 0 1 0 5 】**

ステップ S P 2 8において制御部 4は、ライトスピード検出器 8により読出アドレスと 50

書込アドレスとの差分値  $k$  を算出し、その差分値  $k$  が 256 (スロット) 未満であるか、差分値  $k$  が 1024 (スロット) よりも大きいか、或いは差分値  $k$  が 256 (スロット) 以上 1024 (スロット) 以下の範囲であるかを判定する。

#### 【0106】

ここで差分値  $k$  が 1024 (スロット) よりも大きい場合、このことは読出アドレスが書込アドレスに追い付かれるまでには相当の時間的余裕があることを表しており、このとき制御部 4 は上述のステップ SP23 と同様にステップ SP32 へ移って読出アドレスジャンプ処理を行うことなく終了する。

#### 【0107】

また差分値  $k$  が 256 (スロット) 以上 1024 (スロット) 以下の範囲である場合、このことは読出アドレスに書込アドレスが追い付いており、読出アドレスと書込アドレスとの差が初期ディレイの一定範囲（例えば 1024 スロット ± 100 スロット）から外れる可能性があることを表しており、このとき制御部 4 は次のステップ SP29 へ移る。

。

#### 【0108】

ステップ SP29において制御部 4 は、読出アドレスをアドレスジャンプさせる際に、オーディオデータ D1 の信号レベル変化が少ないゼロクロス近傍で、かつ読出アドレスから近い先に位置するアドレスジャンプ予定の読出アドレスをフォワードオフセットゼロクロスアドレスとし、当該フォワードオフセットゼロクロスアドレスと現時点の読出アドレスとの差  $f_{ok}$  を算出する。

#### 【0109】

そして制御部 4 は、その差  $f_{ok}$  が 1024 (スロット) 以上の場合、フォワードオフセットゼロクロスアドレスへ読出アドレスをアドレスジャンプさせてしまうと、初期ディレイの一定範囲（例えば 1024 スロット ± 100 スロット）から外れる可能性が高いのでステップ SP32 へ移って読出アドレスジャンプ処理を行うことなく終了する。

#### 【0110】

一方、制御部 4 は差  $f_{ok}$  が 1024 (スロット) よりも小さい場合、フォワードオフセットゼロクロスアドレスへ読出アドレスをアドレスジャンプさせても、初期ディレイの一定範囲（例えば 1024 スロット ± 100 スロット）に収まる可能性が高いので読出アドレスジャンプ処理を行うべく次のステップ SP30 へ移る。

#### 【0111】

さらにステップ SP28 における差分値  $k$  が 256 (スロット) よりも小さい場合、このことは読出アドレスが書込アドレスに追い付かれる直前の状態にあることを表しており、このとき制御部 4 は次のステップ SP31 へ移る。

#### 【0112】

ステップ SP31 において制御部 4 は、読出アドレスをアドレスジャンプさせる際に、オーディオデータ D1 の信号レベルの変化が少ないゼロクロス近傍で、かつ読出アドレスから遠い先に位置するアドレスジャンプ予定の読出アドレスをモアフォワードオフセットゼロクロスアドレスとし、当該モアフォワードオフセットゼロクロスアドレスと現時点の読出アドレスとの差  $m_{ok}$  を算出する。

#### 【0113】

そして制御部 4 は、その差  $m_{ok}$  が 1024 (スロット) 以上の場合、モアフォワードオフセットゼロクロスアドレスへ読出アドレスをアドレスジャンプさせてしまうと、初期ディレイの一定範囲（例えば 1024 スロット ± 100 スロット）から外れる可能性が高いのでステップ SP32 へ移って読出アドレスジャンプ処理を行うことなく終了する。

#### 【0114】

一方、制御部 4 は差  $m_{ok}$  が 1024 (スロット) よりも小さい場合、モアフォワードゼロクロスアドレスへ読出アドレスをアドレスジャンプさせても、初期ディレイの一定範囲（例えば 1024 スロット ± 100 スロット）に収まる可能性が高いので読出アドレスジャンプ処理を行うべく次のステップ SP30 へ移る。

10

20

30

40

50

## 【0115】

ステップSP30において制御部4は、読出アドレスをフォワードオフセットゼロクロスアドレス若しくはモアフォワードオフセットゼロクロスアドレスへアドレスジャンプさせることにより直流成分が重畠しているオーディオデータD1をデータ間引きして読出アドレスが書込アドレスに追い付かれることを予め防止すると共に、アドレスジャンプ前に読み出した直流成分が重畠しているオーディオデータD1とアドレスジャンプ後に読み出す直流成分が重畠しているオーディオデータD1との連続性を保持し、次のステップSP32へ移って処理を終了する。

## 【0116】

(3-2) 読出速度が書込速度よりも速い場合の読出アドレスジャンプ処理手順 10

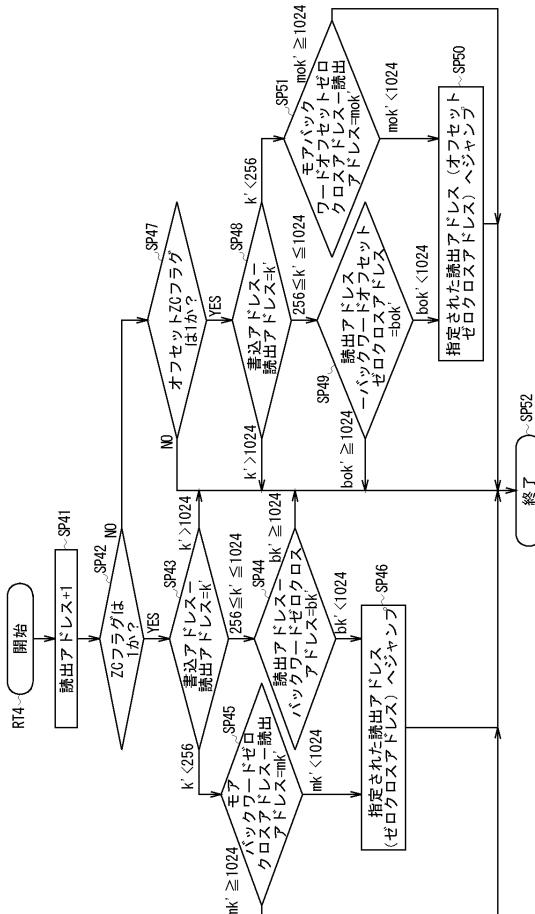

オーディオ入出力制御装置1の制御部4は、アプリケーションプログラムであるアドレスジャンプ処理プログラムに従い、ビデオテープレコーダのプログラムプレイ機能が動作する際にビデオの变速再生処理に応じてオーディオデータD1の読出速度が書込速度よりも速い場合にオーディオの音程変化を起こさせることなく、かつオーディオの連続性を維持するための読出アドレスジャンプ処理手順について図20のフローチャートを用いて具体的に説明する。

## 【0117】

実際に、オーディオ入出力制御装置1の制御部4は、ルーチンRT4の開始ステップから入ってステップSP41へ移り、リングバッファ10から読み出すべき現時点における読出アドレスに「1」を加算することにより次の読出アドレスへ移行し、次のステップSP42へ移る。 20

## 【0118】

ステップSP42において制御部4は、次の読出アドレスに相当するリングバッファ10のスロットに書き込まれているオーディオデータD1のヘッダを参照し、当該ヘッダの「zcFlag1」又は「zcFlag0」のフラグ情報として「1」がセットされているか否かを判定する。

## 【0119】

ここで肯定結果を得られると、このことは「zcFlag1」又は「zcFlag0」のフラグ情報として「1」がセットされていること、すなわち次の読出アドレスから読み出すべきオーディオデータD1がゼロクロス直前又はゼロクロス直後のデータであることを表しており、このとき制御部4は次のステップSP43へ移る。 30

## 【0120】

ステップSP43において制御部4は、ライトスピード検出器8により書込アドレスと読出アドレスとの差分値 $k'$ を算出し、その差分値 $k'$ が256(スロット)未満であるか、差分値 $k'$ が1024(スロット)よりも大きいか、或いは差分 $k$ が256(スロット)以上1024(スロット)以下の範囲であるかを判定する。

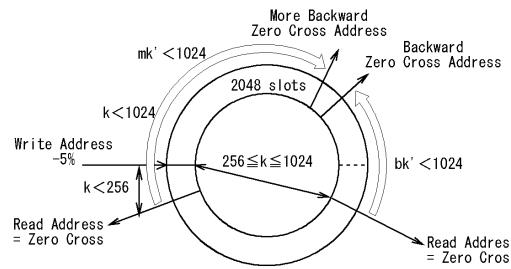

## 【0121】

ここで図21に示すように、差分値 $k'$ が1024(スロット)よりも大きい場合、このことは書込アドレスが読出アドレスに追い付かれるまでには相当の時間的余裕があることを表しており、このとき制御部4はステップSP52へ移って読出アドレスジャンプ処理を行うことなく終了する。 40

## 【0122】

また差分値 $k'$ が256(スロット)以上1024(スロット)以下の範囲である場合、このことは書込アドレスに読出アドレスが次第に追い付いてきており、書込アドレスと読出アドレスとの差が初期ディレイの一定範囲(例えば1024スロット±100スロット)から外れる可能性が出てきたことを表しており、このとき制御部4は次のステップSP44へ移る。

## 【0123】

ステップSP44において制御部4は、読出アドレスをアドレスジャンプさせる際に、オーディオデータD1の信号レベル変化が少ないゼロクロス近傍で、かつ読出アドレスか 50

ら少し戻した先に位置するアドレスジャンプ予定の読み出アドレスをバックワードゼロクロスアドレスとし、読み出アドレスと当該バックワードゼロクロスアドレスとの差  $b_k'$  を算出する。

#### 【0124】

そして制御部4は、その差  $b_k'$  が1024（スロット）以上の場合、バックワードゼロクロスアドレスへ読み出アドレスをアドレスジャンプさせてしまうと、初期ディレイの一定範囲（例えば1024スロット±100スロット）から外れる可能性が高いので、ステップSP52へ移って読み出アドレスジャンプ処理を行うことなく終了する。

#### 【0125】

一方、制御部4は差  $b_k'$  が1024（スロット）よりも小さい場合、バックワードゼロクロスアドレスへ読み出アドレスをアドレスジャンプさせても、初期ディレイの一定範囲（例えば1024スロット±100スロット）に収まる可能性が高いので読み出アドレスジャンプ処理を行うべく次のステップSP46へ移る。

#### 【0126】

さらにステップSP43における差分値  $k'$  が256（スロット）よりも小さい場合、このことは書込アドレスが読み出アドレスに追い付かれる直前の状態にあることを表しており、このとき制御部4は次のステップSP45へ移る。

#### 【0127】

ステップSP45において制御部4は、読み出アドレスをアドレスジャンプさせる際に、オーディオデータD1の信号レベルの変化が少ないゼロクロス近傍で、かつ読み出アドレスから大きく戻した先に位置するアドレスジャンプ予定の読み出アドレスをモアバックワードゼロクロスアドレスとし、当該モアバックワードゼロクロスアドレスと読み出アドレスとの差  $m_k'$  を算出する。

#### 【0128】

そして制御部4は、その差  $m_k'$  が1024（スロット）以上の場合、モアバックワードゼロクロスアドレスへ読み出アドレスをアドレスジャンプさせてしまうと、初期ディレイの一定範囲（例えば1024スロット±100スロット）から外れる可能性が高いのでステップSP52へ移って読み出アドレスジャンプ処理を行うことなく終了する。

#### 【0129】

一方、制御部4は差  $m_k'$  が1024（スロット）よりも小さい場合、モアバックワードゼロクロスアドレスへ読み出アドレスをアドレスジャンプさせても、初期ディレイの一定範囲（例えば1024スロット±100スロット）に収まる可能性が高いので読み出アドレスジャンプ処理を行うべく次のステップSP46へ移る。

#### 【0130】

ステップSP46において制御部4は、読み出アドレスをバックワードゼロクロスアドレス若しくはモアバックワードゼロクロスアドレスへアドレスジャンプさせることにより、同一のオーディオデータD1を再度読み出しながらデータ補間して書込アドレスが読み出アドレスに追い付かれることを予め防止すると共にし、アドレスジャンプ前に読み出したオーディオデータD1とアドレスジャンプ後に読み出すオーディオデータD1との連続性を保持し、次のステップSP52へ移って処理を終了する。

#### 【0131】

これに対してステップSP42で否定結果が得られると、このことは「zcFlag1」又は「zcFlag0」のフラグ情報として「0」がセットされていること、すなわちゼロクロスとは無関係のオーディオデータD1であることを表しており、このとき制御部4は次のステップSP47へ移る。

#### 【0132】

ここで制御部4は、例えオーディオデータD1がゼロクロスとは無関係であっても当該オーディオデータD1に直流成分が重畠しているためにゼロクロスを検出できていない可能性もあるため、次のステップSP47以降の処理へ移るようになされている。

#### 【0133】

10

20

30

40

50

ステップSP47において制御部4は、当該オーディオデータD1のヘッダを参照し、当該ヘッダの「オフセットzcFlag1」又は「オフセットzcFlag0」のフラグ情報として「1」がセットされているか否かを判定する。

#### 【0134】

ここで否定結果が得られると、このことは「zcFlag1」又は「zcFlag0」と、「オフセットzcFlag1」又は「オフセットzcFlag0」のフラグ情報として何れも「0」がセットされていること、すなわち直流成分が重畠していないオーディオデータD1及び直流成分が重畠しているオーディオデータD1の双方共にゼロクロスしていないため、読み出アドレスジャンプ処理を行うタイミングではないことを表しており、このとき制御部4はステップSP52へ移って処理を終了する。 10

#### 【0135】

一方ステップSP47で肯定結果が得られると、このことは直流成分が重畠しているオーディオデータD1について、直流成分が除去されたオーディオデータD1として考えた場合にバーチャルゼロクロスを検出し得たことを表しており、このとき制御部4は次のステップSP48へ移る。 20

#### 【0136】

ステップSP48において制御部4は、ライトスピード検出器8により書き込みアドレスと読み出アドレスとの差分値 $k'$ を算出し、その差分値 $k'$ が256(スロット)未満であるか、差分値 $k'$ が1024(スロット)よりも大きいか、或いは差分値 $k'$ が256(スロット)以上1024(スロット)以下の範囲であるかを判定する。 20

#### 【0137】

ここで差分値 $k'$ が1024(スロット)よりも大きい場合、このことは書き込みアドレスが読み出アドレスに追い付かれるまでには相当の余裕があることを表しており、このとき制御部4は上述のステップSP43と同様にステップSP52へ移って読み出アドレスジャンプ処理を行うことなく終了する。 30

#### 【0138】

またステップSP48における差分値 $k'$ が256(スロット)以上1024(スロット)以下の範囲である場合、このことは書き込みアドレスに読み出アドレスが追い付いており、書き込みアドレスと読み出アドレスとの差が初期ディレイの一定範囲(例えば1024スロット±100スロット)から外れる可能性が出てきたことを表しており、このとき制御部4は次のステップSP49へ移る。 30

#### 【0139】

ステップSP49において制御部4は、読み出アドレスをアドレスジャンプさせる際に、オーディオデータD1の信号レベルの変化が少ないゼロクロス近傍で、かつ読み出アドレスから少し戻した先に位置するアドレスジャンプ予定の読み出アドレスをバックワードオフセットゼロクロスアドレスとし、読み出アドレスと当該バックワードオフセットゼロクロスアドレスとの差 $bok'$ を算出する。 40

#### 【0140】

そして制御部4は、その差 $bok'$ が1024(スロット)以上の場合、バックワードオフセットゼロクロスアドレスへ読み出アドレスをアドレスジャンプさせてしまうと、初期ディレイの一定範囲(例えば1024スロット±100スロット)から外れる可能性が高いのでステップSP52へ移って読み出アドレスジャンプ処理を行うことなく終了する。 40

#### 【0141】

一方、制御部4は差 $bok'$ が1024(スロット)よりも小さい場合、バックワードゼロクロスアドレスへ読み出アドレスをアドレスジャンプさせても、初期ディレイの一定範囲(例えば1024スロット±100スロット)に収まる可能性が高いので読み出アドレスジャンプ処理を行うべく次のステップSP50へ移る。

#### 【0142】

さらにステップSP48における差分値 $k'$ が256(スロット)よりも小さい場合、このことは書き込みアドレスが読み出アドレスに追い付かれる直前の状態にあることを表してお 50

り、このとき制御部4は次のステップSP51へ移る。

**【0143】**

ステップSP51において制御部4は、読出アドレスをアドレスジャンプさせる際に、オーディオデータD1の信号レベルの変化が少ないゼロクロス近傍で、かつ読出アドレスから遠く戻す先に位置するアドレスジャンプ予定の読出アドレスをモアバックワードオフセットゼロクロスアドレスとし、当該モアバックワードオフセットゼロクロスアドレスと読出アドレスとの差 $mok'$ を算出する。

**【0144】**

そして制御部4は、その差 $mok'$ が1024(スロット)以上の場合、モアバックワードオフセットゼロクロスアドレスへ読出アドレスをアドレスジャンプさせてしまうと、初期ディレイの一定範囲(例えば1024スロット±100スロット)から外れる可能性が高いのでステップSP52へ移って読出アドレスジャンプ処理を行うことなく終了する。

10

**【0145】**

一方、制御部4は差 $mok'$ が1024(スロット)よりも小さい場合、モアバックワードゼロクロスアドレスへ読出アドレスをアドレスジャンプさせても、初期ディレイの一定範囲(例えば1024スロット±100スロット)に収まる可能性が高いので読出アドレスジャンプ処理を行うべく次のステップSP50へ移る。

**【0146】**

ステップSP50において制御部4は、読出アドレスをバックワードオフセットゼロクロスアドレス若しくはモアバックワードオフセットゼロクロスアドレスへアドレスジャンプさせることにより、直流成分が重畠しているオーディオデータD1を再度読み出しながらデータ補間して書込アドレスが読出アドレスに追い付かれることを予め防止すると共に、アドレスジャンプ前に読み出した直流成分が重畠しているオーディオデータD1とアドレスジャンプ後に読み出す直流成分が重畠しているオーディオデータD1との連続性を保持し、次のステップSP52へ移って処理を終了する。

20

**【0147】**

(4) 動作及び効果

以上の構成において、オーディオ入出力制御装置1の制御部4は、リングバッファ10にオーディオデータD1を書込速度48[kHz]±5%で書き込み、当該リングバッファ10から一定の読み出し速度48[kHz]で読み出す際、書込速度と読み出し速度との速度差を検出し、当該検出した速度差に応じて書込アドレスが読み出アドレスを追い越したり、読み出アドレスが書込アドレスを追い越すことがないように、読み出アドレスを強制的にアドレスジャンプさせる。

30

**【0148】**

このときオーディオ入出力制御装置1の制御部4は、ゼロクロス直前の読み出アドレスと、ゼロクロス直後の読み出アドレスとを結ぶようにアドレスジャンプさせることにより、アドレスジャンプ前の読み出アドレスに対応したオーディオデータD1と、アドレスジャンプ後の読み出アドレスに対応したオーディオデータD1との間で信号レベルの変化を極力少なくすることができるため、実際上アドレスジャンプによってオーディオデータD1の連続性が途切れても、ユーザの聴感的にはオーディオデータD1の連続性を維持しているかのような印象を与え、かつ音程変化のない音声を出力することができる。

40

**【0149】**

またオーディオ入出力制御装置1の制御部4は、読み出アドレスをアドレスジャンプさせることにより、当該読み出アドレスを先に進ませる場合には当該オーディオデータD1をデータ間引きすることになり、当該読み出アドレスを後ろに戻す場合には同じオーディオデータD1を再度読み出してデータ補間することになるため、変速再生処理したビデオに対してオーディオを時間的に合わせることができる。

**【0150】**

このようにオーディオ入出力制御装置1の制御部4は、読み出アドレスのアドレスジャン

50

プを行うだけで上述の効果を奏するようになされており、かくして多くの加算や乗算等の演算が必要なクロスフェード処理を行う場合と比較して格段に信号処理量を低減することができる。

#### 【0151】

さらにオーディオ入出力制御装置1の制御部4は、読出アドレスと書込アドレスとの差として1024スロット±100スロット程度の一定範囲からなる初期ディレイを保持するように制御していることにより、書込アドレスが読出アドレスを追い越したり、読出アドレスが書込アドレスを追い越すといったリスクを予め回避することができる。

#### 【0152】

以上の構成によれば、オーディオ入出力制御装置1の制御部4は、ビデオテープレコーダがプログラムプレイ機能を動作させ、ビデオの变速再生処理に合わせて音程を変化させることなく音声を出力する場合、信号処理量を大幅に低減しつつ当該オーディオデータD1の品位についても保持することができる。10

#### 【0153】

##### (5) 他の実施の形態

なお上述の実施の形態においては、2048スロットのリングバッファ10を用いるようにした場合について述べたが、本発明はこれに限らず、オーディオの品位を考慮して4096スロットのリングバッファを用いたり、初期ディレイを少なくする点を考慮して1048スロットのリングバッファを用いるようにしても良い。

#### 【0154】

また上述の実施の形態においては、オフセット検出器5として、リングバッファ10の2048スロットに順次書き込むオーディオデータD1の信号レベルの合計値を2048で除算することにより平均値を算出し、当該平均値を直流成分のオフセット量として検出するようにした場合について述べたが、本発明はこれに限らず、オーディオデータD1の最大値と最小値の中間値を直流成分のオフセット量として検出するようにしても良い。20

#### 【0155】

さらに上述の実施の形態においては、オーディオデータD1を書込速度48[kHz]±5%でスロット毎に書き込む場合に本発明を適用するようにした場合について述べたが、本発明はこれに限らず、オーディオデータD1のリングバッファ10に対する書込速度が48[kHz]±5%に固定されるのではなく変動する場合に本発明を適用するようにしても良い。30

#### 【0156】

さらに上述の実施の形態においては、プログラムプレイ機能を動作させる際にビデオの变速再生処理に合わせてオーディオデータD1の入出力を制御するようにした場合について述べたが、本発明はこれに限らず、ビデオの变速再生処理とは無関係にオーディオデータD1の入出力を制御するようにしても良い。

#### 【0157】

さらに上述の実施の形態においては、本発明の入出力制御装置1をビデオテープレコーダに搭載するようにした場合について述べたが、本発明はこれに限らず、ビデオ編集装置やボイスレコーダ、オーディオ録音装置、パーソナルコンピュータ、ハードディスクレコーダ又は携帯電話機等のその他種々の電子機器に搭載するようにしても良い。40

#### 【0158】

さらに上述の実施の形態においては、本発明のオーディオ入出力制御装置をメモリとしてのリングバッファ10、アドレス変更手段及び読出アドレス決定手段としての制御部4によって構成するようにした場合について述べたが、本発明はこれに限らず、その他種々の構成でなるメモリ、アドレス変更手段及び読出アドレス決定手段によってオーディオ入出力制御装置を構成するようにしても良い。

#### 【産業上の利用可能性】

#### 【0159】

本発明のオーディオ入出力制御装置及びオーディオ入出力制御方法は、例えばオーディ50

オーディオを高品位のまま時間伸張又は時間圧縮する用途に適用することができる。

【図面の簡単な説明】

【0160】

【図1】リングバッファ上における書込データと読出データの位置関係を示す略線図である。

【図2】読出データが書込データを追い越す様子を示す略線図である。

【図3】書込データが読出データを追い越す様子を示す略線図である。

【図4】クロスフェード処理の説明に供する略線図である。

【図5】書込アドレスが読出アドレスを追い越すときのクロスフェード処理の説明に供する略線図である。 10

【図6】読出アドレスが書込アドレスを追い越すときのクロスフェード処理の説明に供する略線図である。

【図7】読出アドレスジャンプ処理の説明に供する略線図である。

【図8】ゼロクロスを用いた読出アドレスジャンプ処理の説明に供する略線図である。

【図9】書込速度が読出速度よりも速い場合のディレイ量の変化を示す略線図である。

【図10】読出速度が書込速度よりも速い場合のディレイ量の変化を示す略線図である。

【図11】読出アドレスのジャンプタイミングを示す略線図である。

【図12】オーディオデータのデータ構造を示す略線図である。

【図13】直流成分が重畠したオーディオデータの波形を示す略線図である。

【図14】オーディオ入出力制御装置の回路構成を示す略線的ブロック図である。 20

【図15】ローレベル検出処理手順の説明に供するフローチャートである。

【図16】ゼロクロス検出処理手順の説明に供するフローチャートである。

【図17】オフセット検出器の構成を示す略線図である。

【図18】書込速度が読出速度よりも速い場合の読出アドレスジャンプ処理手順を示すフローチャートである。

【図19】読出速度が書込速度よりも速い場合の読出アドレスジャンプ処理手順を示すフローチャートである。

【図20】書込速度が読出速度よりも速い場合のアドレスジャンプイメージを示す略線図である。 30

【図21】読出速度が書込速度よりも速い場合のアドレスジャンプイメージを示す略線図である。

【符号の説明】

【0161】

1 …… オーディオ入出力制御装置、 2 …… ローレベル検出器、 3 …… ゼロクロス検出器

、 4 …… 制御部、 5 …… オフセット検出器、 6 …… ライトアドレスジェネレータ、 7 ……

リードアドレスジェネレータ、 8 …… ライトスピード検出器、 10 …… リングバッファ。

【図1】

【図2】

図2 読出データが書込データを追い越す様子

【図3】

図3 書込データが読出データを追い越す様子

【図4】

図4 クロスフェード処理

【図5】

図5 書込アドレスが読出アドレスを追い越すときのクロスフェード処理

【図6】

図6 読出アドレスが書込アドレスを追い越すときのクロスフェード処理

【図7】

図7 読出アドレスジャンプ処理

【図8】

図8 ゼロクロスを用いた読出アドレスジャンプ処理

【図 9】

図 9 書込速度が読出速度より速い場合のディレイ量の変化

【図 10】

図 10 読出速度が書込速度より速い場合のディレイ量の変化

【図 11】

(A) 書込速度が読出速度よりも速い場合

(B) 読出速度が書込速度よりも速い場合

図 11 読出アドレスのジャンプタイミング

【図 12】

図 12 オーディオデータのデータ構造

【図 1 3】

図 1 3 直流成分が重畠したオーディオデータの波形

【図 1 4】

図 1 4 オーディオ入出力制御装置

【図 1 5】

図 1 5 ローレベル検出処理手順

【図 1 6】

図 1 6 ゼロクロス検出処理手順

【図 17】

図 17 オフセット検出器の構成

【図 19】

図 19 書込速度が読出速度より速い場合のアドレスジャンプイメージ

【図 18】

図 18 書込速度が読出速度より速い場合の読み出アドレスジャンプ処理手順

【図 20】

図 20 読出速度が書込速度より速い場合の読み出アドレスジャンプ処理手順

【図21】

図21 読出速度が書き込み速度より速い場合のアドレスジャンプイメージ

---

フロントページの続き

(56)参考文献 特開昭61-075396(JP,A)

特開2001-223994(JP,A)

特開2002-232846(JP,A)

特開平08-083096(JP,A)

特開2000-138591(JP,A)

特開平08-202391(JP,A)

(58)調査した分野(Int.Cl., DB名)

G10L 19/00-21/04

G11B 20/10

JSTPlus (JDreamII)