(12)

## Patentschrift

(21) Aktenzeichen: 102 62 374.0

(51) Int Cl.: G11C 5/14 (2006.01)

(22) Anmeldetag: 08.02.2002

(45) Veröffentlichungstag

der Patenterteilung: 15.05.2014

Innerhalb von neun Monaten nach Veröffentlichung der Patenterteilung kann nach § 59 Patentgesetz gegen das Patent Einspruch erhoben werden. Der Einspruch ist schriftlich zu erklären und zu begründen. Innerhalb der Einspruchsfrist ist eine Einspruchsgebühr in Höhe von 200 Euro zu entrichten (§ 6 Patentkostengesetz in Verbindung mit der Anlage zu § 2 Abs. 1 Patentkostengesetz).

(30) Unionspriorität:

**09/788,120**

**16.02.2001 US**

(62) Teilung aus:

**102 96 285.5**

(73) Patentinhaber:

**SanDisk Corp., Sunnyvale, Calif., US**

(74) Vertreter:

**Schoppe, Zimmermann, Stöckeler, Zinkler & Partner, 82049, Pullach, DE**

(72) Erfinder:

**Gongwer, Geoffrey Steven, Los Altos, Calif., US;

Cerneia, Raul Adrian, Santa Clara, Calif., US;

Wang, Yongliang, Saratoga, Calif., US; Wang, Chi-Ming, Fremont, Calif., US; Conley, Kevin M., San Jose, Calif., US**

(56) Ermittelter Stand der Technik:

**US 6 079 023 A

US 6 009 034 A

US 5 621 685 A**

(54) Bezeichnung: **System zur Erzeugung und Verteilung von Versorgungsspannungen in Speichersystemen**

(57) Zusammenfassung: Ein Speichersystem, das eine externe Versorgungsspannung von einem Host empfängt, umfasst eine Mehrzahl von Speicherchips, wobei jeder der Speicherchips zumindest eine Mehrzahl von Datenspeicher-elementen umfasst, wobei zumindest einer der Speicherchips ferner zumindest eine erste Spannungserzeugungsschaltung umfasst, die betreibbar ist, um zumindest eine im Speicher erzeugte Versorgungsspannung zu erzeugen; eine Speichersteuerung, die wirksam gekoppelt ist, um auf die Speicherchips zuzugreifen; und einen Leistungsbus, der mit jedem der Speicherchips gekoppelt ist, wobei der Leistungsbus die zumindest eine im Speicher erzeugte Versorgungsspannung an die Speicherchips liefert, wobei die im Speicher erzeugte Versorgungsspannung ferner an die Speichersteuerung geliefert wird.

## Beschreibung

**[0001]** Die Erfindung bezieht sich auf eine Spannungserzeugung und insbesondere auf eine Spannungserzeugung, die innerhalb von Speichersystemen stattfindet.

**[0002]** Speicherkarten werden üblicherweise verwendet, um digitale Daten zur Verwendung bei verschiedenen Produkten (z. B. Elektronikprodukten) zu speichern. Beispiele von Speicherkarten sind Flash-Karten, die Speicherzellen vom Flash-Typ oder EEPROM-Typ verwenden, um die Daten zu speichern. Flash-Karten weisen einen relativ geringen Formfaktor auf und werden bisher verwendet, um digitale Daten für Produkte wie beispielsweise Kameras, in der Hand zu haltende Computer, Set-Top-Boxen, in der Hand zu haltende oder andere kleine Audiowiedergabe-Geräte/-aufzeichnungsgeräte (z. B. MP3-Vorrichtungen) und medizinische Überwachungsgeräte zu speichern. Ein wichtiger Lieferant von Flash-Karten ist SanDisk Corporation, Sunnyvale, CA, USA.

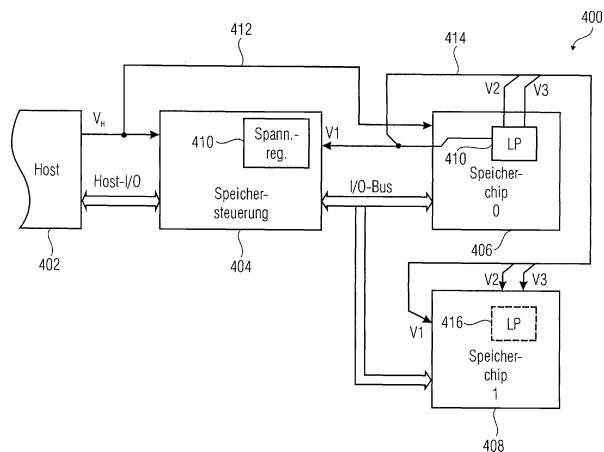

**[0003]** Fig. 1 ist ein Blockdiagramm eines herkömmlichen Speichersystems **100**. Das herkömmliche Speichersystem **100** liefert eine nicht-flüchtige Datenspeicherung und stellt beispielsweise eine Speicherplatte (z. B. Flash-Karte) dar. Das herkömmliche Speichersystem **100** ist mit einem Host **102** gekoppelt. Der Host **102** kann beispielsweise ein Personal-Computer oder ein elektronisches Gerät sein. Das Speichersystem **100** umfasst eine Speichersteuerung **104** und Speicherchips **106** und **108**. Die Speichersteuerung **104** umfasst einen Spannungsregler **110**. Ein Host-Eingabe/Ausgabe-Bus (Host-I/O-Bus) koppelt die Speichersteuerung **104** mit dem Host **102**. Der Host **102** liefert außerdem der Speichersteuerung **104** eine Versorgungsspannung  $V_{DD}$ . Der Spannungsregler **110** in der Speichersteuerung **104** empfängt die Versorgungsspannung  $V_{DD}$  und regelt die Versorgungsspannung, um eine geregelte Versorgungsspannung  $V_{DDR}$  zu erzeugen. Die geregelte Versorgungsspannung  $V_{DDR}$  wird an jeden der Speicherchips **106** und **108** geliefert. Die geregelte Versorgungsspannung  $V_{DDR}$  ist ein feststehender Spannungspegel (in der Regel innerhalb eines Toleranzbereichs), der den Speicherchips **106** und **108** geliefert wird. Bei diesem Beispiel erfordern die Speicherchips **106** und **108**, dass die Versorgungsspannung, die an die Speicherchips **106** und **108** geliefert wird, einen bestimmten Spannungspegel aufweist. Da das Speichersystem **100** mit diversen unterschiedlichen Hosts gekoppelt ist, kann die Versorgungsspannung  $V_{DD}$  über verschiedene Spannungsbreiten variieren, beispielsweise 1,8 Volt, 3,3 Volt oder 5 Volt. Es ist jedoch typisch, dass aktuelle Speicherchips erfordern, dass die Spannung 3,3 Volt betrage. Der Spannungsregler **110** gewährleistet, dass die geregelte Versorgungsspannung  $V_{DDR}$  unabhängig von dem Pegel der Versorgungspan-

nung  $V_{DD}$  auf einen bestimmten Spannungspegel (z. B. 3,3 Volt) eingestellt ist.

**[0004]** In jedem Fall erfordern die Speicherchips **106** und **108** für ihren Betrieb diverse andere Versorgungsspannungspegel als den bestimmten Spannungspegel (d. h.  $V_{DDR}$ ), der von der Speichersteuerung **104** empfangen wird. Somit umfassen die Speicherchips **106** und **108** Ladungspumpenschaltungen **112** bzw. **114**. Die Ladungspumpenschaltungen **112** und **114** empfangen die geregelte Versorgungsspannung  $V_{DDR}$  und erzeugen unabhängig und intern zusätzliche Versorgungsspannungspegel zur internen Verwendung durch ihren zugeordneten Speicherchip. Bei einem anderen Beispiel können die Speicherchips arbeiten, nachdem sie unterschiedliche Versorgungsspannungen empfangen haben, wenn die Speichersteuerung keine Spannungsregelung liefert. Dabei ist der Speicherchipentwurf jedoch komplexer, und die optimale Leistungsfähigkeit ist verloren, da Speicherchips den Eingangsversorgungsspannungspegel erfassen und anschließend einen Satz von Betriebsparametern auswählen müssen, die dem erfassten Pegel der Eingangsversorgungsspannung entsprechen.

**[0005]** Ein Problem bei dem herkömmlichen Speichersystem **100** besteht darin, dass jeder der Speicherchips eine Ladungspumpenschaltungsanordnung umfassen muss. Die Ladungspumpenschaltungsanordnung nimmt nicht nur wertvolle Halbleiterfläche der Speicherchips ein, sondern bewirkt auch eine beträchtliche Rauscherzeugung, wenn die zusätzlichen Versorgungsspannungen erzeugt werden. Die Rauscherzeugung kann die empfindlichen analogen Abschnitte der Speicherchips nachteilig beeinflussen. Dementsprechend verschlechtert das durch die Ladungspumpenschaltungsanordnung gelieferte zusätzliche Rauschen die Betriebsleistungsfähigkeit der Speicherchips.

**[0006]** Spannungserzeugungsschaltungen für Speichersysteme werden z. B. in der US 5 621,685 A, der US 6,079,023 A oder der US 6,009,034 A beschrieben.

**[0007]** Es ist die Aufgabe der Erfindung, verbesserte Lösungsansätze zum Erzeugen diverser unterschiedlicher Versorgungsspannungspegel zur Verwendung durch Speicherchips, die eine nicht-flüchtige Datenspeicherung liefern, zu schaffen.

**[0008]** Diese Aufgabe wird durch ein Speichersystem nach Anspruch 1 und ein elektronische System nach Anspruch 10 gelöst.

**[0009]** Allgemein gesagt bezieht sich die Erfindung auf Techniken zum Erzeugen und Liefern verschiedener Spannungspegel in einem Speichersystem, das mehrere Speicherblöcke (z. B. Speicherchips)

aufweist. Die verschiedenen Spannungspegel können durch eine Spannungserzeugungsschaltungsanordnung (z. B. Ladungspumpen- und/oder Reglerschaltungsanordnung) in dem Speichersystem erzeugt werden. Die verschiedenen Spannungspegel können durch einen Leistungsbus an oder zwischen Speicherblöcke geliefert werden.

**[0010]** Weitere Aspekte und Vorteile der Erfindung ergeben sich aus der folgenden ausführlichen Beschreibung, die zusammen mit den beiliegenden Zeichnungen zu betrachten ist, die beispielhaft die Prinzipien der Erfindung veranschaulichen.

**[0011]** Die Erfindung wird durch die folgende ausführliche Beschreibung in Verbindung mit den beiliegenden Zeichnungen, bei denen gleiche Bezugszeichen gleiche strukturelle Elemente benennen, ohne weiteres ersichtlich. Es zeigen:

**[0012]** **Fig. 1** ein Blockdiagramm eines herkömmlichen Speichersystems;

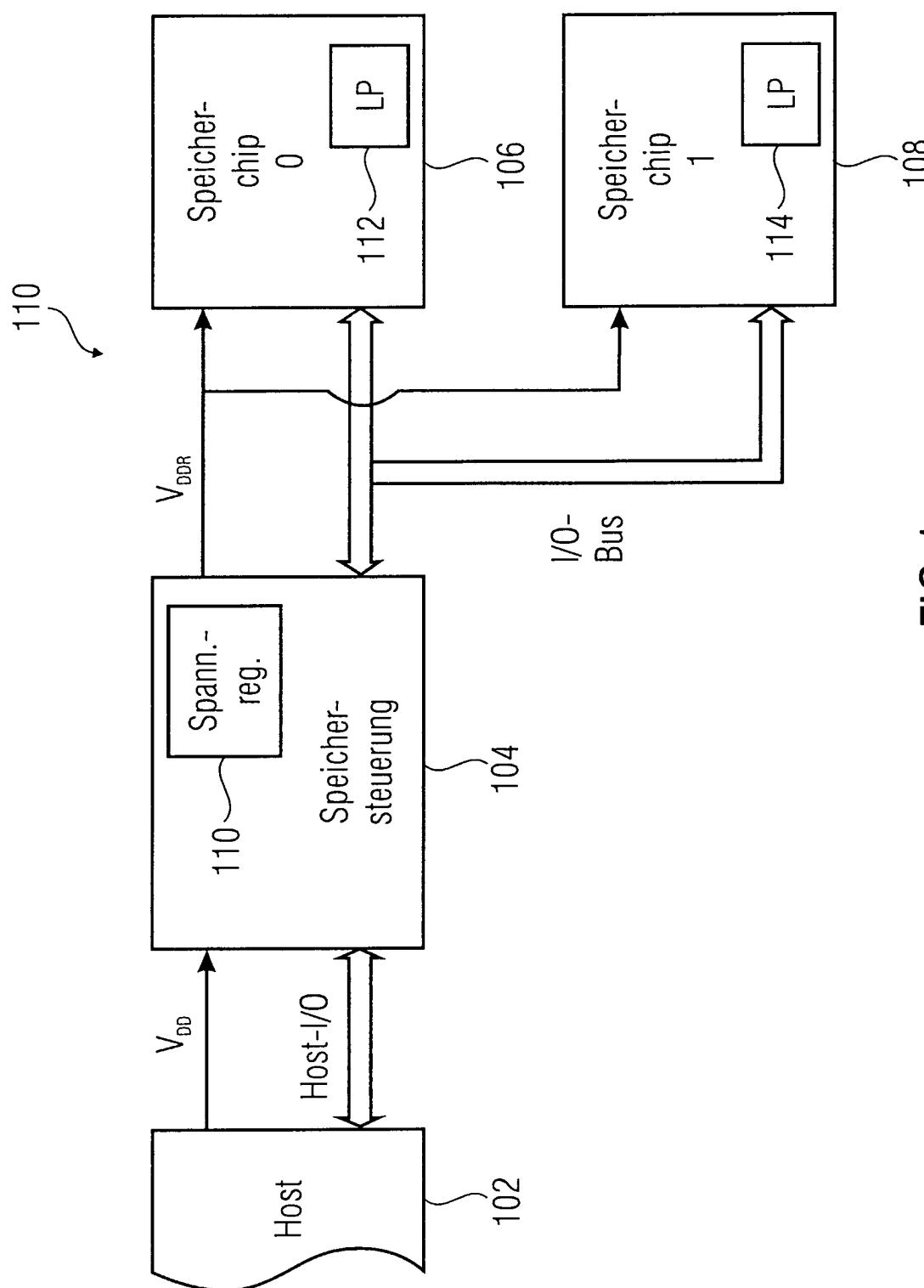

**[0013]** **Fig. 2** ein Blockdiagramm eines Speichersystems gemäß einem Beispiel;

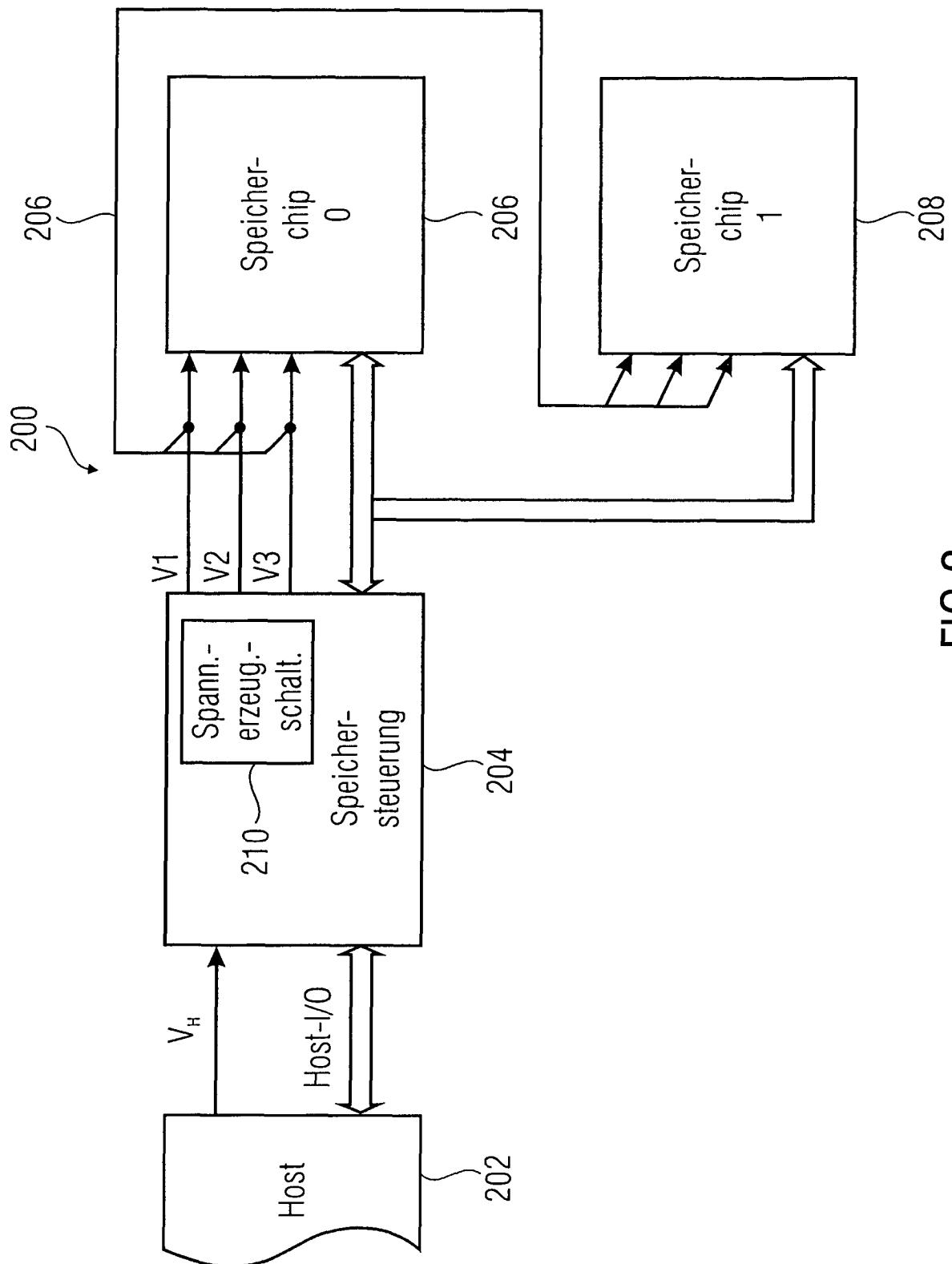

**[0014]** **Fig. 3** ein Blockdiagramm eines Speichersystems gemäß einem weiteren Beispiel;

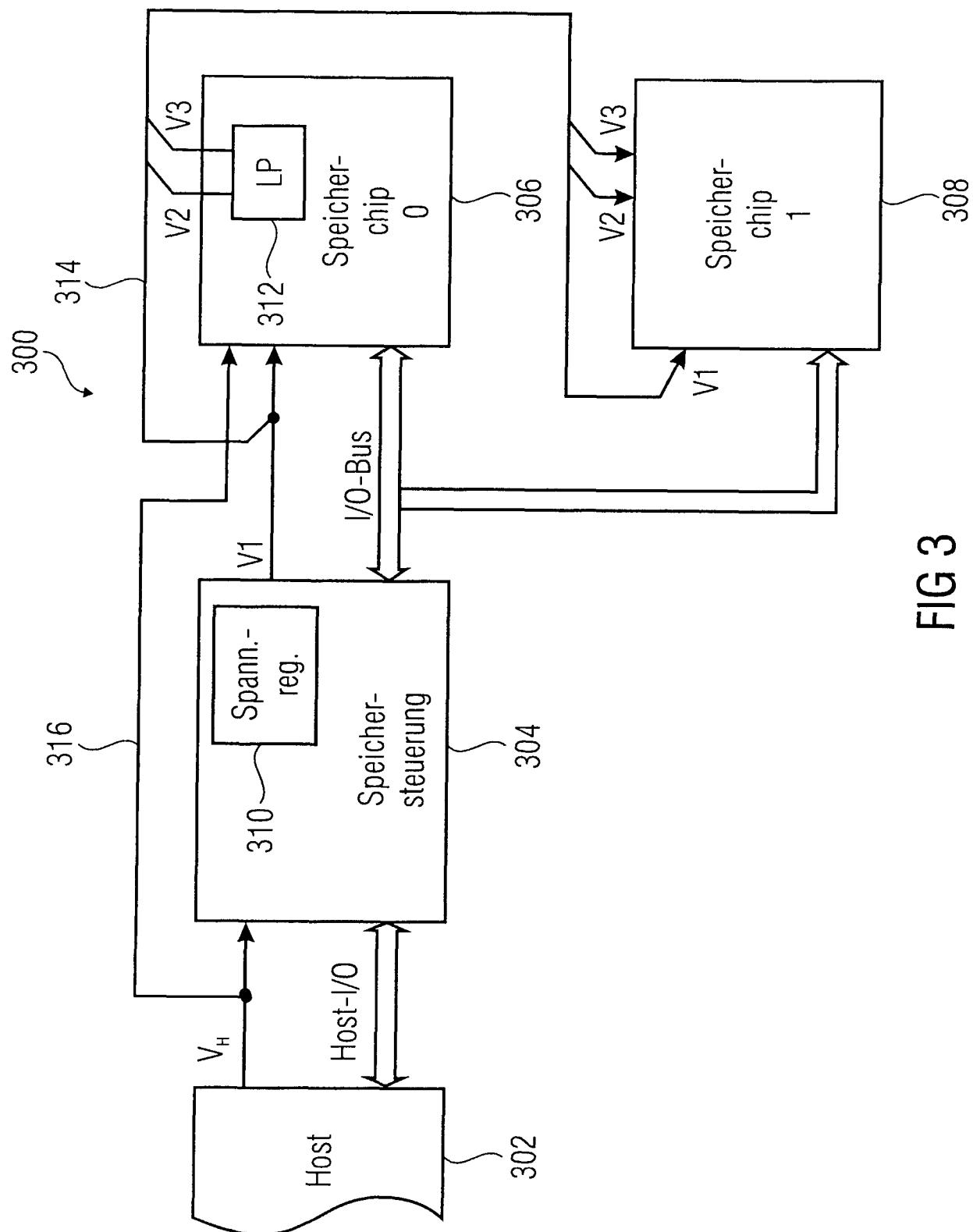

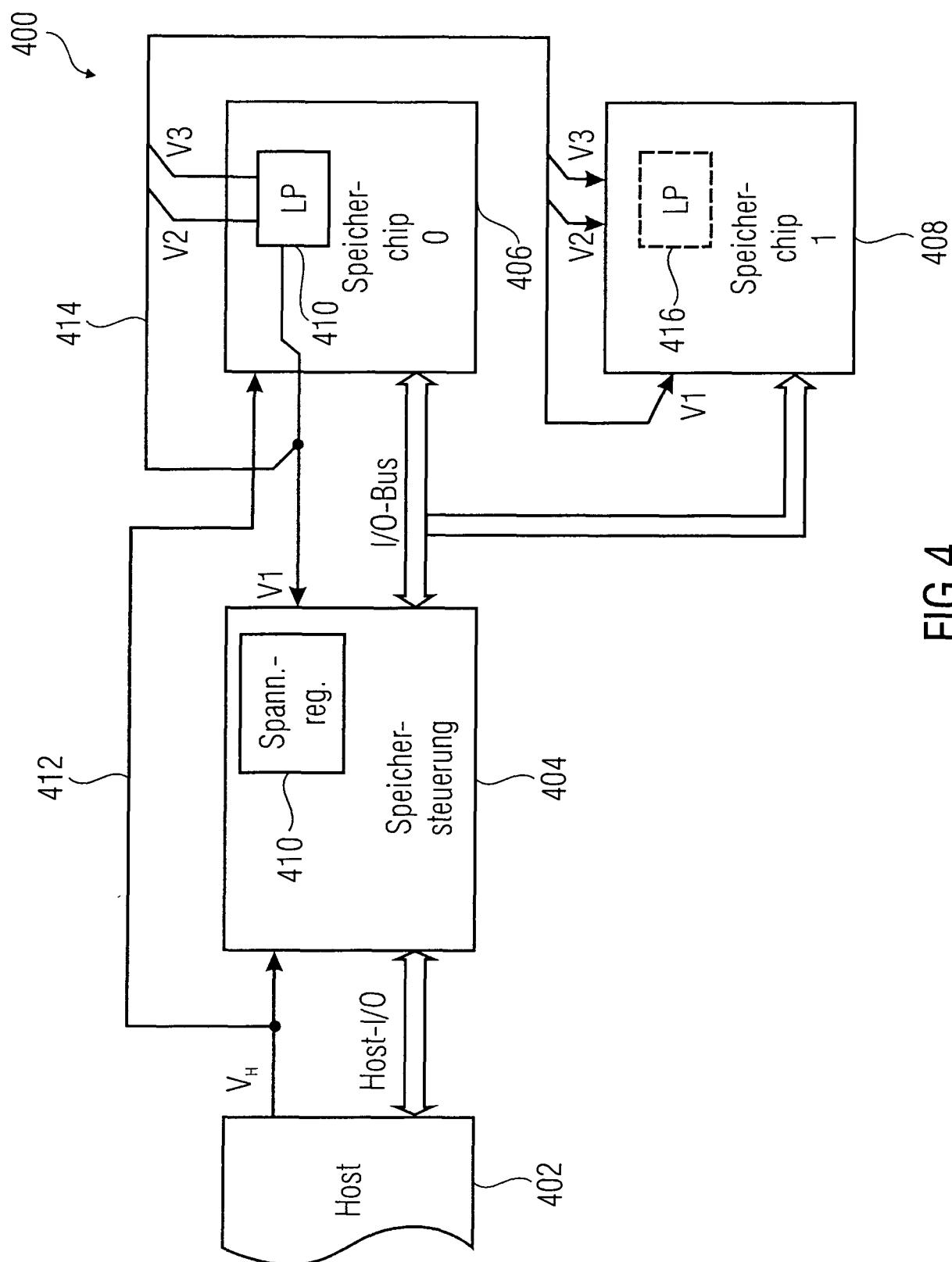

**[0015]** **Fig. 4** ein Blockdiagramm eines Speichersystems gemäß einem Ausführungsbeispiel der Erfindung; und

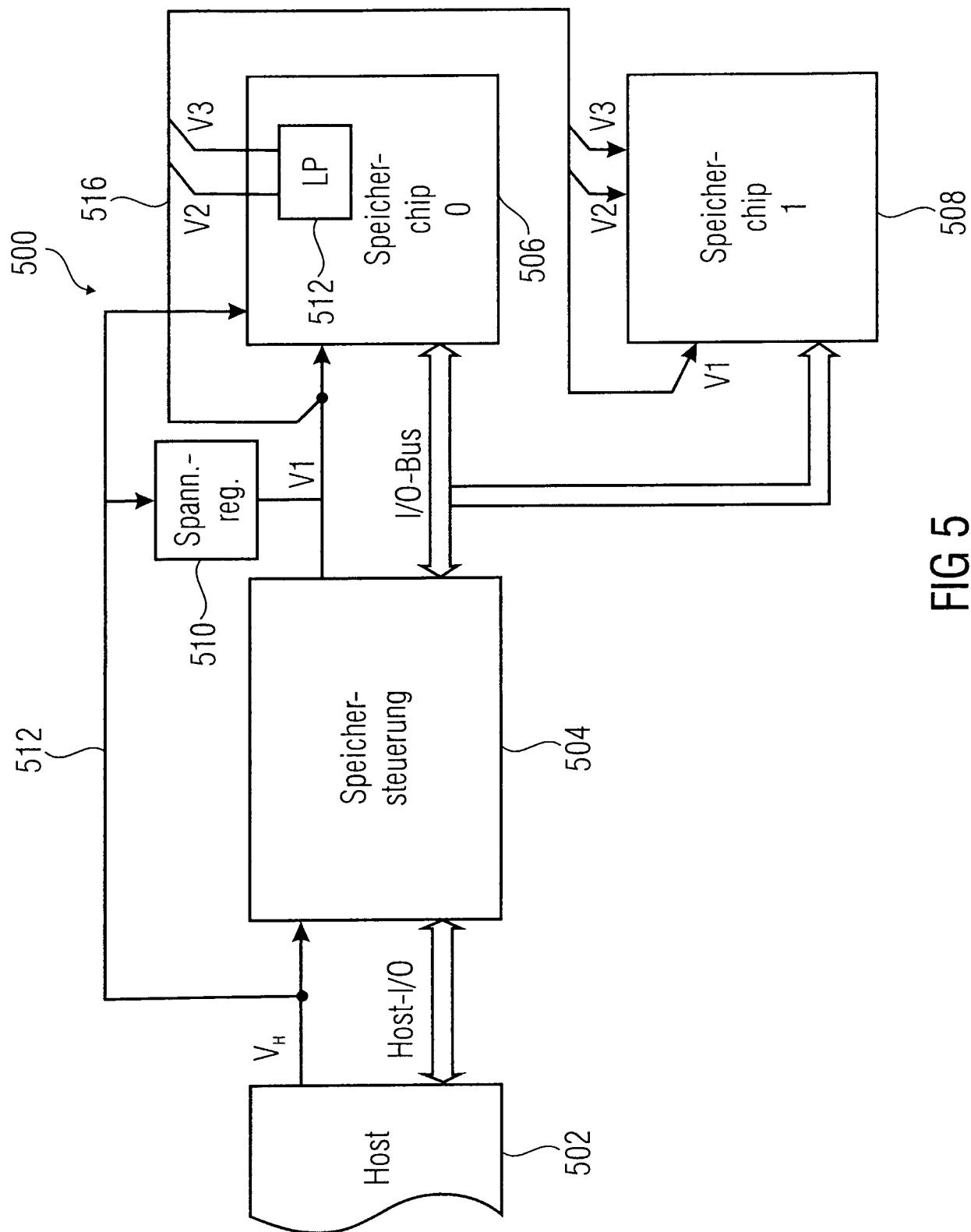

**[0016]** **Fig. 5** ein Blockdiagramm eines Speichersystems gemäß einem noch weiteren Beispiel.

**[0017]** Die Erfindung bezieht sich auf Techniken zum Erzeugen und Liefern verschiedener Spannungspegel in einem Speichersystem, das mehrere Speicherblöcke (z. B. Speicherchips) aufweist. Die verschiedenen Spannungspegel können durch eine Spannungserzeugungsschaltungsanordnung (z. B. Ladungspumpen- und/oder Reglerschaltungsanordnung) in dem Speichersystem erzeugt werden. Die verschiedenen Spannungspegel können durch einen Leistungsbus an oder zwischen mehrere Speicherblöcke geliefert werden.

**[0018]** Gemäß einem Aspekt der Erfindung sind Ladungspumpen- und/oder Reglerschaltungen in einem der Speicherblöcke eines Speichersystems vorgesehen (es sei denn, es sind Sicherungen zum Zweck einer Fehlertoleranz vorgesehen), und ein Leistungsbus wird verwendet, um die erzeugten Spannungspegel an andere der Speicherblöcke zu verteilen. Bei diesem Aspekt muss bestenfalls lediglich einer der Speicherblöcke eine Ladungspumpen- und/oder Reglerschaltungsanordnung umfassen. Daher dient die Erfindung dazu, das Ausmaß zu begrenzen, in dem ein durch die Ladungspumpen- und/oder

Reglerschaltungsanordnung erzeugtes unerwünschtes Rauschen den Betrieb von empfindlichen analogen Komponenten von Speicherblöcken eines Speichersystems stört.

**[0019]** Gemäß einem weiteren Aspekt der Erfindung erzeugt eine Speichersteuerung mehrere Versorgungsspannungspegel, die (z. B. über einen Leistungsbus) an jeden der Speicherblöcke verteilt werden. Bei diesem Aspekt müssen die Speicherblöcke keinerlei Ladungspumpen- oder Reglerschaltungsanordnung umfassen, da die Speichersteuerung alle benötigten Versorgungsspannungen auf zentrale Weise erzeugen und sie an jeden der Speicherblöcke verteilen kann.

**[0020]** Ausführungsbeispiele dieses Aspekts der Erfindung werden nachstehend erläutert. Fachleute werden jedoch ohne weiteres erkennen, dass die hierin in Bezug auf diese Figuren angegebene ausführliche Beschreibung Erläuterungszwecken dient, während sich die Erfindung über diese begrenzten Ausführungsbeispiele hinaus erstreckt.

**[0021]** **Fig. 2** ist ein Blockdiagramm eines Speichersystems **200** gemäß einem Beispiel. Das Speichersystem **200** ist beispielsweise einer Speicherplatte (beispielsweise einer Einstekkarte), einem Speicherstift oder einem anderen Datenspeicherprodukt zugeordnet. Beispiele einer Speicherplatte umfassen PC-Karte (früher PCMCIA-Vorrichtung), Flash-Karte, Flash-Disk, Multimedialplatte und ATA-Karte.

**[0022]** Das Speichersystem **200** arbeitet mit einem Host **202** zusammen. Insbesondere speichert das Speichersystem **200** Daten, die durch den Host **202** verwendet werden. Das Speichersystem **200** und der Host **202** kommunizieren über einen Host-Eingabe/Ausgabe-Bus (Host-I/O-Bus). Der Host **202** liefert dem Speichersystem **200** eine Hostspannung  $V_H$  (Versorgungsspannung).

**[0023]** Das Speichersystem **200** umfasst eine Speichersteuerung **204** und Speicherblöcke **206** und **208**. Bei diesem Ausführungsbeispiel umfasst das Speichersystem **200** zwei Speicherblöcke. Man sollte jedoch beachten, dass das Speichersystem **200** zwei oder mehr Speicherblöcke umfassen kann. In der Regel werden zusätzliche Speicherblöcke zu dem Speichersystem **200** hinzugefügt, um die Datenspeicherkapazität desselben zu erhöhen.

**[0024]** Die Speichersteuerung **204** umfasst eine Spannungserzeugungsschaltung **210**. Die Spannungserzeugungsschaltung **210** empfängt die durch den Host **202** gelieferte Hostspannung ( $V_H$ ) und erzeugt eine Mehrzahl von Versorgungsspannungen, die an die Speicherblöcke **206** und **208** geliefert werden. Bei diesem Beispiel (und anderen, nachstehenden Beispielen) ist die Mehrzahl von Versor-

gungsspannungen als Versorgungsspannungen V1, V2 und V3 dargestellt. Die Versorgungsspannungen V1, V2 und V3 stellen die Spannungspiegel dar, die durch die Speicherblöcke **206** und **208** während ihres Betriebs verwendet werden. Dementsprechend umfassen die Speicherblöcke **206** und **208** nicht ferner eine Ladungspumpen-Regelungsschaltungsanordnung, da diese Speicherblöcke **206** und **208** intern keine anderen Versorgungsspannungen erzeugen als diejenigen Versorgungsspannungen V1, V2 und V3, die von der Speichersteuerung **204** empfangen werden. Demnach erzeugt die Speichersteuerung **204** alle benötigten Versorgungsspannungen für die Speicherblöcke **206** und **208**, und somit wird in den Speicherblöcken **206** und **208** keine Ladungspumpen-Regelungsschaltungsanordnung benötigt. Folglich stört kein durch die Ladungspumpenschaltungsanordnung erzeugtes Rauschen den Betrieb (insbesondere den Betrieb von empfindlichen analogen Komponenten) der Speicherblöcke **206** und **208**. Ferner muss die teure Formfläche der Halbleiterformen, die den Speicherblöcken **206** und **208** zugeordnet sind, nicht durch eine Ladungspumpen-Reglerschaltungsanordnung eingenommen werden.

**[0025]** Überdies werden die durch die Speichersteuerung **204** erzeugten Versorgungsspannungen V1, V2 und V3 dem Speicherblock **206** geliefert. Ein Leistungsbus **212** arbeitet, um die Versorgungsspannungen V1, V2 und V3 zwischen den Speicherblock **206** und den Speicherblock **208** zu liefern. Mit anderen Worten trägt der Leistungsbus **212** die Versorgungsspannungen V1, V2 und V3 zu dem Speicherblock **208**. Ferner, falls das Speichersystem **200** zusätzliche Speicherblöcke umfasst, liefert der Leistungsbus **212** die Versorgungsspannungen V1, V2 und V3 auch an die anderen, zusätzlichen Speicherblöcke. Der Leistungsbus **212** kann auch als Lieferant der Versorgungsspannungen V1, V2 und V3 an den Speicherblock **206** angesehen werden.

**[0026]** In der Regel weist die Speichersteuerung **204** Ausgangskontakte (z. B. Anschlussstifte, Anschlussflächen, Anschlüsse usw.) auf, um die Versorgungsspannungen V1, V2 und V3 auszugeben. Die Speicherblöcke **206** und **208** weisen Eingangskontakte auf, um die Versorgungsspannungen V1, V2 und V3 zu empfangen. Bei einer Implementierung werden Verbindungselemente (z. B. Drähte, Leiterbahnen usw.) verwendet, um die Ausgangskontakte der Speichersteuerung **204** mit den Eingangskontakten des Speicherblocks **206** sowie mit Verbindungselementen des Leistungsbusses **212** zu koppeln. Bei einem anderen Beispiel werden Verbindungselemente des Leistungsbusses **212** verwendet, um die Ausgangskontakte der Speichersteuerung **204** mit den Eingangskontakten beider Speicherblöcke **206** und **208** zu koppeln.

**[0027]** Der Pegel der Versorgungsspannungen kann mit der Implementierung variieren. Als Beispiel kann die Hostspannung ( $V_H$ ) 3,3 oder 1,8 Volt betragen, und der Pegel der Versorgungsspannungen V1, V2 und V3 kann 2,5 Volt, 6,5 Volt und 3,3 Volt betragen. Obwohl das Beispiel des in **Fig. 2** gezeigten Speichersystems **200** an der Speichersteuerung **204** Versorgungsspannungen V1, V2 und V3 erzeugt, sollte man verstehen, dass die Speichersteuerung **204** eine beliebige Anzahl einer Mehrzahl unterschiedlicher Versorgungsspannungspegel erzeugen kann, die durch einen oder mehrere der Speicherblöcke des Speichersystems **200** benötigt werden.

**[0028]** Jeder der Speicherblöcke **206** und **208** umfasst ein Array aus Datenspeicherelementen, die eine nicht-flüchtige digitale Datenspeicherung liefern. Bei einem Beispiel sind die Datenspeicherelemente elektrisch programmierbar und elektrisch lösbar. Beispielsweise können die Datenspeicherelemente auf Floating-Gate-Bauelementen beruhen. Die Speicherblöcke **206** und **208** sind jeweils separate Halbleiterformen, -chips oder -Produkte. Die Speicherblöcke können beispielsweise EEPROM- oder FLASH-Bauelemente sein. Die Speichersteuerung **204** ist ferner oft ein(e) separate(s, r) Halbleiterform, -chip oder -Produkt.

**[0029]** **Fig. 3** ist ein Blockdiagramm eines Speichersystems **300** gemäß einem weiteren Beispiel. Das Speichersystem **300** ist mit einem Host **302** gekoppelt. Die Schnittstelle zwischen dem Speichersystem **300** und dem Host **302** umfasst eine Hostspannung ( $V_H$ ) und einen Host-I/O-Bus.

**[0030]** Das Speichersystem **300** umfasst eine Speichersteuerung **304** und Speicherblöcke **306** und **308**. Obwohl das Speichersystem **300** lediglich zwei Speicherblöcke umfasst, sollte man verstehen, dass in dem Speichersystem **300** auch weitere Speicherblöcke vorgesehen sein können. Die Speichersteuerung **304** und die Speicherblöcke **306** und **308** kommunizieren über einen I/O-Bus. Ferner erzeugt ein Spannungsregler **310** in der Speichersteuerung **304** eine Versorgungsspannung V1. Die Versorgungsspannung V1, die durch den Spannungsregler **310** erzeugt wird, stellt beispielsweise eine geregelte Version der Hostspannung  $V_H$  dar. Die Versorgungsspannung V1 wird an den Speicherblock **306** geliefert.

**[0031]** Der Speicherblock **306** umfasst ferner eine Ladungspumpenschaltungsanordnung **312**. Die Ladungspumpenschaltungsanordnung **312** empfängt die Versorgungsspannung V1 von der Speichersteuerung **304** und erzeugt zumindest eine zusätzliche Versorgungsspannung. Bei diesem Beispiel wird angenommen, dass die Ladungspumpenschaltungsanordnung **312** eine zweite Versorgungsspannung V2 und eine dritte Versorgungsspannung V3 erzeugt. Dementsprechend sollte man beachten, dass die

Ladungspumpenschaltungsanordnung **312** mehr als zwei Versorgungsspannungen erzeugen könnte oder eine einzige Versorgungsspannung erzeugen könnte. In der Regel umfasst die Ladungspumpenschaltungsanordnung **312** eine Ladungspumpe und/oder einen Regler.

**[0032]** Das Speichersystem **300** umfasst ferner einen Leistungsbus **314**. Der Leistungsbus **314** empfängt die Versorgungsspannung **V1** von der Speichersteuerung **304** (oder dem Speicherblock **306**) und empfängt ferner die Versorgungsspannungen **V2** und **V3** von dem Speicherblock **306**. Anschließend transportiert der Leistungsbus **314** diese Versorgungsspannungen zu den anderen Speicherblöcken, nämlich dem Speicherblock **308**. Insbesondere können der Speicherblock **306** und der Speicherblock **308** jeweils drei Kontakte (z. B. Anschlüsse, Anschlussstifte oder Anschlussflächen) umfassen, um mit den Versorgungsspannungen **V1**, **V2** bzw. **V3** gekoppelt zu sein. Der Leistungsbus **314** verbindet diese drei Anschlüsse jedes der Speicherblöcke **306** und **308** jeweils miteinander. Somit kann die Versorgungsspannung **V1**, die durch die Speichersteuerung **304** erzeugt wird, nicht nur mit dem Speicherblock **306**, sondern auch mit dem Speicherblock **308**, unter Verwendung des Leistungsbusses **314**, gekoppelt werden. Desgleichen können die durch die Ladungspumpenschaltungsanordnung **312** erzeugten Versorgungsspannungen **V2** und **V3** nicht nur in dem Speicherblock **306** intern verwendet werden, sondern auch durch den Leistungsbus **314** extern an den Speicherblock **308** (und möglicherweise andere Blöcke) geliefert werden. Demnach erfordert das Speichersystem **300** lediglich, dass einer der Speicherblöcke eine Ladungspumpenschaltungsanordnung umfasst, um die zusätzlichen Versorgungsspannungspegel, die durch die verschiedenen Speicherblöcke benötigt werden, zu erzeugen.

**[0033]** Ferner kann die Hostspannung **V<sub>H</sub>** auch an den Speicherblock **306** geliefert werden. Die Ladungspumpenschaltungsanordnung **312** kann dann unter Verwendung der ersten Versorgungsspannung **V1** und/oder der Hostspannung **V<sub>H</sub>** die zweite und die dritte Versorgungsspannung **V2** bzw. **V3** erzeugen. Die Verfügbarkeit der Hostspannung **V<sub>H</sub>** an dem Speicherblock **306** kann die Ladungspumpenschaltungsanordnung **312** befähigen, die zweite und die dritte Versorgungsspannung **V2** bzw. **V3** effizienter zu erzeugen. Falls die Hostspannung **V<sub>H</sub>** beispielsweise 5,0 Volt beträgt und die erste Versorgungsspannung **V1** 3,0 Volt beträgt, so wäre ein Erzeugen einer dritten Versorgungsspannung von 6,5 Volt von einem Anfangspunkt von 5,0 Volt im Gegensatz zu einem Anfangspunkt von 3,0 Volt effizienter (d. h. es wäre ein geringes Maß eines Ladungspumpens erforderlich). Die Hostspannung **V<sub>H</sub>** kann über ein Verbindungselement **316** direkt mit dem Speicherblock **306** gekoppelt werden. Das Verbindungselement **316** kann als

Draht, Leiterbahn oder andere elektronische Verbindung implementiert sein. Alternativ könnte die Hostspannung **V<sub>H</sub>** durch die Speichersteuerung **304** indirekt an den Speicherblock **306** geliefert werden.

**[0034]** Man sollte ferner beachten, dass ein in dem Speicherblock **308** veranschaulichtes gestricheltes Kästchen eine optionale Ladungspumpenschaltung **318** darstellt. Die optionale Ladungspumpenschaltung **318** kann als sekundäre oder Sicherungs-Ladungspumpenschaltung in dem Speicherblock **308** (oder anderen Speicherblöcken in dem Speichersystem) vorgesehen sein. Bei einer Implementierung kann die optionale Ladungspumpenschaltung **318** verwendet werden, um eine oder mehrere zusätzliche Versorgungsspannungen für den Speicherblock **308** zu erzeugen, die nicht von dem Leistungsbus **314** erhältlich sind. Bei einer anderen Implementierung kann die Ladungspumpenschaltung **318** aktiviert werden, um in dem Fall, in dem die Ladungspumpenschaltungsanordnung **312** funktionsuntüchtig ist, die Versorgungsspannungen **V2** und **V3** zu erzeugen und somit die Versorgungsspannungen **V2** und **V3** über den Leistungsbus **314** an den Speicherblock **306** zu liefern. Bei einem Beispiel, das derartige optionale Ladungspumpenschaltungen umfasst, kann die Hostspannung **V<sub>H</sub>** auch über den Leistungsbus **314** oder ein Verbindungselement **320** mit dem Speicherblock **308** gekoppelt sein.

**[0035]** Fig. 4 ist ein Blockdiagramm eines Speichersystems **400** gemäß einem Ausführungsbeispiel der Erfindung. Das Speichersystem **400** ist mit einem Host **402** gekoppelt. Der Host **402** und das Speichersystem **400** kommunizieren über einen Host-I/O-Bus. Der Host **402** liefert ferner eine Hostspannung **V<sub>H</sub>** an die Speichersteuerung **404**. Das Speichersystem **400** umfasst die Speichersteuerung **404** und Speicherblöcke **406** und **408**. Bei diesem Ausführungsbeispiel umfasst der Speicherblock **406**, wie auch das in Fig. 3 veranschaulichte Speichersystem **300**, eine Ladungspumpenschaltungsanordnung **410**. Im Gegensatz zu dem Speichersystem **300** umfasst die Speichersteuerung **404** jedoch keinen Spannungsregler. Mit anderen Worten erzeugt die Speichersteuerung **404** keine Versorgungsspannungen, die durch die Speicherblöcke **406** und **408** verwendet werden. Bei diesem Ausführungsbeispiel liefert die in dem Speicherblock **406** vorgesehene Ladungspumpenschaltungsanordnung **410** stattdessen alle durch die Speicherblöcke **406** und **408** benötigten Versorgungsspannungen. Insbesondere kann die Ladungspumpenschaltungsanordnung **410** eine Mehrzahl von Versorgungsspannungen, nämlich Versorgungsspannungen **V1**, **V2** und **V3**, erzeugen. Die Ladungspumpenschaltungsanordnung **410** empfängt die durch den Host **402** über ein Verbindungselement **412** gelieferte Hostspannung **V<sub>H</sub>**. Die Ladungspumpenschaltungsanordnung **410** verwendet die Hostspannung **V<sub>H</sub>** beim Erzeugen der Ver-

sorgungsspannungen V1, V2 und V3. Die Ladungspumpenschaltungsanordnung **410** kann die Versorgungsspannung V1 nicht nur intern an den Speicherblock **406**, sondern auch extern an die Speichersteuerung **404** liefern, falls dies durch die Speichersteuerung gewünscht wird. Ferner sind die Versorgungsspannungen V1, V2 und V3 (zusätzlich dazu, dass sie innerhalb des Speicherblocks **406** verwendet werden) mit einem Leistungsbust **414** gekoppelt. Der Leistungsbust **414** arbeitet, um die Versorgungsspannungen V1, V2 und V3 zwischen die Speicherblöcke **406** und **408** zu koppeln. Daher werden die Versorgungsspannungen V1, V2 und V3 dem Speicherblock **408** über den Leistungsbust **414** geliefert. Mit anderen Worten erzeugt der Speicherblock **408** keine Versorgungsspannungspegel intern, sondern empfängt die Versorgungsspannungspegel stattdessen über den Leistungsbust **414**.

**[0036]** Ferner sollte man beachten, dass ein in dem Speicherblock **408** veranschaulichtes gestricheltes Kästchen eine optionale Ladungspumpenschaltung **416** darstellt. Die optionale Ladungspumpenschaltung **416** kann in dem Speicherblock **408** (oder anderen Speicherblöcken in dem Speichersystem) als sekundäre oder Sicherungs-Ladungspumpenschaltung vorgesehen sein. Bei einer Implementierung kann die optionale Ladungspumpenschaltung **416** verwendet werden, um eine oder mehrere zusätzliche Versorgungsspannungen für den Speicherblock **408** zu erzeugen, die nicht von dem Leistungsbust **414** erhältlich sind. Bei einer anderen Implementierung kann die Ladungspumpenschaltung **416** aktiviert sein, um in dem Fall, in dem die Ladungspumpenschaltungsanordnung **410** funktionsuntüchtig ist, die Versorgungsspannungen V1, V2 und V3 zu erzeugen und somit die Versorgungsspannungen V1, V2 und V3 über den Leistungsbust **414** an den Speicherblock **406** zu liefern. Bei einem Ausführungsbeispiel, das derartige optionale Ladungspumpenschaltungen umfasst, kann die Hostspannung  $V_H$  über den Leistungsbust **414** auch mit dem Speicherblock **408** gekoppelt sein.

**[0037]** Fig. 5 ist ein Blockdiagramm eines Speichersystems **500** gemäß einem noch weiteren Beispiel. Das Speichersystem **500** ist mit einem Host **502** gekoppelt. Der Host **502** und das Speichersystem **500** kommunizieren über einen Host-I/O-Bus. Der Host **502** liefert ferner eine Hostspannung  $V_H$  an das Speichersystem **500**.

**[0038]** Das Speichersystem **500** umfasst eine Speichersteuerung **504** und Speicherblöcke **506** und **508**. Die Speichersteuerung **504** und die Speicherblöcke **506** und **508** kommunizieren über einen I/O-Bus. Das Speichersystem **500** umfasst ferner einen Spannungsregler **510**. Bei diesem Beispiel stellt der Spannungsregler **510** eine von der Speichersteuerung **504** oder den Speicherblöcken **506** und **508** separate funktionelle Einheit dar. In der Regel ist der Span-

nungsregler **510** als separate(r) Halbleiterform oder -chip in dem Speichersystem **500** vorgesehen. Der Spannungsregler **510** empfängt die Hostspannung  $V_H$  über ein Verbindungselement **512**. Das Verbindungselement **512** kann ferner die Hostspannung  $V_H$  mit dem Speicherblock **506** koppeln. Der Spannungsregler **510** erzeugt eine erste Versorgungsspannung V1. Der Spannungsregler **510** liefert die erste Versorgungsspannung V1 an die Speichersteuerung **504** und den Speicherblock **506**.

**[0039]** Ferner umfasst der Speicherblock **506** eine Ladungspumpenschaltungsanordnung **514**. Die Ladungspumpenschaltungsanordnung **514** arbeitet, um zumindest eine zusätzliche Versorgungsspannung zu erzeugen. Bei diesem Beispiel sei angenommen, dass die Ladungspumpenschaltungsanordnung **514** eine zweite Versorgungsspannung V2 und eine dritte Versorgungsspannung V3 erzeugt. Die Ladungspumpenschaltungsanordnung **514** empfängt die Hostspannung  $V_H$  sowie die erste Versorgungsspannung V1 und ist somit in der Lage, unter Verwendung einer der beiden oder beider dieser Quellenspannungen die Versorgungsspannungen V2 und V3 zu erzeugen. Durch Verwenden der Hostspannung  $V_H$  ist die Ladungspumpenschaltungsanordnung **514** oft in der Lage, jede der Versorgungsspannungen V2 oder V3 effizienter zu erzeugen, da ein geringes Maß eines „Ladungspumpens“ erforderlich ist.

**[0040]** Das Speichersystem **500** umfasst ferner einen Leistungsbust **516**. Der Leistungsbust **516** koppelt die Versorgungsspannungen V1, V2 und V3 mit dem Speicherblock **508**. Die Versorgungsspannungen V1, V2 und V3 werden somit über den Leistungsbust **516** in den Speicherblock **508** eingegeben. Mit anderen Worten erzeugt der Speicherblock **508** keine der Versorgungsspannungen. In der Tat umfasst der Speicherblock **508** in der Regel keinerlei Ladungspumpenschaltungsanordnung. Falls gewünscht, könnte der Speicherblock **508** jedoch eine Sicherungs-Ladungspumpenschaltung zur Verwendung umfassen, falls die Hauptladungspumpenschaltungsanordnung **514** ausfallen sollte.

**[0041]** Bei dem in Fig. 4 veranschaulichten Ausführungsbeispiel der Erfindung umfasst das Speichersystem zwei Speicherblöcke. Man sollte jedoch beachten, dass die Speichersysteme allgemein zwei oder mehr Speicherblöcke umfassen können. In der Regel werden zusätzliche Speicherblöcke zu den Speichersystemen hinzugefügt, um ihre Datenspeicherkapazität zu erhöhen. Diese zusätzlichen Speicherblöcke sind normalerweise so konfiguriert und/oder arbeiten so wie die Speicherblöcke **208**, **308**, **408** oder **508**. Bei allen der oben erläuterten Beispielen und Ausführungsbeispielen der Erfindung kann ferner eine optionale Ladungspumpen- und/oder Reglerschaltungsanordnung in einem oder

mehreren der Speicherblöcke vorgesehen sein. Eine derartige optionale Ladungspumpen- und/oder Reglerschaltungsanordnung kann als Sicherungs- oder Sekundärfunktion dienen, falls die Hauptladungspumpen- und/oder Reglerschaltungsanordnung funktionsuntüchtig wird. Zusätzlich oder alternativ dazu kann die optionale Ladungspumpen- und/oder Reglerschaltungsanordnung arbeiten, um in den Fällen, in denen die durch die Speicherblöcke benötigten zusätzlichen Spannungen nicht an die Speicherblöcke geliefert werden, eine zusätzliche interne Spannungserezeugung zu liefern.

**[0042]** Die Erfindung eignet sich zur Verwendung bei sowohl Einebenenspeichern als auch Mehrebenenspeichern. Die Speicher oder Speicherblöcke sind Datenspeichervorrichtungen, die Datenspeicherelemente umfassen. Die Datenspeicherelemente können auf Halbleiterbauelementen (z. B. Floating-Gate) oder anderen Typen von Bauelementen beruhen. Bei Mehrebenenspeichern speichert jedes Datenspeicherelement zwei oder mehr Datenbits.

**[0043]** Die Erfindung kann sich ferner auf ein elektronisches System beziehen, das ein Speichersystem gemäß der obigen Erläuterung umfasst. Speichersysteme (d. h. Speicherkarten) werden üblicherweise verwendet, um digitale Daten zur Verwendung bei verschiedenen Elektronikprodukten zu speichern. Das Speichersystem ist oft von dem Elektroniksystem entfernbare, so dass die gespeicherten digitalen Daten tragbar sind. Die Speichersysteme gemäß der Erfindung können einen relativ geringen Formfaktor aufweisen und verwendet werden, um digitale Daten für Elektronikprodukte wie beispielsweise Kameras, in der Hand zu haltende oder Notebook-Computer, Netzwerkkarten, Netzwerkgeräte, Set-Top-Boxen, in der Hand zu haltende oder andere kleine Audiowiedergabegeräte/-aufzeichnungsgeräte (z. B. MP3-Geräte) und medizinische Überwachungsvorrichtungen zu speichern.

**[0044]** Die Vorteile der Erfindung sind zahlreich. Verschiedene Ausführungsbeispiele oder Implementierungen können einen oder mehrere der folgenden Vorteile liefern. Ein Vorteil der Erfindung besteht darin, dass Erzeugung und Verteilung von Versorgungsspannungen kosteneffektiver gestaltet sind. Ein weiterer Vorteil der Erfindung besteht darin, dass kein Rauschen von einer Erzeugung unterschiedlicher Spannungspegel die Speicherzugriffsleistungsfähigkeit hemmt. Ein weiterer Vorteil der Erfindung besteht darin, dass zuverlässige Hochleistungs-Speichersysteme erhalten werden können. Ein weiterer Vorteil der Erfindung besteht darin, dass Speichersysteme mit einem geringen Leistungsverbrauch und einer größeren Flexibilität beim Steuerungsentwurf implementiert werden können.

## Patentansprüche

1. Speichersystem (**400**), das eine externe Versorgungsspannung ( $V_H$ ) von einem Host (**402**) empfängt, wobei das Speichersystem (**400**) folgende Merkmale aufweist:

eine Mehrzahl von Speicherchips (**406, 408**), wobei jeder der Speicherchips (**406, 408**) zumindest eine Mehrzahl von Datenspeicherelementen umfasst, wobei zumindest einer der Speicherchips (**406**) ferner zumindest eine erste Spannungserzeugungsschaltung (**410**) umfasst, die betreibbar ist, um zumindest eine im Speicher erzeugte Versorgungsspannung ( $V_1$ ) zu erzeugen;

eine Speichersteuerung (**404**), die wirksam gekoppelt ist, um auf die Speicherchips (**406, 408**) zuzugreifen; und

einen Leistungsbus (**414**), der mit jedem der Speicherchips (**406, 408**) gekoppelt ist, wobei der Leistungsbus (**414**) die zumindest eine im Speicher erzeugte Versorgungsspannung ( $V_1$ ) an die Speicherchips (**406, 408**) liefert,

wobei die im Speicher erzeugte Versorgungsspannung ( $V_1$ ) ferner an die Speichersteuerung (**404**) geliefert wird.

2. Speichersystem (**400**) gemäß Anspruch 1, bei dem, wenn das Speichersystem (**400**) wirksam mit dem Host (**402**) verbunden ist, die externe Versorgungsspannung ( $V_H$ ) an den zumindest einen der Speicherchips (**406**) geliefert wird, der zumindest die erste Spannungserzeugungsschaltung (**410**) umfasst.

3. Speichersystem (**400**) gemäß Anspruch 2, wobei das Speichersystem (**400**) ferner folgendes Merkmal aufweist:

einen Eingabe/Ausgabe-Bus (I/O-Bus), der wirksam die Speichersteuerung (**404**) und jeden der Speicherchips (**406, 408**) koppelt.

4. Speichersystem (**400**) gemäß Anspruch 1, bei dem zumindest ein weiterer der Speicherchips (**406, 408**) ferner zumindest eine Spannungserzeugungsschaltung (**416**) umfasst, die betreibbar ist, um die zumindest eine im Speicher erzeugte Versorgungsspannung zu erzeugen.

5. Speichersystem (**400**) gemäß Anspruch 1, wobei das Speichersystem (**400**) eine Speicherplatte ist.

6. Speichersystem (**400**) gemäß Anspruch 1, bei dem die erste Spannungserzeugungsschaltung (**410**) eine Mehrzahl von im Speicher erzeugten Versorgungsspannungen ( $V_1, V_2, V_3$ ) erzeugt, wobei eine der im Speicher erzeugten Versorgungsspannungen die zumindest eine im Speicher erzeugte Versorgungsspannung ist, und

bei dem der Leistungsbus (**414**) die Mehrzahl von im Speicher erzeugten Versorgungsspannungen an die Speicherchips (**406, 408**) liefert.

7. Speichersystem (**400**) gemäß Anspruch 6, bei dem zumindest eine der Mehrzahl von im Speicher erzeugten Versorgungsspannungen (V1, V2, V3) an die Speichersteuerung (**404**) geliefert wird.

8. Speichersystem (**400**) gemäß Anspruch 1 oder 7, bei dem die Speichersteuerung (**404**) keine Spannungserzeugungsschaltungsanordnung zum Erzeugen jeglicher Versorgungsspannungen zur Verwendung durch jeglichen der Speicherchips (**406, 408**) umfasst.

9. Speichersystem (**400**) gemäß Anspruch 1, wobei das Speichersystem (**400**) ferner folgende Merkmale aufweist:

einen von der Speichersteuerung (**404**) und den Speicherchips (**406, 408**) getrennten Spannungsregler, wobei der Spannungsregler eine im Regler erzeugte Versorgungsspannung erzeugt, die an den Leistungsbus geliefert wird, und

bei dem die im Regler erzeugte Versorgungsspannung über den Leistungsbus (**414**) an die Speicherchips (**406, 408**) geliefert wird.

10. Elektronisches System, das folgende Merkmale aufweist:

eine Datenerfassungsvorrichtung; und

eine Datenspeichervorrichtung, die auf entfernbar Weise mit der Datenerfassungseinheit gekoppelt ist, wobei die Datenspeichervorrichtung durch die Datenerfassungsvorrichtung erfasste Daten speichert und wobei die Datenspeichervorrichtung ein Speichersystem (**400**) gemäß einem der vorhergehenden Ansprüche umfasst.

11. Elektronisches System gemäß Anspruch 10, bei dem die Datenerfassungsvorrichtung entweder eine Kamera, eine Netzwerkkarte oder ein Netzwerkgerät, ein in der Hand zu haltender oder Notebook-Computer, eine Set-Top-Box, ein in der Hand zu haltendes oder anderes kleines Audiowiedergabegerät/aufzeichnungsgerät oder eine medizinische Überwachungseinrichtung ist.

Es folgen 5 Seiten Zeichnungen

## Anhängende Zeichnungen

FIG 1

(STAND DER TECHNIK)

FIG 2

FIG 3

FIG 4

FIG 5