(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2007-335581

(P2007-335581A)

(43) 公開日 平成19年12月27日(2007.12.27)

(51) Int.CI.

H01L 23/12

(2006.01)

F 1

H01L 23/12

H01L 23/12

501W

テーマコード(参考)

Q

審査請求 未請求 請求項の数 15 O L (全 22 頁)

(21) 出願番号

特願2006-164822 (P2006-164822)

(22) 出願日

平成18年6月14日 (2006.6.14)

(71) 出願人 503121103

株式会社ルネサステクノロジ

東京都千代田区大手町二丁目6番2号

(74) 代理人 100080001

弁理士 筒井 大和

(72) 発明者 田上 哲治

東京都千代田区丸の内二丁目4番1号 株式会社ルネサステクノロジ内

(54) 【発明の名称】半導体装置の製造方法

(57) 【要約】 (修正有)

【課題】半導体装置の多ピン化を図りつつ配線に電解めっきを施すことを可能にする手段を提供する。

【解決手段】正面のデバイス領域3v内においてボンディングリード3jの内側領域に給電用のリング状の共通配線3pが形成されたパッケージ基板3を用いることで、共通配線3pに接続する複数の給電用の第1めっき線3r及び第4めっき線3uを配置できるため、裏面の全てのランド部に対して電解めっき用の給電線を配置することができる。これにより、パッケージ基板3の正面と前記裏面の配線に対して電解めっきを施すことが可能になり、前記裏面の周囲に亘って複数列の前記ランド部が設けられていても全ての前記ランド部に電解めっきを施すことができ、その結果、半導体装置の多ピン化を図りつつ、配線に電解めっきを施すことができる。

【選択図】図9

3j: ボンディングリード(ボンディング電極)

3p: 共通配線

3r: めっき線(給電用引き出し配線)

3s: 第1めっき線(給電用引き出し配線)

3u: 第4めっき線(給電用引き出し配線)

3v: デバイス領域

**【特許請求の範囲】****【請求項 1】**

(a) 主面に形成された複数のボンディング電極と、前記主面に対向する裏面に形成された複数のランド部と、前記主面の前記ボンディング電極の内側領域に形成された給電用の共通配線と、前記共通配線と電気的に接続する複数の給電用引き出し配線とを有する配線基板のデバイス領域内において、前記給電用引き出し配線を介して給電を行って各配線及び電極にメッキを形成した後、前記共通配線と前記給電用引き出し配線とを分離して形成された前記配線基板を準備する工程と、

(b) 前記配線基板の前記主面上に半導体チップを搭載する工程と、

(c) 前記半導体チップの電極と前記配線基板の前記ボンディング電極とを電気的に接続する工程と、

(d) 前記配線基板の前記ランド部に外部端子を設ける工程とを有する半導体装置の製造方法。

**【請求項 2】**

請求項 1 記載の半導体装置の製造方法において、前記共通配線は、リング状に形成されていることを特徴とする半導体装置の製造方法。

**【請求項 3】**

請求項 2 記載の半導体装置の製造方法において、前記(a)工程で準備する前記配線基板は、前記リング状の共通配線とその内側領域が除去された基板であることを特徴とする半導体装置の製造方法。

**【請求項 4】**

請求項 1 記載の半導体装置の製造方法において、前記共通配線と接続し、かつ前記配線基板の端部まで延在する前記給電用引き出し配線が前記主面の角部に配置されていることを特徴とする半導体装置の製造方法。

**【請求項 5】**

請求項 1 記載の半導体装置の製造方法において、前記配線基板は、前記ランド部に接続する引き出し配線によって平面方向に引き出されて配置された第1ビア部と、前記ランド部上に配置された第2ビア部とを有していることを特徴とする半導体装置の製造方法。

**【請求項 6】**

請求項 1 記載の半導体装置の製造方法において、前記(a)工程で準備する前記配線基板は、エッチングによって前記共通配線と前記給電用引き出し配線とが切断分離された基板であることを特徴とする半導体装置の製造方法。

**【請求項 7】**

請求項 1 記載の半導体装置の製造方法において、前記(a)工程で、エッチングによって前記共通配線と前記給電用引き出し配線とが切断分離された前記配線基板を準備し、前記(b)工程において、前記エッチングによって形成された凹部を覆うように前記半導体チップを前記配線基板の主面上に搭載することを特徴とする半導体装置の製造方法。

**【請求項 8】**

請求項 1 記載の半導体装置の製造方法において、前記配線基板の裏面に複数列で前記複数のランド部が設けられ、前記複数列のうち最内周と内側から2列目の前記ランド部は、これらのランド部に接続する引き出し配線によって平面方向に引き出されてビア部と接続し、さらに主面側で内方に延在して前記共通配線に接続する前記給電用引き出し配線と前記ビア部とが接続されていることを特徴とする半導体装置の製造方法。

**【請求項 9】**

請求項 1 記載の半導体装置の製造方法において、前記複数の給電用引き出し配線に繋がるそれぞれの前記ランド部は、信号用のランド部であることを特徴とする半導体装置の製造方法。

**【請求項 10】**

請求項 1 記載の半導体装置の製造方法において、前記複数の給電用引き出し配線のうち、電源もしくはグランド用の複数の給電用引き出し配線は、前記共通配線の一部によって

10

20

30

40

50

繋がっていることを特徴とする半導体装置の製造方法。

【請求項 1 1】

請求項 1 記載の半導体装置の製造方法において、前記配線基板の裏面に 5 列で前記複数のランド部が設けられていることを特徴とする半導体装置の製造方法。

【請求項 1 2】

請求項 1 記載の半導体装置の製造方法において、前記配線基板の裏面に 5 列で前記複数のランド部が設けられ、前記 5 列のうち最外周の前記ランド部に、前記配線基板の端部まで延在する前記給電用引き出し配線が接続されていることを特徴とする半導体装置の製造方法。

【請求項 1 3】

請求項 1 記載の半導体装置の製造方法において、前記配線基板の裏面に 5 列で前記複数のランド部が設けられ、前記 5 列のうち外側から 2 列目と 3 列目の前記ランド部は、これらのランド部に接続する引き出し配線によって平面方向に引き出されてビア部と接続し、さらに正面側で前記配線基板の端部まで延在する前記給電用引き出し配線と前記ビア部とが接続されていることを特徴とする半導体装置の製造方法。

【請求項 1 4】

請求項 1 記載の半導体装置の製造方法において、前記配線基板の裏面に 5 列で前記複数のランド部が設けられ、前記 5 列のうち最内周と内側から 2 列目の前記ランド部は、これらのランド部に接続する引き出し配線によって平面方向に引き出されてビア部と接続し、さらに正面側で内方に延在して前記共通配線に接続する前記給電用引き出し配線と前記ビア部とが接続されていることを特徴とする半導体装置の製造方法。

【請求項 1 5】

請求項 1 記載の半導体装置の製造方法において、前記(c)工程の後、樹脂封止して前記半導体チップを樹脂体によって覆うことを特徴とする半導体装置の製造方法。

【発明の詳細な説明】

【技術分野】

【0 0 0 1】

本発明は、半導体装置の製造技術に関し、特に、給電線が設けられた配線基板を用いる半導体装置の製造に適用して有効な技術に関する。

【背景技術】

【0 0 0 2】

製品部分に、第 2 の導体配線パターンの複数を短絡させるための第 1 の引き出し配線、及びこれを途中で短絡させないで接続させるための繋ぎ線が設けられ、第 1 の導体配線パターンを介して第 2 の導体配線パターンに電解めっき皮膜が施された後、繋ぎ線が削除されて複数の第 2 の導体配線パターン間が断線される削除部を有してなる技術がある（例えば、特許文献 1 参照）。

【0 0 0 3】

また、基板の一面側に、外側ヴィア群よりも外側に形成しためっき用バスラインと、外側ヴィア群の各ヴィアとを導体パターンによって接続すると共に、基板の他面側に、内側ヴィア群よりも内側に形成し、内側ヴィア群の各ヴィアと導体パターンによって接続しためっき用共通ラインと、基板の他面側で且つ外側ヴィア群よりも外側に形成しためっき用バスラインから給電して電解めっきを施す技術がある（例えば、特許文献 2 参照）。

【特許文献 1】特開 2005-79129 号公報（図 1）

【特許文献 2】特開 2002-50715 号公報（図 1）

【発明の開示】

【発明が解決しようとする課題】

【0 0 0 4】

配線基板上に半導体チップが搭載された BGA (Ball Grid Array) 等の半導体装置では、その高機能化に伴って、ボンディング電極の数が増大する傾向にある。近年では、半導体装置の小型化も同時に要求されるため、配線基板の正面に設けられた複数のボンディン

10

20

30

40

50

グ電極は複数列に配置しなければ、配線基板サイズを低減することは困難である。

#### 【0005】

ここで、配線基板上の配線には、基板の製造段階でめっき形成が行われる。このめっき形成工程は、後のワイヤボンディング工程におけるワイヤとボンディング電極との接合強度を向上させるために、ボンディング電極の表面上にめっき膜を形成するものである。また、ランド部においても半田ボールとの接合強度を向上するためのめっき膜を形成するものもある。めっきは、例えば、ニッケルと金のそれぞれの膜からなる。めっき形成の方法としては、主に、電解めっき方法と無電解めっき方法とが知られているが、電解めっき方法によって形成されためっき膜の方が無電解めっき方法に比較してワイヤボンディングに対する接合強度が高く、さらに電解めっき方法の方がめっきの膜厚をコントロールするのが容易である等のメリットがある。10

#### 【0006】

したがって、電解めっき方法を採用することが好ましいが、電解めっき方法を採用する場合には、配線基板にめっき用の給電線を設けることが必要になる。

#### 【0007】

ところが、小型化・多ピン化が図られたBGA等では、上記したように配線基板の正面側においてボンディング電極が複数列に亘って配置されている。そのため、配線基板の外周に沿って複数のボンディング電極、及び複数のボンディング電極と複数の給電用引出し配線を介して繋がる複数のスルーホール部が密集して配置されているため、内周（内側）に配置された複数のボンディング電極に電解を供給するための給電線を配線基板の端部（各辺）まで延在させることは困難である。一方、配線基板の裏面側においても半導体装置の小型化・多ピン化に伴い、半田ボールが設けられる複数のランド部が格子状に配置され、隣り合うランド部間のピッチも狭ピッチ化（例えば、ピッチ0.4mm）されるため、隣り合ったランド部の間に給電線を通すことは困難な状態である。すなわち、配線基板の裏面側において、全てのランド部（特に配線基板の中心側に配置されたランド部）に対して基板の端部まで延在する電解めっき用の給電線を配置することは困難であるという問題が発生する。20

#### 【0008】

なお、前記特許文献1（特開2005-79129号公報）及び特許文献2（特開2002-50715号公報）には、電解めっき方法によるめっき形成が開示されており、両者とも基板の裏面の内側箇所（中央部）で電解めっき用の引き出し配線の共通化を行っている。30

#### 【0009】

この構造で、半導体装置が多ピンの場合、例えば、基板の裏面に全周に亘って5列でランド部が設けられている場合には、内側から2列目以降のランド部からはスペースが無いため内側（中央部）に向けて給電用の引き出し配線を配置することができず、中央部での電解めっき用の引き出し配線の共通化が図れない。同様に、基板の裏面には全周に亘って5列でランド部が設けられているため、中央部の共通配線から基板外側に向けて電解めっき用の引き出し配線を引き出すこともできない（最外周列に配置された隣り合うランド部の間は、最外周列から2列目に配置されたランド部と繋がる給電線が通せるだけのスペースしかない）。さらに、基板の裏面に共通配線が設けられていると、レジスト（ソルダレジスト）塗布後、エッティングによって共通配線を分離した後、共通配線の端部がレジストから露出した状態となり、吸湿の問題や導電性異物付着による電気的ショートの問題等が発生する。40

#### 【0010】

本発明の目的は、半導体装置の多ピン化を図りつつ、配線に電解めっきを施すことを可能にすることができる技術を提供することにある。

#### 【0011】

また、本発明の他の目的は、半導体装置の小型化を図りつつ、配線に電解めっきを施すことを可能にすることができる技術を提供することにある。50

**【 0 0 1 2 】**

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

**【課題を解決するための手段】****【 0 0 1 3 】**

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、以下のとおりである。

**【 0 0 1 4 】**

すなわち、本発明は、主面に形成された複数のボンディング電極と、主面のボンディング電極の内側領域に形成された給電用の共通配線と、共通配線と電気的に接続する複数の給電用引き出し配線とを有する配線基板のデバイス領域内において、給電用引き出し配線を介して給電を行って各配線及び電極にメッキを形成した後、共通配線と給電用引き出し配線とを分離して形成された配線基板を準備する工程を含むものである。さらに、配線基板の主面上に半導体チップを搭載する工程と、半導体チップの電極と配線基板のボンディング電極とを電気的に接続する工程と、配線基板の裏面のランド部に外部端子を設ける工程とを含んでいる。

**【発明の効果】****【 0 0 1 5 】**

本願において開示される発明のうち、代表的なものによって得られる効果を簡単に説明すれば、以下のとおりである。

**【 0 0 1 6 】**

主面のデバイス領域内においてボンディング電極の内側領域に給電用の共通配線が形成された配線基板を用いることで、共通配線に接続する複数の給電用引き出し配線を配置することができ、全てのランド部に対して電解めっき用の給電線を配置することができる。その結果、配線基板の裏面の全周に亘って複数列のランド部が設けられていても全てのランド部に電解めっきを施すことができ、半導体装置の多ピン化を図りつつ、配線に電解めっきを施すことができる。

**【発明を実施するための最良の形態】****【 0 0 1 7 】**

以下の実施の形態では特に必要なとき以外は同一または同様な部分の説明を原則として繰り返さない。

**【 0 0 1 8 】**

さらに、以下の実施の形態では便宜上その必要があるときは、複数のセクションまたは実施の形態に分割して説明するが、特に明示した場合を除き、それらはお互いに無関係なものではなく、一方は他方の一部または全部の変形例、詳細、補足説明などの関係にある。

**【 0 0 1 9 】**

また、以下の実施の形態において、要素の数など（個数、数値、量、範囲などを含む）に言及する場合、特に明示した場合および原理的に明らかに特定の数に限定される場合などを除き、その特定の数に限定されるものではなく、特定の数以上でも以下でも良いものとする。

**【 0 0 2 0 】**

以下、本発明の実施の形態を図面に基づいて詳細に説明する。なお、実施の形態を説明するための全図において、同一の機能を有する部材には同一の符号を付し、その繰り返しの説明は省略する。

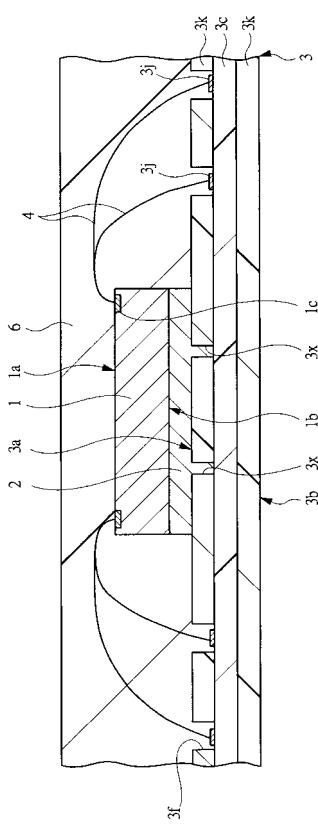

**【 0 0 2 1 】****（実施の形態）**

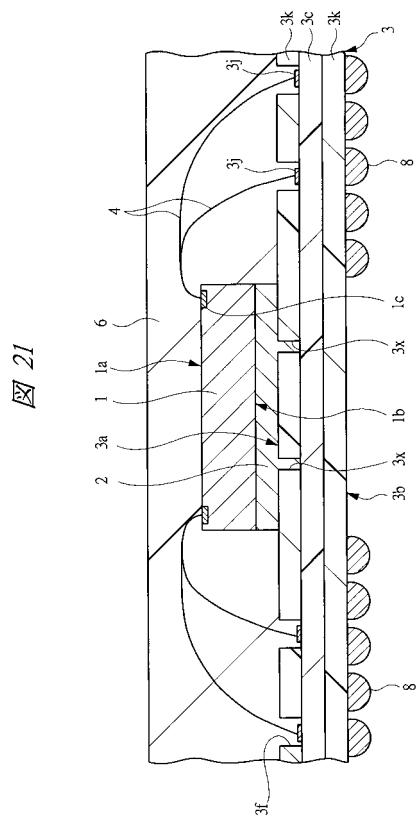

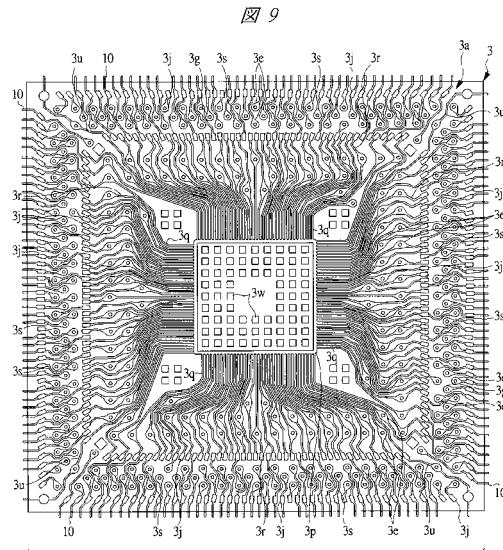

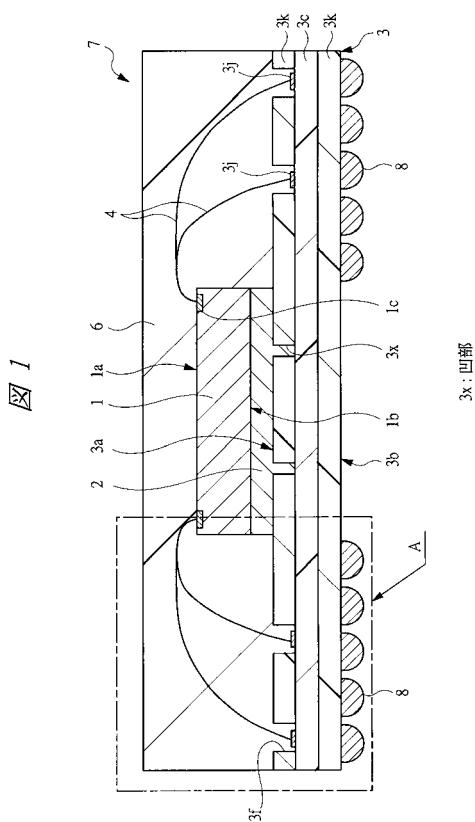

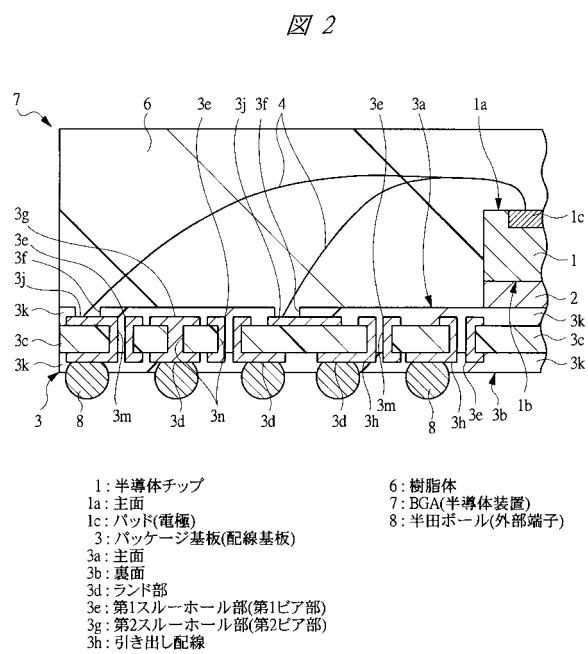

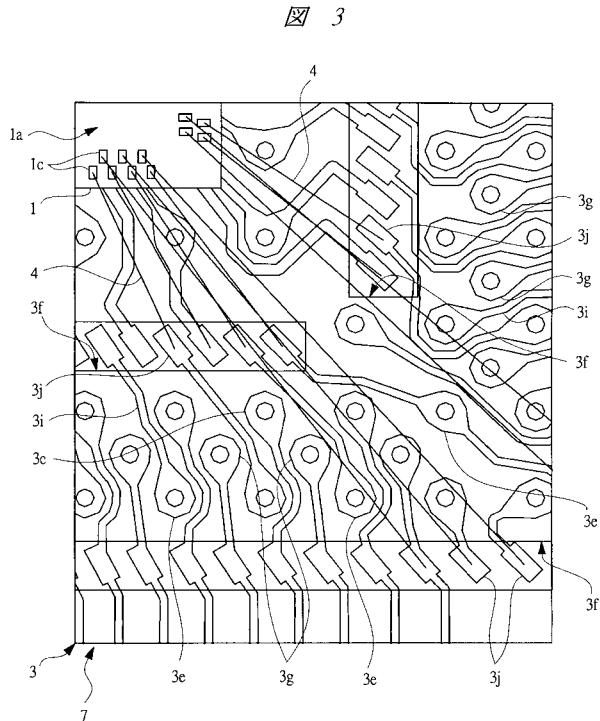

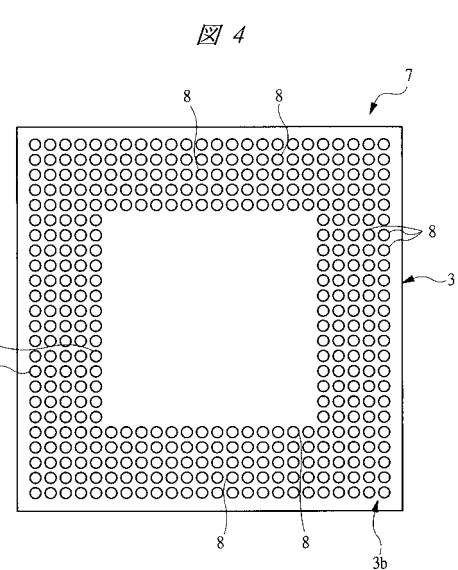

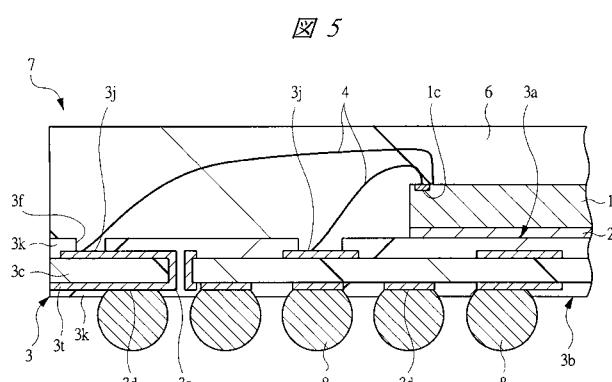

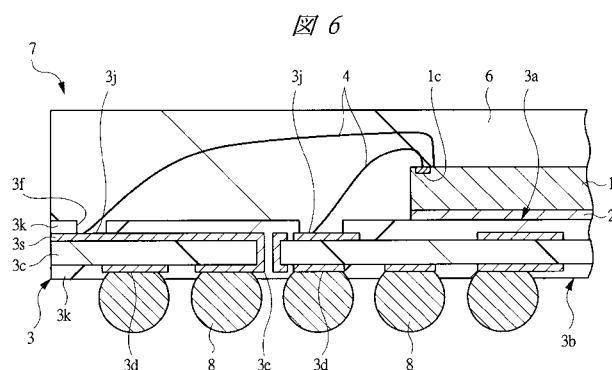

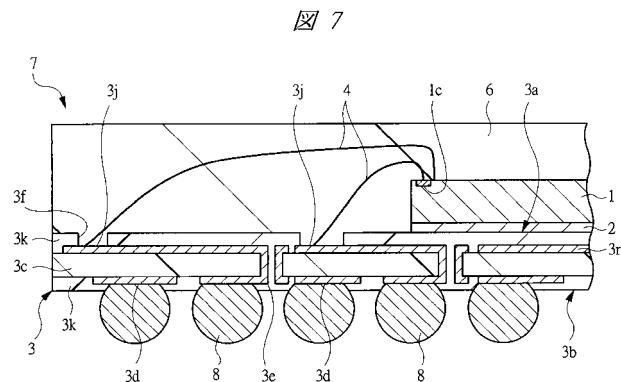

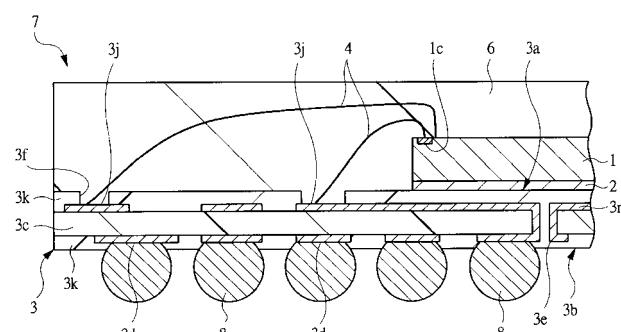

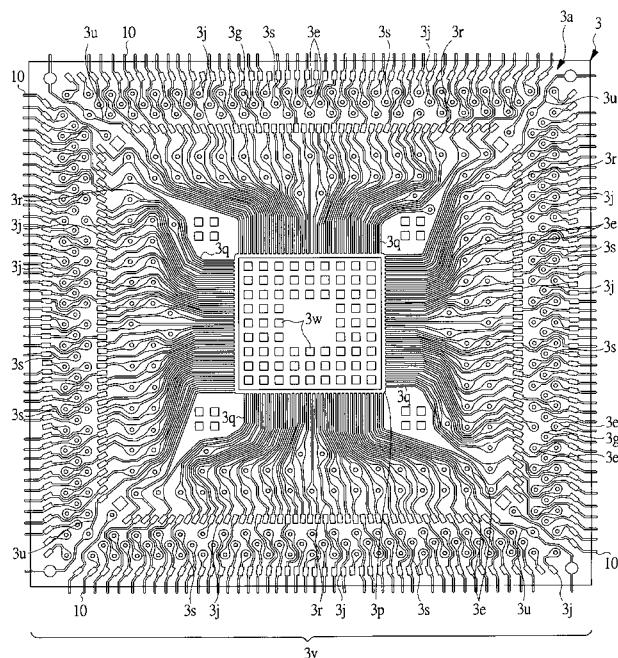

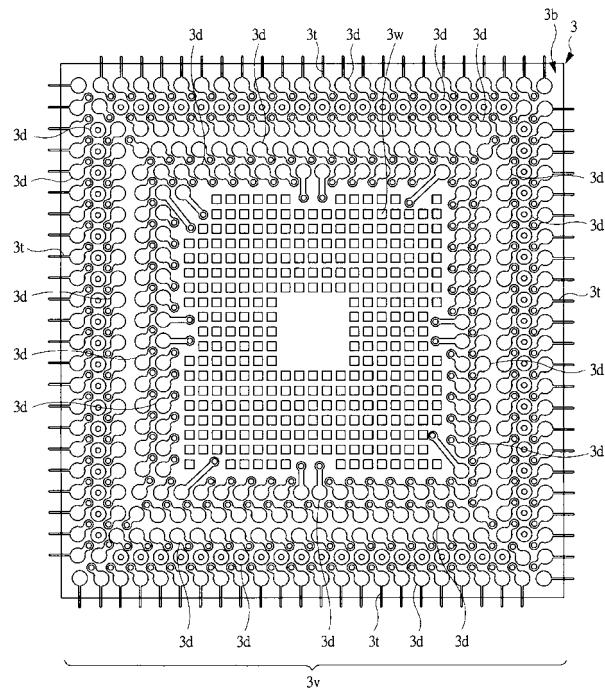

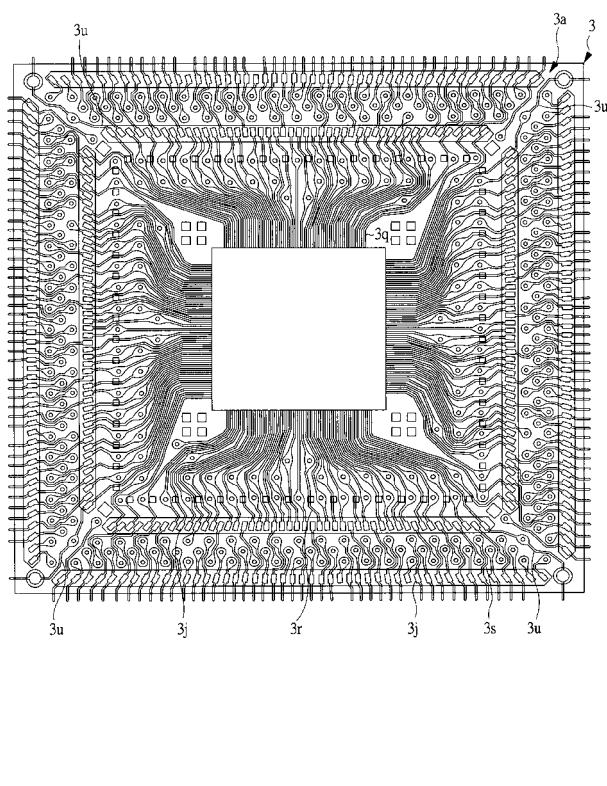

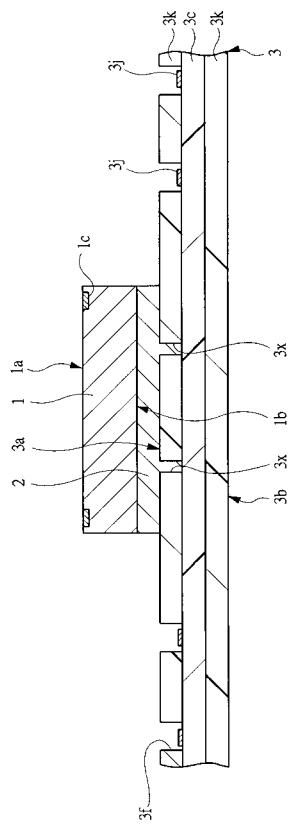

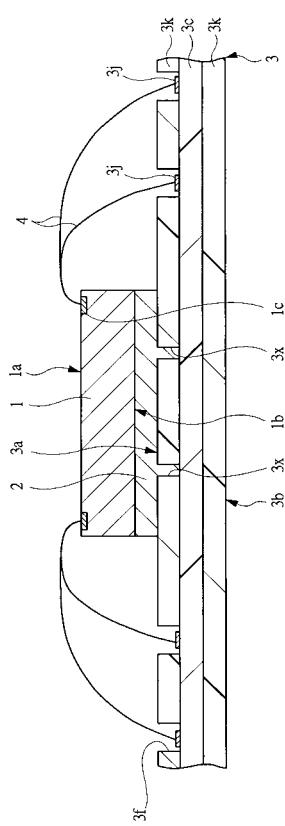

図1は本発明の実施の形態の半導体装置の構造の一例を示す断面図、図2は図1に示すA部の構造を示す拡大部分断面図、図3は図1に示す半導体装置の内部構造の一例を樹脂体を透過して示す拡大部分平面図、図4は図1に示す半導体装置の構造の一例を示す裏面

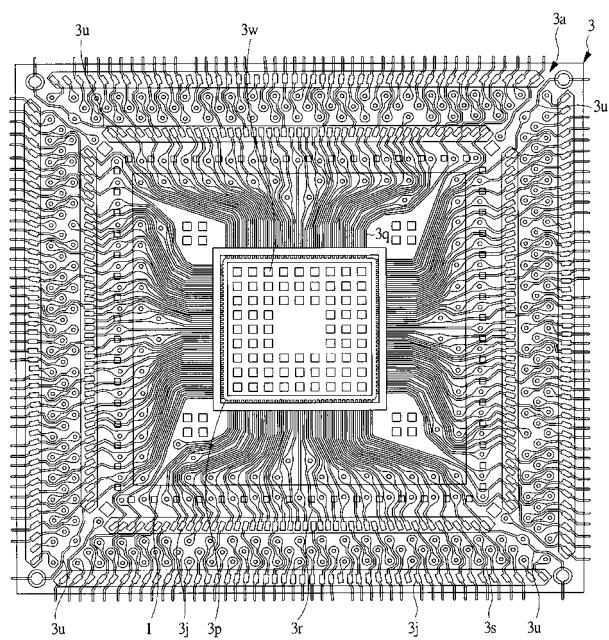

図である。また、図5は図1に示す半導体装置の最外周のランド部と接続する給電線の一例を示す拡大部分断面図、図6は外側から2列目のランド部と接続する給電線の一例を示す拡大部分断面図、図7は外側から3列目と4列目のランド部と接続する配線の一例を示す拡大部分断面図、図8は図1に示す半導体装置の最内周のランド部と接続する給電線の一例を示す拡大部分断面図である。さらに、図9は図1に示す半導体装置の組み立てで用いられる配線基板の正面の配線パターンの一例を示す平面図、図10は図9に示す配線基板の裏面の配線パターンの一例を示す平面図、図11は図9に示す配線基板の正面側のレジスト膜の開口部のレイアウトの一例を示す平面図、図12は図9に示す配線基板の製造におけるエッチバック時のマスクエリアの一例を示す平面図である。

## 【0022】

また、図13は図9に示す配線基板の製造におけるエッチバック後の構造の一例を示す平面図、図14は図9に示す配線基板の製造におけるエッチバック前の処理手順の一例を示す断面図、図15は図9に示す配線基板の製造におけるエッチバック前後の処理手順の一例を示す断面図、図16は変形例の配線基板の正面の配線パターンを示す平面図である。さらに、図17は図1に示す半導体装置の組み立てにおけるダイボンディング後の構造の一例を示す断面図、図18は図17に示すダイボンディング後の構造の一例を示す平面図、図19はワイヤボンディング後の構造の一例を示す断面図、図20は樹脂モールディング後の構造の一例を示す断面図、図21は半田ボール搭載後の構造の一例を示す断面図である。

## 【0023】

本実施の形態の半導体装置は、配線基板上に半導体チップ1が搭載された樹脂封止型の半導体パッケージであり、本実施の形態ではその一例として、図1～図4に示すようなBGA7を取り上げて説明する。なお、BGA7は、例えば、300ピン以上の外部端子を有しており、比較的ピン数が多い半導体パッケージである。図4に示すように、配線基板の裏面3bに複数の外部端子である半田ボール8が格子状に配置されて取り付けられている。

## 【0024】

図1～図4に示すBGA7の構造について説明すると、パッケージ基板(配線基板)3と、パッケージ基板3の正面3a上に搭載された半導体チップ1と、半導体チップ1のパッド(電極)1cとパッケージ基板3の正面3aのボンディングリード(ボンディング電極)3jとを電気的に接続する導電性のワイヤ4と、パッケージ基板3の裏面3bのランド部3d上に設けられた複数の半田ボール(外部端子)8と、樹脂体6とからなる。

## 【0025】

半導体チップ1は、例えば、シリコンなどによって形成され、その正面1aには集積回路が形成されている。また、半導体チップ1におけるその厚さと交差する平面形状は方形状であり、本実施の形態では正方形である。さらに、図3に示すように正面1aの周縁部には集積回路と電気的に接続される複数のパッド1cが形成されている。また、このパッド1cと、パッケージ基板3の正面3a上に形成されたボンディングリード3jとが導電性のワイヤ4によってそれぞれ電気的に接続されている。このワイヤ4は、例えば、金線等である。

## 【0026】

また、半導体チップ1は、図1に示すように、その裏面1bが、ペースト剤やダイアタチフィルム等の接着剤2を介してパッケージ基板3に固着され、正面1aを上方に向かた状態でパッケージ基板3に搭載されている。

## 【0027】

また、樹脂体6は、例えば、エポキシ系樹脂等からなるとともに、パッケージ基板3の正面3a側に形成されており、半導体チップ1及び複数の導電性のワイヤ4を樹脂封止するものである。

## 【0028】

また、パッケージ基板3の裏面3bに設けられた複数の外部端子である半田ボール8は

10

20

30

40

50

、例えば、P b - S n 等の半田からなり、図 4 に示すように、パッケージ基板 3 の裏面 3 b に、例えは 5 列配置で格子状に設けられている。

#### 【 0 0 2 9 】

ここで、パッケージ基板 3 は、図 1 及び図 2 に示すように、主面 3 a と、主面 3 a に対向する裏面 3 b と、コア材 3 c と、主面 3 a に形成された複数の導体パターンと、裏面 3 b に形成された複数の導体パターンと、前記導体パターンの一部を除いてこの導体パターンを覆う絶縁膜であるソルダレジスト膜 3 k とを有している。

#### 【 0 0 3 0 】

すなわち、本実施の形態のパッケージ基板 3 は、その主面 3 a と裏面 3 b とに前記導体パターンが形成された 2 層配線構造の基板である。なお、ソルダレジスト膜 3 k は、主面 3 a 及び裏面 3 b それぞれの表面に形成されており、主面 3 a 側では、ソルダレジスト膜 3 k の開口部 3 f に複数のボンディングリード 3 j が露出している。一方、裏面 3 b では、それぞれのランド部 3 d がソルダレジスト膜 3 k から露出している。

#### 【 0 0 3 1 】

また、パッケージ基板 3 の主面 3 a には、図 3 及び図 9 に示すように、複数のボンディングリード 3 j と、それぞれのボンディングリード 3 j に配線部 3 i を介して接続された複数のビア部（スルーホール）とが形成されている。複数のボンディングリード 3 j は、主面 3 a の周縁部及びその内側に 2 列に並んで配置されている。

#### 【 0 0 3 2 】

一方、パッケージ基板 3 の裏面 3 b には、図 2 及び図 10 に示すように複数のランド部 3 d と、複数のランド部 3 d のうちの一部のランド部 3 d に接続された引き出し配線 3 h と、引き出し配線 3 h に接続されたビア部（スルーホール）とがそれぞれ複数形成されている。その際、複数のランド部 3 d は裏面 3 b の外周部に沿って 5 列に並んで形成されている。

#### 【 0 0 3 3 】

したがって、主面 3 a に設けられた複数のボンディングリード 3 j は、それぞれ対応するビア部（スルーホール）を介して裏面 3 b のランド部 3 d に電気的に接続されている。なお、主面 3 a のボンディングリード 3 j 、配線部 3 i 、ビア部（スルーホール）、裏面 3 b のランド部 3 d 、配線部 3 i 及びビア部（スルーホール）等の導体パターンは、例えは、銅合金によって形成されており、前記導体パターンには電解めっき処理が施されている。すなわち、各導体パターンには、給電線が接続されており、給電線から給電を行って各導体パターンにおけるソルダレジスト膜 3 k から露出した面（複数のボンディングリード、複数のランド部）にめっき膜 3 z を形成している。めっき膜 3 z は、例えは、金とニッケルのそれぞれの膜からなる。

#### 【 0 0 3 4 】

また、パッケージ基板 3 におけるその厚さと交差する平面形状は方形状であり、本実施の形態では正方形である。

#### 【 0 0 3 5 】

さらに、本実施の形態のパッケージ基板 3 に形成された複数のビア部は、図 2 に示すように、ランド部 3 d に接続する引き出し配線 3 h によって平面方向に引き出されて配置された第 1 スルーホール部（第 1 ビア部）3 e と、ランド部 3 d 上（ランド部 3 d と平面的に重なる位置）に配置された、所謂パッドオンビアと呼称される第 2 スルーホール部（第 2 ビア部）3 g とを含んでいる。すなわち、パッケージ基板 3 には、ランド部 3 d から平面方向に引き出されて配置された第 1 スルーホール部 3 e と、パッドオンビアである第 2 スルーホール部 3 g とが混載して設けられており、それぞれが複数個設けられている。

#### 【 0 0 3 6 】

また、第 1 スルーホール部 3 e 及び第 2 スルーホール部 3 g 等の前記ビア部は、コア材 3 c に形成された貫通孔 3 n と、貫通孔 3 n の内部に配置された導体膜 3 m とから形成されている。すなわち、貫通孔 3 n の内壁に導体膜 3 m が形成されており、この導体膜 3 m が主面 3 a 側の導体パターン及び裏面 3 b 側の導体パターンと接続されている。なお、貫

通孔 3 n の内部には、導体膜 3 m のみが充填されていてもよいし、また、導体膜 3 m と絶縁膜が配置されていてもよい。

#### 【 0 0 3 7 】

ここで、パッドオンビア（第 2 スルーホール部 3 g ）は、ランド部 3 d 上に直接配置するため、引き出し配線 3 h を必要とせず、したがって、狭い限られた領域であっても配置することができる。すなわち、パッドオンビアは、配線密度が比較的高い領域に形成する方がより有効である。

#### 【 0 0 3 8 】

しかしながら一方で、パッドオンビアは、引き出し配線 3 h によって引き出される第 1 スルーホール部 3 e と比較すると、その内部に配置される導体部の強度が低い。そのため、ワイヤボンディング時には付与されるボンディング荷重（キャピラリによる荷重）により、引き出し配線 3 h を介して平面的に離間されたビア部と接続されるボンディングリード 3 j と比較して、導体膜 3 m にクラックが生じ易い。したがって、パッドオンビアを基板内の応力が集中し易い領域に配置することは避けた方が好ましく、応力が集中しにくい領域に配置することが好ましい。

#### 【 0 0 3 9 】

すなわち、パッケージ基板 3 において、引き出し配線 3 h によって引き出される第 1 スルーホール部 3 e と、パッドオンビアである第 2 スルーホール部 3 g の混載を行う際には、パッドオンビアの配置位置を考慮して設けなければならない。

#### 【 0 0 4 0 】

例えば、パッケージ基板 3 においては、パッケージ基板 3 の中心から遠い位置ほど、応力が集中し易い。したがって、パッドオンビアである第 2 スルーホール部 3 g は、引き出し配線 3 h によって引き出される第 1 スルーホール部 3 e に比べてその内部に配置される導体膜 3 m の強度が低いため、最外周のランド部 3 d には第 2 スルーホール部 3 g を配置しない方が好ましい。すなわち、複数のランド部 3 d のうち、最外周に配置されたランド部 3 d は、引き出し配線 3 h を介して第 1 スルーホール部 3 e に接続されている方が好ましい。

#### 【 0 0 4 1 】

さらに、図 3 に示すように、パッケージ基板 3 の半導体チップ 1 の対角線の延長線上には強度が高い第 1 スルーホール部 3 e が配置されていることが好ましい。すなわち、パッケージ基板 3 の対角線上を含む角部付近には応力が集中し易いため、比較的内部の導体膜 3 m の強度が高い第 1 スルーホール部 3 e を配置し、パッドオンビア（第 2 スルーホール部 3 g ）は配置しないようにすることが好ましい。

#### 【 0 0 4 2 】

また、図 2 に示すように、パッケージ基板 3 の正面 3 a に形成されたボンディングリード 3 j は、引き出し配線 3 h を介して平面的に離間した位置に形成されたビア部（第 1 スルーホール部 3 e、第 2 スルーホール部 3 g ）と接続されることが好ましい。これは、上記したようにビアの直径がボンディングリード 3 j の配置ピッチよりも大きいため、ボンディングリード 3 j の直下にビア部を形成してパッケージ基板 3 の裏面 3 b 側に引き回すとした場合、1つのビア部が複数のボンディングリード 3 j に跨って配置されてしまうため、隣り合ったボンディングリード同士がビア部を介して電気的にショートしてしまう。このショートを抑制するためにはボンディングリード 3 j の配置ピッチをビア部の直径よりも大きくしなければならず、これによりパッケージ基板 3 の小型化が困難となる。したがって、ボンディングリード 3 j にはパッドオンビア（第 2 スルーホール部 3 g ）を配置しないで、引き出し配線 3 h を介して平面的に離間した位置に形成されたビア部（第 1 スルーホール部 3 e、第 2 スルーホール部 3 g ）を接続されることが好ましい。

#### 【 0 0 4 3 】

また、本実施の形態の B G A 7 では、パッケージ基板 3 の正面 3 a には、図 9 に示すように、複数のボンディングリード 3 j が周縁部とその内側に 2 列に並んで配置されている。一方、裏面 3 b には、図 10 に示すように、複数のランド部 3 d が外周部に沿って 5 列

10

20

30

40

50

に並んで形成されている。

【0044】

すなわち、図9に示すように、主面3aの最外周には複数のボンディングリード(第1のボンディングリード)3jが配置されており、さらに、その内側に3列に亘って第1スルーホール部3e及び第2スルーホール部3g等のビア部が配置され、その内側に複数のボンディングリード(第2のボンディングリード)3jが配置されている。そこで、ボンディングリード3jの直下で、かつ最外周にはパッドオンビア(第2スルーホール部3g)は配置しない方が好ましいため、裏面3bの最外周には、引き出し配線3hを介して第1スルーホール部3eに接続するランド部3dが配置されている。

【0045】

また、内側のボンディングリード3jは、外側から3列目のランド部3dと4列目のランド部3dの間に応するパッケージ基板3の主面3a側に配置されており、ボンディングリード3jの直下にはパッドオンビア(第2スルーホール部3g)を配置しない方が好ましいため、主面3aの内側のボンディングリード3jの直下にも、引き出し配線3hを介して第1スルーホール部3eに接続するランド部3dが配置されており、この列のランド部3dが外側から3列目のランド部3dの列となっている。

【0046】

したがって、パッケージ基板3の裏面3bにおいて、複数のパッドオンビア(第2スルーホール部3g)は、主面3a側の最外周のボンディングリード3jと内側のボンディングリード3jの間の領域に対応して、5列のランド部3dのうちの外側から2列目のランド部3d上に配置されている。

【0047】

その際、裏面3bにおいて、最外周のランド部3dに接続する引き出し配線3hは内側に向けて引き出され、その端部に第1スルーホール部3eが接続されており、かつ外側から3列目のランド部3dに接続する引き出し配線3hは外側に向けて引き出され、その端部に第1スルーホール部3eが接続されている。

【0048】

したがって、外側から2列目のランド部3d上に配置されたパッドオンビア(第2スルーホール部3g)は、外側から内側に向かう方向において第1スルーホール部3eによって挟まれて配置されている。

【0049】

すなわち、最外周のランド部3dと外側から3列目のランド部3dとの間の領域には、外側から2列目のランド部3dと、加えてその周囲に第1スルーホール部3eが配置されているため、非常に高密度配線の領域となる。したがって、この領域に引き出し配線3hを必要としないパッドオンビアである第2スルーホール部3gを配置することは、配線スペースが少ないとする観点からも非常に有効である。

【0050】

なお、最外周のボンディングリード3jから外方に延在するめっき線10は、デバイス領域3vの外周の境界線を跨がってさらに外方に延在している。

【0051】

ここで、本実施の形態のBGA7のパッケージ基板3では、前述したように主面3aのボンディングリード3j、配線部3i、ビア部(スルーホール)、裏面3bのランド部3d、配線部3i及びビア部(スルーホール)等の導体パターンに電解めっき処理が施されている。すなわち、各導体パターンには、給電線が接続されており、給電線から給電を行って各導体パターンの表面にめっきを形成している。

【0052】

ただし、前述したようにパッケージ基板3の裏面3bにおいて、全周に亘って5列にランド部3dが敷き詰められているとともに、最外周のランド部3dと外側から3列目のランド部3dとの間の領域には、外側から2列目のランド部3dと、加えてその周囲に第1スルーホール部3eが配置されているため、非常に高密度配線の領域となっており、各導

10

20

30

40

50

体パターンに単純に給電線を接続するのは困難な状態となっている。

#### 【0053】

そこで、本実施の形態のBGA7のパッケージ基板3では、給電線の引き回しに特徴を有している。

#### 【0054】

図9に示すように、パッケージ基板3のデバイス領域3vの正面3aには、全周に亘って2列で形成された複数のボンディングリード3jの内側領域に給電用の共通配線3pが形成されている。この共通配線3pは、リング状に形成されている。すなわち、パッケージ基板3の正面3aにおいて、2列配置で形成された複数のボンディングリード3jの内側領域の中央付近に四角形を成すリング状の給電用の共通配線3pが形成されている。10

#### 【0055】

さらに、四角形のリング状の給電用の共通配線3pには、その4つの辺それぞれに対して複数のめっき線（給電用引き出し配線）3qが接続され、4方向の基板外方に向かってそれぞれ複数のめっき線3qが延在しており、各めっき線3qは、2列配置のボンディングリード3jのうちの内側のボンディングリード3jや、さらにその内側に配置された第1スルーホール部3e（ビア部）に接続されている。

#### 【0056】

したがって、裏面3bの5列に配置されたランド部3dのうち、最内周と内側から2列目のランド部3dは、ビア部を介して正面3aのめっき線3q（第1めっき線3r）に接続され、この第1めっき線3rが共通配線3pに接続されており、また、外側から2列目と3列目のランド部3dは、ビア部を介して正面3aの第2めっき線3sに接続され、この第2めっき線3sがパッケージ基板3の端部まで延在している。さらに、最外周のランド部3dは、裏面3bにおいてランド部3dに接続する第3めっき線3tがパッケージ基板3の端部まで直接延在している。ここで、図9に示すように、最外周のランド部3dにおいて、パッケージ基板3の外周のボンディングリード（第1ボンディングリード）3jと電気的に接続される場合には、最外周のランド部3dはビア部を介してパッケージ基板3の正面3aの外周のボンディングリード3jに接続し、さらに外周のボンディングリード3jから外方に延在するめっき線10に接続してもよい。20

#### 【0057】

また、正面3aの2列のボンディングリード3jのうち外側のボンディングリード3jはこれと接続するめっき線10がパッケージ基板3の端部まで直接延在しており、一方、内側のボンディングリード3jでは、第1めっき線3rによって共通配線3pに接続されているものと、第1スルーホール部3eを介して裏面3b側でパッケージ基板3の端部まで延在しているものとが混在している。30

#### 【0058】

さらに、パッケージ基板3の正面3aの4つの角部には共通配線3pから基板端部まで延在する第4めっき線3uが設けられている。

#### 【0059】

したがって、本実施の形態のパッケージ基板3では、裏面3bの最外周～3列目までのランド部3d、さらに正面3aの外側のボンディングリード3j及び一部の内側のボンディングリード3jについては、基板の端部まで延在する給電線を介して直接給電が行われ、裏面3bの最内周～2列目までのランド部3d及び正面3aの一部の内側のボンディングリード3jについては、第4めっき線3u、共通配線3p及び第1めっき線3rを介して給電が行われる。40

#### 【0060】

ここで、裏面3bのランド部3dの配線引き回しの詳細について説明する。まず、図5及び図10に示すように、パッケージ基板3の裏面3bの最外周の各ランド部3dには、パッケージ基板3の端部まで延在する第3めっき線3tがそれぞれ接続されている。すなわち、最外周のランド部3dは、基板の端部までが極めて近いため、直接外部と第3めっき線3tによって接続されている。したがって、めっき形成の際の最外周の各ランド部350

dに対する給電は、外部から裏面3bの第3めっき線3tを介して直接行われる。

#### 【0061】

また、図6及び図10に示すように、パッケージ基板3の裏面3bの外側から2列目及び3列目のランド部3dには、それぞれ第2スルーホール部3g(図2参照、パッドオンビア)と引き出し配線3hが接続されている。外側から2列目のランド部3dは第2スルーホール部3gを介して主面3a側でパッケージ基板3の端部まで延在する第2めっき線3sと接続されている。また、3列目のランド部3dは、引き出し配線3hによって平面方向に引き出されて第1スルーホール部3eと接続し、さらに主面3a側でパッケージ基板3の端部まで延在する第2めっき線3sと接続されている。すなわち、外側から2列目及び3列目のランド部3dは、第2スルーホール部3gまたは第1スルーホール部3eによって主面3a側に引き出され、主面3a側で第2めっき線3sによって基板の端部に引き出されている。10

#### 【0062】

したがって、めっき形成の際の外側から2列目及び3列目のランド部3dに対する給電は、外部から主面3aの第2めっき線3sと、第2スルーホール部3gまたは第1スルーホール部3eと、裏面3bの引き出し配線3hとを介して行われる。

#### 【0063】

また、図7、8及び図10に示すように、パッケージ基板3の裏面3bの最内周と内側から2列目のランド部3dには引き出し配線3hが接続され、この引き出し配線3hによって平面方向に引き出されて第1スルーホール部3eと接続し、さらに主面3a側で内方に延在して共通配線3pに接続する第1めっき線3rと接続されている。すなわち、最内周及び内側から2列目のランド部3dは、第1スルーホール部3eによって主面3a側に引き出され、主面3a側で第1めっき線3rによって共通配線3pに接続されている。20

#### 【0064】

さらに、図9に示すように、パッケージ基板3の主面3aの4つの角部には共通配線3pに接続し、かつこの共通配線3pから基板端部まで延在する第4めっき線3uが設けられている。すなわち、パッケージ基板3の主面3aの角部には、ボンディングリード3jの2列の配列上、スペースが僅かに残されているため、そこに基板の端部から共通配線3pまで延在する第4めっき線3uが設けられている。このスペースが残されている理由について説明すると、図1に示すように、パッケージ基板3の主面3aの内側のボンディングリード3jの列に囲まれた領域には、半導体チップ1が搭載される。半導体チップ1を搭載した後、半導体チップ1のパッド1cとパッケージ基板3の外側のボンディングリード3j及び内側のボンディングリード3jとをそれぞれ複数のワイヤ4を介して電気的に接続する。このとき、半導体チップ1の1辺の長さは、パッケージ基板3の1辺の長さよりも短いため、外側のボンディングリード3jがパッケージ基板3の角部付近まで配置されていると、パッケージ基板3の角部付近のボンディングリード3jと、それに対応する半導体チップ1のパッド1cとを電気的に接続するワイヤ4の長さが長くなるので、安定したワイヤ4のループ形状を形成することが困難となる。このような理由から、パッケージ基板3の角部付近にはボンディングリード3jが配置されていないため、パッケージ基板3の内側のめっき線3qを引き回すことが可能である。一方、パッケージ基板3の裏面3b側は、図4に示すように、複数のランド部3dが格子状に配置されているため、パッケージ基板3の裏面3bにおける角部付近は、主面3a側の角部付近に比べるとスペースがない。30

#### 【0065】

したがって、めっき形成の際の最内周及び2列目のランド部3dに対する給電は、外部から主面3aの第4めっき線3uと共に共通配線3pと第1めっき線3rと第1スルーホール部3eと裏面3bの引き出し配線3hを介して行われる。40

#### 【0066】

このようにパッケージ基板3の裏面3bにおいてその全周に亘って5列にランド部3dが敷き詰められ、かつ最外周のランド部3dと外側から3列目のランド部3dとの間の領50

域が高密度配線になっている多ピンのBGA7であっても、各ランド部3dに給電線用のめっき線3qを接続することができ、めっき用の給電を行って配線及び電極上に金及びニッケルのめっき膜を形成することが可能である。

#### 【0067】

なお、めっき形成後は、エッチング（エッチバック）により、リング状の共通配線3pと、これに繋がる複数の第1めっき線3r及び第4めっき線3uとを切断分離してそれらの給電用引き出し配線を絶縁する。

#### 【0068】

また、共通配線3pに接続された複数の第1めっき線3rに繋がるそれぞれのランド部3dは、信号用のランド部3dであってもよいし、電源もしくはグランド用のランド部3dであってもよい。すなわち、信号用のランド部3dである場合には、めっき形成後、エッチングによって共通配線3pと第1めっき線3rとを切断分離することで、それぞれの第1めっき線3r及びこれに繋がるランド部3dが絶縁されるため、これらのランド部3dが信号用のものであってもよい。また、電源もしくはグランド用のランド部3dである場合には、これらのランド部3dが第1めっき線3rを介して共通配線3pに接続する一部のみを、エッチングせずに残すことにより、電源もしくはグランドとして共通化することが可能であり、電源もしくはグランドの安定化を図ることができる。

#### 【0069】

なお、図9及び図10に示すように、パッケージ基板3の正面3a及び裏面3bの略中央には複数の小さな四角形のダミーパターン3wが設けられている。これらのダミーパターン3wは基板の空きスペースに略均等な間隔で複数設けられており、これによって基板における局所的な応力集中を緩和して基板の反りを低減することができる。

#### 【0070】

次に、図14及び図15に示す製造フローにしたがって、給電用引き出し配線を切断分離するエッチバックを含むパッケージ基板3の形成方法について説明する。

#### 【0071】

まず、図14のステップS1に示すように、両面銅張板準備を行う。すなわち、コア材3cの表裏両面に銅材3yが張り付けられた板材を準備する。その後、ステップS2に示すドリル加工を行って複数の貫通孔3nを形成する。すなわち、ドリル加工によって所定の位置に複数の貫通孔3nを形成する。

#### 【0072】

その後、ステップS3に示すスルーホールメッキ形成を行う。ここでは、電解めっきによって前記板材の表裏面及び貫通孔3n内に金とニッケルのめっき膜3zをそれぞれ形成する。その際、本実施の形態のパッケージ基板3では、その各ランド部3dに給電線用のめっき線3qが直接もしくは共通配線3pを介して電気的に接続されているため、めっき用の給電を行うことで、各配線及び電極上に金及びニッケルのめっき膜3zを形成することができる。

#### 【0073】

その後、ステップS4に示すレジスト塗布を行う。ここでは、レジストを塗布して表裏面のめっき膜3zを覆うようにレジスト膜5を形成する。その後、ステップS5に示すパターンングを行う。すなわち、パターンに合わせてレジスト膜5の所定箇所を開口させる。

#### 【0074】

その後、ステップS6に示す銅エッチングを行う。ここでは、ステップS5のパターンングで開口した箇所の下部のめっき膜3zと銅材3yをエッチングによって除去する。その後、ステップS7に示すレジスト除去を行う。ここでは、ステップS4で表裏面に形成したレジスト膜5を除去する。

#### 【0075】

これによって、図9及び図10に示す表裏面の配線パターンが形成される。

#### 【0076】

10

20

30

40

50

その後、図15のステップS8に示すSR(ソルダレジスト膜3k)塗布を行う。すなわち、めっき膜3zの表裏面と開口された箇所とにソルダレジスト膜3kを塗布する。

#### 【0077】

その後、ステップS9に示す露光現像を行う。ここでは、最終的にエッチバックを行う箇所を含む所定の複数箇所の露光現像を行って、ソルダレジスト膜3kに図11に示すよう開口部3fを形成する。その後、ステップS10に示すフィルム貼り付けを行う。ここでは、エッチバックを行う箇所(基板の正面3a側の共通配線3pの周囲)のみ開口したフィルム9を、ソルダレジスト膜3kの上から貼り付ける。すなわち、図12に示すように、エッチバックを行う領域のみをリング状に開口させ、その他の領域をフィルム9で覆う。

10

#### 【0078】

その後、ステップS11に示すエッチング(エッチバック)を行う。ここでは、エッチングによって所定箇所の銅材3yとめっき膜3zを除去する。すなわち、図12に示すようにマスクであるフィルム9で覆った状態でエッチングを行い(図12の斜線部がフィルム9)、これによって共通配線3pと、第1めっき線3r及び第4めっき線3uとを切斷分離する。

#### 【0079】

その後、ステップS12に示すフィルム剥離を行う。すなわち、表裏面のフィルム9を剥がすことにより、図13に示すように共通配線3pの周囲にリング状に凹部3xが形成され、その結果、リング状の共通配線3pと、第1めっき線3r及び第4めっき線3uとが切斷分離する。

20

#### 【0080】

その後、ステップS13に示す表面処理を行う。ここではソルダレジスト膜3kの不要な開口部3fを埋める処理を施す。

#### 【0081】

これにより、パッケージ基板3の製造完了となる。

#### 【0082】

次に、図16に示す本実施の形態の変形例について説明する。

#### 【0083】

図16の変形例は、図15のステップS11のエッチバックで、リング状の共通配線3pとその内側領域全てが除去されたものであり、これによって、共通配線3pとこれに繋がる第1めっき線3r及び第4めっき線3uとを分離したものである。すなわち、エッチバックの領域としては、図13に示すように共通配線3pの周囲をリング状にエッチングして、共通配線3pとこれに繋がる第1めっき線3r及び第4めっき線3uを切斷分離してもよいし、図16の変形例に示すように、リング状の共通配線3pとその内側領域全てをエッチングして、共通配線3pとこれに繋がる第1めっき線3r及び第4めっき線3uを分離してもよい。

30

#### 【0084】

ただし、共通配線3pの内側のダミーパターン3wは、残しておいた方が好ましい。すなわち、図13に示すように、共通配線3pの周囲をリング状にだけエッチングして、複数のダミーパターン3wはそのまま残すことにより、基板の反りを低減することができる。

40

#### 【0085】

次に、本実施の形態のBGA7の組み立てについて説明する。

#### 【0086】

まず、パッケージ基板3のデバイス領域3vにおいて、共通配線3pとめっき線3qを介して給電を行って各配線及び電極にメッキを形成した後、共通配線3pとめっき線3q(第1めっき線3r及び第4めっき線3u)を分離して形成されたパッケージ基板3を準備する。すなわち、正面3a側のデバイス領域3v内に図13に示す配線パターンが形成され、一方、裏面3b側のデバイス領域3v内に図10に示す配線パターンが形成され

50

た多数個取り基板（パッケージ基板3）を準備する。なお、各デバイス領域には、図2に示すようなランド部3dから引き出し配線3hによって引き出された第1スルーホール部3eと、ランド部3d上に配置された第2スルーホール部3g（パッドオンビア）とが混載されている多数個取り基板を準備する。

#### 【0087】

その後、ダイボンディングを行って、図17及び図18に示すように、パッケージ基板3の正面3a上に接着剤2を介して半導体チップ1を固着する。その際、基板製造工程のエッチング（エッチバック）によって形成された凹部3xを覆うように半導体チップ1をパッケージ基板3の正面3a上に搭載して固着する。なお、図18は半導体チップ1を透過してチップ下部の配線パターンも示す図となっている。10

#### 【0088】

その後、ワイヤボンディングを行う。ここでは、図19に示すように、半導体チップ1の正面1aのパッド1cと、これに対応するパッケージ基板3のボンディングリード3jとを金線等の導電性のワイヤ4によって電気的に接続する。

#### 【0089】

その後、樹脂モールディングを行う。ここでは、パッケージ基板3の正面3aにおいて、複数の半導体チップ1や複数のワイヤ4を一括して覆って樹脂封止する。これによって、図20に示すように、半導体チップ1や複数のワイヤ4が樹脂体6によって覆われる。なお、封止用樹脂は、例えば、熱硬化性のエポキシ系樹脂等である。

#### 【0090】

その後、図21に示すように、ボールマウントを行ってパッケージ基板3の裏面3bの各ランド部3dに外部端子である半田ボール8を接続する。20

#### 【0091】

その後、個片化を行う。例えば、ダイシングによって切断して各BGA7に個片化する。個片化により、デバイス領域3vの外周の境界線を跨がっているめっき線10は、前記境界線で切断されるため、切断後（個片化後）のパッケージ基板3からは外部に突出しない。

#### 【0092】

本実施の形態のBGA（半導体装置）7の製造方法によれば、正面3aのデバイス領域3v内においてボンディングリード3jの内側領域に給電用のリング状の共通配線3pが形成されたパッケージ基板3を用いることで、複数のランド部3dが敷き詰められた裏面3b側に比べて正面3a側はスペースがあるため、共通配線3pに接続する複数の給電用のめっき線3q（第1めっき線3r及び第4めっき線3u）を引き回すことができる。したがって、ビア部（第1スルーホール部3eまたは第2スルーホール部3g）を介して裏面3b側の全てのランド部3dに対して電解めっき用の給電線を配置することが可能になる。30

#### 【0093】

すなわち、正面3a側は2列配置のボンディングリード3jのみであるため、ある程度スペースがある。特に角部にスペースがあるため、共通配線3pに接続し、かつ基板の端部まで延在する第4めっき線3uを角部に配置することで、外部から共通配線3pに対して給電を行う際にもこの第4めっき線3uを介して行うことが可能である。40

#### 【0094】

その結果、パッケージ基板3の正面3aと裏面3bの配線や電極に対して電解めっきを施すことが可能になり、裏面3bの全周に亘って複数列のランド部3dが敷き詰められた半導体装置においても全てのランド部3dに電解めっきを施すことができる。

#### 【0095】

その結果、半導体装置（BGA7）の多ピン化を図りつつ、配線や電極に電解めっきを施すことが可能になる。

#### 【0096】

また、複数列のランド部3dが狭ピッチで配置されていても全てのランド部3dに電解

50

めっきを施すことができるため、半導体装置（BGA7）の小型化を図りつつ、配線や電解めっきを施すことが可能になる。

#### 【0097】

さらに、正面3aに共通配線3pが形成され、かつ電解めっきを施した後、共通配線3pの周囲をエッティング（エッチバック）して共通配線3pと、これに繋がる第1めっき線3r及び第4めっき線3uとを切断分離したパッケージ基板3であることにより、エッチバックによって形成された凹部3xを半導体チップ1の搭載で覆うことができ、さらに、半導体チップ1を封止用樹脂（樹脂体6）によって覆うことができる。

#### 【0098】

これにより、給電用引き出し配線切断による配線の端部が露出することを阻止でき、共通配線3pの周囲をエッチバックして形成された凹部3xからの吸湿の発生、もしくは導電性異物の付着による電気的ショートの発生を防止することができる。10

#### 【0099】

以上、本発明者によってなされた発明を発明の実施の形態に基づき具体的に説明したが、本発明は前記発明の実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることは言うまでもない。

#### 【0100】

例えば、前記実施の形態では、外部端子が半田ボール8の場合を説明したが、外部端子は半田ボール8以外の場合であってもよい。すなわち、共通配線3pを介した給電による電解めっき形成が行われて製造された配線基板を用いて組み立てられる多ピンの半導体装置であれば、LGA（Land Grid Array）等の半導体装置であってもよい。その際、外部端子の配列数は、5列以外の複数列であってもよい。20

#### 【産業上の利用可能性】

#### 【0101】

本発明は、配線基板を有する電子装置の製造技術に好適である。

#### 【図面の簡単な説明】

#### 【0102】

【図1】本発明の実施の形態の半導体装置の構造の一例を示す断面図である。

【図2】図1に示すA部の構造を示す拡大部分断面図である。

【図3】図1に示す半導体装置の内部構造の一例を樹脂体を透過して示す拡大部分平面図である。30

【図4】図1に示す半導体装置の構造の一例を示す裏面図である。

【図5】図1に示す半導体装置の最外周のランド部と接続する給電線の一例を示す拡大部分断面図である。

【図6】図1に示す半導体装置の外側から2列目のランド部と接続する給電線の一例を示す拡大部分断面図である。

【図7】図1に示す半導体装置の外側から3列目と4列目のランド部と接続する配線の一例を示す拡大部分断面図である。

【図8】図1に示す半導体装置の最内周のランド部と接続する給電線の一例を示す拡大部分断面図である。

【図9】図1に示す半導体装置の組み立てで用いられる配線基板の正面の配線パターンの一例を示す平面図である。40

【図10】図9に示す配線基板の裏面の配線パターンの一例を示す平面図である。

【図11】図9に示す配線基板の正面側のレジスト膜の開口部のレイアウトの一例を示す平面図である。

【図12】図9に示す配線基板の製造におけるエッチバック時のマスクエリアの一例を示す平面図である。

【図13】図9に示す配線基板の製造におけるエッチバック後の構造の一例を示す平面図である。

【図14】図9に示す配線基板の製造におけるエッチバック前の処理手順の一例を示す断50

面図である。

【図15】図9に示す配線基板の製造におけるエッチバック前後の処理手順の一例を示す断面図である。

【図16】変形例の配線基板の正面の配線パターンを示す平面図である。

【図17】図1に示す半導体装置の組み立てにおけるダイボンディング後の構造の一例を示す断面図である。

【図18】図17に示すダイボンディング後の構造の一例を示す平面図である。

【図19】図1に示す半導体装置の組み立てにおけるワイヤボンディング後の構造の一例を示す断面図である。

【図20】図1に示す半導体装置の組み立てにおける樹脂モールディング後の構造の一例を示す断面図である。 10

【図21】図1に示す半導体装置の組み立てにおける半田ボール搭載後の構造の一例を示す断面図である。

#### 【符号の説明】

##### 【0103】

- |     |                     |    |

|-----|---------------------|----|

| 1   | 半導体チップ              |    |

| 1 a | 正面                  |    |

| 1 b | 裏面                  |    |

| 1 c | パッド(電極)             |    |

| 2   | 接着剤                 | 20 |

| 3   | パッケージ基板(配線基板)       |    |

| 3 a | 正面                  |    |

| 3 b | 裏面                  |    |

| 3 c | コア材                 |    |

| 3 d | ランド部                |    |

| 3 e | 第1スルーホール部(第1ビア部)    |    |

| 3 f | 開口部                 |    |

| 3 g | 第2スルーホール部(第2ビア部)    |    |

| 3 h | 引き出し配線              |    |

| 3 i | 配線部                 | 30 |

| 3 j | ボンディングリード(ボンディング電極) |    |

| 3 k | ソルダレジスト膜            |    |

| 3 m | 導体膜                 |    |

| 3 n | 貫通孔                 |    |

| 3 p | 共通配線                |    |

| 3 q | めっき線(給電用引き出し配線)     |    |

| 3 r | 第1めっき線(給電用引き出し配線)   |    |

| 3 s | 第2めっき線(給電用引き出し配線)   |    |

| 3 t | 第3めっき線(給電用引き出し配線)   |    |

| 3 u | 第4めっき線(給電用引き出し配線)   | 40 |

| 3 v | デバイス領域              |    |

| 3 w | ダミーパターン             |    |

| 3 x | 凹部                  |    |

| 3 y | 銅材                  |    |

| 3 z | めっき膜                |    |

| 4   | ワイヤ                 |    |

| 5   | レジスト膜               |    |

| 6   | 樹脂体                 |    |

| 7   | BGA(半導体装置)          |    |

| 8   | 半田ボール(外部端子)         | 50 |

9 フィルム

10 めっき線

【図1】

【図2】

【図3】

【図4】

【図5】

3t: 第3めっき線(給電用引き出し配線)

【図6】

【図7】

【図8】

【 図 9 】

9

3j: ボンディングリード(ボンディング電極)

3p: 共通配線

3q: めっき線(給電用引き出し配線)

3r: 第1めっき線(給電用引き出し配線)

3s: 第2めっき線(給電用引き出し配線)

3u: 第4めっき線(給電用引き出し配線)

3v: デバイス領域

【 図 1 0 】

☒ 10

【図 1 1】

图 11

【 図 1 2 】

図 12

【図13】

図13

【図14】

図14

【図15】

図15

【図16】

図16

【図17】

【図19】

【図18】

【図20】

【 図 2 1 】