(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5905408号

(P5905408)

(45) 発行日 平成28年4月20日(2016.4.20)

(24) 登録日 平成28年3月25日(2016.3.25)

(51) Int.Cl.

G06F 12/08 (2016.01)

F 1

G06F 12/08 513

G06F 12/08 509F

G06F 12/08 579

請求項の数 27 (全 21 頁)

(21) 出願番号 特願2013-89640 (P2013-89640)

(22) 出願日 平成25年4月22日 (2013.4.22)

(65) 公開番号 特開2013-235576 (P2013-235576A)

(43) 公開日 平成25年11月21日 (2013.11.21)

審査請求日 平成27年10月1日 (2015.10.1)

(31) 優先権主張番号 10-2012-0048455

(32) 優先日 平成24年5月8日 (2012.5.8)

(33) 優先権主張国 韓国 (KR)

早期審査対象出願

(73) 特許権者 390019839

三星電子株式会社

Samsung Electronics

Co., Ltd.

大韓民国京畿道水原市靈通区三星路 129

129, Samsung-ro, Yeongtong-gu, Suwon-si, Gyeonggi-do, Republic

of Korea

(74) 代理人 100086368

弁理士 萩原 誠

(72) 発明者 季 會 鎮

大韓民国ソウル特別市江南区道谷洞 527

番地 道谷レックスレアパート202棟1

103号

最終頁に続く

(54) 【発明の名称】マルチCPUシステムとそれを含むコンピューティングシステム

## (57) 【特許請求の範囲】

## 【請求項1】

マルチCPUプロセッサ(multi-CPU processor)を含み、

前記マルチCPUプロセッサは、

少なくとも第1コア、第1キャッシュ、及び前記第1キャッシュをアクセスするための

第1キャッシュコントローラを含む第1CPUと、

少なくとも第2コア及び第2キャッシュをアクセスするための第2キャッシュコントロ

ーラを含む第2CPUと、を含み、前記第2キャッシュは、共有領域と非共有領域とを備え、

前記第1キャッシュは、前記第2キャッシュの前記共有領域から具現されるマルチCP

Uデータ処理システム。

## 【請求項2】

選択信号に基づいて、前記第1キャッシュコントローラまたは前記第2キャッシュコントローラからデータを前記第1キャッシュに入力する共有回路をさらに含む請求項1に記載のマルチCPUデータ処理システム。

## 【請求項3】

前記第1CPU、前記第2CPU、及び前記第1キャッシュを独立してターンオンまたはターンオフするための複数の制御信号を出力する電力管理ユニットをさらに含む請求項1に記載のマルチCPUデータ処理システム。

## 【請求項4】

10

20

前記電力管理ユニットは、前記第1キャッシュに電源を保持する間に、前記第1キャッシュを除いた前記第1CPUと前記第2CPUとの間で選択的に電源をスイッチする請求項3に記載のマルチCPUデータ処理システム。

【請求項5】

前記第1キャッシュと前記共有回路は、第1SOCに埋設され、前記第1キャッシュを除いた前記第1CPUは、第2SOCに埋設される請求項2に記載のマルチCPUデータ処理システム。

【請求項6】

前記第1キャッシュを除いた前記第1CPUは、第1電力領域に具現され、前記第1キャッシュを除いた前記第2CPUは、第2電力領域に具現され、前記第1キャッシュは、第3電力領域に具現され、10

前記第1電力領域、前記第2電力領域、及び前記第3電力領域のそれぞれは、独立して制御可能な請求項5に記載のマルチCPUデータ処理システム。

【請求項7】

少なくとも第1コア、第1キャッシュ、及び前記第1キャッシュからデータをアクセスするための第1キャッシュコントローラを含む第1CPUと、

少なくとも第2コア及び第2キャッシュからデータをアクセスするための第2キャッシュコントローラを含む第2CPUと、を含み、

前記第1キャッシュは、前記第2キャッシュの共有領域から具現され、

前記第1キャッシュを除いた前記第1CPUは、第1ダイに具現され、前記第2CPUは、第2ダイに具現されるマルチCPUデータ処理システム。20

【請求項8】

選択信号に基づいて、前記第1キャッシュから前記第1キャッシュコントローラまたは前記第2キャッシュコントローラにデータを出力する共有回路をさらに含み、前記共有回路は、前記第2ダイ内に具現される請求項7に記載のマルチCPUデータ処理システム。

【請求項9】

前記共有回路のための複数の制御信号ラインは、前記第1ダイと前記第2ダイとの間に接続して連結される複数のTSV(Through Silicon Via)を含む請求項8に記載のマルチCPUデータ処理システム。

【請求項10】

L1キャッシュと前記第1キャッシュは、共通基板に具現される請求項7に記載のマルチCPUデータ処理システム。30

【請求項11】

少なくとも1つのアドレスラインは、L1キャッシュと前記第1キャッシュとに共通する請求項7に記載のマルチCPUデータ処理システム。

【請求項12】

前記第1キャッシュを除いた前記第1CPUは、第1電力領域に位置し、前記第1キャッシュを除いた前記第2CPUは、第2電力領域に位置し、前記第1キャッシュは、第3電力領域に位置する請求項7に記載のマルチCPUデータ処理システム。

【請求項13】

前記第3電力領域がパワーオンを保持する間に、前記第1電力領域と前記第2電力領域とに電力を選択的に供給する電力管理ユニットをさらに含む請求項12に記載のマルチCPUデータ処理システム。40

【請求項14】

前記マルチCPUデータ処理システムは、スマートフォン、ラップトップPC、またはタブレットPCとして具現される請求項7に記載のマルチCPUデータ処理システム。

【請求項15】

前記第1キャッシュは、L2キャッシュまたはL3キャッシュである請求項7に記載のマルチCPUデータ処理システム。

【請求項16】

50

第 1 C P U が第 1 キャッシュコントローラを通じて第 1 キャッシュをアクセスする段階と、

第 2 C P U が第 2 キャッシュコントローラを通じて第 2 キャッシュをアクセスする段階と、

前記第 1 キャッシュのフラッシング ( f l u s h i n g ) なしに前記第 1 C P U から前記第 2 C P U にキャッシュアクセス動作をスイッチする段階と、を含み、前記第 2 キャッシュは、共有領域と非共有領域とを備え、

前記第 1 キャッシュは、前記第 2 キャッシュの前記共有領域から具現されるマルチ C P U プロセッサを利用したデータ処理方法。

**【請求項 17】**

10

選択信号に基づいて、前記第 1 C P U または前記第 2 C P U から前記第 2 キャッシュに入力されるデータをマルチブレクシング ( M u l t i p l e x i n g ) する段階をさらに含む請求項 16 に記載のマルチ C P U プロセッサを利用したデータ処理方法。

**【請求項 18】**

スヌーピング ( s n o o p i n g ) なしに前記第 1 C P U から前記第 2 C P U にキャッシュアクセス動作をスイッチする段階をさらに含む請求項 16 に記載のマルチ C P U プロセッサを利用したデータ処理方法。

**【請求項 19】**

20

前記第 2 C P U から前記第 1 C P U にキャッシュアクセス動作をスイッチし、前記第 2 キャッシュの非共有領域に対するフラッシング動作を行う段階をさらに含む請求項 16 に記載のマルチ C P U プロセッサを利用したデータ処理方法。

**【請求項 20】**

前記第 2 C P U から前記第 1 C P U にキャッシュアクセス動作をスイッチし、前記第 2 キャッシュの非共有領域に対するスヌーピング動作を行う段階をさらに含む請求項 16 に記載のマルチ C P U プロセッサを利用したデータ処理方法。

**【請求項 21】**

少なくとも第 1 コア、第 1 キャッシュ、前記第 1 キャッシュをアクセスするための第 1 キャッシュコントローラを含む第 1 C P U と、

少なくとも第 2 コア及び前記第 1 キャッシュの保存容量よりも大きな保存容量を有する第 2 キャッシュをアクセスするための第 2 キャッシュコントローラを含む第 2 C P U と、

30

選択信号に基づいて、前記第 1 キャッシュコントローラを通じて前記第 1 コアまたは前記第 2 キャッシュコントローラを通じて前記第 2 コアから前記第 1 キャッシュにデータを伝送するマルチブレクサと、

前記選択信号に基づいて、前記第 1 キャッシュから前記第 1 キャッシュコントローラを通じて前記第 1 コアまたは前記第 2 キャッシュコントローラを通じて前記第 2 コアへデータを伝送するためのデマルチブレクサと、

を含むプロセッサ。

**【請求項 22】**

前記第 1 キャッシュは、前記第 2 キャッシュの共有領域から具現される請求項 21 に記載のプロセッサ。

40

**【請求項 23】**

マルチ C P U プロセッサを含み、

前記マルチ C P U プロセッサは、

少なくとも第 1 コア、第 1 キャッシュ、前記第 1 キャッシュをアクセスするための第 1 キャッシュコントローラを含む第 1 C P U と、

少なくとも第 2 コア及び第 2 キャッシュをアクセスするための第 2 キャッシュコントローラを含む第 2 C P U と、

前記第 1 C P U と前記第 2 C P U とのうち少なくとも 1 つ及び前記第 1 キャッシュに電源を選択的に供給する電力管理ユニット ( P M U ) と、

データバスを通じて前記マルチ C P U プロセッサへの / からのメモリアクセスを制御す

50

るメモリコントローラと、を含み、前記第1キャッシュは、前記第2キャッシュの共有領域から具現されるマルチCPUデータ処理システム。

**【請求項24】**

前記電力管理ユニットは、前記第1キャッシュに電源が供給される間に、前記第1CPUと前記第2CPUとのターンオンまたはターンオフを独立して制御するための複数の制御信号を出力する請求項23に記載のマルチCPUデータ処理システム。

**【請求項25】**

前記第1キャッシュを除いた前記第1CPUは、第1電力領域に位置し、前記第1キャッシュを除いた前記第2CPUは、第2電力領域に位置し、前記第1キャッシュは、第3電力領域に位置する請求項23に記載のマルチCPUデータ処理システム。 10

**【請求項26】**

前記電力管理ユニットは、前記第3電力領域に電源が供給される間に、前記第1電力領域と前記第2電力領域との間で電力を選択的にスイッチする請求項25に記載のマルチCPUデータ処理システム。

**【請求項27】**

前記マルチCPUデータ処理システムは、スマートフォン、ラップトップPC、またはタブレットPCとして具現される請求項23に記載のマルチCPUデータ処理システム。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、マルチCPUシステム(multi-CPU system)に係り、特に、2つのCPUによって物理的に共有されるレベル2(L2)キャッシュを含むマルチCPUシステムとそれを含むコンピューティングシステムとに関する。 20

**【背景技術】**

**【0002】**

CPUの動作周波数が高くなるにつれて、消費電力も増加する。動作周波数及び電圧スケーリング(Dynamic Voltage and Frequency Scaling, DVFS)は、CPU動作周波数と消費電力を適切に調節するための1つの技術である。

**【0003】**

マルチCPUシステムで、キャッシュ(cache)のようなCPU資源の共有は、チップ密度(chip density)を増加させ、消費電力を低下させることができる。しかし、キャッシュ一貫性(cache coherency)を保持するために、増加したプロセスと動作上でトレードオフ(trade-off)が発生する恐れがある。例えば、キャッシュが1つ以上のCPUによって共有される時、データフラッシング(flushing)とスヌーピング(snooping)は、共有キャッシュ使用が1つのCPUから他のCPUにスイッチングされる時に必要である。過度なフラッシング動作とスヌーピング動作は、プロセスレイテンシー(process latency)を増加させ、マルチCPUシステムの全般的な性能に影響を及ぼす可能性がある。 30

**【先行技術文献】**

**【特許文献】**

**【0004】**

**【特許文献1】**韓国特許出願公開2011-1017068号公報

**【特許文献2】**米国特許第6,434,672号公報

**【特許文献3】**米国特許第6,751,706号公報

**【特許文献4】**米国特許出願公開第2009-0049248号明細書

**【発明の概要】**

**【発明が解決しようとする課題】**

**【0005】**

本発明が解決しようとする技術的な課題は、CPUスケーリング時に、L2キャッシュ 50

の一貫性を保持するためのスヌーピング動作のオーバーヘッド(overhead)と前記L2キャッシュのコールドスタート(cold-start)を除去することができるマルチCPUシステムとそれを含むコンピューティングシステムとを提供することにある。また、2つのCPUによって物理的に共有されるL2キャッシュを含むマルチCPUシステムとそれを含むコンピューティングシステムとを提供することにある。

**【課題を解決するための手段】**

**【0006】**

本発明の実施形態によるマルチCPUデータ処理システムは、マルチCPUプロセッサ(multi-CPU processor)を含み、前記マルチCPUプロセッサは、少なくとも1つの第1コア、第1キャッシュ、及び前記第1キャッシュをアクセスするための第1キャッシュコントローラを含む第1CPUと、少なくとも1つの第2コアと第2キャッシュとをアクセスするための第2キャッシュコントローラを含む第2CPUと、を含み、前記第1キャッシュは、前記第2キャッシュの共有領域から具現される。10

**【0007】**

前記マルチCPUデータ処理システムは、選択信号に基づいて、前記第1キャッシュコントローラまたは前記第2キャッシュコントローラからデータを前記第1キャッシュに入力する共有回路をさらに含む。前記マルチCPUデータ処理システムは、前記第1CPU、前記第2CPU、及び前記第1キャッシュを独立してターンオンまたはターンオフするための複数の制御信号を出力する電力管理ユニットをさらに含む。

前記電力管理ユニットは、前記第1キャッシュに電源を保持する間に、前記第1キャッシュを除いた前記第1CPUと前記第2CPUとの間で選択的に電源をスイッチ(switch)する。20

**【0008】**

前記第1キャッシュと前記共有回路は、第1SoC(System on Chip)に具現され、前記第1キャッシュを除いた前記第1CPUは、第2SoCに具現される。前記第1キャッシュを除いた前記第1CPUは、第1電力領域に具現され、前記第1キャッシュを除いた前記第2CPUは、第2電力領域に具現され、前記第1キャッシュは、第3電力領域に具現され、前記第1電力領域、前記第2電力領域、及び前記第3電力領域のそれぞれは、独立して制御可能である。

**【0009】**

本発明の実施形態によるマルチCPUデータ処理システムは、少なくとも1つの第1コア、第1キャッシュ、及び前記第1キャッシュからデータをアクセスするための第1キャッシュコントローラを含む第1CPUと、少なくとも1つの第2コア及び第2キャッシュからデータをアクセスするための第2キャッシュコントローラを含む第2CPUと、を含み、前記第1キャッシュは、前記第2キャッシュの共有領域から具現され、前記第1キャッシュを除いた前記第1CPUは、第1ダイ(die)に具現され、前記第2CPUは、第2ダイに具現される。30

**【0010】**

前記マルチCPUデータ処理システムは、選択信号に基づいて、前記第1キャッシュから前記第1キャッシュコントローラまたは前記第2キャッシュコントローラにデータを出力する共有回路をさらに含み、前記共有回路は、前記第2ダイ内に具現される。前記共有回路のための複数の制御信号ラインは、前記第1ダイと前記第2ダイとの間に接続して連結される複数のTSV(Through Silicon Via)を含む。40

L1キャッシュと前記第1キャッシュは、共通基板に具現される。少なくとも1つのアドレスライン(address line)は、L1キャッシュと前記第1キャッシュとに共通する。

**【0011】**

本発明の実施形態によるマルチCPUプロセッサを利用したデータ処理方法は、1CPUが第1キャッシュコントローラを通じて第1キャッシュをアクセスする段階と、第2CPUが第2キャッシュコントローラを通じて第2キャッシュをアクセスする段階と、前記50

第1キャッシュのフラッシングなしに前記第1CPUから前記第2CPUにキャッシュアクセス動作をスイッチする段階と、を含み、前記第1キャッシュは、前記第2キャッシュの共有領域から具現される。

#### 【0012】

前記方法は、スヌーピングなしに前記第1CPUから前記第2CPUにキャッシュアクセス動作をスイッチングする段階をさらに含む。前記方法は、前記第2CPUから前記第1CPUにキャッシュアクセス動作をスイッチングし、前記第2キャッシュの非共有領域に対するフラッシング動作を行う段階をさらに含む。

前記方法は、前記第2CPUから前記第1CPUにキャッシュアクセス動作をスイッチングし、前記第2キャッシュの非共有領域に対するスヌーピング動作を行う段階をさらに含む。

10

#### 【0013】

本発明の実施形態によるプロセッサは、少なくとも1つの第1コア、第1キャッシュ、前記第1キャッシュをアクセスするための第1キャッシュコントローラを含む第1CPUと、少なくとも1つの第2コアと前記第1キャッシュとの保存容量よりも大きな保存容量を有する第2キャッシュをアクセスするための第2キャッシュコントローラを含む第2CPUと、選択信号に基づいて、前記第1キャッシュコントローラを通じて前記第1コアまたは前記第2キャッシュコントローラを通じて前記第2コアから前記第1キャッシュにデータを伝送するマルチプレクサ(multiplexer)と、前記選択信号に基づいて、前記第1キャッシュから前記第1キャッシュコントローラを通じて前記第1コアまたは前記第2キャッシュコントローラを通じて前記第2コアからデータを伝送するためのデマルチプレクサ(demultiplexer)と、を含む。

20

#### 【0014】

本発明の実施形態によるマルチCPUデータ処理システムは、マルチCPUプロセッサを含み、前記マルチCPUプロセッサは、少なくとも1つの第1コア、第1キャッシュ、前記第1キャッシュをアクセスするための第1キャッシュコントローラを含む第1CPUと、少なくとも1つの第2コアと第2キャッシュとをアクセスするための第2キャッシュコントローラを含む第2CPUと、前記第1CPUと前記第2CPUとのうち少なくとも1つに電源を選択的に供給する電力管理ユニット(PMU)と、データバスを通じて前記マルチCPUプロセッサにノードメモリアクセスを制御するメモリコントローラと、を含み、前記第1キャッシュは、前記第2キャッシュの共有領域から具現される。前記マルチCPUデータ処理システムは、スマートフォン、ラップトップPC、またはタブレットPCとして具現される。

30

#### 【発明の効果】

#### 【0015】

本発明の実施形態による複数のCPUを含むマルチCPUシステムは、L2キャッシュの少なくとも一部を複数のCPUが物理的に共有することによって、マルチCPUシステムの面積を減少させることができる。また、マルチCPUシステムでCPUスケーリングが行われる時、スヌーピング動作のオーバーヘッドを除去するか、または減少させることができる。

40

マルチCPUシステムでCPUスケーリングが行われる時、L2キャッシュのコールドスタートを除去することができる。また、マルチCPUシステムでL2キャッシュの少なくとも一部が、複数のCPUによって物理的に共有されることによって、大量のデータ伝送が可能となる。

#### 【図面の簡単な説明】

#### 【0016】

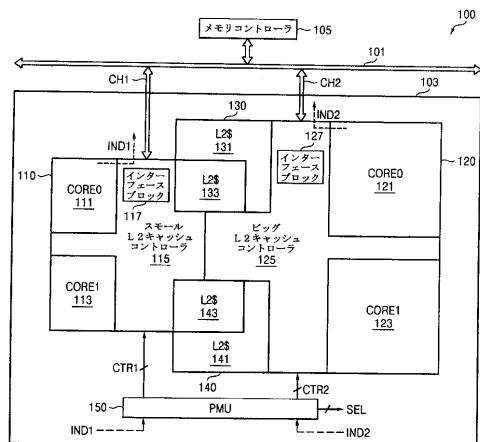

【図1A】本発明の実施形態によるマルチCPUシステムの概略的なブロック図。

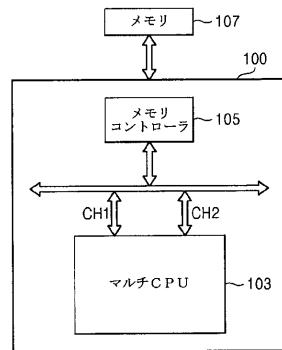

【図1B】図1AのマルチCPUシステムを含むコンピューティングシステムのブロック図。

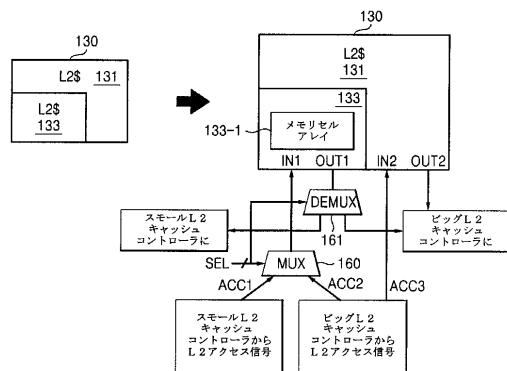

【図2】図1Aの第2CPUに集積されたレベル2(L2)キャッシュの概略的なブロック図。

50

ク図。

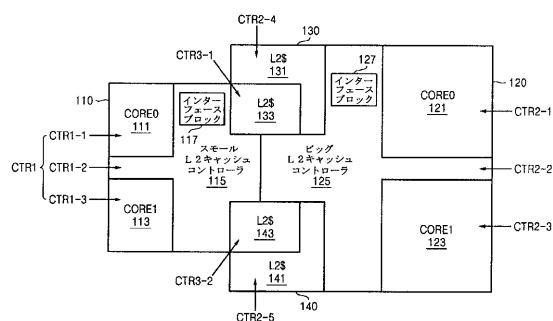

【図3】図1AのマルチCPUの複数の電力領域を示すブロック図。

【図4】図1AのマルチCPUのCPUスケーリングの一実施形態を示す図。

【図5】図4の本発明の実施形態によるCPUスケーリングプロセスのフローチャート。

【図6】図1AのマルチCPUのCPUスケーリングの他の実施形態を説明する概念図。

【図7】本発明の実施形態による他のCPUスケーリングプロセスのフローチャート。

【図8】本発明の他の実施形態によるマルチCPUシステムの概略的なブロック図。

【図9】本発明の実施形態によるボードアセンブリーのブロック図。

【図10】本発明の実施形態によるコンピュータプラットフォームを示す図。

【図11】本発明の実施形態によるマルチCPUシステムを含むコンピューティングシステムの一実施形態を示す図。 10

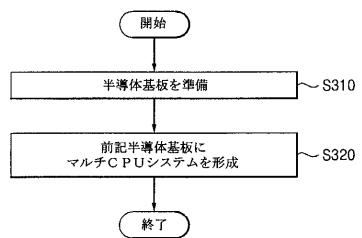

【図12】本発明の実施形態によるマルチCPUシステムを製造する方法を説明するフローチャート。

【発明を実施するための形態】

【0017】

以下、添付した図面を参照して、本発明を詳しく説明する。

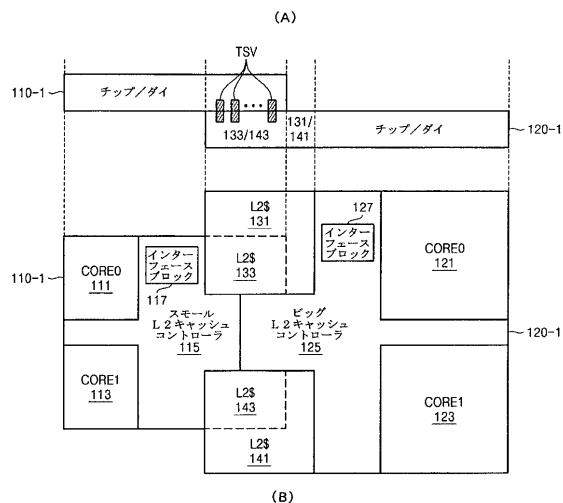

図1Aは、本発明の実施形態によるマルチCPU(multi-Central Processing Unit)システムの概略的なブロック図を示す。図1Aを参照すると、マルチCPUシステム100は、システムバス101、マルチCPU103、及びメモリコントローラ105を含む。 20

ここで、マルチCPUシステム100は、1つのシステムオンチップ(System on Chip、SoC)として具現可能である。例えば、マルチCPUシステム100は、1つのマスク(mask)を用いて具現可能である。

【0018】

マルチCPU103は、第1CPU110と第2CPU120とを含みうる。実施形態によって、マルチCPU103は、電力管理ユニット(Power Management Unit、PMU)150をさらに含みうる。図1Aでは、説明の便宜上、2つのCPU110、120を含むマルチCPU103が示されているが、本発明の概念は、2つ以上のCPUを含むマルチCPUにそのまま適用可能である。

【0019】

第1CPU110は、少なくとも1つの第1CPUコア111、113と第1レベル2(level-2、L2)キャッシュコントローラ115とを含みうる。したがって、第1CPU110は、マルチコアCPUとして具現可能である。少なくとも1つの第1CPUコア111、113は、レベル1(level1、L1)キャッシュ、例えば、命令キャッシュ(instruction cache)とデータキャッシュ(data cache)とを含みうる。少なくとも1つの第1CPUコア111、113は、第1レベル2(L2)キャッシュコントローラ115と通信のための周辺回路をさらに含みうる。

第1L2キャッシュコントローラ115は、第1通信チャネルCH1を通じてシステムバス101とインターフェーシングする第1インターフェースブロック117とを含みうる。 40

【0020】

第2CPU120は、少なくとも1つの第2CPUコア121、123、第2L2キャッシュコントローラ125、及び少なくとも1つのL2キャッシュ130、140を含みうる。したがって、第2CPU120は、マルチコアCPUとして具現可能である。少なくとも1つの第2CPUコア121、123は、L1キャッシュ、例えば、命令キャッシュとデータキャッシュとを含みうる。少なくとも1つの第2CPUコア121、123は、第2L2キャッシュコントローラ125と通信のための周辺回路をさらに含みうる。

【0021】

第2L2キャッシュコントローラ125は、第2通信チャネルCH2を通じてシステムバス101とインターフェーシングする第2インターフェースブロック127とを含みうる。 50

る。この際、第1L2キャッシュコントローラ115と第2L2キャッシュコントローラ125は、構造的に互いに独立して具現され、独立して動作することができる。したがって、各L2キャッシュコントローラ115、125が、システムバス101と通信するためには、別途の通信チャネルCH1、CH2が必要である。

第1CPU110と第2CPU120のそれぞれは、相応するL1キャッシュと相応するL2キャッシュとを含む。L2キャッシュは、データキャッシュであり、L2キャッシュの容量とサイズは、L1キャッシュの容量とサイズよりも大きい。

#### 【0022】

実施形態を示すために、第1CPU110、第1L2キャッシュコントローラ115及び第1L2キャッシュのようなコンポーネント(components)の‘第1グループ’は、‘スマール(small)’グループ、例えば、スマールCPU110、スマールL2キャッシュコントローラ115などに分類される。第2CPU120、第2L2キャッシュコントローラ125及び第2L2キャッシュのようなコンポーネントの‘第2グループ’は、‘ビッグ(big)’グループ、例えば、ビッグCPU120、ビッグL2キャッシュコントローラ125などに分類される。

#### 【0023】

第1CPU110は、各L2キャッシュ133、143を含む。第2CPU120は、各L2キャッシュ130、140を含む。図1Aの発明の実施形態によって、各第1(または、スマール)L2キャッシュ133、143は、第1CPU110と第2CPU120とによって機能的に共有されうる。すなわち、各第1L2キャッシュ133、143は、第1CPU110または第2CPU120によってアクセス(access)されうる。ここで、アクセスは、ライト(write)動作またはリード(read)動作のために必要な動作を意味する。

#### 【0024】

また、各第1(または、スマール)L2キャッシュ133、143は、各第2(または、ビッグ)L2キャッシュ131、141の一部である。例えば、スマールL2キャッシュは、ビッグL2キャッシュの一部から形成されうる。例えば、ビッグL2キャッシュは、2MBメモリ装置であり、スマールL2キャッシュは、スマールCPUとビッグCPUとによって共有され、ビッグL2キャッシュの25%容量、例えば、512KB容量で形成されうる。各第2L2キャッシュ130、140の各非共有領域131及び141は、第2L2キャッシュコントローラ125を通じて第2CPU120によってのみアクセスされうる。例えば、各非共有領域131及び141は、2MBメモリ装置の1.5MBであり得る。

#### 【0025】

第2L2キャッシュコントローラ125は、共有L2キャッシュ133及び143と非共有L2キャッシュ131及び141とを含んだ第2L2キャッシュ130及び140の全部を同時にアクセスすることができる。しかし、共有L2キャッシュ133及び143は、第1L2キャッシュコントローラ115と第2L2キャッシュコントローラ125とによって同時にアクセスすることはできない。

#### 【0026】

PMU150は、第1CPU110から出力された第1指示信号IND1と第2CPU120から出力された第2指示信号IND2とのうち少なくとも1つに基づいて、複数の制御信号CTR1、CTR2、及び/または選択信号SELを使って、スマールCPU110とビッグCPU120とに電力を選択的に供給する。

それぞれの指示信号IND1、IND2は、システムバス101を通じてPMU150に供給されうる。各信号SEL、CTR1、及びCTR2は、1つまたはそれ以上の制御モード信号を含みうる。

#### 【0027】

複数の第1制御信号CTR1に基づいて、第1CPU110は、電力領域(power domain)別に電力供給及び/またはリセット(reset)を独立して制御するこ

10

20

30

40

50

とができる。複数の第2制御信号CTR2に基づいて、第2CPU120は、電力領域別に電力供給及び／またはリセットを独立して制御することができる。また、第1CPU110と第2CPU120は、選択信号SELに応答して、CPUスケーリング(scaling)、すなわち、複数のCPU110、120の間のスイッチング(switching)を制御することができる。

#### 【0028】

図1Aでは、説明の便宜上、各L2キャッシュ130、140の少なくとも一部133、143が、各CPU110、120によって物理的に共有される構造が示されているが、本発明の技術的思想は、L2キャッシュの代りにレベル3(L3)キャッシュが物理的に共有される構造にも適用可能である。例えば、第2CPU120に具現された機能ブロックは、各CPU110、120、例えば、L2キャッシュまたはL3キャッシュによって共有される。前記機能ブロックが、L3キャッシュである時、各L2キャッシュコントローラは、L3キャッシュコントローラに代替されうる。10

#### 【0029】

各CPU110、120は、各通信チャネルCH1、CH2とシステムバス101とを通じてメモリコントローラ105と通信することができる。メモリコントローラ105は、マルチCPUシステムに接続されたメモリ、例えば、メインメモリをアクセスすることができる。説明の便宜上、各要素101、105は、図1AのマルチCPU103の外部に示されているが、各要素101、105は、マルチCPU103の内部に具現されることもある。20

#### 【0030】

図1Bは、図1AのマルチCPUシステムを含むコンピューティングシステムのブロック図である。図1Bを参照すると、前記コンピューティングシステムは、マルチCPUシステム100とメモリ107とを含みうる。前述したように、メモリコントローラ105は、マルチCPUシステム100とメモリ107との間のデータ通信を制御またはインターフェース(interface)することができる。

#### 【0031】

図2は、図1Aの第2CPUに集積されたレベル2(L2)キャッシュの概略的なブロック図である。図1Aと図2とに示したように、L2キャッシュ130は、非共有領域(non-shared region)である専用領域131と共有領域133とを含む。また、L2キャッシュ140は、専用領域141と共有領域143とを含む。各L2キャッシュ130、140の構造は、実質的に同一なので、L2キャッシュ130についての説明は、L2キャッシュ140に適用可能である。30

#### 【0032】

共有領域133または143は、L2キャッシュ130または140の一部に具現され、共有領域133または143は、L2キャッシュ130または140の少なくとも1つのアドレスラインを共有する。前述したように、専用領域131は、第2L2キャッシュコントローラ125によってのみアクセスされ、共有領域133は、選択信号SELによって第1L2キャッシュコントローラ115と第2L2キャッシュコントローラ125とのうち何れか1つが選択的にアクセスすることができる。40

#### 【0033】

共有回路は、第1選択器160と第2選択器161とを含む。実施形態によって、前記共有回路は、ビッグCPU120の内部に具現されるが、共有領域133の外部に具現可能である。他の実施形態によって、第1選択器160と第2選択器161は、共有領域133の内部に具現可能である。例えば、第1選択器160は、マルチプレクサとして具現可能であり、第2選択器161は、デマルチプレクサとして具現可能である。他の実施形態によって、前記共有回路は、第1選択器160を含み、第2選択器161を含まないこともある。

#### 【0034】

第1L2キャッシュコントローラ115が、共有領域133をアクセスしようとする時50

、第1選択器160は、選択信号SELに応答して、第1L2キャッシュコントローラ115から出力された複数の第1アクセス信号ACC1を共有領域133の第1入力ポートIN1に伝送する。

#### 【0035】

第1グループまたはスモールグループによるライト動作のために、第1L2キャッシュコントローラ115は、共有領域133にデータをライトし、複数の第1アクセス信号ACC1、例えば、メモリセルアレイ133-1にデータをライトするために必要なデータと複数の制御信号は、第1選択器16を通じて第1入力ポートIN1に伝送することができる。第1グループによるリード動作のために、第1L2キャッシュコントローラ115は、共有領域133に保存されたデータをリードし、複数の第1アクセス信号ACC1、例えば、メモリセルアレイ133-1からデータをリードするために必要なデータと複数の制御信号は、第1選択器160を通じて第1入力ポートIN1に伝送され、共有領域133の第1出力ポートOUT1から出力されたデータは、第2選択器161を通じて第1L2キャッシュコントローラ115に伝送される。10

#### 【0036】

実施形態によって、第2選択器161が含まれない場合、第1出力ポートOUT1から出力されたデータは、第1L2キャッシュコントローラ115に直接伝送することができる。

L2キャッシュコントローラ125のような第2グループまたはビッググループによって共有領域133にアクセスのために、第1選択器160は、選択信号SELに応答して、第2L2キャッシュコントローラ125から出力された複数の第2アクセス信号ACC2を第1入力ポートIN1に伝送する。例えば、第2L2キャッシュコントローラ125が、共有領域133にデータをライトする時、複数の第2アクセス信号ACC2、例えば、メモリセルアレイ133-1にデータをライトするために必要なデータと複数の制御信号は、第1選択器160を通じて第1入力ポートIN1に伝送される。20

#### 【0037】

第2L2キャッシュコントローラ125が、共有領域133に保存されたデータをリードする時、複数の第2アクセス信号ACC2、例えば、メモリセルアレイ133-1からデータをリードするために必要な複数の制御信号は、第2選択器161を通じて第1入力ポートIN1に伝送され、第1出力ポートOUT1を通じて出力されたデータは、第2選択器161を通じて第2L2キャッシュコントローラ125に伝送される。実施形態によって、第2選択器161が含まれない場合、第1出力ポートOUT1から出力されたデータは、第2L2キャッシュコントローラ125に直接伝送することができる。30

#### 【0038】

第2L2キャッシュコントローラ125が、専用領域131にデータをライトする時、第2L2キャッシュコントローラ125から出力された複数の第3アクセス信号ACC3、例えば、メモリセルアレイ133-1にデータをライトするために必要なデータと複数の制御信号は、専用領域131の第2入力ポートIN2に入力される。

第2L2キャッシュコントローラ125が、専用領域131に保存されたデータをリードする時、複数の第3アクセス信号ACC3、例えば、メモリセルアレイ133-1からデータをリードするために必要な制御信号は、第2入力ポートIN2に直接伝送され、専用領域131の第2出力ポートOUT2を通じて出力されたデータは、第2L2キャッシュコントローラ125に直接伝送される。共有回路は、スモールL2キャッシュコントローラまたはビッグL2キャッシュコントローラによって共有L2キャッシュに/からエラーデータのアクセスを防止するための構造を有する。40

#### 【0039】

図3は、図1AのマルチCPUの複数の電力領域を示すブロック図である。

図1と図3とを参照すると、第1CPU110は、電力領域111、113、及び115を含む。複数の第1制御信号CTR1-1~CTR1-3(集合的に、「CTR1」)のそれぞれは、電力領域111、113、及び115のそれぞれに供給される。

第1制御信号CTR1-1、CTR1-2、及びCTR1-3のそれぞれによって、電力領域111、113、及び115のそれぞれに供給される電力及び／または電力領域111、113、及び115のそれぞれのリセットが独立して制御される。また、第1インターフェースブロック117が、別途の電力領域と定義される時、別途の制御信号が、第1インターフェースブロック117に供給されることもある。前記別途の制御信号は、第1制御信号CTR1に含まれうる。

#### 【0040】

第2CPU120は、電力領域121、123、125、131、133、141、及び143を含む。複数の第2制御信号CTR2-1～CTR2-5（集合的に、「CTR2'）のそれぞれは、電力領域121、125、123、131、及び141のそれぞれに供給される。

10

第2制御信号CTR2-1～CTR2-5のそれぞれによって、電力領域121、125、123、131、133、及び141のそれぞれに供給される電力及び／または電力領域121、125、123、131、133、及び141のそれぞれのリセットが独立して制御される。また、第2インターフェースブロック127が、別途の電力領域と定義される時、別途の制御信号は、第2インターフェースブロック127に供給されうる。前記別途の制御信号は、第2制御信号CTR2に含まれうる。

各共有L2キャッシュ133、143は、各制御信号CTR3-1、CTR3-2によって独立して制御される。各制御信号CTR3-1、CTR3-2は、各制御信号CTR1またはCTR2に含まれることもある。

20

#### 【0041】

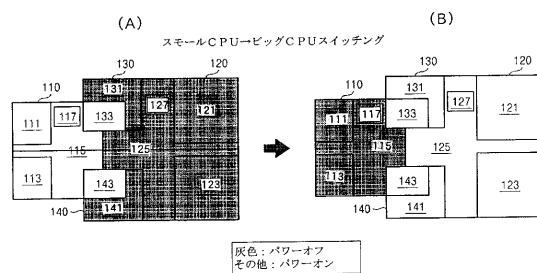

図4の(A)と(B)は、図1AのマルチCPUのCPUスケーリングの一実施形態を示す。

異なるサイズと異なる能力とを有する複数のCPUを含むマルチCPUデータ処理システムで、ピーク能(peak performance)は、複数のCPUの間のスケーリング使用(scaling usage)によって達成されうる。例えば、低いワークロード(low workload)で、スマートCPU110は、最適化された電力使用のために、最高MIPS/mW(Millions of Instructions Per Second per milliwatt)で動作する電力駆動CPU(power-driven CPU)として使われる。

30

#### 【0042】

高い(high)ワークロードで、ビッグCPU120は、たとえ低いMIPS/mWを有しても、ピーク能で動作する性能駆動CPU(performance-driven CPU)として使われる。ここで、CPUスケーリング(CPU scaling)は、同じ動作電圧でスマートCPU110からビッグCPU120にスイッチングする動作またはビッグCPU120からスマートCPU110にスイッチングする動作を意味する。

すなわち、CPUスケーリングは、動作電圧を変化させなくても、消費電力に対するワークロード遂行能力(例えば、MIPS/mW)を変化させるか、または1つのCPU命令を実行するために必要なエネルギー量を変化させることができる。

40

#### 【0043】

図4の(A)を参照すると、スマートCPU110が動作中である時、スマートCPU110の各電力領域111、113、及び115(必要に応じては、117を含む)は、パワーオン状態(POWER ON)であり、ビッグCPU120の各電力領域121～125、131、及び141(必要に応じては、127を含む)は、パワーオフ状態(POWER OFF)である。

#### 【0044】

共有L2キャッシュで動作する各電力領域133、143は、パワーオン状態である。第1L2キャッシュコントローラ115は、各選択器160、161を通じて少なくとも1つの共有領域133、143をアクセスすることができる。スマートCPU110のワ

50

ークロード (work load) が増加すれば、ビッグCPU120へのスケーリングが必要である。スマートCPU110からビッグCPU120にCPUスケーリングまたはCPUスイッチングを行うために、第1CPU110の第1コア111は、第1指示信号IND1を第1通信チャネルCH1とシステムバス101を通じてPMU150に伝送する。

#### 【0045】

PMU150は、第1指示信号IND1に応答して、複数の第1制御信号CTR1、複数の第2制御信号CTR2、及び選択信号SELを出力する。したがって、スマートCPU110の電力領域111、113、及び115のそれぞれは、複数の第1制御信号CTR1のそれそれに応答して、現在作業(job)を中断する。10

同時に、ビッグCPU110の電力領域121、123、125、131、及び141のそれぞれは、複数の第2制御信号CTR2-1～CTR2-5のそれぞれに応答してターンオンされ、前記作業に対する動作を開始または受け継ぐことができる。

#### 【0046】

スマートCPU110によって使われた少なくとも1つの共有領域133、143は、ビッグCPU120のL2キャッシュ130または140のサブセット(subset)として使われる。スマートCPU110からビッグCPU120へのスケーリング過程は、スヌーピング動作(snooping operation)を要しない。また、ビッグCPU120は、少なくとも1つのL2キャッシュ130、140に対するコールドスタートを行わなくても良い。少なくとも1つのL2キャッシュ130または140の少なくとも1つの専用領域131、141は、電力領域121、123、及び125と共に準備(READY)状態になりうる。20

#### 【0047】

スマートCPU110からビッグCPU120へのCPUスケーリングの間に、少なくとも1つの共有領域133、143に供給される電力は、そのままON(ON)状態を保持する。また、スマートCPU110からビッグCPU120へのCPUスケーリングの間に、各選択器160、161は、スイッチされるので、第2L2キャッシュコントローラ125は、各選択器160、161を通じて少なくとも1つの共有領域133、143をアクセスすることができる。

したがって、ビッグCPU120を含む構造は、CPUスケーリングまたはCPUスイッチング直後に最適の性能を発揮することができる。30

#### 【0048】

図4の(B)に示したように、スマートCPU110からビッグCPU120へのCPUスケーリング直後、スマートCPU110の各電力領域111、113、及び115は、パワーオフ状態になり、ビッグCPU120の各電力領域121～125、131、及び141は、パワーオン状態になる。

マルチCPUシステム100が、スヌーピング動作を支援しない時、スマートCPU110は、少なくとも1つの共有領域133、143に保存され、ECC(Error Correction Code)を含まないデータをチャネルCH1、バス101、及びメモリコントローラ105を通じてメモリ107に伝送またはフラッシングする。次いで、ビッグCPU120は、メモリ107に保存されたデータをメモリコントローラ105、バス101、及びチャネルCH2を通じてリードする。ビッグCPU120は、リードされたデータにECCを付け加え、ECC付加されたデータを少なくとも1つの共有領域133、143に保存することができる。40

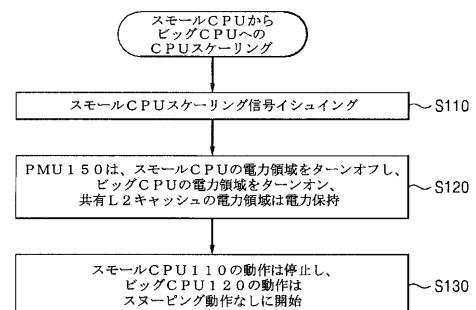

#### 【0049】

図5は、図4の本発明の実施形態によるCPUスケーリングプロセス(scaling process)のフローチャートである。図1Aから図5を参照すると、スマートCPU110からビッグCPU120へのCPUスケーリングは、スマートCPU110が第1指示信号、またはスケーリング信号IND1をイシュuing)することによって始まる(ステップS110)。PMU150は、スマートCPU110の対応50

電力領域の電力をターンオフ (turn-off) し、ビッグCPU120の対応電力領域の電力をターンオン (turn-on) し、各共有L2キャッシュ133、143の電力領域の電力を保持する (ステップS120)。

#### 【0050】

スモールCPU110の動作は停止し、ビッグCPU120の動作はスヌーピング動作なしに始まる (ステップS130)。実施形態によって、スモールCPU110が、少なくとも1つの共有領域133、143に保存されたデータをメモリ107に伝送する時、ビッグCPU120は、必要であれば、メモリ107に保存されたデータを読み出す。

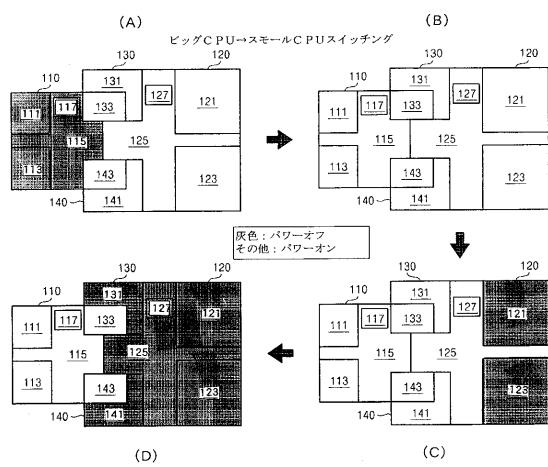

図6の(A)、(B)、(C)、及び(D)は、図1AのマルチCPUのCPUスケーリングの他の実施形態を説明する概念図である。図6の(A)から(D)は、ビッグCPU120からスモールCPU110へのCPUスケーリング過程を示す。

10

#### 【0051】

図1Aから図3、及び図6の(A)から(D)を参照すると、図6の(A)に示したように、ビッグCPU120が動作する時、スモールCPU110の各電力領域111、113、及び115は、パワーオフ状態であり、ビッグCPU120の各電力領域121、123、125、131、133、141、及び143は、パワーオン状態である。この際、第2L2キャッシュコントローラ125は、少なくとも1つの共有領域133、143をアクセスすることができる。

#### 【0052】

ビッグCPU120からスモールCPU110にCPUスケーリングのために、ビッグCPU120の第1コア121は、第2指示信号IND2を第2通信チャネルCH2とシステムバス101を通じてPMU150に出力する。PMU150は、第2指示信号IND2に応答して、複数の第1制御信号CTR1、複数の第2制御信号CTR2、及び選択信号SELを出力する。

20

選択信号SELに応答して、各選択器160、161は、少なくとも1つの共有領域133、143と第2L1キャッシュコントローラ115との間の通信チャネルを形成する。

。

#### 【0053】

図6の(B)に示したように、スモールCPU110の各電力領域111、113、及び115は、複数の第1制御信号CTR1のそれぞれに応答して、パワーオン状態になり、ビッグCPU120の各電力領域121～125、130、及び140は、複数の第2制御信号CTR2に応答して、パワーオン状態を保持する。各共有L2キャッシュ133、143の各電力領域は、第2制御信号CTRL3に応答して、パワーオン状態を保持する。

30

#### 【0054】

ビッグCPU120の少なくとも1つの電力領域121～125のデータは、少なくとも1つのL2キャッシュ130、140にアップデートされ、ビッグCPU120は、第2通信チャネルCH2を通じてスヌーピング動作を行いながら、少なくとも1つの専用領域133、143に対するフラッシング動作 (flushing operation) を行う。このフラッシング動作によるデータは、チャネルCH2、バス101、及びメモリコントローラ105を通じてメモリ107に伝送することができる。

40

#### 【0055】

図6の(C)に示したように、フラッシング動作が行われる間に、ビッグCPU120の各電力領域121、123は、複数の第2制御信号CTR2のうち対応する制御信号のそれぞれに応答して、パワーオフ状態になる。

フラッシング動作が完了すれば、図6の(D)に示したように、ビッグCPU120の各電力領域125、131、及び141は、複数の第2制御信号CTR2のうち対応する制御信号のそれぞれに応答して、パワーオフ状態になる。したがって、CPUスケーリングが完了すれば、スモールCPU110の第1L2キャッシュコントローラ115は、各選択器160、161を通じて少なくとも1つの共有領域133、143をアクセスする

50

ことができる。

#### 【0056】

図6の(A)から(D)に示したように、CPUスケーリングの間に、少なくとも1つの共有領域133、143に供給される各電力は、制御信号CTR3に応答して、そのまま保持される。また、CPUスケーリングの間に、少なくとも1つの共有領域133、143は、第2通信チャネルCH2を通じてスヌーピング動作を行わない。すなわち、少なくとも1つの共有領域133、143が、各CPU110、120によって物理的に共有されるので、スヌーピング動作が行われる全体領域は、減少する利点がある。

#### 【0057】

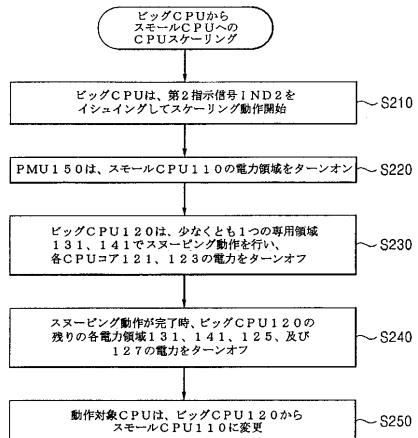

図7は、本発明の実施形態による他のCPUスケーリングプロセスのフローチャートである。図6の(A)から図7を参照すると、ビッグCPU120は、第2指示信号IND2をイシュイニングしてCPUスケーリング動作を始める(ステップS210)。PMU150は、スマールCPU110の各電力領域をターンオンする(ステップS220)。ビッグCPU120は、少なくとも1つの専用領域131、141に対するスヌーピング動作を行い、各CPUコア121、123の電力は、ターンオフされる(ステップS230)。スヌーピング動作が完了すれば、ビッグCPU120の残りの電力領域131、141、125、及び127の電力は、ターンオフされ(ステップS240)、動作対象CPUは、ビッグCPU120からスマールCPU110に変更される(ステップS250)。

#### 【0058】

図8の(A)と(B)は、本発明の他の実施形態によるマルチCPUシステムの概略的なブロック図である。図8の(A)と(B)とを参照すると、マルチCPUシステムは、第1CPU110-1と第2CPU120-1とを含む。図8の(A)は、前記マルチCPUシステムの正面図を示し、図8の(B)は、前記マルチCPUシステムの平面図を示す。

#### 【0059】

図8の(A)と(B)とに示したように、第1CPU110-1は、第2CPU120-1上に積層(stack)される。第1CPU110-1と第2CPU120-1は、互いに異なるチップ(chip)またはダイとして具現可能である。少なくとも1つの共有L2キャッシュ領域133、143は、第2CPU120-1に具現可能である。少なくとも1つの共有L2キャッシュ領域133、143は、垂直的電気的ピア(vertical electrical vias)、例えば、TSV(Through Silicon on Vias)を通じて第1CPU110-1によってアクセスされうる。

#### 【0060】

スマールCPU110の構成要素を含むチップ110-1は、自分のL2キャッシュを含まない。その代りに、ビッグCPU120の全体L2キャッシュ130、140は、チップ120-1内に位置し、チップ120-1内に物理的に位置するL2キャッシュの共有部分133、143は、スマールCPU110とビッグCPU120とによって使われる。

第1CPU110-1の構造は、図1Aの第1CPU110の構造を含み、第2CPU120-1の構造は、図1Aの第2CPU120の構造を含む。ここで、図1AのPMU150に対応するPMUは、第2CPU120-1に具現可能である。このような実施形態で、CTR1のように、MPUに関連した複数の制御信号は、複数のTSVのうちの少なくとも1つを通じて伝送することができる。

#### 【0061】

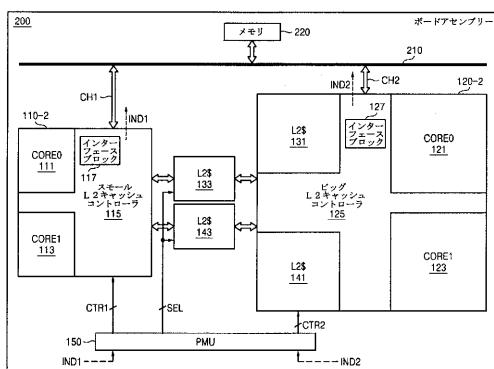

図9は、本発明の実施形態によるボードアセンブリ(board assembly)のブロック図である。図9を参照すると、ボードアセンブリ200は、第1CPU110-2、第2CPU120-2、少なくとも1つの共有領域133、143、PMU150、バス210、及びメモリ220を含む。図1A、図8の(A)、(B)、及び図9を参照すると、少なくとも1つの共有領域133、143は、第1CPU110-2と第2CPU120-2によって物理的に共有される。

10

20

30

40

50

U 1 2 0 - 2 とは別途に具現可能である。少なくとも 1 つの共有領域 1 3 3、1 4 3 を除けば、図 1 A の第 1 C P U 1 1 0 の構造と動作は、図 9 の第 1 C P U 1 1 0 - 2 の構造と動作と実質的に同一であり、図 1 A の第 2 C P U 1 2 0 の構造と動作は、図 9 の第 2 C P U 1 2 0 - 2 の構造と動作と実質的に同一である。

#### 【 0 0 6 2 】

第 1 L 2 キャッシュコントローラ 1 1 5 または第 1 インターフェースブロック 1 1 7 は、第 1 通信チャネル C H 1 を通じてバス 2 1 0 と通信することができる。第 2 L 2 キャッシュコントローラ 1 2 5 または第 2 インターフェースブロック 1 2 7 は、第 2 通信チャネル C H 2 を通じてバス 2 1 0 と通信することができる。各第 1 通信チャネル C H 1、C H 2 は、電気的通信チャネルまたは光学的通信チャネルとして具現可能である。各 L 2 キャッシュコントローラ 1 1 5、1 2 5 は、少なくとも 1 つの共有領域 1 3 3、1 4 3 を選択的にアクセスすることができる。10

#### 【 0 0 6 3 】

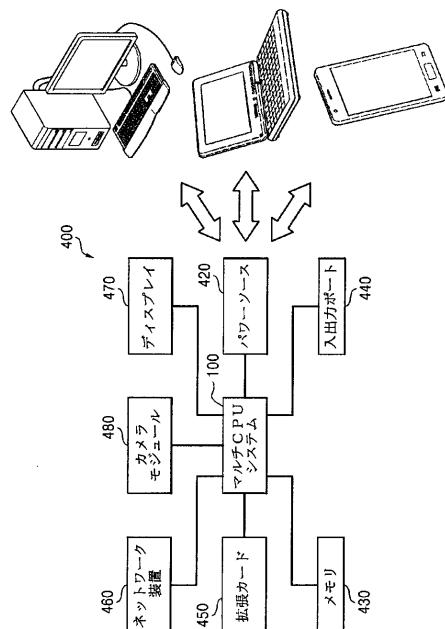

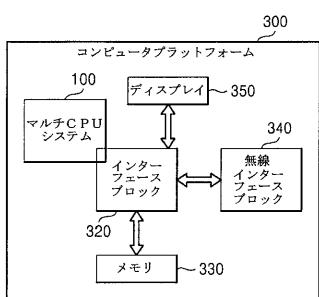

図 1 0 は、本発明の実施形態によるコンピュータプラットフォーム ( computer platform ) を示す。図 1 0 を参照すると、コンピュータプラットフォーム 3 0 0 は、コンピューティングシステムのような電子装置に使われる。これらの電子装置は、P C ( Personal Computer )、デジタル T V 、または携帯用装置 ( portable device ) として具現可能である。ここで、携帯用装置は、ラップトップコンピュータ ( laptop computer )、携帯電話、スマートフォン ( smart phone )、タブレット ( tablet ) PC、P D A ( Personal Digital Assistant )、E D A ( Enterprise Digital Assistant )、デジタルスチルカメラ ( Digital Still Camera )、デジタルビデオカメラ ( Digital Video Camera )、P M P ( Portable Multimedia Player )、P D N ( Personal Navigation Device または Portable Navigation Device )、携帯用ゲームコンソール ( handheld game console )、または電子ブック ( e - book ) などとして具現可能である。20

#### 【 0 0 6 4 】

コンピュータプラットフォーム 3 0 0 は、マルチ C P U システム 1 0 0 、インターフェースブロック 3 2 0 、及びメモリ 3 3 0 を含む。実施形態によって、コンピュータプラットフォーム 3 0 0 は、無線インターフェースブロック 3 4 0 とディスプレイ 3 5 0 とのうち少なくとも 1 つをさらに含みうる。30

マルチ C P U システム 1 0 0 は、インターフェースブロック 3 2 0 を通じてメモリ 3 3 0 、無線インターフェースブロック 3 4 0 、またはディスプレイ 3 5 0 と通信することができる。インターフェースブロック 3 2 0 は、多様なインターフェース制御機能を行う 1 つまたはそれ以上の回路ブロックを含む。前記制御機能は、メモリアクセス制御、グラフィック制御、入出力インターフェース制御、または無線ネットワークアクセス制御などを含む。

#### 【 0 0 6 5 】

これらの回路ブロックのそれぞれは、別途の独立したチップとして具現されるか、マルチ C P U システム 1 0 0 の一部として具現されるか、またはマルチ C P U システム 1 0 0 の内部に具現可能である。40

メモリ 3 3 0 は、インターフェースブロック 3 2 0 を通じてマルチ C P U システム 1 0 0 とデータを送受信することができる。無線インターフェースブロック 3 4 0 は、アンテナを通じてコンピュータプラットフォーム 3 0 0 を無線ネットワーク、例えば、移動通信ネットワークまたは無線 L A N ( Local Area Network ) に接続させることができる。

#### 【 0 0 6 6 】

図 1 1 は、本発明の実施形態によるマルチ C P U システムを含むコンピューティングシステムの一実施形態を示す。図 1 1 を参照すると、コンピューティングシステム 4 0 0 は50

、 P C 、データサーバ、ラップトップコンピュータ、または携帯用装置として具現可能である。

コンピューティングシステム 400 は、マルチ C P U システム 100 、パワーソース 420 、メモリ 430 、複数の入出力ポート 440 、拡張カード 450 、ネットワーク装置 460 、及びディスプレイ 470 を含みうる。実施形態によって、コンピューティングシステム 400 は、カメラモジュール 480 をさらに含みうる。

#### 【 0067 】

マルチ C P U システム 100 は、要素 420 ~ 480 のうち少なくとも 1 つの動作を制御することができる。パワーソース 420 は、要素 103 、及び 430 ~ 480 のうち少なくとも 1 つに動作電圧を供給することができる。メモリ 430 は、揮発性メモリまたは不揮発性メモリとして具現可能である。実施形態によって、メモリ 430 に対するデータアクセス動作、例えば、リード動作、ライト動作（または、プログラム動作）、またはイレーズ動作を制御することができるメモリコントローラは、マルチ C P U システム 100 に集積（または、内蔵）されうる。10

#### 【 0068 】

他の実施形態によって、メモリコントローラは、マルチ C P U システム 100 とメモリ 430 との間に別途に具現可能である。複数の入出力ポート 440 は、コンピューティングシステム 400 にデータを伝送するか、またはコンピューティングシステム 400 から出力されたデータを外部装置に伝送しうる複数のポートを意味する。例えば、入出力ポート 440 は、コンピュータマウスのようなポインティング装置（ p o i n t i n g d e v i c e ）を接続するためのポート、プリンタを接続するためのポート、または U S B ドライブを接続するためのポートのうち少なくとも 1 つを含みうる。拡張カード 450 は、 S D ( S e c u r e D i g i t a l ) カードまたは M M C ( M u l t i M e d i a C a r d ) として具現可能である。実施形態によって、拡張カード 450 は、 S I M ( S u b s c r i b e r I d e n t i f i c a t i o n M o d u l e ) カードまたは U S I M ( U n i v e r s a l S u b s c r i b e r I d e n t i t y M o d u l e ) カードであり得る。20

#### 【 0069 】

ネットワーク装置 460 は、コンピューティングシステム 400 を有線ネットワークまたは無線ネットワークに接続させる装置を意味する。ディスプレイ 470 は、メモリ 430 、入出力ポート 440 、拡張カード 450 、またはネットワーク装置 460 から出力されたデータをディスプレイすることができる。カメラモジュール 480 は、光学イメージを電気的なイメージに変換することができるモジュールを意味する。したがって、カメラモジュール 480 から出力された電気的なイメージは、メモリ 430 、または拡張カード 450 に保存することができる。また、カメラモジュール 480 から出力された電気的なイメージは、マルチ C P U システム 100 の制御によってディスプレイ 470 を通じてディスプレイされうる。30

#### 【 0070 】

図 10 と図 11 とには、マルチ C P U システム 100 が、各コンピューティングシステム 300 または 400 の要素として示されているが、実施形態によって、マルチ C P U システム 100 は、マルチ C P U 103 またはボードアセンブリ 200 に代替されうる。この場合、各コンピューティングシステム 300 または 400 の構造は、マルチ C P U 103 またはボードアセンブリ 200 に適するように変更されうる。40

#### 【 0071 】

図 12 は、本発明の実施形態によるマルチ C P U システムを製造する方法を説明するフローチャートである。図 1A と図 12 とを参照すると、半導体基板が準備される（ステップ S310 ）。この半導体基板上に少なくとも 1 つの第 1 C P U コア 111 、 113 に接続された第 1 L 2 キャッシュコントローラ 115 を含む第 1 C P U 110 と、少なくとも 1 つの第 2 C P U コア 121 、 123 に接続された第 2 L 2 キャッシュコントローラ 125 を含む第 2 C P U 120 とが形成される（ステップ S320 ）。50

**【0072】**

第1CPU110と第2CPU120とのオーバーラップ領域133、143に、第1L2キャッシュコントローラ115と第2L2キャッシュコントローラ125とによって選択的にアクセス可能な共有L2キャッシュが形成される。

この半導体基板上に、システムバス101、システムバス101と第1キャッシュコントローラ115との間に第1通信チャネルCH1、及びシステムバス101と第2キャッシュコントローラ125との間に第2通信チャネルCH2が形成される。実施形態によつて、S310段階とS320段階は、同時に具現されることもあり、互いに異なる時間に具現されることもある。

**【0073】**

10

図8の(A)と(B)とに示したように、第1CPU110-1と第2CPU120-1が、互いに異なるチップまたはダイに形成された後、第1CPU110-1と第2CPU120-1が、少なくとも1つの共有領域133、143を共有できるように、垂直的電気的ピア(TSV)を通じて互いに接続されうる。

**【産業上の利用可能性】****【0074】**

本発明は、マルチCPUプロセッサまたはそれを含むマルチCPUデータ処理システムに使用可能である。

**【符号の説明】****【0075】**

20

100：マルチCPUシステム

101：システムバス

103：マルチCPU

110：第1CPU

111、113：CPUコア

115：L2キャッシュコントローラ

117：第1インターフェースブロック

120：第2CPU

121、123：CPUコア

125：L2キャッシュコントローラ

30

130、140：L2キャッシュ

131、141：L2キャッシュの専用領域

133、143：L2キャッシュの共有領域

127：第2インターフェースブロック

210：バス

220：メモリ

【図1A】

【図1B】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図11】

【図10】

【図 1 2】

---

フロントページの続き

(72)発明者 申 榮 敏

大韓民国ソウル特別市麻浦区城山一洞251-23番地7通1班

審査官 後藤 彰

(56)参考文献 特表2010-534377(JP,A)

特開2010-003042(JP,A)

(58)調査した分野(Int.Cl., DB名)

G 06 F 12 / 08