(19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

FL

(11) 特許番号

特許第6190068号 (P6190068)

(45) 発行日 平成29年8月30日(2017.8.30)

(24) 登録日 平成29年8月10日(2017.8.10)

(51) Int. Cl.

GO6F 13/362 (2006.01)

GO6F 13/362 52OA

請求項の数 28 (全 22 頁)

(21) 出願番号 特願2016-540922 (P2016-540922)

(86) (22) 出願日 平成26年9月9日 (2014.9.9)

(65) 公表番号 特表2016-530653 (P2016-530653A)

(43)公表日 平成28年9月29日 (2016.9.29) (86)国際出願番号 PCT/US2014/054778

(87) 国際公開番号 W02015/035380

(87) 国際公開日 平成27年3月12日 (2015.3.12) 審査請求日 平成29年2月9日 (2017.2.9)

(31) 優先権主張番号 61/875,547

(32) 優先日 平成25年9月9日(2013.9.9)

(33) 優先権主張国 米国 (US) (31) 優先権主張番号 14/480,540

(32) 優先日 平成26年9月8日 (2014.9.8)

(33) 優先権主張国 米国(US)

(73) 特許権者 507364838

クアルコム、インコーポレイテッド アメリカ合衆国 カリフォルニア 921 21 サン ディエゴ モアハウス ドラ

イブ 5775

(74)代理人 100108453

弁理士 村山 靖彦

(74)代理人 100163522

弁理士 黒田 晋平

(72) 発明者 仙石 祥一郎

アメリカ合衆国・カリフォルニア・921 21-1714・サン・ディエゴ・モアハ

ウス・ドライヴ・5775

最終頁に続く

(54) 【発明の名称】複数のマスタがシングルマスタバスアーキテクチャにおいて動作できるようにする方法および装置

#### (57)【特許請求の範囲】

#### 【請求項1】

早期審査対象出願

複数のマスタデバイスが結合される単線割込み要求(IRQ)バスであって、前記複数のマスタデバイスは、1つのアクティブマスタデバイスと、1つまたは複数の非アクティブマスタデバイスとを含む、単線割込み要求(IRQ)バスと、

前記複数のマスタデバイスが結合されるデータバスと、

前記アクティブマスタデバイス内の処理回路とを備え、前記処理回路は、

前記IRQバスを介してアサートされた割込み信号に基づいて、前記データバスに結合されるすべてのデバイスに関する前記データバスを介しての通信を管理し、

IRQ信号がアサートされたときを確認するために前記IRQバスを監視し、

どの非アクティブマスタデバイスが前記IRQバス上で前記IRQ信号をアサートしたかを確認するために、前記データバスを介して前記非アクティブマスタデバイスをポーリングし

マスタ要求を行ったという非アクティブマスタデバイスからの指示を得ると、前記データバスの制御をアサート中非アクティブマスタデバイスに引き渡すように構成される、デバイス。

## 【請求項2】

前記非アクティブマスタデバイスからの前記マスタ要求は前記IRQバスを介して得られる、請求項1に記載のデバイス。

【請求項3】

20

前記非アクティブマスタデバイスからの前記指示は前記データバスを介して得られる、 請求項1に記載のデバイス。

#### 【請求項4】

前記処理回路はさらに、

前記データバスの制御を転送するために、前記アサート中非アクティブマスタデバイス にインジケータを送るように構成される、請求項1に記載のデバイス。

#### 【請求項5】

前記処理回路はさらに、

前記得られたインジケータに基づいて、前記IRQ信号が関連付けられる前記アサート中非アクティブマスタデバイスを識別するように構成される、請求項1に記載のデバイス。

10

#### 【請求項6】

前記処理回路はさらに、

前記IRQ信号が関連付けられるデバイスグループを識別するように構成される、請求項1に記載のデバイス。

#### 【請求項7】

前記処理回路はさらに、

どのデバイスが前記IRQバス上で前記IRQ信号をアサートしたかを確認するために、前記識別されたグループに関する前記デバイスをスキャンするように構成される、請求項6に記載のデバイス。

20

## 【請求項8】

各グループに関連付けられる前記IRQ信号は、他のグループに関連付けられる他のIRQ信号とは異なるパルス幅を有する、請求項6に記載のデバイス。

#### 【請求項9】

各デバイスグループは単一のデバイスを含む、請求項6に記載のデバイス。

#### 【請求項10】

前記処理回路はさらに、

ポーリングされる各非アクティブマスタデバイスから得られたステータスレジスタ内の特定のビットを調べることによって、前記ポーリングされる非アクティブマスタデバイスが前記IRQ信号をアサートし、前記マスタ要求を行ったか否かを確認するように構成される、請求項1に記載のデバイス。

30

#### 【請求項11】

マスタ要求を行ったという前記非アクティブマスタデバイスからの前記指示は、前記1つまたは複数の非アクティブマスタデバイスから前記アクティブマスタデバイスへの送信を符号化することによって得られた未使用のビット内に符号化される、請求項1に記載のデバイス。

#### 【請求項12】

少なくとも前記アサート中非アクティブマスタデバイスは、マスタ動作モードと、スレープ動作モードとの間で切り替わる、請求項1に記載のデバイス。

#### 【請求項13】

デバイス上で動作可能な方法であって、

40

単線割込み要求(IRQ)バスを介してアサートされた割込み信号に基づいて、データバスに結合されるすべてのデバイスに関する前記データバスを介しての通信を管理するステップであって、複数のマスタデバイスが前記IRQバスおよび前記データバスに結合される、管理するステップと、

IRQ信号がアサートされたときを確認するために前記IRQバスを監視するステップと、 どの非アクティブマスタデバイスが前記IRQバス上で前記IRQ信号をアサートしたかを確 認するために、前記データバスを介して前記非アクティブマスタデバイスをポーリングす

記するために、前記ゲークバスを介して前記ポグラグインマスクラバイスをボージングするステップと、 マスタ要求を行ったという非アクティブマスタデバイスからの指示を得ると 前記デー

マスタ要求を行ったという非アクティブマスタデバイスからの指示を得ると、前記データバスの制御をアサート中非アクティブマスタデバイスに引き渡すステップとを含む、方

法。

#### 【請求項14】

前記データバスの制御を転送するために、前記アサート中非アクティブマスタデバイス にインジケータを送るステップをさらに含む、請求項13に記載の方法。

#### 【請求項15】

前記得られたインジケータに基づいて、前記IRQ信号が関連付けられる前記アサート中非アクティブマスタデバイスを識別するステップをさらに含む、請求項13に記載の方法。

#### 【請求項16】

前記IRQ信号が関連付けられるデバイスグループを識別するステップをさらに含む、請求項13に記載の方法。

10

## 【請求項17】

どのデバイスが前記IRQバス上で前記IRQ信号をアサートしたかを確認するために、前記識別されたグループに関する前記デバイスをスキャンするステップをさらに含む、請求項16に記載の方法。

#### 【請求項18】

各グループに関連付けられる前記IRQ信号は、他のグループに関連付けられる他のIRQ信号とは異なるパルス幅を有する、請求項16に記載の方法。

#### 【請求項19】

ポーリングされる各非アクティブマスタデバイスから得られたステータスレジスタ内の特定のビットを調べることによって、前記ポーリングされる非アクティブマスタデバイスが前記IRQ信号をアサートし、前記マスタ要求を行ったか否かを確認するステップをさらに含む、請求項13に記載の方法。

20

## 【請求項20】

前記データバスは、カメラ制御インターフェース拡張(CCIe)互換バスである、請求項13に記載の方法。

#### 【請求項21】

1つまたは複数の命令を記憶している<u>機械可読記憶媒体</u>であって、少なくとも1つのプロセッサによって実行されたときに、前記少なくとも1つのプロセッサに、

割込み要求(IRQ)バスを介してアサートされた割込み信号に基づいて、データバスに結合されるすべてのデバイスに関する前記データバスを介しての通信を管理することであって、複数のマスタデバイスが前記IRQバスおよび前記データバスに結合される、管理することと、

30

IRQ信号がアサートされたときを確認するために前記IRQバスを監視することと、

どの非アクティブマスタデバイスが前記IRQバス上で前記IRQ信号をアサートしたかを確認するために、前記データバスを介して前記非アクティブマスタデバイスをポーリングすることと、

マスタ要求を行ったという非アクティブマスタデバイスからの指示を得ると、前記データバスの制御をアサート中非アクティブマスタデバイスに引き渡すこととを行わせる、<u>機</u>械可読記憶媒体。

#### 【請求項22】

40

50

単線割込み要求(IRQ)バスに結合するための第1のインターフェースであって、複数の他のデバイスが前記単線割込み要求(IRQ)バスに結合される、第1のインターフェースと、

データバスに結合するための第2のインターフェースであって、前記複数の他のデバイスが前記データバスに結合される、第2のインターフェースと、

前記第1のインターフェースおよび前記第2のインターフェースに結合される処理回路と を備え、前記処理回路は、

前記IRQバスを介してアサートされた割込み信号に基づいて、前記データバスに結合されるすべてのデバイスに関する前記データバスを介しての通信を管理し、

IRQ信号がアサートされたときを確認するために前記IRQバスを監視し、

どの非アクティブマスタデバイスが前記IRQバス上で前記IRQ信号をアサートしたかを確

認するために、前記データバスを介して前記非アクティブマスタデバイスをポーリングし

マスタ要求を行ったという非アクティブマスタデバイスからの指示を得ると、前記データバスの制御をアサート中非アクティブマスタデバイスに引き渡すように構成される、デバイス。

## 【請求項23】

前記非アクティブマスタデバイスからの前記マスタ要求は前記第1のインターフェースを介して得られる、請求項22に記載のデバイス。

#### 【請求項24】

前記非アクティブマスタデバイスからの前記指示は前記第2のインターフェースを介して得られる、請求項22に記載のデバイス。

#### 【請求項25】

前記データバスは、カメラ制御インターフェース拡張(CCIe)互換バスである、請求項22 に記載のデバイス。

#### 【請求項26】

前記データバスは双方向バスである、請求項22に記載のデバイス。

#### 【請求項27】

前記処理回路はさらに、

前記データバスの制御を転送するために、前記アサート中非アクティブマスタデバイス に前記データバスを介してインジケータを送るように構成される、請求項22に記載のデバ イス。

#### 【請求項28】

前記処理回路はさらに、

ポーリングされる各非アクティブマスタデバイスから得られたステータスレジスタ内の特定のビットを調べることによって、前記ポーリングされる非アクティブマスタデバイスが前記IRQ信号をアサートし、前記マスタ要求を行ったか否かを確認するように構成される、請求項22に記載のデバイス。

## 【発明の詳細な説明】

## 【技術分野】

## [0001]

関連出願の相互参照

本特許出願は、本出願の譲受人に譲渡され、参照により本明細書に明確に組み込まれる、2013年9月9日に出願された「Method and Apparatus to Enable a Multiple Masters to Operate in a Single Master Bus Architecture」と題する仮特許出願第61/875,547号、および2014年9月8日に出願された「Method and Apparatus to Enable a Multiple Master s to Operate in a Single Master Bus Architecture」と題する非仮特許出願第14/480,540号の優先権を主張する。

## [0002]

本開示は、いくつかのマスタデバイスがシングルマスタバスの制御を共有できるように することに関する。

## 【背景技術】

#### [0003]

I2C(I<sup>2</sup>Cとも呼ばれる)は、マザーボード、埋め込みシステム、携帯電話または他の電子デバイスに低速周辺装置を取り付けるために用いられるマルチマスタシリアルシングルエンドバスである。I2Cバスは、クロック(SCL)線と、7ビットアドレス指定を用いるデータ線(SDA)とを含む。バスは、ノードに関する2つの役割:マスタおよびスレーブを有する。マスタノードは、クロックを生成し、スレーブノードとの通信を開始するノードである。スレーブノードは、クロックを受信し、マスタによってアドレス指定されたときに応答するノードである。I2Cバスは、任意の数のマスタノードが存在できることを意味するマルチマスタバスである。さらに、マスタとスレーブの役割は、メッセージの間で(すなわち

10

20

30

40

、STOPが送られた後に)切り替えられる場合がある。I2Cは、メッセージの基本タイプを規定し、それらの各々はSTARTで開始し、STOPで終了する。

#### [0004]

カメラの実装形態との関連では、単方向送信を用いて、センサから画像を取り込み、そのような画像データをベースバンドプロセッサ内のメモリに送信することができ、一方、制御データは、ベースバンドプロセッサとセンサおよび他の周辺デバイスとの間で交換することができる。一例では、ベースバンドプロセッサとイメージセンサ(および/または1つまたは複数のスレーブノード)との間のそのような制御データのために、カメラ制御インターフェース(CCI)プロトコルが用いられる場合がある。一例では、CCIプロトコルは、イメージセンサとベースバンドプロセッサとの間のI2Cシリアルバスを介して実施される場合がある。

#### [00005]

レガシーI2Cは、複数のマスタデバイスがスレープ識別子(ID)期間中にバスラインをローにドライブする、または引き込むことができるようにすることによって、マルチマスタバス調停を実装した。どのマスタデバイスがバスラインをローにドライブするにしても、最も長いドライブがバスの制御を得る。レガシーI2Cとは異なり、CCIおよびCCI拡張(CCIe)では、いつでも2つ以上のCCIeデバイスがバスをドライブできないようにするので、I2Cと同じ、マスタデバイスのためのバス調停は不可能である。

## 【発明の概要】

【発明が解決しようとする課題】

#### [0006]

それゆえ、シングルマスタバスが複数のマスタデバイスを有することができるようにする方法が必要とされている。

#### 【課題を解決するための手段】

## [0007]

単線割込み要求(IRQ)バスと、データバスと、アクティブマスタデバイス内の処理回路 とを備える、デバイスが提供される。単線割込み要求(IRQ)バスは、そのバスに結合され る複数のマスタデバイスを有することができ、複数のマスタデバイスは、1つのアクティ ブマスタデバイスと、1つまたは複数の非アクティブマスタデバイスとを含む。また、デ ータバスも、そのバスに結合される複数のマスタデバイスを有することができる。アクテ ィブマスタデバイス内の処理回路は、(a) IRQバス上でアサートされた割込み信号に基づい てデータバスに結合されるすべてのデバイスに関するデータバスを介しての通信を管理し 、(b) IRQ信号がアサートされたときを確認するためにIRQバスを監視し、(c) どの非アクテ ィブマスタデバイスがIRQバス上でIRQ信号をアサートしたかを確認するために、データバ スを介して非アクティブマスタデバイスをポーリングし、および/または(d)マスタ要求を 行ったという非アクティブマスタデバイスからの指示を得ると、データバスの制御をアサ ート中非アクティブマスタデバイスに引き渡すように構成される。非アクティブマスタデ バイスからのマスタ要求は、IRQバスを介して得ることができる。非アクティブマスタデ バイスからの指示は、データバスを介して得ることができる。一例では、マスタ要求を行 ったという非アクティブマスタデバイスからの指示は、1つまたは複数の非アクティブマ スタデバイスからアクティブマスタデバイスへの送信を符号化することによって得られた 未使用のビット内に符号化することができる。

#### [0008]

一例では、処理回路は、(a) IRQ信号が関連付けられるデバイスグループを識別し、および/または(b) どのデバイスがIRQバス上でIRQ信号をアサートしたかを確認するために、識別されたグループに関するデバイスをスキャンするようにさらに構成することができる。各グループが関連付けられるIRQ信号は、他のグループに関連付けられる他のIRQ信号とは異なるパルス幅を有することができる。

#### [0009]

さらに、処理回路は、ポーリングされる各非アクティブマスタデバイスから得られたス

20

10

30

40

テータスレジスタ内の特定のビットを調べることによって、ポーリングされる非アクティブマスタデバイスがIRQ信号をアサートし、マスタ要求を行ったか否かを確認するようにさらに構成することができる。別の態様によれば、処理回路は、データバスの制御を転送するために、アサート中非アクティブマスタデバイスにインジケータを送るようにさらに構成することができる。いくつかの実装形態では、少なくともアサート中非アクティブマスタデバイスは、マスタ動作モードと、スレーブ動作モードとの間で切り替わることができる。

#### [0010]

デバイス上で使用できる方法も提供され、(a)単線割込み要求(IRQ)バス上でアサートされた割込み信号に基づいてデータバスに結合されるすべてのデバイスに関するデータバスを介しての通信を管理することであって、複数のマスタデバイスがIRQバスおよびデータバスに結合される、管理すること、(b) IRQ信号がアサートされたときを確認するためにIRQバスを監視すること、(c)どの非アクティブマスタデバイスがIRQバス上でIRQ信号をアサートしたかを確認するために、データバスを介して非アクティブマスタデバイスをポーリングすること、および/または(d)マスタ要求を行ったという非アクティブマスタデバイスからの指示を得ると、データバスの制御をアサート中非アクティブマスタデバイスに引き渡すことを含む。一例では、データバスの制御を引き渡すことは、データバスの制御を転送するために、(アクティブ)デバイスがアサート中非アクティブマスタデバイスにインジケータを送ることを含むことができる。

## [0011]

別の態様によれば、その方法は、(a) IRQ信号が関連付けられるデバイスグループを識別すること、および/または(b) どのデバイスがIRQバス上でIRQ信号をアサートしたかを確認するために、識別されたグループに関するデバイスをスキャンすることをさらに含むことができる。各グループに関連付けられる場合があるIRQ信号は、他のグループに関連付けられる他のIRQ信号とは異なるパルス幅を有する。また、その方法は、ポーリングされる各非アクティブマスタデバイスから得られたステータスレジスタ内の特定のビットを調べることによって、ポーリングされる非アクティブマスタデバイスがIRQ信号をアサートし、マスタ要求を行ったか否かを確認することを含むことができる。

## [0012]

第1のインターフェースと、第2のインターフェースと、処理回路とを備える、例示的なアクティブマスタデバイスも提供される。第1のインターフェースは、そのアクティブマスタデバイスを、複数の他のデバイスが結合される単線割込み要求(IRQ)バスに結合するための役割を果たすことができる。第2のインターフェースは、そのアクティブマスタを、複数の他のデバイスがやはり結合されるデータバスに結合するための役割を果たすことができる。処理回路は、(a)IRQバス上でアサートされた割込み信号に基づいてデータバスに結合されるすべてのデバイスに関するデータバスを介しての通信を管理し、(b)IRQ信号がアサートされたときを確認するためにIRQバスを監視し、(c)どの非アクティブマスタデバイスがIRQバス上でIRQ信号をアサートしたかを確認するために、データバスを介して非アクティブマスタデバイスをポーリングし、および/または(d)マスタ要求を行ったという非アクティブマスタデバイスからの指示を得ると、データバスの制御をアサート中非アクティブマスタデバイスに引き渡すように構成することができる。非アクティブマスタデバイスからの指示は、第2のインターフェースを介して得ることができる。

## [0013]

様々な特徴、性質、および利点は、同様の参照文字が全体を通じて対応して識別する図面と併せて読まれたとき、以下に記載の詳細な説明から明らかになる場合がある。

#### 【図面の簡単な説明】

## [0014]

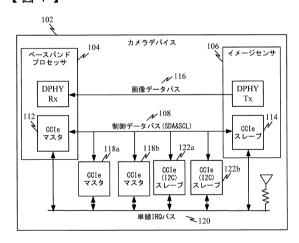

【図1】ベースバンドプロセッサおよびイメージセンサを有し、画像データバスおよび制御データバスを実装するデバイスを示すブロック図である。

10

20

30

40

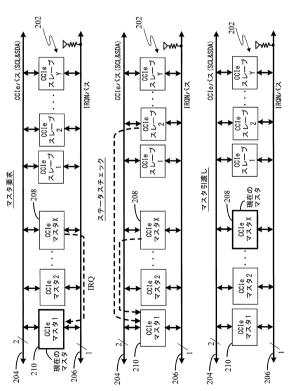

【図2】CCIeバスおよび割込み(IRQ)バスに結合される複数のマスタデバイスおよび/またはスレーブデバイスを含むシステム内のマスタ要求および引渡し動作を示す図である。

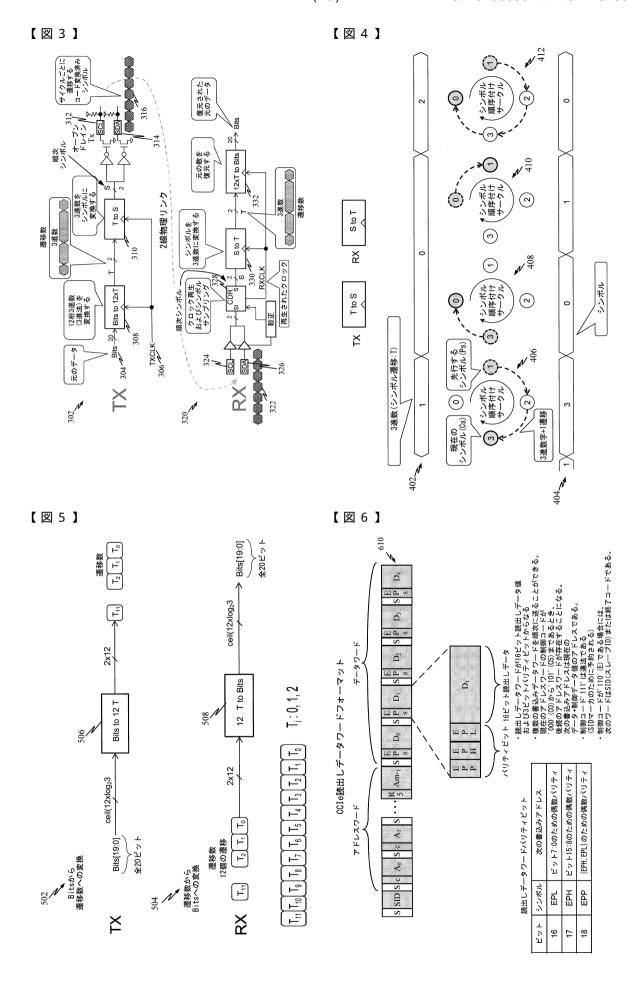

【図3】コード変換されたシンボル内にクロック信号を埋め込むために、送信機において データビットをコード変換し、コード変換されたシンボルにするための例示的な方法を示 すプロック図である。

【図4】3進数(遷移番号)と(順次)シンボルとの間の変換の一例を示す図である。

【図5】送信機におけるビットから遷移番号への、そしてその後の、受信機における遷移番号からビットへの例示的な変換を示す図である。

【図 6 】16ビット(0~15)が読出しデータであり、3ビットがパリティビット(16~18)であるデータワードを示す図である。

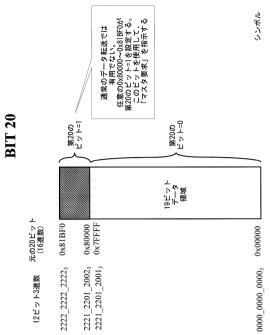

【図7】図3、図4および図5に示される符号化方式から生じる余分な(第20の)ビットの利用可能性を示す図である。

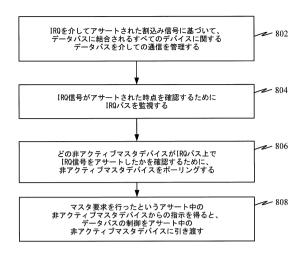

【図8】共有単線割込み要求(IRQ)バスに結合される複数のデバイスを2つ以上のグループにグループ化することを含み、各グループが異なるIRQ信号に関連付けられる、方法を示す図である。

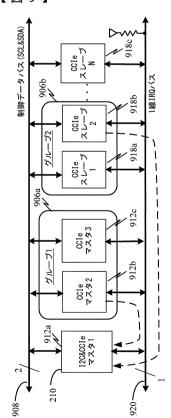

【図9】単線IRQバスを複数のスレーブデバイスおよび1つまたは複数のマスタデバイスによっていかに共有できるかを示すブロック図である。

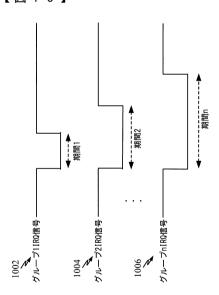

【図10】異なるグループに割り当てることができるか、または関連付けることができる 異なるIRQ信号の例を示す図である。

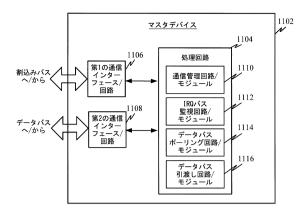

【図11】シングルマスタバス上でのマルチマスタ動作のために構成される例示的なマスタデバイスを示すブロック図である。

【発明を実施するための形態】

#### [0015]

以下の説明では、実施形態を完全に理解してもらうために、具体的な詳細が与えられる。しかしながら、実施形態はこれらの具体的な詳細を用いることなく実施できることは当業者によって理解されるだろう。たとえば、回路は、不必要な詳細で実施形態を不明瞭にしないために、プロック図で示される場合がある。他の例では、よく知られている回路、構造、および技法は、実施形態を不明瞭にしないために、詳細に示されない場合がある。

## [0016]

## 概説

第1の特徴は、複数のマスタデバイスがシングルマスタバスを共有するための方法を提供する。いくつかのバスアーキテクチャ(たとえば、CCIおよびCCIe)において、単一のマスタのみが、共有されるデータバスを制御することを許される。そのようなバスアーキテクチャにおいて複数のマスタデバイスの動作に対応するために、新たなマスタデバイスが、共有単線割込み(IRQ)バスを介してIRQ信号をトリガするための機構が提供される。その後、現在のマスタデバイスは、どのマスタデバイスがIRQ信号をアサートしているかを確認するために、共有されるデータバスを介して他のマスタデバイスをポーリングする。アサート中マスタデバイスを識別すると、現在のマスタデバイスは、新たなマスタデバイスにデータバスの制御を与える。

#### [0017]

一態様によれば、他のマスタデバイスは、マスタモードにおいてのみ動作することができる。第2の態様によれば、他のマスタデバイスは、データバスの現在のマスタデバイスからデータバスの使用を要求することによって、マスタデバイス動作に切り替わることができるスレーブデバイスとすることができる。

#### [0018]

マスタ権限を転送するための例示的な方法

図1は、ベースバンドプロセッサ104およびイメージセンサ106を有し、画像データバス116および制御データバス108(たとえば、I2Cバス)を実装するデバイス102を示すブロック図である。図1はカメラデバイス内の制御データバス108を示すが、この制御データバス108を示すが、この制御データバス108が種々の異なるデバイスおよび/またはシステム内に実装される場合があることは明らか

10

20

30

40

20

30

40

50

にすべきである。画像データは、画像データバス116(たとえば、高速差動DPHYリンク)を介して、イメージセンサ106からベースバンドプロセッサ104に送られる場合がある。一例では、制御データバス108は2つの線、クロック線(SCL)およびシリアルデータ線(SDA)を備えることができる。データ線SDAおよびクロック線SCLは、制御データバス108上にあるすべてのデバイス112、114、118および122に結合することができる。

## [0019]

この例では、CCIeマスタ112が、CCIeスレーブ114と、複数の非アクティブマスタ118aおよび118bと、複数のCCIe(I2C)スレーブ122aおよび122bとに結合されるアクティブマスタである。制御データバス108アーキテクチャは、一度に1つのアクティブマスタのみを可能にする。さらに、マスタ112、118およびスレーブ114および122は、共有単線IRQバス120に結合することができる。

#### [0020]

非アクティブCCIeマスタ118aおよび118bは、一実装形態では、マスタとしてのみ動作す るように構成することができる(たとえば、それらのマスタはスレーブとして動作するこ とができない)。一般に、「マスタ」は、制御データバス108に結合されるデバイスであり 、制御データバス108を介して(他のデバイスからの)通信を管理する。アクティブマスタ になるために、非アクティブマスタは、現在のマスタによる制御データバス108を介して の制御を(たとえば、1つずつ)与えられる場合がある。たとえば、非アクティブマスタ118 aがアクティブになりたい場合には、非アクティブマスタ118aは、(たとえば、単線共有IR Qバス120をプルダウンすることによって) IRQバス120上でIRQ信号をアサートする。現在ア クティブのマスタ112は、割込み信号を受信し、その後、どのデバイスが、いかなる理由 で割込みをアサートしたかを判断するために、制御データバス108に結合されるすべての デバイスをポーリング/スキャンする。たとえば、スレーブ114は、制御バス108の一時的 使用を要求することができる。さらに、非アクティブマスタ118aおよび/または118bは、 マスタ要求を行うことができる。すなわち、非アクティブマスタ118aおよび/または118b は、一時的な時間以上にわたって、制御を引き継ぎ、制御バス108を制御するための要求 を行う。通常、新たにアクティブになるマスタは、無制限に、または別の非アクティブマ スタが制御を求めるまで、制御データバス108を制御する。一態様によれば、共有単線IRQ バス120は、マスタデバイス112、118aおよび118bだけでなく、スレーブデバイス114、122 aおよび122bにも結合される。この共有IRQ線120は、プルアップ(たとえば、ハイに引き込 まれる)場合があり、スレーブデバイスがIRQ信号をアサートするときにローに引き込まれ る場合がある。すなわち、各スレーブデバイス114、122aおよび122bは、IRQ信号(たとえ ば、要求)をマスタデバイス112に送ることによって、制御データバス108上で送信するた めのアクセスを独立して要求することができる。

#### [0021]

制御データバス108を介して、ベースバンドプロセッサ104と、イメージセンサ106および他の周辺デバイス114、122aおよび122b(スレーブデバイス)との間で制御データを交換することができる。

#### [0022]

いくつかの例では、単線IRQバスは、非同期バスとすることができる(たとえば、マスタデバイスまたは任意の他のデバイスによって管理されない)。これは、スレーブデバイスがいつでもIRQ信号を一方的にアサートできることを意味する。別の例では、単線IRQバスは、スレーブデバイスからマスタデバイスへの単方向信号送信専用とすることができる。すなわち、単線IRQバスは、IRQ信号のためにのみ使用することができ、他のタイプの信号には使用できない。一例では、制御データバス108は、カメラ制御インターフェース(CCI)またはCCI拡張互換バスとすることができる。別の例では、制御データバスは、スレーブデバイスとマスタデバイスとの間の双方向バスとすることができる。

#### [0023]

一態様によれば、カメラ動作をサポートするために、改善された(すなわち、1MHzより高い)動作モードをマルチモード制御データバス108を介して実施することができる。I2C

バスを介してのこの改善された動作モードは、カメラの適用例のために使用されるとき、 カメラ制御インターフェース拡張(CCIe)モードと呼ばれる場合がある。この例では、ベー スバンドプロセッサ104はマスタノード112を含み、イメージセンサ106はスレーブノード1 14を含み、マスタノード112とスレーブノード114はいずれも、制御データバス108に結合 されたスレーブ122aおよび122bのような他のレガシーI2Cデバイスの適切な動作に影響を 与えることなく、制御データバス108を介してカメラ制御インターフェース拡張(CCIe)モ ードに従って動作することができる。一態様によれば、制御データバス108を介してのこ の改善されたモードは、CCIeデバイスと、任意のレガシーI2Cスレーブデバイス122aおよ び122bとの間に任意のブリッジデバイスを用いることなく実施することができる。一態様 によれば、レガシーI2Cデバイス122aおよび122bは、第1のクロック、第1のバス速度およ び/または第1の信号プロトコルを有する第1のモードにおいて動作することができ、一方 、CCIe対応デバイスは、第2のクロック、第2のバス速度および/または第2のプロトコルを 有する第2のモードにおいて動作することができる。第1のクロック、第1のバス速度、お よび/または第1の信号プロトコルは、第2のクロック、第2のバス速度、および/または第2 のプロトコルとは異なる場合がある。たとえば、第2のクロックおよび/または第2のバス 速度はそれぞれ、第1のクロックおよび/または第1のバス速度よりも速くすることができ るか、または高い速度を有することができる。

#### [0024]

一態様によれば、すべてのスレーブデバイス114、122aおよび122bは、第1の動作モードと第2の動作モードとを切り替える必要がないようなCCIe対応デバイスとすることができる。すなわち、すべてのシグナリングおよび/または通信は、第2のモードに従って(たとえば、第2のクロック、第2のバス速度および/または第2のプロトコルにおいて)実行することができる。たとえば、第2のモードは、第1の速度より高いビット速度を与えることができるので、第1のモードと第2のモードとの間を行き来する必要はない。実際には、第1のモードに適合するレガシーデバイスに対応する必要はないので、第2のモードより高い/速いビット速度を与える第3の動作モードを実施することができる。

#### [0025]

図2は、CCIeバス204(たとえば、制御データバス)およびIRQバス206に結合される複数のマスタおよび/またはスレーブデバイス202を含むシステムにおけるマスタ要求および引渡し動作を示す。非アクティブマスタX208が、IRQバス206上で割込み信号をアサートする。現在アクティブのマスタ1 210(現在のマスタ)が、アサートされた割込み信号を受信する。マスタ1 210は、どのデバイスがIRQ信号をアサートしたかを確認するために、CCIeバス204を介して各非アクティブマスタをポーリングする。アサート中マスタを識別すると、現在アクティブのマスタ210は、CCIeバス204の制御を放棄し、アサート中非アクティブマスタ208が、新たな現在アクティブのマスタになる。

#### [0026]

一例では、アサート中マスタを確認するために非アクティブマスタをそのようにポーリングすることは、ポーリングされている各非アクティブマスタ内の1つまたは複数のステータスレジスタをチェックする(たとえば、読み出すことを要求する)ことができる。一例では、そのようなステータスレジスタは、デバイスがIRQ信号をトリガ/アサートしたか否か、および/またはそのようなアサートがマスタ要求を目的とする(たとえば、制御データバスのマスタになることを要求する)か否かを指示することができる。一例では、非アクティブマスタがCCIeバス204の制御を引き継ぐのに、(IRQ信号をアサートした後に)非アクティブマスタによって現在のマスタにマスタ要求を指示するそのようなステータスレジスタ(またはCCIeバスを介しての他の情報)を搬送すれば十分な場合がある。他の実装形態では、非アクティブマスタは(たとえば、現在アクティブのマスタが現在CCIeバスの制御を有し、アクティブマスタになるべきであることを指示する付加メッセージを受信することができる。

[0027]

10

20

30

いくつかの実装形態では、CCIおよびCCIeのように、マスタ要求がアサートされている 否かを指示する特定の機構が利用できない場合がある(たとえば、ステータスレジスタが 、複数のマスタをサポートすることを意図していなかったため)。結果として、非アクティブマスタが、その新たなマスタとしてCCIeバス204を制御したいことを指示できるよう にする方法が必要とされる。

#### [0028]

第1の特徴によれば、20ビットのうちの19ビットしかデータのために使用されないので、1つの予備ビットを利用することができる。この予備ビットを用いて、マスタ要求を指示することができる。

#### [0029]

通常のI2Cバスは、シリアルクロック(SCL)線およびシリアルデータ(SDA)線を含む。しかしながら、1つの特徴によれば、CCIeバス204は、クロックがシンボル送信内に埋め込まれる符号化されたデータ送信のために、これら2つの線を再利用することができる。

## [0030]

図3は、コード変換されたシンボル内にクロック信号を埋め込むために、送信機においてデータビットをコード変換し、コード変換済みシンボルにするための例示的な方法を示すブロック図である。送信機302において、一連のデータビット304が3進数(3進法)(すなわち、「遷移数」)に変換され、その後、3進数が(順次)シンボルに変換され、シンボルがクロック線SCL312およびデータ線SDA314を介して送信される。一例では、2進データの元の20ビットが、12桁3進数に変換されることになるビット/遷移数変換器ブロック308に入力される。12桁3進数の各桁は、「遷移数」を表すことができる。2つの連続する遷移数は、同じ数字を有することができる。各遷移数は、2つの連続する順次シンボルが同じ値を有しないように、遷移/シンボルブロック310において順次シンボルに変換される。順次シンボルごとに1つの遷移が保証されるので、そのような順次シンボル遷移は、クロック信号を埋め込むための役割を果たすことができる。その後、各順次シンボル316が2線物理リンク(たとえば、SCL線312およびSDA線314を備える12Cバス)を介して送られる。

#### [0031]

図4は、3進数(遷移数)402と(順次)シンボル404との間の変換の一例を示す図である。3 進数、3進法は、遷移数とも呼ばれ、3つの取り得る数字または状態、0、1または2のうちの1つを有することができる。3進数の2つの連続する数字において同じ値が現れる場合もあるが、2つの連続するシンボルは同じ値を有しない。

## [0032]

変換関数は、先行する生のシンボル値に、遷移数+1を加算する。加算の結果として、3 より大きな数になる場合には、その数が0からロールオーバし、その結果が、現在のシンボルのための状態番号になる。

#### [0033]

第1のサイクル406において、第1の遷移数1が入力されるときに、先行するシンボルが1であるので、先行するシンボルに遷移数1+1が加算され、その結果3が、物理リンクに送られる現在のシンボル状態になる。

#### [0034]

第2のサイクル408では、次のサイクルにおいて遷移数0が入力され、先行するシンボル3に遷移数0+1が加算される。加算の結果として、4は3より大きくなるので、ロールオーバされた数0が現在のシンボルになる。

## [0035]

第3のサイクル410では、同じ遷移数0が入力される。変換ロジックが先行するシンボル0に1を加算し、現在のシンボル1を生成する。

#### [0036]

第4のサイクル412では、遷移数2が入力される。変換ロジックは、遷移数2+1を先行するシンボル1に加算し、現在のシンボル0を生成する(加算の結果、すなわち、4が3より大きいので、ロールオーバされた数0が現在のシンボルになる)。

10

20

30

#### [0037]

結果として、2つの連続する3進数字402が同じ数を有する場合であっても、この変換は、2つの連続するシンボル数字が異なる状態値を有することを保証する。このため、一連のシンボル404内の保証されたシンボル遷移がクロック信号を埋め込むための役割を果たすことができ、それにより、データ送信のためのI2Cバス内のクロック線SCLを解放することができる。

#### [0038]

図3を再び参照すると、受信機320において、そのプロセスは入れ替えられ、コード変換済みシンボルが元のビットに変換され、そのプロセスにおいて、シンボル遷移からクロック信号が抽出される。受信機320は、2線物理リンク(たとえば、SCL線324およびSDA線326を備える12Cバス)を介して一連の順次シンボル322を受信する。受信された順次シンボル322は、クロック・データ再生(CDR)ブロック328に入力され、クロックタイミングを再生し、コード変換済みシンボル(S)をサンプリングする。その後、シンボル/遷移数変換器ブロック330が、コード変換済み(順次)シンボルを、遷移数、すなわち、1つの3進数字に変換する。この例では、遷移数/ビット変換器332は、12個の遷移数を変換して、12桁3進数から元のデータの20ビットを復元する。

#### [0039]

本明細書において示される本技法を用いて、I2C標準バスが提供し、本明細書においてCCIeモードと呼ばれるものを超えて、制御バス108(図1)または204(図2)のリンク速度を高めることができる。一例において、制御データバス108に結合されるマスタノードおよび/またはスレープノードが、標準的なI2Cバスを使用して可能である同じ制御データバスより高いビット速度を達成するために、シンボル送信内にクロック信号を埋め込む送信機および/または受信機(図3に示される)を実装することができる。

#### [0040]

図5は、送信機502におけるビットから遷移数への、そしてその後、受信機504における遷移数からビットへの例示的な変換を示す。この例は、12個の遷移シンボルを用いる2線システムの場合の送信を示す。送信機502は、2進情報、Bitsを「Bits/12xT」変換器506に供給し、12個のシンボル遷移数T0~T11を生成する。受信機504は12個のシンボル遷移数T0~T11を受信し、シンボル遷移数は「12xT/Bits」変換器508に供給され、2進情報(Bits)が取り出される。T0~T11の1つのTあたりにr個の取り得るシンボル遷移状態がある場合には、12個の遷移が $r^{12}$ 個の異なる状態を送ることができる。2線バスの場合、 $r=2^2$ -1である。結果として、遷移T0...T11は、 $(2^2-1)^{12}$ 個の異なる状態を有することができるデータを含む。結果として、r=4-1=3であり、状態の数= $(4-1)^{12}=531441$ である。

#### [0041]

この例において、12個のシンボル遷移数を用いる2線システムの場合、1つのTあたりの取り得るシンボル遷移、r は $3(=2^2-1)$  と考えることができる。1つのグループ内のシンボル数が12である場合には、それぞれがTi: 0, 1, 2である12桁3進数(3進法):T11, T10,..., T2, T1, T0を用いることができる。たとえば、 $\{T11,T10,...,T2,T1,T0\}=\{2,1,0,0,1,1,0,1,0,1,2,1\}$  の場合、3進数は、

2100\_1101\_01213(3進数)

$=2 \times 3^{11} + 1 \times 3^{10} + 0 \times 3^{9} + 0 \times 3^{8}$

$+1 \times 3^7 + 1 \times 3^6 + 0 \times 3^5 + 1 \times 3^4$

$0 \times 3^3 + 1 \times 3^2 + 2 \times 3^1 + 1 \times 3^0$

=416356(0x65A64)

である。

## [0042]

このようにして、12個の遷移数を1つの数に変換することができる。3進数2100,1101,11 01,0121<sub>3</sub>が、たとえば図3の遷移数として用いられる場合があり、それにより、各整数が順次シンボルにマッピングされる場合があり、その逆も同様であることに留意されたい。

## [0043]

10

20

30

2線システムおよび12個のシンボル遷移数の場合に示される例は、n線システムおよびm個のシンボル遷移数に一般化することができる。T0~Tm-1の1つのTあたりにr個の取り得るシンボル遷移状態がある場合、m個の遷移がr<sup>m</sup>個の異なる状態、すなわち、r =  $2^{n-1}$ 1個の状態を送ることができる。結果として、遷移T0...Tm-1は、 $(2^{n}-1)^{m}$ 個の異なる状態を有することができるデータを含む。

## [0044]

図6はデータワード610を示しており、ただし、16ビット(ビット0~15)は読出しデータ であり、3ビットはパリティビット(16~18)である。言い換えると、読出しデータワード は16ビット読出しデータ値および3ビットパリティビットからなることができる。現在の アドレスワードの制御コードが'000'(C0)~'101'(C5)であるとき、後続のアドレスワード が存在することになる。次の書込みアドレスは、現在のデータのアドレス+制御データ値 である。'111'の制御コードは、SIDマーカのために予約されるので、違法である。制御コ ードが '110'(E)である場合には、次のワードはSID(スレーブID)または終了コードである 。図6には示されないが、データワード610は、非アクティブマスタデバイスが本明細書に おいて示されるようにアクティブマスタデバイスになろうと試みることを指示するために 用いられる予備ビット(たとえば、第20のビット、またはビットカウントが第0のビットか ら開始するとき、「ビット19」とも呼ばれる)を有することができる。図3~図5に示され るコード変換方式は、19ビット(ビット0~18と呼ばれる場合もある)がデータワード610に よって利用される場合があり、CCIeバス204(図2)を介して送信するために符号化される場 合があることを示す。しかし、そのコード変換方式は、12桁3進数内の少なくとも20ビッ トを実効的に送信することができる。ビット19が設定されるとき、ビット13~18は常に0 であり、ビット[12-0]は0x0000から0x1BF0までのみを表すことができる。結果として、ビ ット19(第20のビット)は、非アクティブマスタによって、マスタ要求を指示するために用 いられる場合がある。

#### [0045]

図7は、図3、図4および図5に示される符号化方式から生じる余分な(第20の)ビットの利用可能性を示す図である。コンピュータ科学において一般的であるように、ビット単位のカウントは0から開始し、第20のビットは多くの場合に、ビット19と呼ばれる。ここで、ビット0~18は、0000\_0000\_00003から2221\_2201\_20013の3進数範囲内で表される。2221\_2201\_20023から2222\_2222\_22223の範囲内の3進数は使用されない。結果として、3進数範囲2221\_2201\_20023から2222\_2222222223を用いて、ビット19(すなわち、第20のビット)を表すことができる。言い換えると、2221\_2201\_200233進数は、1000\_0000\_0000\_00000\_000002 進数(0x80000 16進数)であり、2222\_2222\_222233進数(0x81BF0)は取り得る最も大きな12桁の3進数である。マスタ要求の一実装形態では、アサート中非アクティブマスタによって、第20のビット(ビット19)が1に設定される。

## [0046]

図8は、アクティブマスタデバイスが、データバスの制御を非アクティブマスタデバイスに転送するための方法を示す。アクティブマスタデバイスは、制御データバスおよび共有単線割込み(IRQ)バスに結合することができる。複数の非アクティブマスタデバイスおよび/またはスレーブデバイスも、制御データバスおよび共有単線割込みバスに結合することができる。アクティブマスタデバイスは、IRQバスを介してアサートされる割込み信号に基づいて、データバスに結合されるすべてのデバイスに関するデータバスを介しての通信を管理することができる。アクティブマスタデバイスは、IRQ信号がアサートされたときを確認するために、IRQバスを監視することができる、804。その後、マスタデバイスは、どの非アクティブマスタデバイスがIRQバス上でIRQ信号をアサートしたかを確認するために、非アクティブマスタデバイスをポーリングすることができる、806。マスタ要求を行ったという非アクティブマスタデバイスのうちの1つからの指示を得ると、アクティブマスタは、データバスの制御をアサート中非アクティブマスタデバイスに引き渡す、808。

50

[0047]

20

10

30

20

30

40

50

図9は、単線IRQバス920が複数のスレーブデバイス918a~cおよび1つまたは複数のマスタデバイス912a~cによっていかに共有される場合があるかを示すブロック図であり、図2に示されるようなマスタ制御の要求および転送を実施することができる。この例では、スレーブデバイス918a~cおよびマスタデバイス912a~cは論理的にグループ化される(たとえば、グループ-1 906a、グループ-2 906bなど)。そのようなグループ化は、たとえば、あらかじめ構成することができるか、またはアクティブマスタ1デバイス912aによる起動時に動的に規定することができ(たとえば、列挙による)、その場合、マスタデバイス2および3 912b~cは非アクティブである。そのようなグループ化によって、マスタデバイス912aは、許容できないほどの遅延を生じることなく、どのスレーブデバイスおよび/または非アクティブマスタデバイスがIRQバス920上でIRQ信号をトリガしたかを、より迅速に識別できるようになる。

[0048]

各デバイスグループ906aおよび906bは、異なるIRQ信号を有することができる(たとえば 、図10に示される)。たとえば、第1のグループ906aは、第1の期間を有する第1の信号を用 いることができ、第2のグループ906bは、第2の期間を有する第2の信号を用いることがで き、それ以外も同様である。たとえば、「期間」は、アサート中スレーブデバイスによっ てIRQバス920がローに引き込まれる時間長とすることができる。他の形の信号区別、たと えば、異なるスレーブデバイスグループによって用いられるIRQ信号に関して異なる電圧 レベルなどを用いることもできることに留意されたい。一実装形態では、デバイスの「グ ループ」は、各「グループ」が単一のデバイスを含む場合があるように、論理グループを 規定することができる。他の実装形態では、各「グループ」は、2つ、3つおよび/または4 つのデバイスまたはそれより多くのデバイスを含むことができる。グループあたりのスレ ーブデバイスまたはマスタデバイスの数は、アサート中デバイスに問い合わせ、識別する のに要する時間の関数とすることができる。たとえば、IRQバス920に結合されるすべての デバイスがアクティブマスタデバイス912aによって問い合わせられなければならない場合 には、これにより、許容できないほどの長い遅延が生じるおそれがある。結果として、デ バイスをグループ化し、グループごとに異なるIRQ信号を使用することによって、マスタ デバイス912aは、マスタ要求を指示するために設定されたビット19を有するアサート中デ バイスを識別できるようになる。さらに、非アクティブマスタが906aにグループ化され、 スレーブが906bにグループ化されるように示されるが、非アクティブマスタおよびスレー ブは、一緒にグループ化することができる。

[0049]

マスタデバイス912aは、共有単線IRQバス920上でIRQ信号の発生を検出し、グループ内の各デバイスに問い合わせ、どのデバイスがIRQ信号をトリガまたはアサートしたかを識別する。たとえば、IRQ信号がグループ2 906bスレーブデバイスを識別する場合には、アクティブマスタデバイス912aは、グループ2内の第1のスレーブデバイス918aに(制御データバス908を用いて)レジスタステータス要求を送ることができる。

[0050]

第1のスレーブデバイス918aのステータス応答が、アサート中スレーブデバイスでないことを指示する場合には、マスタデバイス912aは、グループ2内の第2のスレーブデバイス918bに(制御データバス908を用いて)別のレジスタステータス要求を送ることができる。このプロセスは、IRQ信号をアサートしたスレーブデバイスが識別されるまで(スレーブがマスタになることができる一実装形態の場合)、グループ2906b内のすべてのスレーブデバイスに対して繰り返される。このプロセスは、IRQ信号をアサートしたスレーブデバイスが識別されるまで、グループ2906b内のすべてのスレーブデバイスに対して繰り返される。これは、グループからIRQステータスをスキャンする1つの方法であり、第1の要求中スレーブが見つけられるとき(たとえば、グループ内にさらに要求中スレーブが存在する場合であっても)、スキャニングが終わる。この方法が用いられるとき、マスタは第1の要求中スレーブからの要求のみに対応することを指示するか、または大域的に通知しなければならないので、対応されていないスレーブは、対応されるべきIRQを再発行しなければ

ならないことを知ることができる。

#### [0051]

グループからのIRQステータスをスキャンする別の方法は、グループ内のすべてのスレーブをスキャンし(そして、第1の要求中スレーブを検出した後であってもスキャンし続け)、すべての要求中スレーブのリストを保持することである。このようにして、現在アクティブのマスタは、スレーブにIRQを再発行させることなく、複数の要求中スレーブを見つけ、すべての要求に対応することができる。

#### [0052]

同様に、非アクティブマスタ912b~cのうちの1つからアクティブマスタ912aにシグナリングすることができる。たとえば、IRQ信号がグループ1 906aを識別する場合には、アクティブマスタデバイス912aは、グループ1内の第1の非アクティブマスタデバイス912bにレジスタステータス要求を(制御データバス908を用いて)送ることができる。

## [0053]

第1の非アクティブマスタデバイス912bのステータス応答が、アサート中非アクティブマスタデバイスでないことを指示する場合には、アクティブマスタデバイス912aは、グループ1内の第2の非アクティブマスタデバイス912cに(制御データバス908を用いて)別のレジスタステータス要求を送ることができる。このプロセスは、IRQ信号をアサートした非アクティブマスタデバイスが識別されるまで、グループ1 906a内のすべての非アクティブマスタデバイスが、IRQステータスレジスタのビット19を設定しているとき、現在のマスタは、その非アクティブマスタをアクティブにさせる。本明細書において用いられるときに、アクティブマスタという用語は、制御データバスを能動的に制御することを意味する。さらに、非アクティブマスタは、外部活動だけでなく、内部活動も行っている可能性があるが、非アクティブマスタは、制御データバスを介しての現在の制御を有しない。それゆえ、非アクティブは、活動していないことを意味するのではなく、むしろ、そのデバイスがその時点で制御データバスの通信または使用を能動的に制御または管理していないことのみを意味する。

#### [0054]

図10は、異なるグループに割り当てることができるか、または関連付けることができる 異なるIRQ信号の例を示す図である。この例は、第1の期間を有する第1のIRQ信号1002と、 第2の期間を有する第2のIRQ信号1004と、第3の期間を有する第3のIRQ信号1006とを示す。 さらに、異なるグループを区別する任意の方法を利用して、割込み要求を送るグループを 識別することができる。一例では、すべての非アクティブマスタデバイスに特定の信号を 割り当てることができ、その信号を用いて、IRQバスを介してのマスタ要求を指示するこ とができる。

#### [0055]

図11は、シングルマスタバスを介してのマルチマスタ動作のために構成された例示的なマスタデバイスを示すブロック図である。マスタデバイス1102は、第1の通信インターフェース/回路1106、第2の通信インターフェース/回路1108、および/または処理回路1104を含むことができる。第1の通信インターフェース/回路1106は、複数の他のデバイスが結合される場合がある単線割込み要求(IRQ)バスに結合するための役割を果たすことができる。第2の通信インターフェース/回路1108は、複数の他のデバイスがやはり結合されるデータバスに結合するための役割を果たすことができる。

#### [0056]

処理回路1104は、本明細書において説明される1つまたは複数の機能を実行する種々のサブ回路および/またはモジュールを含むことができる。たとえば、通信管理回路/モジュール1110は、IRQバスを介してアサートされた割込み信号に基づいて、データバスに結合されるすべてのデバイスに関するデータバスを介しての通信を管理するように構成することができる。IRQバス監視回路/モジュール1112は、IRQ信号がアサートされたときを確認するために、IRQバスを監視するように構成することができる。データバスポーリング回路/モジュール1114は、どの非アクティブマスタデバイスがIRQバス上でIRQ信号をアサー

10

20

30

40

20

30

40

50

トしたかを確認するために、データバスを介して非アクティブマスタデバイスをポーリングするように構成することができる。データバス引渡し回路/モジュール1116は、マスタ要求を行ったという非アクティブマスタデバイスからの指示を得ると、データバスの制御をアサート中非アクティブマスタデバイスに引き渡すように構成することができる。一例では、非アクティブマスタデバイスからのマスタ要求は、第1のインターフェースを介して得ることができる。非アクティブマスタデバイスからの指示は、第2のインターフェースを介して得ることができる。種々の例において、データバスはカメラ制御インターフェース拡張(CCIe)互換バスおよび/または双方向バスとすることができる。

#### [0057]

いくつかの実装形態では、処理回路は、得られたインジケータに基づいて、IRQ信号が関連付けられるアサート中非アクティブマスタデバイスを識別するようにさらに構成することができる。たとえば、各非アクティブマスタデバイスからのインジケータが異なるパルス幅を有する場合には、これは、アサート中非アクティブマスタを識別するのに十分である場合がある。

#### [0058]

他の実装形態では、処理回路は、IRQ信号が関連付けられるデバイスグループを識別するようにさらに構成することができる。たとえば、各デバイスグループは、単一のデバイスまたは複数のデバイスを含むことができる。グループが複数のデバイスを含む場合、処理回路は、どのデバイスがIRQバス上でIRQ信号をアサートしたかを確認するために、識別されたグループに関するデバイスをスキャンするようにさらに構成することができる。各グループが関連付けられるIRQ信号は、他のグループに関連付けられる他のIRQ信号とは異なるパルス幅を有することができる。

## [0059]

処理回路は、(a)ポーリングされる各非アクティブマスタデバイスから得られたステータスレジスタ内の特定のビットを調べることによって、ポーリングされる非アクティブマスタデバイスがIRQ信号をアサートし、マスタ要求を行ったか否かを確認し、および/または(b)データバスの制御を転送するために、データバスを介してアサート中非アクティブマスタデバイスにインジケータを送るようにさらに構成することができる。

#### [0060]

図面に示された構成要素、ステップ、特徴、および/または機能のうちの1つまたは複数は、再配置し、かつ/または組み合わせて単一の構成要素、ステップ、特徴または機能にすることができるか、あるいは複数の構成要素、ステップ、または機能において具現することができる。本明細書において開示された新規の特徴から逸脱することなく、さらなる要素、構成要素、ステップ、および/または機能も追加することもできる。図示される装置、デバイス、および/または構成要素は、図示された方法、特徴、またはステップのうちの1つまたは複数を実行するように構成することができる。本明細書において記載の新規のアルゴリズムは、ソフトウェアにおいて効率的に実現され、および/またはハードウェアに埋め込まれてもよい。

## [0061]

さらに、実施形態は、流れ図、フロー図、構造図、またはブロック図として示されるプロセスとして説明される場合があることに留意されたい。流れ図は、動作を順次プロセスとして説明する場合があるが、動作の多くは、並列にまたは同時に実行することができる。さらに、動作の順序は並べ替えることができる。プロセスは、その動作が完了したとき、終了する。プロセスは、方法、関数、手順、サブルーチン、サブプログラムなどに対応することができる。プロセスが関数に対応するときには、その終了は、その関数が、呼出し関数またはメイン関数に戻ることに対応する。

#### [0062]

さらに、記憶媒体は、リードオンリーメモリ(ROM)、ランダムアクセスメモリ(RAM)、磁気ディスク記憶媒体、光記憶媒体、フラッシュメモリデバイス、および/または情報を記憶するための他の機械可読媒体を含む、データを記憶するための1つまたは複数のデバイ

20

30

40

50

スを表す場合がある。「機械可読媒体(machine readable medium)」という用語は、限定はしないが、ポータブルまたは固定記憶デバイス、光記憶デバイス、ワイヤレスチャネル、ならびに命令および/またはデータを記憶するか、包含するか、または搬送することができる種々の他の媒体を含む。

#### [0063]

さらに、実施形態は、ハードウェア、ソフトウェア、ファームウェア、ミドルウェア、マイクロコード、またはそれらの任意の組合せによって実現することができる。ソフトウェア、ファームウェア、ミドルウェア、またはマイクロコードにおいて実現される場合、必要なタスクを実行するためのプログラムコードまたはコードセグメントは、記憶媒体をは他の記憶装置などの機械可読媒体に記憶することができる。プロセッサは必要なタスクを実行することができる。コードセグメントは、手順、関数、サブプログラム、プログラム、ルーチン、サブルーチン、モジュール、ソフトウェアパッケージ、クラス、またはの、ボータ構造もしくはプログラムステートメントの任意の組合せを表すことができる。コードセグメントは、情報、データ、引数、パラメータ、またはメモリ内容を渡し、かつ/または受け取ることによって、別のコードセグメントまたはハードウェア回路に結合することができる。情報、引数、パラメータ、データなどは、メモリ共有、メッセージパッシング、トークンパッシング、ネットワーク伝送などを含む任意の適切な手段を介して渡すことができるか、転送することができるか、または送信することができる。

#### [0064]

本明細書において開示される例に関して説明される種々の例示的な論理ブロック、モジュール、回路、要素、および/または構成要素は、汎用プロセッサ、デジタルシグナルプロセッサ(DSP)、特定用途向け集積回路(ASIC)、フィールドプログラマブルゲートアレイ(FPGA)もしくは他のプログラマブル論理構成要素、個別ゲートもしくはトランジスタ論理、個別ハードウェア構成要素、または本明細書において説明される機能を実行するように設計されたそれらの任意の組合せで実現または実行することができる。汎用プロセッサはマイクロプロセッサとすることができるが、代替形態では、プロセッサは、任意の従来のプロセッサ、コントローラ、マイクロコントローラ、または状態機械とすることができる。プロセッサはまた、コンピューティング構成要素の組合せ、たとえば、DSPとマイクロプロセッサとの組合せ、いくつかのマイクロプロセッサ、DSPコアと連係した1つまたは複数のマイクロプロセッサ、あるいは他の任意のそのような構成として実現することができる。

## [0065]

本明細書において開示される例に関連して説明される方法またはアルゴリズムは、ハードウェアにおいて直接に、プロセッサによって実行可能なソフトウェアモジュールにおいて、またはその両方の組合せにおいて、処理ユニット、プログラミング命令、または他の指示の形において具現することができ、単一のデバイス内に含まれる場合があるか、複数のデバイスにわたって分散する場合がある。ソフトウェアモジュールは、RAMメモリ、フラッシュメモリ、ROMメモリ、EPROMメモリ、EEPROMメモリ、レジスタ、ハードディスク、リムーバブルディスク、CD-ROM、または当技術分野で知られている任意の他の形態の記憶媒体に存在することができる。記憶媒体は、プロセッサがその記憶媒体から情報を読み取り、かつその記憶媒体に情報を書き込むことができるように、プロセッサに結合することができる。代替形態では、記憶媒体はプロセッサと一体に構成することができる。

#### [0066]

本明細書において開示された実施形態に関連して説明される種々の例示的な論理ブロック、モジュール、回路、およびアルゴリズムステップを、電子ハードウェア、コンピュータソフトウェア、または両方の組合せとして実現できることは当業者はさらに理解されよう。ハードウェアとソフトウェアとのこの互換性を明確に示すために、種々の例示的な構成要素、ブロック、モジュール、回路、およびステップが、これまで概してそれらの機能の観点から説明されてきた。そのような機能がハードウェアで実現されるか、ソフトウェアにおいて実施されるのかは、システム全体に課される特定の用途および設計制約によっ

#### て決まる。

### [0067]

本明細書において記載される本発明の種々の特徴は、本発明から逸脱することなく、異 なるシステムにおいて実施することができる。上記の実施形態は例にすぎず、本発明を限 定するものと解釈すべきではないことに留意されたい。実施形態の説明は、例示的であり 、特許請求の範囲を限定することは意図していない。したがって、本教示は、他のタイプ の装置、ならびに多くの代替形態、変更形態、および変形形態に容易に適用できることは 当業者には明らかであろう。

508 12xT/Bits变换器

610 データワード

## 【符号の説明】 10 [0068] 102 デバイス 104 ベースバンドプロセッサ 106 イメージセンサ 108 制御データバス 112 CCIeマスタ 114 CCIeスレーブ 116 画像データバス 118a 非アクティブマスタ 118b 非アクティブマスタ 20 120 単線共有IRQバス 202 スレーブデバイス 204 CCIeバス 206 IRQバス 208 非アクティブマスタX 210 現在アクティブのマスタ1 302 送信機 304 一連のデータビット 308 ビット/ 遷移数変換器ブロック 310 遷移/シンボルブロック 30 312 クロック線SCL 314 データ線SDA 316 順次シンボル 320 受信機 322 順次シンボル 324 SCL線 326 SDA線 328 クロック-データ再生(CDR)ブロック 330 シンボル/遷移数変換器ブロック 332 遷移数/ビット変換器 40 402 3進数(遷移数) 404 順次シンボル 第1のサイクル 406 408 第2のサイクル 410 第3のサイクル 412 第4のサイクル 502 送信機 504 受信機 506 Bits/12xT变换器

```

グループ1

906a

906b

グループ2

912a

マスタデバイス

912b

マスタデバイス

マスタデバイス

912c

スレーブデバイス

918a

918b

スレーブデバイス

918c

スレーブデバイス

920 単線IRQバス

第1のIRQ信号

1002

1004

第2のIRQ信号

1006

第3のIRQ信号

1102

マスタデバイス

1104

処理回路

第1の通信インターフェース/回路

1106

第2の通信インターフェース/回路

1108

1110

通信管理回路/モジュール

1112

IRQバス監視回路/モジュール

データバスポーリング回路/モジュール

1114

```

1116 データバス引渡し回路/モジュール

20

10

## 【図1】

## 【図2】

【図7】

【図8】

【図9】

【図10】

# 【図11】

## フロントページの続き

(72)発明者 リチャード・ドミニク・ウィートフェルト アメリカ合衆国・カリフォルニア・92121-1714・サン・ディエゴ・モアハウス・ドライブ・5775

(72)発明者 ジョージ・アラン・ウィリー アメリカ合衆国・カリフォルニア・92121-1714・サン・ディエゴ・モアハウス・ドライヴ・5775

## 審査官 田中 啓介

(56)参考文献 特開2006-120146(JP,A) 特開2012-194829(JP,A) 特開平05-282244(JP,A)

(58)調査した分野(Int.CI., DB名)

G 0 6 F 3 / 0 0 、 3 / 1 8 G 0 6 F 1 3 / 2 0 - 1 3 / 4 2 H 0 4 L 2 5 / 0 0 - 2 5 / 6 6