(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4826213号

(P4826213)

(45) 発行日 平成23年11月30日(2011.11.30)

(24) 登録日 平成23年9月22日(2011.9.22)

(51) Int.Cl.

F 1

H03K 19/0185 (2006.01)

H03K 19/00 101B

H03K 17/687 (2006.01)

H03K 17/687 F

請求項の数 17 (全 69 頁)

(21) 出願番号 特願2005-320938 (P2005-320938)

(22) 出願日 平成17年11月4日 (2005.11.4)

(65) 公開番号 特開2006-279918 (P2006-279918A)

(43) 公開日 平成18年10月12日 (2006.10.12)

審査請求日 平成20年10月17日 (2008.10.17)

(31) 優先権主張番号 特願2005-57596 (P2005-57596)

(32) 優先日 平成17年3月2日 (2005.3.2)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000002185

ソニー株式会社

東京都港区港南1丁目7番1号

(74) 代理人 100094053

弁理士 佐藤 隆久

(72) 発明者 甚田 誠一郎

東京都品川区北品川6丁目7番35号 ソ

ニー株式会社内

審査官 宮島 郁美

最終頁に続く

(54) 【発明の名称】 レベルシフト回路およびシフトレジスタ並びに表示装置

## (57) 【特許請求の範囲】

## 【請求項 1】

入力信号をレベルシフトして出力するレベルシフト回路であって、

第1のノードの電圧に応じてオンまたはオフし、当該電圧が第1のしきい値のときにオンとオフとを切り換え、当該オンのとき、レベルシフト信号の出力端子へ第1の電圧を出力する第1のスイッチと、

第2のノードの電圧に応じてオンまたはオフし、当該電圧が第2のしきい値のときにオンとオフとを切り換え、当該オンのとき、上記出力端子へ第2の電圧を出力する第2のスイッチと、

一方の端子に第1の入力信号を入力し、他方の端子が上記第1のノードに接続される第1のキャパシタと、

一方の端子に第2の入力信号を入力し、他方の端子が上記第2のノードに接続される第2のキャパシタと、

所定の期間において、上記第1のノードを上記第2の電圧で充電した状態から当該第1のノードの電圧を上記第1のしきい値に設定し、上記第2のノードを上記第1の電圧で充電した状態から当該第2のノードの電圧を上記第2のしきい値に設定する電圧設定回路と

を有するレベルシフト回路。

## 【請求項 2】

上記第1のしきい値および上記第2のしきい値は、上記第1の電圧から上記第2の電圧までの範囲に含まれており、

10

20

上記第1のスイッチは、上記第1のノードの電圧が上記第1のしきい値に対して上記第2の電圧側にある場合にオンし、上記第1の電圧側にある場合にオフし、

上記第2のスイッチは、上記第2のノードの電圧が上記第2のしきい値に対して上記第1の電圧側にある場合にオンし、上記第2の電圧側にある場合にオフし、

上記電圧設定回路は、第1の期間において、上記第1のノードの電圧が上記第1のしきい値に対して上記第2の電圧側にあるように上記第1のキャパシタを充電し、当該充電後の第2の期間において、オン状態の上記第1のスイッチから出力される電圧を上記第1のノードに供給し、第3の期間において、上記第2のノードの電圧が上記第2のしきい値に対して上記第1の電圧側にあるように上記第2のキャパシタを充電し、当該充電後の第4の期間において、オン状態の上記第2のスイッチから出力される電圧を上記第2のノードに供給する。10

請求項1に記載のレベルシフト回路。

【請求項3】

上記電圧設定回路は、上記第2の期間において上記第1のスイッチがオフした後、上記第3の期間における上記第2のキャパシタの充電を行う、

請求項2に記載のレベルシフト回路。

【請求項4】

上記電圧設定回路は、上記第1の期間において、上記第2のノードの電圧が上記第2のしきい値に対して上記第2の電圧側にあるように上記第2のキャパシタを充電する、20

請求項3に記載のレベルシフト回路。

【請求項5】

上記電圧設定回路は、

上記第1の期間において、上記第1のしきい値に対して上記第2の電圧側にある所定の電圧を上記第1のノードに供給する第1の電圧供給回路と、

上記第2の期間において、オンのときに上記第1の電圧が出力される上記第1のスイッチの一方の端子と上記第1のノードとを接続する第3のスイッチと、

上記第3の期間において、上記第2のしきい値に対して上記第1の電圧側にある所定の電圧を上記第2のノードに供給する第2の電圧供給回路と、

上記第4の期間において、オンのときに上記第2の電圧が出力される上記第2のスイッチの一方の端子と上記第2のノードとを接続する第4のスイッチと30

を含む、

請求項3に記載のレベルシフト回路。

【請求項6】

上記電圧設定回路は、上記第1の期間、上記第2の期間、上記第3の期間および上記第4の期間において、上記第1のスイッチと上記出力端子とを遮断する、および／または、上記第2のスイッチと上記出力端子とを遮断する、

請求項3に記載のレベルシフト回路。

【請求項7】

上記電圧設定回路は、上記第1の期間および上記第2の期間において、上記第1のスイッチと上記出力端子とを遮断し、上記第2のスイッチと上記出力端子とを接続し、上記第3の期間および上記第4の期間において、上記第1のスイッチと上記出力端子とを接続し、上記第2のスイッチと上記出力端子とを遮断する、40

請求項3に記載のレベルシフト回路。

【請求項8】

上記電圧設定回路は、上記第1の期間および上記第2の期間の少なくとも一部と上記第3の期間および上記第4の期間の少なくとも一部とが重なる第5の期間において、上記第1のスイッチと上記出力端子とを遮断する、および／または、上記第2のスイッチと上記出力端子とを遮断する、

請求項2に記載のレベルシフト回路。

【請求項9】

10

20

30

40

50

上記電圧設定回路は、

上記第1の期間において、上記第1のしきい値に対して上記第2の電圧側にある所定の電圧を上記第1のノードに供給する第1の電圧供給回路と、

上記第1の期間および上記第2の期間において、オンのときに上記第1の電圧が出力される上記第1のスイッチの一方の端子と上記第1のノードとを接続する第3のスイッチと、

上記第3の期間において、上記第2のしきい値に対して上記第1の電圧側にある所定の電圧を上記第2のノードに供給する第2の電圧供給回路と、

上記第3の期間および上記第4の期間において、オンのときに上記第2の電圧が出力される上記第2のスイッチの一方の端子と上記第2のノードとを接続する第4のスイッチと、

上記第1の期間および上記第2の期間において上記第1のスイッチと上記出力端子とを遮断し、上記第3の期間および上記第4の期間において上記第2のスイッチと上記出力端子とを遮断する第5のスイッチと、

を含む、

請求項2に記載のレベルシフト回路。

【請求項10】

上記電圧設定回路は、

上記第1の期間において、上記第1のしきい値に対して上記第2の電圧側にある所定の電圧を上記第1のノードに供給する第1の電圧供給回路と、

上記第2の期間において、オンのときに上記第1の電圧が出力される上記第1のスイッチの一方の端子と上記第1のノードとを接続する第3のスイッチと、

上記第3の期間において、上記第2のしきい値に対して上記第1の電圧側にある所定の電圧を上記第2のノードに供給する第2の電圧供給回路と、

上記第4の期間において、オンのときに上記第2の電圧が出力される上記第2のスイッチの一方の端子と上記第2のノードとを接続する第4のスイッチと、

を含み、

上記第3のスイッチは、

上記第1のスイッチに接続される第1端子と、上記第1のノードに接続される第2端子と、当該第1端子と当該第2端子との間の導通状態を制御する電圧を入力する制御端子とを有する第1スイッチ素子と、

上記第1スイッチ素子の制御端子と第1端子との間に接続される第1容量素子と、

上記第1スイッチ素子をオンまたはオフに駆動する電圧を入力する第1駆動入力ノードと、

上記第1駆動入力ノードと上記第1スイッチ素子の制御端子との間に接続され、上記第1スイッチ素子をオンに駆動する電圧が上記第1駆動入力ノードに入力されている状態で、上記第1スイッチ素子の制御端子の電圧が上記第1の電圧と上記第2の電圧との間の所定のしきい値に対して上記第2の電圧側にある場合にオンし、当該しきい値に対して上記第1の電圧側にある場合にオフする第2スイッチ素子と、

を含み、

上記第4のスイッチは、

上記第2のスイッチに接続される第1端子と、上記第2のノードに接続される第2端子と、当該第1端子と当該第2端子との間の導通状態を制御する電圧を入力する制御端子とを有する第3スイッチ素子と、

上記第3スイッチ素子の制御端子と第1端子との間に接続される第2容量素子と、

上記第3スイッチ素子をオンまたはオフに駆動する電圧を入力する第2駆動入力ノードと、

上記第2駆動入力ノードと上記第3スイッチ素子の制御端子との間に接続され、上記第3スイッチ素子をオンに駆動する電圧が上記第2駆動入力ノードに入力されている状態で、上記第3スイッチ素子の制御端子の電圧が上記第1の電圧と上記第2の電圧との間の

10

20

30

40

50

所定のしきい値に対して上記第1の電圧側にある場合にオンし、当該しきい値に対して上記第2の電圧側にある場合にオフする第4スイッチ素子と

を含む、

請求項2に記載のレベルシフト回路。

【請求項11】

上記出力端子からレベルシフト信号を出力する期間において、第3の電圧から第4の電圧までの電圧を有する入力信号を上記第1の入力信号および上記第2の入力信号として上記第1のキャパシタおよび上記第2のキャパシタに入力する第1の入力回路と、

上記電圧設定回路が上記第1のノードおよび上記第2のノードの電圧設定を行う期間において、上記第3の電圧から上記第4の電圧までの範囲に含まれる所定の電圧を上記第1の入力信号および上記第2の入力信号として上記第1のキャパシタおよび上記第2のキャパシタに入力する第2の入力回路と

を有する、

請求項2に記載のレベルシフト回路。

【請求項12】

初段に入力されたパルス信号を後段へ順次に伝送する、継続接続された複数のシフト段を具備し、

上記シフト段は、

前段からパルス信号が入力される期間、並びに、次段へパルス信号が出力される期間を検出する検出回路と、

上記検出回路が検出したパルス信号の入力期間および出力期間において、入力されるクロック信号の1サイクル内に含まれるパルス信号をレベルシフトして出力するレベルシフト回路と、

上記検出回路が検出したパルス信号の入力期間および出力期間において、上記レベルシフト回路から出力される信号をパルス信号として次段に出力し、上記レベルシフト回路を初期化する所定の期間において、一定のレベルの信号を次段に出力する出力回路と

を有し、

上記レベルシフト回路は、

第1のノードの電圧が、第1の電圧から第2の電圧までの範囲に含まれる第1のしきい値に対して上記第2の電圧側にある場合にオンし、上記第1のノードの電圧が、上記第1のしきい値に対して上記第1の電圧側にある場合にオフし、当該オンのとき、レベルシフト信号の出力端子へ上記第1の電圧を出力する第1のスイッチと、

第2のノードの電圧が、上記第1の電圧から上記第2の電圧までの範囲に含まれる第2のしきい値に対して上記第1の電圧側にある場合にオンし、上記第2のノードの電圧が、上記第2のしきい値に対して上記第2の電圧側にある場合にオフし、当該オンのとき、上記出力端子へ上記第2の電圧を出力する第2のスイッチと、

一方の端子に上記クロック信号を入力し、他方の端子が上記第1のノードに接続される第1のキャパシタと、

一方の端子に上記クロック信号を入力し、他方の端子が上記第2のノードに接続される第2のキャパシタと、

上記所定の期間において、上記第1のノードを上記第2の電圧で充電した状態から当該第1のノードの電圧を上記第1のしきい値に設定し、上記第2のノードを上記第1の電圧で充電した状態から当該第2のノードの電圧を上記第2のしきい値に設定する電圧設定回路と、

上記検出回路が検出したパルス信号の入力期間および出力期間において、上記クロック信号を上記第1のキャパシタおよび上記第2のキャパシタに入力する第1の入力回路と、

上記電圧設定回路が上記第1のノードおよび上記第2のノードの電圧設定を行う期間において、第3の電圧から第4の電圧までの範囲に含まれる所定の電圧を上記クロック信号の代わりに上記第1のキャパシタおよび上記第2のキャパシタに入力する第2の入力回

10

20

30

40

50

路と

を有し、

上記クロック信号は、上記第3の電圧と上記第4の電圧を交互に繰り返す信号であり、

継続接続される2つのシフト段は、互いの周期が等しく位相が異なるクロック信号を入

力する、

シフトレジスタ。

【請求項13】

継続接続される2つのシフト段は、互いに位相が反転したクロック信号を入力し、

各シフト段に含まれる検出回路は、上記第4の電圧を有するクロック信号が上記レベル

シフト回路においてレベルシフトされる期間を、パルス信号の出力期間として検出する、

請求項12に記載のシフトレジスタ。

【請求項14】

継続接続される2つのシフト段は、その一方が第1のクロック信号、他方が第2のクロ

ック信号を入力し、

1のシフト段を間に挟んで離れた2つのシフト段の一方に含まれる検出回路は、上記第

3の電圧を有するクロック信号が上記レベルシフト回路においてレベルシフトされる期間

を、パルス信号の出力期間として検出し、

当該離れた2つのシフト段の他方に含まれる検出回路は、上記第4の電圧を有するクロ

ック信号が上記レベルシフト回路においてレベルシフトされる期間を、パルス信号の出力

期間として検出し、

上記第1のクロック信号を入力するシフト段に含まれる検出回路と、当該シフト段の後

段に含まれる検出回路は、互いに同じ電圧を有するクロック信号が上記レベルシフト回路

においてレベルシフトされる期間を、パルス信号の出力期間として検出し、

上記第1のクロック信号は、上記第2のクロック信号が上記第3の電圧のとき、上記第

3の電圧から上記第4の電圧へ変化する、

請求項12に記載のシフトレジスタ。

【請求項15】

上記レベルシフト回路は、上記第1のスイッチに上記第1の電圧を入力する経路、およ

び/または、上記第2のスイッチに上記第2の電圧を入力する経路に挿入され、少なくとも

も上記検出回路が検出するパルス信号の入力期間および出力期間並びに上記所定の期間に

おいてオンし、他の期間においてオフする第6のスイッチを有する、

請求項12に記載のシフトレジスタ。

【請求項16】

入力信号をレベルシフトして出力するレベルシフト回路と、

複数の画素を含む画素アレイ部と、

上記レベルシフト回路から出力されるレベルシフト信号に応じて上記画素アレイ部の各

画素を駆動する駆動回路と

を具備し、

上記レベルシフト回路は、

第1のノードの電圧に応じてオンまたはオフし、当該電圧が第1のしきい値のときにお

ンとオフとを切り替え、当該オンのとき、上記レベルシフト信号の出力端子へ第1の電

圧を出力する第1のスイッチと、

第2のノードの電圧に応じてオンまたはオフし、当該電圧が第2のしきい値のときにお

ンとオフとを切り替え、当該オンのとき、上記出力端子へ第2の電圧を出力する第2の

スイッチと、

一方の端子に第1の入力信号を入力し、他方の端子が上記第1のノードに接続される

第1のキャパシタと、

一方の端子に第2の入力信号を入力し、他方の端子が上記第2のノードに接続される

第2のキャパシタと、

上記第1のノードを上記第2の電圧で充電した状態から当該第1のノードの電圧を上

10

20

30

40

50

記第1のしきい値に設定し、上記第2のノードを上記第1の電圧で充電した状態から当該第2のノードの電圧を上記第2のしきい値に設定する電圧設定回路と

を有する、

表示装置。

【請求項17】

行列状に配列された複数の画素を含む画素アレイ部と、

上記画素アレイ部の各行を順番に選択するパルス信号を発生する第1のシフトレジスタと、当該選択した行に属する各画素を順番に選択するパルス信号を発生する第2のシフトレジスタとを有し、選択した画素を駆動する駆動回路と

を具備し、

10

上記第1のシフトレジスタおよび上記第2のシフトレジスタは、

初段に入力されたパルス信号を後段へ順次に伝送する、縦続接続された複数のシフトを具備し、

上記シフト段は、

前段からパルス信号が入力される期間、並びに、次段へパルス信号が出力される期間を検出する検出回路と、

上記検出回路が検出したパルス信号の入力期間および出力期間において、入力されるクロック信号の1サイクル内に含まれるパルス信号をレベルシフトして出力するレベルシフト回路と、

上記検出回路が検出したパルス信号の入力期間および出力期間において、上記レベルシフト回路から出力される信号をパルス信号として次段に出力し、上記レベルシフト回路を初期化する所定の期間において、一定のレベルの信号を次段に出力する出回路と

を有し、

20

上記レベルシフト回路は、

第1のノードの電圧が、第1の電圧から第2の電圧までの範囲に含まれる第1のしきい値に対して上記第2の電圧側にある場合にオンし、上記第1のノードの電圧が、上記第1のしきい値に対して上記第1の電圧側にある場合にオフし、当該オンのとき、レベルシフト信号の出力端子へ上記第1の電圧を出力する第1のスイッチと、

第2のノードの電圧が、上記第1の電圧から上記第2の電圧までの範囲に含まれる第2のしきい値に対して上記第1の電圧側にある場合にオンし、上記第2のノードの電圧が、上記第2のしきい値に対して上記第2の電圧側にある場合にオフし、当該オンのとき、上記出力端子へ上記第2の電圧を出力する第2のスイッチと、

30

一方の端子に上記クロック信号を入力し、他方の端子が上記第1のノードに接続される第1のキャパシタと、

一方の端子に上記クロック信号を入力し、他方の端子が上記第2のノードに接続される第2のキャパシタと、

上記所定の期間において、上記第1のノードを上記第2の電圧で充電した状態から当該第1のノードの電圧を上記第1のしきい値に設定し、上記第2のノードを上記第1の電圧で充電した状態から当該第2のノードの電圧を上記第2のしきい値に設定する電圧設定回路と、

40

上記検出回路が検出したパルス信号の入力期間および出力期間において、上記クロック信号を上記第1のキャパシタおよび上記第2のキャパシタに入力する第1の入回路と、

上記電圧設定回路が上記第1のノードおよび上記第2のノードの電圧設定を行う期間において、第3の電圧から第4の電圧までの範囲に含まれる所定の電圧を上記クロック信号の替わりに上記第1のキャパシタおよび上記第2のキャパシタに入力する第2の入回路と

を有し、

上記クロック信号は、上記第3の電圧と上記第4の電圧を交互に繰り返す信号であり、縦続接続される2つのシフト段は、互いの周期が等しく位相が異なるクロック信号を入

50

力する、

表示装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、入力信号の振幅を変換するレベルシフト回路とこのレベルシフト回路を搭載する表示装置に係り、特に、液晶表示装置や有機EL(OLED)表示装置などの表示装置に用いられるレベルシフト回路に関するものである。

【背景技術】

【0002】

レベルシフト回路には従来から種々の方式があり、例えば、カレントミラー回路を用いて構成されたレベルシフト回路が知られている(例えば、特許文献1参照)。

【0003】

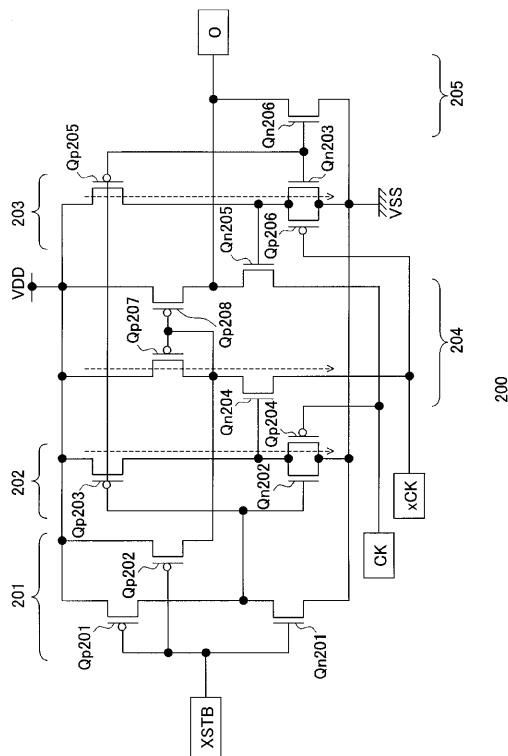

図4-1は、従来のカレントミラー型レベルシフト回路の構成の一例を示す図である。

図4-1に示すカレントミラー型レベルシフト回路200は、回路動作制御部201と、2つのバイアスシフト部202および203と、レベルシフト部204と、出力部205とを有する。

【0004】

回路動作制御部201は、p型MOSトランジスタQp201, Qp202と、n型MOSトランジスタQn201とを有する。

p型MOSトランジスタQp201およびn型MOSトランジスタQn201は、正側の電源電圧VDDが供給される電源ライン(以下、「電源ラインVDD」と表記する)と、負側の電源電圧VSSが供給される電源ライン(以下、「電源ラインVSS」と表記する)との間に直列に接続され、ゲート同士およびドレイン同士がそれぞれ共通に接続されている。

p型MOSトランジスタQp202は、そのソースが電源ラインVDDに接続され、そのゲートがp型MOSトランジスタQp201およびn型MOSトランジスタQn201の各ゲートに接続される。

【0005】

p型MOSトランジスタQp201およびn型MOSトランジスタQn201の共通接続されたゲートには、回路動作制御信号XSTBが入力される。この回路動作制御信号XSTBは、回路のスタンバイ時(非駆動時)においてロー・レベルに設定され、回路の駆動時においてハイ・レベルに設定される。

【0006】

バイアスシフト部202は、p型MOSトランジスタQp203, Qp204と、n型MOSトランジスタQn202とを有する。

p型MOSトランジスタQp203およびn型MOSトランジスタQn202は、電源ラインVDDと電源ラインVSSとの間に直列に接続され、互いのゲートがp型MOSトランジスタQp201およびn型MOSトランジスタQn201のドレインに共通に接続される。p型MOSトランジスタQp204は、n型MOSトランジスタQn202と並列に接続され、そのゲートにクロック信号CKが入力される。

このバイアスシフト部202においては、クロック信号CKの直流バイアスをシフトする動作が行われる。

【0007】

バイアスシフト部203は、p型MOSトランジスタQp205, Qp206と、n型MOSトランジスタQn203とを有する。

p型MOSトランジスタQp205およびn型MOSトランジスタQn203は、電源ラインVDDと電源ラインVSSとの間に直列に接続され、互いのゲートが共通に接続される。p型MOSトランジスタQp206は、n型MOSトランジスタQn203と並列に接続され、そのゲートにクロック信号xCKが入力される。クロック信号xCKは、ク

10

20

30

40

50

ロック信号CKに対して逆相の信号である。

このバイアスシフト部203においては、逆相のクロック信号xCCKの直流バイアスをシフトする動作が行われる。

#### 【0008】

レベルシフト部204は、p型MOSトランジスタQp207, p208と、n型MOSトランジスタQn204, Qn205とを有する。

p型MOSトランジスタQp207およびQp208は、カレントミラー回路を構成する。p型MOSトランジスタQp207およびQp208のソースは電源ラインVDDに共通接続され、そのゲートはp型MOSトランジスタQp207のドレインに共通接続される。p型MOSトランジスタQp207のドレインは、p型MOSトランジスタQp202のドレインに接続される。10

n型MOSトランジスタQn204は、そのドレインがp型MOSトランジスタQp207のドレインに接続され、そのゲートがp型MOSトランジスタQp203およびn型MOSトランジスタQn202のドレインに接続され、そのソースにクロック信号xCCKが入力される。n型MOSトランジスタQn205は、そのドレインがp型MOSトランジスタQp208のドレインに接続され、そのゲートがp型MOSトランジスタQp205およびn型MOSトランジスタQn203のドレインに接続され、そのソースにクロック信号CKが入力される。

このレベルシフト部204は、互いに逆位相のクロック信号xCCKおよびCKをn型MOSトランジスタQn204およびn205のソースに入力するカレントミラーアンプを構成する。20

#### 【0009】

出力部205は、n型MOSトランジスタQ206を有する。n型MOSトランジスタQ206は、そのドレインがp型MOSトランジスタQp208およびn型MOSトランジスタQn205のドレインに接続され、そのソースが電源ラインVSSに接続され、そのゲートがp型MOSトランジスタQp205およびn型MOSトランジスタQn203のゲートに接続される。

【特許文献1】特開2003-347926号公報

#### 【発明の開示】

##### 【発明が解決しようとする課題】

#### 【0010】

図41に示すレベルシフト回路200では、カレントミラー回路を構成する対のp型MOSトランジスタQp207, Qp208の特性が良く揃っている必要があるため、トランジスタの特性のばらつきに回路の動作が影響を受け易い。30

#### 【0011】

また、このレベルシフト回路200では、カレントミラー回路の動作に伴ってトランジスタにリーケ電流が流れる。すなわち、クロック信号CK, xCKの直流バイアスをシフトするバイアスシフト部202および203と、このクロック信号CK, xCKの振幅を電源電圧VSS - VDDの振幅に変換するレベルシフト部204において、図中の点線で示した経路にリーケ電流が流れる。そのため、レベルシフト回路200は、リーケ電流による消費電力が大きくなる。40

#### 【0012】

本発明はかかる事情に鑑みてなされたものであり、その目的は、トランジスタ等の素子の特性ばらつきに回路動作が影響を受け難いレベルシフト回路およびシフトレジスタと、そのようなレベルシフト回路やシフトレジスタを搭載する表示装置を提供することにある。

#### 【課題を解決するための手段】

#### 【0013】

本発明の第1の観点に係るレベルシフト回路は、入力信号をレベルシフトして出力する。このレベルシフト回路は、第1のノードの電圧に応じてオンまたはオフし、当該電圧が50

第1のしきい値のときにオンとオフとを切り換え、当該オンのとき、レベルシフト信号の出力端子へ第1の電圧を出力する第1のスイッチと、第2のノードの電圧に応じてオンまたはオフし、当該電圧が第2のしきい値のときにオンとオフとを切り換え、当該オンのとき、上記出力端子へ第2の電圧を出力する第2のスイッチと、一方の端子に第1の入力信号を入力し、他方の端子が上記第1のノードに接続される第1のキャパシタと、一方の端子に第2の入力信号を入力し、他方の端子が上記第2のノードに接続される第2のキャパシタと、所定の期間において、上記第1のノードを上記第2の電圧で充電した状態から当該第1のノードの電圧を上記第1のしきい値に設定し、上記第2のノードを上記第1の電圧で充電した状態から当該第2のノードの電圧を上記第2のしきい値に設定する電圧設定回路とを有する。

10

#### 【0014】

本発明の第2の観点に係るシフトレジスタは、初段に入力されたパルス信号を後段へ順次に伝送する、継続接続された複数のシフト段を具備する。

上記シフト段は、前段からパルス信号が入力される期間、並びに、次段へパルス信号が出力される期間を検出する検出回路と、上記検出回路が検出したパルス信号の入力期間および出力期間において、入力されるクロック信号の1サイクル内に含まれるパルス信号をレベルシフトして出力するレベルシフト回路と、上記検出回路が検出したパルス信号の入力期間および出力期間において、上記レベルシフト回路から出力される信号をパルス信号として次段に出力し、上記レベルシフト回路を初期化する所定の期間において、一定のレベルの信号を次段に出力する出力回路とを有する。

20

上記レベルシフト回路は、第1のノードの電圧が、第1の電圧から第2の電圧までの範囲に含まれる第1のしきい値に対して上記第2の電圧側にある場合にオンし、上記第1のノードの電圧が、上記第1のしきい値に対して上記第1の電圧側にある場合にオフし、当該オンのとき、レベルシフト信号の出力端子へ上記第1の電圧を出力する第1のスイッチと、第2のノードの電圧が、上記第1の電圧から上記第2の電圧までの範囲に含まれる第2のしきい値に対して上記第1の電圧側にある場合にオンし、上記第2のノードの電圧が、上記第2のしきい値に対して上記第2の電圧側にある場合にオフし、当該オンのとき、上記出力端子へ上記第2の電圧を出力する第2のスイッチと、一方の端子に上記クロック信号を入力し、他方の端子が上記第1のノードに接続される第1のキャパシタと、一方の端子に上記クロック信号を入力し、他方の端子が上記第2のノードに接続される第2のキャパシタと、上記所定の期間において、上記第1のノードを上記第2の電圧で充電した状態から当該第1のノードの電圧を上記第1のしきい値に設定し、上記第2のノードを上記第1の電圧で充電した状態から当該第2のノードの電圧を上記第2のしきい値に設定する電圧設定回路と、上記検出回路が検出したパルス信号の入力期間および出力期間において、上記クロック信号を上記第1のキャパシタおよび上記第2のキャパシタに入力する第1の入力回路と、上記電圧設定回路が上記第1のノードおよび上記第2のノードの電圧設定を行う期間において、第3の電圧から第4の電圧までの範囲に含まれる所定の電圧を上記クロック信号の代わりに上記第1のキャパシタおよび上記第2のキャパシタに入力する第2の入力回路とを有する。

30

上記クロック信号は、上記第3の電圧と上記第4の電圧を交互に繰り返す信号であり、継続接続される2つのシフト段は、互いの周期が等しく位相が異なるクロック信号を入力する。

40

#### 【0015】

本発明の第3の観点に係る表示装置は、入力信号をレベルシフトして出力するレベルシフト回路と、複数の画素を含む画素アレイ部と、上記レベルシフト回路から出力されるレベルシフト信号に応じて上記画素アレイ部の各画素を駆動する駆動回路とを有する。第3の観点に係る表示装置は、このレベルシフト回路として、上記第1の観点に係るレベルシフト回路を有する。

#### 【0016】

本発明の第4の観点に係る表示装置は、行列状に配列された複数の画素を含む画素アレ

50

イ部と駆動回路とを具備する。上記駆動回路は、上記画素アレイ部の各行を順番に選択するパルス信号を発生する第1のシフトレジスタと、当該選択した行に属する各画素を順番に選択するパルス信号を発生する第2のシフトレジスタとを有しており、選択した画素を駆動する。第4の観点に係る表示装置は、この第1のシフトレジスタおよび第2のシフトレジスタとして、上記第2の観点に係るシフトレジスタを有する。

#### 【0017】

上記本発明によると、上記所定の期間において、上記第1のノードの電圧は上記第1のしきい値に設定され、上記第2のノードの電圧は上記第2のしきい値に設定される。そして、この所定の期間の後、上記第1のノードおよび上記第2のノードは、フローティング状態に設定される。

10

この状態で、上記第1の入力信号の電圧が僅かに変化すると、上記第1のノードはフローティング状態にあるため、上記第1の入力信号の電圧変化に応じて上記第1のノードの電圧が上記第1のしきい値から変化し、上記第1のスイッチのオンとオフが切り換わる。

また、この状態で、上記第2の入力信号の電圧が僅かに変化すると、上記第2のノードはフローティング状態にあるため、上記第2の入力信号の電圧変化に応じて上記第2のノードの電圧が上記第2のしきい値から変化し、上記第2のスイッチのオンとオフが切り換わる。

例えば、上記第1のスイッチがオフからオン、上記第2のスイッチがオンからオフへ変化するように上記第1の入力信号および上記第2の入力信号の電圧が僅かに変化すると、上記出力端子の電圧は、上記第2の電圧から上記第1の電圧へ変化する。逆に、上記第2のスイッチがオンからオフ、上記第2のスイッチがオフからオンへ変化するように上記第1の入力信号および上記第2の入力信号の電圧が僅かに変化すると、上記出力端子の電圧は、上記第1の電圧から上記第2の電圧へ変化する。

20

このように、上記第1の入力信号および上記第2の入力信号の僅かな電圧変化によって、上記出力端子からは、上記第1の電圧と上記第2の電圧との間で変化するレベルシフト信号が出力される。

#### 【0018】

上記第1のしきい値および上記第2のしきい値は、好適には、上記第1の電圧から上記第2の電圧までの範囲に含まれる。

また、好適には、上記第1のスイッチは、上記第1のノードの電圧が上記第1のしきい値に対して上記第2の電圧側にある場合にオンし、上記第1の電圧側にある場合にオフし、上記第2のスイッチは、上記第2のノードの電圧が上記第2のしきい値に対して上記第1の電圧側にある場合にオンし、上記第2の電圧側にある場合にオフする。

30

この場合、上記電圧設定回路は、第1の期間において、上記第1のノードの電圧が上記第1のしきい値に対して上記第2の電圧側にあるように上記第1のキャパシタを充電し、当該充電後の第2の期間において、オン状態の上記第1のスイッチから出力される電圧を上記第1のノードに供給し、第3の期間において、上記第2のノードの電圧が上記第2のしきい値に対して上記第1の電圧側にあるように上記第2のキャパシタを充電し、当該充電後の第4の期間において、オン状態の上記第2のスイッチから出力される電圧を上記第2のノードに供給しても良い。

40

#### 【0019】

また、上記電圧設定回路は、上記第2の期間において上記第1のスイッチがオフした後、上記第3の期間における上記第2のキャパシタの充電を行っても良い。

この場合、好適には、上記電圧設定回路は、上記第1の期間において、上記第2のノードの電圧が上記第2のしきい値に対して上記第2の電圧側にあるように上記第2のキャパシタを充電する。

また、この場合、上記電圧設定回路は、上記第1の期間、上記第2の期間、上記第3の期間および上記第4の期間において、上記第1のスイッチと上記出力端子とを遮断しても良いし、上記第2のスイッチと上記出力端子とを遮断しても良い。

あるいは、上記電圧設定回路は、上記第1の期間および上記第2の期間において、上記

50

第1のスイッチと上記出力端子とを遮断し、上記第2のスイッチと上記出力端子とを接続し、上記第3の期間および上記第4の期間において、上記第1のスイッチと上記出力端子とを接続し、上記第2のスイッチと上記出力端子とを遮断しても良い。

【0020】

また、上記電圧設定回路は、上記第1の期間および上記第2の期間の少なくとも一部と上記第3の期間および上記第4の期間の少なくとも一部とが重なる第5の期間において、上記第1のスイッチと上記出力端子とを遮断しても良いし、上記第2のスイッチと上記出力端子とを遮断しても良い。。

【発明の効果】

【0021】

本発明によれば、トランジスタ等の素子の特性ばらつきに回路の動作が影響を受け難くすることができる。

10

【発明を実施するための最良の形態】

【0022】

以下、本発明の実施形態について、図面を参照して説明する。

【0023】

<第1の実施形態>

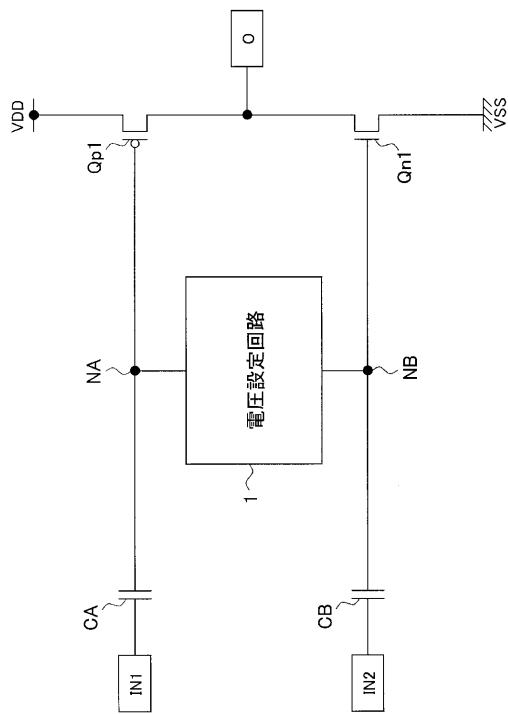

図1は、本発明の第1の実施形態に係るレベルシフト回路の構成の一例を示す図である。

図1に示すレベルシフト回路は、p型MOSトランジスタQ<sub>p1</sub>と、n型MOSトランジスタQ<sub>n1</sub>と、キャパシタC<sub>A</sub>と、キャパシタC<sub>B</sub>と、電圧設定回路1とを有する。

20

【0024】

p型MOSトランジスタQ<sub>p1</sub>を含む回路は、本発明の第1のスイッチの一実施形態である。

n型MOSトランジスタQ<sub>n1</sub>を含む回路は、本発明の第2のスイッチの一実施形態である。

キャパシタC<sub>A</sub>は、本発明の第1のキャパシタの一実施形態である。

キャパシタC<sub>B</sub>は、本発明の第2のキャパシタの一実施形態である。

【0025】

p型MOSトランジスタQ<sub>p1</sub>は、ノードNAの電圧に応じてオンまたはオフするスイッチとして動作する。p型MOSトランジスタQ<sub>p1</sub>は、ノードNAの電圧が‘V<sub>DD</sub>-V<sub>thp</sub>’のときにオンとオフとを切り換え、そのオンのとき、レベルシフト信号Oの出力端子に正側の電圧‘V<sub>DD</sub>’を出力する。なお、‘V<sub>thp</sub>’は、p型MOSトランジスタQ<sub>p1</sub>のしきい電圧を示す。

30

p型MOSトランジスタQ<sub>p1</sub>は、ノードNAの電圧が‘V<sub>DD</sub>-V<sub>thp</sub>’より高い場合にオフし、‘V<sub>DD</sub>-V<sub>thp</sub>’より低い場合にオンする。

図1の例に示すように、p型MOSトランジスタQ<sub>p1</sub>のソースは電源ラインV<sub>DD</sub>に接続され、そのドレインはレベルシフト信号Oの出力端子に接続され、そのゲートはノードNAに接続される。

【0026】

40

n型MOSトランジスタQ<sub>n1</sub>は、ノードNBの電圧に応じてオンまたはオフするスイッチとして動作する。n型MOSトランジスタQ<sub>n1</sub>は、ノードNBの電圧が‘V<sub>SS</sub>+V<sub>thn</sub>’のときにオンとオフとを切り換え、そのオンのとき、レベルシフト信号Oの出力端子に負側の電圧‘V<sub>SS</sub>’を出力する。なお、‘V<sub>thn</sub>’は、n型MOSトランジスタQ<sub>n1</sub>のしきい電圧を示す。

n型MOSトランジスタQ<sub>n1</sub>は、ノードNBの電圧が‘V<sub>SS</sub>+V<sub>thn</sub>’より高い場合にオンし、‘V<sub>SS</sub>+V<sub>thn</sub>’より低い場合にオフする。

図1の例に示すように、n型MOSトランジスタQ<sub>n1</sub>のソースは電源ラインV<sub>SS</sub>に接続され、そのドレインはレベルシフト信号Oの出力端子に接続され、そのゲートはノードNBに接続される。

50

## 【0027】

キャパシタC Aは、その一方の端子に第1の入力信号IN 1を入力し、他方の端子がノードN Aに接続される。

## 【0028】

キャパシタC Bは、その一方の端子に第2の入力信号IN 2を入力し、他方の端子がノードN Bに接続される。

## 【0029】

電圧設定回路1は、例えばレベルシフト動作を開始する前や、レベルシフト動作中の所定の期間において、ノードN Aの電圧を‘V DD - V th p’に設定し、ノードN Bの電圧を‘V SS + V th n’に設定する。そして、当該所定の期間の後、ノードN AおよびN Bをフローティング状態にする。

## 【0030】

電圧設定回路1は、例えば次のようにして、ノードN AおよびN Bを上記の電圧に設定する。

すなわち、電圧設定回路1は、まず第1の期間において、ノードN Aの電圧が‘V DD - V th p’より低い電圧になるようにキャパシタC Aを充電し、この充電後の第2の期間において、オン状態にあるp型MOSトランジスタQ p 1から出力される電圧をノードN Aに供給する。これにより、ノードN Aの電圧は電圧‘V DD’に向かって上昇し、その電圧が‘V DD - V th p’に達したところで、p型MOSトランジスタQ p 1が自らオフする。その結果、ノードN Aの電圧は‘V DD - V th p’に設定される。

また、電圧設定回路1は、第3の期間において、ノードN Bの電圧が‘V SS + V th n’より高い電圧になるようにキャパシタC Bを充電し、この充電後の第4の期間において、オン状態にあるn型MOSトランジスタQ n 1から出力される電圧をノードN Bに供給する。これにより、ノードN Bの電圧は電圧‘V SS’に向かって低下し、その電圧が‘V SS + V th n’に達したところで、n型MOSトランジスタQ n 1が自らオフする。その結果、ノードN Bの電圧は‘V SS + V th n’に設定される。

## 【0031】

ここで、上述した構成を有する図1に示すレベルシフト回路の動作を説明する。

所定の期間において、ノードN AおよびN Bの電圧は、p型MOSトランジスタQ p 1およびn型MOSトランジスタQ n 1のオン／オフの切り換わり点の電圧(‘V DD - V th p’、‘V SS + V th n’)にそれぞれ設定される。そして、上記所定の期間の後、ノードN AおよびN Bは、フローティング状態に設定される。

この状態で、第1の入力信号IN 1の電圧が低下する方向に変化すると、ノードN Aはフローティング状態にあるため、ノードN Aの電圧も第1の入力信号IN 1に応じて‘V DD - V th p’より低下する方向に変化する。これにより、p型MOSトランジスタQ p 1はオンする。また、第2の入力信号の電圧が低下する方向に変化すると、ノードN Bはフローティング状態にあるため、ノードN Bの電圧も第2の入力信号IN 2に応じて‘V SS + V th n’より低下する方向に変化する。これにより、n型MOSトランジスタQ n 1はオフする。したがって、この場合、p型MOSトランジスタQ p 1がオン、n型MOSトランジスタQ n 1がオフするため、レベルシフト信号Oの電圧は‘V DD’になる。

逆に、第1の入力信号IN 1および第2の入力信号IN 2の電圧が共に上昇する方向に変化すると、ノードN AおよびN Bの電圧もこれに応じて共に上昇する方向に変化するため、p型MOSトランジスタQ p 1はオフし、n型MOSトランジスタQ n 1はオンする。その結果、レベルシフト信号Oの電圧は‘V SS’になる。

このように、図1に示すレベルシフト回路によれば、比較的小さい振幅を持つ第1の入力信号IN 1および第2の入力信号IN 2を、電源電圧V DD～V SSの範囲で変化する振幅の大きいレベルシフト信号Oに変換することができる。

## 【0032】

また、図1に示すレベルシフト回路では、電圧設定回路1によってノードN Aの電圧が

10

20

30

40

50

‘VDD - Vthp’に設定され、ノードNBの電圧が‘VSS + Vthn’に設定される。これにより、例えば製造上のばらつきによってトランジスタのしきい電圧‘Vthp’、‘Vthn’がばらついても、ノードNAおよびNBの電圧は、電圧設定回路1によって、このばらつきを加味した適切な電圧に設定される。

したがって、図1に示すレベルシフト回路によれば、トランジスタ(Qp1, Qn1)のしきい電圧のばらつきに影響されることなく、安定したレベルシフト動作を行うことができる。

### 【0033】

更に、図1に示すレベルシフト回路では、第1の入力信号IN1および第2の入力信号IN2を同相の信号とすることにより、p型MOSトランジスタQp1またはn型MOSトランジスタQn1の何れか一方をオン、他方をオフに設定することができるため、p型MOSトランジスタQp1およびn型MOSトランジスタQn1を貫通するリーク電流はほとんど流れない。ノードNAおよびNBについても、レベルシフト動作時にはフローティング状態になるため、リーク電流は流れない。

したがって、図1に示すレベルシフト回路によれば、レベルシフト動作に伴うリーク電流を抑制し、消費電力を小さくすることができる。

### 【0034】

しかも図1に示すレベルシフト回路において、ノードNAおよびNBの電圧は、p型MOSトランジスタQp1およびn型MOSトランジスタQn1のオン／オフの切り換わり点の電圧にそれぞれ設定されている。これにより、第1の入力信号IN1および第2の入力信号IN2の信号振幅が、しきい電圧‘Vthp’、‘Vthn’より小さい振幅であっても、レベルシフト動作が可能である。

したがって、図1に示すレベルシフト回路によれば、トランジスタのしきい電圧より小さい振幅の信号であっても、電源電圧VDD～VSSの範囲で変化する振幅の大きい信号に変換することができ、信号の変換範囲を広くすることができる。

### 【0035】

#### <第2の実施形態>

次に、本発明の第2の実施形態について説明する。

本実施形態に係るレベルシフト回路は、上述した第1の実施形態に係るレベルシフト回路における電圧設定回路の構成をより具体化したものである。

### 【0036】

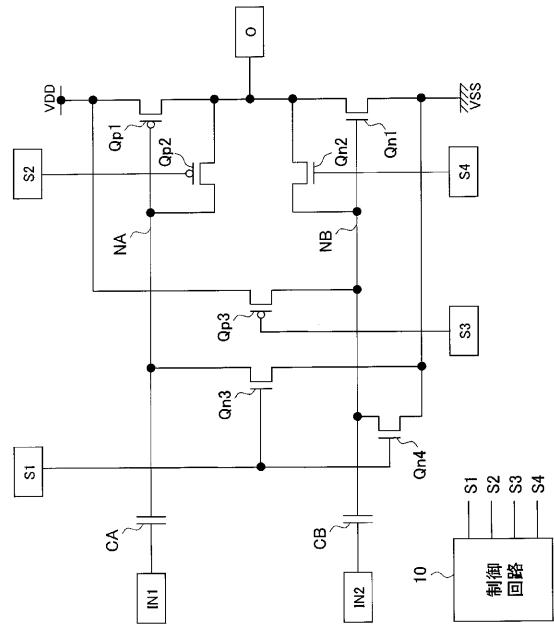

図2は、本発明の第2の実施形態に係るレベルシフト回路の構成の一例を示す図であり、図1と図2の同一符号は同一の構成を有する。

図2に示すレベルシフト回路は、図1に示すレベルシフト回路における電圧設定回路1として、p型MOSトランジスタQp2, Qp3と、n型MOSトランジスタQn2, Qn3, Qn4と、制御回路10とを有しており、他の構成については図1に示すレベルシフト回路と同じである。

### 【0037】

図2に示すレベルシフト回路において、p型MOSトランジスタQp1を含む回路は、本発明の第1のスイッチの一実施形態である。

n型MOSトランジスタQn1を含む回路は、本発明の第2のスイッチの一実施形態である。

キャパシタCAは、本発明の第1のキャパシタの一実施形態である。

キャパシタCBは、本発明の第2のキャパシタの一実施形態である。

n型MOSトランジスタQn3およびQn4を含む回路は、本発明の第1の電圧供給回路の一実施形態である。

p型MOSトランジスタQp3を含む回路は、本発明の第2の電圧供給回路の一実施形態である。

p型MOSトランジスタQp2を含む回路は、本発明の第3のスイッチの一実施形態である。

10

20

30

40

50

n型MOSトランジスタQn2を含む回路は、本発明の第4のスイッチの一実施形態である。

【0038】

n型MOSトランジスタQn3は、ゲートに入力される制御信号S1に応じて、ノードNAに電圧‘VSS’を供給する。n型MOSトランジスタQn3は、ノードNAと電源ラインVSSとの間に接続されており、第1の期間（図3の時刻t1～t2）においてオン状態に設定される。

【0039】

n型MOSトランジスタQn4は、ゲートに入力される制御信号S1に応じて、ノードNBに電圧‘VSS’を供給する。n型MOSトランジスタQn4は、ノードNBと電源ラインVSSとの間に接続されており、第1の期間（図3の時刻t1～t2）においてオン状態になる。

10

【0040】

p型MOSトランジスタQp2は、ゲートに入力される制御信号S2に応じて、p型MOSトランジスタQp1のドレインとノードNAとを接続または遮断するスイッチとして動作する。p型MOSトランジスタQp2は、第2の期間（図3の時刻t2～t3）においてp型MOSトランジスタQp1のドレインとノードNAとを接続する。

【0041】

p型MOSトランジスタQp3は、ゲートに入力される制御信号S3に応じて、ノードNBに電圧‘VDD’を供給する。p型MOSトランジスタQp3は、ノードNBと電源ラインVDDとの間に接続されており、第3の期間（図3の時刻t3～t4）においてオン状態に設定される。

20

【0042】

n型MOSトランジスタQn2は、ゲートに入力される制御信号S4に応じてn型MOSトランジスタQn1のドレインとノードNBとを接続または遮断するスイッチとして動作する。n型MOSトランジスタQn2は、第4の期間（図3の時刻t4～t5）において、n型MOSトランジスタQn1のドレインとノードNBとを接続する。

【0043】

制御回路10は、ノードNAおよびNBに適切な電圧が設定されるように、上述した制御信号S1～S4を生成する。

30

すなわち、第1の期間（t1～t2）において、制御信号S1を電圧‘VDD’に設定し、他の期間において、制御信号S1を電圧‘VSS’に設定する。

第1の期間に続く第2の期間（t2～t3）において、制御信号S2を電圧‘VSS’に設定し、他の期間において、制御信号S2を電圧‘VDD’に設定する。

第2の期間に続く第3の期間（t3～t4）において、制御信号S3を電圧‘VSS’に設定し、他の期間において、制御信号S3を電圧‘VDD’に設定する。

第3の期間に続く第4の期間（t4～t5）において、制御信号S4を電圧‘VDD’に設定し、他の期間において、制御信号S4を電圧‘VSS’に設定する。

【0044】

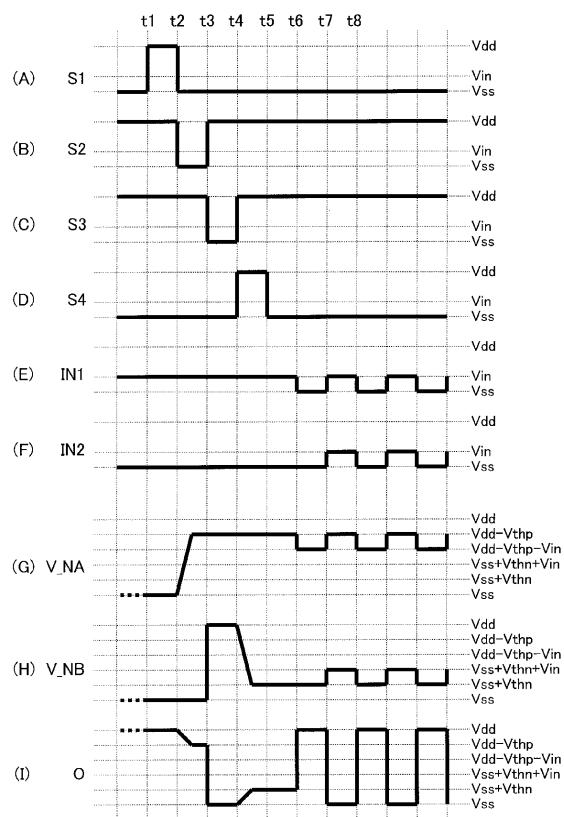

次に、上述した構成を有する図2に示すレベルシフト回路の動作について、図3を参照して説明する。

40

【0045】

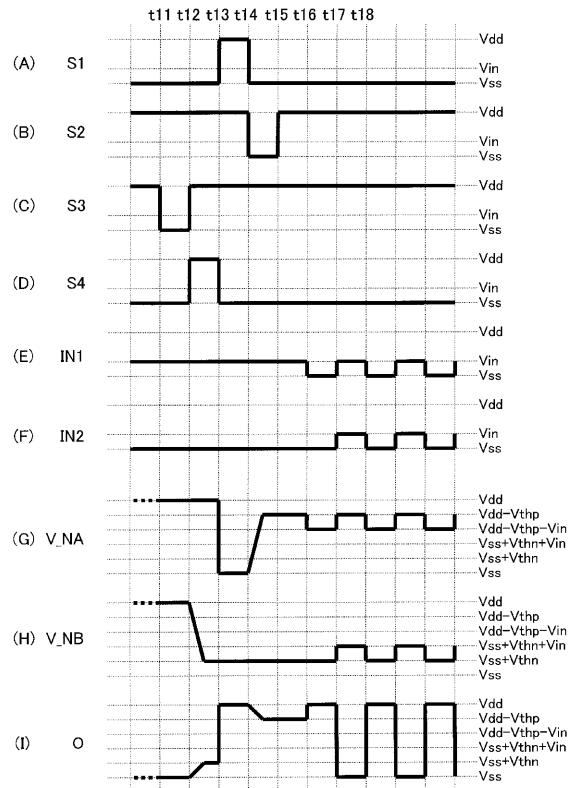

図3は、図2に示すレベルシフト回路における各部の信号波形の一例を示す図である。

図3（A）は、制御信号S1の電圧波形を示す。

図3（B）は、制御信号S2の電圧波形を示す。

図3（C）は、制御信号S3の電圧波形を示す。

図3（D）は、制御信号S4の電圧波形を示す。

図3（E）は、第1の入力信号IN1の電圧波形を示す。

図3（F）は、第2の入力信号IN2の電圧波形を示す。

図3（G）は、ノードNAの電圧V\_NAの電圧波形を示す。

50

図3 (H) は、ノードN Bの電圧V\_N Bの電圧波形を示す。

図3 (I) は、レベルシフト信号Oの電圧波形を示す。

#### 【0046】

ノードN AおよびN Bの電圧設定を行う前の初期の状態において、制御回路10は、制御信号S1およびS4を電圧‘VSS’、制御信号S2およびS3を電圧‘VDD’に設定する。この場合、電圧設定回路の各トランジスタ(Qp2, Qp3, Qn2, Qn3, Qn4)は全てオフする。

#### 【0047】

また、この初期の状態において、第1の入力信号IN1は電圧‘Vin’に設定され、第2の入力信号IN2は電圧‘VSS’に設定される。なお、第1の入力信号IN1および第2の入力信号IN2は、電圧‘Vin’をハイレベル、電圧‘VSS’をローレベルとする2値の信号である。10

#### 【0048】

第1の期間(t1 ~ t2)において、制御回路10は制御信号S1を電圧‘VDD’に設定する。これにより、n型MOSトランジスタQn3がオンし、ノードN Aは電圧‘VSS’に設定され、p型MOSトランジスタQp1はオンする。

#### 【0049】

このとき、n型MOSトランジスタQn4がオンし、ノードN Bも電圧‘VSS’に設定されるため、n型MOSトランジスタQn1はオフする。

第1の期間(t1 ~ t2)においてn型MOSトランジスタQn1をオフすることにより、p型MOSトランジスタQp1およびn型MOSトランジスタQn1が同時にオンすることによる貫通電流の発生を防止することができる。20

#### 【0050】

ノードN Aが電圧‘VSS’に設定された後の第2の期間(t2 ~ t3)において、制御回路10は制御信号S1を電圧‘VSS’に戻し、制御信号S2を電圧‘VSS’に立ち下げる。これにより、p型MOSトランジスタQp2がオンし、ノードN Aとp型MOSトランジスタQp1のドレインとが接続される。

このとき、p型MOSトランジスタQp1はオン状態にあり、電源ラインVDDからp型MOSトランジスタQp1を介してノードN Aに電流が流れため、ノードN Aの電圧V\_N Aは電圧‘VDD’に向かって上昇する。30

電圧V\_N Aが‘VDD - Vthp’に達すると、p型MOSトランジスタQp1が自らオフするため、電圧V\_N Aの上昇は停止する。その結果、ノードN Aの電圧V\_N Aは‘VDD - Vthp’に設定される。

#### 【0051】

p型MOSトランジスタQp1がオフした後の第3の期間(t3 ~ t4)において、制御回路10は制御信号S2を電圧‘VDD’に戻し、制御信号S3を電圧‘VSS’に立ち下げる。これにより、p型MOSトランジスタQp3がオンし、ノードN Bは電圧‘VDD’に設定され、n型MOSトランジスタQn1はオンする。

#### 【0052】

なお、このときp型MOSトランジスタQp1はオフ状態にあるため、n型MOSトランジスタQn1がオンに変化しても、両者を貫通する電流は流れない。40

#### 【0053】

ノードN Bが電圧‘VDD’に設定された後の第4の期間(t4 ~ t5)において、制御回路10は制御信号S3を電圧‘VDD’に戻し、制御信号S4を電圧‘VDD’に立ち上げる。これにより、n型MOSトランジスタQn2がオンし、ノードN Bとn型MOSトランジスタQn1のドレインとが接続される。

このとき、n型MOSトランジスタQn1はオン状態にあり、ノードN Bからn型MOSトランジスタQn1を介して電源ラインVSSに電流が流れため、ノードN Bの電圧V\_N Bは電圧‘VSS’に向かって低下する。

電圧V\_N Bが‘VSS + Vthn’に達すると、n型MOSトランジスタQn1が自50

らオフするため、電圧  $V_{NB}$  の低下は停止する。その結果、ノード  $NB$  の電圧  $V_{NB}$  は ' $V_{SS} + V_{thn}$ ' に設定される。

#### 【0054】

ノード  $NA$  の電圧  $V_{NA}$  が ' $V_{DD} - V_{thp}$ '、ノード  $NB$  の電圧  $V_{NB}$  が ' $V_{SS} + V_{thn}$ ' に設定された後、第1の入力信号  $IN_1$  および第2の入力信号  $IN_2$  は同相に変化する（時刻  $t_6$  以降）。

例えば時刻  $t_6 \sim t_7$  において、第1の入力信号  $IN_1$  および第2の入力信号  $IN_2$  がローレベル ( $V_{SS}$ ) になり、電圧  $V_{NA}$  は ' $V_{DD} - V_{thp} - V_{in}$ '、電圧  $V_{NB}$  は ' $V_{SS} + V_{thn}$ ' になる。これにより、p型MOSトランジスタ  $Q_{p1}$  がオン、n型MOSトランジスタ  $Q_{n1}$  がオフするため、レベルシフト信号  $O$  は電圧 ' $V_{DD}$ ' になる。

10

また、例えば時刻  $t_7 \sim t_8$  において、第1の入力信号  $IN_1$  および第2の入力信号  $IN_2$  がハイレベル ( $V_{in}$ ) になり、電圧  $V_{NA}$  は ' $V_{DD} - V_{thp}$ '、電圧  $V_{NB}$  は ' $V_{SS} + V_{thn} + V_{in}$ ' になる。これにより、n型MOSトランジスタ  $Q_{n1}$  がオン、p型MOSトランジスタ  $Q_{p1}$  がオフするため、レベルシフト信号  $O$  は電圧 ' $V_{SS}$ ' になる。

#### 【0055】

以上説明したように、本実施形態に係るレベルシフト回路によれば、ノード  $NA$  の電圧が ' $V_{DD} - V_{thp}$ ' に設定され、ノード  $NB$  の電圧が ' $V_{SS} + V_{thn}$ ' に設定されるため、トランジスタ ( $Q_{p1}$ ,  $Q_{n1}$ ) のしきい電圧のばらつきに影響されることなく、安定したレベルシフト動作を行うことができる。

20

また、ノード  $NA$  および  $NB$  の電圧設定期間 ( $t_1 \sim t_5$ ) やレベルシフト動作の期間において、p型MOSトランジスタ  $Q_{p1}$  および n型MOSトランジスタ  $Q_{n1}$  が同時にオンすることを防止できるため、レベルシフト動作に伴うリーク電流を抑制し、消費電力を小さくすることができる。

更に、ノード  $NA$  および  $NB$  の電圧が、p型MOSトランジスタ  $Q_{p1}$  および n型MOSトランジスタ  $Q_{n1}$  のオン / オフの切り換わり点の電圧にそれぞれ設定されるため、トランジスタのしきい電圧より小さい振幅の信号であってもレベルシフト動作が可能であり、信号の変換範囲を広くすることができる。

30

#### 【0056】

##### <第3の実施形態>

次に、本発明の第3の実施形態について説明する。

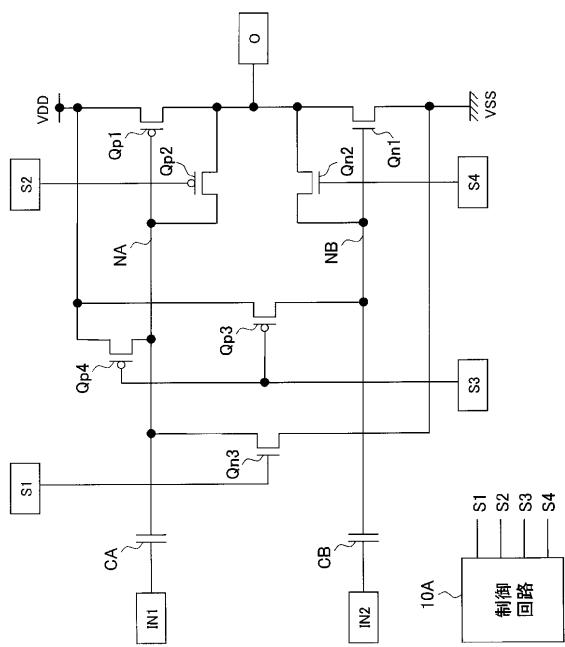

第2の実施形態に係るレベルシフト回路（図2）では、高電位側のノード  $NA$  の電圧設定を行った後に低電位側のノード  $NB$  の電圧設定を行うが、本実施形態に係るレベルシフト回路（図4）では、低電位側のノード  $NB$  の電圧設定を行った後に高電位側のノード  $NA$  の電圧設定を行う。

#### 【0057】

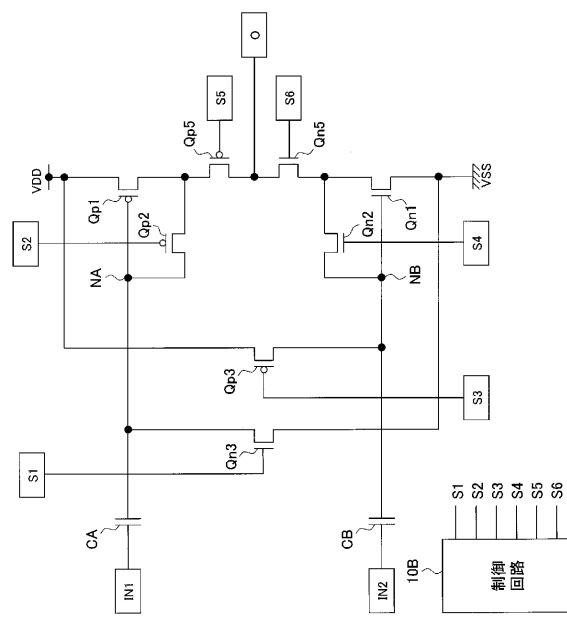

図4は、本発明の第3の実施形態に係るレベルシフト回路の構成の一例を示す図であり、図1と図3の同一符号は同一の構成を有する。

図4に示すレベルシフト回路は、図1に示すレベルシフト回路における電圧設定回路1として、p型MOSトランジスタ  $Q_{p2}$ ,  $Q_{p3}$ ,  $Q_{p4}$  と、n型MOSトランジスタ  $Q_{n2}$ ,  $Q_{n3}$  と、制御回路  $10A$  とを有しており、他の構成については図1に示すレベルシフト回路と同じである。

40

#### 【0058】

図4に示すレベルシフト回路において、n型MOSトランジスタ  $Q_{n1}$  を含む回路は、本発明の第1のスイッチの一実施形態である。

p型MOSトランジスタ  $Q_{p1}$  を含む回路は、本発明の第2のスイッチの一実施形態である。

キャパシタ  $CB$  は、本発明の第1のキャパシタの一実施形態である。

キャパシタ  $CA$  は、本発明の第2のキャパシタの一実施形態である。

50

p型MOSトランジスタQp3およびQp4を含む回路は、本発明の第1の電圧供給回路の一実施形態である。

n型MOSトランジスタQn3を含む回路は、本発明の第2の電圧供給回路の一実施形態である。

n型MOSトランジスタQn2を含む回路は、本発明の第3のスイッチの一実施形態である。

p型MOSトランジスタQp2を含む回路は、本発明の第4のスイッチの一実施形態である。

#### 【0059】

p型MOSトランジスタQp3は、ゲートに入力される制御信号S3に応じて、ノードNBに電圧‘VDD’を供給する。p型MOSトランジスタQp3は、ノードNBと電源ラインVDDとの間に接続されており、第1の期間（図5の時刻t11～t12）においてオン状態に設定される。 10

#### 【0060】

p型MOSトランジスタQp4は、ゲートに入力される制御信号S3に応じて、ノードNAに電圧‘VDD’を供給する。p型MOSトランジスタQp4は、ノードNAと電源ラインVDDとの間に接続されており、第1の期間（図5の時刻t11～t12）においてオン状態に設定される。

#### 【0061】

n型MOSトランジスタQn2は、ゲートに入力される制御信号S4に応じて、n型MOSトランジスタQn1のドレインとノードNBとを接続または遮断するスイッチとして動作する。n型MOSトランジスタQn2は、第2の期間（図5の時刻t12～t13）において、n型MOSトランジスタQn1のドレインとノードNBとを接続する。 20

#### 【0062】

n型MOSトランジスタQn3は、ゲートに入力される制御信号S1に応じて、ノードNAに電圧‘VSS’を供給する。n型MOSトランジスタQn3は、ノードNAと電源ラインVSSとの間に接続されており、第3の期間（図5の時刻t13～t14）においてオン状態に設定される。

#### 【0063】

p型MOSトランジスタQp2は、ゲートに入力される制御信号S2に応じて、p型MOSトランジスタQp1のドレインとノードNAとを接続または遮断するスイッチとして動作する。p型MOSトランジスタQp2は、第4の期間（図5の時刻t14～t15）において、p型MOSトランジスタQp1のドレインとノードNAとを接続する。 30

#### 【0064】

制御回路10Aは、ノードNAおよびNBに適切な電圧が設定されるように、上述した制御信号S1～S4を生成する。

すなわち、第1の期間（t11～t12）において、制御信号S3を電圧‘VSS’に設定し、他の期間において、制御信号S3を電圧‘VDD’に設定する。

第1の期間に続く第2の期間（t12～t13）において、制御信号S4を電圧‘VDD’に設定し、他の期間において、制御信号S4を電圧‘VSS’に設定する。 40

第2の期間に続く第3の期間（t13～t14）において、制御信号S1を電圧‘VDD’に設定し、他の期間において、制御信号S1を電圧‘VSS’に設定する。

第3の期間に続く第4の期間（t14～t15）において、制御信号S2を電圧‘VSS’に設定し、他の期間において、制御信号S2を電圧‘VDD’に設定する。

#### 【0065】

次に、上述した構成を有する図4に示すレベルシフト回路の動作について、図5を参照して説明する。

#### 【0066】

図5は、図4に示すレベルシフト回路における各部の信号波形の一例を示す図である。

図5（A）～（I）の信号波形は、図3（A）～（I）の信号波形に対応する。 50

## 【0067】

ノードN AおよびN Bの電圧設定を行う前の初期の状態において、制御回路10Aは制御信号S1およびS4を電圧‘VSS’、制御信号S2およびS3を電圧‘VDD’に設定し、電圧設定回路の各トランジスタ(Qp2, Qp3, Qp4, Qn2, Qn3)を全てオフさせる。

また、この初期の状態において、第1の入力信号IN1はハイレベルの電圧‘Vin’に設定され、第2の入力信号IN2はローレベルの電圧‘VSS’に設定される。

## 【0068】

第1の期間(t1 ~ t2)において、制御回路10Aは制御信号S3を電圧‘VSS’に設定する。これにより、p型MOSトランジスタQp3がオンし、ノードN Bは電圧‘VDD’に設定され、n型MOSトランジスタQn1はオンする。

10

## 【0069】

このとき、p型MOSトランジスタQp4がオンし、ノードN Aも電圧‘VDD’に設定されるため、p型MOSトランジスタQp1はオフする。

第1の期間(t11 ~ t12)においてp型MOSトランジスタQp1をオフすることにより、p型MOSトランジスタQp1およびn型MOSトランジスタQn1が同時にオンすることによる貫通電流の発生を防止することができる。

## 【0070】

ノードN Bが電圧‘VDD’に設定された後の第2の期間(t12 ~ t13)において、制御回路10Aは制御信号S3を電圧‘VDD’に戻し、制御信号S4を電圧‘VDD’に立ち上げる。これにより、n型MOSトランジスタQn2がオンし、n型MOSトランジスタQn1のドレインとノードN Bとが接続される。

20

このとき、n型MOSトランジスタQn1はオン状態にあり、ノードN Bからn型MOSトランジスタQn1を介して電源ラインVSSに電流が流れため、ノードN Bの電圧V\_N Bは電圧‘VSS’に向かって低下する。

電圧V\_N Bが‘VSS + Vthn’に達すると、n型MOSトランジスタQn1が自らオフするため、電圧V\_N Bの低下は停止する。その結果、ノードN Bの電圧V\_N Bは‘VSS + Vthn’に設定される。

## 【0071】

n型MOSトランジスタQn1がオフした後の第3の期間(t13 ~ t14)において、制御回路10Aは制御信号S4を電圧‘VSS’に戻し、制御信号S1を電圧‘VDD’に立ち上げる。これにより、n型MOSトランジスタQn3がオンし、ノードN Aは電圧‘VSS’に設定され、p型MOSトランジスタQp1はオンする。

30

## 【0072】

なお、このときn型MOSトランジスタQn1はオフ状態にあるため、p型MOSトランジスタQp1がオンに変化しても、両者を貫通する電流は流れない。

## 【0073】

ノードN Aが電圧‘VSS’に設定された後の第4の期間(t14 ~ t15)において、制御回路10Aは制御信号S1を電圧‘VSS’に戻し、制御信号S2を電圧‘VSS’に立ち下げる。これにより、p型MOSトランジスタQp2がオンし、p型MOSトランジスタQp1のドレインとノードN Aとが接続される。

40

このとき、p型MOSトランジスタQp1はオン状態にあり、電源ラインVDDからp型MOSトランジスタQp1を介してノードN Aに電流が流れため、ノードN Aの電圧V\_N Aは電圧‘VDD’に向かって上昇する。

電圧V\_N Aが‘VDD - Vthp’に達すると、p型MOSトランジスタQp1が自らオフするため、電圧V\_N Aの上昇は停止する。その結果、ノードN Aの電圧V\_N Aは‘VDD - Vthp’に設定される。

## 【0074】

ノードN Aの電圧V\_N Aが‘VDD - Vthp’、ノードN Bの電圧V\_N Bが‘VSS + Vthn’に設定された後の動作については、図2に示すレベルシフト回路と同様

50

である。

例えば時刻  $t_{16} \sim t_{17}$  において、第1の入力信号  $I_{N1}$  および第2の入力信号  $I_{N2}$  がローレベル ( $V_{SS}$ ) になると、p型MOSトランジスタ  $Q_{p1}$  がオン、n型MOSトランジスタ  $Q_{n1}$  がオフし、レベルシフト信号  $O$  は電圧 ‘ $V_{DD}$ ’ になる。

また、例えば時刻  $t_{17} \sim t_{18}$  において、第1の入力信号  $I_{N1}$  および第2の入力信号  $I_{N2}$  がハイレベル ( $V_{IN}$ ) になると、n型MOSトランジスタ  $Q_{n1}$  がオン、p型MOSトランジスタ  $Q_{p1}$  がオフし、レベルシフト信号  $O$  は電圧 ‘ $V_{SS}$ ’ になる。

#### 【0075】

以上説明したように、本実施形態に係るレベルシフト回路においても、図2に示すレベルシフト回路と同様な動作が実現されるため、これと同様な効果を奏することができる。

10

すなわち、ノードNAの電圧が ‘ $V_{DD} - V_{thp}$ ’、ノードNBの電圧が ‘ $V_{SS} + V_{thn}$ ’ に設定されるため、トランジスタ ( $Q_{p1}$ ,  $Q_{n1}$ ) のしきい電圧のばらつきに影響されることなく、安定したレベルシフト動作を行うことができる。

また、p型MOSトランジスタ  $Q_{p1}$  およびn型MOSトランジスタ  $Q_{n1}$  が同時にオンすることを防止できるため、レベルシフト動作に伴うリーク電流を抑制できる。

また、ノードNAおよびNBの電圧が、p型MOSトランジスタ  $Q_{p1}$  およびn型MOSトランジスタ  $Q_{n1}$  のオン/オフの切り換わり点の電圧にそれぞれ設定されるため、トランジスタのしきい電圧より小さい振幅の信号であってもレベルシフト動作が可能である。

#### 【0076】

20

##### <第4の実施形態>

次に、本発明の第4の実施形態について説明する。

第2および第3の実施形態に係るレベルシフト回路では、p型MOSトランジスタ  $Q_{p1}$  およびn型MOSトランジスタ  $Q_{n1}$  が同時にオンすることによる貫通電流の発生を防ぐため、ノードNAおよびNBの電圧設定が別々に行われているが、本実施形態に係るレベルシフト回路では、両者の電圧設定を並行に行う。

#### 【0077】

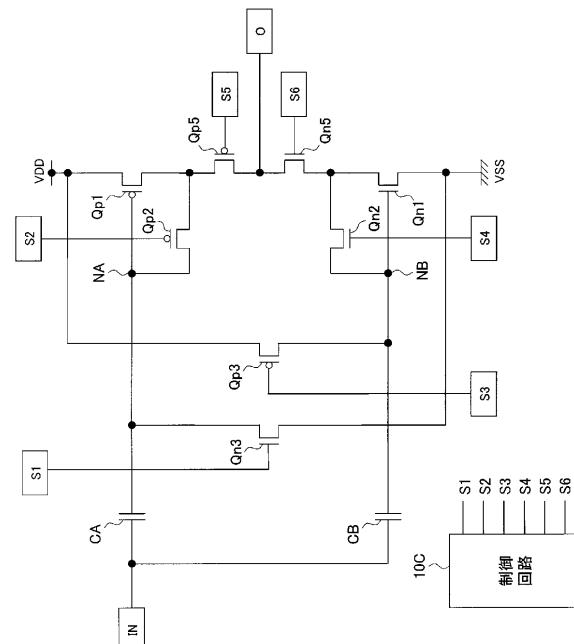

図6は、本発明の第4の実施形態に係るレベルシフト回路の構成の一例を示す図であり、図1と図6の同一符号は同一の構成を有する。

図6に示すレベルシフト回路は、図1に示すレベルシフト回路における電圧設定回路1として、p型MOSトランジスタ  $Q_{p2}$ ,  $Q_{p3}$ ,  $Q_{p5}$  と、n型MOSトランジスタ  $Q_{n2}$ ,  $Q_{n3}$ ,  $Q_{n5}$  と、制御回路10Bとを有しており、他の構成については図1に示すレベルシフト回路と同じである。

30

#### 【0078】

図6に示すレベルシフト回路において、p型MOSトランジスタ  $Q_{p1}$  を含む回路は、本発明の第1のスイッチの一実施形態である。

n型MOSトランジスタ  $Q_{n1}$  を含む回路は、本発明の第2のスイッチの一実施形態である。

キャパシタCAは、本発明の第1のキャパシタの一実施形態である。

キャパシタCBは、本発明の第2のキャパシタの一実施形態である。

40

n型MOSトランジスタ  $Q_{n3}$  を含む回路は、本発明の第1の電圧供給回路の一実施形態である。

p型MOSトランジスタ  $Q_{p3}$  を含む回路は、本発明の第2の電圧供給回路の一実施形態である。

p型MOSトランジスタ  $Q_{p2}$  を含む回路は、本発明の第3のスイッチの一実施形態である。

n型MOSトランジスタ  $Q_{n2}$  を含む回路は、本発明の第4のスイッチの一実施形態である。

p型MOSトランジスタ  $Q_{p5}$  およびn型MOSトランジスタ  $Q_{n5}$  を含む回路は、本発明の第5のスイッチの一実施形態である。

50

## 【0079】

n型MOSトランジスタQn3は、ゲートに入力される制御信号S1に応じて、ノードNAに電圧‘VSS’を供給する。n型MOSトランジスタQn3は、ノードNAと電源ラインVSSとの間に接続されており、第1の期間（図7の時刻t21～t22）においてオン状態に設定される。

## 【0080】

p型MOSトランジスタQp2は、ゲートに入力される制御信号S2に応じて、p型MOSトランジスタQp1のドレインとノードNAとを接続または遮断するスイッチとして動作する。p型MOSトランジスタQp2は、第2の期間（図7の時刻t22～t23）において、p型MOSトランジスタQp1のドレインとノードNAとを接続する。

10

## 【0081】

p型MOSトランジスタQp3は、ゲートに入力される制御信号S3に応じて、ノードNBに電圧‘VDD’を供給する。p型MOSトランジスタQp3は、ノードNBと電源ラインVDDとの間に接続されており、第1の期間（図7の時刻t21～t22）においてオン状態に設定される。

## 【0082】

n型MOSトランジスタQn2は、ゲートに入力される制御信号S4に応じて、n型MOSトランジスタQn1のドレインとノードNBとを接続または遮断するスイッチとして動作する。n型MOSトランジスタQn2は、第2の期間（図7の時刻t22～t23）において、n型MOSトランジスタQn1のドレインとノードNBとを接続する。

20

## 【0083】

p型MOSトランジスタQp5は、ゲートに入力される制御信号S5に応じて、p型MOSトランジスタQp1のドレインとレベルシフト信号Oの出力端子とを接続または遮断するスイッチとして動作する。p型MOSトランジスタQp5は、第1の期間および第2の期間（図7のt21～t23）において、オフ状態に設定される。

## 【0084】

n型MOSトランジスタQn5は、ゲートに入力される制御信号S6に応じて、n型MOSトランジスタQn1のドレインとレベルシフト信号Oの出力端子とを接続または遮断するスイッチとして動作する。n型MOSトランジスタQn5は、第1の期間および第2の期間（図7のt21～t23）において、オフ状態に設定される。

30

## 【0085】

制御回路10Bは、ノードNAおよびNBに適切な電圧が設定されるように、上述した制御信号S1～S6を生成する。

すなわち、第1の期間（t21～t22）において、制御信号S1を電圧‘VDD’、制御信号S3を電圧‘VSS’に設定し、他の期間において、制御信号S1を電圧‘VSS’、制御信号S3を電圧‘VDD’に設定する。制御信号S1およびS3は逆相の信号となる。

また、第1の期間に続く第2の期間（t22～t23）において、制御信号S2を電圧‘VSS’、制御信号S4を電圧‘VDD’に設定し、他の期間において、制御信号S2を電圧‘VDD’、制御信号S4を電圧‘VSS’に設定する。制御信号S2およびS4は逆相の信号となる。

40

更に、第1の期間および第2の期間（t21～t23）において、制御信号S5を電圧‘VDD’、制御信号S6を電圧‘VSS’に設定し、他の期間において、制御信号S5を電圧‘VSS’、制御信号S6を電圧‘VDD’に設定する。制御信号S5およびS6は逆相の信号となる。

## 【0086】

次に、上述した構成を有する図6に示すレベルシフト回路の動作について、図7を参照して説明する。

## 【0087】

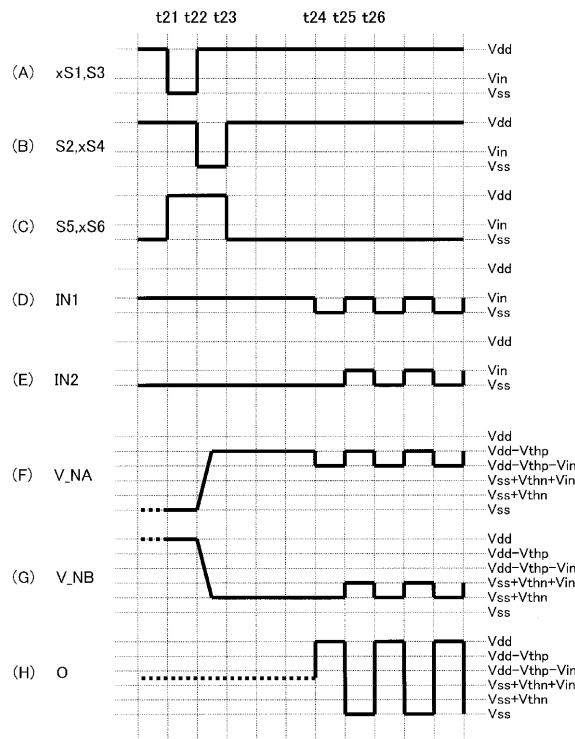

図7は、図6に示すレベルシフト回路における各部の信号波形の一例を示す図である。

50

図7(A)は、制御信号S3の電圧波形を示す。

図7(B)は、制御信号S2の電圧波形を示す。

図7(C)は、制御信号S5の電圧波形を示す。

図7(D)～(H)の信号波形は、図3(E)～(I)の信号波形に対応する。

#### 【0088】

なお、制御信号S1の電圧波形は、図7(A)に示す制御信号S3に対して逆相になる。

制御信号S4の電圧波形は、図7(B)に示す制御信号S2に対して逆相になる。

制御信号S6の電圧波形は、図7(C)に示す制御信号S5に対して逆相になる。

#### 【0089】

ノードNAおよびNBの電圧設定を行う前の初期の状態において、制御回路10Bは制御信号S1およびS4を電圧‘VSS’、制御信号S2およびS3を電圧‘VDD’に設定し、トランジスタQp2, Qp3, Qn2, Qn3をオフさせる。

また、この初期の状態において、第1の入力信号IN1はハイレベルの電圧‘Vin’に設定され、第2の入力信号IN2はローレベルの電圧‘VSS’に設定される。

#### 【0090】

第1の期間(t21～t22)において、制御回路10Bは制御信号S1を電圧‘VDD’に設定し、制御信号S3を電圧‘VSS’に設定する。これにより、n型MOSトランジスタQn3およびp型MOSトランジスタQp3が共にオンし、ノードNAが電圧‘VSS’、ノードNBが電圧‘VDD’に設定される。これにより、p型MOSトランジスタQp1およびn型MOSトランジスタQn1が共にオンする。

一方、このとき制御回路10Bは制御信号S5を電圧‘VDD’、制御信号S6を電圧‘VSS’に設定するため、p型MOSトランジスタQp5およびn型MOSトランジスタQn5が共にオフする。そのため、p型MOSトランジスタQp1およびn型MOSトランジスタQn1が同時にオンしても、貫通電流は流れない。

#### 【0091】

ノードNAが電圧‘VSS’、ノードNBが電圧‘VDD’に設定された後の第2の期間(t22～t23)において、制御回路10Bは制御信号S1を電圧‘VSS’、制御信号S3を電圧‘VDD’に戻し、代わりに制御信号S2を電圧‘VSS’、制御信号S4を電圧‘VDD’に設定する。これにより、p型MOSトランジスタQp2がオンし、p型MOSトランジスタQp1のドレインとノードNAとが接続されるとともに、n型MOSトランジスタQn2がオンし、n型MOSトランジスタQn1のドレインとノードNBとが接続される。

このとき、p型MOSトランジスタQp1はオン状態にあるため、ノードNAの電圧V\_NAは電圧‘VDD’に向かって上昇し、この電圧V\_NAが‘VDD - Vthp’に達したところで、p型MOSトランジスタQp1が自らオフする。また、n型MOSトランジスタQn1はオン状態にあるため、ノードNBの電圧V\_NBは電圧‘VSS’に向かって低下し、この電圧V\_NBが‘VSS + Vthn’に達したところで、n型MOSトランジスタQn1が自らオフする。

その結果、ノードNAの電圧V\_NAは‘VDD - Vthp’に設定され、ノードNBの電圧V\_NBは‘VSS + Vthn’に設定される。

#### 【0092】

なお、この第2の期間(t22～t23)において、制御回路10Bは制御信号S5を電圧‘VDD’、制御信号S6を電圧‘VSS’に引き続き設定するため、p型MOSトランジスタQp1およびn型MOSトランジスタQn1が同時にオンする状態になっても、貫通電流は流れない。

#### 【0093】

ノードNAの電圧V\_NAが‘VDD - Vthp’、ノードNBの電圧V\_NBが‘VSS + Vthn’に設定された後の動作については、図2に示すレベルシフト回路と同様である。

10

30

40

50

## 【0094】

以上説明したように、本実施形態に係るレベルシフト回路においても、図2に示すレベルシフト回路と同様な動作が実現されるため、これと同様な効果を奏することができる。

すなわち、ノードNAの電圧が‘VDD-Vthp’、ノードNBの電圧が‘VSS+Vthn’に設定されるため、トランジスタ(Qp1, Qn1)のしきい電圧のばらつきに影響されることなく、安定したレベルシフト動作を行うことができる。

また、ノードNAおよびNBの電圧が、p型MOSトランジスタQp1およびn型MOSトランジスタQn1のオン／オフの切り換わり点の電圧にそれぞれ設定されるため、トランジスタのしきい電圧より小さい振幅の信号であってもレベルシフト動作が可能である。

10

## 【0095】

また、本実施形態に係るレベルシフト回路によれば、p型MOSトランジスタQp1およびn型MOSトランジスタQn1が同時にオンする期間において、p型MOSトランジスタQp5およびn型MOSトランジスタQn5をオフさせることにより、貫通電流の発生を確実に防止することができる。

## 【0096】

更に、本実施形態に係るレベルシフト回路によれば、ノードNAおよびNBの電圧設定を並行に行うことができるため、この電圧設定に伴ってレベルシフト信号Oの出力が無効になる期間を短縮することができる。

## 【0097】

20

## &lt;第5の実施形態&gt;

次に、本発明の第5の実施形態について説明する。

## 【0098】

図8は、本発明の第5の実施形態に係るレベルシフト回路の構成の一例を示す図であり、図6と図8の同一符号は同一の構成要素を示す。

図8に示すレベルシフト回路は、図6に示すレベルシフト回路における制御回路10Bを制御回路10Cに置き換え、更に、キャパシタCAおよびCBに対して共通の入力信号INを印加したものであり、他の構成については図6に示すレベルシフト回路と同じである。

## 【0099】

30

制御回路10Cは、次のようなタイミングの制御信号S1～S6を生成する。

すなわち、第1の期間(図9の時刻t31～t32)において、制御信号S1を電圧‘VDD’に設定し、他の期間において、制御信号S1を電圧‘VSS’に設定する。

第1の期間に続く第2の期間(図9の時刻t32～t33)において、制御信号S2を電圧‘VSS’に設定し、他の期間において、制御信号S2を電圧‘VDD’に設定する。

第2の期間に続く第3の期間(図9の時刻t33～t34)において、制御信号S3を電圧‘VSS’に設定し、他の期間において、制御信号S3を電圧‘VDD’に設定する。

第3の期間に続く第4の期間(図9の時刻t34～t35)において、制御信号S4を電圧‘VDD’に設定し、他の期間において、制御信号S4を電圧‘VSS’に設定する。

40

## 【0100】

上述した構成を有する図8に示すレベルシフト回路の動作について、図9を参照して説明する。

## 【0101】

50

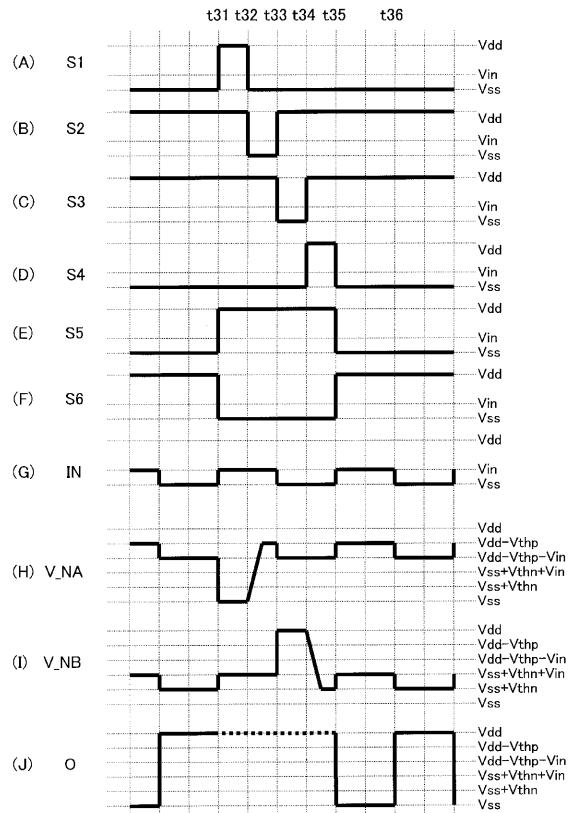

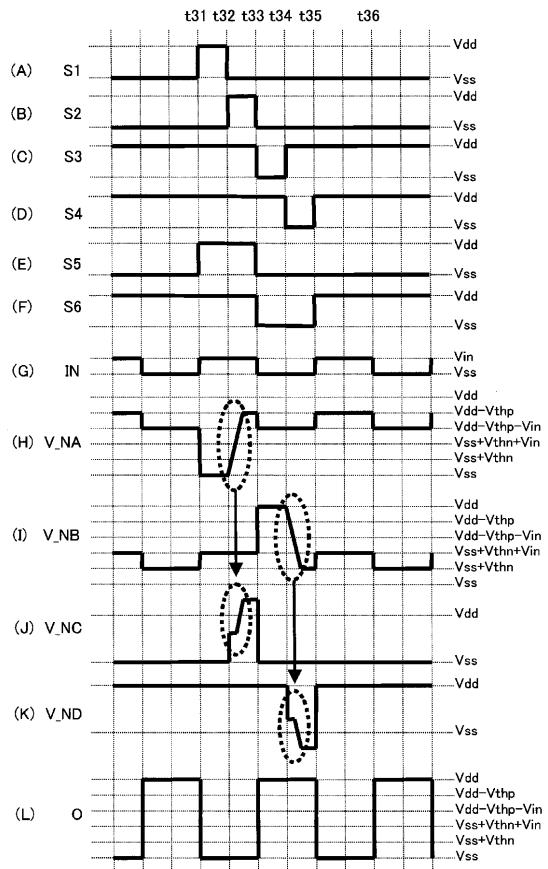

図9は、図8に示すレベルシフト回路における各部の信号波形の一例を示す図である。

図9(A)～(D),(H)～(J)の信号波形は、図3(A)～(D),(G)～(I)の信号波形に対応する。

図9(E)は、制御信号S5の電圧波形を示す。

図9(F)は、制御信号S6の電圧波形を示す。

図9(G)は、入力信号INの電圧波形を示す。

#### 【0102】

ノードNAおよびNBの電圧設定を行う前の初期の状態において、制御回路10Cは制御信号S1およびS4を電圧‘VSS’、制御信号S2およびS3を電圧‘VDD’に設定する。この場合、トランジスタQp2,Qp3,Qn2,Qn3はオフに設定される。 10

一方、この初期の状態において、入力信号INは、ハイレベル(Vin)とローレベル(VSS)との間で任意に変化する状態にある。

#### 【0103】

入力信号INがハイレベル(Vin)になる第1の期間(t31～t32)において、制御回路10Cは制御信号S1を電圧‘VDD’に設定する。これにより、n型MOSトランジスタQn3がオンし、ノードNAが電圧‘VSS’に設定され、p型MOSトランジスタQp1がオンする。

#### 【0104】

ノードNAが電圧‘VSS’に設定された後の第2の期間(t32～t33)において、制御回路10Cは制御信号S1を電圧‘VSS’に戻し、制御信号S2を電圧‘VSS’に立ち下げる。これにより、p型MOSトランジスタQp2がオンし、p型MOSトランジスタQp1のドレインとノードNAとが接続される。 20

このとき、p型MOSトランジスタQp1はオン状態にあるため、ノードNAの電圧V\_NAは電圧‘VDD’に向かって上昇する。電圧V\_NAが‘VDD-Vthp’に達したところで、p型MOSトランジスタQp1が自らオフし、ノードNAの電圧V\_NAは‘VDD-Vthp’に設定される。

#### 【0105】

p型MOSトランジスタQp1がオフした後、入力信号INがローレベル(VSS)になる第3の期間(t33～t34)において、制御回路10Cは制御信号S2を電圧‘VDD’に戻し、制御信号S3を電圧‘VSS’に立ち下げる。これにより、p型MOSトランジスタQp3がオンし、ノードNBが電圧‘VDD’に設定され、n型MOSトランジスタQn1がオンする。 30

#### 【0106】

ノードNBが電圧‘VDD’に設定された後の第4の期間(t4～t5)において、制御回路10Cは制御信号S3を電圧‘VDD’に戻し、制御信号S4を電圧‘VDD’に立ち上げる。これにより、n型MOSトランジスタQn2がオンし、ノードNBとn型MOSトランジスタQn1のドレインとが接続される。

このとき、n型MOSトランジスタQn1はオン状態にあるため、ノードNBの電圧V\_NBは電圧‘VSS’に向かって低下する。電圧V\_NBが‘VSS+Vthn’に達したところで、n型MOSトランジスタQn1が自らオフし、ノードNBの電圧V\_NBは‘VSS+Vthn’に設定される。 40

#### 【0107】

上述した第1の期間～第4の期間(t31～t35)を通じて、制御回路10Bは制御信号S5を電圧‘VDD’、制御信号S6を電圧‘VSS’に設定する。これにより、p型MOSトランジスタQp5およびn型MOSトランジスタQn5がオフするため、この期間においてp型MOSトランジスタQp1およびn型MOSトランジスタQn1が同時にオンする状態になっても、貫通電流は流れない。

#### 【0108】

ノードNAの電圧V\_NAが‘VDD-Vthp’、ノードNBの電圧V\_NBが‘VSS+Vthn’に設定された後の動作については、図2に示すレベルシフト回路と同様

である。

【0109】

以上説明したように、本実施形態に係るレベルシフト回路においても、図2に示すレベルシフト回路と同様な動作が実現されるため、これと同様な効果を奏することができる。

すなわち、ノードNAの電圧が‘VDD-Vthp’、ノードNBの電圧が‘VSS+Vthn’に設定されるため、トランジスタ(Qp1, Qn1)のしきい電圧のばらつきに影響されることなく、安定したレベルシフト動作を行うことができる。

また、ノードNAおよびNBの電圧が、p型MOSトランジスタQp1およびn型MOSトランジスタQn1のオン／オフの切り換わり点の電圧にそれぞれ設定されるため、トランジスタのしきい電圧より小さい振幅の信号であってもレベルシフト動作が可能である。

10

【0110】

また、本実施形態に係るレベルシフト回路によれば、ノードNAおよびNBの電圧を設定する期間(t31～t35)においてp型MOSトランジスタQp5およびn型MOSトランジスタQn5をオフさせることにより、貫通電流の発生を確実に防止することができる。

【0111】

更に、本実施形態に係るレベルシフト回路によれば、入力信号INがハイレベル(Vin)のときにノードNAの電圧設定(第1の期間および第2の期間)を行い、入力信号INがローレベル(VSS)のときにノードNBの電圧設定(第3の期間および第4の期間)を行う。これにより、第2～第4の実施形態に係るレベルシフト回路のように、2つの入力信号(IN1, IN2)を同時に別の電圧に設定する必要がないため、回路構成を簡易化することができる。

20

【0112】

<第6の実施形態>

次に、本発明の第6の実施形態について説明する。

【0113】

第6の実施形態に係るレベルシフト回路は、例えば図8に示すレベルシフト回路と同様の構成を有しており、両者の違いは、p型MOSトランジスタQp5およびn型MOSトランジスタQn6の制御方法にある。

30

【0114】

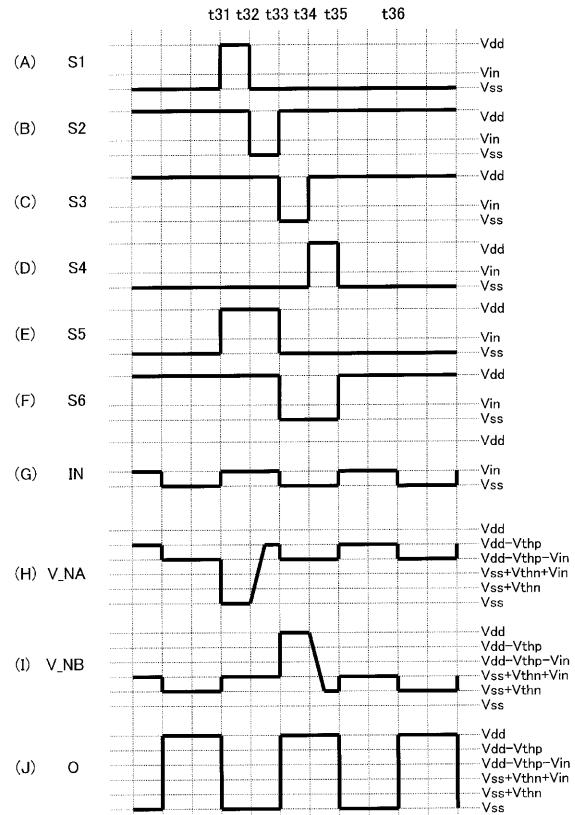

図10は、第6の実施形態に係るレベルシフト回路における各部の信号波形の一例を示す図である。

図10(A)～(J)の信号波形は、図9(A)～(J)の信号波形に対応する。

【0115】

本実施形態に係るレベルシフト回路では、図10(E)に示すように、入力信号INがハイレベル(Vin)になる第1の期間および第2の期間(t31～t33)において、制御信号S5およびS6が電圧‘VDD’に設定される。これにより、p型MOSトランジスタQp5がオフ、n型MOSトランジスタQn5がオンするため、レベルシフト信号Oの出力端子はn型MOSトランジスタQn1を介して電源ラインVSSに接続される。

40

【0116】

ここで、図10(I)に示すように、この第1の期間および第2の期間(t31～t33)においてノードNBの電圧V\_NBが‘VSS+Vthn+Vin’程度まで上昇しているものとすると、この期間においてn型MOSトランジスタQn1はオンするため、レベルシフト信号Oは電圧‘VSS’になる。

【0117】

また、本実施形態に係るレベルシフト回路では、図10(F)に示すように、入力信号INがローレベル(VSS)になる第3の期間および第4の期間(t33～t35)において、制御信号S5およびS6が電圧‘VSS’に設定される。これにより、p型MOSトランジスタQp5がオン、n型MOSトランジスタQn5がオフするため、レベルシフ

50

ト信号Oの出力端子はp型MOSトランジスタQp1を介して電源ラインVDDに接続される。

【0118】

ここで、図10(H)に示すように、この第3の期間および第4の期間(t33～t35)においてノードNAの電圧V\_NBが‘VDD-Vthp-Vin’程度まで低下しているものとすると、この期間においてp型MOSトランジスタQp1はオンするため、レベルシフト信号Oは電圧‘VDD’になる。

【0119】

このように、本実施形態に係るレベルシフト回路では、入力信号INがハイレベル(Vin)になる期間においてノードNAの電圧設定を行い、かつ、そのときにp型MOSトランジスタQp5をオフ、n型MOSトランジスタQn5をオンさせることにより、ノードNAの電圧設定を行いながら、これと並行して、入力信号INに応じた電圧‘VSS’のレベルシフト信号Oを出力することができる。同様に、入力信号INがローレベル(VSS)になる期間においてノードNBの電圧設定を行い、かつ、そのときにp型MOSトランジスタQp5をオン、n型MOSトランジスタQn5をオフさせることにより、ノードNBの電圧設定を行いながら、これと並行して、入力信号INに応じた電圧‘VDD’のレベルシフト信号Oを出力することができる。

つまり、本実施形態に係るレベルシフト回路によれば、ノードNAおよびNBの電圧設定と並行して、レベルシフト信号Oを出力することができる。

【0120】

<第7の実施形態>

次に、本発明の第7の実施形態について説明する。

【0121】

第7の実施形態に係るレベルシフト回路は、p型MOSトランジスタQp2およびn型MOSトランジスタQn2の制御方法に関して、上述した実施形態(第2～第6の実施形態)に係るレベルシフト回路と異なっている。

すなわち、第7の実施形態に係るレベルシフト回路は、ノードNAに電圧‘VSS’を供給する期間(第1の期間)において、p型MOSトランジスタQp2がオンする。また、ノードNBに電圧‘VDD’を供給する期間(第3の期間)において、n型MOSトランジスタQn2がオンする。

これにより、第1の期間においてp型MOSトランジスタQp1のドレイン電圧を‘VSS’に初期化するとともに、第3の期間においてn型MOSトランジスタQn1のドレイン電圧を‘VDD’に初期化する。

【0122】

ここでは一例として、本実施形態に係るレベルシフト回路の構成が図8に示すレベルシフト回路と同じであるものとする。また、各トランジスタの制御方法が、p型MOSトランジスタQp2およびn型MOSトランジスタQn2を除いて、第6の実施形態に係るレベルシフト回路と同じであるものとする。

【0123】

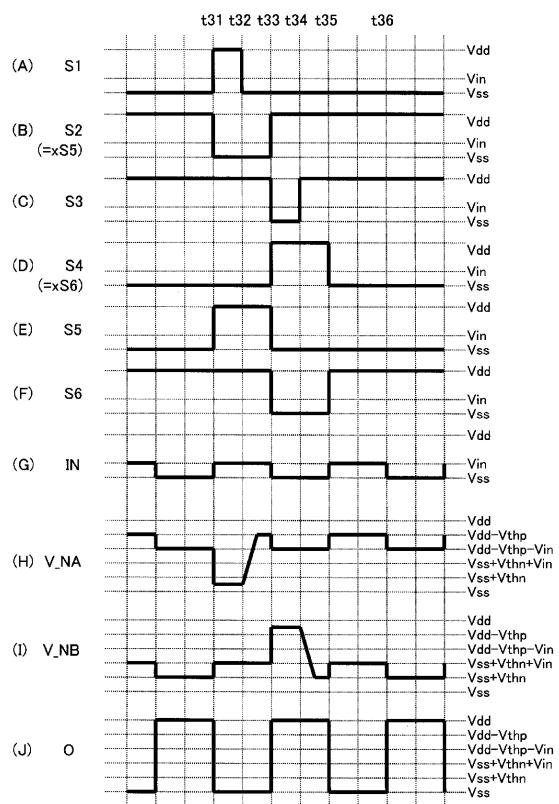

図11は、第7の実施形態に係るレベルシフト回路における各部の信号波形の一例を示す図である。

図11(A)～(J)の信号波形は、図9(A)～(J)の信号波形に対応する。

【0124】

本実施形態に係るレベルシフト回路では、図11(B)に示すように、p型MOSトランジスタQp1がオンする第1の期間(t31～t32)において、制御信号S2がローレベル(VSS)に設定されることにより、p型MOSトランジスタQp2がオンする。p型MOSトランジスタQp2がオンすると、p型MOSトランジスタQp1のドレイン電圧は‘VSS’に初期化される。

第1の期間(t31～t32)においてp型MOSトランジスタQp5がオフしているため、このときp型MOSトランジスタQp2がオフすると、p型MOSトランジスタQ

10

20

30

40

50

p<sub>1</sub>のドレインはフロー・ティング状態になる。これに対し、本実施形態に係るレベルシフト回路では、第1の期間においてp型MOSトランジスタQ<sub>p2</sub>がオンするため、p型MOSトランジスタQ<sub>p1</sub>のドレイン電圧安定化することができる。

【0125】

第1の期間(t<sub>31</sub> ~ t<sub>32</sub>)においてノードNAが‘VSS’に設定されると、次に第2の期間(t<sub>32</sub> ~ t<sub>33</sub>)においてp型MOSトランジスタQ<sub>p1</sub>がオフする。このときp型MOSトランジスタQ<sub>p2</sub>はオンのままであるため、ノードNAの電圧は‘VSS’から‘VSS - Vthp’まで上昇する。

【0126】

次に、n型MOSトランジスタQ<sub>n1</sub>がオンする第3の期間(t<sub>33</sub> ~ t<sub>34</sub>)において、制御信号S<sub>4</sub>がハイレベル(VDD)に設定されることにより、n型MOSトランジスタQ<sub>n2</sub>がオンする。n型MOSトランジスタQ<sub>n2</sub>がオンすると、n型MOSトランジスタQ<sub>n1</sub>のドレイン電圧は‘VDD’に初期化される。

第3の期間(t<sub>33</sub> ~ t<sub>34</sub>)においてn型MOSトランジスタQ<sub>n5</sub>がオフしているため、このときn型MOSトランジスタQ<sub>n2</sub>がオフすると、n型MOSトランジスタQ<sub>n1</sub>のドレインはフロー・ティング状態になる。これに対し、本実施形態に係るレベルシフト回路では、第3の期間においてn型MOSトランジスタQ<sub>n2</sub>がオンするため、n型MOSトランジスタQ<sub>n1</sub>のドレイン電圧を安定化することができる。

【0127】

第3の期間(t<sub>33</sub> ~ t<sub>34</sub>)においてノードNBが‘VDD’に設定されると、次に第4の期間(t<sub>34</sub> ~ t<sub>35</sub>)においてn型MOSトランジスタQ<sub>n1</sub>がオフする。このときn型MOSトランジスタQ<sub>n2</sub>はオンのままであるため、ノードNBの電圧は‘VDD’から‘VDD - Vthn’まで低下する。

【0128】

このように、本実施形態に係るレベルシフト回路では、ノードNAの電圧設定を行う第1の期間および第2の期間においてp型MOSトランジスタQ<sub>p2</sub>がオンすることにより、p型MOSトランジスタQ<sub>p1</sub>のドレイン電圧を‘VSS’に安定化することができる。同様に、ノードNBの電圧設定を行う第3の期間および第4の期間においてn型MOSトランジスタQ<sub>n2</sub>がオンすることにより、n型MOSトランジスタQ<sub>n1</sub>のドレイン電圧を‘VDD’に安定化することができる。

【0129】

また、本実施形態に係るレベルシフト回路によれば、p型MOSトランジスタQ<sub>p5</sub>の制御信号S<sub>5</sub>(図11(E))を論理反転することによってp型MOSトランジスタQ<sub>p2</sub>の制御信号S<sub>2</sub>(図11(B))を生成できるとともに、n型MOSトランジスタQ<sub>n5</sub>の制御信号S<sub>6</sub>(図11(F))を論理反転することによってn型MOSトランジスタQ<sub>n2</sub>の制御信号S<sub>4</sub>(図11(D))を生成できる。そのため、制御回路の構成を簡易化することができる。

もし、p型MOSトランジスタQ<sub>p2</sub>をn型MOSトランジスタに置換し、n型MOSトランジスタQ<sub>n2</sub>をp型MOSトランジスタに置換すれば、制御信号S<sub>2</sub>とS<sub>5</sub>を共通化し、制御信号S<sub>4</sub>とS<sub>6</sub>を共通化できるため、制御回路を更に簡易化することができる。

【0130】

<第8の実施形態>

次に、本発明の第8の実施形態について説明する。

【0131】

本実施形態に係るレベルシフト回路は、上述した実施形態(第2 ~ 第6の実施形態)に係るレベルシフト回路において、p型MOSトランジスタQ<sub>p2</sub>をn型MOSトランジスタに置換し、n型MOSトランジスタQ<sub>n2</sub>をp型MOSトランジスタに置換し、かつ、これらのトランジスタをブートスラップ方式によって駆動する回路を設けたものである。

【0132】

10

20

30

40

50

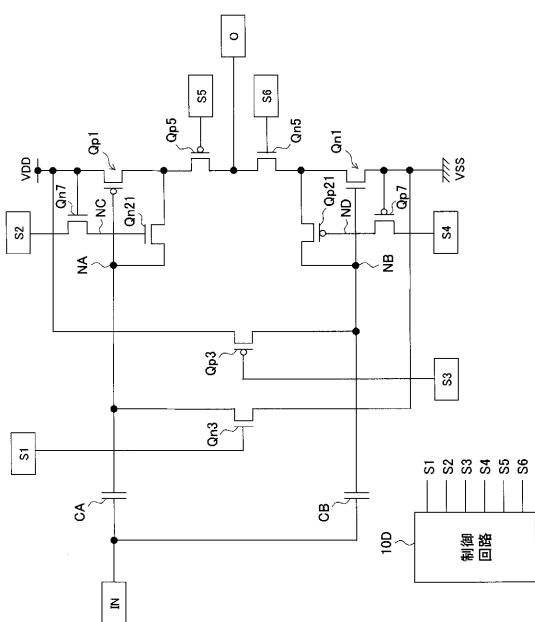

図12は、本実施形態に係るレベルシフト回路の構成の一例を示す図である。

本実施形態に係るレベルシフト回路は、図12に示すように、図8に示すレベルシフト回路におけるp型MOSトランジスタQp2をn型MOSトランジスタQn21に置換し、n型MOSトランジスタQn2をp型MOSトランジスタQp21に置換し、更にブートストラップ方式の駆動回路としてn型MOSトランジスタQn7およびp型MOSトランジスタQp7を設けたものである。

n型MOSトランジスタQn21は、本発明の第1スイッチ素子の一実施形態である。

n型MOSトランジスタQn7は、本発明の第2スイッチ素子の一実施形態である。

p型MOSトランジスタQp21は、本発明の第3スイッチ素子の一実施形態である。

p型MOSトランジスタQp7は、本発明の第4スイッチ素子の一実施形態である。

10

### 【0133】

n型MOSトランジスタQn7は、そのゲートが電源ラインVDDに接続され、そのソースがn型MOSトランジスタQn21のゲートに接続され、そのドレインに制御信号S2が入力される。

p型MOSトランジスタQp7は、そのゲートが電源ラインVDDに接続され、そのソースがp型MOSトランジスタQp21のゲートに接続され、そのドレインに制御信号S4が入力される。

### 【0134】

図12に示すレベルシフト回路における制御信号(S1～S6)のタイミング関係は、第6の実施形態に係るレベルシフト回路と同じである。ただし、両者の制御信号S1、S2の論理値は反転している(図10(B)と図13(B)並びに図10(D)と図13(D)を参照)。

20

### 【0135】

図13は、第8の実施形態に係るレベルシフト回路における各部の信号波形の一例を示す図である。

図13(A)～(I)，(L)の信号波形は、図10(A)～(I)，(J)の信号波形にそれぞれ対応する。

図13(J)の信号波形は、n型MOSトランジスタQn21のゲートとn型MOSトランジスタQn7のソースとが接続されるノードNCの電圧‘V\_NC’を示す。

図13(K)の信号波形は、p型MOSトランジスタQp21のゲートとp型MOSトランジスタQp7のソースとが接続されるノードNDの電圧‘V\_ND’を示す。

30

### 【0136】

なお、以下の説明において‘Vthn(Qn7)’、‘Vthn(Qn21)’はそれぞれn型MOSトランジスタQn7、Qn21のしきい電圧を示す。

‘Vthp(Qp7)’、‘Vthp(Qp21)’はそれぞれp型MOSトランジスタQp7、Qp21のしきい電圧を示す。

‘Vthp(Qp1)’、‘Vthn(Qn1)’はそれぞれp型MOSトランジスタQp1、n型MOSトランジスタQn1のしきい電圧を示す。

### 【0137】

第1の期間(t31～t32)において、制御信号S1がハイレベル(VDD)、制御信号S2がローレベル(VSS)に設定され、n型MOSトランジスタQn3およびQn7がオンする。n型MOSトランジスタQn3がオンすると、ノードNAの電圧V\_NA(図13(H))が電圧‘VSS’に設定されるため、p型MOSトランジスタQp1がオンする。また、n型MOSトランジスタQn7がオンすると、n型MOSトランジスタQn21のゲートにはローレベル(VSS)の制御信号S2が入力されるため、n型MOSトランジスタQn21がオフする。

40

### 【0138】

次に第2の期間(t32～t33)において、制御信号S1がローレベル(VSS)、制御信号S2がハイレベル(VDD)に設定され、n型MOSトランジスタQn3がオフする。

50

制御信号 S 2 がハイレベル ( V D D ) に設定されると、ノード N C には n 型 M O S トランジスタ Q n 7 を介して電圧 ‘ V D D ’ が供給されるため、ノード N C の電圧 V \_ N C は ‘ V D D - V t h n ( Q n 7 ) ’ に設定される。これにより、n 型 M O S トランジスタ Q n 2 1 がオンする。

n 型 M O S トランジスタ Q n 2 1 がオンすると、ノード N A には p 型 M O S トランジスタ Q p 1 および n 型 M O S トランジスタ Q n 2 1 を介して電圧 ‘ V D D ’ が供給されるため、ノード N A の電圧 V \_ N A が時間と共に上昇する ( 図 13 ( H ) ) 。

#### 【 0139 】

ノード N A の電圧 V \_ N A が ‘ V D D - V t h n ( Q n 7 ) - V t h n ( Q n 2 1 ) ’ に達すると、ノード N C の電圧 V \_ N C が ‘ V D D - V t h n ( Q n 7 ) ’ に達し、n 型 M O S トランジスタ Q n 7 がオンからオフへ切り替わる。ノード N A の電圧が更に上昇すると、n 型 M O S トランジスタ Q n 2 1 のゲートとドレインとの間の寄生的な容量素子に蓄積される電荷によって、ノード N C の電圧 V \_ N C が正側に押し上げられるため、電圧 V \_ N C は電圧 V \_ N A と共に上昇する ( 図 13 ( J ) ) 。

ノード N A の電圧 V \_ N A が ‘ V D D - V t h p ( Q p 1 ) ’ に達すると、p 型 M O S トランジスタ Q p 1 がオンからオフへ切り替わり、ノード N A の電圧上昇が停止する。これにより、ノード N A の電圧は ‘ V D D - V t h p ( Q p 1 ) ’ に設定される。

#### 【 0140 】

次に第 3 の期間 ( t 3 3 ~ t 3 4 ) において、制御信号 S 3 がローレベル ( V S S ) 、制御信号 S 4 がハイレベル ( V D D ) に設定され、p 型 M O S トランジスタ Q p 3 および Q p 7 がオンする。p 型 M O S トランジスタ Q p 3 がオンすると、ノード N B の電圧 V \_ N B ( 図 13 ( I ) ) が電圧 ‘ V D D ’ に設定されるため、n 型 M O S トランジスタ Q n 1 がオンする。また、p 型 M O S トランジスタ Q p 7 がオンすると、p 型 M O S トランジスタ Q p 2 1 のゲートにはハイレベル ( V D D ) の制御信号 S 4 が入力されるため、p 型 M O S トランジスタ Q p 2 1 がオフする。

#### 【 0141 】

次に第 4 の期間 ( t 3 4 ~ t 3 5 ) において、制御信号 S 3 がハイレベル ( V D D ) 、制御信号 S 4 がローレベル ( V S S ) に設定され、p 型 M O S トランジスタ Q p 3 がオフする。

制御信号 S 4 がローレベル ( V S S ) に設定されると、ノード N D には p 型 M O S トランジスタ Q p 7 を介して電圧 ‘ V S S ’ が供給されるため、ノード N D の電圧 V \_ N D は ‘ V D D + V t h p ( Q p 7 ) ’ に設定される。これにより、p 型 M O S トランジスタ Q p 2 1 がオンする。

p 型 M O S トランジスタ Q p 2 1 がオンすると、ノード N B には n 型 M O S トランジスタ Q n 1 および p 型 M O S トランジスタ Q p 2 1 を介して電圧 ‘ V S S ’ が供給されるため、ノード N B の電圧 V \_ N B が時間と共に低下する ( 図 13 ( I ) ) 。

#### 【 0142 】

ノード N B の電圧 V \_ N B が ‘ V S S + V t h p ( Q p 7 ) + V t h p ( Q p 2 1 ) ’ に達すると、ノード N D の電圧 V \_ N D が ‘ V D D - V t h p ( Q p 7 ) ’ に達し、p 型 M O S トランジスタ Q p 7 がオンからオフへ切り替わる。ノード N B の電圧がここから更に低下すると、p 型 M O S トランジスタ Q p 2 1 のゲートとドレインとの間の寄生的な容量素子に蓄積される電荷によって、ノード N D の電圧 V \_ N C が押し下げられるため、電圧 V \_ N D は電圧 V \_ N B と共に低下する ( 図 13 ( J ) ) 。

ノード N B の電圧 V \_ N B が ‘ V S S + V t h n ( Q n 1 ) ’ に達すると、n 型 M O S トランジスタ Q n 1 がオンからオフへ切り替わり、ノード N B の電圧低下が停止する。これにより、ノード N B の電圧は ‘ V D D + V t h n ( Q n 1 ) ’ に設定される。

#### 【 0143 】

以上説明したように、本実施形態に係るレベルシフト回路によれば、p 型 M O S トランジスタ Q p 1 のドレインとゲートを接続するためのスイッチに n 型 M O S トランジスタ Q n 2 1 , Q n 7 によるブートストラップ方式のスイッチを用いるため、p 型 M O S トラン

10

20

40

50

ジスタQ pのしきい値V t h p (Q p 1)が比較的小さい場合でも、ノードN Aの電圧を確実に‘V D D - V t h p (Q p 1)’まで上昇させることができる。

また、n型MOSトランジスタQ n 1のドレインとゲートを接続するためのスイッチにp型MOSトランジスタQ p 2 1, Q p 7によるブートストラップ方式のスイッチを用いるため、n型MOSトランジスタQ nのしきい値V t h n (Q n 1)が比較的小さい場合でも、ノードN Bの電圧を確実に‘V S S + V t h n (Q n 1)’まで低下させることができる。

#### 【0144】

なお、上述の実施形態では、n型MOSトランジスタQ n 2 1およびp型MOSトランジスタQ p 2 1のゲートとドレイン（若しくはソース）との間の寄生容量素子を利用してブートストラップ動作を実現しているが、もし寄生容量素子だけでは不十分な場合は、これらのゲートとドレイン（若しくはソース）との間にキャパシタを接続することによって、ブートストラップ動作に必要な静電容量値を補っても良い。

#### 【0145】

<第9の実施形態>

次に、本発明の第9の実施形態について説明する。

#### 【0146】

本実施形態に係るレベルシフト回路は、上述した実施形態（第2～第6の実施形態）に係るレベルシフト回路において、キャパシタC A, C Bに共通の信号を入力するための回路を設けたものである。

#### 【0147】

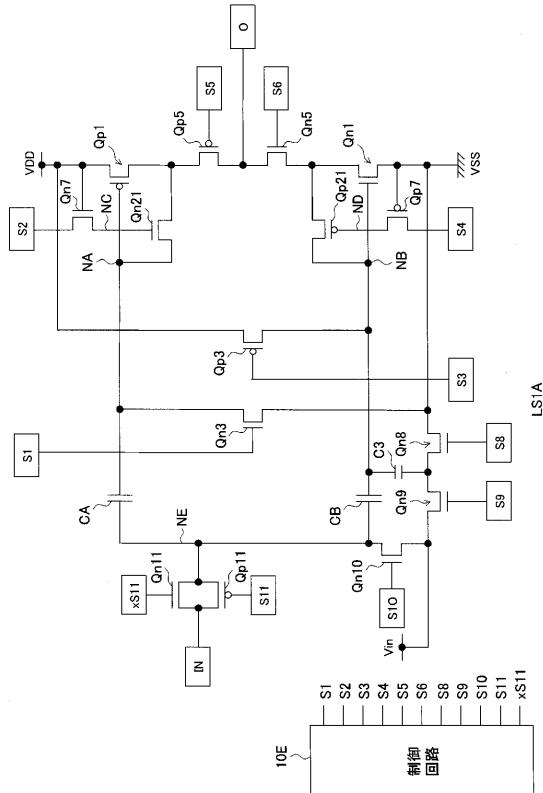

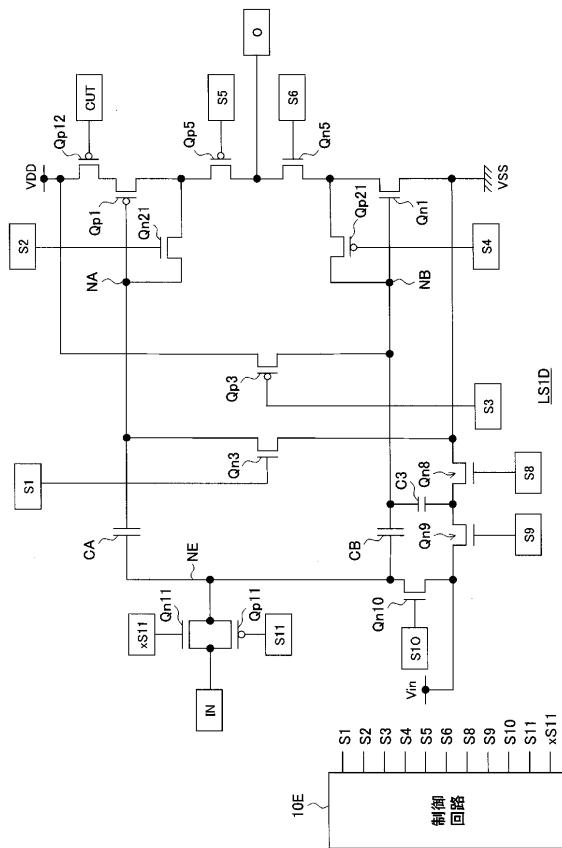

図14は、本実施形態に係るレベルシフト回路の第1の構成例を示す図である。

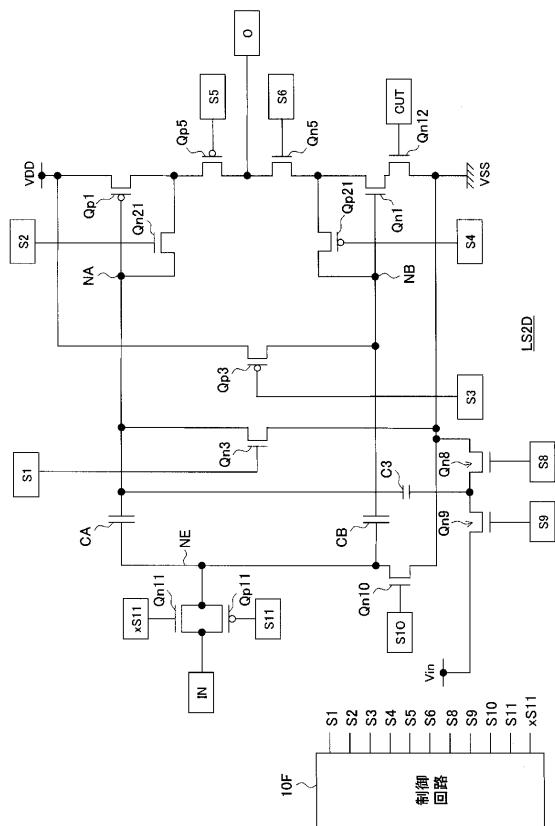

図14に示すレベルシフト回路L S 1 Aは、図12に示すレベルシフト回路の制御回路10 Cを制御回路10 Eに置換し、更にn型MOSトランジスタQ n 8～Q n 11と、p型MOSトランジスタQ p 1 1と、キャパシタC 3とを設けたものであり、他の構成は図12に示すレベルシフト回路と同じである。

#### 【0148】

p型MOSトランジスタQ p 1 1およびn型MOSトランジスタQ n 1 1によって構成される回路は、本発明の第1の入力回路の一実施形態である。

n型MOSトランジスタQ n 1 0は、本発明の第2の入力回路の一実施形態である。

キャパシタC 3は、本発明の第3のキャパシタの一実施形態である。

n型MOSトランジスタQ n 8およびQ n 9によって構成される回路は、本発明の第3の電圧供給回路の一実施形態である。

#### 【0149】

キャパシタC Aの一方の端子（ノードN Aに接続されていない方の端子）と、キャパシタC Bの一方の端子（ノードN Bに接続されていない方の端子）は、ノードN Eにおいて共通に接続される。

#### 【0150】

n型MOSトランジスタQ n 8は、そのソースが電源ラインV S Sに接続され、そのドレインがn型MOSトランジスタQ n 9のソースに接続され、そのゲートに制御信号S 8が入力される。

n型MOSトランジスタQ n 9は、そのドレインに電圧‘V i n’が入力され、そのゲートに制御信号S 9が入力される。

n型MOSトランジスタQ n 1 0は、そのソースがノードN Eに接続され、そのドレインに電圧‘V i n’が入力され、そのゲートに制御信号S 1 0が入力される。

#### 【0151】

キャパシタC 3は、その一方の端子がノードN Bに接続され、他方の端子がn型MOSトランジスタQ n 8のドレインおよびn型MOSトランジスタQ n 9のソースに接続される。

#### 【0152】

10

20

30

40

50

p型MOSトランジスタQp11およびn型MOSトランジスタQn11は並列に接続されており、トランジスタを構成する。このトランジスタの一方の端子には入力信号INが入力され、他方の端子はノードNEに接続される。p型MOSトランジスタQp11のゲートには制御信号S11が入力され、n型MOSトランジスタQn11のゲートにはその論理反転信号である制御信号XS11が入力される。

#### 【0153】

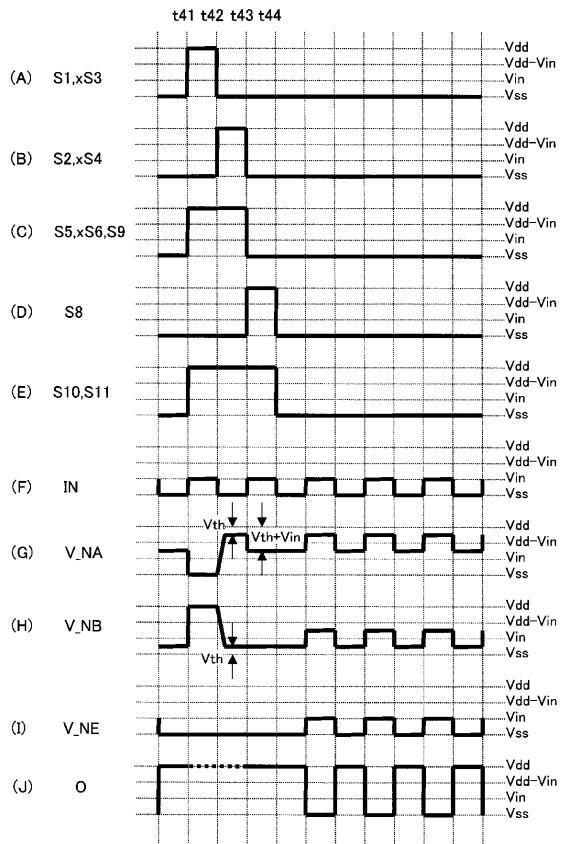

制御回路10Eは、次のようなタイミングの制御信号S1～S11, XS11を生成する。

すなわち、第1の期間（図15の時刻t41～t42）において、制御信号S1を電圧‘VDD’、制御信号S3を電圧‘VSS’に設定し、他の期間において、制御信号S1を電圧‘VSS’、制御信号S3を電圧‘VDD’に設定する。第1の期間では、ノードNAの電圧を‘VDD’に初期化する動作と、ノードNBの電圧を‘VSS’に初期化する動作が実行される。

#### 【0154】

制御回路10Eは、第1の期間に続く第2の期間（図15の時刻t42～t43）において、制御信号S2を電圧‘VDD’、制御信号S4を電圧‘VSS’に設定し、他の期間において、制御信号S2を電圧‘VSS’、制御信号S4を電圧‘VDD’に設定する。第2の期間では、ノードNAの電圧をp型MOSトランジスタQp1のしきい値まで上昇させる動作と、ノードNBの電圧をn型MOSトランジスタQn1のしきい値まで低下させる動作が実行される。

#### 【0155】

第2の期間に続く期間（図15の時刻t43～t44）を、以下では第6の期間と呼ぶ。制御回路10Eは、この第6の期間において、制御信号S9を電圧‘VDD’に設定し、他の期間において、制御信号S9を電圧‘VSS’に設定する。第6の期間では、ノードNBの電圧が‘VSS + Vthn(Qn1) + Vin’に設定され、n型MOSトランジスタQn1がオンする。

#### 【0156】

また制御回路10Eは、第1の期間および第2の期間（t41～t43）において、制御信号S5を電圧‘VDD’、制御信号S6を電圧‘VSS’、制御信号S8を電圧‘VDD’に設定し、その他の期間において、制御信号S5を電圧‘VSS’、制御信号S6を電圧‘VDD’、制御信号S8を電圧‘VSS’に設定する。第1の期間および第2の期間では、p型MOSトランジスタQp5およびn型MOSトランジスタQn5がオフし、出力端子Oがフローティング状態になる。また、キャパシタC3にn型MOSトランジスタQn1のしきい値‘Vthn(Qn1)’が充電される。

#### 【0157】

更に制御回路10Eは、第1、第2および第6の期間（t41～t44）において、制御信号S10を電圧‘VDD’、制御信号S11を電圧‘VDD’、制御信号XS11を電圧‘VSS’に設定し、その他の期間において、制御信号S10を電圧‘VSS’、制御信号S11を電圧‘VSS’、制御信号XS11を電圧‘VDD’に設定する。第1、第2および第6の期間において、トランジスタ（Qp11, Qn11）がオフし、ノードNEには電圧‘Vin’が入力される。

#### 【0158】

上述した構成を有する図14に示すレベルシフト回路LS1Aの動作について、図15を参照して説明する。

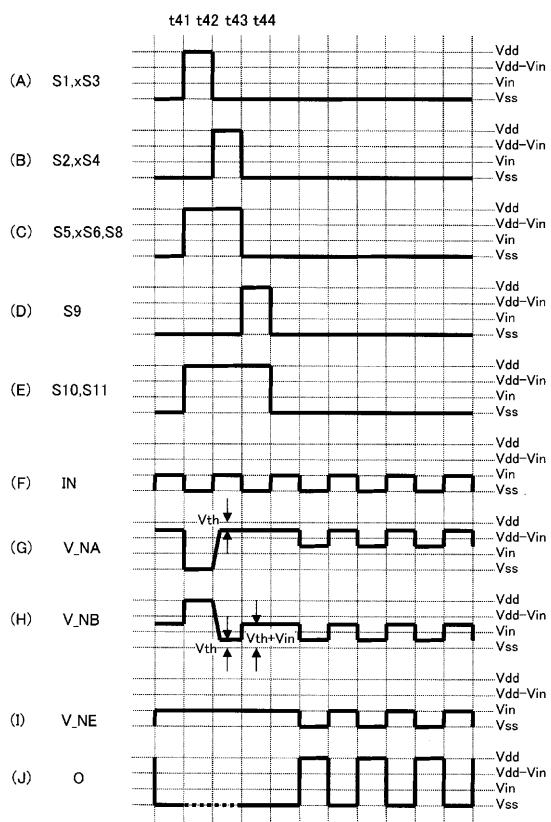

#### 【0159】

図15は、図14に示すレベルシフト回路LS1Aにおける各部の信号波形の一例を示す図である。

図15(A)は、制御信号S1の電圧波形を示す。制御信号S3の電圧波形は、この制御S1の電圧波形を論理反転したものに相当する。

図15(B)は、制御信号S2の電圧波形を示す。制御信号S4の電圧波形は、この制

10

20

30

40

50

御 S 2 の電圧波形を論理反転したものに相当する。

図 15 ( C ) は、制御信号 S 5 および S 8 の電圧波形を示す。制御信号 S 6 の電圧波形は、この制御信号 S 5 , S 8 の電圧波形を論理反転したものに相当する。

図 15 ( D ) は、制御信号 S 9 の電圧波形を示す。

図 15 ( E ) は、制御信号 S 10 および S 11 の電圧波形を示す。

図 15 ( F ) は、入力信号 IN の電圧波形を示す。

図 15 ( G ) は、ノード N A の電圧 V\_N A の波形を示す。

図 15 ( H ) は、ノード N B の電圧 V\_N B の波形を示す。

図 15 ( I ) は、ノード N E の電圧 V\_N E の波形を示す。

図 15 ( J ) は、出力信号 O の電圧波形を示す。

10

#### 【 0 1 6 0 】

第 1 の期間 ( t 4 1 ~ t 4 2 ) において、制御回路 10 E は制御信号 S 1 を電圧 ‘ V D D ’ 、制御信号 S 2 を電圧 ‘ V S S ’ 、制御信号 S 3 を電圧 ‘ V S S ’ 、制御信号 S 4 を電圧 ‘ V D D ’ に設定する。これにより、n 型MOSトランジスタ Q\_n 3 がオン、n 型MOSトランジスタ Q\_n 2 1 がオフ、p 型MOSトランジスタ Q\_p 3 がオン、p 型MOSトランジスタ Q\_p 2 1 がオフするため、ノード N A が電圧 ‘ V S S ’ に初期化され、ノード N B が電圧 ‘ V D D ’ に初期化される。

#### 【 0 1 6 1 】

次いで第 2 の期間 ( t 4 2 ~ t 4 3 ) において、制御回路 10 E は制御信号 S 1 を電圧 ‘ V S S ’ 、制御信号 S 2 を電圧 ‘ V D D ’ 、制御信号 S 3 を電圧 ‘ V D D ’ 、制御信号 S 4 を電圧 ‘ V S S ’ に設定する。これにより、n 型MOSトランジスタ Q\_n 3 がオフ、n 型MOSトランジスタ Q\_n 2 1 がオン、p 型MOSトランジスタ Q\_p 3 がオフ、p 型MOSトランジスタ Q\_p 2 1 がオンするため、ノード N A の電圧 V\_N A が ‘ V D D - V t h p ( Q\_p 1 ) ’ 、ノード N B の電圧 V\_N B が ‘ V S S + V t h n ( Q\_n 1 ) ’ に設定される。

20

#### 【 0 1 6 2 】

第 1 の期間および第 2 の期間 ( t 4 1 ~ t 4 3 ) において、制御回路 10 E は制御信号 S 5 を電圧 ‘ V D D ’ 、制御信号 S 6 を電圧 ‘ V S S ’ に設定する。これにより、p 型MOSトランジスタ Q\_p 5 および n 型MOSトランジスタ Q\_n 5 が共にオフし、p 型MOSトランジスタ Q\_p 1 および n 型MOSトランジスタ Q\_n 1 の貫通電流が防止される。

30

また、この第 1 の期間および第 2 の期間において、制御回路 10 E は制御信号 S 8 を電圧 ‘ V D D ’ に設定する。これにより、n 型MOSトランジスタ Q\_n 8 がオンし、キャパシタ C\_3 に電圧 ‘ V t h n ( Q\_n 1 ) ’ が充電される。

#### 【 0 1 6 3 】

次に第 6 の期間 ( t 4 3 ~ t 4 4 ) において、制御回路 10 E は、制御信号 S 1 , S 2 , S 5 を電圧 ‘ V S S ’ 、制御信号 S 3 , S 4 , S 6 を電圧 ‘ V D D ’ に設定する。これにより、n 型MOSトランジスタ Q\_n 3 , Q\_n 2 1 および p 型MOSトランジスタ Q\_p 3 , Q\_p 2 1 が全てオフする。

また第 6 の期間において、制御回路 10 E は、制御信号 S 8 を電圧 ‘ V S S ’ 、制御信号 S 9 を電圧 ‘ V D D ’ に設定する。これにより、n 型MOSトランジスタ Q\_n 8 がオフ、n 型MOSトランジスタ Q\_n 9 がオンし、キャパシタ C\_3 の一方の端子 ( ノード N B に接続されていない方の端子 ) の電圧は ‘ V S S ’ から ‘ V S S + V i n ’ へ上昇する。ここで、キャパシタ C\_3 の容量値がキャパシタ C\_B に比べて十分大きい場合 ( 例えば 3 倍以上の場合 ) 、 ‘ V S S ’ と ‘ V S S + V i n ’ との差分 ( V i n ) だけノード N B の電圧 V\_N B が上昇する。すなわち、ノード N\_N B の電圧は ‘ V S S + V t h n ( Q\_n 1 ) ’ から ‘ V S S + V t h n ( Q\_n 1 ) + V i n ’ へ正側にシフトする。これにより、n 型MOSトランジスタ Q\_n 1 はオフからオンへ切り替わる。

40

#### 【 0 1 6 4 】

上述した第 1 , 第 2 および第 6 の期間 ( t 4 1 ~ t 4 4 ) において、制御回路 10 E は制御信号 S 10 を電圧 ‘ V D D ’ に設定する。これにより、第 1 , 第 2 および第 6 の期間

50

においてn型MOSトランジスタQn10がオンし、ノードNEには電圧‘Vin’が入力される。

#### 【0165】

第6の期間( $t_{43} \sim t_{44}$ )の後、制御回路10Eは制御信号S9, S10, S11を電圧‘VSS’、制御信号XS11を電圧‘VDD’に設定する。これにより、n型MOSトランジスタQn10がオフ、トランスマルチゲート(Qp11, Qn11)がオンし、ノードNEには入力信号INが入力される。入力信号INは、電圧‘Vin’と電圧‘VSS’とを交互に繰り返す信号である。

#### 【0166】

入力信号INが電圧‘Vin’のとき、ノードNAおよびNBの電圧は第6の期間と同じ状態になるため、p型MOSトランジスタQp1はオフ、n型MOSトランジスタQn1はオンする。これにより、出力信号Oが電圧‘VSS’になる。10

他方、入力信号INが‘VSS’のとき、ノードNAおよびNBの電圧が負側へ電圧‘Vin’だけシフトする。すなわち、ノードNAの電圧が‘VDD - Vthp(Qp1)’から‘VDD - Vthp(Qp1) - Vin’へシフトし、ノードNBの電圧が‘VSS + Vthn(Qn1) + Vin’から‘VSS + Vthn(Qn1)’へシフトする。そのため、p型MOSトランジスタQp1がオン、n型MOSトランジスタQn1がオフし、出力信号Oが電圧‘VDD’になる。

#### 【0167】

以上説明したように、図14に示すレベルシフト回路LS1Aによれば、レベルシフトされた出力信号Oの出力期間(例えば図15の時刻 $t_{44}$ 以降)において、ノードNEには入力信号INが入力され、ノードNAおよびNBの電圧設定を行う期間( $t_{41} \sim t_{44}$ )においては、入力信号INの振幅に相当する‘VSS’～‘Vin’の電圧範囲に含まれる所定の電圧がノードNEに入力される。これにより、ノードNEに入力信号INを入力することなく、ノードNAおよびNBの電圧を設定することができる。すなわち、入力信号INのタイミングと無関係にノードNAおよびNBの電圧を設定することができる。20

図15では第1の期間( $t_{41} \sim t_{42}$ )、第2の期間( $t_{42} \sim t_{43}$ )、第6の期間( $t_{43} \sim t_{44}$ )を入力信号INのタイミングに合わせているが、本実施形態に係るレベルシフト回路では、この期間を入力信号INのタイミングに依存しない任意の時間幅に設定することができる。30

このように、入力信号INのタイミングと無関係にノードNAおよびNBの電圧を初期化することができる、回路システム内のグローバルな信号(例えばシステムクロック信号など)を入力信号INとして直接用いることが可能になるため、特別なクロック信号を生成する必要がなくなり、回路構成を簡易化することができる。

#### 【0168】

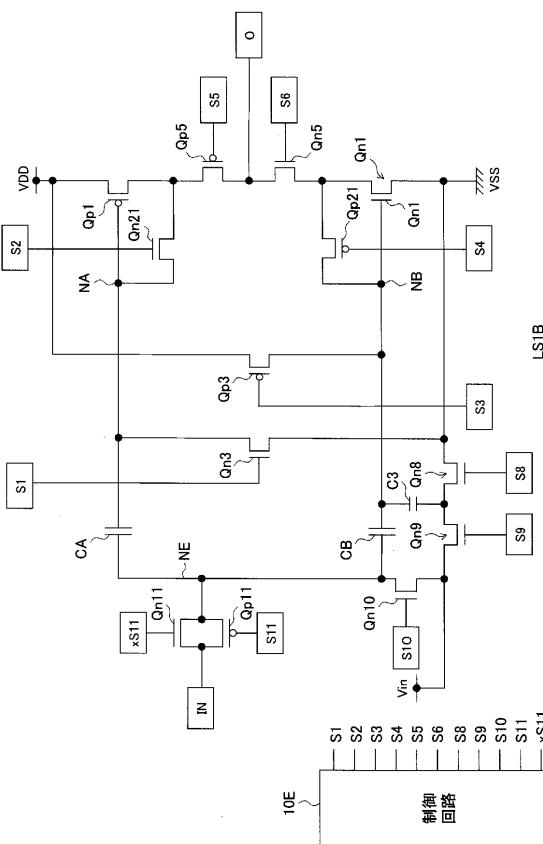

次に、本実施形態に係るレベルシフト回路の第2の構成例について、図16を参照して説明する。

#### 【0169】

図16に示す第2の構成例のレベルシフト回路LS1Bは、図14に示すレベルシフト回路におけるp型MOSトランジスタQp7およびn型MOSトランジスタQn7を削除し、n型MOSトランジスタQn21のゲートに制御信号S2を直接入力するとともに、p型MOSトランジスタQp21のゲートに制御信号S4を直接入力したものである。40

#### 【0170】

p型MOSトランジスタQp1のしきい値Vthp(Qp1)が比較的大きく、n型MOSトランジスタQn7およびQn21のしきい値Vthn(Qn7), Vthn(Qn21)が比較的小さい場合、ノードNAの電圧が‘VDD - Vthp(Qp1)’まで上昇した状態でも、‘VDD’のゲート電圧によってn型MOSトランジスタQn21をオフに駆動することができる。

また、n型MOSトランジスタQn1のしきい値Vthn(Qn1)が比較的大きく、

50

p型MOSトランジスタQp7およびQp21のしきい値Vthp(Qp7), Vthp(Qp21)が比較的小さい場合、ノードNBの電圧が‘VSS+Vthn(Qn1)’まで低下した状態でも、‘VSS’のゲート電圧によってp型MOSトランジスタQp21をオンに駆動することが可能である。

第2の構成例では、図16に示すようにブートストラップ動作用のトランジスタ(Qn7, Qp7)を省略することによって、回路構成を簡易化することができる。

#### 【0171】

次に、本実施形態に係るレベルシフト回路の第3の構成例について、図17を参照して説明する。

#### 【0172】

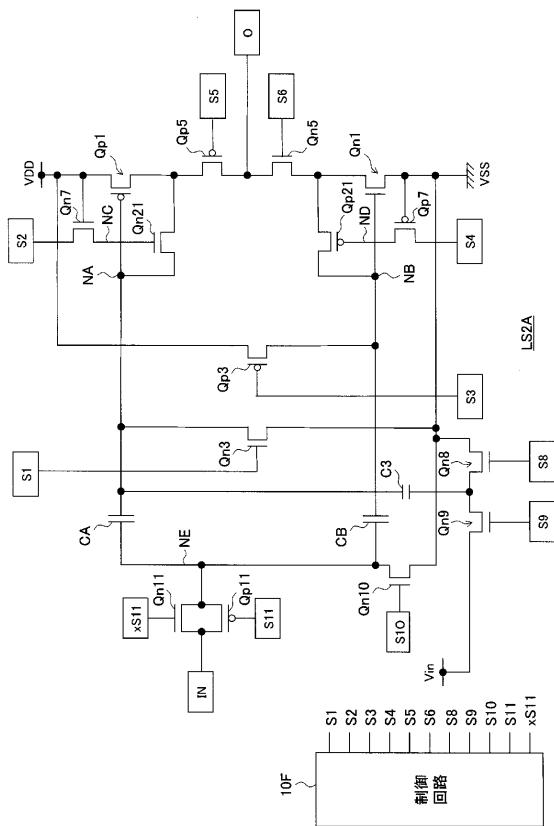

図17に示す第3の構成例のレベルシフト回路LS2Aは、図14に示すレベルシフト回路LS1AにおけるキャパシタC3とn型MOSトランジスタQn10の接続関係を変更し、更に、制御回路10Eを制御回路10Fに置換したものであり、他の構成は図14に示すレベルシフト回路LS1Aと同じである。

#### 【0173】

キャパシタC3は、その一方の端子がノードNAに接続され、他方の端子がn型MOSトランジスタQn8のドレインおよびn型MOSトランジスタQn9のソースに接続される。

#### 【0174】

n型MOSトランジスタQn10は、そのドレインがノードNEに接続され、そのソースが電源ラインVSSに接続され、そのゲートに制御信号S10が入力される。

#### 【0175】

制御回路10Fは、制御回路10Eにおける制御信号S8とS9のタイミングを交換する。すなわち制御回路10Fは、制御回路10Eにおいて制御信号S8として出力していた信号を制御信号S9として出力し、制御回路10Eにおいて制御信号S9として出力していた信号を制御信号S8として出力する。制御回路10Fにおける他の制御信号のタイミングは制御回路10Eと同じである。

#### 【0176】

図18は、図17に示すレベルシフト回路LS2Aにおける各部の信号波形の一例を示す図である。

図18(A)～(J)の信号波形は、図15(A)～(J)の信号波形と対応する。

#### 【0177】

図17に示すレベルシフト回路LS2Aでは、第1の期間および第2の期間(t41～t43)において、制御回路10Eが制御信号S9を電圧‘VDD’に設定し、制御信号S8を‘VSS’に設定する。これにより、n型MOSトランジスタQn9がオン、n型MOSトランジスタQn8がオフし、キャパシタC3に電圧‘VDD-Vthp(Qp1)’が充電される。

#### 【0178】

次に第6の期間(t43～t44)において、制御回路10Eは制御信号S9を電圧‘VSS’、制御信号S8を電圧‘VDD’に設定する。これにより、n型MOSトランジスタQn9がオフ、n型MOSトランジスタQn8がオンし、キャパシタC3の一方の端子(ノードNAに接続されていない方の端子)の電圧は‘VSS+Vin’から‘VSS’へ低下する。ここで、キャパシタC3の容量値がキャパシタCAに比べて十分大きい場合(例えば3倍以上の場合)、この‘VSS+Vin’と‘VSS’との差分(Vin)だけノードNAの電圧V\_NAが低下する。すなわち、ノードN\_NAの電圧は‘VDD-Vthp(Qp1)’から‘VDD-Vthp(Qp1)-Vin’へ負側にシフトする。これにより、p型MOSトランジスタQp1はオフからオンへ切り替わる。

#### 【0179】

上述した第1、第2および第6の期間(t41～t44)において、制御回路10Fは制御信号S10を電圧‘VDD’に設定する。これにより、第1、第2および第6の期間

10

20

30

40

50

においてn型MOSトランジスタQn10がオンし、ノードNEには電圧‘VSS’が入力される。

【0180】

第6の期間( $t_{43} \sim t_{44}$ )の後、制御回路10Eは制御信号S9, S10, S11を電圧‘VSS’、制御信号XS11を電圧‘VDD’に設定する。これにより、n型MOSトランジスタQn10がオフ、トランジスタ(Qp11, Qn11)がオンし、ノードNEには入力信号INが入力される。入力信号INは、電圧‘Vin’と電圧‘VSS’とを交互に繰り返す信号である。

【0181】

入力信号INが電圧‘Vin’のとき、ノードNAおよびNBの電圧は第6の期間と同じ状態になるため、p型MOSトランジスタQp1はオン、n型MOSトランジスタQn1はオフする。これにより、出力信号Oが電圧‘VDD’になる。

他方、入力信号INが‘VDD’のとき、ノードNAおよびNBの電圧が正側へ電圧‘Vin’だけシフトする。すなわち、ノードNAの電圧が‘VDD - Vthp(Qp1) - Vin’から‘VDD - Vthp(Qp1)’へシフトし、ノードNBの電圧が‘VSS + Vthn(Qn1)’から‘VSS + Vthn(Qn1) + Vin’へシフトする。そのため、n型MOSトランジスタQn1がオン、p型MOSトランジスタQp1がオフし、出力信号Oが電圧‘VSS’になる。

【0182】

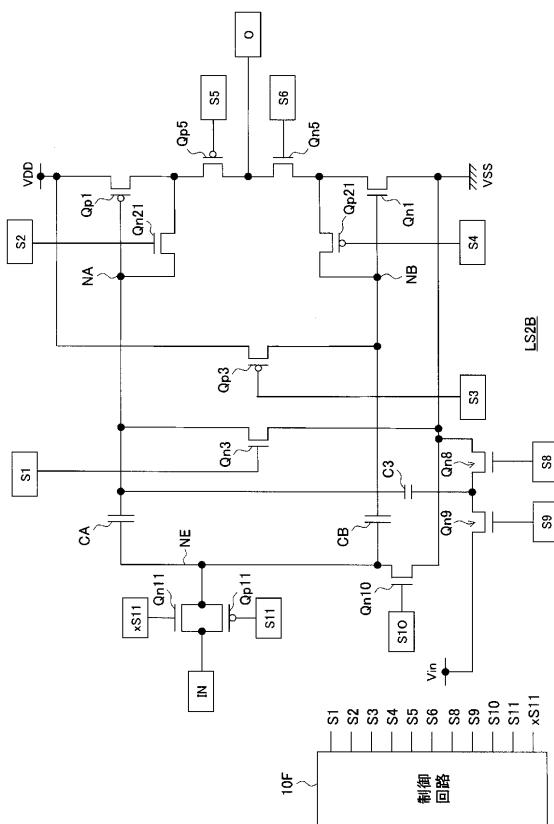

次に、本実施形態に係るレベルシフト回路の第4の構成例について、図19を参照して説明する。

【0183】

図19に示す第4の構成例のレベルシフト回路LS2Bは、図17に示すレベルシフト回路LS2Aにおけるp型MOSトランジスタQp7およびn型MOSトランジスタQn7を削除し、n型MOSトランジスタQn21のゲートに制御信号S2を直接入力するとともに、p型MOSトランジスタQp21のゲートに制御信号S4を直接入力したものである。

図16に示す第2の構成例のレベルシフト回路LS1Bと同様に、p型MOSトランジスタQp1およびn型MOSトランジスタQn1のしきい値が比較的大きく、n型MOSトランジスタQn7, Qn21およびp型MOSトランジスタQp7, Qp21のしきい値が比較的小さい場合、ブーストストラップ動作を行わなくても、n型MOSトランジスタQn21およびp型MOSトランジスタQp21をオンに駆動することが可能である。

第4の構成例では、図19に示すようにブーストストラップ動作用のトランジスタ(Qn7, Qp7)を省略することによって、回路構成を簡易化することができる。

【0184】

<第10の実施形態>

次に、本発明の第10の実施形態について説明する。

【0185】

第10の実施形態は、上述した実施形態のレベルシフト回路を用いて構成されるシフトレジスタに関するものである。

【0186】

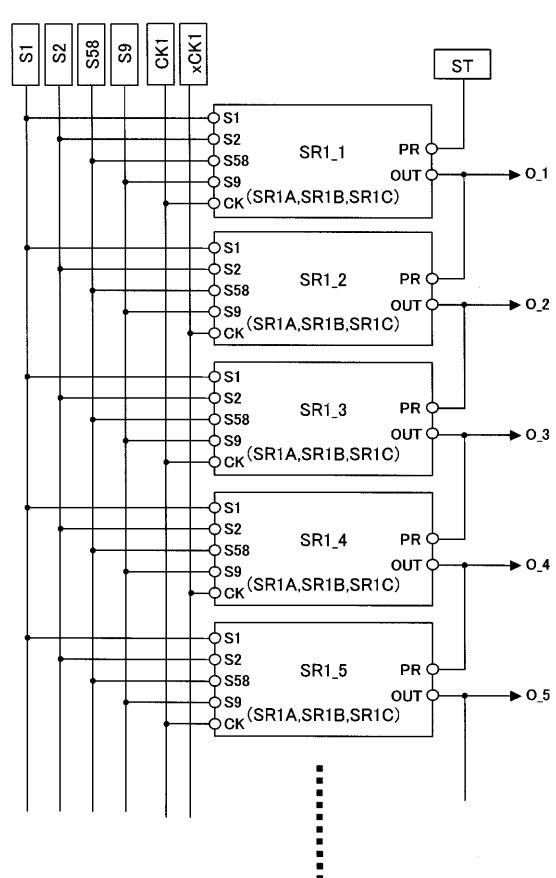

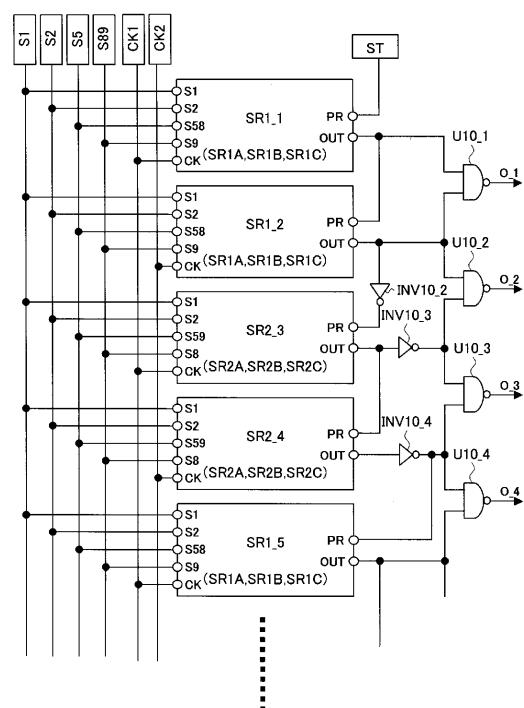

図20は、第10の実施形態に係るシフトレジスタの構成の一例を示す図である。

図20に示すシフトレジスタは、縦続接続された複数のシフト段SR1\_1, SR1\_2, SR1\_3, …を有する。

【0187】

各シフト段(SR1\_1, SR1\_2, SR1\_3, …)は、制御信号S1, S2, S58, S9の入力端子、並びに、クロック信号CKの入力端子を備えているとともに、レベルシフトされた出力信号OUTの出力端子、並びに、前段からの入力信号PRの入力端子を備えている。

【0188】

10

20

30

40

50

各シフト段 ( S R 1 \_ 1 , S R 1 \_ 2 , S R 1 \_ 3 , ... ) における制御信号 S 1 , S 2 , S 5 8 , S 9 の入力端子には、それぞれ、制御信号 S 1 , S 2 , S 5 8 , S 9 が共通に入力される。

【 0 1 8 9 】

奇数段のシフト段 ( S R 1 \_ 1 , S R 1 \_ 3 , S R 1 \_ 5 , ... ) におけるクロック信号 C K の端子には、クロック信号 C K 1 が共通に入力される。クロック信号 C K 1 は、電圧 ' V i n ' と電圧 ' V S S ' を交互に繰り返す信号である。

偶数段のシフト段 ( S R 1 \_ 2 , S R 1 \_ 4 , S R 1 \_ 6 , ... ) におけるクロック信号 C K の端子には、クロック信号 C K 1 を論理反転したクロック信号 x C K 1 が共通に入力される。

10

【 0 1 9 0 】

これを言い換えると、縦続接続された 2 つのシフト段 S R 1 \_ i および S R 1 \_ ( i + 1 ) には、互いに位相が反転したクロック信号が入力される。ただし、' i ' は自然数を示す。

【 0 1 9 1 】

シフト段 S R 1 \_ ( i + 1 ) における入力信号 P R の入力端子には、シフト段 S R 1 \_ i の出力信号 O U T が入力される。

また、初段 ( S R 1 \_ 1 ) における入力信号 P R の入力端子には、スタート信号 S T が入力される。

【 0 1 9 2 】

20

シフト段 S R 1 \_ i の出力信号 O U T は、シフトレジスタの第 i 段の出力信号 O \_ i として出力される。

【 0 1 9 3 】

図 2 0 に示すシフトレジスタにおけるシフト段の幾つかの構成例について説明する。

【 0 1 9 4 】

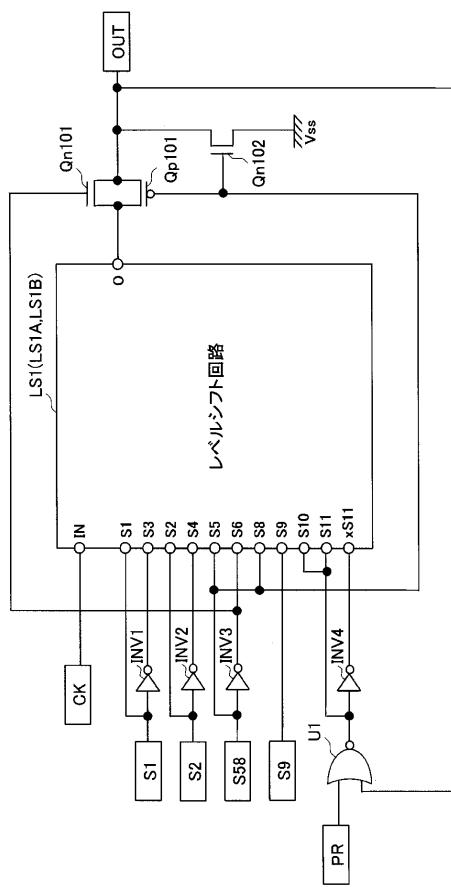

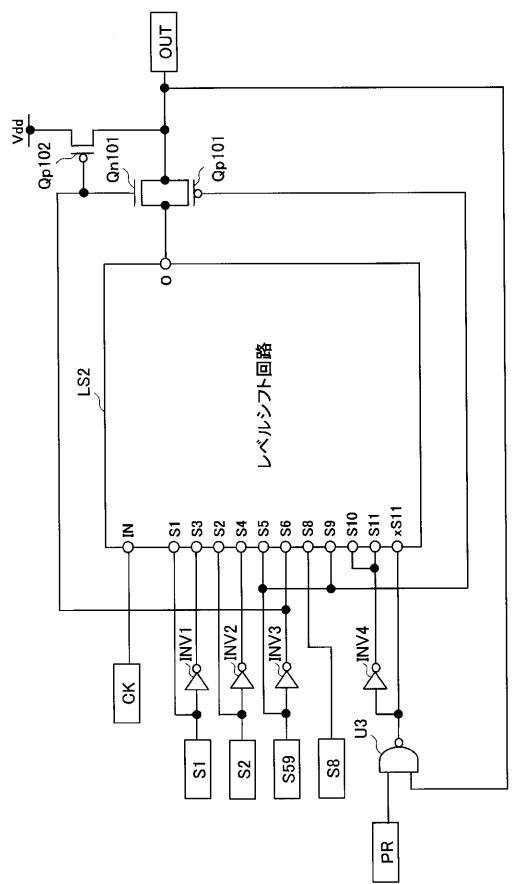

図 2 1 は、図 2 0 に示すシフトレジスタにおけるシフト段の第 1 の構成例を示す図である。

図 2 1 に示すシフト段 S R 1 A は、レベルシフト回路 L S 1 と、インバータ回路 I N V 1 ~ I N V 4 と、N O R 回路 U 1 と、p 型M O S トランジスタ Q p 1 0 1 と、n 型M O S トランジスタ Q n 1 0 1 および Q n 1 0 2 とを有する。

30

【 0 1 9 5 】

N O R 回路 U 1 は、本発明の検出回路の一実施形態である。

p 型M O S トランジスタ Q p 1 0 1 、n 型M O S トランジスタ Q n 1 0 1 および Q n 1 0 2 によって構成される回路は、本発明の出力回路の一実施形態である。

【 0 1 9 6 】

レベルシフト回路 L S 1 は、N O R 回路 U 1 から出力される信号がローレベル ( V S S ) のとき、クロック信号 C K の 1 サイクル内に含まれるパルス信号をレベルシフトして出力する。

レベルシフト回路 L S 1 は、例えば図 1 4 に示すレベルシフト回路 L S 1 A や図 1 6 に示すレベルシフト回路 L S 1 B と同様な構成を有する。ただし、各制御信号は外部から供給されるため、制御回路 1 0 E は省略される。

40

【 0 1 9 7 】

N O R 回路 U 1 は、シフト段 S R 1 A に対する前段からの入力信号 P R と、シフト段 S R 1 A の出力信号 O U T との反転論理和を演算し、制御信号 S 1 0 および S 1 1 として出力する。N O R 回路 U 1 の出力信号は、ハイレベル ( V D D ) のパルスが前段から入力信号 P R として入力される期間、並びに、ハイレベル ( V D D ) のパルスが次段へ出力信号 O U T として出力される期間においてローレベル ( V S S ) になる。

【 0 1 9 8 】

n 型M O S トランジスタ Q n 1 0 1 と p 型M O S トランジスタ Q p 1 0 1 は並列に接続されており、トランジスタを構成する。このトランジスタは、レベルシ

50

フト回路 L S 1 の出力信号 O の端子と、シフト段 S R 1 A の出力信号 O U T の端子との間に接続される。p 型MOS トランジスタ Q p 1 0 1 のゲートには制御信号 S 5 が入力され、n 型MOS トランジスタ Q n 1 0 1 のゲートには制御信号 S 6 が入力される。

#### 【 0 1 9 9 】

n 型MOS トランジスタ Q n 1 0 2 は、シフト段 S R 1 A の出力信号 O U T の端子と電源ライン V S S との間に接続される。n 型MOS トランジスタ Q n 1 0 2 のゲートには、制御信号 S 5 が入力される。

#### 【 0 2 0 0 】

インバータ I N V 1 は、シフト段 S R 1 A に入力される制御信号 S 1 を論理反転し、制御信号 S 3 を生成する。

10

インバータ I N V 2 は、シフト段 S R 1 A に入力される制御信号 S 2 を論理反転し、制御信号 S 4 を生成する。

インバータ I N V 3 は、シフト段 S R 1 A に入力される制御信号 S 5 8 を論理反転し、制御信号 S 6 を生成する。

インバータ I N V 4 は、N O R 回路 U 1 から出力される制御信号 S 1 1 を論理反転し、制御信号 x S 1 1 を生成する。

#### 【 0 2 0 1 】

シフト段 S R 1 A に入力されるクロック信号 C K ( C K 1 または x C K 1 ) は、入力信号 I N としてレベルシフト回路 L S 1 に入力される。

シフト段 S R 1 A に入力される制御信号 S 5 8 は、制御信号 S 5 および S 8 としてレベルシフト回路 L S 1 に入力される。

20

シフト段 S R 1 A に入力される制御信号 S 9 は、そのまま制御信号 S 9 としてレベルシフト回路 L S 1 に入力される。

#### 【 0 2 0 2 】

図 2 1 に示すシフト段 S R 1 A では、制御信号 S 5 8 がハイレベル ( V D D ) のとき、n 型MOS トランジスタ Q n 1 0 1 および p 型MOS トランジスタ Q p 1 0 1 で構成されるトランジスタゲートがオフし、n 型MOS トランジスタ Q n 1 0 2 がオンする。すなわち、ノード N A および N B の電圧設定が終了しておらず、レベルシフト回路 L S 1 の出力信号 O が不定な状態にある期間において、次段には一定の電圧 V S S が出力される。

他方、制御信号 S 5 8 がローレベル ( V S S ) のとき、トランジスタゲート ( Q p 1 0 1 , Q n 1 0 1 ) がオンし、n 型MOS トランジスタ Q n 1 0 2 がオフする。すなわち、ノード N A および N B の電圧設定が終了し、レベルシフト回路 L S 1 の出力信号 O がハイレベルまたはローレベルに確定する期間において、次段にはレベルシフト回路 L S 1 の出力信号 O が出力される。

30

#### 【 0 2 0 3 】

次に、シフト段の第 2 の構成例について説明する。

#### 【 0 2 0 4 】

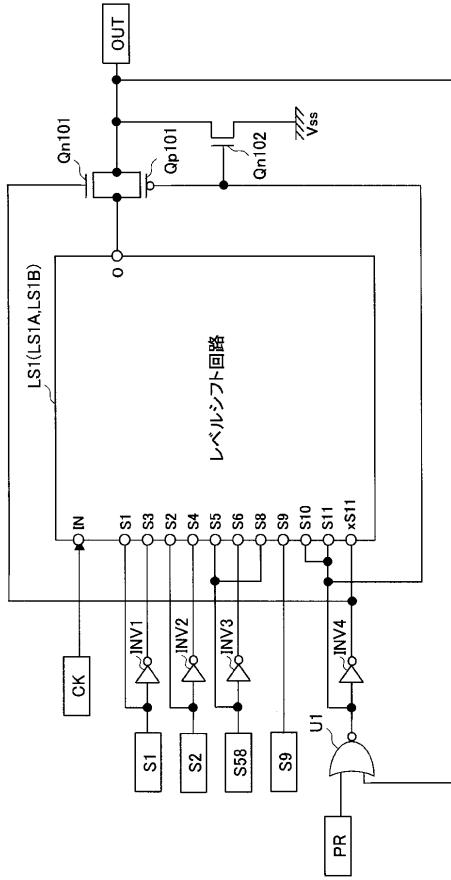

図 2 2 は、図 2 0 に示すシフトレジスタにおけるシフト段の第 2 の構成例を示す図である。

図 2 2 に示すシフト段 S R 1 B は、図 2 1 に示すシフト段 S R 1 A と同様の構成を有しており、両者の違いは p 型MOS トランジスタ Q p 1 0 1 および n 型MOS トランジスタ Q n 1 0 1 のゲートに入力される制御信号にある。

40

すなわち、シフト段 S R 1 B では、p 型MOS トランジスタ Q p 1 0 1 および n 型MOS トランジスタ Q n 1 0 2 のゲートに制御信号 S 1 1 が入力され、n 型MOS トランジスタ Q n 1 0 1 のゲートに制御信号 x S 1 1 が入力される。

#### 【 0 2 0 5 】

シフト段 S R 1 B によると、制御信号 S 1 1 がハイレベル ( V D D ) 、制御信号 x S 1 1 がローレベル ( V S S ) のとき、n 型MOS トランジスタ Q n 1 0 1 および p 型MOS トランジスタ Q p 1 0 1 で構成されるトランジスタゲートがオフし、n 型MOS トランジスタ Q n 1 0 2 がオンする。すなわち、レベルシフト回路 L S 1 においてレベルシフト

50

動作が行われない期間において、次段には一定の電圧VSSが出力される。

他方、制御信号S11がローレベル(VSS)、制御信号xS11がハイレベル(VDD)のとき、トランスファーゲート(Qp101, Qn101)がオンし、n型MOSトランジスタQn102がオフする。すなわち、レベルシフト回路LS1においてレベルシフト動作が行われる期間において、次段にはレベルシフト回路LS1の出力信号Oが出力される。

#### 【0206】

次に、シフト段の第3の構成例について説明する。

#### 【0207】

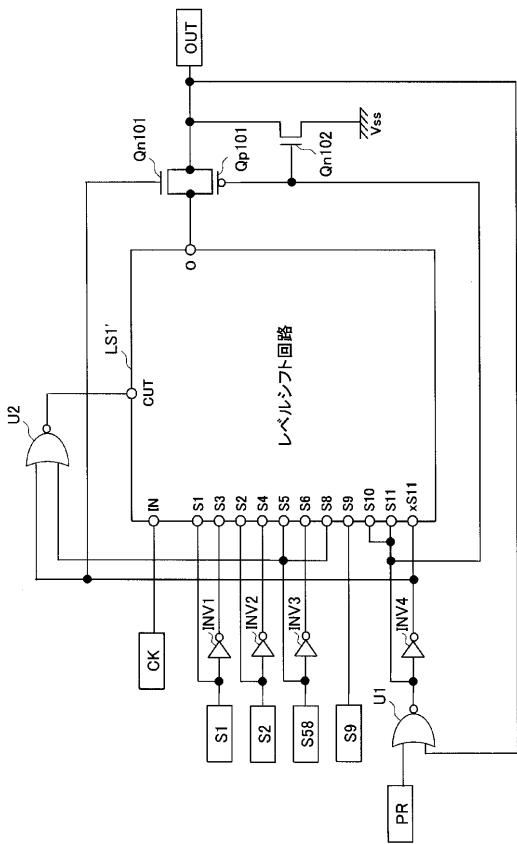

図23は、図20に示すシフトレジスタにおけるシフト段の第3の構成例を示す図である。 10

図23に示すシフト段SR1Cは、図22に示すシフト段SR1Bにおけるレベルシフト回路LS1(LS1AまたはLS1B)を次に述べるLS1'(LS1CまたはLS1D)に置換し、更にOR回路U2を追加したものであり、他の構成はシフト段SR1Bと同じである。

#### 【0208】

図24は、レベルシフト回路LS1'の第1の構成例を示す図である。

図24に示すレベルシフト回路LS1Cは、図14に示すレベルシフト回路LS1Aにp型MOSトランジスタQp12を追加したものであり、他の構成要素はレベルシフト回路LS1Aと同じである。 20

p型MOSトランジスタQp12は、p型MOSトランジスタQp1のソースと電源ラインVDDとを接続する経路に挿入され、そのゲートに制御信号CUTが入力される。

#### 【0209】

図25は、レベルシフト回路LS1'の第2の構成例を示す図である。

図25に示すレベルシフト回路LS1Dは、図16に示すレベルシフト回路LS1Bにp型MOSトランジスタQp12を追加したものであり、他の構成要素はレベルシフト回路LS1Bと同じである。

p型MOSトランジスタQp12は、レベルシフト回路LS1Cと同様に、p型MOSトランジスタQp1のソースと電源ラインVDDとを接続する経路に挿入され、そのゲートに制御信号CUTが入力される。 30

#### 【0210】

図23に示すシフト段SR1Cにおいて、NOR回路U2は、制御信号S5と制御信号xS11の反転論理和を演算し、その演算結果を制御信号CUTとしてレベルシフト回路LS1'に供給する。

#### 【0211】

制御信号S5がハイレベル(VDD)のとき、または、制御信号xS11がハイレベル(VDD)のとき、NOR回路U2より出力される制御信号CUTはローレベル(VSS)になり、p型MOSトランジスタQp12はオンする。すなわち、ノードNAおよびNBの電圧設定が行われる期間や、レベルシフト回路LS1'においてレベルシフト動作が行われる期間において、p型MOSトランジスタQp1のソースは電源ラインVDDに接続される。 40

他方、制御信号S5がローレベル(VSS)かつ制御信号xS11がローレベル(VSS)のとき、NOR回路U2より出力される制御信号CUTはハイレベル(VDD)となり、p型MOSトランジスタQp12はオフする。すなわち、ノードNAおよびNBの電圧設定が行われておらず、かつ、レベルシフト回路LS1'においてレベルシフト動作が行われていない期間において、p型MOSトランジスタQp1のソースは電源ラインVDDから遮断される。したがって、p型MOSトランジスタQp1に電流を流す必要がないときには、p型MOSトランジスタQp1のソースを電源ラインVDDから遮断することによって、p型MOSトランジスタQp1に流れる無駄なリーク電流を抑制する。

#### 【0212】

10

20

30

40

50

次に、上述した構成を有する本実施形態に係るシフトレジスタの動作について、図26を参照して説明する。

【0213】

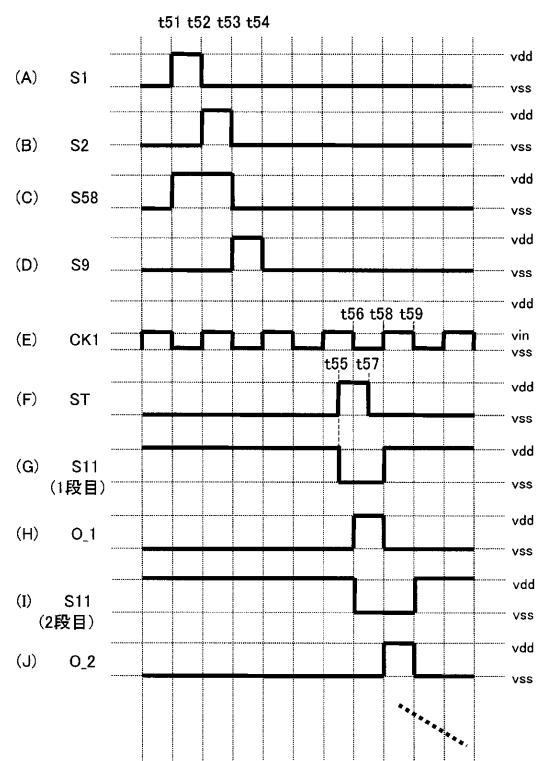

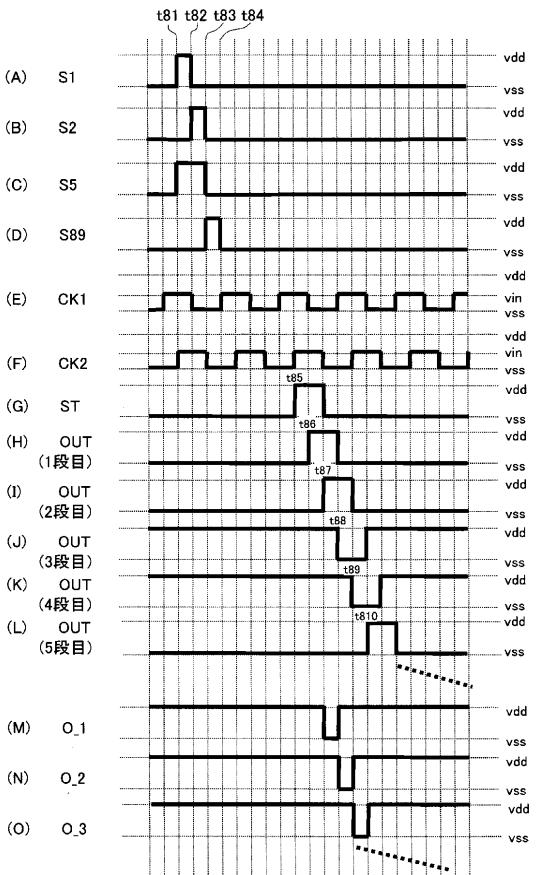

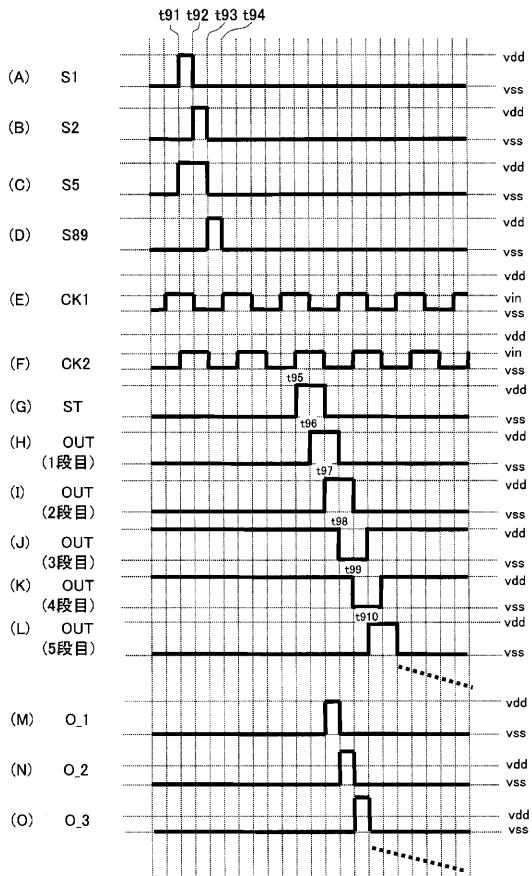

図26は、本実施形態に係るシフトレジスタにおける各部の信号波形の一例を示す図である。

図26(A)は、制御信号S1の電圧波形を示す。

図26(B)は、制御信号S2の電圧波形を示す。

図26(C)は、制御信号S58の電圧波形を示す。

図26(D)は、制御信号S9の電圧波形を示す。

図26(E)は、クロック信号CK1の電圧波形を示す。

図26(F)は、スタート信号STの電圧波形を示す。

図26(G)は、1段目のシフト段SR1\_1の内部で生成される制御信号S11の電圧波形を示す。

図26(H)は、1段目のシフト段SR1\_1の出力信号O\_1を示す。

図26(I)は、2段目のシフト段SR1\_2の内部で生成される制御信号S11の電圧波形を示す。

図26(J)は、2段目のシフト段SR1\_2の出力信号O\_2を示す。

【0214】

図26に示す時刻t51～t54の期間では、図15に示す時刻t41～44と同様な動作によって、各シフト段(SR1\_1, SR1\_2, ...)に含まれるレベルシフト回路LS1(LS1')が初期化される。

すなわち、第1の期間(t51～t52)においては、ノードNAが電圧‘VSS’、ノードNBが‘電圧VDD’に設定される。第2の期間(t52～t53)においては、ノードNAが電圧‘VDD - Vthp(Qp1)’に設定され、ノードNBが電圧‘VSS + Vthn(Qn1)’に設定される。第6の期間(t53～t54)においては、ノードNBが電圧‘VSS + Vthn(Qn1) + Vin’に設定される。

【0215】

シフト動作を行う前の初期状態において、各シフト段(SR1\_1, SR1\_2, ...)の入力信号PRおよび出力信号OUTは全てローレベル(VSS)になっているものとする。

この場合、シフト段の入力信号PRおよび出力信号OUTがローレベル(VSS)になるため、シフト段内部のNOR回路U1で生成される制御信号S10およびS11は全てハイレベル(VDD)になる。

制御信号S10およびS11がハイレベルになると、レベルシフト回路のノードNEに電圧‘Vin’が供給される。ノードNEが電圧‘Vin’になると、図15に示すように、ノードNA, NBの電圧設定を行う第1および第2の期間(t51～t53)を除いて、出力信号Oがローレベル(VSS)になる。

ノードNA, NBの電圧設定を行う第1および第2の期間(t51～t53)では、レベルシフト回路の出力に接続されるトランスマニアゲート(Qn101, Qp101)がオフし、n型MOSトランジスタQn102がオンすることにより、シフト段の出力信号OUTはローレベル(VSS)になる。

したがって、シフト動作を行う前の初期状態において、各シフト段の入出力信号はローレベル(VSS)に保たれる。

【0216】

時刻t51～t54におけるレベルシフト回路の初期化が終了すると、シフトレジスタの1段目のシフト段SR1\_1にハイレベル(VDD)のパルスがスタート信号STとして入力される。このパルスは、例えば図26(F)に示すように、クロック信号CK1のハイレベル(Vin)からローレベル(VSS)への立下り時(t56)においてハイレベル(VDD)となり、かつクロック信号CK1の1サイクルの期間よりパルス幅が短くなるように生成される(t55～t57)。

## 【0217】

スタート信号 S\_T がハイレベル (VDD) になると、1段目のシフト段 S\_R1\_1 に含まれるNOR回路 U\_1 においてローレベル (VSS) の制御信号 S\_1\_1 が生成される (図 26 (G))。

制御信号 S\_1\_1 がローレベル (VSS) になると、1段目のシフト段 S\_R1\_1 に含まれるレベルシフト回路 LS\_1 (LS1') のノード N\_E に、クロック信号 CK\_1 が入力される。クロック信号 CK\_1 が時刻 t\_5\_6 においてハイレベル (V\_in) からローレベル (VSS) に立ち下がると、レベルシフト回路 LS\_1 (LS1') の出力信号 OUT (= 'O\_1') はローレベル (VSS) からハイレベル (VDD) に立ち上がる (図 26 (H))。

## 【0218】

1段目のシフト段 S\_R1\_1 の出力信号 O\_1 がハイレベル (VDD) になると、2段目のシフト段 S\_R1\_2 に含まれるNOR回路 U\_1 においてローレベル (VSS) の制御信号 S\_1\_1 が生成される (図 26 (I))。

制御信号 S\_1\_1 がローレベル (VSS) になると、2段目のシフト段 S\_R1\_2 に含まれるレベルシフト回路 LS\_1 (LS1') のノード N\_E に、クロック信号 x CK\_1 が入力される。クロック信号 x CK\_1 は時刻 t\_5\_6 の後にハイレベル (V\_in) になるため、レベルシフト回路 LS\_1 (LS1') の出力信号 OUT (= 'O\_2') はローレベル (VSS) になる (図 26 (J))。

## 【0219】

時刻 t\_5\_7 においてスタート信号 S\_T のハイレベル (VDD) のパルスが終了しても、1段目のシフト段 S\_R1\_1 におけるNOR回路 U\_1 にはハイレベル (VDD) の出力信号 OUT が入力されるため、NOR回路 U\_1 の出力信号 (制御信号 S\_1\_1) は引き続きローレベル (VSS) に保たれる (図 26 (G))。これにより、1段目のシフト段 S\_R1\_1 ではレベルシフト動作が続行され、出力信号 O\_1 はハイレベルに保たれる (図 26 (H))。

## 【0220】

時刻 t\_5\_8 においてクロック信号 CK\_1 がローレベル (VSS) からハイレベル (V\_in) に立ち上ると、1段目のシフト段 S\_R1\_1 におけるレベルシフト回路 LS\_1 (LS1') の出力信号 OUT がハイレベル (VDD) からローレベル (VSS) に立ち下がる。出力信号 OUT がローレベル (VSS) になると、NOR回路 U\_1 の入力信号が全てローレベル (VSS) になるため、NOR回路 U\_1 から出力される制御信号 S\_1\_1 がハイレベル (VDD) になる。制御信号 S\_1\_1 がハイレベル (VDD) になると、レベルシフト回路 LS\_1 (LS1') におけるレベルシフト動作が停止され、以降クロック信号 CK\_1 がハイレベル (V\_in) からローレベル (VSS) へ立ち下がっても、1段目のシフト段 S\_R1\_1 の出力信号 O\_1 はローレベル (VSS) のまま保持される。

## 【0221】

他方、時刻 t\_5\_8 においてクロック信号 x CK\_1 がハイレベル (V\_in) からローレベル (VSS) へ立ち下がると、このクロック信号 x CK\_1 を入力したシフト段 S\_R1\_2 の出力信号 O\_2 はローレベル (VSS) からハイレベル (VDD) に立ち上がる (図 26 (J))。出力信号 O\_2 がハイレベル (VDD) になることにより、2段目のシフト段 S\_R1\_2 に含まれるNOR回路 U\_1 の出力信号 (制御信号 S\_1\_1) は引き続きローレベル (VSS) に保持され、レベルシフト動作が続行される。

以降、同様な動作によって、ハイレベルのパルス信号がクロック信号 CK\_1 および x CK\_1 に同期しながら、後段のシフト段へ順次に伝播される。

## 【0222】

以上説明したように、本実施形態によれば、先の各実施形態で述べたレベルシフト回路を用いてシフトレジスタを構成することができる。したがって、トランジスタのしきい電圧のばらつきに影響されない安定なレベルシフト動作を行いつつ、シフトレジスタとしての機能を実現することができる。

## 【0223】

また、本実施形態によれば、各シフト段を構成するレベルシフト回路におけるリーク電流を非常に小さくすることができるため、消費電力を大幅に削減することができる。

## 【0224】

特に、図24や図25に示すレベルシフト回路LS1'で構成されたシフト段SRCを用いた場合、p型MOSトランジスタQp1に電流を流す必要がない期間（レベルシフト回路LS'1の入力信号PRおよび出力信号OUTが非パルスのローレベルになり、かつ、ノードNA, NBの電圧設定が行われない制御信号S5がローレベルの期間）において、p型MOSトランジスタQp12がオフし、p型MOSトランジスタQp1と電源ラインVDDとが遮断される。これにより、ノードNA, NBの電圧が飛び込みノイズや電源電圧変動などで不安定になった場合でも、p型MOSトランジスタQp1に流れるリーク電流をp型MOSトランジスタQp12によって効果的に遮断することができる。

10

## 【0225】

更に、本実施形態によれば、各シフト段を構成するレベルシフト回路において、トランジスタのしきい値より小さい振幅の信号でもレベルシフト動作を行うことができるため、小振幅のクロック信号で動作可能である。

## 【0226】

なお、上述の実施形態では、制御信号S3, S4, S6を生成するインバータ回路INV1~INV3を各シフト段に設けているが、これらのインバータ回路を複数のシフト段で共有しても良い。これにより、回路素子を削減することができる。

20

## 【0227】

また、上述の実施形態では、レベルシフト回路を初期化するために4つの制御信号（S1, S2, S58, S9）を必要としているが、これらの制御信号の幾つかを他の制御信号に基づいて生成可能である。

## 【0228】

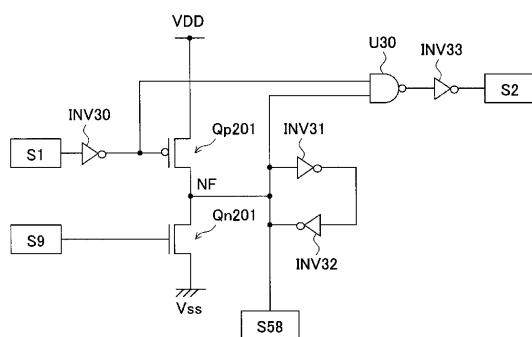

図27は、制御信号S1およびS9に基づいて制御信号S2およびS58を生成する回路の一例を示す図である。

図27に示す回路は、インバータ回路INV30~INV33と、NAND回路U30と、p型MOSトランジスタQp201と、n型MOSトランジスタQn201とを有する。

30

## 【0229】

インバータ回路INV30は、制御信号S1を論理反転する。

## 【0230】

p型MOSトランジスタQp201は、そのソースが電源ラインVDDに接続され、そのドレインがノードNFに接続され、そのゲートがインバータ回路30の出力に接続される。

n型MOSトランジスタQn201は、そのソースが電源ラインVSSに接続され、そのドレインがノードNFに接続され、そのゲートに制御信号S9が入力される。

## 【0231】

インバータ回路INV31とINV32は、互いの入力と出力がリング状に接続される。このリング状に接続されたインバータ回路INV31およびINV32の一端（図27の例ではインバータ回路INV32の出力）が、ノードNFに接続される。このノードNFにおいて制御信号S58が発生する。

40

## 【0232】

NAND回路U30は、インバータ回路INV30の出力信号（制御信号×S1）と、ノードNFの信号（制御信号S58）との反転論理積を演算する。インバータ回路INV33は、NOR回路30の出力信号を論理反転し、制御信号S2として出力する。

## 【0233】

図28は、図27に示す回路の各部の信号波形の一例を示す図である。

時刻t61において制御信号S1がハイレベル、制御信号S9がローレベルになると、

50

p型MOSトランジスタQ<sub>p</sub>201がオン、n型MOSトランジスタQ<sub>n</sub>201がオフするため、制御信号S58はハイレベルになる(図28(C))。また、このとき、インバータ回路INV30の出力信号はローレベルであるため、制御信号S2はローレベルになる。

時刻t62において制御信号S1がローレベルになると、p型MOSトランジスタQ<sub>p</sub>201がオフする。このとき、ノードNFの電圧は、リング状に接続されたインバータ回路INV31およびINV32によって保持されるため、ハイレベルに保持される。また、NAND回路U30の2つの入力信号は共にハイレベルになるため、制御信号S2はハイレベルになる。

時刻t63において制御信号S9がハイレベルになると、n型MOSトランジスタQ<sub>n</sub>201がオンするため、制御信号S58はローレベルになる。また、このとき、NAND回路U30にローレベルの制御信号S58が入力されるため、制御信号S2もローレベルになる。

#### 【0234】

このように、図27に示す回路によれば、制御信号S1およびS9に基づいて制御信号S2およびS58を生成することにより、シフトレジスタの制御のために外部から供給する信号の数を減らすことができる。

#### 【0235】

<第11の実施形態>

次に、本発明の第11の実施形態について説明する。

20

#### 【0236】

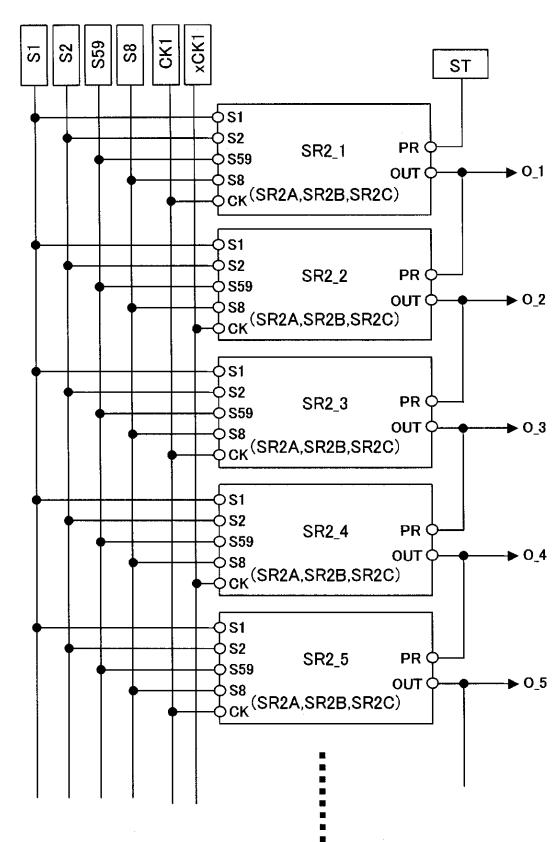

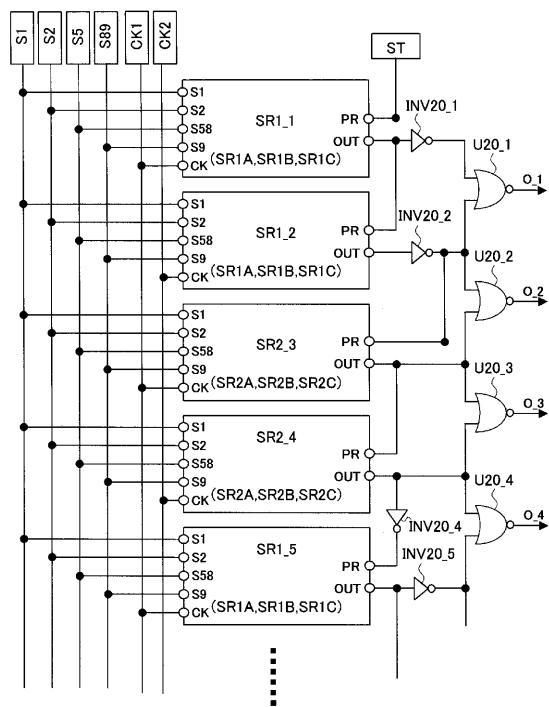

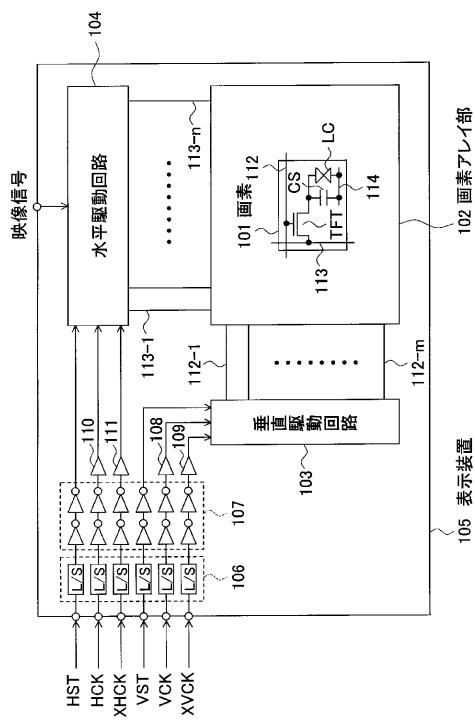

図29は、第11の実施形態に係るシフトレジスタの構成の一例を示す図である。

図29に示すシフトレジスタは、縦続接続された複数のシフト段SR2\_1, SR2\_2, SR2\_3, ...を有する。

#### 【0237】

各シフト段(SR2\_1, SR2\_2, SR2\_3, ...)は、制御信号S1, S2, S59, S8の入力端子、並びに、クロック信号CKの入力端子を備えているとともに、レベルシフトされた出力信号OUTの出力端子、並びに、前段からの入力信号PRの入力端子を備えている。

#### 【0238】

30

各シフト段(SR2\_1, SR2\_2, SR2\_3, ...)における制御信号S1, S2, S59, S8の入力端子には、それぞれ、制御信号S1, S2, S59, S8が共通に入力される。

#### 【0239】

奇数段のシフト段(SR2\_1, SR2\_3, SR2\_5, ...)におけるクロック信号CKの端子には、クロック信号CK1が共通に入力される。

偶数段のシフト段(SR2\_2, SR2\_4, SR2\_6, ...)におけるクロック信号CKの端子には、クロック信号CK1を論理反転したクロック信号xCCK1が共通に入力される。

#### 【0240】

40

これを言い換えると、縦続接続された2つのシフト段SR2\_iおよびSR2\_(i+1)には、互いに位相が反転したクロック信号が入力される。

#### 【0241】

シフト段SR2\_(i+1)における入力信号PRの入力端子には、シフト段SR2\_iの出力信号OUTが入力される。

また、初段(SR2\_1)における入力信号PRの入力端子には、スタート信号STが入力される。

#### 【0242】

シフト段SR2\_iの出力信号OUTは、シフトレジスタの第i段の出力信号O\_iとなる。

50

## 【0243】

図29に示すシフトレジスタにおけるシフト段の幾つかの構成例について説明する。

## 【0244】

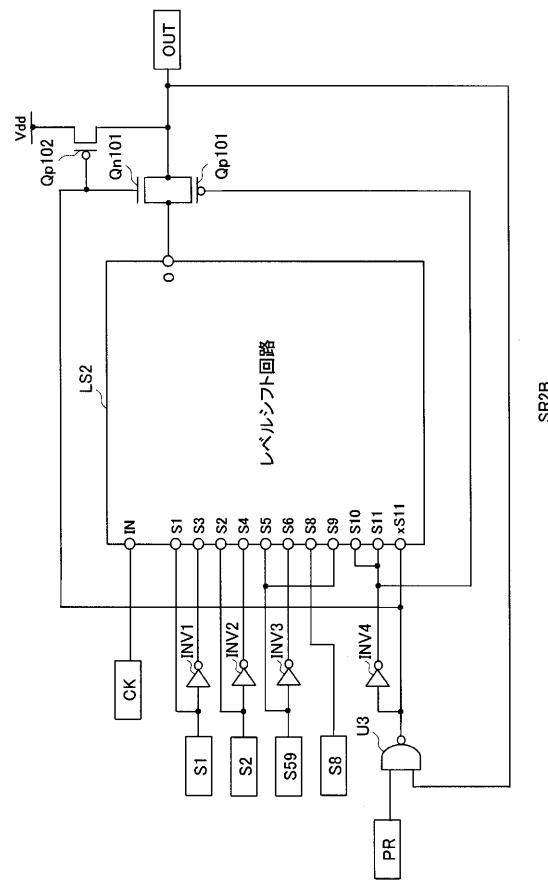

図30は、図29に示すシフトレジスタにおけるシフト段の第1の構成例を示す図である。

図30に示すシフト段SR2Aは、レベルシフト回路LS2と、インバータ回路INV1～INV4と、NAND回路U3と、p型MOSトランジスタQp101, Qp102と、n型MOSトランジスタQn101とを有する。

## 【0245】

NAND回路U3は、本発明の検出回路の一実施形態である。

p型MOSトランジスタQp101, Qp102およびn型MOSトランジスタQn101によって構成される回路は、本発明の出力回路の一実施形態である。

## 【0246】

レベルシフト回路LS2は、NAND回路U3から出力される信号がハイレベル(VDD)のとき、クロック信号CKの1サイクル内に含まれるパルス信号をレベルシフトして出力する。

レベルシフト回路LS2は、例えば図17に示すレベルシフト回路LS2Aや図19に示すレベルシフト回路LS2Bと同様な構成を有する。ただし、各制御信号は外部から供給されるため、制御回路10Fは省略される。

## 【0247】

NAND回路U3は、シフト段SR2Aに対する前段からの入力信号PRと、シフト段SR2Aの出力信号OUTとの反転論理和を演算し、制御信号XS11として出力する。NAND回路U3の出力信号は、ローレベル(VSS)のパルスが前段から入力信号PRとして入力される期間、並びに、ローレベル(VSS)のパルスが次段へ出力信号OUTとして出力される期間においてハイレベル(VDD)になる。

## 【0248】

n型MOSトランジスタQn101とp型MOSトランジスタQp101は並列に接続されており、トランスマルチゲートを構成する。このトランスマルチゲートは、レベルシフト回路LS2の出力信号Oの端子と、シフト段SR2Aの出力信号OUTの端子との間に接続される。p型MOSトランジスタQp101のゲートには制御信号S5が入力され、n型MOSトランジスタQn101のゲートには制御信号S6が入力される。

## 【0249】

p型MOSトランジスタQp102は、シフト段SR2Aの出力信号OUTの端子と電源ラインVDDとの間に接続される。p型MOSトランジスタQp102のゲートには、制御信号S6が入力される。

## 【0250】

インバータINV1は、シフト段SR2Aに入力される制御信号S1を論理反転し、制御信号S3を生成する。

インバータINV2は、シフト段SR2Aに入力される制御信号S2を論理反転し、制御信号S4を生成する。

インバータINV3は、シフト段SR2Aに入力される制御信号S5を論理反転し、制御信号S6を生成する。

インバータINV4は、NAND回路U3から出力される制御信号XS11を論理反転し、制御信号S10およびS11を生成する。

## 【0251】

シフト段SR2Aに入力されるクロック信号CK(CK1またはXCK1)は、入力信号INとしてレベルシフト回路LS2に入力される。

シフト段SR2Aに入力される制御信号S59は、制御信号S5およびS9としてレベルシフト回路LS2に入力される。

シフト段SR2Aに入力される制御信号S8は、そのまま制御信号S8としてレベルシ

10

20

30

40

50

フト回路 L S 2 に入力される。

【 0 2 5 2 】

図 3 0 に示すシフト段 S R 2 A では、制御信号 S 5 9 がハイレベル ( V D D ) のとき、n 型M O S トランジスタ Q n 1 0 1 および p 型M O S トランジスタ Q p 1 0 1 で構成されるトランジスタがオフし、p 型M O S トランジスタ Q p 1 0 2 がオンする。すなわち、ノード N A および N B の電圧設定が終了しておらず、レベルシフト回路 L S 2 の出力信号 O が不定な状態にある期間において、次段には一定の電圧 V S S が出力される。

他方、制御信号 S 5 9 がローレベル ( V S S ) のとき、トランジスタ ( Q p 1 0 1 , Q n 1 0 1 ) がオンし、p 型M O S トランジスタ Q p 1 0 2 がオフする。すなわち、ノード N A および N B の電圧設定が終了し、レベルシフト回路 L S 2 の出力信号 O がハイレベルまたはローレベルに確定する期間において、次段にはレベルシフト回路 L S 1 の出力信号 O が出力される。

【 0 2 5 3 】

次に、シフト段の第 2 の構成例について説明する。

【 0 2 5 4 】

図 3 1 は、図 2 9 に示すシフトレジスタにおけるシフト段の第 2 の構成例を示す図である。

図 3 1 に示すシフト段 S R 2 B は、図 3 0 に示すシフト段 S R 2 A と同様の構成を有しており、両者の違いは p 型M O S トランジスタ Q p 1 0 1 , Q p 1 0 2 および n 型M O S トランジスタ Q n 1 0 1 のゲートに入力される制御信号にある。

すなわち、シフト段 S R 2 B では、n 型M O S トランジスタ Q n 1 0 1 および p 型M O S トランジスタ Q p 1 0 2 のゲートに制御信号 X S 1 1 が入力され、p 型M O S トランジスタ Q p 1 0 1 のゲートに制御信号 S 1 1 が入力される。

【 0 2 5 5 】

シフト段 S R 2 B によると、制御信号 S 1 1 がハイレベル ( V D D ) 、制御信号 X S 1 1 がローレベル ( V S S ) のとき、n 型M O S トランジスタ Q n 1 0 1 および p 型M O S トランジスタ Q p 1 0 1 で構成されるトランジスタがオフし、p 型M O S トランジスタ Q p 1 0 2 がオンする。すなわち、レベルシフト回路 L S 2 においてレベルシフト動作が行われない期間において、次段には一定の電圧 V S S が出力される。

他方、制御信号 S 1 1 がローレベル ( V S S ) 、制御信号 X S 1 1 がハイレベル ( V D D ) のとき、トランジスタ ( Q p 1 0 1 , Q n 1 0 1 ) がオンし、p 型M O S トランジスタ Q p 1 0 2 がオフする。すなわち、レベルシフト回路 L S 2 においてレベルシフト動作が行われる期間において、次段にはレベルシフト回路 L S 2 の出力信号 O が出力される。

【 0 2 5 6 】

次に、シフト段の第 3 の構成例について説明する。

【 0 2 5 7 】

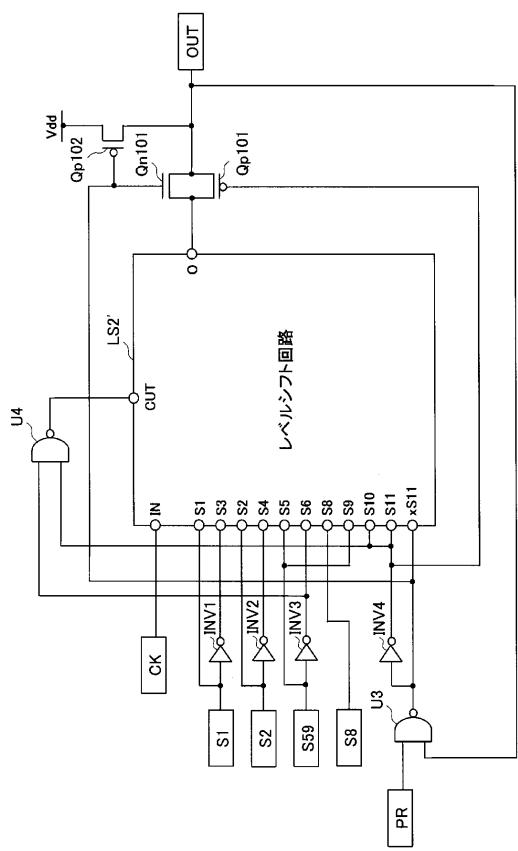

図 3 2 は、図 2 9 に示すシフトレジスタにおけるシフト段の第 3 の構成例を示す図である。

図 3 2 に示すシフト段 S R 2 C は、図 3 1 に示すシフト段 S R 2 B におけるレベルシフト回路 L S 2 ( L S 2 A または L S 2 B ) を次に述べる L S 2 ' ( L S 2 C または L S 2 D ) に置換し、更に N A N D 回路 U 4 を追加したものであり、他の構成はシフト段 S R 2 B と同じである。

【 0 2 5 8 】

図 3 3 は、レベルシフト回路 L S 2 ' の第 1 の構成例を示す図である。

図 3 3 に示すレベルシフト回路 L S 2 C は、図 1 7 に示すレベルシフト回路 L S 2 A に n 型M O S トランジスタ Q n 1 2 を追加したものであり、他の構成要素はレベルシフト回路 L S 2 A と同じである。

n 型M O S トランジスタ Q n 1 2 は、n 型M O S トランジスタ Q n 1 のソースと電源ライン V S S とを接続する経路に挿入され、そのゲートに制御信号 C U T が入力される。

10

20

30

40

50

## 【0259】

図34は、レベルシフト回路LS2'の第2の構成例を示す図である。

図34に示すレベルシフト回路LS2Dは、図19に示すレベルシフト回路LS2Bにn型MOSトランジスタQn12を追加したものであり、他の構成要素はレベルシフト回路LS2Bと同じである。

n型MOSトランジスタQn12は、レベルシフト回路LS2Cと同様に、n型MOSトランジスタQn1のソースと電源ラインVSSとを接続する経路に挿入され、そのゲートに制御信号CUTが入力される。

## 【0260】

NAND回路U4は、制御信号S6と制御信号S11の反転論理積を演算し、その演算結果を制御信号CUTとしてレベルシフト回路LS2'に供給する。 10

## 【0261】

制御信号S6がローレベル(VSS)のとき、または、制御信号S11がローレベル(VSS)のとき、NAND回路U4より出力される制御信号CUTはハイレベル(VDD)になり、n型MOSトランジスタQn12はオンする。すなわち、ノードNAおよびNBの電圧設定が行われる期間や、レベルシフト回路LS2'においてレベルシフト動作が行われる期間において、n型MOSトランジスタQn1のソースは電源ラインVSSに接続される。

他方、制御信号S6がハイレベル(VDD)かつ制御信号S11がハイレベル(VDD)のとき、NAND回路U4より出力される制御信号CUTはローレベル(VSS)となり、n型MOSトランジスタQn12はオフする。すなわち、ノードNAおよびNBの電圧設定が行われておらず、かつ、レベルシフト回路LS2'においてレベルシフト動作が行われていない期間において、n型MOSトランジスタQn1のソースは電源ラインVSSから遮断される。したがって、n型MOSトランジスタQn1に電流を流す必要がないときには、n型MOSトランジスタQn1のソースを電源ラインVSSから遮断することによって、n型MOSトランジスタQn1に流れる無駄なリーク電流を抑制する。 20

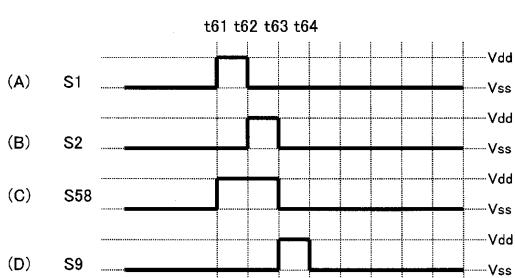

## 【0262】

次に、上述した構成を有する本実施形態に係るシフトレジスタの動作について、図35を参照して説明する。

## 【0263】

図35は、本実施形態に係るシフトレジスタにおける各部の信号波形の一例を示す図である。 30

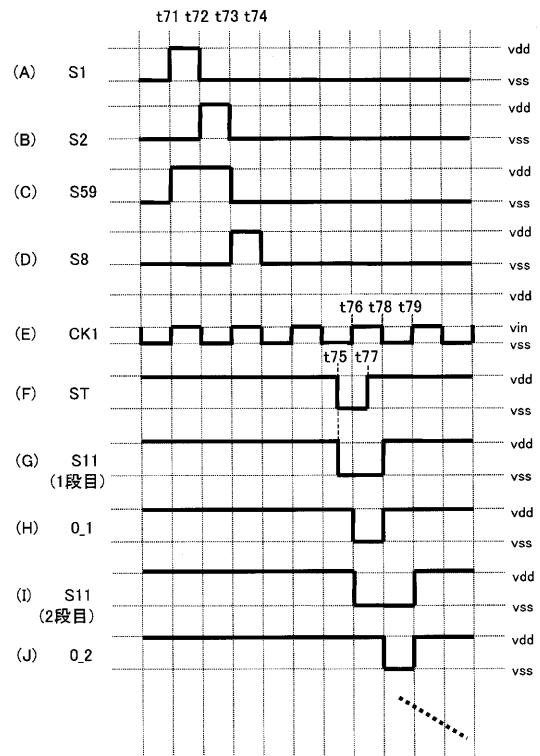

図35(A)は、制御信号S1の電圧波形を示す。

図35(B)は、制御信号S2の電圧波形を示す。

図35(C)は、制御信号S59の電圧波形を示す。

図35(D)は、制御信号S8の電圧波形を示す。

図35(E)は、クロック信号CK1の電圧波形を示す。

図35(F)は、スタート信号STの電圧波形を示す。

図35(G)は、1段目のシフト段SR2\_1の内部で生成される制御信号S11の電圧波形を示す。 40

図35(H)は、1段目のシフト段SR2\_1の出力信号O\_1を示す。

図35(I)は、2段目のシフト段SR2\_2の内部で生成される制御信号S11の電圧波形を示す。

図35(J)は、2段目のシフト段SR2\_2の出力信号O\_2を示す。

## 【0264】

図35に示す時刻t71～t74の期間では、図18に示す時刻t41～t44と同様な動作によって、各シフト段(SR2\_1, SR2\_2, ...)に含まれるレベルシフト回路LS2(LS2')が初期化される。

すなわち、第1の期間(t71～t72)においては、ノードNAが電圧‘VSS’、ノードNBが‘電圧VDD’に設定される。第2の期間(t72～t73)においては、 50

ノードN Aが電圧‘V D D - V t h p ( Q p 1 )’に設定され、ノードN Bが電圧‘V S S + V t h n ( Q n 1 )’に設定される。第6の期間(t 7 3 ~ t 7 4)においては、ノードN Aが電圧‘V D D - V t h n ( Q p 1 ) - V i n ’に設定される。

### 【0265】

シフト動作を行う前の初期状態において、各シフト段(S R 2 \_ 1, S R 2 \_ 2, ...)の入力信号P Rおよび出力信号O U Tは全てハイレベル(V D D)になっているものとする。

この場合、シフト段の入力信号P Rおよび出力信号O U Tがハイレベル(V D D)になるため、シフト段内部で生成される制御信号S 1 0およびS 1 1は全てハイレベル(V D D)になる。

制御信号S 1 0およびS 1 1がハイレベルになると、レベルシフト回路のノードN Eに電圧‘V S S’が供給される。ノードN Eが電圧‘V S S’になると、図18に示すように、ノードN A, N Bの電圧設定を行う第1および第2の期間(t 7 1 ~ t 7 3)を除いて、出力信号Oがハイレベル(V D D)になる。

ノードN A, N Bの電圧設定を行う第1および第2の期間(t 7 1 ~ t 7 3)では、レベルシフト回路の出力に接続されるトランスマジックゲート(Q n 1 0 1, Q p 1 0 1)がオフし、p型MOSトランジスタQ p 1 0 2がオンすることにより、シフト段の出力信号O U Tはハイレベル(V D D)になる。

したがって、シフト動作を行う前の初期状態において、各シフト段の入出力信号はハイレベル(V D D)に保たれる。

### 【0266】

時刻t 7 1 ~ t 7 4におけるレベルシフト回路の初期化が終了すると、シフトレジスタの1段目のシフト段S R 2 \_ 1にローレベル(V S S)のパルスがスタート信号S Tとして入力される。このパルスは、例えば図35(F)に示すように、クロック信号C K 1のローレベル(V S S)からハイレベル(V i n)への立ち上がり時(t 7 6)においてローレベル(V S S)となり、かつクロック信号C K 1の1サイクルの期間よりパルス幅が短くなるように生成される(t 7 5 ~ t 7 7)。

### 【0267】