(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7022511号**

**(P7022511)**

(45)発行日 令和4年2月18日(2022.2.18)

(24)登録日 令和4年2月9日(2022.2.9)

(51)国際特許分類

|         |                 |     |         |       |         |

|---------|-----------------|-----|---------|-------|---------|

| G 0 6 F | 12/00 (2006.01) | F I | G 0 6 F | 12/00 | 5 5 0 B |

| G 0 6 F | 12/06 (2006.01) |     | G 0 6 F | 12/06 | 5 2 4   |

請求項の数 17 (全34頁)

|                   |                                  |          |                                                                                                                                                                             |

|-------------------|----------------------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (21)出願番号          | 特願2017-33466(P2017-33466)        | (73)特許権者 | 390019839<br>三星電子株式会社<br>Samsung Electronics<br>Co., Ltd.<br>大韓民国京畿道水原市靈通区三星路12<br>9<br>129, Samsung-ro, Yeo<br>ngtong-gu, Suwon-si<br>, Gyeonggi-do, Repub<br>lic of Korea |

| (22)出願日           | 平成29年2月24日(2017.2.24)            |          |                                                                                                                                                                             |

| (65)公開番号          | 特開2017-157214(P2017-157214<br>A) |          |                                                                                                                                                                             |

| (43)公開日           | 平成29年9月7日(2017.9.7)              |          |                                                                                                                                                                             |

| 審査請求日             | 令和2年1月23日(2020.1.23)             | (74)代理人  | 110000051<br>特許業務法人共生国際特許事務所                                                                                                                                                |

| 審判番号              | 不服2021-6195(P2021-6195/J1)       | (72)発明者  | 張牧天<br>アメリカ合衆国, 95051 カリフォ<br>ルニア州, サンタクララ, ビア トリノ<br>最終頁に続く                                                                                                                |

| 審判請求日             | 令和3年5月14日(2021.5.14)             |          |                                                                                                                                                                             |

| (31)優先権主張番号       | 62/303,352                       |          |                                                                                                                                                                             |

| (32)優先日           | 平成28年3月3日(2016.3.3)              |          |                                                                                                                                                                             |

| (33)優先権主張国・地域又は機関 | 米国(US)                           |          |                                                                                                                                                                             |

| (31)優先権主張番号       | 62/303,343                       |          |                                                                                                                                                                             |

| (32)優先日           | 平成28年3月3日(2016.3.3)              |          |                                                                                                                                                                             |

| (33)優先権主張国・地域又は機関 | 最終頁に続く                           |          |                                                                                                                                                                             |

(54)【発明の名称】 インモジュール機能を遂行するメモリモジュール

**(57)【特許請求の範囲】****【請求項1】**

メモリアレイと、

前記メモリアレイをホスト装置にインターフェイス (interface) するために前記メモリアレイに連結されたインターフェイスと、

前記メモリアレイ及び前記インターフェイスに連結されたコントローラと、を備え、

前記インターフェイスは、前記メモリアレイのフィードバック状態情報を前記ホスト装置にインターフェイスするために標準のDIMM (Dual In-Line Memory Module) ピンアウト (pin out) 構成から用途変更された複数のコネクション (connection) を含み、

前記コントローラは、前記メモリアレイのエラー訂正動作を制御し、そして前記インターフェイスを通じて前記ホスト装置からコマンド (command) を受信し、前記受信されたコマンドに応答して、前記エラー訂正動作の結果に関連するフィードバック状態情報を前記インターフェイスの前記用途変更された複数のコネクションを通じて前記ホスト装置に提供し、前記エラー訂正動作の結果が失敗である場合に措置を遂行するように前記ホスト装置に指示するフィードバック状態情報を前記インターフェイスの前記用途変更された複数のコネクションを通じて前記ホスト装置に提供するように前記インターフェイスを制御し、

前記フィードバック状態情報は、前記ホスト装置に無効アクセスを通知して前記メモリアレイと前記ホスト装置との間の動作を調整するために使用され、無効理由のカテゴリー

アドレス、及びヒントに関連した情報を含むことを特徴とするメモリモジュール。

**【請求項 2】**

前記コントローラは、前記メモリアレイのリフレッシュ動作をさらに制御し、前記メモリアレイの前記リフレッシュ動作の間、前記リフレッシュ動作が遂行中であることを示すフィードバック状態情報を前記インターフェイスの前記用途変更された複数のコネクションを通じて前記ホスト装置に提供するように前記インターフェイスを制御することを特徴とする請求項 1 に記載のメモリモジュール。

**【請求項 3】**

前記コントローラは、前記メモリアレイのリフレッシュ動作をさらに制御し、前記メモリアレイの前記リフレッシュ動作の間、フィードバック状態情報を前記インターフェイスの前記用途変更された複数のコネクションを通じて前記ホスト装置に提供するように前記インターフェイスを制御し、

10

前記フィードバック状態情報は、ランク識別 (Rank Identification) 及びバンク識別 (Bank Identification) が現在リフレッシュ動作中であることを示し、前記リフレッシュ動作が完了すると、前記ホスト装置に完了したことを知らせることを特徴とする請求項 1 に記載のメモリモジュール。

**【請求項 4】**

前記コントローラは、前記メモリアレイのスクラビング動作をさらに制御し、前記スクラビング動作が遂行中であることを示すフィードバック状態情報を前記インターフェイスの前記用途変更された複数のコネクションを通じて前記ホスト装置に提供するように前記インターフェイスを制御することを特徴とする請求項 1 に記載のメモリモジュール。

20

**【請求項 5】**

前記メモリアレイは、複数の不揮発性メモリセルを含み、

前記コントローラは、前記メモリアレイのウェアレベリング動作をさらに制御し、前記ウェアレベリング動作が遂行中であることを示すフィードバック状態情報を前記インターフェイスの前記用途変更された複数のコネクションを通じて前記ホスト装置に提供するように前記インターフェイスを制御することを特徴とする請求項 1 に記載のメモリモジュール。

**【請求項 6】**

前記メモリアレイは、複数の不揮発性メモリセルを含み、

前記コントローラは、前記メモリアレイのウェアレベリング動作をさらに制御し、フィードバック状態情報を前記インターフェイスの前記用途変更された複数のコネクションを通じて前記ホスト装置に提供するように前記インターフェイスをさらに制御し、

30

前記フィードバック状態情報は、前記ウェアレベリング動作が遂行中であることを示すことを特徴とする請求項 1 に記載のメモリモジュール。

**【請求項 7】**

DRAM (Dynamic Random Access Memory) 及び複数の NV RAM (Non-Volatile Random Access Memory) を含むメモリセルのアレイを含み、DIMM (Dual In-Line Memory Module) で構成されたメモリアレイと、

前記メモリアレイに連結されたコントローラと、を備え、

40

前記DIMMは、前記メモリアレイの動作状態をホスト装置にインターフェイスするように標準のDIMMピンアウト構成で用途変更された複数のコネクション (connection) を含み、

前記コントローラは、前記メモリアレイのウェアレベリング (wear-leveling) 動作を制御し、ウェアレベリング動作が遂行中であることを示すフィードバック状態情報、及び前記ウェアレベリング動作中に別の動作をスケジュールするよう前記ホスト装置に指示するフィードバック状態情報を、標準のDIMMピンアウト構成で用途変更された複数のコネクションを含むインターフェイスのうちの前記用途変更された複数のコネクションを通じて前記ホスト装置に提供し、

前記フィードバック状態情報は、前記ホスト装置に無効アクセスを通知して前記メモリ

50

アレイと前記ホスト装置との間の動作を調整するために使用され、無効理由のカテゴリーアドレス、及びヒントに関連した情報を含むことを特徴とするメモリモジュール。

【請求項 8】

前記コントローラは、前記メモリアレイのリフレッシュ動作をさらに制御し、前記リフレッシュ動作が発生したことのフィードバック状態情報を前記インターフェイスの前記用途変更された複数のコネクションを通じて前記ホスト装置に提供することを特徴とする請求項 7 に記載のメモリモジュール。

【請求項 9】

前記コントローラは、前記メモリアレイのエラー訂正動作をさらに制御し、前記エラー訂正動作が完了したこと及び前記エラー訂正動作の結果を示すフィードバック状態情報を前記インターフェイスの前記用途変更された複数のコネクションを通じて前記ホスト装置に提供することを特徴とする請求項 7 に記載のメモリモジュール。

10

【請求項 10】

前記コントローラは、前記メモリアレイのスクラビング動作をさらに制御し、前記スクラビング動作が発生したことを示すフィードバック状態情報を前記インターフェイスの前記用途変更された複数のコネクションを通じて前記ホスト装置に提供することを特徴とする請求項 7 に記載のメモリモジュール。

【請求項 11】

メモリセルのアレイを含むメモリアレイと、

インターフェイスと、

20

前記メモリアレイ及び前記インターフェイスに連結されたコントローラと、を備え、

前記メモリアレイは、前記メモリアレイの動作状態をホスト装置にインターフェイスする

ように標準のDIMMピンアウト構成で用途変更された複数のコネクションを含むDIMMで構成され、

前記インターフェイスは、前記メモリアレイを前記ホスト装置にインターフェイス(*interface*)するために前記DIMMの複数のコネクションを含んで前記メモリアレイに連結され、

前記コントローラは、前記メモリアレイのリフレッシュ動作、前記メモリアレイのエラー訂正動作、前記メモリアレイのスクラビング(*scrubbing*)動作、及び前記メモリアレイのウェアレベリング(*wear-leveling*)動作のうちの少なくとも1つを制御し、前記インターフェイスを通じて前記ホスト装置からコマンドを受信し、前記受信したコマンドに応答して、前記コントローラによって制御される動作に関連するホスト装置にフィードバック状態情報を前記インターフェイスのうちの前記標準のDIMMピンアウト構成で用途変更された複数のコネクションを通じて提供し、

30

前記フィードバック状態情報は、前記ホスト装置に無効アクセスを通知して前記メモリアレイと前記ホスト装置との間の動作を調整するために使用され、無効理由のカテゴリーアドレス、及びヒントに関連した情報を含むことを特徴とするメモリモジュール。

【請求項 12】

前記コントローラは、前記メモリアレイの前記リフレッシュ動作を制御し、前記メモリアレイの前記リフレッシュ動作の間、前記リフレッシュ動作が遂行中であることを示すフィードバック状態情報を前記インターフェイスの前記用途変更された複数のコネクションを通じて前記ホスト装置に提供するように前記インターフェイスをさらに制御することを特徴とする請求項 1 に記載のメモリモジュール。

40

【請求項 13】

前記コントローラは、前記メモリアレイの前記エラー訂正動作を制御し、前記エラー訂正動作の結果を示すフィードバック状態情報を前記インターフェイスの前記用途変更された複数のコネクションを通じて前記ホスト装置に提供するように前記インターフェイスをさらに制御することを特徴とする請求項 1 に記載のメモリモジュール。

【請求項 14】

前記コントローラは、前記エラー訂正動作の結果が失敗(*failure*)である場合に

50

措置を遂行するように、前記ホスト装置に指示するフィードバック状態情報を前記インターフェイスの前記用途変更された複数のコネクションを通じて前記ホスト装置に提供するように前記インターフェイスをさらに制御することを特徴とする請求項13に記載のメモリモジュール。

**【請求項15】**

前記コントローラは、前記メモリアレイの前記スクラビング動作を制御し、前記スクラビング動作が遂行中であることを示すフィードバック状態情報を前記インターフェイスの前記用途変更された複数のコネクションを通じて前記ホスト装置に提供するように前記インターフェイスをさらに制御することを特徴とする請求項11に記載のメモリモジュール。

**【請求項16】**

前記メモリアレイは、複数の不揮発性メモリセルを含み、

前記コントローラは、前記メモリアレイの前記ウェアレベリング動作を制御し、前記ウェアレベリング動作が遂行中であることを示すフィードバック状態情報を前記インターフェイスの前記用途変更された複数のコネクションを通じて前記ホスト装置に提供するように前記インターフェイスをさらに制御することを特徴とする請求項11に記載のメモリモジュール。

**【請求項17】**

複数の不揮発性メモリセルを含むメモリアレイと、

前記メモリアレイをホスト装置にインターフェイス(interface)するために前記メモリアレイに連結されたインターフェイスと、

前記メモリアレイ及び前記インターフェイスに連結されたコントローラと、を備え、

前記インターフェイスは、前記メモリアレイのフィードバック状態情報を前記ホスト装置にインターフェイスするために標準のDIMM(Dual In-Line Memory Module)ピンアウト(pin out)構成から用途変更された複数のコネクション(connection)を含み、

前記コントローラは、前記メモリアレイのウェアレベリング(wear-leveling)動作を制御し、そして前記インターフェイスを通じて前記ホスト装置からコマンド(command)を受信し、前記受信されたコマンドに応答して、前記ウェアレベリング動作が遂行中であることを示すフィードバック状態情報、及び前記ウェアレベリング動作中に別の動作をスケジュールするように前記ホスト装置に指示するフィードバック状態情報を前記インターフェイスの前記用途変更された複数のコネクションを通じて前記ホスト装置に提供するように前記インターフェイスを制御し、

前記フィードバック状態情報は、前記ホスト装置に無効アクセスを通知して前記メモリアレイと前記ホスト装置との間の動作を調整するために使用され、無効理由のカテゴリーアドレス、及びヒントに関連した情報を含むことを特徴とするメモリモジュール。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、メモリシステムに関し、より詳しくはインモジュール機能を遂行するメモリモジュールに関する。

**【背景技術】**

**【0002】**

メモリのRAS(Reliability Availability Serviceability)機能は、従来、CPU(Central Processing Unit)及び/又はメモリコントローラ(MC:Memory Controller)によってシステムレベルで遂行されるか又は管理されてきた。一部の構成では、CPUとメモリコントローラとはホストシステムの分離された要素で構成される。他の構成では、CPUとメモリコントローラとは一体に集積された形態で構成される。本明細書で使用する略語「CPU/MC」は、CPU及び/又はメモリコントローラ(MC)を意味する。例えば、CPU/MCは、従来、DRAM(Dynamic Random Access Me

10

20

30

40

50

mory) のリフレッシュ動作を遂行するために、システムメモリのDRAMにリフレッシュコマンドを伝送してきた。また、ECC( Error Correcting Code )を使用するエラー訂正是、従来、個別のメモリ位置を読み出し、ECCを使用してデータを訂正し、そして訂正されたデータを再書き込みするCPU/MCによって遂行された。

#### 【0003】

従来、CPU/MCによって遂行されるメモリの他のRAS機能は、システムメモリの「スクラビング(scrubbing)」である。CPU/MCは、システムメモリ内で周期的にシステムメモリの領域を読み出し、(ECCを使用して)エラーを訂正し、そして訂正されたデータを再びシステムメモリの該当領域に書き込む。従来、CPU/MCによって遂行されるさらに他のRAS機能は、ウェアレベリング(wear-leveling)管理である。例えば、不揮発性メモリ内のウェア(wear)水準を均等に調節するために、CPU/MCは書き込み及び読出しコマンドを利用してメモリページを交換(swap)するように書き込みカウント(write-count)テーブル及びリマップ(remap)テーブルを利用して不揮発性メモリのメモリページをリマッピング(remapping)する。

10

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0004】

本発明は、上記従来の問題点に鑑みてなされたものであって、本発明の目的は、インモジュールリフレッシュ機能、インモジュールECC機能、インモジュールスクラビング、及びインモジュールウェアレベリング管理機能を含むインモジュール機能を遂行するメモリモジュールを提供することにある。

20

#### 【課題を解決するための手段】

#### 【0005】

上記目的を達成するためになされた本発明の一態様によるメモリモジュールは、メモリアレイと、前記メモリアレイをホスト装置にインターフェイス(interface)するためにメモリアレイに連結されたインターフェイスと、前記メモリアレイ及び前記インターフェイスに連結されたコントローラと、を備え、前記インターフェイスは、前記メモリアレイのフィードバック状態情報を前記ホスト装置にインターフェイスするために標準のDIMM(Dual In-Line Memory Module)ピンアウト(pinout)構成から用途変更された複数のコネクション(connection)を含み、前記コントローラは、前記メモリアレイの少なくとも1つのリフレッシュ動作を制御し、前記メモリアレイのエラー訂正動作を制御し、前記メモリアレイのメモリスクラビング(scrubbing)動作を制御し、前記メモリアレイのウェアレベリング(wear-leveling)コントロール動作を制御し、前記インターフェイスを通じて前記ホスト装置からコマンド(command)を受信し、前記受信されたコマンドに応答してコマンドが受信される時に前記コントローラによって制御される動作に関連する前記インターフェイスを通じて前記ホスト装置にフィードバック状態情報を提供することを特徴とする。

30

#### 【0006】

上記目的を達成するためになされた本発明の他の態様によるメモリモジュールは、DRAM(Dynamic Random Access Memroy)及びNVRAM(Non-Volatile Random Access Memory)を含むメモリセルのアレイを含み、DIMM(Dual In-Line Memory Module)で構成されたメモリアレイと、前記メモリアレイに連結されたコントローラと、を備え、前記コントローラは、前記メモリアレイの少なくとも1つのリフレッシュ動作を制御し、前記メモリアレイのエラー訂正動作を制御し、前記メモリアレイのメモリスクラビング(scrubbing)動作を制御し、前記メモリアレイのウェアレベリング(wear-leveling)コントロール動作を制御し、前記コントローラによって制御される動作と

40

50

関連されたホスト装置にインターフェイスを通じてフィードバック状態情報を提供し、前記インターフェイスは、標準のDIMMピンアウト構成で用途変更された複数のコネクションを含むことを特徴とする。

**【0007】**

上記目的を達成するためになされた本発明のさらに他の態様によるメモリモジュールは、メモリセルのアレイを含むメモリアレイと、インターフェイスと、前記メモリアレイ及び前記インターフェイスに連結されたコントローラと、を備え、前記メモリアレイは、前記メモリアレイの動作状態をホスト装置にインターフェイスするように標準のDIMMピンアウト構成で用途変更された複数のコネクションを含むDIMMで構成され、前記インターフェイスは、前記メモリアレイを前記ホスト装置にインターフェイス(*interface*)するために前記DIMMの複数のコネクションを含んで前記メモリアレイに連結され、前記コントローラは、前記メモリアレイの少なくとも1つのリフレッシュ動作を制御し、前記メモリアレイのエラー訂正動作を制御し、前記メモリアレイのメモリスクラビング(*scrubbing*)動作を制御し、前記メモリアレイのウェアレベリング(*wear-leveling*)コントロール動作を制御することを特徴とする。10

**【発明の効果】**

**【0008】**

本発明によれば、メモリモジュールは、インモジュールリフレッシュ機能、インモジュールECC機能、インモジュールスクラビング、及びインモジュールウェアレベリング管理機能を支援することができる。また、インモジュールRAS機能を使用してシステムの安定性及び性能を向上させ、電力消耗を減少させる効果を奏する。20

**【図面の簡単な説明】**

**【0009】**

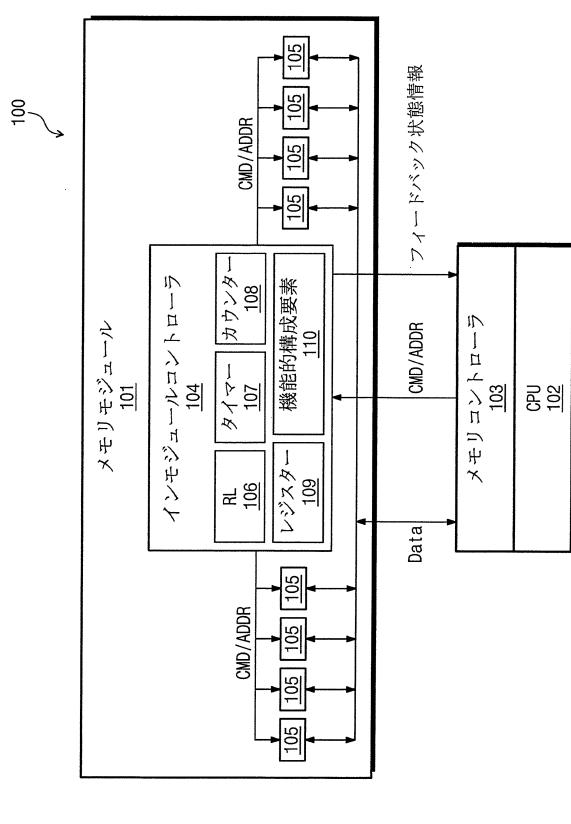

【図1】本発明の一実施形態によるメモリモジュールを含むシステムの機能ブロック図である。

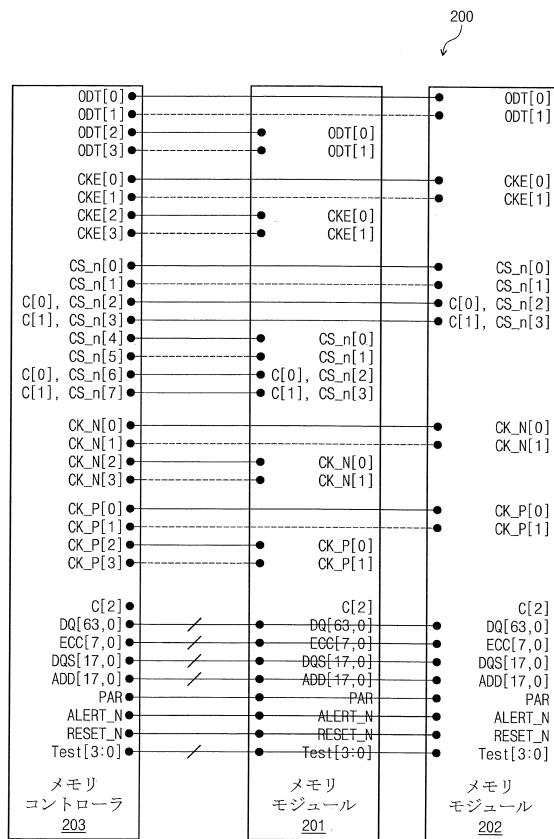

【図2】本発明の一実施形態による選択されたピンがRASフィードバック状態情報を伝送するように用途変更されたメモリチャンネル内のメモリモジュールコネクターのピンアウト(*pinout*)を示す図である。

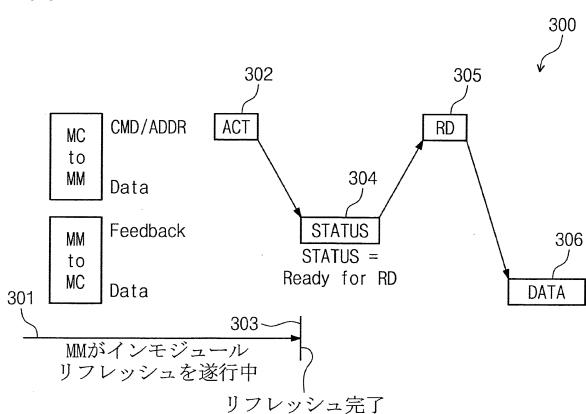

【図3】本発明の一実施形態によるメモリモジュールがインモジュール(*in-module*)リフレッシュ動作を遂行するように動作調整(*coordination*)を提供するためのメモリコントローラとメモリモジュールとの間の信号シーケンス(*sequence*)を示す図である。30

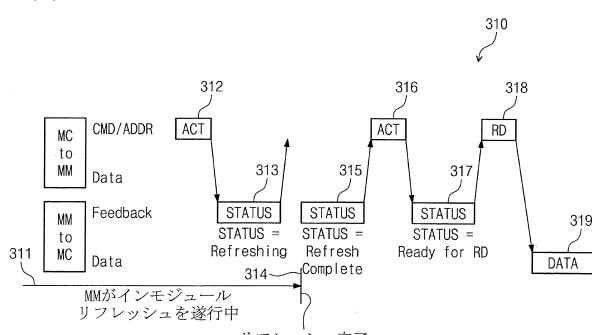

【図4】本発明の他の実施形態によるメモリモジュールがインモジュールリフレッシュ機能を遂行するように動作調整を提供するためのメモリコントローラとメモリモジュールとの間の信号シーケンスを示す図である。

【図5】本発明の一実施形態によるメモリモジュールがインモジュールECC動作を遂行するように動作調整を提供するためのメモリコントローラとメモリモジュールとの間の信号シーケンスを示す図である。

【図6】本発明の他の実施形態によるメモリがインモジュールECC動作を遂行し、その結果、エラー訂正失敗が発生するように動作調整を提供するためのメモリコントローラとメモリモジュールとの間の信号シーケンスを示す図である。40

【図7】本発明の一実施形態によるメモリモジュールがインモジュールスクラビング(*scrubbing*)動作を遂行するように動作調整を提供するためのメモリモジュールとメモリコントローラとの間の信号シーケンスを示す図である。

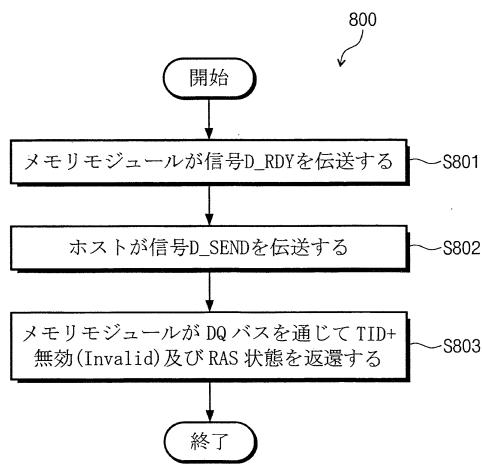

【図8】本発明の他の実施形態によるメモリモジュールがインモジュールスクラビングを遂行するように動作調整を提供するためのメモリモジュールとメモリコントローラとの間の信号シーケンスを示す図である。

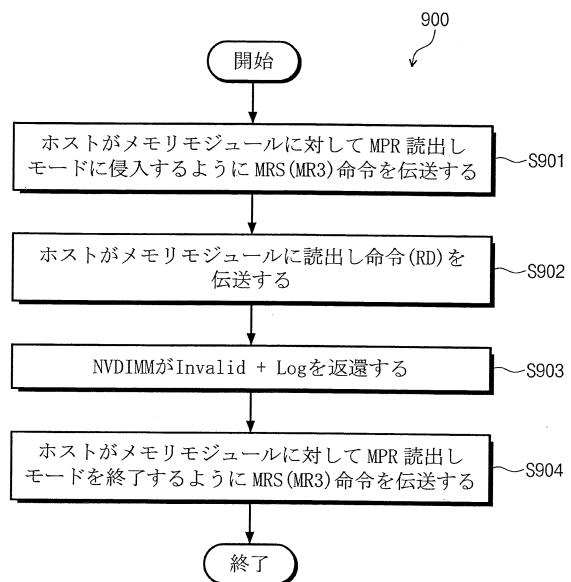

【図9】本発明のその他の実施形態によるメモリモジュールがインモジュールスクラビングを遂行するように動作調整を提供するためのメモリモジュールとメモリコントローラとの間の信号シーケンスを示す図である。50

【図10】本発明の一実施形態によるメモリモジュールがインモジュールウェアレベリング(wear-leveling)を遂行するように動作調整を提供するためのメモリモジュールとメモリコントローラとの間の信号シーケンスを示す図である。

【図11】本発明の他の実施形態によるメモリモジュールがインモジュールウェアレベリングを遂行するように動作調整を提供するためのメモリモジュールとメモリコントローラとの間の信号シーケンスを示す図である。

【図12】本発明の一実施形態によるDQ(データ)バスを通じてRASフィードバック状態メッセージが伝送されるCPU/MCとメモリモジュールとの間のインターフェイスを示す図である。

【図13】本発明の一実施形態によるDQバスを通じてRASフィードバック状態メッセージが伝送される方法を示すフローチャートである。 10

【図14】本発明の一実施形態によるRASフィードバック状態メッセージを読み出すようにMRSコマンドを利用してメモリモジュールを構成する方法を示すフローチャートである。

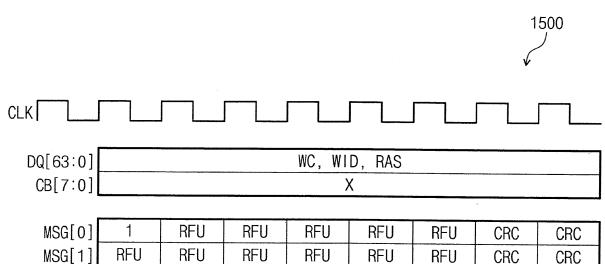

【図15】本発明の一実施形態によるDQバスがフィードバック状態情報を伝送するために使用される場合のRASフィードバック状態メッセージの配列を示す図である。

【図16】本発明の一実施形態によるD\_RDY信号として使用されるALERT\_nピンを示す信号図である。

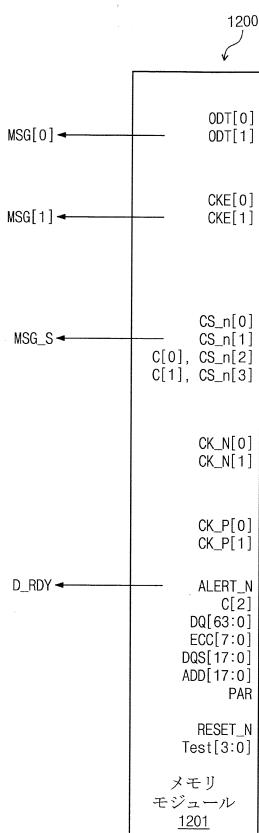

【図17】本発明の他の実施形態による選択されたピンがD\_RDY信号と関連された状態情報(例えば、キャッシュ情報等)を伝送するように用途が変更されたメモリチャンネル内のメモリモジュールコネクターのピンアウトを示す図である。 20

【図18】本発明の一実施形態によるTB(Transaction Burst)命令を示す信号フローチャートである。

【図19】本発明の一実施形態によるTS(Transaction Status)メッセージを示す信号フローチャートである。

【図20】本発明の一実施形態によるRS(Read Status)リターンメッセージの配列を示す図である。

【図21】本発明の一実施形態によるインモジュールリフレッシュ機能、インモジュールECC機能、インモジュールスクラビング、及び/又はインモジュールウェアレベリング管理を制御するか、又は支援し、動作調整をホスト装置に提供するメモリモジュールを含む電子装置を示すブロック図である。 30

【図22】本発明の一実施形態によるインモジュールリフレッシュ機能、インモジュールECC機能、インモジュールスクラビング、及び/又はインモジュールウェアレベリング管理を制御するか、又は支援し、動作調整をホスト装置に提供するメモリモジュールを含むメモリシステムを示すブロック図である。

#### 【発明を実施するための形態】

##### 【0010】

本明細書に記載の発明は、インモジュールリフレッシュ機能、インモジュールECC機能、インモジュールスクラビング、及び/又はインモジュールウェアレベリング管理を制御するか又は支援し、動作調整をホスト装置に提供するメモリモジュールに関する。 40

##### 【0011】

以下、本発明を実施するための形態の具体例を、図面を参照しながら詳細に説明する。しかし、当業者には本明細書に開示された様相(aspect)をこのような特定の細部事項が無くても実施可能である。なお、広く公知された方法、手続、構成要素、及び回路は、本明細書に開示された発明を曖昧にしないよう詳細には説明しない。

##### 【0012】

本明細書に記載された「一実施形態」又は「1つの実施形態」を参照することは、特定の特徴、構造、又は機能が本明細書に記載された少なくとも1つの実施形態に含まれた実施形態に関連して説明されることを意味する。したがって、本明細書にわたって多様な部分に記載された「一実施形態内の」、「1つの実施形態内の」、又は「一実施形態を参照し

10

20

30

40

50

て」等の句節（又は、類似の意味を内包する他の句節）は、必ず全て同一の実施形態を指すものではない。

#### 【0013】

本明細書で使用される「例示的な」という単語は、「例（example、instance）又は図示（illustration）として提供される」ということを意味する。また、特定の特徴、構造、又は機能は、1つ又は1つ以上の実施形態で任意の適切な方式に組み合せることができる。明細書上の文脈にしたがって、単数用語は対応する複数形態を含み、複数用語は該当する単数形態を含む。さらに、本明細書に図示され記載される構成要素ダイヤグラムを含む多様な図面は单なる例示的な目的のものであり、スケールに合うように図示されたものではない。同様に、多様な波形（waveform）とタイミング図とは单なる例示的な目的で図示される。

10

#### 【0014】

本明細書で使用される「第1」、「第2」等の用語は、先行する名詞に対するラベル（label）として使用され、順序が明示的に定義されない限り、何らかの形態（即ち、空間的、時間的、論理的等）の順序を暗示するものではない。その上で、同一の参照番号は、同一又は類似する機能を有する部品、構成要素、ブロック、回路、ユニット、又はモジュールに関連する2つ以上の図面にわたって使用される。但し、このような使用は、単に図示の単純化と説明の簡易化のためである。該当する構成、その構成要素、又はユニットの構造的な細部事項が、全ての実施形態で同一ではない。また、このような使用は、共通に参照されるパーツ／モジュールが本明細書に開示された特定の実施形態を具現する唯一の方法を意味するものではない。

20

#### 【0015】

本明細書で使用される「モジュール（module）」という用語は、個別的又は集合的により大きいシステムの一部として具現される回路を意味する。例えば、より大きいシステムの一部は、IC（Integrated Circuit）、1つ以上の集積回路として具現された回路を含むアセンブリ（assembly）、SOC（System On Chip）等を含む。但し、より大きいシステムの例は、これに制限されるものではない。本明細書で使用される「中央処理ユニット」、「CPU」、「メモリコントローラ」、「MC」、及び「CPU/MC」の用語及び略語（acronyms）は、CPU及び／又はMCのホストシステム機能を提供する1つ以上の装置を意味する。また、「中央処理ユニット」、「CPU」、「メモリコントローラ」、「MC」、及び「CPU/MC」の用語及び略語は、文脈にしたがって交替されて使用される。

30

#### 【0016】

本明細書に記載された発明は、インモジュールリフレッシュ機能、インモジュールECC機能、インモジュールスクラビング、及び／又はインモジュールウェアレベリング管理を制御するか又は支援し、動作調整をホスト装置に提供するメモリモジュールに関する。一実施形態として、インモジュールRAS機能を使用してシステムの信頼性、性能、電力消耗、システムヘルス（system health）を向上させ、又は維持するために、本明細書に開示されたメモリモジュールは、メモリモジュールとCPU/MCとの間の調整を提供する。他の実施形態として、インモジュールRAS機能を提供するメモリモジュールは、DIMM（Dual In-Line Memory）で具現される。さらに他の実施形態として、本明細書に開示された発明によるメモリモジュールは、初期化（initialization）の時に選択的に構成可能な調整オプションを提供する。また、例えば、システム性能及び／又はシステム電力消耗を最適化するために、本明細書に開示された発明によるメモリモジュールは、ホストCPU/MCによって使用され、選択可能な報告（report）メカニズムのコンテンツ（content）を提供する。

40

#### 【0017】

図1は、本発明の一実施形態によるメモリモジュールを含むシステムの機能ブロック図である。システム100は、メモリモジュール101以外に、ホストシステムのCPU102を含む。ホストシステムのCPU102は、CPU102と一体のメモリコントローラ

50

103を含む。なお、メモリコントローラ（以下、MCと略記）103はCPU102から分離されてもよい。

#### 【0018】

メモリモジュール101は、SDDR (Synchronous Double Data Rate)と互換性のあるNVDIMM (Non-Volatile Dual In-Line Memory Module)で具現される。他の実施形態として、メモリモジュール101は、SDDR4 (Synchronous DDR4)と互換性のあるNVDIMMで具現される。さらに他の実施形態として、メモリモジュール101は、DIMMとは異なる構成で具現される。

#### 【0019】

メモリモジュール101とCPU102/MC103とは、インターフェイスによって動作中に互いに通信可能に連結される。当該インターフェイスを通じて、CPU102/MC103は、コマンド及びアドレス(CMD/ADDR)とデータ(Data)とをメモリモジュール101に伝送し、メモリモジュール101は、データとRASフィードバック状態情報(又はメッセージ)とをCPU102/MC103に伝送する。RASフィードバック状態情報は、CPU102/MC103の動作と共にメモリモジュール101によって提供されるRAS機能を調整するために使用される。

10

#### 【0020】

メモリモジュール101は、インモジュールコントローラ104と複数のメモリチップ105とを含む。一実施形態として、複数のメモリチップ105は、不揮発性メモリチップで構成される。本実施形態で、複数のメモリチップ105の各々は、不揮発性メモリセルのアレイを含むように構成される。他の実施形態として、複数のメモリチップ105は、DRAMメモリチップで構成され、複数のメモリチップ105の各々は、DRAMメモリセルのアレイを含むように構成される。さらに他の実施形態では、複数のメモリチップ105は、1つ以上の不揮発性メモリセルアレイ(例えば、NVRAM (Non-volatile Random Access Memory))及び1つ以上のDRAMメモリセルアレイの組み合せで構成される。その他の実施形態として、1つ以上の複数のメモリチップ105は、1つ以上のDRAM-FPGAs (Dynamic Random Access Memory Field Programmable Gate Arrays)を含むように構成される。

20

#### 【0021】

インモジュールコントローラ104は、CPU102/MC103からコマンド及びアドレス情報を受信して処理し、コマンド及びアドレス情報を複数のメモリチップ105に提供する。データはCPU102/MC103及び複数のメモリチップ105の間で両方向(bi-directionally)に提供される。一実施形態では、データパス(data path)は、インモジュールコントローラ104を通過する。他の実施形態では、データはインモジュールコントローラ104を含まないバスを通過する。

30

#### 【0022】

インモジュールコントローラ104は、1つ以上のインモジュールRAS機能(例えば、インモジュールリフレッシュ機能、インモジュールECC機能、インモジュールスクラビング機能、及び/又はインモジュールウェアレベリング機能等)を提供するように構成される。インモジュールコントローラ104は、リフレッシュロジック(RL: Refresh Logic)106、1つ以上のタイマー107、1つ以上のカウンター108、1つ以上のレジスター109、及び/又は他の機能的構成要素110を含む。例えば、他の機能的構成要素110は、インモジュールコントローラ104が1つ以上のインモジュールRAS機能を提供するためのテーブル、ドライバー、メモリアレイ、及びロジック等を含む。但し、他の機能的構成要素110の例はこれに制限されない。一実施形態として、インモジュールコントローラ104は、インモジュールRAS機能に関するRASフィードバック状態情報をCPU102/MC103に提供するように構成される。RASフィードバック状態情報は、メモリモジュール101とCPU102/MC103との動作

40

50

を調整する。他の実施形態として、メモリモジュール101は、図12～図15を参照して説明するデータバスにしたがってRASフィードバック状態情報を提供するように構成される。

#### 【0023】

メモリモジュール101がNVDIMMで構成された実施形態において、メモリモジュール101は、メモリモジュール101によって提供されたインモジュールRAS機能に関連するRASフィードバック状態情報を伝送するように用途が変更されたコネクター上のピン（又は、コネクション（connection））を含む。例えば、一実施形態として、メモリモジュールコネクターの5個のピンは、RASフィードバック状態情報を伝送するように用途が変更される。他の実施形態として、メモリモジュールコネクターの8個のピンは、RASフィードバック状態情報を伝送するように用途が変更される。さらに他の実施形態では、用途が変更されたコネクターピンの数は、上述の実施形態によるメモリモジュールコネクターの5個又は8個のピンとは異なる。本明細書で使用される「用途を変更する」及び「用途変更された」の用語は、コネクターピンの信号方向及び機能が該当ピンに対して従前に設定された機能及び信号方向から変更されたことを意味する。

10

#### 【0024】

図2は、本発明の一実施形態による選択されたピンがRASフィードバック状態情報を伝送するように用途変更されたメモリチャンネル内のメモリモジュールコネクターのピンアウト（pinout）を示す図である。より具体的に、図2は、メモリチャンネル200の2つのメモリモジュール（201、202）の例示的なピンアウトを示す。図2に示す実施形態で、2つのメモリモジュール（201、202）のメモリモジュールコネクターの5個のピンは、メモリコントローラ203にRASフィードバック状態情報を伝送するように用途変更されている。図2ではメモリコントローラ203を図示したが、メモリコントローラ203は、CPU及び/又は内装メモリコントローラを含むCPUによって代替されることは容易に理解される。

20

#### 【0025】

図2に点線で示したように、5個の例示的なコネクターピン（ODT[1]、CKE[1]、CS\_n[1]、CK\_N[1]、及びCK\_P[1]）は、メモリコントローラ203にRASフィードバック状態情報を伝送するように用途変更された。8個のコネクターピンがRASフィードバック状態情報をメモリコントローラに伝送するように用途変更された実施形態では、例示的なコネクターピンは（ODT[1]、CKE[1]、CS\_n[1]、CK\_N[1]、CK\_P[1]、RFU[144]（図示せず）、RFU[205]（図示せず）、及びRFU[207]（図示せず））を含む。本発明の実施形態において、メモリモジュールの他のコネクターピンがメモリコントローラにRASフィードバック状態情報を伝送するように用途変更されることは容易に理解される。用途変更されたコネクターピンに対する追加的な細部事項は全体的に本明細書の参考に引用された米国仮出願（出願番号：US62/303,349）を参照して提供される。

30

#### 【0026】

RASフィードバック状態情報が伝送されるサイクルの数は、特定メモリモジュールによって決定され、及び/又はメモリモジュールの初期化時点でCPU/MCによって選択的に構成される。伝送されるRASフィードバック状態情報の具体的な構成は、RASフィードバック状態情報が伝送されるサイクルの数にしたがって変更される。例えば、一実施形態で、図2に示すように5個のコネクターピンが用途変更された場合、RASフィードバック状態情報は3サイクルを通じて伝送される。この場合、RASフィードバック状態情報は、15ビットの情報を含む。8個のコネクターピンが用途変更された他の実施形態で、RASフィードバック状態情報は、16ビットの情報を含み、RASフィードバック状態情報を伝送するために2サイクルを使用する。サイクル数及び/又はRASフィードバック状態情報を伝達するビット数は、本明細書に記載された実施形態に制限されない。

40

#### 【0027】

RASフィードバック状態情報は、CPU/MCに無効（invalid）アクセスにを

50

通知してメモリモジュールとCPU/MCとの間の動作を調整するために使用され、及び/又は記録された(logged)統計を報告するために使用される。さらに、RASフィードバック状態情報は、原因(reason)のカテゴリー、アドレス、及びヒントに関連した情報を含む。これは表2、表4～表7を参照して詳細に説明される。

#### 【0028】

表1は、用途変更された5個のコネクターピンを含む第1実施例に対する一部の情報と、用途変更された8個のコネクターピンを含む第2実施例に対する対照的な情報を示す。用途変更されたコネクターピンに対する追加的な細部事項は、本明細書の参考に引用された上述の米国仮出願(出願番号:US 6 2 / 3 0 3 , 3 4 9 )を参照して提供される。

#### 【0029】

##### 【表1】

コネクターピン用途変更の第1及び第2実施例

| フィードバック状態情報に対して使用可能なピンの総数 | 5                                                                                                                 | 8                                                                                                                 |

|---------------------------|-------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|

| フィードバック状態情報に対して用途変更されたピン  | ODT[1], CKE[1], CS_n[1], CK_N[1] and CK_P[1]                                                                      | ODT[1], CKE[1], CS_n[1], CK_N[1], CK_P[1], RFU[144], RFU[205] and RFU[207]                                        |

| 速度                        | Single Data Rate                                                                                                  | Single Data Rate                                                                                                  |

| フィードバックレイテンシ(Latency)     | 3 cycles                                                                                                          | 2 cycles                                                                                                          |

| ランクアドレスに対して用途変更されたピン      | [CS2_n, C0]→[CS1_n, C0]<br>C2→[CS3_n, C2]<br>[CS3_n, C1]→[CS2_n, C1]                                              | [CS3_n, C1]→[CS1_n, C1]<br>C2→[CS3_n, C2]                                                                         |

| 制限(Limitation)            | No DDP Support<br>4 Rank/Channel<br>Maximum 8 Logic R/C<br>Support:<br>1 Rank x 1-4 Stacks<br>1-4 Rank x 1 Stacks | No DDP Support<br>4 Rank/Channel<br>Maximum 8 Logic R/C<br>Support:<br>1 Rank x 1-4 Stacks<br>1-4 Rank x 1 Stacks |

| コメント(Comment)             | Can have up to 8 R/C with changes in JEDEC 3D stack organization                                                  | Can have up to 8 R/C with changes in JEDEC 3D stack organization                                                  |

#### 【0030】

図3は、本発明の一実施形態によるメモリモジュールがインモジュール(in-module)リフレッシュ動作を遂行するように動作調整(coordination)を提供するためのメモリコントローラとメモリモジュールとの間の信号シーケンス(sequence)を示す図である。

#### 【0031】

図4は、本発明の他の実施形態によるメモリモジュールがインモジュールリフレッシュ動作を遂行するように動作調整を提供するためのメモリコントローラとメモリモジュールとの間の信号シーケンスを示す図である。

#### 【0032】

本実施形態で、図3及び図4の各々の信号シーケンスは、メモリモジュールの初期化時点

10

20

30

40

50

で選択可能である。図3の信号シーケンス300において、インモジュールリフレッシュ動作はメモリコントローラに対して透過的である。これはメモリモジュールがリフレッシュ動作を完了するために活性化(activate)命令を無視するためである。メモリコントローラの観点で、活性化命令を完了し、メモリコントローラが読出し又は書込み命令を発行(issue)するのにより長い時間が掛かるだけである。

#### 【0033】

図4の信号シーケンス310で、インモジュールリフレッシュ動作は、メモリコントローラから受信した活性化命令に応答してリフレッシュ動作が進行中であることを示すフィードバック状態メッセージを提供する。応答において、メモリコントローラは、活性化命令が完了されるのを待つ間に、他の要請及び/又は動作及び/又はコンテキスト(context)のスイッチをスケジュールする。一実施形態として、メモリコントローラは、セットアップ命令を伝送する。インモジュールリフレッシュ動作中に活性化命令に応答してセットアップ命令はインモジュールコントローラを選択的に信号シーケンス300及び信号シーケンス310の中の1つが選択されるモードに配置する。一実施形態で、インモジュールリフレッシュ動作に関連したフィードバック状態メッセージの特定コンテンツはメモリモジュールの初期化時点で選択可能である。

10

#### 【0034】

図3で、同図の上の部分には、メモリコントローラMCからメモリモジュールMMに伝送される信号又はメッセージを示す。一方、下の部分には、メモリモジュールからメモリコントローラに伝送される信号又はメッセージを示す。図3の301時点で、メモリモジュールがインモジュールリフレッシュ動作を遂行することを示した。302時点で、メモリコントローラは活性化命令ACTをメモリモジュールに提供する。メモリモジュールがインモジュールリフレッシュ動作を遂行する間、活性化命令は無視され、リフレッシュ動作は中断されない。303時点で、メモリモジュールはインモジュールリフレッシュ動作を完了する。304時点で、メモリモジュールはメモリモジュールが読出し命令RDに対して準備されたことのRASフィードバック状態メッセージを伝送する。305時点で、メモリコントローラは読出し命令をメモリモジュールに伝送する。306時点で、メモリモジュールはこれに応答して受信された読出し命令に対応されるデータを出力する。

20

#### 【0035】

図4で、同図の上の部分には、メモリコントローラMCからメモリモジュールMMに伝送される信号又はメッセージを示す。一方、下の部分にはメモリモジュールからメモリコントローラに伝送される信号又はメッセージを示す。図4の311時点で、メモリモジュールはインモジュールリフレッシュ動作を遂行する。312時点で、メモリコントローラは活性化命令ACTをメモリモジュールに伝送する。313時点で、メモリモジュールはメモリモジュールがリフレッシュ動作を遂行し、メモリコントローラに対してリフレッシュ動作が完了された後に再試行することを表示するRASフィードバック状態メッセージを伝送する。メモリモジュールの動作を調整するために、メモリコントローラはリフレッシュ動作が完了する時まで他の要請及び/又は動作及び/又はコンテキスト(context)のスイッチをスケジュールすることができる。RASフィードバック状態メッセージはリフレッシュ動作が進行されるメモリのランク/バンクの識別(identification)と関連された情報を含む。314時点で、メモリモジュールはインモジュールリフレッシュ動作を完了する。315時点で、メモリモジュールはリフレッシュ動作が完了したことのRASフィードバック状態メッセージを伝送する。RASフィードバック状態メッセージはリフレッシュ動作が完了されたメモリのランク/バンクの識別と関連された情報を含むことができる。316時点で、メモリコントローラは活性化命令ACTをメモリモジュールに伝送する。317時点で、メモリモジュールはメモリモジュールが読出し命令に対する準備されたことのRASフィードバック状態メッセージを伝送する。318時点で、メモリコントローラは読出し命令RDをメモリモジュールに伝送する。319時点で、メモリモジュールはこれに応答して受信された読出し命令に対応されるデータを出力する。

30

40

50

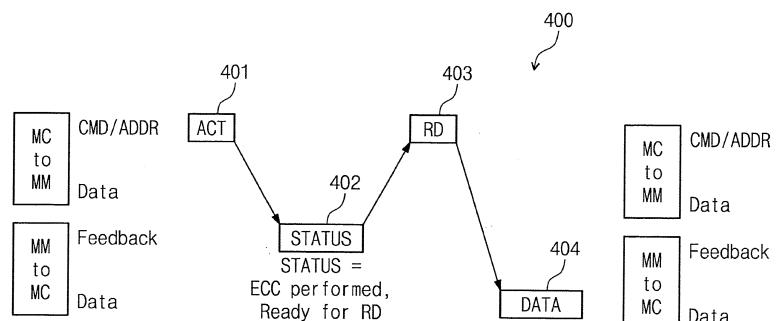

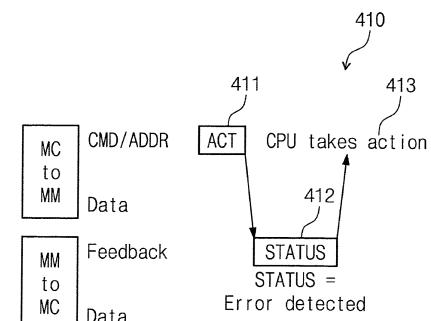

**【 0 0 3 6 】**

図 5 は、本発明の一実施形態によるメモリモジュールがインモジュール E C C 動作を遂行するように動作調整を提供するためのメモリコントローラとメモリモジュールとの間の信号シーケンスを示す図である。

**【 0 0 3 7 】**

図 6 は、本発明の他の実施形態によるメモリがインモジュール E C C 動作を遂行し、その結果、エラー訂正失敗が発生するように動作調整を提供するためのメモリコントローラとメモリモジュールとの間の信号シーケンスを示す図である。

**【 0 0 3 8 】**

図 5 の信号シーケンス 4 0 0 で、インモジュールエラー訂正動作がメモリモジュールによって遂行される。図 6 の信号シーケンス 4 1 0 で、インモジュールエラー訂正動作がメモリモジュールによって再び遂行される。但し、図 6 の信号シーケンス 4 1 0 では、エラー訂正失敗が発生し、フィードバック状態メッセージはエラーが感知されたが、訂正されなかったことを示す。一実施形態で、インモジュールエラー訂正動作に関連されたフィードバック状態メッセージの特定コンテンツはメモリモジュールの初期化時点での選択可能である。

10

**【 0 0 3 9 】**

図 5 で、同図の上の部分には、メモリコントローラ M C からメモリモジュール M M に伝送される信号又はメッセージを示す。一方、下の部分には、メモリモジュールからメモリコントローラに伝送される信号又はメッセージを示す。図 5 の 4 0 1 時点で、メモリコントローラは活性化命令 A C T をメモリモジュールに提供する。4 0 2 時点で、メモリモジュールはこれに応答して E C C 動作が遂行され、読み出し命令 R D に対して準備されたことを示す R A S フィードバック状態メッセージを伝送する。R A S フィードバック状態メッセージはエラーが訂正されたメモリ位置に対する住所情報を含むことができる。メモリコントローラはエラー訂正イベントを記録することができる。4 0 3 時点で、メモリコントローラは読み出し命令を伝送する。4 0 4 時点で、メモリモジュールは読み出し命令に対応するデータを出力する。このような信号シーケンスで、E C C がメモリモジュールによって遂行される間に、C P U / M C は一般的な方法で読み出し及び書き込み命令を発行する。

20

**【 0 0 4 0 】**

図 6 で、同図の上の部分には、メモリコントローラ M C からメモリモジュール M M に伝送される信号又はメッセージを示す。一方、下の部分には、メモリモジュールからメモリコントローラに伝送される信号又はメッセージを示す。図 6 の 4 1 1 時点で、メモリコントローラはメモリモジュールに活性化命令 A C T を伝送する。4 1 2 時点で、メモリモジュールはこれに応答して E C C 動作が失敗し、エラーが訂正されなかったことを表示する R A S フィードバック状態メッセージを伝送する。追加的に、R A S フィードバック状態メッセージはエラーが発生したが、訂正されない位置を識別するアドレス情報を含む。4 1 3 時点で、メモリコントローラ（又は、C P U ）はエラーを記録し、及び／又は適切な措置を遂行することができる。このような信号シーケンスで、E C C がメモリモジュールによって遂行される間に、C P U / M C は一般的な方法で読み出し及び書き込み命令を発行する。メモリモジュールの試行は、エラーを訂正するのに失敗したが、エラーが感知されたことと感知されたエラーのアドレスとを示し、C P U / M C が適切な措置を遂行することを示す。

30

40

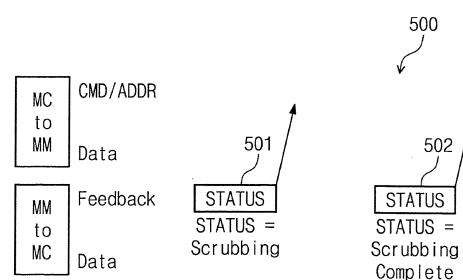

**【 0 0 4 1 】**

図 7 は、本発明の一実施形態によるメモリモジュールがインモジュールスクランピング（ s c r u b b i n g ）動作を遂行するように動作調整を提供するためのメモリモジュールとメモリコントローラとの間の信号シーケンスを示す図である。

**【 0 0 4 2 】**

図 8 は、本発明の他の実施形態によるメモリモジュールがインモジュールスクランピング動作を遂行するように動作調整を提供するためのメモリモジュールとメモリコントローラとの間の信号シーケンスを示す図である。

50

**【 0 0 4 3 】**

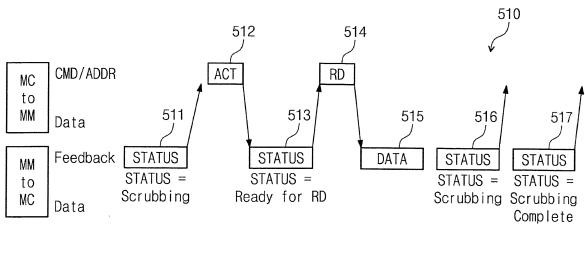

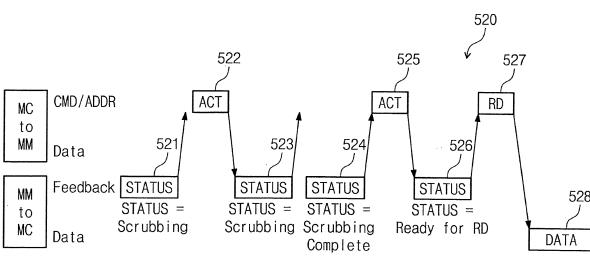

図9は、本発明のその他の実施形態によるメモリモジュールがインモジュールスクラビング動作を遂行するように動作調整を提供するためのメモリモジュールとメモリコントローラとの間の信号シーケンスを示す図である。

**【 0 0 4 4 】**

本実施形態で、図7～図9の信号シーケンスの各々は、メモリモジュールの初期化時点で選択可能である。図7の信号シーケンス500で、図示されたインモジュールスクラビング動作はメモリモジュールがスクラビング動作が進行中であり、そしてスクラビング動作が完了される時を示すフィードバック状態メッセージを提供する基本動作を示す。図8の信号シーケンス510で、インモジュールスクラビング動作はスクラビング動作が進行中であることを示すフィードバック状態メッセージを含む。スクラビング動作は一般アクセスによって中断される。スクラビング動作はスクラビング動作が中断された位置で再開され、スクラビング動作が進行中であることを示すRASフィードバック状態メッセージが伝送される。

10

**【 0 0 4 5 】**

図9の信号シーケンス520で、インモジュールスクラビング動作は一般アクセスより高い優先順位を有する。スクラビング動作が進行中であることを示すフィードバック状態メッセージに応答して、活性化命令が完了されるのを待つ間にメモリコントローラは他の要請及び／又は動作及び／又はコンテキストのスイッチをスケジュールする。一実施形態として、インモジュールスクラビング動作に関連されたフィードバック状態メッセージの特定コンテンツもまたメモリモジュールの初期化時点で選択可能である。

20

**【 0 0 4 6 】**

図7で、同図の上の部分には、メモリコントローラMCからメモリモジュールMMに伝送される信号又はメッセージを示す。一方、下の部分には、メモリモジュールからメモリコントローラに伝送される信号又はメッセージを示す。図7の501時点では、メモリモジュールはスクラビング動作が遂行されていることを示すRASフィードバックメッセージをメモリコントローラに伝送する。スクラビング動作中に、メモリモジュールは周期的にメモリの領域からデータを読み出し、ECCを利用して何らかのエラーを訂正し、訂正されたデータをメモリの該当領域に再書き込みする。

30

**【 0 0 4 7 】**

このような信号シーケンスの実施形態に対して、スクラビング動作は優先順位を有し、スクラビング動作が遂行される間にメモリコントローラはスクラビングイベントを記録する。メモリコントローラは、スクラビング動作の中で他の要請及び／又は動作及び／又はコンテキストのスイッチをスケジュールする。502時点では、メモリモジュールは、スクラビング動作が完了したことのRASフィードバックメッセージをメモリコントローラに伝送する。仮にRASフィードバックメッセージがスクラビング動作が完了し、1つ以上のエラーが検出されたが、訂正されなかったことをまた表示し、RASフィードバックメッセージがエラーが検出された各々の住所を示す場合、メモリコントローラは適切な措置を遂行する。

40

**【 0 0 4 8 】**

図8で、同図の上の部分には、メモリコントローラMCからメモリモジュールMMに伝送される信号又はメッセージを示す。一方、下の部分には、メモリモジュールからメモリコントローラに伝送される信号又はメッセージを示す。図8の511時点では、メモリモジュールはスクラビング動作が遂行されていることを示すRASフィードバックメッセージをメモリコントローラに伝送する。512時点では、メモリコントローラはスクラビング動作を中断する活性化命令をメモリモジュールに伝送する。513時点では、メモリモジュールはメモリモジュールが読み出し命令RDに対して準備されたことのRASフィードバック状態メッセージを伝送する。514時点では、メモリコントローラは読み出し命令をメモリモジュールに伝送する。515時点では、メモリモジュールはこれに応答して受信された読み出し命令に対応するデータを出力する。516時点では、メモリモジュールはスクラビング動作

50

が中断された位置でスクラビング動作を再開し、スクラビング動作が進行中であることを示す R A S フィードバック状態メッセージをメモリコントローラに伝送する。512 時点及び 513 時点に示すように、メモリコントローラはスクラビング動作を再び中断することができる。517 時点で、メモリモジュールはスクラビング動作が完了したことの R A S フィードバックメッセージをメモリコントローラに伝送する。仮に R A S フィードバックメッセージがスクラビング動作が完了され、1 つ以上のエラーが検出されたが、訂正されなかったことを表示し、R A S フィードバックメッセージがエラーが検出された各々の住所を示す場合、メモリコントローラは適切な措置を遂行する。

#### 【 0 0 4 9 】

図 9 で、同図の上の部分には、メモリコントローラ M C からメモリモジュール M M に伝送される信号又はメッセージを示す。一方、下の部分には、メモリモジュールからメモリコントローラに伝送される信号又はメッセージを示す。図 9 の 521 時点で、メモリモジュールはスクラビング動作が遂行中であることを示す R A S フィードバックメッセージをメモリコントローラに伝送する。

10

#### 【 0 0 5 0 】

このような信号シーケンスの実施形態で、スクラビング動作は優先順位を有し、スクラビング動作が遂行される間にメモリコントローラはスクラビングイベントを記録することができ、他の要請及び / 又は動作及び / 又はコンテキストのスイッチをスケジュールする。522 時点で、メモリコントローラは活性化命令 A C T をメモリモジュールに伝送する。523 時点で、メモリモジュールはスクラビング動作が遂行中である R A S フィードバック状態メッセージをメモリコントローラに伝送する。R A S フィードバック状態メッセージはスクラビング動作が完了される前の時間長さ ( L a t e n c y ) を示す情報を含む。メモリコントローラは表示されたレイテンシに基づいて待つか、又はコンテキストスイッチをする。524 時点で、メモリモジュールは、スクラビング動作が完了したことの R A S フィードバックメッセージをメモリコントローラに伝送する。仮に R A S フィードバックメッセージがスクラビング動作が完了され、1 つ以上のエラーが検出されたが、訂正されなかったことを表示し、R A S フィードバックメッセージがエラーが検出された各々の住所を示す場合、メモリコントローラは適切な措置を遂行する。525 時点で、メモリコントローラは、活性化命令 A C T をメモリモジュールに伝送する。526 時点で、メモリモジュールは、メモリモジュールが読出し命令に対して準備されたことの R A S フィードバック状態メッセージを伝送する。527 時点で、メモリコントローラは読出し命令 R D をメモリモジュールに伝送する。528 時点で、メモリモジュールはこれに応答して受信された読出し命令に対応するデータを出力する。

20

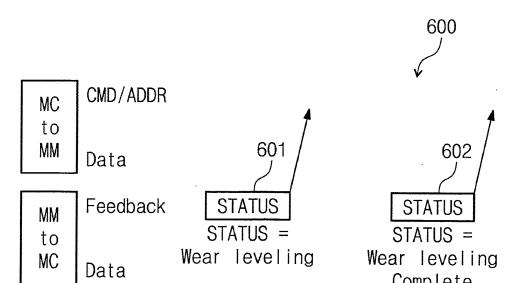

#### 【 0 0 5 1 】

図 10 は、本発明の一実施形態によるメモリモジュールがインモジュールウェアレベリング ( w e a r - l e v e l i n g ) を遂行するように動作調整を提供するためのメモリモジュールとメモリコントローラとの間の信号シーケンスを示す図である。

30

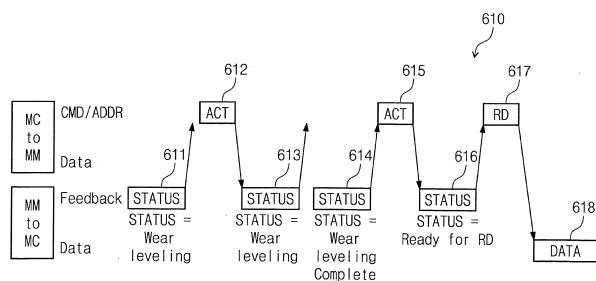

#### 【 0 0 5 2 】

図 11 は、本発明の他の実施形態によるメモリモジュールがインモジュールウェアレベリングを遂行するように動作調整を提供するためのメモリモジュールとメモリコントローラとの間の信号シーケンスを示す図である。

40

#### 【 0 0 5 3 】

本実施形態で、図 10 及び図 11 の信号シーケンスの各々は、メモリモジュールの初期化時点で選択可能である。図 10 の信号シーケンス 600 で、図示されたインモジュールウェアレベリング動作は一般アクセスより高い優先順位を有する。メモリモジュールは、ウェアレベリング動作が進行中であることを示すフィードバック状態メッセージを伝送し、メモリコントローラは活性化命令が完了されることを待つ間に他の要請及び / 又は動作及び / 又はコンテキストのスイッチをスケジュールする。

#### 【 0 0 5 4 】

図 11 の信号シーケンス 610 で、インモジュールウェアレベリング動作は、活性化命令

50

に応答してウェアレベリング動作が進行中にあることを示すフィードバック状態メッセージを提供する。しかし、ウェアレベリング動作は優先順位を有し、ウェアレベリング動作は中断されない。フィードバック状態に応答して、メモリコントローラは活性化命令が完了されることを待つ間に他の要請及び／又は動作及び／又はコンテキストのスイッチをスケジュールする。フィードバック状態メッセージは、ウェアレベリング動作が完了される時にメモリモジュールによって伝送され、メモリコントローラは正常アクセスを開始する。一実施形態として、インモジュールウェアレベリング動作に関連されたフィードバック状態メッセージの特定コンテンツはメモリモジュールの初期化時点で選択可能である。

#### 【0055】

図10で、同図の上の部分には、メモリコントローラMCからメモリモジュールMMに伝送される信号又はメッセージを示す。一方、下の部分には、メモリモジュールからメモリコントローラに伝送される信号又はメッセージを示す。図10の601時点では、メモリモジュールはウェアレベリング動作が遂行中であることを示すRASフィードバックメッセージをメモリコントローラに伝送する。ウェアレベリング動作中に、例えばメモリモジュールは不揮発性メモリ内のウェア(wear)水準を均等に調節するためにメモリページを交換するように書き込みカウント(write-count)テーブル及びリマップ(remap)テーブルを利用して不揮発性メモリのメモリページをリマッピング(remapping)する。このような信号シーケンスの実施形態に対して、ウェアレベリング動作は優先順位を有する。ウェアレベリング動作が遂行中に、メモリコントローラはウェアレベリングイベントを記録する。追加的に、メモリコントローラは他の要請及び／又は動作をスケジュールする。602時点で、メモリモジュールはウェアレベリング動作が完了したことのRASフィードバックメッセージをメモリコントローラに伝送する。

10

#### 【0056】

図11で、同図の上の部分には、メモリコントローラMCからメモリモジュールMMに伝送される信号又はメッセージを示す。一方、下の部分には、メモリモジュールからメモリコントローラに伝送される信号又はメッセージを示す。図11の611時点では、メモリモジュールはウェアレベリング動作が遂行中であることを示すRASフィードバック状態メッセージをメモリコントローラに伝送する。このような信号シーケンスの実施形態に対して、ウェアレベリング動作は優先順位を有し、ウェアレベリング動作が遂行される間にメモリコントローラはウェアレベリングイベントを記録することができ、他の要請及び／又は動作及び／又はコンテキストのスイッチをスケジュールすることができる。612時点で、メモリコントローラは活性化命令をメモリモジュールに伝送する。

20

#### 【0057】

613時点で、メモリモジュールはウェアレベリング動作が遂行中であり、ウェアレベリング動作が完了された後に再試行することを示すRASフィードバック状態メッセージをメモリコントローラに伝送する。RASフィードバック状態メッセージはウェアレベリング動作が完了される前の時間長さ(Latency)を示す情報を含む。メモリコントローラは表示されたレイテンシに基づいて待つか、又はコンテキストスイッチをする。このような信号シーケンスの614時点で、メモリモジュールはウェアレベリング動作が完了したことのRASフィードバックメッセージをメモリコントローラに伝送する。615時点で、メモリコントローラは活性化命令をメモリモジュールに伝送する。616時点で、メモリモジュールはメモリモジュールが読み出し命令に対して準備されたことのRASフィードバック状態メッセージを伝送する。617時点で、メモリコントローラは読み出し命令RDをメモリモジュールに伝送する。618時点で、メモリモジュールはこれに応答して受信された読み出し命令に対応するデータを出力する。

30

#### 【0058】

表2は、CPU/MC(例えば、ホスト)によって遂行される潜在的な対応動作と共にRASフィードバック状態メッセージ内に含まれる例示的な情報を示す。

#### 【0059】

40

50

【表 2】

## R A S 状態情報の例

|                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                       |

|--------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 無効接近の通知<br>(n o t i f i c a t i o n<br>o f i n v a l i d a c c<br>e s s) | <ul style="list-style-type: none"> <li>-キヤッショリードミスによる (ホストアクション: NVMアクセスを待つ)</li> <li>-リフレッシュによる (ホストアクション: リフレッシュ完了又はNVMアクセスを待つ)</li> <li>-ウェアレベリングによる (ホストアクション: NVMD IMM指定 (s p e c i f i e d) 時間の後に再試図)</li> <li>-ガーベッジコレクションによる (ホストアクション: NVMD IMM指定時間の後に再試図)</li> <li>-余裕 (s p a r e d) メモリへのデータ移動 (m i g r a t<br/>i o n) による (ホストアクション: NVMD IMM指定時間の後に再試図)</li> <li>-復旧できない誤謬による</li> </ul> |

| レポート記録<br>(r e p o r t s   l o g)                                        | <ul style="list-style-type: none"> <li>-感知されたエラーの数</li> <li>-訂正されたエラーの数</li> <li>-書き込み失敗の数</li> <li>-失敗したランクの数</li> <li>-ウェアレベリングイベントの数</li> <li>-ガーベッジコレクションイベントの数</li> </ul>                                                                                                                                                                                                                        |

10

20

## 【0060】

5個のコネクターピンが用途変更された実施形態を再び参照すると、5個の用途変更されたコネクターピンによって伝達され、4サイクルを使用する例示的なR A S フィードバック状態メッセージが表3に示すように整理される。

## 【0061】

【表3】

## R A S フィードバック状態メッセージの例

| Bit     | 4                      | 3        | 2                 | 1       | 0      |

|---------|------------------------|----------|-------------------|---------|--------|

| Cycle 0 | Sync                   | TID[5:4] |                   | Success | Parity |

| Cycle 1 | TID[3:0]               |          |                   |         | Parity |

| Cycle 2 | Status Code Type [1:0] |          | Status Code [5:4] |         | Parity |

| Cycle 3 | Status Code [3:0]      |          |                   |         | Parity |

30

40

## 【0062】

表3に示すR A S フィードバック状態メッセージの例で、「S y n c」は、R A S 状態メッセージが新しいフィードバックパケット (p a c k e t) であることを示す。「T I D」は、アドレスと同様であるトランザクション (t r a n s a c t i o n) I D (i d e n t i f i c a t i o n) を示す。パリティー (p a r i t y) は、R A S フィードバック状態メッセージを保護するのに使用される情報を示す。表3のR A S フィードバック状態メッセージに対して用途変更された5個のピンのI D (I d e n t i f i c a t i o n) は便宜的に定義される。

50

表4～表7は、R A S フィードバック状態メッセージに含まれる情報の追加的な例を示す。

【0063】

【表4】

#### R A S フィードバック状態メッセージ情報の例

| Success | 状態コードタイプ<br>Status Code Type<br>[1:0] | 状態コード<br>Status Code(Operations)<br>[5:3] | 状態コード<br>Status Code (Retry)<br>[2:1] | 説明<br>Description                                                                     |

|---------|---------------------------------------|-------------------------------------------|---------------------------------------|---------------------------------------------------------------------------------------|

| 0x0     | 0x00                                  | 0x000                                     | 0x00                                  | 特定T I Dのメモリ内の致命的エラー<br>Fatal error in the Memory with specific TID                    |

|         |                                       |                                           | 0x01 - 0x11                           | RFU                                                                                   |

|         |                                       |                                           | 0x00 - 0x11                           | RFU                                                                                   |

|         |                                       | 0x000                                     | 0x00 - 0x11                           | RFU                                                                                   |

|         |                                       | 0x001                                     | 0x00                                  | Activation Failure with uncorrectable Error                                           |

|         |                                       |                                           | 0x01 - 0x11                           | RFU                                                                                   |

|         |                                       | 0x010                                     | 0x00                                  | Activation Failure after GC (Capacity Failure, fatal)                                 |

|         |                                       |                                           | 0x01                                  | RFU                                                                                   |

|         |                                       |                                           | 0x10                                  | G Cによる活性化失敗、短いレイテンシに再試図<br>Activation Failure because of GC, retry with small latency |

|         |                                       |                                           | 0x11                                  | Activation Failure because of GC, retry with large latency                            |

|         |                                       | 0x011                                     | 0x00                                  | Activation Failure after WL (Capacity Failure, fatal)                                 |

|         |                                       |                                           | 0x01                                  | RFU                                                                                   |

|         |                                       |                                           | 0x10                                  | Activation Failure because of WL, retry with small latency                            |

|         |                                       |                                           | 0x11                                  | Activation Failure because of WL, retry with large latency                            |

|         |                                       | 0x100                                     | 0x00 - 0x01                           | RFU                                                                                   |

|         |                                       |                                           | 0x10                                  | Activation Failure because of Refresh, retry with small latency                       |

|         |                                       |                                           | 0x11                                  | Activation Failure because of Refresh, retry with large latency                       |

|         |                                       |                                           | 0x101 - 0x11                          | 0x00 - 0x11                                                                           |

|         |                                       |                                           | RFU                                   |                                                                                       |

【0064】

10

20

30

40

50

【表 5】

RASフィードバック状態メッセージ情報の例

| Success | 状態コードタイプ<br>Status Code Type<br>[1:0] | 状態コード<br>Status Code(Opreations)<br>[5:3] | 状態コード<br>Status Code (Retry)<br>[2:1] | 説明<br>Description                                          |

|---------|---------------------------------------|-------------------------------------------|---------------------------------------|------------------------------------------------------------|

| 0x0     | 0x0                                   | 0x000                                     | 0x00-0x11                             | RFU                                                        |

|         |                                       | 0x001                                     | 0x00                                  | Write Failure with Uncorrectable Error                     |

|         |                                       |                                           | 0x01-0x11                             | RFU                                                        |

|         |                                       | 0x010                                     | 0x00                                  | Write Failure after GC (Capacity Failure, fatal)           |

|         |                                       |                                           | 0x01                                  | RFU                                                        |

|         |                                       |                                           | 0x10                                  | Write Failure because of GC, retry with small latency      |

|         |                                       |                                           | 0x11                                  | Write Failure because of GC, retry with large latency      |

|         |                                       | 0x011                                     | 0x00                                  | Write Failure after WL (Capacity Failure, fatal)           |

|         |                                       |                                           | 0x01                                  | RFU                                                        |

|         |                                       |                                           | 0x10                                  | Write Failure because of WL, retry with small latency      |

|         |                                       |                                           | 0x11                                  | Write Failure because of WL, retry with large latency      |

|         |                                       | 0x100                                     | 0x00-0x01                             | RFU                                                        |

|         |                                       |                                           | 0x10                                  | Write Failure because of Refresh, retry with small latency |

|         |                                       |                                           | 0x11                                  | Write Failure because of Refresh, retry with large latency |

|         | 0x11                                  | 0x101-0x111                               | 0x00-0x11                             | RFU                                                        |

|         |                                       | 0x000                                     | 0x00-0x11                             | RFU                                                        |

|         |                                       | 0x001                                     | 0x00                                  | Act+Write Failure with Uncorrectable Error                 |

|         |                                       |                                           | 0x01-0x11                             | RFU                                                        |

|         |                                       | 0x010-0x111                               | 0x01-0x11                             | RFU                                                        |

【0065】

10

20

30

40

50

【表 6】

## R A S フィードバック状態メッセージ情報の例

| Success | 状態コードタイプ<br>Status Code Type<br>[1:0] | 状態コード<br>Status Code<br>[5:1] | 説明<br>Description                                                 |

|---------|---------------------------------------|-------------------------------|-------------------------------------------------------------------|

| 0x1     | 0x00                                  | 0x00000                       | 特定 T I D のメモリが<br>準備される<br>(Memory with<br>specific TID is ready) |

|         |                                       | 0x00001-0x11111               | RFU                                                               |

|         | 0x01                                  | 0x00000                       | Activation Success<br>w/o Error                                   |

|         |                                       | 0x00100                       | Activation Success<br>with Correctable<br>Error                   |

|         |                                       | 0x01000                       | Activation Success<br>after GC                                    |

|         |                                       | 0x01100                       | Activation Success<br>after WL                                    |

|         |                                       | 0x10000                       | Activation Success<br>after Refresh                               |

|         |                                       | Others                        | RFU                                                               |

10

20

【0066】

【表 7】

## R A S フィードバック状態メッセージ情報の例

| Success | 状態コードタイプ<br>Status Code Type<br>[1:0] | 状態コード<br>Status Code<br>[4:0] | 説明<br>Description                          |

|---------|---------------------------------------|-------------------------------|--------------------------------------------|

| 0x1     | 0x10                                  | 0x00000                       | Write Success w/o<br>Error                 |

|         |                                       | 0x00100                       | Write Success with<br>Correctable Error    |

|         |                                       | 0x01000                       | Write Success after<br>GC                  |

|         |                                       | 0x01100                       | Write Success after<br>WL                  |

|         |                                       | 0x1000                        | Write Success after<br>Refresh             |

|         |                                       | Others                        | RFU                                        |

|         | 0x11                                  | 0x00000                       | ACT + Write Success                        |

|         |                                       | 0x00100                       | ACT + Write Success<br>w/Correctable Error |

|         |                                       | 0x01000                       | ACT + Write Success<br>after GC            |

|         |                                       | 0x01100                       | ACT + Write Success<br>after WL            |

|         |                                       | 0x1000                        | ACT + Write Success<br>after Refresh       |

|         |                                       | Others                        | RFU                                        |

30

40

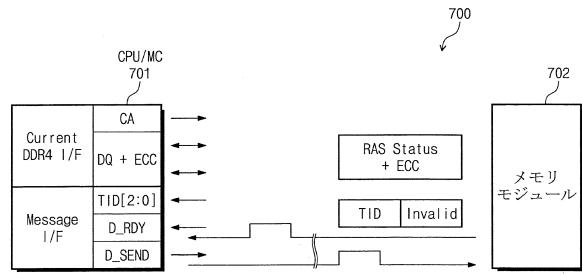

【0067】

図 1 2 は、本発明の一実施形態による D Q (データ) バスを通じて R A S フィードバック状態メッセージが伝送される C P U / M C とメモリモジュールとの間のインターフェイスを示す図である。図 1 3 は、本発明の実施形態による D Q バスを通じて R A S フィードバ

50

ック状態メッセージが伝送される方法を示すフローチャートである。

#### 【0068】

この代替的な (a l t e r n a t i v e) 実施形態では、図13に示すフローチャート800のS801段階で、用途変更された第1のコネクターピンは、フィードバック信号D\_RDYを伝送するように使用される。図12に示すインターフェイス700において、フィードバック信号D\_RDYは、CPU/MC701から注意 (a t t e n t i o n) を要請するためにメモリモジュール702によって使用される。CPU/MC701がフィードバック信号D\_RDYを受信した後、S802段階でCPU/MC701は、用途変更された第2のコネクターピン上で信号D\_SENDを伝送して、S803段階でメモリモジュール702からRASフィードバック状態情報を引き出す。3つの用途変更されたピンがTIDを伝送するために使用される。この代替的な (a l t e r n a t i v e) 実施形態で、RASフィードバック状態メッセージは、DQバスを通じて伝送される。DQバスの相対的な (r e l a t i v e) サイズは、多数の情報ビットがメモリモジュールからCPU/MCに伝送されるようにする。

10

#### 【0069】

他の実施形態で、ホスト（例えば、システムCPU/MC）は、特別なMRS (M o d e R e g i s t e r S e t) 命令を送信して事前にメモリモジュールのRASフィードバック状態情報を要請する。

図14は、本発明の一実施形態によるRASフィードバック状態メッセージを読み出すようにMRSコマンドを利用してメモリモジュールを構成する方法を示すフローチャートである。

20

#### 【0070】

MRS命令は、一般的にDDR4 DIMMに対して定義されている。但し、本発明の実施形態によれば、MRS命令内の使用されないビットは、メモリモジュールが特別なモードに進入するように信号を送るか、又はトリガー (t r i g g e r) する。ここで、特別なモードはMPR読出しモードと呼称され、MPR読出しモードはまた一般的にDDR4 DIMMに対して定義される。図14に示すフローチャート900のS901段階で、ホストはMRS (M R 3) 命令をメモリモジュールに伝送する。S902段階で、ホストは読出し命令RDをメモリモジュールに伝送する。S903段階で、メモリモジュールは一般データの代わりに無効 (I n v a l i d) + ログ (L o g) メッセージを返還 (r e t u r n) する。S904段階で、CPU/MCホストはメモリモジュールが特別なMPRモードを終了するように信号を送るか、又はトリガー (t r i g g e r) するように構成された他のMRS命令を発行する。

30

#### 【0071】

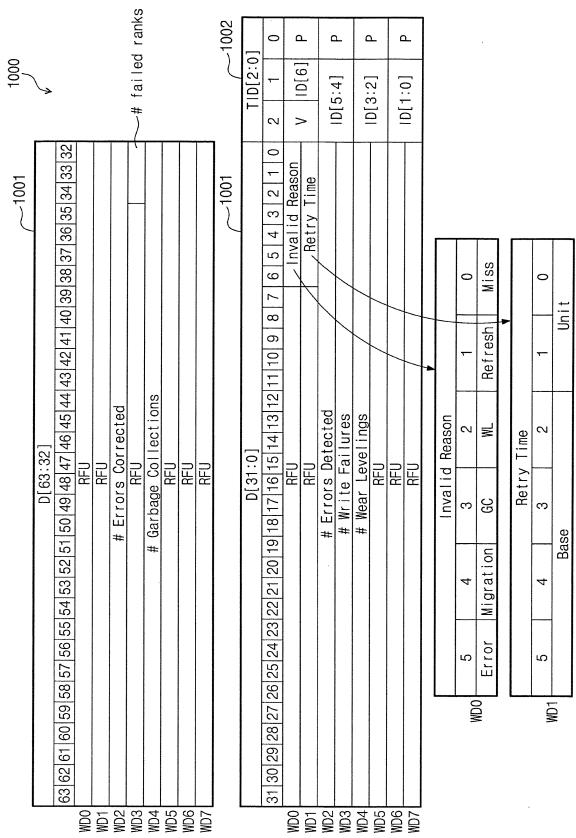

図15は、本発明の一実施形態によるDQバスがフィードバック状態情報を伝送するために使用される場合のRASフィードバック状態メッセージの配列を示す図である。図15のフィードバック状態情報1000に示すように、8個の64ビットのワード (W D 0 ~ W D 7) は、DQバス上でメモリモジュールからの出力であり、これは1001で表示される。4つの3ビットワードは、メモリモジュールから出力されたTID + 無効 (I n v a l i d) メッセージであり、これは1002で表示される。3ビットワードは、用途変更されたコネクターピンを通じて伝送される。

40

#### 【0072】

最初の2つの64ビットワード (WD0、WD1) のビット [6:0] は、各々無効理由 (I n v a l i d R e a s o n) コード及び再試行時間 (R e t r y T i m e) コードを含む。無効理由コードのビット [5] は、エラーが発生したか否かを示す。無効理由コードのビット [4] は、移動 (m i g r a t i o n) が発生したか否かを示す。無効理由コードのビット [3] は、ガーベッジコレクションGC動作が発生したか否かを示す。無効理由コードのビット [2] は、ウェアレベリングWL動作が発生したか否かを示す。無効理由コードのビット [1] は、リフレッシュ動作が発生したか否かを示す。無効理由コードのビット [0] は、ミス (m i s s) が発生したか否かを示す。

50

## 【0073】

再試行時間のビット [5 : 2] は、二進 (binary) 基本 (base) 乗数 (multiplier) を示し、再試行時間のビット [1 : 0] は、基本乗数によって乗じる時間の単位を示す。本実施形態で、二進「00」の単位コードが 100 ns の基本時間を示す。二進「01」の単位コードが 1 us の基本時間を示す。二進「10」の単位コードが 10 us の基本時間を示す。二進「11」の単位コードが 100 us の基本時間を示す。例えば、再試行時間コードのビット [5 : 2] が、二進「0100」（即ち、十進数 4）であり、単位コードを二進「00」である場合、再試行時間コードが 400 ns の再試行時間を示す。

## 【0074】

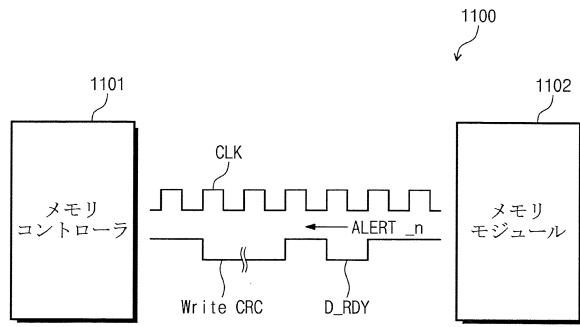

他の実施形態で、既存のコネクターピン ALERT\_n にタイミング定義を追加してメモリモジュールが NVDIMM - P モードにある場合、コネクターピン ALERT\_n は、信号 D\_RDY として使用される。従来の DDR4 仕様 (specification) で、信号 ALERT\_n は 2 つタイプのエラー（書き込み CRC (Cyclic Redundancy Check) エラー、CA (Command Address) パリティエラー）の発生をシグナリング (signaling) するために使用される。このような 2 つのエラーは、信号 ALERT\_n のパルス幅によって区別される。例えば、書き込み CRC エラーが発生した場合、DDR4-2400 仕様のメモリモジュールは、信号 ALERT\_n を大略 6 ~ 10 クロックサイクルの間にロジックローに出力する。CA パリティエラーが発生した場合、DDR4-2400 仕様のメモリモジュールは、信号 ALERT\_n を大略 72 ~ 144 クロックサイクルの間にロジックローに出力する。本発明の実施形態によれば、信号 ALERT\_n の大略 2 サイクルと 3 サイクルとの間の短いパルス幅は、信号 D\_RDY を示すように使用される。したがって、信号 ALERT\_n は、書き込み CRC 及び CA パリティ発生に対する DDR4-2400 仕様にしたがう機能を遂行する。一実施形態として、信号 ALERT\_n が信号 D\_RDY に対して使用される場合、信号 D\_RDY は、常に最も低い優先順位を有し、したがって書き込み CRC 又は CA パリティの発生の検出が保障される。

## 【0075】

表 8 は、本発明の一実施形態による DRAM DIMM モード及び NVDIMM - P モードのメモリモジュールに対するコネクターピンを示す。表 8 に示すように、メモリモジュールが DRAM DIMM モードである場合、ALERT\_n \* ピン（ピン 208）はメモリコントローラの観点で伝送 (Tx) 及び受信 (Rx) 機能を提供するように広く公知された方法に動作する。また、信号 CS\_n [1]（ピン 89）、信号 ODT [1]（ピン 91）、信号 CKE [1]（ピン 203）は、メモリコントローラの観点で伝送機能を提供するように広く公知された方法に動作する。メモリモジュールが NVDIMM - P モードである場合、ピン 208 は、信号 ALERT\_n / D\_RDY として定義され、メモリコントローラの観点で伝送 (Tx) 及び受信 (Rx) 機能の全てを提供する。ピン 89、91、203 は、MSC [2:0] として定義される。ピン 89、91、203 は、メモリコントローラの観点で受信機能を提供する。一実施形態として、信号 ALERT\_n / D\_RDY 及び MSG [2:0] は、SDR (Single Data Rate) 方式に動作する。他の実施形態で、信号 ALERT\_n / D\_RDY 及び MSG [2:0] は、DDR (Double Data Rate) 方式に動作する。

## 【0076】

10

20

30

40

50

## 【表 8】

DRAM DIMMモード及びNVDIMM-Pモードのメモリモジュールに対するコネクターピン

| PIN | DRAM DIMM Mode |       | NVDIMM-P Mode |       |

|-----|----------------|-------|---------------|-------|

|     | Name           | Tx,Rx | Name          | Tx,Rx |

| 89  | CS_n[1]        | Tx    |               |       |

| 91  | ODT[1]         | Tx    | MSG[2:0]      | Rx    |

| 203 | CKE[1]         | Tx    |               |       |

| 208 | ALERT_n*       | Tx/Rx | ALERT_n/D_RDY | Tx/Rx |

10

## 【0077】

表9は、本発明の一実施形態によるNVDIMM-PモードでALERT\_nコネクターピンがD\_RDY信号に使用される場合、コネクターピンALERT\_nに対するタイミング及びメッセージ定義を示す。NVDIMM-Pモードで、コネクターピンALERT\_nのパルス幅は、信号D\_RDYに対して約2サイクル及び3サイクルの間に定義される。約6サイクル及び約10サイクルの間のパルス幅に対して、コネクターピンALERT\_nは、書き込みCRCエラーの発生に定義される。また、約72サイクル及び約144サイクルの間のパルス幅に対してコネクターピンALERT\_nは、CAパリティーエラーの発生として定義される。

20

## 【0078】

## 【表9】

NVDIMM-PモードでALERT\_nコネクターピンがD\_RDY信号として使用される場合、ALERT\_nコネクターピンに対するタイミング及びメッセージ定義

30

| ALERT_n Pulse Width | Definition                |

|---------------------|---------------------------|

| 2~3                 | D_RDY (for NVDIMM-P Mode) |

| 6~10                | Write CRC error           |

| 72~144              | CA parity error           |

## 【0079】

本実施形態で、信号D\_RDYとして使用される前にコネクターピンALERT\_nは、最小限1つのサイクルの間にロジックハイを出力しなければならない。追加的に、各々の信号D\_RDYの後にコネクターピンALERT\_nは、最小限1つのサイクルの間にロジックハイを出力してホストシステムによって認識されるようにしなければならない。

40

## 【0080】

図16は、本発明の一実施形態によるD\_RDY信号として使用されるALERT\_nピンのための信号図である。図16の信号図で、信号流れはメモリモジュール1102からメモリコントローラ1101に向かうことを示す。

## 【0081】

図17は、本発明の他の実施形態による選択されたピンがD\_RDY信号と関連された状態情報（例えば、キャッシング情報等）を伝送するように用途が変更されたメモリチャンネル

50

ル内のメモリモジュールコネクターのピンアウトを示す図である。但し、状態情報の例はこれに制限されない。特に、図17は、メモリチャンネル1200の1つのメモリモジュール1201の例示的なピンアウトの実施形態を示す。メモリチャンネル1200のメモリモジュールの3つのピンは、状態情報（例えば、キャッシュ情報等）をメモリコントローラ（図示せず）又はMC（図示せず）又は一体形のメモリコントローラ（図示せず）を含むCPU（図示せず）に伝送するように用途が変更された。

#### 【0082】

図17に示すように、3つの例示的なコネクターピン(ODT[1]、CKE[1]、CS\_n[1])は、キャッシュ状態情報をメモリコントローラに伝送するように用途変更された。本発明の一実施形態によるメモリモジュールの他のコネクターピンがキャッシュ状態情報をメモリコントローラに伝送するように用途変更されることは容易に理解される。他の実施形態で、例示的なコネクターピン(ODT[1]、CKE[1])は、各々MSG[0]及びMSG[1]としてキャッシュ状態情報を伝送するのに使用され、これによりメッセージは2ビットの幅になる。但し、メッセージはDDR(Double Data Rate)を可能にするメッセージストロボ信号MSG\_Sを含む。

10

#### 【0083】

本実施形態で、専用ピンは、D\_SENDに対して使用されない。代わりに、D\_SENDに対する定義されないDDR4命令が使用され、これはTB(Transaction Burst)命令と称される。TB(Transaction Burst)命令は、既存のコマンド及びアドレスピンを使用して同一の機能を提供するためにトランザクションデータバースト(transaction data burst)を開始する。TB命令は、NVMダイレクト(direct)モード及びDRAM+NVMキャッシュモードで動作する。表10は、TB命令の定義を示す。

20

#### 【0084】

#### 【表10】

トランザクションバスバーストコマンド

(transaction burst command)

| Transaction Burst | Function            |

|-------------------|---------------------|

| 1st clock         | CKE Previous Cycles |

| H                 | CKE Current Cycles  |

| H                 | ACT_n               |

| H                 | RAS_n / A16         |

| L                 | CAS_n / A15         |

| H                 | WE_n / A14          |

| H                 | BG0 - BG1           |

| L                 | BA0 - BA1           |

| L                 | C0 - C2             |

| H                 | BC_n / A12          |

| RFU               | A17; A13; A11, A10  |

30

40

#### 【0085】

50

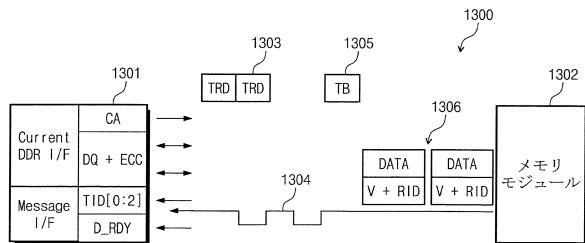

図18は、本発明の一実施形態によるTB(Transaction Burst)命令を示す信号フローチャートである。図18のフローチャート1300に示すように、1303時点で、ホスト1301はCAバス上で2つのTRDコマンドをメモリモジュール1302に伝送する。1304時点で、メモリモジュール1302はこれに応答して2つの読み出しがパッチ(fetch)される準備になったことを表示する。以後、1305時点で、ホスト1301は、2つのデータを出力する2つのバースト(burst)1306を形成するようにメモリモジュール1302に指示するTBコマンドを伝送する。添付される各々のデータは、有効(V:Valid)ビットと該当ID(RID)とを含む。仮にホストが信号D\_RDYを受信しない場合、ホストはTBコマンドを発行しない。TBコマンドとデータの返還との間の時間は固定され、一実施形態でこの時間は「t SND」と同一である。

10

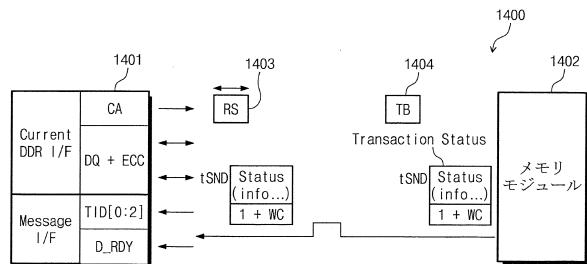

#### 【0086】

図19は、本発明の一実施形態による読み出し状態(RS:Read Status)メッセージを示す信号フローチャートである。図12～図14に示した実施形態と同様に、図19の信号フローチャート1400に示すように、ホスト1401は事前にメモリモジュールから読み出し状態情報を読み出し、又はメモリモジュール1402は事前にt SNDメッセージを利用してホスト1401から注意(attention)を要請し、状態情報をホスト1401に伝送する。1403時点で、ホスト1401がメモリモジュール1402の状態を読み出しを望む場合、ホスト1401はRS命令を伝送する。メモリモジュール1402がホスト1401からの注意を望む場合、メモリモジュール1402は信号D\_RDY(図14で図示せず)を伝送する。そして、1404時点で、ホスト1401は状態情報を読み出すためにTBコマンドをメモリモジュール1402に伝送する。

20

#### 【0087】

本実施形態で、RASフィードバック状態情報の定義は、図12～図14を参照して説明したことと同一である。RASフィードバック状態情報に加えて、状態情報メッセージはまたWC(Write Credit)及び書込みID(Write ID)情報を含む。これにより、メモリモジュールは書込み状態に対する情報を返還する。例えば、書込み状態に対する情報は、WIDチェックによって書込み(write)が成功したか否か、又WCをチェックして追加的な書込みデータを収容できる程度の充分な空間があるか否か等を含む。一実施形態として、CRCはパケット無欠性(integrity)保護のために使用される。

30

#### 【0088】

ホスト1401は、「MSG[0]、cycle1」を読み出して一般データパケットと状態パケットとを区分する。即ち、「MSG[0]」ビットがロジック「0」である場合、ホスト1401はパケットを一般データにデコーディング(decoding)する。仮に「MSG[0]」ビットがロジック「1」である場合、ホスト1401はパケットを状態パケットにデコーディングする。

#### 【0089】

本実施形態で、読み出し状態(RS:Read Status)メッセージは、表11に示すように定義される。

40

#### 【0090】

## 【表 1 1】

読み出し状態 (Read Status) メッセージ

| Read Status | Function           |

|-------------|--------------------|

| H           | CKE Previous Cycle |

| H           | CKE Current Cycle  |

| H           | ACT_n              |

| L           | RAS_n / A16        |

| H           | CAS_n / A15        |

| H           | WE_n / A14         |

| L           | BG0 - BG1          |

| H           | BA0 - BA1          |

| L           | C0-C2              |

| RFU         | BC_n / A12         |

|             | A17, A13, A11, A10 |

|             | A9 - A0            |

10

20

30

## 【0091】

表12は、本発明の一実施形態による例示的な読み出し状態パケットの定義を示す。

## 【0092】

## 【表12】

読み出しパケット (Read Packet) – “読み出し状態 (Read Status)”

| Transaction Packet – “Read Status” |                       |         |         |         |

|------------------------------------|-----------------------|---------|---------|---------|

|                                    | Cycle 1               | Cycle 2 | Cycle 3 | Cycle 4 |

| DQ[63:0]                           | WID0 ~ WID7, RAS, CRC |         |         |         |

| ECC[7:0]                           |                       |         |         |         |

| MSG[0]                             | 1                     | WC[5]   | WC[3]   | WC[1]   |

| MSG[1]                             | WC[6]                 | WC[4]   | WC[2]   | WC[0]   |

| MSG[2]                             | CRC                   | CRC     | CRC     | CRC     |

40

## 【0093】

本実施形態で、読み出し状態 (RS) コマンドは、メモリモジュールの状態を読み出したために使用される。メモリモジュールの状態は、WC (Write Credit) とメモリモジュール応答情報とを含む。読み出し状態コマンドは、NVMダイレクトモードとDRAM + NVMキャッシュモードで使用可能である。図20は、本発明の一実施形態によるRS (Read Status) リターンメッセージの配列を示す図である。

## 【0094】

50

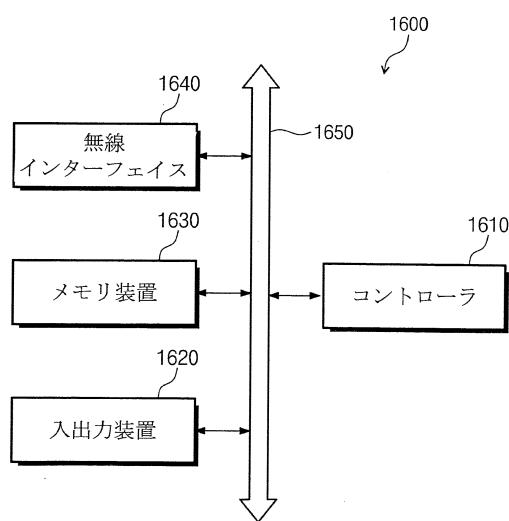

図21は、本発明の一実施形態によるインモジュールリフレッシュ機能、インモジュールECC機能、インモジュールスクラビング、及び／又はインモジュールウェアレベリング管理を制御するか、又は支援し、動作調整をホスト装置に提供するメモリモジュールを含む電子装置を示すブロック図である。

【0095】

電子装置1600は、コンピューティング装置、PDA(Personal Digital Assistant)、ラップトップ(laptop)コンピュータ、モバイルコンピュータ、ウェブタブレット(tablet)、無線フォン、スマートフォン、デジタルミュージックプレーヤー、又は有線や無線電子装置で使用される。但し、これに制限されるものではない。電子装置1600は、バス1650を通じてそれぞれ連結されたコントローラ1610、入出力装置1620、メモリ装置1630、及び無線インターフェイス1640を含む。例えば、入出力装置1620は、キーパッド、キーボード、ディスプレイ、又はタッチスクリーンディスプレーを含む。但し、入出力装置1620の例はこれに制限されない。例えば、コントローラ1610は、少なくとも1つのマイクロプロセッサ(microprocessor)、少なくとも1つのデジタルシグナルプロセッサ(digital signal processor)、少なくとも1つのマイクロコントローラ(microcontroller)等を含む。メモリ装置1630は、コントローラ1610によって使用されるコマンドコードやユーザーデータを格納するように構成される。本実施形態で、メモリ装置1630は、本発明の一実施形態によるインモジュールリフレッシュ機能、インモジュールECC機能、インモジュールスクラビング、及び／又はインモジュールウェアレベリング管理を制御するか、又は支援し、動作調整をホスト装置に提供するメモリモジュールを含む。

10

20

30

40

【0096】

電子装置1600は、RF信号を利用して無線通信ネットワークからデータを受信するか、又は無線通信ネットワークにデータを伝送するように構成された無線インターフェイス1640を利用する。例えば、無線インターフェイス1640は、アンテナ、無線送受信機等を含む。電子装置1600は、通信システムの通信インターフェイスプロトコルとして使用される。例えば、通信インターフェイスプロトコルは、CDMA(Code Division Multiple Access)、GSM(登録商標)(Global System for Mobile Communications)、NADC(North American Digital Communications)、E-TDMA(Extended Time Division Multiple Access)、WCDMA(登録商標)(Wideband CDMA)、CDMA2000(登録商標)、Wi-Fi(登録商標)、Muni Wi-Fi(Municipal Wi-Fi)、ブルートゥース(登録商標)(Bluetooth(登録商標))、DECT(登録商標)(Digital Enhanced Cordless Telecommunications)、Wireless USB(登録商標)(Wireless Universal Serial Bus)、Flash OFDM(Fast low-latency access with seamless handoff Orthogonal Frequency Division Multiplexing)、IEEE 802.20、GPRS(General Packet Radio Service)、iBurst(登録商標)、WiBro(登録商標)(Wireless Broadband)、WiMAX(登録商標)、WiMAX-Advanced、UMTS TDD(Universal Mobile Telecommunication Service-Time Division Duplex)、HSPA(High Speed Packet Access)、EVDO(Evolution Data Optimized)、LTE-Advanced(Long Term Evolution-Advanced)、MMDS(Multichannel Multipoint Distribution Service)等を含む。但し、通信インターフェイスプロトコルの例はこれに制限されない。

50

**【 0 0 9 7 】**

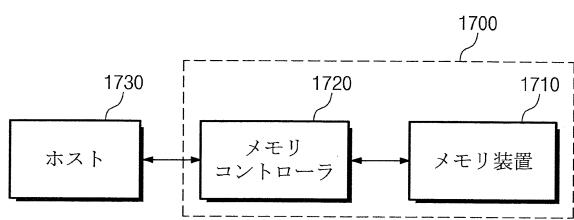

図22は、本発明の一実施形態によるインモジュールリフレッシュ機能、インモジュールECC機能、インモジュールスクーリング、及び／又はインモジュールウェアレベリング管理を制御するか、或いは支援し、動作調整をホスト装置に提供するメモリモジュールを含むメモリシステムを示すブロック図である。

**【 0 0 9 8 】**

メモリシステム1700は、大量のデータを格納するためのメモリ装置1710及びメモリコントローラ1720を含む。ホスト1730の読み出し／書き込み要請に応答して、メモリコントローラ1720は、メモリ装置1710に格納されたデータを読み出すか、又はメモリ装置1710にデータを書き込むようにメモリ装置1710を制御する。メモリコントローラ1720は、ホスト1730（例えば、モバイル装置又はコンピュータシステム）から提供されたアドレスをメモリ装置1710の物理アドレスにマッピングするためのアドレスマッピングテーブルを含む。メモリ装置1710は、本発明の一実施形態によるインモジュールリフレッシュ機能、インモジュールECC機能、インモジュールスクーリング、及び／又はインモジュールウェアレベリング管理を制御するか、又は支援し、動作調整をホスト装置に提供するメモリモジュールを含む。

10

**【 0 0 9 9 】**

以上、本発明の実施形態について図面を参照しながら詳細に説明したが、本発明は、上述の実施形態に限定されるものではなく、本発明の技術的範囲から逸脱しない範囲内で多様に変更実施することが可能である。

20

**【 符号の説明 】****【 0 1 0 0 】**

|                                     |                |    |

|-------------------------------------|----------------|----|

| 100                                 | システム           |    |

| 101、201、202、702、1102、1201、1302、1402 | メモリモジュール(MM)   |    |

| 102                                 | CPU            |    |

| 103、203、1101、1720                   | メモリコントローラ(MC)  |    |

| 104                                 | インモジュールコントローラ  |    |

| 105                                 | メモリチップ         |    |

| 106                                 | リフレッシュロジック(RL) | 30 |

| 107                                 | タイマー           |    |

| 108                                 | カウンター          |    |

| 109                                 | レジスター          |    |

| 110                                 | 機能的構成要素        |    |

| 200、1200                            | メモリチャンネル       |    |

| 700                                 | インターフェイス       |    |

| 701                                 | CPU/MC         |    |

| 1000                                | フィードバック状態情報    |    |

| 1301、1401、1730                      | ホスト            |    |

| 1600                                | 電子装置           | 40 |

| 1610                                | コントローラ         |    |

| 1620                                | 入出力装置          |    |

| 1630                                | メモリ装置          |    |

| 1640                                | 無線インターフェイス     |    |

| 1650                                | バス             |    |

| 1700                                | メモリシステム        |    |

| 1710                                | メモリ装置          |    |

40

50

【図面】

【図 1】

【図 2】

【図 3】

【図 4】

10

20

30

40

50

【図 5】

【図 6】

10

【図 7】

【図 8】

20

【図 9】

【図 10】

30

40

50

【図 1 1】

【図 1 2】

10

【図 1 3】

【図 1 4】

20

30

40

50

【図 15】

【図 16】

10

20

【図 17】

【図 18】

30

40

50

【図 19】

【図 20】

10

【図 21】

【図 22】

20

30

40

50

---

フロントページの続き

米国(US)

(31)優先権主張番号 62/303,347

(32)優先日 平成28年3月3日(2016.3.3)

(33)優先権主張国・地域又は機関

米国(US)

(31)優先権主張番号 62/303,349

(32)優先日 平成28年3月3日(2016.3.3)

(33)優先権主張国・地域又は機関

米国(US)

(31)優先権主張番号 62/347,569

(32)優先日 平成28年6月8日(2016.6.8)

(33)優先権主張国・地域又は機関

米国(US)

(31)優先権主張番号 15/213,386

(32)優先日 平成28年7月18日(2016.7.18)

(33)優先権主張国・地域又は機関

米国(US)

早期審査対象出願

プレイス 2920

(72)発明者 牛 迪 民

アメリカ合衆国, 94087 カリフォルニア州, サニーベール, ホルトハウス テラス 527

(72)発明者 チェン 宏 忠

アメリカ合衆国, 95032 カリフォルニア州, ロスガトス, # 6 カールトン アベニュー 120

(72)発明者 林 スン ヨン

大韓民国 京畿道 華城市 半月洞 山16

(72)発明者 金 寅 東

大韓民国 京畿道 華城市 半月洞 山16

(72)発明者 崔 璋 石

アメリカ合衆国, 95008 カリフォルニア州, キャンプベル, ブレイスブリッジ コート 1

226

合議体

審判長 田中 秀人

審判官 篠原 功一

金子 秀彦

(56)参考文献 国際公開第2014/143056 (WO, A1)

特開2014-157391 (JP, A)

特開2012-89137 (JP, A)

特開2008-171163 (JP, A)

(58)調査した分野 (Int.Cl., DB名)

G06F 12/00 - 12/06