(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6083934号

(P6083934)

(45) 発行日 平成29年2月22日(2017.2.22)

(24) 登録日 平成29年2月3日(2017.2.3)

(51) Int.Cl.

F 1

H04N 5/353 (2011.01)

H04N 5/335 5 3 0

H04N 5/359 (2011.01)

H04N 5/335 5 9 0

請求項の数 6 (全 24 頁)

(21) 出願番号 特願2012-33358 (P2012-33358)

(22) 出願日 平成24年2月17日 (2012.2.17)

(65) 公開番号 特開2013-172204 (P2013-172204A)

(43) 公開日 平成25年9月2日 (2013.9.2)

審査請求日 平成27年2月17日 (2015.2.17)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100126240

弁理士 阿部 琢磨

(74) 代理人 100124442

弁理士 黒岩 創吾

(72) 発明者 山下 雄一郎

東京都大田区下丸子3丁目30番2号キヤ

ノン株式会社内

(72) 発明者 小島 賀

東京都大田区下丸子3丁目30番2号キヤ

ノン株式会社内

最終頁に続く

(54) 【発明の名称】光電変換装置の駆動方法

## (57) 【特許請求の範囲】

## 【請求項 1】

光電変換部と、

電荷を保持する第1の保持部および第2の保持部と、

前記光電変換部と前記第1の保持部とを接続する第1の転送部と、

前記第1の保持部と前記第2の保持部とを接続する第2の転送部と、

前記光電変換部と電源とを接続する第3の転送部と、を含む画素を、行列状に複数配した光電変換装置であって、

第1の動作モードと第2の動作モードとを有し、

前記第1の動作モードおよび前記第2の動作モードのそれぞれにおいて、露光期間に複数の行の画素に対して同時に電荷の蓄積を行い、前記露光期間の後の読み出し期間に前記複数の行の画素から順次信号の読み出しを行い、

前記第1の動作モードにおいては、

前記露光期間に、前記第3の転送部における、前記光電変換部が保持する電荷に対するポテンシャル障壁を、前記第1の転送部における前記ポテンシャル障壁よりも低くし、且つ、前記第3の転送部の前記電荷に対するポテンシャルを前記光電変換部のポテンシャルよりも高くすることにより、前記光電変換部の飽和電荷量を越えて発生した電荷が前記電源へ排出されるように前記光電変換部で電荷を蓄積し、

前記露光期間の後に、前記複数の行の画素において同時に、前記光電変換部に蓄積された電荷を前記第1の転送部を介して前記第1の保持部に転送し、

10

20

前記露光期間の後の前記読み出し期間に、前記光電変換部の飽和電荷量を越えて発生した電荷が前記電源へ排出されるように前記光電変換部での電荷の蓄積を開始し、

前記第2の動作モードにおいては、

前記露光期間において、前記第3の転送部における前記ポテンシャル障壁を、前記第1の転送部における前記ポテンシャル障壁よりも高くし、且つ、前記第3の転送部の前記電荷に対するポテンシャルを前記光電変換部のポテンシャルよりも高くすることにより、前記光電変換部の飽和電荷量を越えて発生した電荷が前記第1の保持部へ転送されるように前記光電変換部および前記第1の保持部で電荷を蓄積し、

前記露光期間の後の前記読み出し期間において、常に、前記第1および第2の転送部の、前記電荷に対するポテンシャルを、前記光電変換部のポテンシャルよりも高くするとともに、前記第3の転送部の、前記電荷に対するポテンシャルを、前記光電変換部のポテンシャルよりも低くすることで、前記光電変換部で生じた電荷を前記電源へ排出している、ことを特徴とする光電変換装置。 10

#### 【請求項2】

前記第1の動作モードにおいて、

前記露光期間の後の前記読み出し期間であって、前記光電変換部での電荷の蓄積を開始する前に、前記光電変換部で生じた電荷を前記電源へ排出している期間がある、

ことを特徴とする請求項1に記載の光電変換装置。

#### 【請求項3】

前記第1の転送部が埋め込みチャネル型のトランジスタを含むことによって、前記第3の転送部における前記ポテンシャル障壁を、前記第1の転送部における前記ポテンシャル障壁よりも低くしている、 20

ことを特徴とする請求項1または請求項2に記載の光電変換装置。

#### 【請求項4】

前記第3の転送部に少なくとも3値を含む制御信号を供給することにより、前記第3の転送部における前記ポテンシャル障壁を、前記第1の転送部における前記ポテンシャル障壁よりも低くしている、

ことを特徴とする請求項1または請求項2に記載の光電変換装置。

#### 【請求項5】

前記第2の動作モードにおいては、

前記露光期間の後に、前記複数の行の画素において同時に、前記第1の保持部に保持された電荷を前記第2の転送部を介して前記第2の保持部に転送する、

ことを特徴とする請求項1乃至請求項4のいずれか一項に記載の光電変換装置。 30

#### 【請求項6】

第3の動作モードをさらに有し、

前記第3の動作モードにおいて、露光期間に複数の行の画素に対して同時に電荷の蓄積を行い、前記露光期間の後の読み出し期間に前記複数の行の画素から順次信号の読み出しを行い、

前記第3の動作モードにおいては、

前記露光期間において、前記第3の転送部における前記ポテンシャル障壁を、前記第1の転送部における前記ポテンシャル障壁よりも高くし、且つ、前記第3の転送部の前記電荷に対するポテンシャルを前記光電変換部のポテンシャルよりも高くすることにより、前記光電変換部の飽和電荷量を越えて発生した電荷が前記第1の保持部へ転送されるように前記光電変換部および前記第1の保持部で電荷を蓄積し、 40

前記露光期間の後に、前記複数の行の画素において同時に、前記光電変換部に保持された電荷および前記第1の保持部に保持された電荷を、前記第2の保持部に転送する、

ことを特徴とする請求項1乃至請求項5のいずれか一項に記載の光電変換装置。

#### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

本発明は、光電変換装置、撮像システムおよび、光電変換装置の駆動方法に関する。

【背景技術】

【0002】

複数の画素で撮像面を構成する光電変換装置においては、撮像面内の全ての画素で電荷を蓄積する動作の開始時刻および終了時刻を揃える、面内同期型電子シャッタと呼ばれる技術が知られている。

特許文献1には、光電変換部とは別に蓄積部を設け、光電変換部で発生した電荷の大部分を光電変換部では蓄積せずに、電荷蓄積領域に転送する構成が開示されている。蓄積期間の終了後、光電変換部に蓄積された電荷は電荷蓄積部に転送され、その後に電荷蓄積部から浮遊拡散部へとさらに転送される。浮遊拡散部に蓄積された電荷量に応じた電圧信号が、画素から出力される。10

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2006-246450号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

しかしながら、特許文献1に開示された動作では、電荷を浮遊拡散部に転送した後に、電圧信号を画素から出力するまでの間、光電変換部で生じた電荷を電源に排出している。そのため、この間の信号電荷は失われるので、得られる画像の時間的解像度が低下することが懸念される。20

本発明は、上記問題に着目して成された。

【課題を解決するための手段】

【0005】

本発明に係る光電変換装置は、光電変換部と、電荷を保持する第1の保持部および第2の保持部と、前記光電変換部と前記第1の保持部とを接続する第1の転送部と、前記第1の保持部と前記第2の保持部とを接続する第2の転送部と、前記光電変換部と電源とを接続する第3の転送部と、を含む画素を、行列状に複数配した光電変換装置であって、第1の動作モードと第2の動作モードとを有し、前記第1の動作モードおよび前記第2の動作モードのそれぞれにおいて、露光期間に複数の行の画素に対して同時に電荷の蓄積を行い、前記露光期間の後の読み出し期間に前記複数の行の画素から順次信号の読み出しを行い、前記第1の動作モードにおいては、前記露光期間に、前記第3の転送部における、前記光電変換部が保持する電荷に対するポテンシャル障壁を、前記第1の転送部における前記ポテンシャル障壁よりも低くし、且つ、前記第3の転送部の前記電荷に対するポテンシャルを前記光電変換部のポテンシャルよりも高くすることにより、前記光電変換部の飽和電荷量を越えて発生した電荷が前記電源へ排出されるように前記光電変換部で電荷を蓄積し、前記露光期間の後に、前記複数の行の画素において同時に、前記光電変換部に蓄積された電荷を前記第1の転送部を介して前記第1の保持部に転送し、前記露光期間の後の前記読み出し期間に、前記光電変換部の飽和電荷量を越えて発生した電荷が前記電源へ排出されるように前記光電変換部での電荷の蓄積を開始し、前記第2の動作モードにおいては、前記露光期間において、前記第3の転送部における前記ポテンシャル障壁を、前記第1の転送部における前記ポテンシャル障壁よりも高くし、且つ、前記第3の転送部の前記電荷に対するポテンシャルを前記光電変換部のポテンシャルよりも高くすることにより、前記光電変換部の飽和電荷量を越えて発生した電荷が前記第1の保持部へ転送されるように前記光電変換部および前記第1の保持部で電荷を蓄積し、前記露光期間の後の前記読み出し期間において、常に、前記第1および第2の転送部の、前記電荷に対するポテンシャルを、前記光電変換部のポテンシャルよりも高くするとともに、前記第3の転送部の、前記電荷に対するポテンシャルを、前記光電変換部のポテンシャルよりも低くすることで、前記光電変換部で生じた電荷を前記電源へ排出している、ことを特徴とする。4050

**【発明の効果】****【0006】**

本発明によれば、時間的な解像度の低下を抑制できる。

**【図面の簡単な説明】****【0007】**

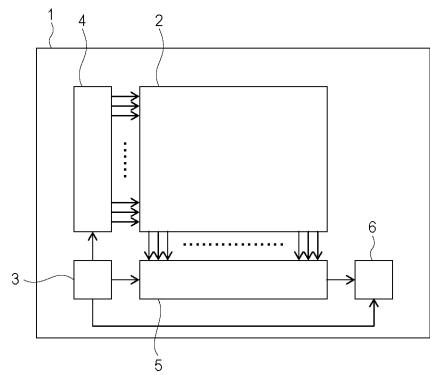

【図1】実施例1に係る光電変換装置の構成を示すブロック図である。

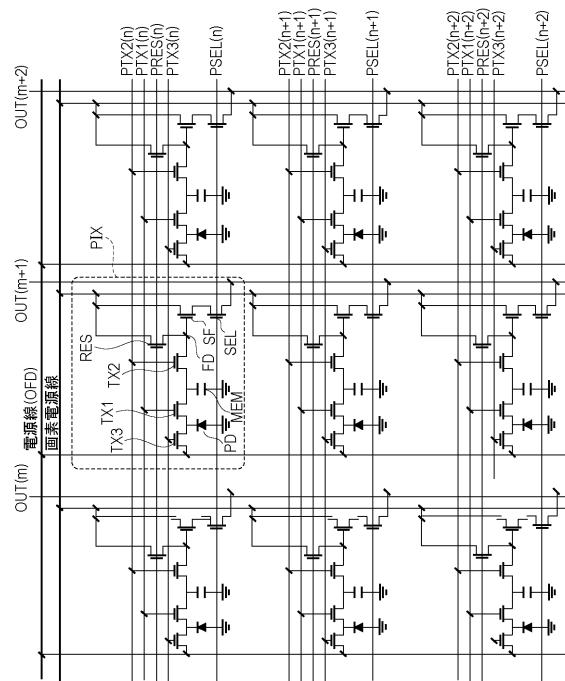

【図2】実施例1に係る撮像領域の構成を示す等価回路図である。

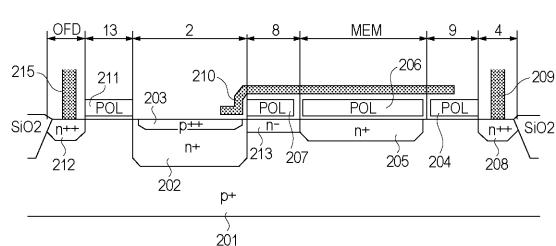

【図3】実施例1に係る画素の構成を示す断面図である。

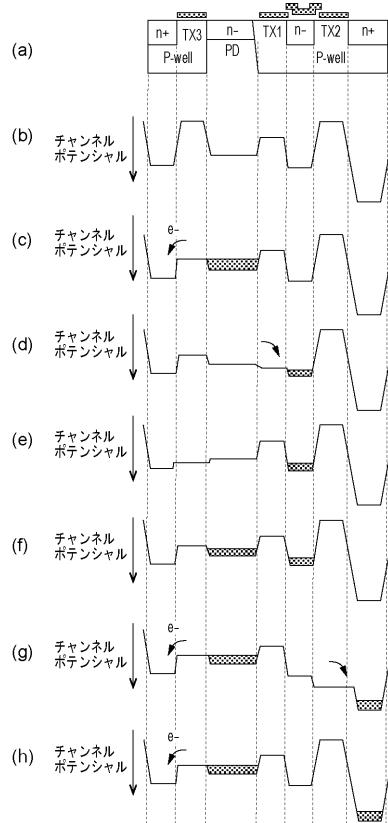

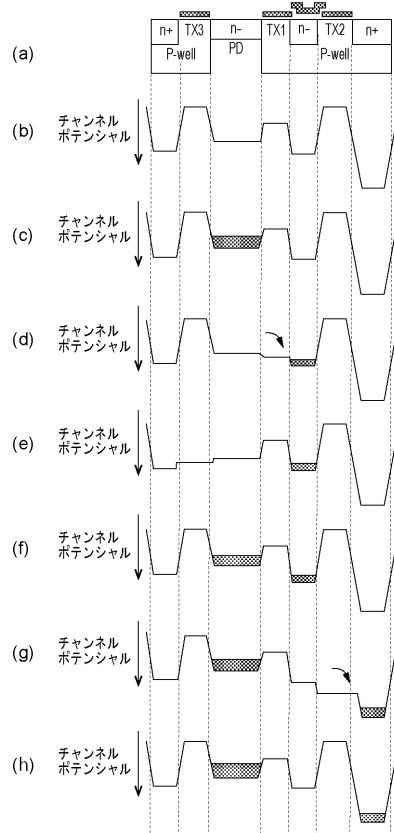

【図4】実施例1に係る画素の断面とポテンシャルを示す図である。

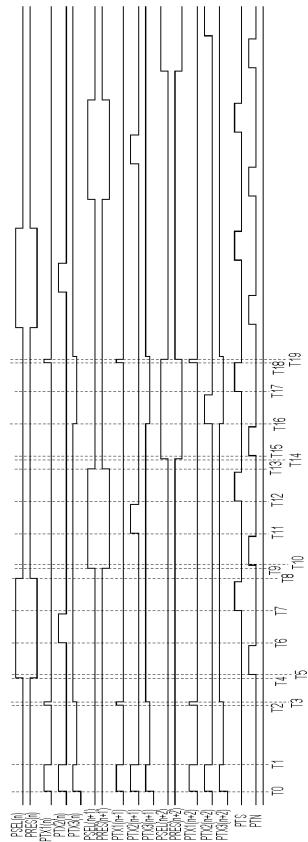

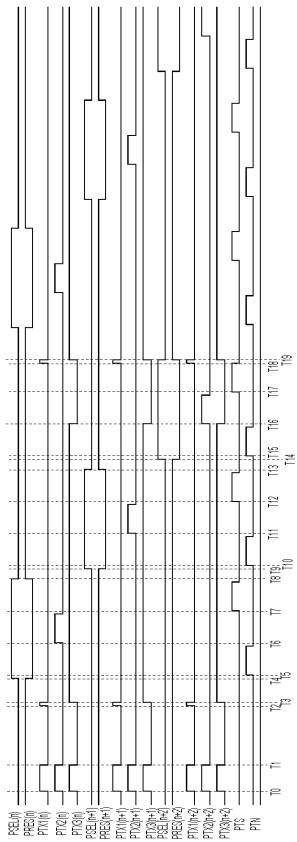

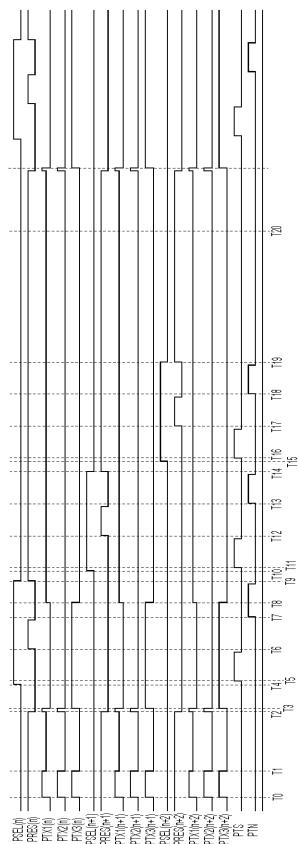

【図5】実施例1に係る動作を示すタイミング図である。

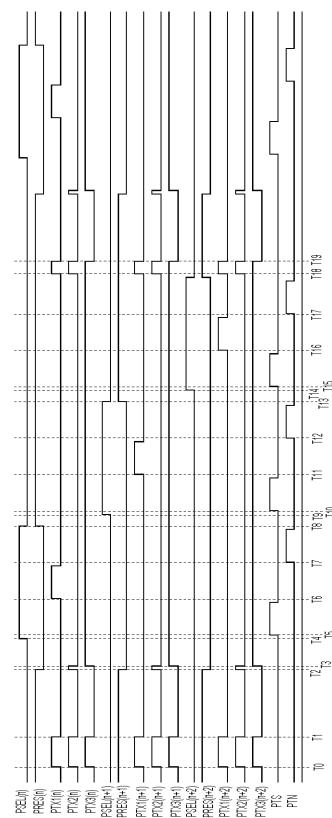

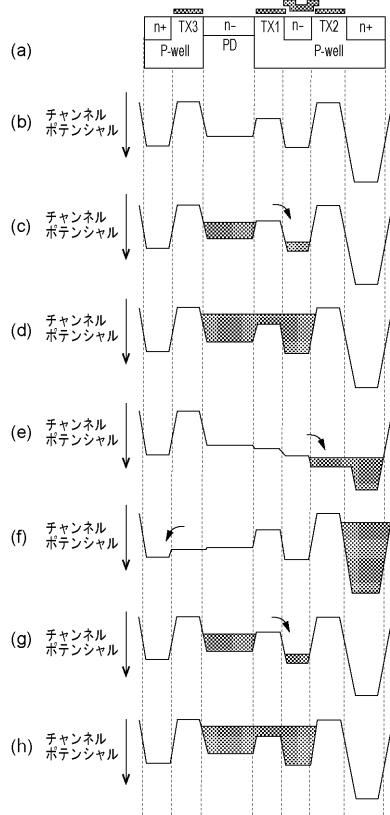

【図6】実施例2に係る画素の断面とポテンシャルを示す図である。

【図7】実施例2に係る動作を示すタイミング図である。

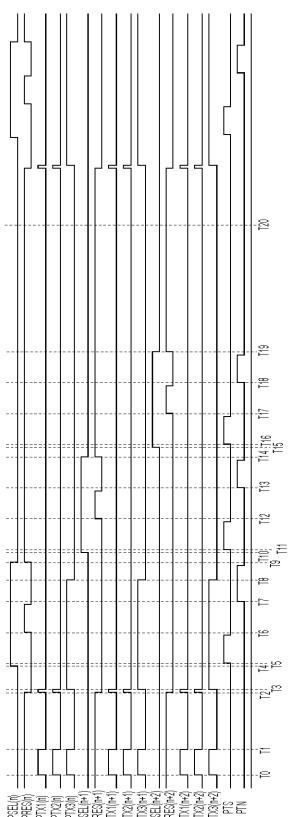

【図8】実施例3に係る画素の断面とポテンシャルを示す図である。

【図9】実施例3に係る動作を示すタイミング図である。

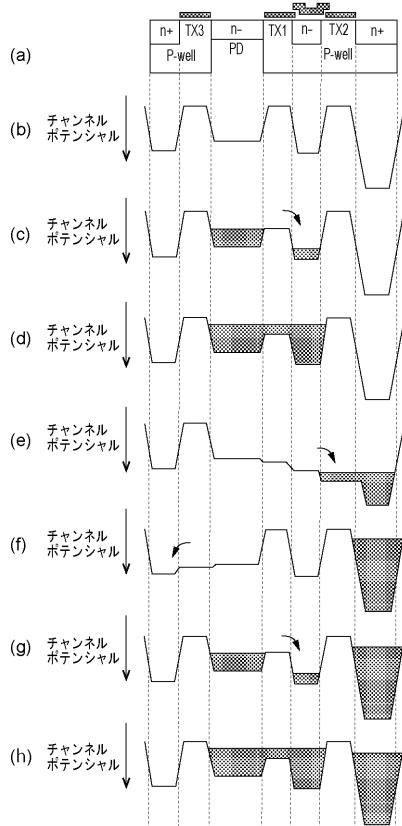

【図10】実施例4に係る画素の断面とポテンシャルを示す図である。

【図11】実施例4に係る動作を示すタイミング図である。

【図12】実施例4の変形例に係る画素の断面とポテンシャルを示す図である。

【図13】実施例4の変形例に係る動作を示すタイミング図である。

【図14】実施例5に係る画素の断面とポテンシャルを示す図である。

【図15】実施例5に係る動作を示すタイミング図である。

【図16】実施例6に係る撮像システムの構成を示すブロック図である。

**【発明を実施するための形態】****【0008】****(実施例1)**

図1を用いて本発明に適用可能な光電変換装置の全体ブロック図の例を説明する。光電変換装置1は半導体基板を用いて1つのチップで構成することができる。光電変換装置1は、複数の画素が配された撮像領域2を有している。更に、光電変換装置1は制御部3を有している。制御部3は、垂直走査部4、信号処理部5及び出力部6に制御信号、電源電圧等を供給する。

**【0009】**

垂直走査部4は撮像領域2に配された複数の画素に駆動パルスを供給する。通常、画素行ごともしくは複数の画素行ごとに駆動パルスを供給する。垂直走査部4はシフトレジスタもしくはアドレスデコーダを用いて構成することができる。

**【0010】**

信号処理部5は、列回路、水平走査回路、水平出力線を含んで構成される。列回路は、各々が、垂直走査部4により選択された画素行に含まれる複数の画素の信号を受ける複数の回路ブロックにより構成されている。各回路ブロックは、信号保持部、增幅回路、ノイズ除去回路、アナログデジタル変換回路のいずれか、もしくはそれらの組み合わせにより構成することができる。水平走査回路はシフトレジスタもしくはアドレスデコーダを用いて構成することができる。

**【0011】**

出力部6は水平出力線を介して伝達された信号を光電変換装置1の外に出力する。出力部6は、バッファもしくは増幅回路を含んで構成されている。

**【0012】**

次に、図2を用いて撮像領域の構成を説明する。図2は、撮像領域2に含まれる画素の等価回路図である。撮像領域2には、画素が行列状に配されているとして、説明の簡略化のために、n行目からn+2行目までのうち、m列目からm+2列目までの、3行×3列の画素を例に取っている。1個の画素を点線で囲い、これをPIXとして示した。

**【0013】**

光電変換部PDであるフォトダイオードPDのアノードは固定電位に接地され、カソー

10

20

30

40

50

ドは第1の転送部である第1転送スイッチTX1を介して第1の保持部MEMの一方の端子に接続される。カソードはさらに第3の転送部である第3転送スイッチTX3を介してオーバーフロードレイン(以下、OFD)として機能する第2の電源である電源線と接続される。第1の保持部MEMの他方の端子は固定電位に接地されている。第1の保持部MEMの一方の端子は、さらに第2の転送部である第2転送スイッチTX2を介して増幅トランジスタSFのゲート端子に接続される。増幅トランジスタSFのゲート端子は、リセット部であるリセットトランジスタRESを介して画素電源線に接続される。ここでは第1から第3の転送部がトランジスタで構成されている例を示している。各トランジスタの制御電極に与えられる信号は、図2では、OFDとして機能する電源線と画素電源線とを分けているが、これらは共通の電源に接続されてもよい。

10

#### 【0014】

選択トランジスタSELは、一方の主電極が垂直信号線に、他方の主電極が増幅トランジスタSFの一方の主電極と接続されている。アクティブな信号PSELが制御電極に入力されると、選択トランジスタの両主電極は導通状態となる。これにより増幅トランジスタSFは、垂直信号線OUTに設けられた不図示の定電流源とでソースフォロワ回路を形成し、増幅トランジスタSFの制御電極であるゲート端子の電位に応じた信号が垂直信号線OUTに現れる。垂直信号線OUTに現れた信号に基づいて光電変換装置から信号が出力され、前述の信号処理部などを経て画像として表示される。また、増幅トランジスタSFのゲート端子と、リセットトランジスタRES及び第2転送スイッチTX2の主電極とが共通に接続される、浮遊拡散部(Floating Diffusion Portion; FD部)であるノードFDは容量値を有しており、電荷を保持することができる。以下では、FD部を第2の保持部と称する。

20

#### 【0015】

次に、図2に示した画素PIXを半導体基板上に形成する場合の断面図の一例を図3に示す。図2の各構成に対応する構成には同じ符号を付している。ここでは、信号電荷として電子を用いる場合を例にとって、半導体領域の導電型は説明する。ホールを用いる場合には各半導体領域の導電型を逆導電型とすればよい。

#### 【0016】

201はP型の半導体領域である。N型の半導体基板にP型の不純物イオンを注入して形成することもできるし、P型の半導体基板を用いてもよい。

30

#### 【0017】

202は光電変換部PDの一部を構成するN型の半導体領域(第1導電型の第1の半導体領域)である。信号電荷である電子と同極性である。P型の半導体領域201(第2導電型の第2の半導体領域)の一部とPN接合を構成する。

#### 【0018】

203はN型半導体領域202の表面に設けられたP型の半導体領域である。光電変換部PDを埋め込み型フォトダイオードするために設けられ、界面準位の影響を低減し光電変換部PD表面で生じる暗電流の発生を抑制する。光電変換部PDは少なくとも第1の半導体領域と、該第1の半導体領域とPN接合を形成する第2の半導体領域とを含んで構成される。

40

#### 【0019】

204は第2転送スイッチを構成する第2の転送電極である。第2の転送電極に供給する電圧によって、電荷保持部と電荷電圧変換部(後述の第4の半導体領域)との間のポテンシャル状態を制御可能である。第2の転送電極は、後述の第3の半導体領域と第4の半導体領域との間の第2の経路上に絶縁膜を介して配される。

#### 【0020】

205は第1の保持部の一部を構成するN型の半導体領域(第1導電型の第3の半導体領域)である。光電変換部PDから転送された電荷を一定期間蓄積可能な構成となっている。206は制御電極である。第3の半導体領域上に絶縁膜を介して配され、第3の半導体領域の、絶縁膜界面近傍の領域のポテンシャル状態を制御可能である。第1の保持部に

50

おいて電荷を保持する期間中に制御電極 206 に電圧を供給することにより、N型半導体領域 205 の表面酸化膜との界面近傍で生じる暗電流の影響を低減させることが可能である。後述するように、この時、供給される電圧は、第3の半導体領域と絶縁膜との界面にホールを集める必要があるため負電圧が好ましく、例えば -3V 程度の電圧が供給される。この電圧は第3の半導体領域の不純物濃度により適宜変更される。

#### 【0021】

第1の保持部MEMは、N型半導体領域205及び制御電極206を含んで構成される。

#### 【0022】

207は第1転送スイッチ8を構成する第1の転送電極である。光電変換部PDと第1の保持部との間の第1の経路のポテンシャル状態を制御可能である。第1の転送電極の下部で、202と205との間に202よりも濃度の低い半導体領域213を持つ。このような埋め込みチャネルを有する構成にすることで、図4で説明するようなポテンシャル関係を持たせることができる。

#### 【0023】

208はフローティングディフュージョン領域(FD領域)であって、FD部に対応する。電荷電圧変換部として機能する。増幅MOSトランジスタのゲートとプラグ209等を介して電気的に接続されている。

#### 【0024】

210は遮光膜である。入射光が第1の保持部へ侵入しないように配置されている。少なくとも第1の保持部MEMを覆っていることが必要であるが、図示するように、第1の転送電極の全体及び第2の転送電極の一部の上部まで延在して配置されると更に遮光機能が高まるので好ましい。

#### 【0025】

211は第3転送スイッチを構成する電荷排出用の制御電極である。光電変換部PDとOFD領域との間の第3の経路のポテンシャル状態を制御可能である。電荷排出制御電極は第3の経路上に絶縁膜を介して配されている。入射光により光電変換部PDに生じた電荷をOFDに排出可能なようにポテンシャル状態を制御する。211に供給する電圧により、光電変換部PDでの蓄積期間(露光期間)の長さを制御可能である。

#### 【0026】

212はOFDを構成する一部(第5の半導体領域)、215は212へ電源電圧を供給するためのプラグであり、不図示の電源と接続されている。つまり、212や215を含めて第2の電源としている。

#### 【0027】

第1転送スイッチ8は、光電変換部PDと第1の保持部とともに第1の転送トランジスタを構成する。また、第2転送スイッチ9は第1の保持部と浮遊拡散部FDとともに第2の転送トランジスタを構成する。そして第3転送スイッチ13は、光電変換部PDと第2の電源とともに第3の転送トランジスタを構成する。

#### 【0028】

図2および3を用いて説明した単位画素が、複数、好ましくは二次元状に配されて、光電変換装置の撮像領域が構成されている。画素はリセット部、増幅部、選択部などを複数の光電変換部PDで共有することも可能である。

#### 【0029】

##### (実施例1)

本発明の実施例を説明する。

#### 【0030】

##### (第1の動作モード)

本実施例においては、リセットトランジスタRESの動作に起因するランダムなノイズ成分も低減できる駆動方法を説明する。

#### 【0031】

10

20

30

40

50

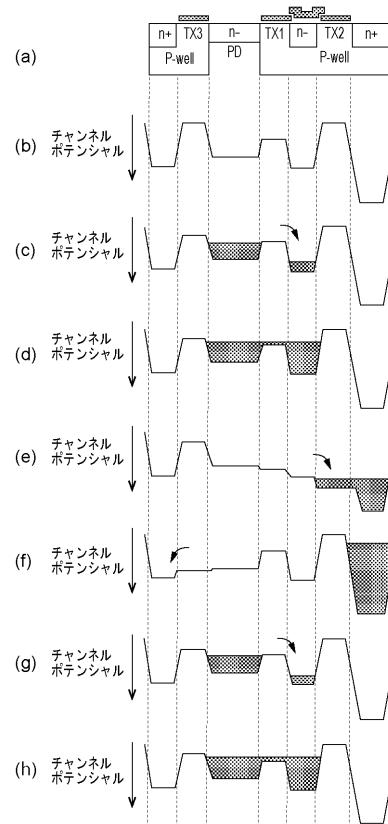

図4(a)は、図3に示した構成のうち、遮光幕210やプラグ209、215などを省略して、一部を抜き出して示したものである。図4(a)のように、第1の保持部のポテンシャルを制御する電極207は、第1および第2の転送部のポテンシャルを制御する電極4および207に一部が重なってもよい。

#### 【0032】

本実施例において、第1の転送部のポテンシャルを制御する信号PTX1～PTX3がLレベルの状態にあっては、第2および第3の転送部のポテンシャルよりも第1の転送部のポテンシャルが高くなるものを考える。例えば、第1の転送部を、埋め込みチャネルを有する構成にすることで、このような関係にできる。

#### 【0033】

図4(b)～(h)は、それぞれの時刻における、図4(a)に示す画素PIXの各領域のポテンシャルを示す図である。図4(b)～(h)において、横軸は対応する図4(a)の位置を示し、縦軸はポテンシャルを表し、図中下に行くほど正電荷に対するポテンシャルが高くなる。本実施例では、光電変換部PDに蓄積される電荷は電子であるので、電子に対しては、図中上に行くほどポテンシャルが高いことになる。

#### 【0034】

図4(b)は、光電変換部PDにも、第1および第2の保持部にも電荷が蓄積されていない状態を示している。この状態で光電変換部PDに光が照射されると、発生した電子が、n-領域に蓄積される。この状態では、電子に対するポテンシャルが、光電変換部PDよりも、第1および第3の転送部の方が高く、光電変換部PDに電荷を蓄積できる。言い換えると、第1および第3の転送部に、電子に対するポテンシャル障壁が形成された状態である。また、第1の転送部の、電子に対するポテンシャルよりも第3の転送部の、電子に対するポテンシャルが高くなっているため、光電変換部PDの飽和電荷量は、第1の転送部のポテンシャルで定まる。これは、第1の転送部に形成される、電子に対するポテンシャル障壁の方が、第3の転送部に形成されるポテンシャル障壁よりも低いと、言い換えることができる。

#### 【0035】

本実施例において、光電変換部PDを露光して、電荷を蓄積させる期間においては、第3の転送部の、電子に対するポテンシャルを、光電変換部PDよりも高く、かつ、第1の転送部よりも低くする。この状態で光電変換部PDの露光が進むと、光電変換部PDで発生した電荷量が、光電変換部PDの飽和電荷量を超える。先に説明したとおり、第1の転送部の、電子に対するポテンシャルよりも第3の転送部の、電子に対するポテンシャルが低くなっているため、光電変換部PDの飽和電荷量を超えて発生した電子は、第3の転送部を介して電源へと排出される。この様子を図4(c)に示す。図において、黒塗りの部分が電子を表している。つまり、光電変換部PDが飽和した状態で、それ以上に発生した電荷が電源へと排出される状態である。

#### 【0036】

次に、光電変換部PDに保持された電荷を、第1の保持部へと転送する。このとき、電子に対するポテンシャルが、光電変換部PDから第1の保持部へと、勾配を持つようにする。この様子を図4(d)に示す。

#### 【0037】

次に、第1の転送部の、電子に対するポテンシャルを再び上げて、光電変換部PDからの電荷が、第1の保持部に流入しないようにする。このとき、第1の転送部の、電子に対するポテンシャルを光電変換部PDよりも高くしており、かつ、第3の転送部のポテンシャルを光電変換部PDよりも低くしているので、光電変換部PDで発生した電子は、第3の転送部を介して電源へと排出される。これにより、光電変換部PDをリセットすることができる。この様子を図4(e)に示す。

#### 【0038】

図4(e)に示した状態で、光電変換部PDをリセットした後、第3の転送部の、電子に対するポテンシャルを、光電変換部PDよりも高くすることで、光電変換部PDは、再

10

20

30

40

50

び電荷を蓄積できる状態になる。この様子を、図4(f)に示す。ここでは、光電変換部PDには、飽和電荷量を超えない量の電荷が蓄積された状態を示している。

#### 【0039】

図4(f)の状態からさらに光電変換部PDの露光が進むと、図4(c)と同様に、光電変換部PDの飽和電荷量を超えて発生した電荷が、第3の転送部を介して電源に排出される。この様子を、図4(g)に示す。

#### 【0040】

図4(g)においては、さらに、第1の保持部に保持された電荷を、第2の転送部を介して第2の保持部に転送している。

#### 【0041】

その後、第2の転送部の、電子に対するポテンシャルを再び高くし、第1の保持部と第2の保持部との間にポテンシャル障壁を形成する。この様子を図4(h)に示す。

10

#### 【0042】

図4(b)～(f)までの動作を、全ての画素に対して同時にを行うことで、面内同期型のシャッタを実現できる。図4(g)～(h)の動作は、行毎に行う。

#### 【0043】

図4(c)と、図4(h)との違いは、第2の保持部に電荷が保持されているか否かである。第2の保持部に保持された電荷量に応じた信号が読み出された後に、第2の保持部がリセットされる。図4(g)～(h)では、第2の保持部がリセットされる前の状態を示している。

20

#### 【0044】

図4で示した動作を、図2および図5を参照しながら、より詳細に説明する。

#### 【0045】

図5に示す信号名は、図2の等価回路図に示した信号と対応している。ここでは、信号PTX1(n)～PTX1(n+2)がLレベルであるときの第1の転送部の、電子に対するポテンシャルは、PTX2(n)～PTX2(n+2)およびPTX3(n)～PTX3(n+2)がLレベルであるときの第2及び第3の転送部の、電子に対するポテンシャルよりも低い構成を考える。

#### 【0046】

また、信号PTSおよびPTNは、列回路が備える、サンプルホールドする2つのサンプルホールド回路の動作を制御する信号である。信号がHレベルになるとサンプリングを行い、信号がHレベルからLレベルになるとホールドされる。ここでは、説明を簡単にするために、サンプルホールド回路が、垂直信号線の信号をサンプルホールドする場合を考える。

30

#### 【0047】

時刻T0において、信号PTX1(n)～PTX1(n+2)、PTX2(n)～PTX2(n+2)、PTX3(n)～PTX3(n+2)がHレベルになる。これにより、光電変換部PDで発生した電荷は、第3の転送部もしくは第1および第2の転送部を介して電源へと排出される。

#### 【0048】

時刻T1に、信号PTX1(n)～PTX1(n+2)、PTX2(n)～PTX2(n+2)がLレベルとなり、PTX3(n)～PTX3(n+2)が中間(Middle; M)レベルになる。この状態が、図4(b)に対応する。時刻T1から、電荷の蓄積期間が開始する。

40

#### 【0049】

時刻T2に、信号PTX1(n)～PTX1(n+2)がHレベルになる。これにより、光電変換部PDに蓄積された電荷が、第1の保持部に転送される。この状態が、図4(d)に対応する。

#### 【0050】

時刻T3に、信号PTX1(n)～PTX1(n+2)がLレベルになると、第1の転

50

送部にポテンシャル障壁が再び形成される。時刻 T 1 ~ T 3 までが、蓄積期間である。蓄積期間において、信号 P T X 3 ( n ) ~ P T X ( 3 n + 2 ) が中間 ( M i d d l e ; M ) レベルにあり、この時のポテンシャルが第 1 の転送部よりも高く、かつ、光電変換部 P D よりも低い状態にあるので、光電変換部の飽和電荷量は、第 3 の転送部のポテンシャルで決まる。光電変換部 P D の飽和電荷量を超えて発生した電荷は、図 4 ( c ) で示したように、第 3 の転送部を介して電源へと排出される。

#### 【 0 0 5 1 】

時刻 T 3 には、さらに、信号 P T X 3 ( n ) ~ P T X 3 ( n + 2 ) が H レベルになる。これにより、光電変換部 P D で発生した電荷は、P D に蓄積されることなく、第 3 の転送部を介して電源へと排出される。この状態が図 4 ( e ) に対応する。

10

#### 【 0 0 5 2 】

時刻 T 4 に、信号 P R E S ( n ) ~ P R E S ( n + 2 ) が L レベルになり、第 2 の保持部のリセット状態が解除される。

#### 【 0 0 5 3 】

また、時刻 T 4 に、信号 P S E L 1 ( n ) が H レベルになることで、n 行目の画素の選択トランジスタが導通し、このときの第 2 の保持部に保持された電荷量に応じた信号が、垂直信号線に現れる。

#### 【 0 0 5 4 】

時刻 T 5 から信号 P T N が一時的に H レベルになることで、この時刻における垂直信号線のレベルがサンプルホールドされる。ここでサンプルホールドされるレベルは、第 2 の保持部をリセットしたことによるノイズ成分が含まれるものである。

20

#### 【 0 0 5 5 】

時刻 T 6 から、信号 P T X 1 ( n ) が H レベルになることで、第 1 の保持部で保持された電荷が、第 2 の保持部に転送される。

#### 【 0 0 5 6 】

時刻 T 7 から信号 P T S が一時的に H レベルになることで、この時刻における垂直信号線のレベルがサンプルホールドされる。ここでサンプルホールドされるレベルは、時刻 T 6 に第 2 の保持部に転送された電荷量に応じた信号に加えて、時刻 T 5 からの動作でサンプルホールドされたノイズ成分を含む。時刻 T 5 からの動作でサンプルホールドされた信号と、時刻 T 7 からの動作でサンプルホールドされた信号との差分処理を行うことで、両者に共通して含まれる、相関性のあるノイズ成分を低減することができる。本実施例においては、差分処理に供される 2 つの信号は、時刻 T 4 に第 2 の保持部のリセットを解除したことによるノイズを含むので、固定的に発生するノイズのみならず、ランダムに発生するノイズ成分も低減することができる。

30

#### 【 0 0 5 7 】

時刻 T 8 に、信号 P S E L 1 ( n ) が L レベルになると、n 行目の画素が持つ選択トランジスタ S E L がオフになり、増幅トランジスタ S F と垂直信号線との電気的な接続が遮断される。また、時刻 T 9 には、信号 P R E S ( n ) が H レベルになることで、第 2 の保持部がリセットされた状態になる。

#### 【 0 0 5 8 】

時刻 T 9 から時刻 T 13までの動作は、時刻 T 4 から時刻 T 8 までの動作が、n + 1 行目の画素について行われるものである。

40

#### 【 0 0 5 9 】

時刻 T 14 から時刻 T 19までの動作は、時刻 T 4 から時刻 T 8 までの動作が、n + 2 行目の画素について行われるものである。

#### 【 0 0 6 0 】

時刻 T 14 から時刻 T 19までの期間は、光電変換部 P D による電荷の蓄積が開始されるという点で、時刻 T 4 から時刻 T 8 まで、および時刻 T 9 から時刻 T 13までの動作と異なっている。

#### 【 0 0 6 1 】

50

本実施例では、時刻 T 1 6 に、信号 P T X 3 ( n ) ~ P T X 3 ( n + 2 ) が M レベルになる。これにより、n 行目から n + 2 行目の画素の光電変換部が、電荷を蓄積できる状態になる。

#### 【 0 0 6 2 】

時刻 T 1 8 に、信号 P T X 1 ( n ) ~ P T X 1 ( n + 2 ) が H レベルになることで、時刻 T 1 6 からの期間に光電変換部 P D に蓄積された電荷が第 1 の保持部に転送される。

#### 【 0 0 6 3 】

時刻 T 1 9 からは、時刻 T 3 から時刻 T 1 9 までの動作が繰り返される。

#### 【 0 0 6 4 】

ところで、図 5 においては、信号 P T X 3 ( n ) ~ P T X 3 ( n + 2 ) が、時刻 T 3 から時刻 T 1 6 までの期間に H レベルになっている。しかしながら、信号 P T X 3 ( n ) ~ P T X 3 ( n + 2 ) が M レベルになる時刻 T 1 6 は、時刻 T 3 よりも後であって、かつ、時刻 T 1 6 から H レベルになる信号 P T S が再び L レベルになるまでの期間で、任意に設定してよい。具体的な設定の仕方としては、入射光量に応じて蓄積時間を変更することが考えられる。10

#### 【 0 0 6 5 】

本実施例によれば、第 1 のフレームの露光期間で発生した電荷を複数の行の画素に対して同時に第 1 の保持部に転送することで面内同期型電子シャッタを実現することができる。さらに、各画素から信号が読み出されるまでの間も、光電変換部 P D で、第 1 のフレームに続く第 2 のフレームのための電荷蓄積を行える。20

#### 【 0 0 6 6 】

本実施例によれば、面内同期型電子シャッタを実現しながら、第 2 の保持部をリセットしたことによるランダムなノイズ成分も低減することができる。

#### 【 0 0 6 7 】

##### ( 第 2 の動作モード )

本発明に係る光電変換装置は、以上で説明した第 1 の動作モード以外にも取り得る。

#### 【 0 0 6 8 】

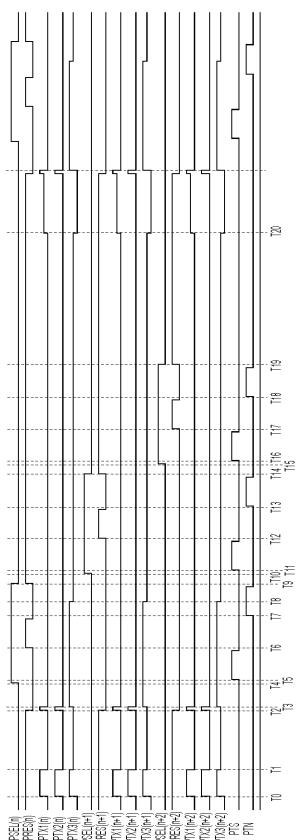

図 6 および図 7 を用いて、第 2 の動作モードの動作を説明する。

#### 【 0 0 6 9 】

本動作モードと、第 1 の動作モードの動作との差異の一つは、本参考例では、第 2 の保持部に保持された電荷量に基づく信号を出力する動作を行っている間に、光電変換部で発生する電荷を蓄積せず、第 3 の転送部を介して電源に排出する点である。言い換えると、画素から信号を読み出す動作と、光電変換部による電荷蓄積動作を時間的に多重化しない点である。30

#### 【 0 0 7 0 】

本動作モードでは、光電変換部の露光期間において、第 1 の転送部の、電子に対するポテンシャルが光電変換部より高く、かつ、第 3 の転送部よりも低く設定されている。このため、光電変換部の飽和電荷量は、第 1 の転送部のポテンシャルで定まる。この構成において、飽和電荷量を超える電荷が発生すると、電荷は第 1 の転送部を介して第 1 の保持部に転送される。40

#### 【 0 0 7 1 】

図 6 は、本動作モードの動作を示すタイミング図である。図 5 に示した第 1 の動作モードのタイミング図との相違点を中心に説明する。

#### 【 0 0 7 2 】

第 1 の動作モードでは、時刻 T 1 から時刻 T 3 までの露光期間において、信号 P T X 3 ( n ) ~ P T X 3 ( n + 2 ) は M レベルであったのに対して、本動作モードでは L レベルにする。これにより、第 1 の動作モードの場合よりも、第 3 の転送部における、電子に対するポテンシャルが高くなる。そのため、光電変換部の飽和電荷量を超えて発生した電荷は電源に排出されるのではなく、第 1 の転送部を介して第 1 の保持部に蓄積される。

#### 【 0 0 7 3 】

50

20

30

40

50

時刻 T<sub>2</sub> から時刻 T<sub>3</sub> にかけて信号 P T X<sub>1</sub>(n) ~ P T X<sub>1</sub>(n + 2) は L レベルを維持し、信号 P T X<sub>2</sub>(n) ~ P T X<sub>2</sub>(n + 2) が H レベルになる点でも、第 1 の動作モードと異なる。これは、第 1 の動作モードでは、光電変換部のみで電荷を蓄積し、第 1 の転送部に電荷を転送する時刻をもって画素の露光期間を終えていたのに対して、本動作モードでは、第 1 の保持部で電荷を蓄積するためである。これに伴って、信号 P R E S(n) ~ P R E S(n + 2) は、時刻 T<sub>2</sub> に L レベルになる。

#### 【0074】

時刻 T<sub>3</sub>までの期間に、光電変換部で発生し、第 1 の保持部に蓄積された電荷は、時刻 T<sub>3</sub>に信号 P T X<sub>2</sub>(n) ~ P T X<sub>2</sub>(n + 2) が L レベルになることで、第 2 の保持部へ転送される。ここまで動作を、複数の行の画素に対して同時にを行うことで、面内同期型電子シャッタを実現できる。10

#### 【0075】

本動作モードにおいて、時刻 T<sub>3</sub>に、信号 P T X<sub>3</sub>(n) ~ P T X<sub>3</sub>(n + 2) が H レベルになり、第 3 の転送部の、電子に対するポテンシャルが、光電変換部の、電子に対するポテンシャルよりも低くなる。この結果、時刻 T<sub>3</sub>までに光電変換部が保持していた電荷と、時刻 T<sub>3</sub>以降に発生した電荷は、第 3 の転送部を介して電源に排出される。

#### 【0076】

時刻 T<sub>4</sub>から始まる動作では、n 行目から n + 2 行目の画素が、垂直走査部 4 によって順次選択され、それぞれの画素から信号が読み出される。20

#### 【0077】

本動作モードにおいても、ノイズ成分を低減するために、1つの画素につき 2 回のサンプルホールドを行う。本動作モードにおいては、光電変換で得た電荷に基づく信号を先にサンプルホールドする。

#### 【0078】

時刻 T<sub>18</sub>から時刻 T<sub>19</sub>にかけて、信号 P T X<sub>1</sub>(n) ~ P T X<sub>1</sub>(n + 2) および信号 P T X<sub>2</sub>(n) ~ P T X<sub>2</sub>(n + 2) を H レベルにすることで、光電変換部、第 1 の保持部、および第 2 の保持部に保持された電荷をリセットする。時刻 T<sub>19</sub>から次の露光期間が始まる。

#### 【0079】

図 6 に示した動作においては、各行の画素から信号を読み出す期間を除いて信号 P R E S(n) ~ P R E S(n + 2) が H レベルとなっているが、信号 P T X<sub>2</sub>(n) ~ P T X<sub>2</sub>(n + 2) が H レベルとなる前に、信号 P R E S(n) ~ P R E S(n + 2) をパルス状に H レベルにしてもよい。30

#### 【0080】

上述した動作を行えば、フォトダイオードが蓄積できるよりも多くの電荷がフォトダイオードで発生しても、蓄積時間の開始と終了とを好適に規定することができる。

#### 【0081】

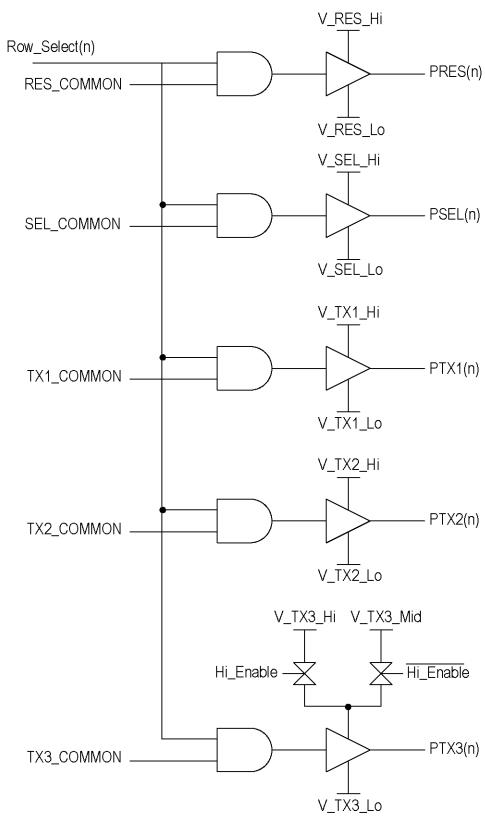

図 7 は、本実施例に係る垂直走査部の一部の構成を示す図である。特に、n 行目の画素に対する出力部分を示している。

#### 【0082】

n 行目の画素に対応する出力部分では、5 個の並列に設けられた A N D 回路を備え、そのそれぞれに対してバッファ回路が設けられている。バッファ回路は、例えばインバータ回路である。40

#### 【0083】

図 7において、信号 R o w \_ S e l e c t(n) は、不図示のシフトレジスタやデコーダの、画素の配列の n 行目に対応する出力である。信号 R o w \_ S e l e c t(n) は、5 個の A N D 回路の一方の入力に共通に入力される。

#### 【0084】

5 個の A N D 回路の他方の入力には、入力に信号 R E S \_ C O M M O N、S E L \_ C O M M O N、T X 1 \_ C O M M O N、T X 2 \_ C O M M O N、および T X 3 \_ C O M M O N が入力される。50

のいずれかが与えられ、信号 R o w \_ S e l e c t ( n ) との論理積が、それぞれの出力として現れる。

#### 【 0 0 8 5 】

信号 R E S \_ C O M M O N 、 S E L \_ C O M M O N 、 T X 1 \_ C O M M O N 、 および T X 2 \_ C O M M O N が与えられる A N D 回路の後段に設けられた各バッファ回路は、 H レベルか L レベルの出力を出せるように構成されている。例えば、信号 R E S \_ C O M M O N が与えられる A N D 回路に着目すると、信号 R o w \_ S e l e c t ( n ) と、 R E S \_ C O M M O N との論理積が 1 であれば、バッファの出力は、電源 V \_ R E S \_ H i に対応し、信号 P R E S ( n ) が H レベルになる。一方、信号 R o w \_ S e l e c t ( n ) と、 R E S \_ C O M M O N との論理積が 0 であれば、バッファの出力は、電源 V \_ R E S \_ L o に対応し、信号 P R E S ( n ) が L レベルになる。

10

#### 【 0 0 8 6 】

信号 P T X 3 \_ C O M M O N が与えられる A N D 回路の後段に設けられたバッファ回路は、 M レベルの信号 P T X 3 ( n ) を出力できるように、バッファ回路の電源が 3 値を取れるように構成されている。ここでは、 H レベルに対応する電圧 V \_ T X 3 \_ H i と、 M レベルに対応する電圧 V \_ T X 3 \_ M i d とを、信号 H i \_ E n a b l e で切り替えられるようになっている。信号 / H i \_ E n a b l e は、信号 H i \_ E n a b l e とは逆相の関係にある。

#### 【 0 0 8 7 】

上記のように構成することで、 M レベルの信号を撮像領域の画素に供給することができる。

20

#### 【 0 0 8 8 】

図 7 に示した構成を単位として、この単位が、撮像領域の各行に対応して設けられ、これらに対して、信号 P R E S ( n ) ~ P R E S ( n + 2 ) 、 P S E L ( n ) ~ P S E L ( n + 2 ) 、 P T X 1 ( n ) ~ P T X 1 ( n + 2 ) 、 P T X 2 ( n ) ~ P T X 2 ( n + 2 ) 、 および P T X 3 ( n ) ~ P T X 3 ( n + 2 ) は、共通に与えられる。

#### 【 0 0 8 9 】

ここでは、信号 P T X 3 ( n ) が M レベルを取り得る場合を例に取っているが、後述の実施例の動作を行う際にも、必要な信号に対しては同様の構成にすることで、 M レベルを出力できる。

30

#### 【 0 0 9 0 】

上述の第 1 の動作モードは、光電変換部で電荷を蓄積し、光電変換部に蓄積された電荷を、複数の画素に対して同時に、第 1 の保持部へと転送することにより面内同期型電子シャッタを実現している。第 1 の保持部に保持された電荷を第 2 の保持部に順次転送し、画素からの信号を読み出している。そして、画素から信号を読み出す動作と並行して、光電変換部による電荷の蓄積が行われる。これにより、画素から信号を読み出す期間に光電変換部で発生する電荷も、電源に排出されずに信号電荷として利用できるため、得られる画像の時間的な解像度が低下することを抑制できる。

#### 【 0 0 9 1 】

ところが、第 1 の動作モードでは、光電変換部の飽和電荷量を超える電荷が発生する、第 1 の保持部に流出してしまうことが懸念される。これに対して、第 2 の動作モードによれば、光電変換部の飽和電荷量を超える電荷を第 1 の保持部で蓄積させることにより、第 1 の動作モードよりも高光量の撮像条件に対応することができる。

40

#### 【 0 0 9 2 】

本実施例によれば、第 1 および第 2 の動作モードを選択的に実行することができる。これにより、撮像条件に応じて、好適な画像を取得することができる。動作モードの切り替え方は、ユーザが手動で切り替えてよいし、後述するように、撮像シーンの光量検知を行い、その結果から自動的に切り替えるようにしてもよい。

#### 【 0 0 9 3 】

( 実施例 2 )

50

本発明の別の実施例を説明する。

#### 【0094】

実施例1との差異の一つは、実施例1の第1の動作モードでは、第3の転送部のポテンシャルをHレベル、Lレベル、およびMレベルの三値で制御していたのに対して、本変形例では、第3の転送部のポテンシャルをHレベルおよびLレベル二値で制御する点である。

#### 【0095】

図8は、本変形例に係る画素PIXの断面図と、そのポテンシャルの様子を示す図であって、図4に対応するものである。図4(b)～図4(h)の各々は、図4(b)～図4(h)のそれぞれと対応する。以下では、実施例3との相違点を中心に説明を行う。

10

#### 【0096】

図4に示した実施例1のポテンシャル図に対して、図8に示した本変形例に係るポテンシャル図においては、図8(c)～(h)の期間に、第3の転送部におけるポテンシャルが、第1の転送部よりも低くなっている点である。この結果、図4(c)、(g)、(h)とは異なり、光電変換部で発生した電荷は第3の転送部から電源に排出されない。

#### 【0097】

図9に示すタイミング図は、図5において、信号PTX3(n)～PTX3(n+2)がMレベルとなっている期間に、信号PTX3(n)～PTX3(n+2)がHレベルになる点が異なるのみで、その他は変わらないため、説明を省略する。

20

#### 【0098】

本変形例においても、実施例1と同様に、面内同期型電子シャッタを実現しつつ、面内同期型電子シャッタを実現しながら、第2の保持部をリセットしたことに起因するランダムなノイズ成分も低減することができる。

#### 【0099】

##### (実施例3)

上の実施例では、第1の動作モードと第2の動作モードとを切り替えることを説明した。光電変換装置1は、上述の2つの動作モード以外にも、以下で説明する第3の動作モードも取り得る。図を参照しながら本実施例に係る動作を説明する。

#### 【0100】

図10(a)は、図3に示した構成のうち、遮光幕210やプラグ209、215などを省略して、一部を抜き出して示したものである。図10(a)のように、第1の保持部のポテンシャルを制御する電極207は、第1および第2の転送部のポテンシャルを制御する電極204および207に一部が重なってもよい。

30

#### 【0101】

本実施例において、第1の転送部のポテンシャルを制御する信号PTX1～PTX3がLレベルの状態にあっては、第2および第3の転送部のポテンシャルよりも第1の転送部のポテンシャルが高くなるものを考える。例えば、第1の転送部を、埋め込みチャネルを有する構成にすることで、このような関係にできる。

#### 【0102】

図10(b)～(h)は、それぞれの時刻における、図10(a)に示す画素PIXの各領域のポテンシャルを示す図である。図10(b)～(h)において、横軸は対応する図10(a)の位置を示し、縦軸はポテンシャルを表し、図中下に行くほど正電荷に対するポテンシャルが高くなる。本実施例では、光電変換部PDに蓄積される電荷は電子であるので、電子に対しては、図中上に行くほどポテンシャルが高いことになる。

40

#### 【0103】

図10(b)は、光電変換部PDにも、第1および第2の保持部にも電荷が蓄積されていない状態を示している。この状態で光電変換部PDに光が照射されると、発生した電子が、n-領域に蓄積される。この状態では、電子に対するポテンシャルが、光電変換部PDよりも、第1および第3の転送部の方が高く、光電変換部PDに電荷を蓄積できる。言い換えると、第1および第3の転送部に、電子に対するポテンシャル障壁が形成された状

50

態である。また、第1の転送部の、電子に対するポテンシャルよりも第3の転送部の、電子に対するポテンシャルが高くなっているため、光電変換部PDの飽和電荷量は、第1の転送部のポテンシャルで定まる。これは、第1の転送部に形成される、電子に対するポテンシャル障壁の方が、第3の転送部に形成されるポテンシャル障壁よりも高いと、言い換えることができる。

#### 【0104】

光電変換部PDの露光が進むと、光電変換部PDで発生した電荷量が、光電変換部PDの飽和電荷量を超える。先に説明したとおり、第1の転送部のポテンシャルよりも第3の転送部の、電子に対するポテンシャルが高くなっているため、光電変換部PDの、電子に対する飽和電荷量を超えて発生した電子は、第1の転送部を介して第1の保持部へと流れれる。この様子を図10(c)に示す。図において、黒塗りの部分が電子を表している。つまり、光電変換部PDが飽和した状態で、第1の転送部を通して第1の保持部に保持されている状態である。

#### 【0105】

図10(c)の状態からさらに、光電変換部PDの露光が進むと、光電変換部PDで発生した電子は、第1の転送部のポテンシャルで定まる、第1の保持部の飽和電荷量をも超える。つまり、光電変換部PD、第1の転送部、および第1の保持部に電荷が蓄積される状態となる。この様子を図10(d)に示す。別の言い方をすると、光電変換部PD、第1の転送部、および第1の保持部が、電荷を保持する保持部として機能する。

#### 【0106】

次に、光電変換部PD、第1の転送部、および第1の保持部に保持された電荷を、第2の保持部へと転送する。このとき、光電変換部PDに保持された電荷も十分に転送できるように、電子に対するポテンシャルが、光電変換部PDから第2の保持部へと、勾配を持つようになる。この様子を図10(e)に示す。

#### 【0107】

次に、第2の転送部の、電子に対するポテンシャルを十分に上げ、第1の保持部からの電荷が、第2の保持部に流入しないようにする。また、第1の転送部の、電子に対するポテンシャルを光電変換部PDよりも低くしており、かつ、第3の転送部の、電子に対するポテンシャルを光電変換部PDよりも高くしているので、光電変換部PDで発生した電子は、第3の転送部を介して電源へと排出される。これにより、光電変換部PDをリセットすることができる。この様子を図10(f)に示す。

#### 【0108】

図10(b)～(f)までの動作を、全ての画素に対して同時にを行うことで、面内同期型のシャッタを実現できる。図10(f)の状態で、順次画素を選択することで、第2の保持部に保持された電荷量に応じた信号が画素から読み出される。信号が読み出された後に、第2の保持部はリセットされるものとする。

#### 【0109】

図10(f)に示した状態で、光電変換部PDをリセットした後、第3の転送部の、電子に対するポテンシャルを、光電変換部PDよりも高くすることで、光電変換部PDは、再び電荷を蓄積できる状態になる。この様子を、図10(g)に示す。ここでは、図10(c)と同様に、光電変換部PDの飽和電荷量を超えて、電荷が発生した状態を示している。

#### 【0110】

図10(g)の状態からさらに光電変換部PDの露光が進むと、図10(d)と同様に、光電変換部PD、第1の転送部、および第1の保持部で電荷を保持する状態になる。

#### 【0111】

図10(c)および(d)と、図10(g)および(h)との違いは、第2の保持部に電荷が保持されているか否かである。第2の保持部に保持された電荷量に応じた信号が読み出された後に、第2の保持部がリセットされる。図10(f)～(h)では、第2の保持部がリセットされる前の状態を示している。

10

20

30

40

50

**【0112】**

図10で示した動作を、図2および図11を参照しながら、より詳細に説明する。

**【0113】**

図11に示す信号名は、図2の等価回路図に示した信号と対応している。ここでは、信号PTX1(n)～PTX1(n+2)がLレベルであるときの第1の転送部の、電子に対するポテンシャルは、PTX2(n)～PTX2(n+2)およびPTX3(n)～PTX3(n+2)がLレベルであるときの第2及び第3の転送部の、電子に対するポテンシャルよりも低い構成を考える。

**【0114】**

また、信号PTSおよびPTNは、列回路が備える、サンプルホールドする2つのサンプルホールド回路の動作を制御する信号である。信号がHレベルになることでサンプリングを行い、信号がHレベルからLレベルになることでホールドされる。ここでは、説明を簡単にするために、サンプルホールド回路が、垂直信号線の信号をサンプルホールドする場合を考える。

**【0115】**

時刻T0において、信号PTX1(n)～PTX1(n+2)、PTX2(n)～PTX2(n+2)、PTX3(n)～PTX3(n+2)がHレベルになる。これにより、光電変換部PDで発生した電荷は、第3の転送部もしくは第1および第2の転送部を介して電源へと排出される。

**【0116】**

時刻T1に、信号PTX1(n)～PTX1(n+2)、PTX2(n)～PTX2(n+2)、PTX3(n)～PTX3(n+2)がLレベルになる。この状態が、図10(b)に対応する。時刻T1から、電荷の蓄積期間が開始する。

**【0117】**

時刻T2に、信号PRES(n)～PRES(n+2)がLレベルになり、第2の保持部のリセット状態が解除される。

**【0118】**

時刻T2には、また、信号PTX1(n)～PTX1(n+2)およびPTX2(n)～PTX2(n+2)がHレベルになる。これにより、光電変換部PD、第1の転送部、および第1の保持部に蓄積された電荷が、第2の保持部に転送される。この状態が、図10(e)に対応する。

**【0119】**

時刻T3に、信号PTX1(n)～PTX1(n+2)およびPTX2(n)～PTX2(n+2)がLレベルになると、第1および第2の転送部にポテンシャル障壁が再び形成される。時刻T1～T3までが、蓄積期間である。

**【0120】**

時刻T3には、さらに、信号PTX3(n)～PTX3(n+2)がHレベルになる。これにより、光電変換部PDで発生した電荷は、PDに蓄積されることなく、第3の転送部を介して電源へと排出される。この状態が図10(f)に対応する。

**【0121】**

時刻T4に、信号PSEL1(n)がHレベルになることで、n行目の画素の選択トランジスタが導通し、このときの第2の保持部に保持された電荷量に応じた信号が、垂直信号線に現れる。

**【0122】**

時刻T5から信号PTSが一時的にHレベルになることで、この時刻における垂直信号線のレベルがサンプルホールドされる。ここでサンプルホールドされるレベルは、光電変換に基づく信号に加えて、ノイズが重畠したものである。

**【0123】**

時刻T6から信号PRES(n)が一時的にHレベルになることで、n行目の画素の、第2の保持部がリセットされる。

10

20

30

40

50

## 【0124】

時刻T7から信号PTNが一時的にHレベルになることで、この時刻における垂直信号線のレベルがサンプルホールドされる。ここでサンプルホールドされるレベルは、第2の保持部をリセットしたことに対応するレベルであって、ノイズが含まれる。時刻T5からの動作でサンプルホールドされた信号と、時刻T7からの動作でサンプルホールドされた信号との差分処理を行うことで、両者に共通して含まれる、相関性のあるノイズ成分を低減することができる。

## 【0125】

時刻T8に、信号PTX3(n)～PTX3(n+2)がLレベルになると、第3の転送部における、電子に対するポテンシャルが、光電変換部PDにおけるポテンシャルよりも高くなるので、光電変換部PDで電荷を再び蓄積できる状態になる。時刻T8が、次のフレームの露光時間の開始時刻である。10

## 【0126】

時刻T9に、信号PSEL1(n)がLレベルになると、n行目の画素が持つ選択トランジスタSELがオフになり、増幅トランジスタSFと垂直信号線との電気的な接続が遮断される。また、時刻T9には、信号PRESS(n)がHレベルになることで、第2の保持部がリセットされた状態になる。

## 【0127】

時刻T10から時刻T14までの動作、ならびに時刻T15から時刻T19までの動作は、信号PTX3(n)～PTX3(n+2)がLレベルに維持される点を除いては、時刻T4から時刻T8までの動作が、n+1行目ならびにn+2行目の画素について行われるものである。20

## 【0128】

時刻T20からは、時刻T0から時刻T19までの動作が繰り返される。

## 【0129】

図10(g)および(h)は、時刻T8から時刻T12におけるn+1行目の画素または、時刻T8から時刻T17におけるn+2行目の画素の様子を示している。つまり、時刻T1から時刻T3までの露光期間で蓄積した電荷が、それぞれの画素の第2の保持部に保持された状態であって、次のフレームのための電荷蓄積が、光電変換部PDおよび第1の保持部で行われる状態を示している。30

## 【0130】

ところで、図11においては、信号PTX3(n)～PTX3(n+2)が、時刻T3から時刻T8までの期間にHレベルになっている。しかしながら、信号PTX3(n)～PTX3(n+2)がLレベルになる時刻T8は、時刻T3よりも後であって、かつ、時刻T16からHレベルになる信号PTSが再びLレベルになるまでの期間で、任意に設定してよい。具体的な設定の仕方としては、入射光量に応じて蓄積時間を変更することが考えられる。

## 【0131】

本実施例で説明した第3の動作モードによれば、第1のフレームの露光期間で発生した電荷を複数の行の画素に対して同時に第2の保持部に転送することで面内同期型電子シャッタを実現することができる。さらに、第2の保持部に保持された電荷に基づく信号が、各画素から読み出されるまでの間も、光電変換部PDと第1の保持部とで、第1のフレームに続く第2のフレームのための電荷蓄積を行える。40

## 【0132】

従来は、各画素から信号が読み出されるまでの間に発生した電荷は第3の転送部から電源へと排出されていたので、光電変換装置の感度が十分でないおそれがあった。これに対して、本実施例によれば、面内同期型電子シャッタを実現しつつ、光電変換装置の時間的な解像度を向上させることができる。本実施例によれば、第1から第3の動作モードを選択的に実行することができる。

## 【0133】

(実施例 4 )

実施例 3 では、光電変換装置 1 は、第 1 および第 2 の動作モードに加えて、第 3 の動作モードでも動作しうることを説明した。次に、第 3 の動作モードの変形例を説明する。

【 0 1 3 4 】

実施例 2 との差異の一つは、実施例 2 では、例えば、第 1 の転送部を、埋め込みチャネルを有する構成にしていたのに対して、本変形例では、第 1 の転送部のポテンシャルを制御することによって、同様の関係を実現する点である。本変形例では、第 1 の転送部のポテンシャルを制御する信号 P T X 1 ~ P T X 3 が L レベルの状態にあっては、第 1 から第 3 の転送部のポテンシャルが等しくなる場合を考える。具体的には、第 1 から第 3 の転送部を同様の構成にすることが考えられる。

10

【 0 1 3 5 】

図 12 は、本実施例に係る画素 P I X の断面図と、そのポテンシャルの様子を示す図であって、図 10 に対応するものである。図 12 ( b ) ~ 図 12 ( h ) の各々は、図 10 ( b ) ~ 図 10 ( h ) のそれぞれと対応する。以下では、実施例 1 との相違点を中心に説明を行う。

【 0 1 3 6 】

図 12 ( b ) と図 10 ( b ) との違いは、第 1 の転送部のポテンシャルが、第 2 及び第 3 の転送部のポテンシャルと同じになっている点である。これは、実施例 2 とは異なり、第 1 の転送部を第 2 及び第 3 の転送部と同様の構成にしていることに起因する。

20

【 0 1 3 7 】

また、図 12 ( f ) においても、第 1 の転送部のポテンシャルが、第 2 及び第 3 の転送部のポテンシャルと同じになっている。

【 0 1 3 8 】

図 12 ( b ) および図 12 ( f ) 以外のタイミングにおけるポテンシャルの関係は、図 10 と共に通るので説明を省略する。

【 0 1 3 9 】

図 13 は、本変形例における動作を説明するためのタイミング図であって、実施例 2 の図 11 と対応するものである。

【 0 1 4 0 】

図 11 に示した動作と異なる点は、信号 P T X 1 ( n ) ~ P T X 1 ( n + 2 ) が H レベルと L レベルだけでなく、両者の中間 ( M i d d l e ; M ) レベルを含む 3 値を取ることである。

30

【 0 1 4 1 】

本変形例では、時刻 T 1 から時刻 T 3 までの期間および時刻 T 8 から始まる露光期間において、信号 P T X 1 ( n ) ~ P T X 1 ( n + 2 ) を M レベルとして、実施例 2 と同様の動作を実現できる。

【 0 1 4 2 】

第 1 の転送部を少なくとも 3 値を取り得る信号で制御することにより、埋め込みチャネルを有する構成でなくとも、同様の動作ができる。また、信号 P T X 1 ~ P T X 3 が L レベルの状態にあっては、第 1 から第 3 の転送部のポテンシャルが等しくなるので、光電変換部 P D の飽和電荷量が多くなる。このことを利用して、露光期間に光電変換部 P D のみで電荷を保持させ、光電変換部 P D から第 1 の保持部へ電荷を転送することで面内同期型電子シャッタを実現することもできるようになる。そのため、例えば、被写体の輝度が高いとあらかじめ分かっている場合には、本変形例の動作に切り替えて、露光期間における飽和電荷量を増大することができる。

40

【 0 1 4 3 】

なお、信号 P T X 1 ~ P T X 3 が L レベルの状態における、第 1 から第 3 の転送部のポテンシャルが等しくなる場合を説明したが、これらのポテンシャルは厳密に一致していないてもよい。

【 0 1 4 4 】

50

(実施例 5 )

次に、本発明の別の実施例を説明する。

【 0 1 4 5 】

図 1 4 は、本実施例に係る画素 P I X の断面図と、そのポテンシャルの様子を示す図であって、実施例 1 の図 4 に対応するものである。図 1 4 ( b ) ~ ( h ) の各々は、図 1 0 ( b ) ~ 図 1 0 ( h ) のそれぞれと対応する。以下では、実施例 2 で説明した第 3 の動作モードとの相違点を中心に説明する。

【 0 1 4 6 】

実施例 3 との差異の一つは、光電変換部 P D と電源との間に設けられた第 3 の転送部のポテンシャルが、少なくとも 3 値を取る点である。

10

【 0 1 4 7 】

図 1 4 ( c ) および ( d ) で示す画素の露光期間において、本実施例では、第 3 の転送部のポテンシャルが、電子に対して、第 1 の転送部よりも低く、かつ、第 2 の転送部よりも高い点で、実施例 1 とは異なる。同様に、図 1 4 ( g ) および ( h ) に示した露光期間においても、第 3 の転送部のポテンシャルが、電子に対して、第 1 の転送部よりも高く、かつ、第 2 の転送部よりも低い。

【 0 1 4 8 】

少なくとも画素の露光期間において、上述のような関係を保つことにより、光電変換部 P D 、第 1 の転送部、および第 1 の保持部の飽和電荷量を超えて電荷が過剰に発生したとしても、過剰に発生した電荷は第 2 の保持部には流れずに、第 3 の転送部を介して電源へと排出される。つまり、第 2 の保持部に保持された、先の露光期間で発生した電荷と混ざりにくいという利点がある。

20

【 0 1 4 9 】

図 1 5 は、本実施例における動作を説明するためのタイミング図であって、実施例 2 の図 1 1 と対応するものである。

【 0 1 5 0 】

図 1 1 に示した動作と異なる点は、信号 P T X 3 ( n ) ~ P T X 3 ( n + 2 ) が H レベルと L レベルだけでなく、両者の中間 ( M i d d l e ; M ) レベルを含む 3 値を取ることである。

【 0 1 5 1 】

30

本実施例では、時刻 T 1 から時刻 T 3 までの期間および時刻 T 8 から始まる露光期間において、信号 P T X 3 ( n ) ~ P T X 3 ( n + 2 ) を M レベルとしていることで、図 1 4 で説明した動作を実行できる。M レベルは、画素の露光期間において、第 3 の転送部のポテンシャルが、電子に対して、第 1 の転送部よりも高く、かつ、第 2 の転送部よりも低くなる範囲で、任意に設定できる。

【 0 1 5 2 】

(実施例 6 )

本発明に係る別の実施例を説明する。

【 0 1 5 3 】

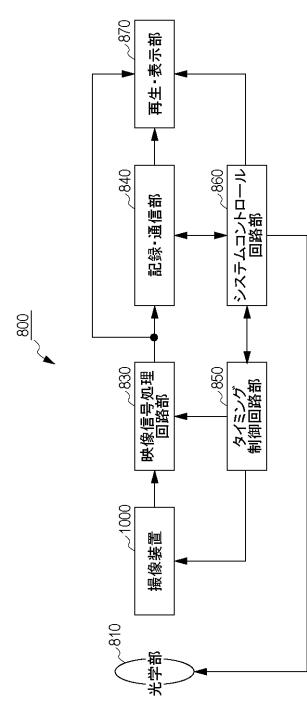

本実施例に係る撮像システムの概略を、図 1 6 を用いて説明する。

40

【 0 1 5 4 】

撮像システム 8 0 0 は、例えば、光学部 8 1 0 、撮像装置 1 0 0 0 、映像信号処理回路部 8 3 0 、記録・通信部 8 4 0 、タイミング制御回路部 8 5 0 、システムコントロール回路部 8 6 0 、および再生・表示部 8 7 0 を含む。撮像装置 1 0 0 0 は、先述の各実施例で説明した光電変換装置が用いられる。ここでは、図 1 に示した制御部 3 が、撮像装置ではなく、タイミング制御回路部 8 5 0 に含まれる場合を例示している。

【 0 1 5 5 】

レンズなどの光学系である光学部は 8 1 0 、被写体からの光を撮像装置 1 0 0 0 の、複数の画素が 2 次元状に配列された画素アレイに結像させ、被写体の像を形成する。撮像装置 1 0 0 0 は、タイミング制御回路部 8 5 0 からの信号に基づくタイミングで、画素部に

50

結像された光に応じた信号を出力する。

【0156】

撮像装置1000から出力された信号は、映像信号処理部である映像信号処理回路部830に入力され、映像信号処理回路部830が、プログラムなどによって定められた方法に従って、入力された電気信号に対してA/D変換などの処理を行う。映像信号処理回路部での処理によって得られた信号は画像データとして記録・通信部840に送られる。記録・通信部840は、画像を形成するための信号を再生・表示部870に送り、再生・表示部870に動画や静止画像が再生・表示させる。記録通信部は、また、映像信号処理回路部830からの信号を受けて、システムコントロール回路部860とも通信を行うほか、不図示の記録媒体に、画像を形成するための信号を記録する動作も行う。

10

【0157】

システムコントロール回路部860は、撮像システムの動作を統括的に制御するものであり、光学部810、タイミング制御回路部850、記録・通信部840、および再生・表示部870の駆動を制御する。また、システムコントロール回路部860は、例えば記録媒体である不図示の記憶装置を備え、ここに撮像システムの動作を制御するのに必要なプログラムなどが記録される。また、システムコントロール回路部860は、例えばユーザの操作に応じて駆動モードを切り替える信号を撮像システム内で供給する。具体的な例としては、読み出す行やリセットする行の変更、電子ズームに伴う画角の変更や、電子防振に伴う画角のずらしなどである。このほか、システムコントロール回路部860は、先の実施例における、動作モードの切り替えや実施例4におけるデジタルセレクタの出力の切り替えを行う。

20

【0158】

タイミング制御回路部850は、制御部であるシステムコントロール回路部860による制御に基づいて撮像装置1000および映像信号処理回路部830の駆動タイミングを制御する。

【0159】

映像信号処理回路部830は、先述の各実施例で説明した補正係数を保持し、撮像装置1000から出力された信号に対して補正処理を行う。

【0160】

撮像システムは、さらに光量検知用のセンサを備えてもよい。先述したように、光量検知用のセンサで検出した光量によって、システムコントロール回路部860が光電変換装置の動作を切り替えることができる。

30

【0161】

以上で説明した各実施例は、本発明を説明するための例示的なものであって、本発明の技術的思想を逸脱しない範囲で様々に変更あるいは組み合わせることが可能である。

【0162】

(その他)

上記の各実施例は、本発明を説明するための例示的なものに過ぎず、本発明の思想を逸脱しない範囲で構成を変えたり、他の実施例と組み合わせたりすることができる。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

---

フロントページの続き

(72)発明者 豊口 銀二郎

東京都大田区下丸子3丁目30番2号キヤノン株式会社内

(72)発明者 鈴木 建

東京都大田区下丸子3丁目30番2号キヤノン株式会社内

審査官 鈴木 肇

(56)参考文献 特開2009-253818(JP,A)

特開平03-114265(JP,A)

特開2010-093644(JP,A)

特開2009-296574(JP,A)

(58)調査した分野(Int.Cl., DB名)

H04N 5/30 - 5/378

H01L 21/339

H01L 27/14 - 27/148

H01L 29/762