(12) 发明专利

(10) 授权公告号 CN 112420832 B

(45) 授权公告日 2023.08.29

(21) 申请号 202010057721.1

(51) Int.CI.

(22) 申请日 2020.01.19

H01L 29/78 (2006.01)

(65) 同一申请的已公布的文献号

H01L 29/423 (2006.01)

申请公布号 CN 112420832 A

H01L 29/06 (2006.01)

(43) 申请公布日 2021.02.26

(56) 对比文件

(30) 优先权数据

CN 106463541 A, 2017.02.22

2019-152836 2019.08.23 JP

JP H08264764 A, 1996.10.11

(73) 专利权人 株式会社东芝

US 2008073707 A1, 2008.03.27

地址 日本东京都

US 2017047316 A1, 2017.02.16

专利权人 东芝电子元件及存储装置株式会

社

US 2017263768 A1, 2017.09.14

WO 2017159034 A1, 2017.09.21

(72) 发明人 西胁达也

审查员 杨蕾

(74) 专利代理机构 永新专利商标代理有限公司

72002

权利要求书2页 说明书8页 附图15页

(54) 发明名称

半导体装置

(57) 摘要

实施方式提供能够减小导通电阻的半导体装置。半导体装置具有第1电极、第1导电型的第1半导体区域、第2导电型的第2半导体区域、第1导电型的第3半导体区域、第1绝缘部、第2电极、栅极电极、第2绝缘部以及第3电极。第2电极设置在第1绝缘部中，具有在第2方向上与第1半导体区域对置的部分。栅极电极设置在第1绝缘部中，在第2方向上隔着栅极绝缘层而与第2半导体区域对置，与第2电极电分离。第2绝缘部与第1绝缘部相连。第2绝缘部的第1方向上的长度比第1半导体区域与第2电极之间的第1绝缘部的厚度长。第2绝缘部的第2方向上的长度比第1绝缘部的厚度的2倍短。第3电极与第2半导体区域、第3半导体区域以及第2电极电连接。

1. 一种半导体装置,其中,具备:

第1电极;

第1导电型的第1半导体区域,设置在上述第1电极之上,与上述第1电极电连接;

第2导电型的第2半导体区域,设置在上述第1半导体区域之上;

第1导电型的第3半导体区域,在上述第2半导体区域之上选择性地设置;

第1绝缘部,在与从上述第1电极朝向上述第1半导体区域的第1方向垂直的第2方向上,与上述第1半导体区域的一部分、上述第2半导体区域以及上述第3半导体区域并排;

第2电极,设置在上述第1绝缘部中,具有在上述第2方向上与上述第1半导体区域对置的部分;

栅极电极,设置在上述第1绝缘部中,在上述第2方向上隔着栅极绝缘层而与上述第2半导体区域对置,并与上述第2电极电分离;

第2绝缘部,与上述第1绝缘部相连,上述第2绝缘部的上述第1方向上的长度比上述第1半导体区域与上述第2电极之间的上述第1绝缘部的厚度长,上述第2方向上的长度比上述第1绝缘部的厚度的2倍短;以及

第3电极,设置在上述第2半导体区域以及上述第3半导体区域之上,与上述第2半导体区域、上述第3半导体区域以及上述第2电极电连接。

2. 如权利要求1所述的半导体装置,其中,

还具备设置在上述第1电极与上述第1半导体区域之间的第1导电型的第4半导体区域;

上述第4半导体区域中的第1导电型的杂质浓度比上述第1半导体区域中的第1导电型的杂质浓度高;

上述第2绝缘部的下端在上述第1方向上与上述第4半导体区域分离。

3. 如权利要求1或2所述的半导体装置,其中,

上述第2绝缘部的上述第2方向上的长度越朝向下方越短。

4. 如权利要求1或2所述的半导体装置,其中,

上述第1绝缘部、上述第2绝缘部、上述栅极电极以及上述第2电极各自在上述第2方向上被设置多个;

上述第1半导体区域具有:

第1部分,位于在上述第2方向上相邻的上述第1绝缘部彼此之间;以及

第2部分,位于在上述第2方向上相邻的上述第2绝缘部彼此之间;

上述第2部分的上述第2方向上的长度比上述第1部分的上述第2方向上的长度长。

5. 如权利要求4所述的半导体装置,其中,

上述第1绝缘部、上述第2绝缘部、上述栅极电极以及上述第2电极各自在与上述第1方向垂直且与上述第2方向交叉的第3方向上被设置多个;

上述第2绝缘部的上述第3方向上的长度比上述第1绝缘部的厚度的2倍短。

6. 如权利要求5所述的半导体装置,其中,

上述第1半导体区域具有:

第3部分,位于在上述第3方向上相邻的上述第1绝缘部彼此之间;以及

第4部分,位于在上述第3方向上相邻的上述第2绝缘部彼此之间;

上述第4部分的上述第3方向上的长度比上述第3部分的上述第3方向上的长度长。

7. 如权利要求1或2所述的半导体装置,其中,

在上述第2绝缘部设有空隙。

8. 如权利要求1或2所述的半导体装置,其中,

上述第1绝缘部以及上述第2绝缘部包含氧化硅。

9. 如权利要求1或2所述的半导体装置,其中,

上述第2绝缘部的上述第1方向上的上述长度相对于上述第2电极的上述第1方向上的

长度的比为0.5以上2.0以下。

10. 如权利要求1或2所述的半导体装置,其中,

上述第2绝缘部的上述第2方向上的上述长度相对于上述第2电极的上述第2方向上的

长度的比为0.5以上2.0以下。

11. 如权利要求1或2所述的半导体装置,其中,

上述第1电极与上述第2绝缘部之间的上述第1方向上的距离相对于上述第1电极与上

述第2半导体区域之间的上述第1方向上的距离的比为0.1以上0.5以下。

## 半导体装置

[0001] 关联申请

[0002] 本申请享受以日本专利申请2019-152836号(申请日:2019年8月23日)为基础申请的优先权。本申请通过参照该基础申请,包括该基础申请的全部内容。

### 技术领域

[0003] 本发明的实施方式涉及半导体装置。

### 背景技术

[0004] 金属氧化物半导体场效应晶体管(Metal Oxide Semiconductor Field Effect Transistor, MOSFET)等半导体装置用于电力转换等用途。期望的是,半导体装置的导通电阻低。

### 发明内容

[0005] 本发明的实施方式提供能够减小导通电阻的半导体装置。

[0006] 实施方式的半导体装置具有第1电极、第1导电型的第1半导体区域、第2导电型的第2半导体区域、第1导电型的第3半导体区域、第1绝缘部、第2电极、栅极电极、第2绝缘部、以及第3电极。上述第1半导体区域设置在上述第1电极之上,与上述第1电极电连接。上述第2半导体区域设置在上述第1半导体区域之上。上述第3半导体区域在上述第2半导体区域之上选择性地设置。上述第1绝缘部在与从上述第1电极朝向上述第1半导体区域的第1方向垂直的第2方向上,与上述第1半导体区域的一部分、上述第2半导体区域以及上述第3半导体区域并排。上述第2电极设置在上述第1绝缘部中,具有在上述第2方向上与上述第1半导体区域对置的部分。上述栅极电极设置在上述第1绝缘部中,在上述第2方向上隔着栅极绝缘层而与上述第2半导体区域对置,并与上述第2电极电分离。上述第2绝缘部与上述第1绝缘部相连。上述第2绝缘部的上述第1方向上的长度比上述第1半导体区域与上述第2电极之间的上述第1绝缘部的厚度长。上述第2绝缘部的上述第2方向上的长度比上述第1绝缘部的厚度的2倍短。上述第3电极设置在上述第2半导体区域以及上述第3半导体区域之上,与上述第2半导体区域、上述第3半导体区域、以及上述第2电极电连接。

### 附图说明

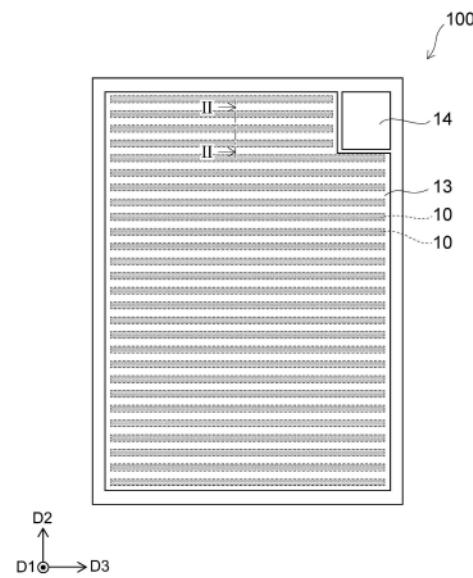

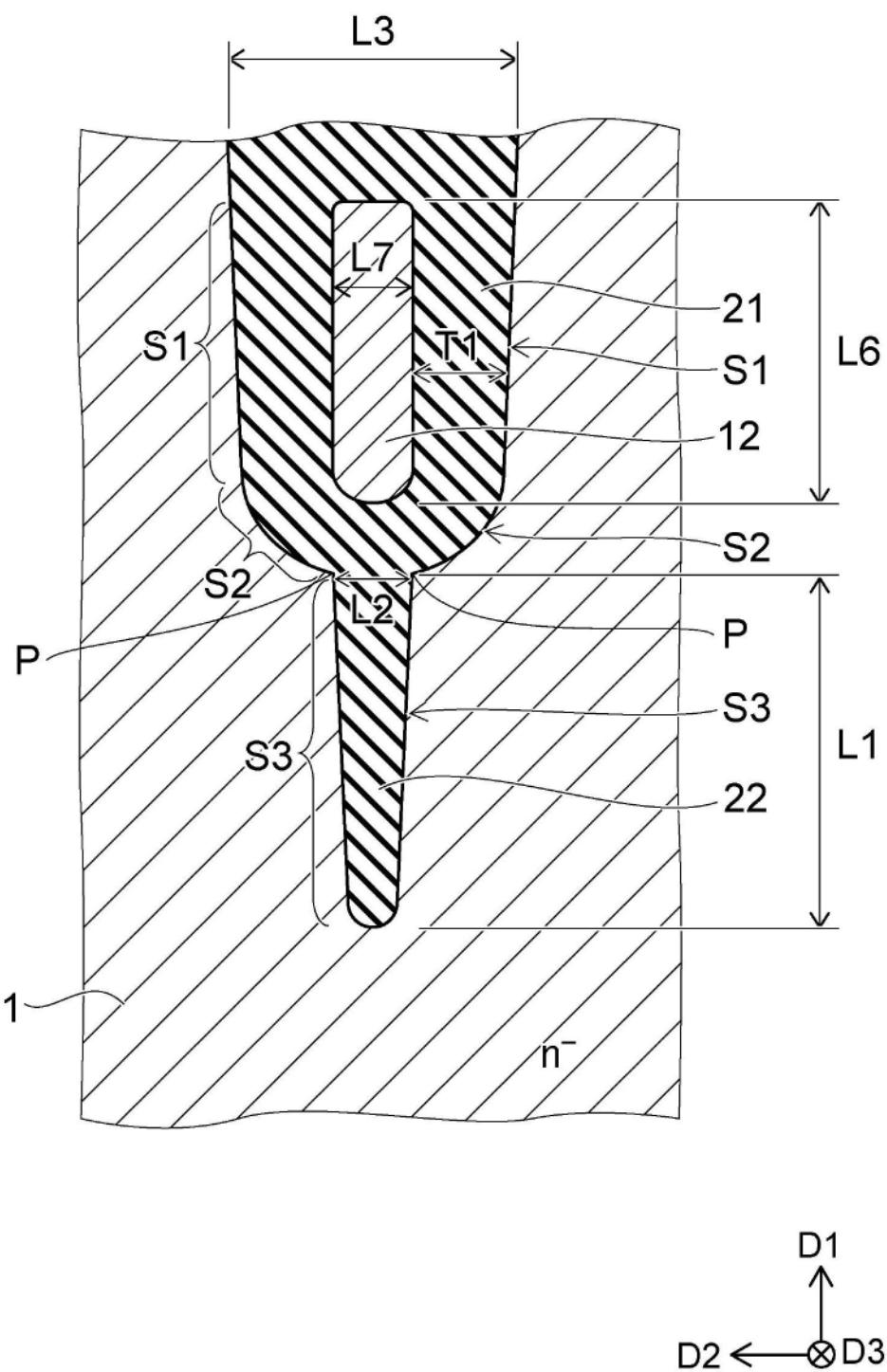

[0007] 图1是表示第1实施方式的半导体装置的俯视图。

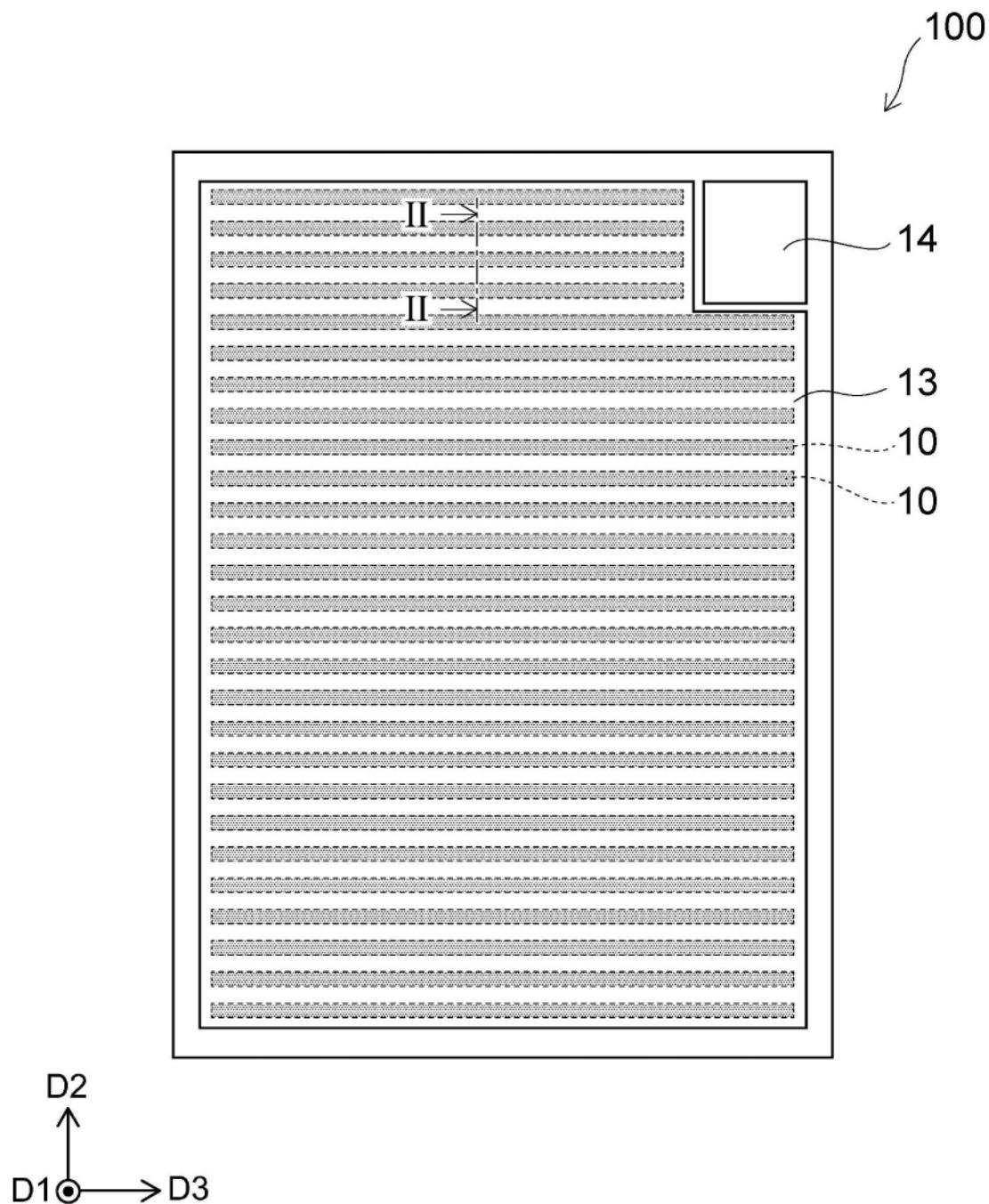

[0008] 图2是包含图1的II-II截面的立体截面图。

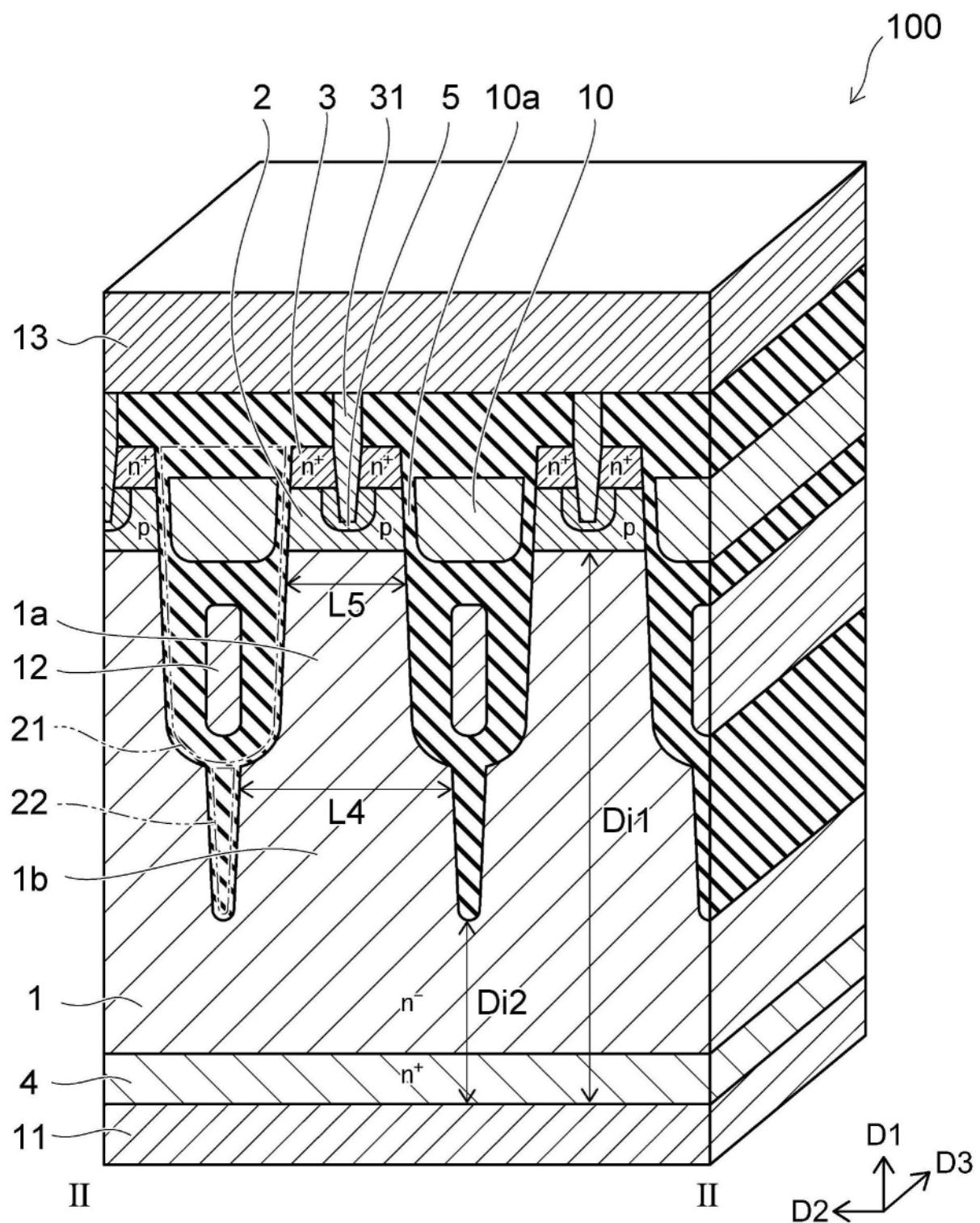

[0009] 图3是将图2的场板电极附近放大后的截面图。

[0010] 图4的(a)~图8的(b)是表示第1实施方式的半导体装置的制造工序的工序截面图。

[0011] 图9是表示第1实施方式的第1变形例的半导体装置的一部分的立体截面图。

[0012] 图10是表示第1实施方式的第2变形例的半导体装置的一部分的立体截面图。

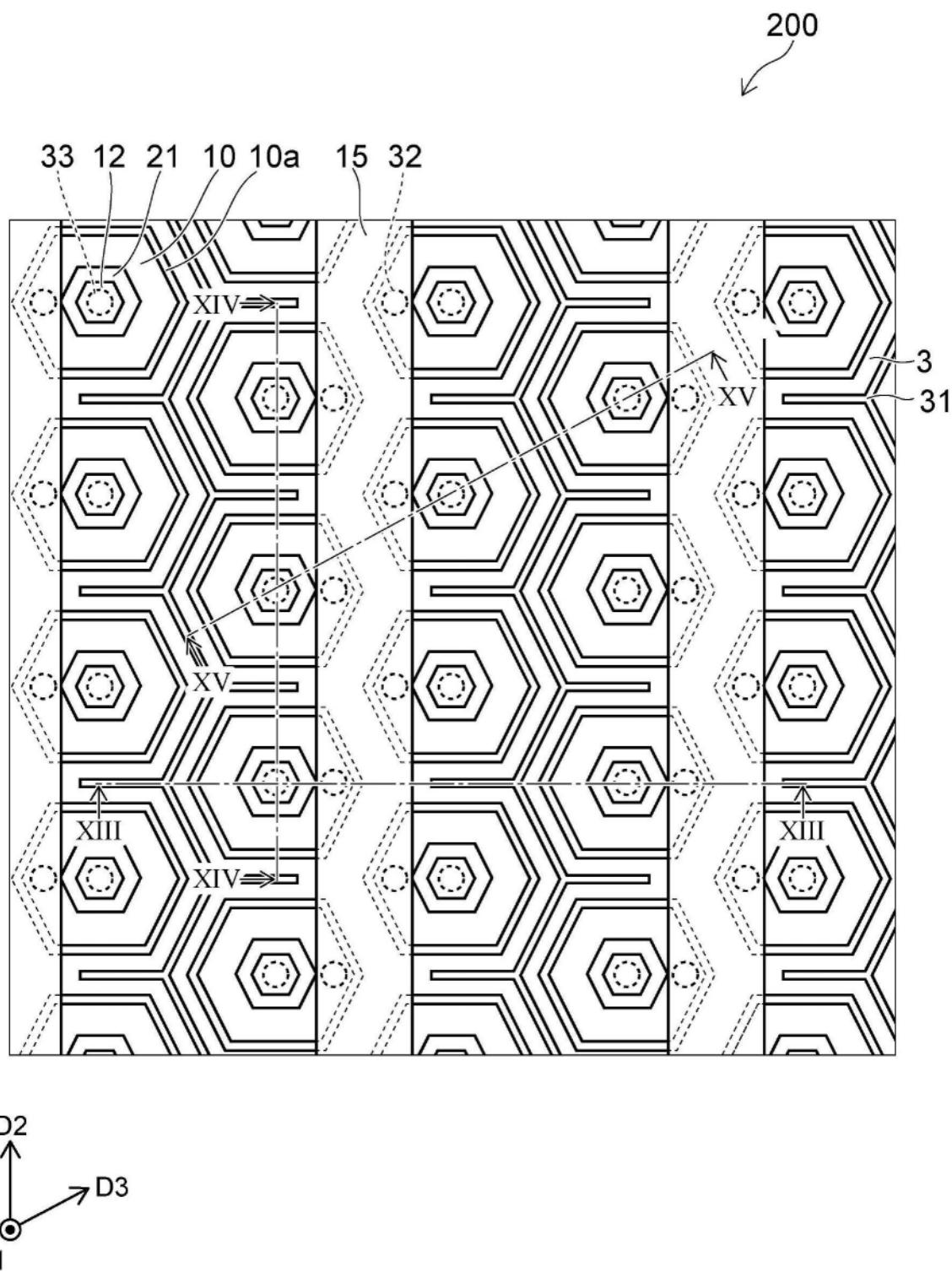

- [0013] 图11是表示第2实施方式的半导体装置的俯视图。

- [0014] 图12是表示图11的部分XII的俯视图。

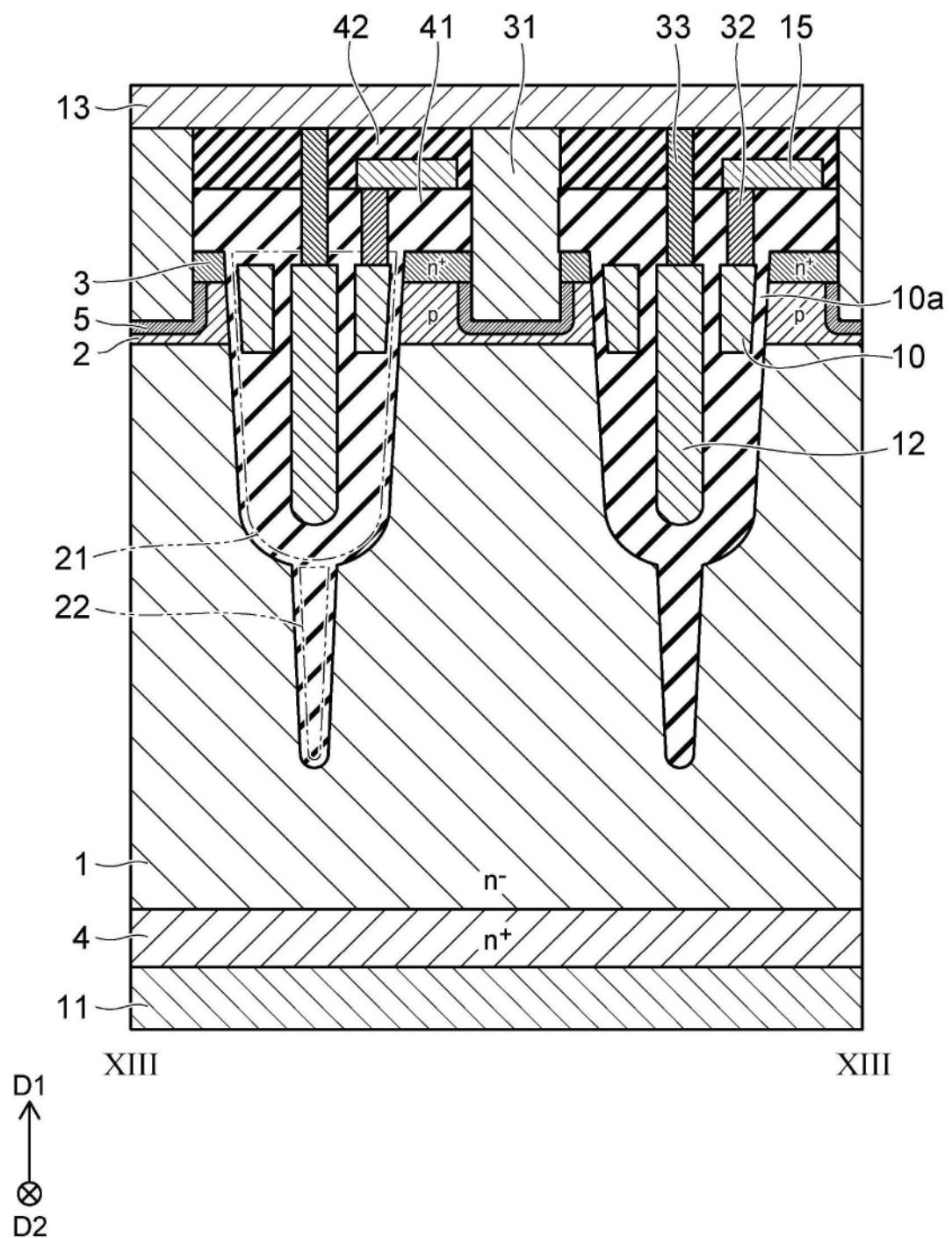

- [0015] 图13是图12的XIII—XIII截面图。

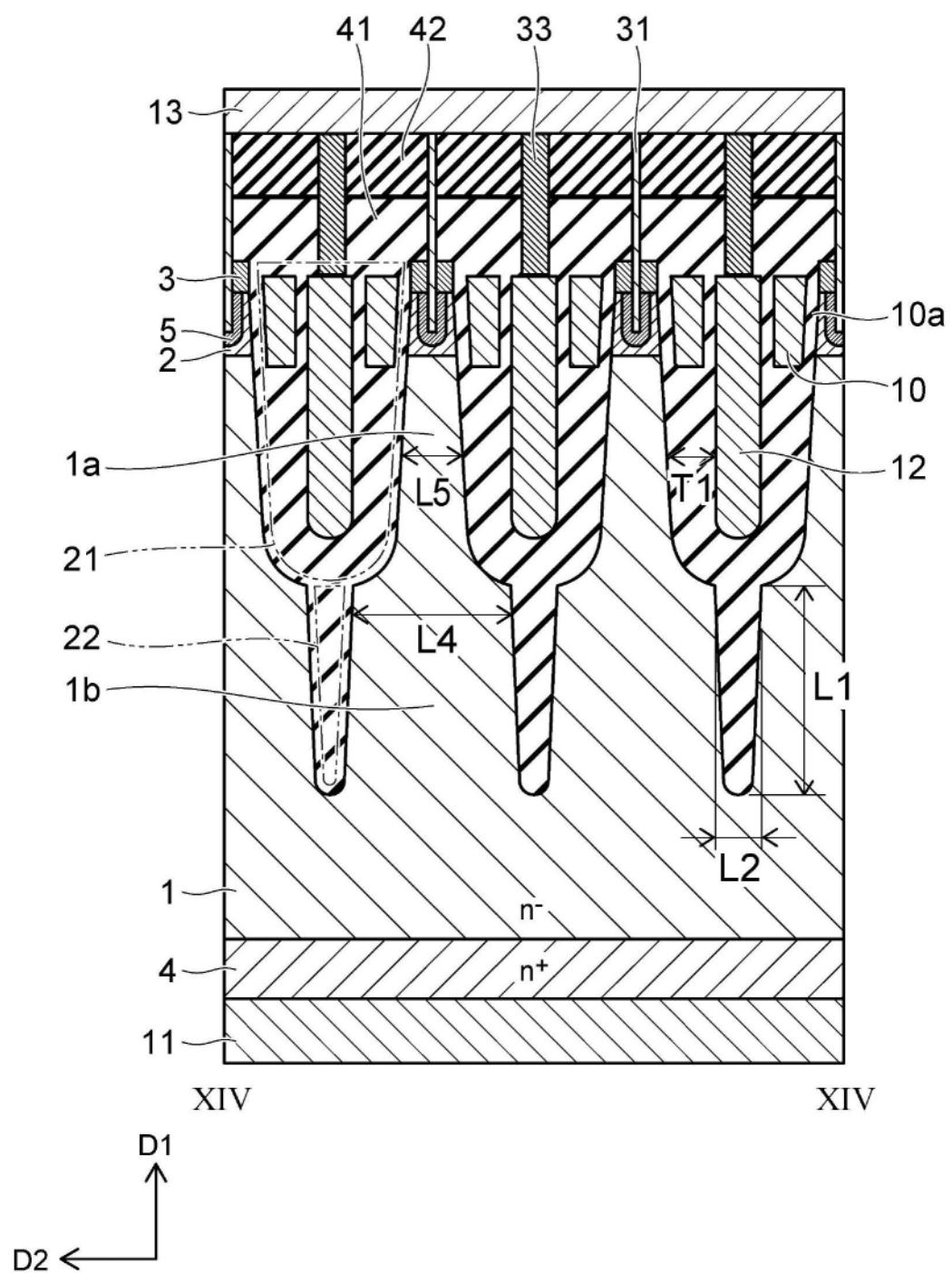

- [0016] 图14是图12的XIV—XIV截面图。

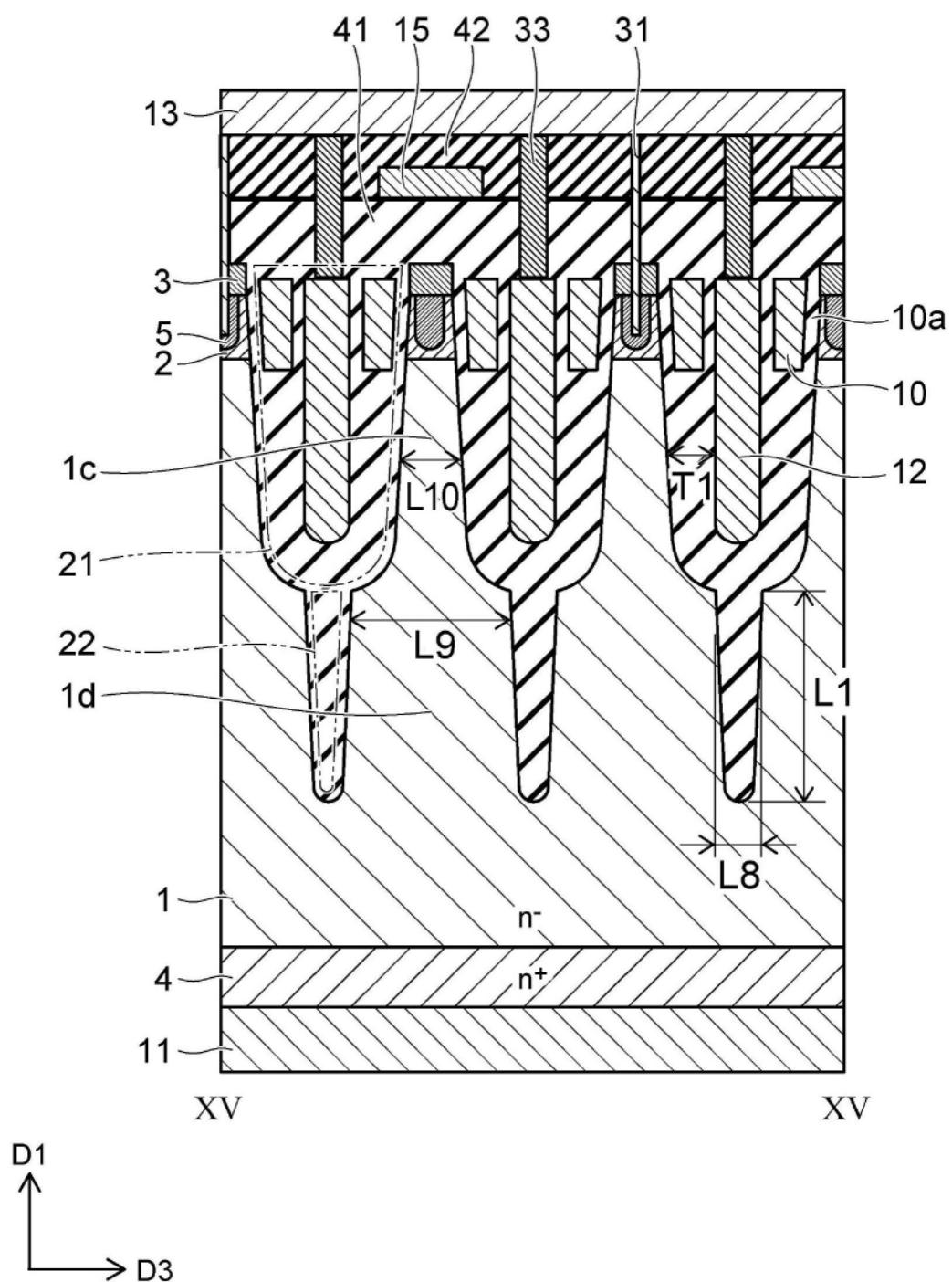

- [0017] 图15是图12的XV—XV截面图。

## 具体实施方式

- [0018] 以下,参照附图对本发明的各实施方式进行说明。

- [0019] 附图是示意性或概念性的,各部分的厚度与宽度之间的关系、部分间的大小的比率等不一定与现实的相同。即使在表示相同部分的情况下,也有根据附图而将彼此的尺寸或比率不同地表示的情况。

- [0020] 在本申请说明书和各图中,对于与已经说明过的要素相同的要素赋予相同的标号并适当省略详细的说明。

- [0021] 以下的说明以及附图中, $n^+$ 、 $n^-$ 以及 $p^+$ 、 $p$ 标记表示各杂质浓度的相对的高低。即,带有“+”的标记表示与不带有“+”以及“-”中的任何一个的标记相比杂质浓度相对高,带有“-”的标记表示与不带有“+”以及“-”中的任何一个的标记相比杂质浓度相对低。在各个区域中包含p型杂质和n型杂质双方的情况下,这些标记表示这些杂质相互补偿后的净杂质浓度的相对高低。

[0022] 对于以下说明的各实施方式,也可以使各半导体区域的p型与n型反转来实施各实施方式。

### [0023] (第1实施方式)

- [0024] 图1是表示第1实施方式的半导体装置的俯视图。

- [0025] 图2是包含图1的II—II截面的立体截面图。

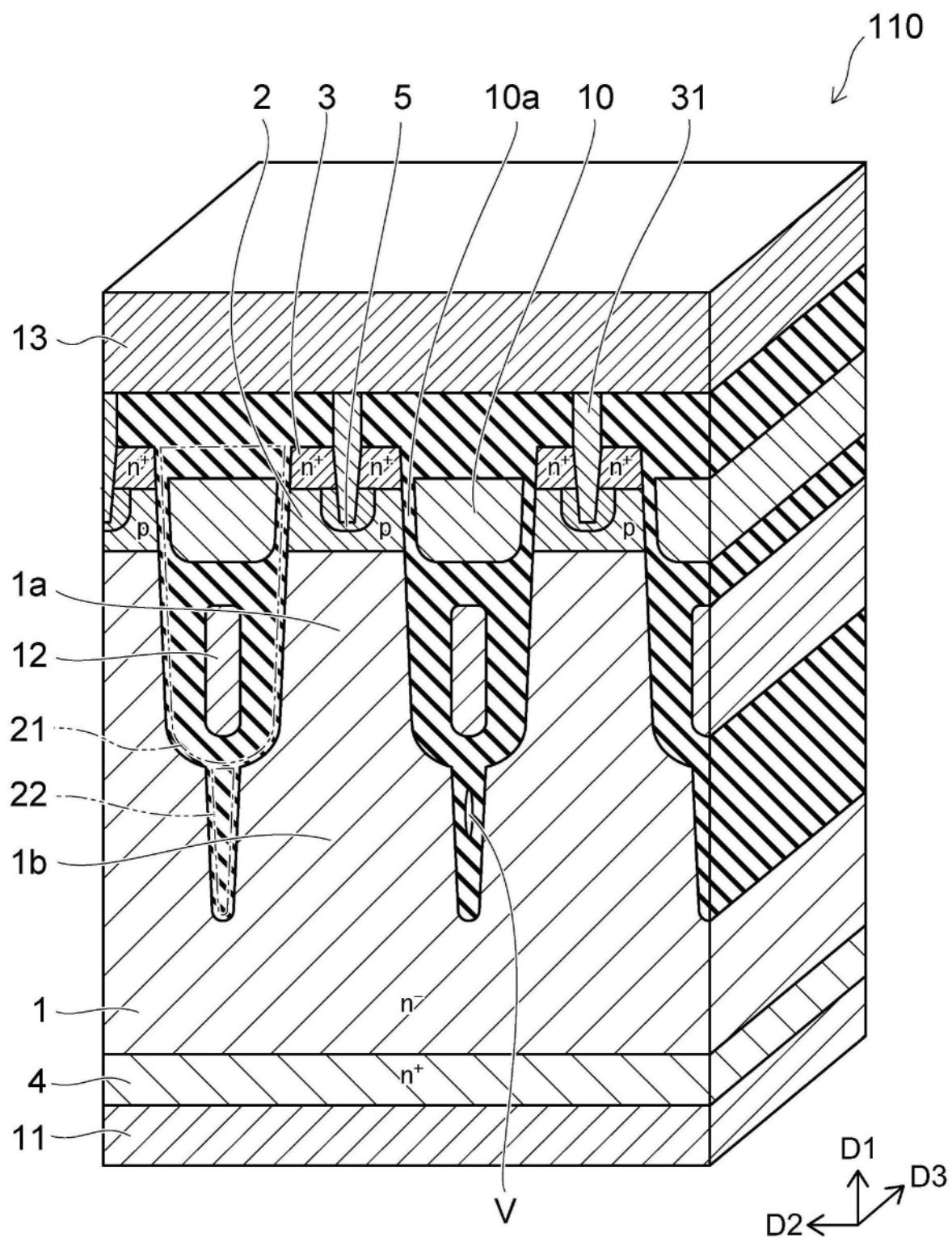

- [0026] 第1实施方式的半导体装置例如是MOSFET。如图1及图2所示,第1实施方式的半导体装置100具有 $n^-$ 型(第1导电型)漂移区域1(第1半导体区域)、 $p$ 型(第2导电型)基底区域2(第2半导体区域)、 $n^+$ 型源极区域3(第3半导体区域)、 $n^+$ 型漏极区域4、 $p^+$ 型接触区域5、栅极电极10、漏极电极11(第1电极)、FP电极12(第2电极)、源极电极13(第3电极)、栅极焊盘14、第1绝缘部21、第2绝缘部22、以及连接部31。

[0027] 以下的各实施方式的说明中,使用第1方向D1、第2方向D2以及第3方向D3。将从漏极电极11朝向 $n^-$ 型漂移区域1的方向设为第1方向D1。将与第1方向D1垂直的一方向设为第2方向D2。将与第1方向D1垂直且与第2方向D2交叉的方向设为第3方向D3。此外,为了便于说明,将从漏极电极11朝向 $n^-$ 型漂移区域1的方向称为“上”,将其相反方向称为“下”。这些方向基于漏极电极11与 $n^-$ 型漂移区域1的相对的位置关系,与重力方向无关。

[0028] 如图1所示,在半导体装置100的上表面设有源极电极13以及栅极焊盘14。源极电极13和栅极焊盘14相互电分离。图1中,对设置在源极电极13之下的栅极电极10赋予点框来表示。如图1所示,栅极电极10在第2方向D2上被设置多个,各栅极电极10沿第3方向D3延伸。在该例中,第3方向D3相对于第2方向D2垂直。

[0029] 如图2表示,在半导体装置100的下表面设有漏极电极11。在漏极电极11之上,隔着 $n^+$ 型漏极区域4设有 $n^-$ 型漂移区域1。 $n^-$ 型漂移区域1经由 $n^+$ 型漏极区域4而与漏极电极11电

连接。p型基底区域2设置在n<sup>-</sup>型漂移区域1之上。n<sup>+</sup>型源极区域3以及p<sup>+</sup>型接触区域5在p型基底区域2之上选择性地设置。

[0030] 第1绝缘部21在第2方向D2上与n<sup>-</sup>型漂移区域1的一部分、p型基底区域2以及n<sup>+</sup>型源极区域3并排。栅极电极10以及FP电极12设置在第1绝缘部21中。FP电极12在第2方向D2上与n<sup>-</sup>型漂移区域1对置。栅极电极10设置在FP电极12之上。栅极电极10在第2方向D2上隔着作为第1绝缘部21的一部分的栅极绝缘层10a而与p型基底区域2对置。半导体装置100中，栅极电极10隔着栅极绝缘层10a还与n<sup>-</sup>型漂移区域1的一部分以及n<sup>+</sup>型源极区域3的一部分对置。在栅极电极10与FP电极12之间设有第1绝缘部21的一部分。由此，栅极电极10与FP电极12相互电分离。

[0031] 第2绝缘部22设置在第1绝缘部21之下，并与第1绝缘部21相连。FP电极12仅设置在第1绝缘部21中。即，FP电极12没有设置在第2绝缘部22中。

[0032] 源极电极13设置在n<sup>+</sup>型源极区域3、p<sup>+</sup>型接触区域5以及栅极电极10之上，与n<sup>+</sup>型源极区域3、p<sup>+</sup>型接触区域5、FP电极12电连接。半导体装置100中，在一个p型基底区域2之上设有一个p<sup>+</sup>型接触区域5以及两个n<sup>+</sup>型源极区域3。p<sup>+</sup>型接触区域5位于比n<sup>+</sup>型源极区域3靠下方的位置。连接部31的一部分在第2方向D2上位于n<sup>+</sup>型源极区域3彼此之间。n<sup>+</sup>型源极区域3以及p<sup>+</sup>型接触区域5经由连接部31而与源极电极13电连接。p型基底区域2经由p<sup>+</sup>型接触区域5以及连接部31而与源极电极13电连接。栅极电极10与源极电极13电分离，并与栅极焊盘14电连接。

[0033] 例如，p型基底区域2、n<sup>+</sup>型源极区域3、p<sup>+</sup>型接触区域5、栅极电极10、FP电极12、第1绝缘部21以及第2绝缘部22在第2方向D2上被设置多个，分别沿第3方向D3延伸。此外，n<sup>-</sup>型漂移区域1具有第1部分1a以及第2部分1b。第1部分1a位于在第2方向D2上相邻的第1绝缘部21彼此之间。第2部分1b位于在第2方向D2上相邻的第2绝缘部22彼此之间。多个第1部分1a和多个第1绝缘部21在第2方向D2上交替地设置。多个第2部分1b和多个第2绝缘部22在第2方向D2上交替地设置。

[0034] 图3是将图2的FP电极12附近放大后的截面图。

[0035] 如图3所示，第2绝缘部22的第1方向D1上的长度L1比n<sup>-</sup>型漂移区域1与FP电极12之间的第1绝缘部21的厚度T1长。此外，第2绝缘部22的第2方向D2上的长度L2比厚度T1的2倍短。长度L2在第1方向D1上变化的情况下，将在第2方向D2上最长的部分的长度作为长度L2来使用。

[0036] 第1绝缘部21与第2绝缘部22的边界例如可以如以下这样决定。

[0037] 第1绝缘部21具有一对侧面S1以及一对弯曲面S2。第2绝缘部22具有一对侧面S3。侧面S1沿着第1方向D1。即，侧面S1相对于第1方向D1的倾斜比侧面S1相对于第2方向D2的倾斜小。弯曲面S2的上端沿着第1方向D1，与侧面S1相连。弯曲面S2的下端沿着第2方向D2，与侧面S3相连。即，弯曲面S2相对于第1方向D1的倾斜越朝向下方越大。另一方面，侧面S3的上端相对于第1方向D1的倾斜比侧面S3的上端相对于第2方向D2的倾斜小。因而，在弯曲面S2与侧面S3之间，存在相对于第1方向D1的倾斜比相对于第2方向D2的倾斜小的点P。在一对弯曲面S2与一对侧面S3之间，分别求出点P。可以将把这些点P连结而得到的面定义为第1绝缘部21与第2绝缘部22的边界。第2绝缘部22的长度L1能够以该边界为基准求出。

[0038] 如果第2绝缘部22的长度L2比厚度T1的2倍短，则长度L2比第1绝缘部21的第1方向

D1上的长度L3短。因此,关于n<sup>-</sup>型漂移区域1,如图2所示,第2部分1b的第2方向D2上的长度L4比第1部分1a的第2方向D2上的长度L5长。在长度L4以及L5各自在第1方向D1上变化的情况下,将在第2方向D2上最长的部分的长度分别作为长度L4以及L5来使用。

[0039] 对半导体装置100的动作进行说明。

[0040] 在相对于源极电极13而言向漏极电极11施加了正电压的状态下,向栅极电极10施加阈值以上的电压。由此,在p型基底区域2形成沟道(反型层),半导体装置100成为导通状态。电子通过沟道从源极电极13流向漏极电极11。然后,如果施加到栅极电极10的电压变得比阈值低,则p型基底区域2中的沟道消失,半导体装置100成为截止状态。

[0041] 如果半导体装置100切换为截止状态,则相对于源极电极13而言向漏极电极11施加的正电压增大。通过正电压的增大,耗尽层从第1绝缘部21与n<sup>-</sup>型漂移区域1的界面朝向n<sup>-</sup>型漂移区域1扩展。通过该耗尽层的扩展,能够提高半导体装置100的耐压。或者,能够在维持半导体装置100的耐压的状态下,提高n<sup>-</sup>型漂移区域1中的n型杂质浓度,减小半导体装置100的导通电阻。

[0042] 对半导体装置100的各结构要素的材料的一例进行说明。

[0043] n<sup>-</sup>型漂移区域1、p型基底区域2、n<sup>+</sup>型源极区域3、n<sup>+</sup>型漏极区域4以及p<sup>+</sup>型接触区域5包含硅、碳化硅、氮化镓或砷化镓作为半导体材料。在作为半导体材料而使用硅的情况下,作为n型杂质可以使用砷、磷或锑。作为p型杂质,可以使用硼。

[0044] 栅极电极10以及FP电极12包含多晶硅等导电材料。导电材料中也可以添加有杂质。

[0045] 第1绝缘部21以及第2绝缘部22包含氧化硅等氧化物系的绝缘材料。

[0046] 漏极电极11、源极电极13以及栅极焊盘14包含铝或铜等金属。

[0047] 连接部31包含钨等金属。

[0048] 对第1实施方式的半导体装置100的制造方法的一例进行说明。

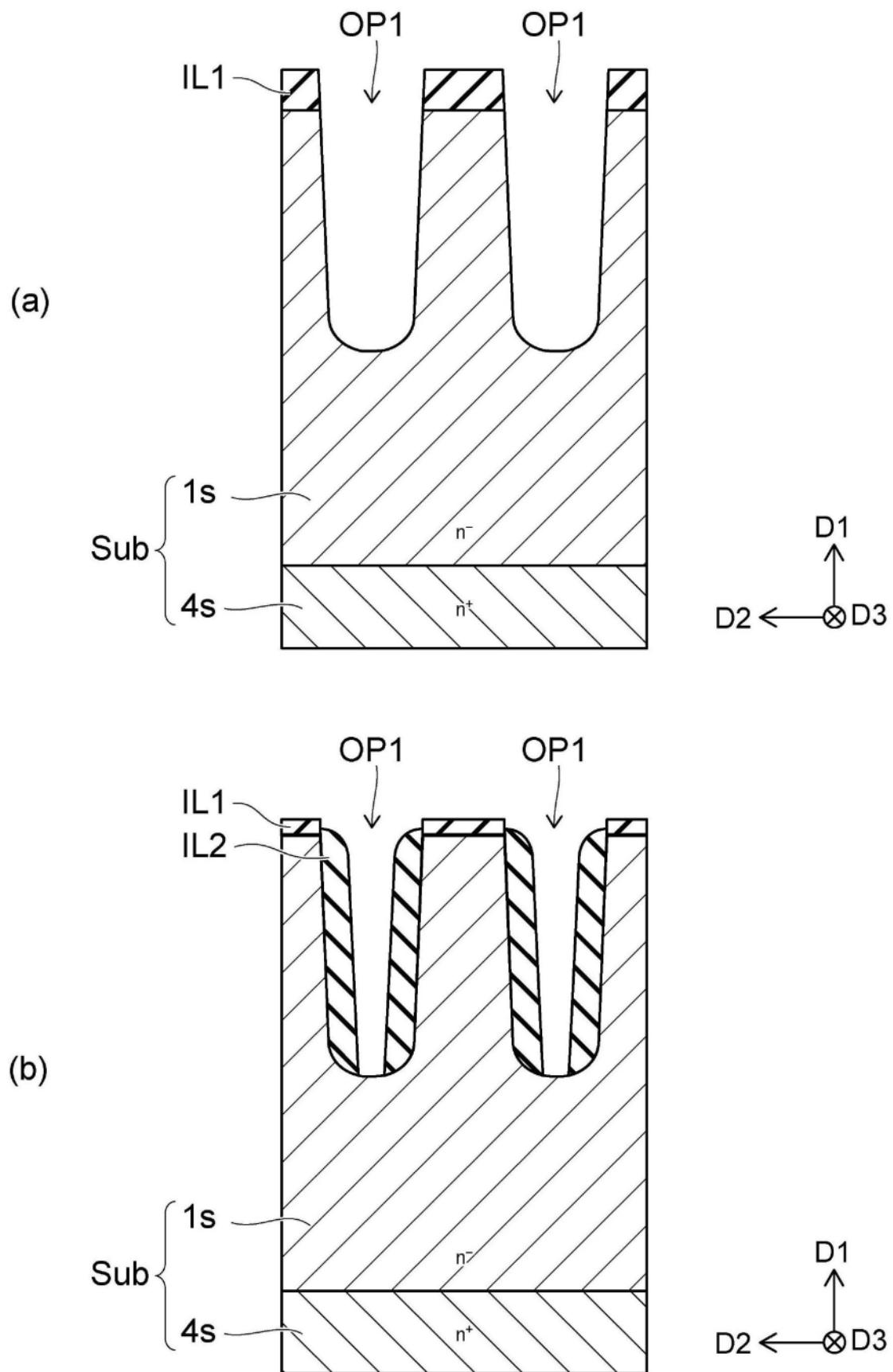

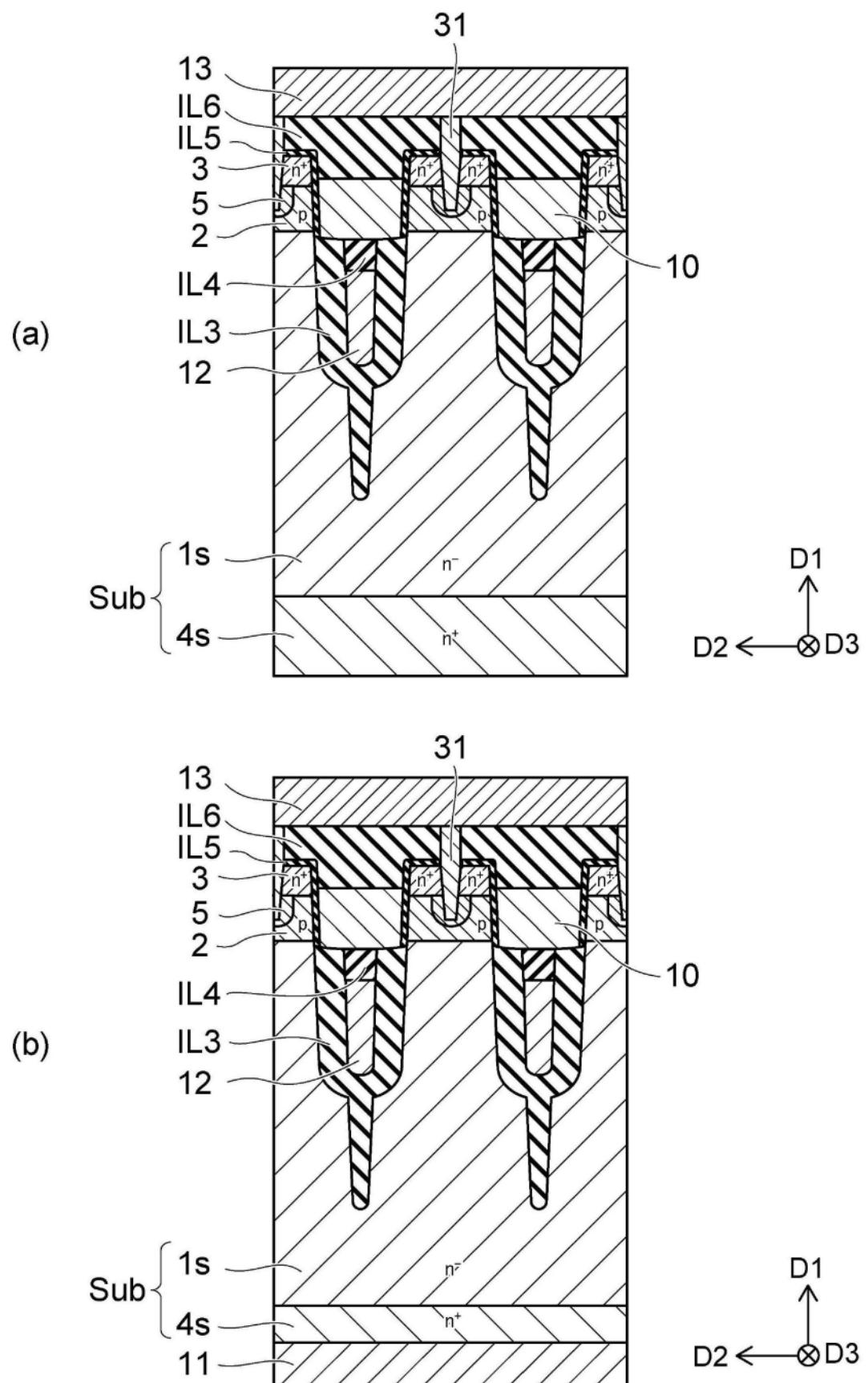

[0049] 图4~图8是表示第1实施方式的半导体装置的制造工序的工序截面图。图4~图8表示与第1方向D1以及第2方向D2平行的截面中的制造工序。

[0050] 准备具有n<sup>+</sup>型半导体层4s和n<sup>-</sup>型半导体层1s的半导体基板Sub。在n<sup>-</sup>型半导体层1s之上形成绝缘层IL1,通过光刻法将绝缘层IL1进行构图。使用绝缘层IL1作为掩模,除去n<sup>-</sup>型半导体层1s的一部分,如图4(a)所示形成开口OP1。开口OP1在第2方向D2上被形成多个,各开口OP1沿第3方向D3延伸。

[0051] 通过热氧化,沿着多个开口OP1的内面分别形成多个绝缘层IL2。通过反应性离子蚀刻(RIE)等的各向异性蚀刻,留下设置于开口OP1的侧面的绝缘层IL2,并且除去设置于开口OP1的底部的绝缘层IL2。由此,如图4(b)所示,n<sup>-</sup>型半导体层1s在开口OP1的底部露出。

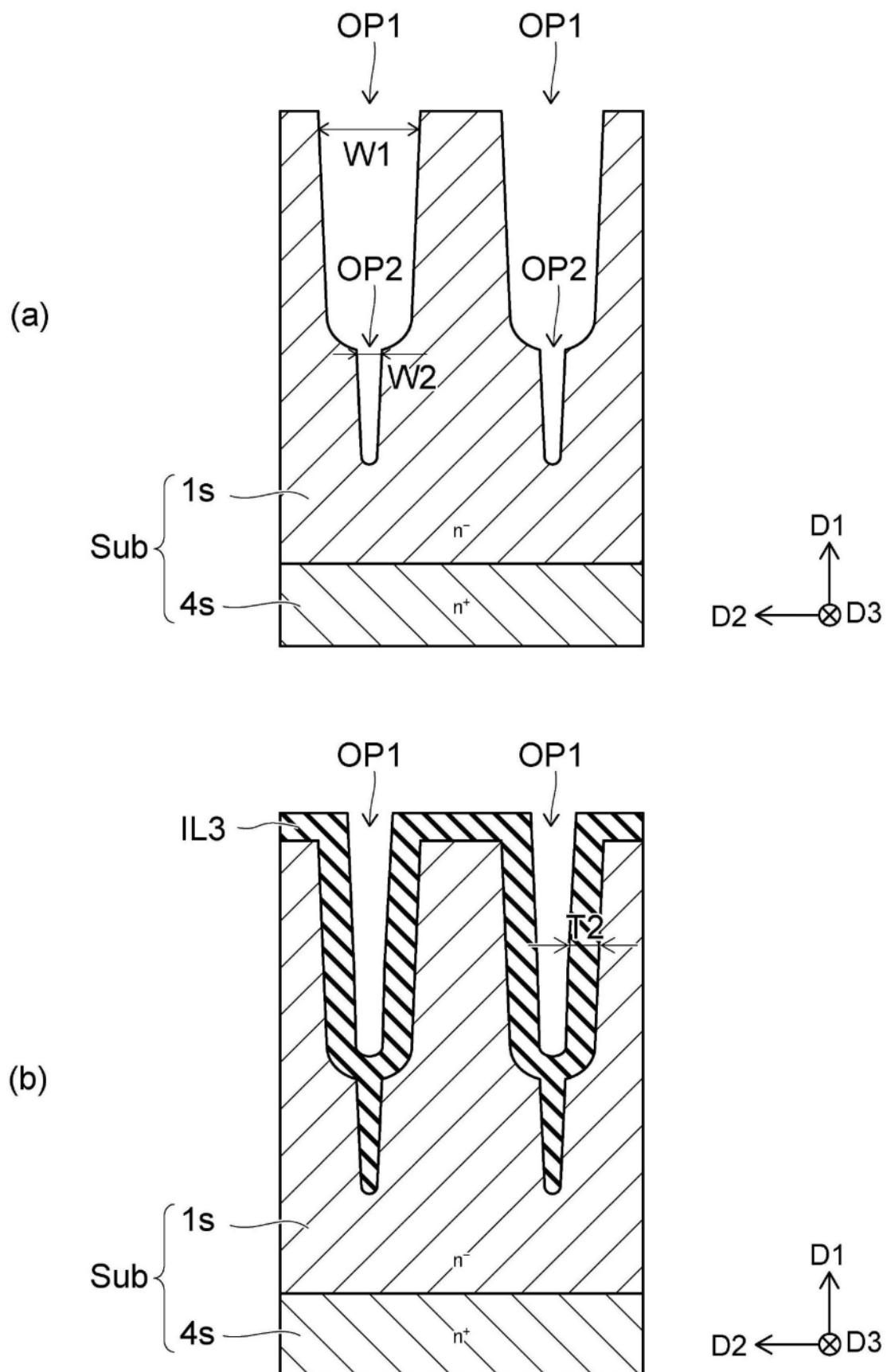

[0052] 使用绝缘层IL1以及IL2作为掩模,除去在开口OP1的底部露出的n<sup>-</sup>型半导体层1s。由此,如图5(a)所示,在开口OP1的底部形成开口OP2。开口OP2的宽度(第2方向D2上的尺寸)W2比开口OP1的宽度W1窄。此外,开口OP2的宽度W2比之后形成的绝缘层IL3的厚度T2的2倍短。

[0053] 除去绝缘层IL1以及IL2。由此,被绝缘层IL1以及IL2覆盖的n<sup>-</sup>型半导体层1s的表面露出。通过热氧化,如图5(b)所示,沿着n<sup>-</sup>型半导体层1s的表面形成绝缘层IL3。绝缘层IL3可以通过化学气相淀积(CVD)形成。如上所述,开口OP2的宽度W2比绝缘层IL3的厚度T2

的2倍短。因此,通过从开口OP2的两侧面沿着第2方向D2形成的绝缘层IL3,开口OP2被填埋。绝缘层IL3的厚度T2对应于图3所示的第1绝缘部21的厚度T1,实质上与厚度T1相同。

[0054] 在绝缘层IL3之上形成填埋多个开口OP1的导电层。例如,导电层包含添加有杂质的多晶硅。使导电层的上表面后退,在各个开口OP1的内侧形成FP电极12。如图6(a)所示,在绝缘层IL3之上形成将多个FP电极12覆盖的绝缘层IL4。

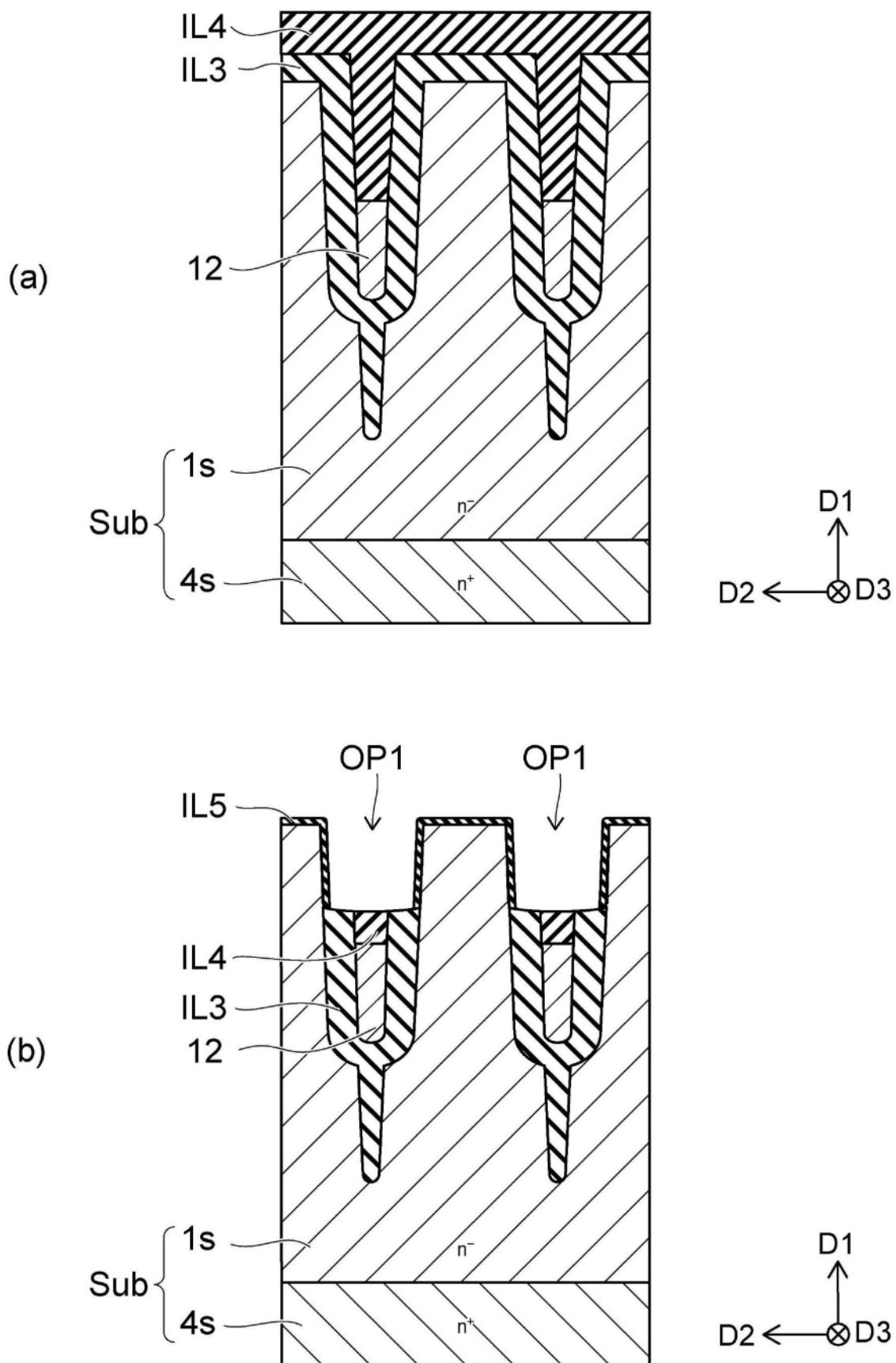

[0055] 使绝缘层IL3以及IL4的上表面后退。由此,n<sup>-</sup>型半导体层1s的表面的一部分以及p型基底区域2的表面露出。通过热氧化,如图6(b)所示,沿着露出的n<sup>-</sup>型半导体层1s以及p型基底区域2的表面形成绝缘层IL5。

[0056] 在绝缘层IL5之上形成填埋多个开口OP1的导电层。例如,导电层包含添加有杂质的多晶硅。使导电层的上表面后退,在各个开口OP1的内侧形成栅极电极10。在n<sup>-</sup>型半导体层1s的表面将p型杂质进行离子注入,形成p型基底区域2。此时,栅极电极10的下端位于比n<sup>-</sup>型半导体层1s与p型基底区域2的界面靠下方的位置。在p型基底区域2的表面将n型杂质进行离子注入,如图7(a)所示,形成n<sup>+</sup>型源极区域3。

[0057] 在绝缘层IL5之上形成覆盖多个栅极电极10的绝缘层IL6。将绝缘层IL6、绝缘层IL5、n<sup>+</sup>型源极区域3以及p型基底区域2各自的一部分除去,形成到达p型基底区域2的开口OP3。通过多个开口OP3,向多个p型基底区域2将p型杂质分别进行离子注入,如图7(b)所示,形成多个p<sup>+</sup>型接触区域5。

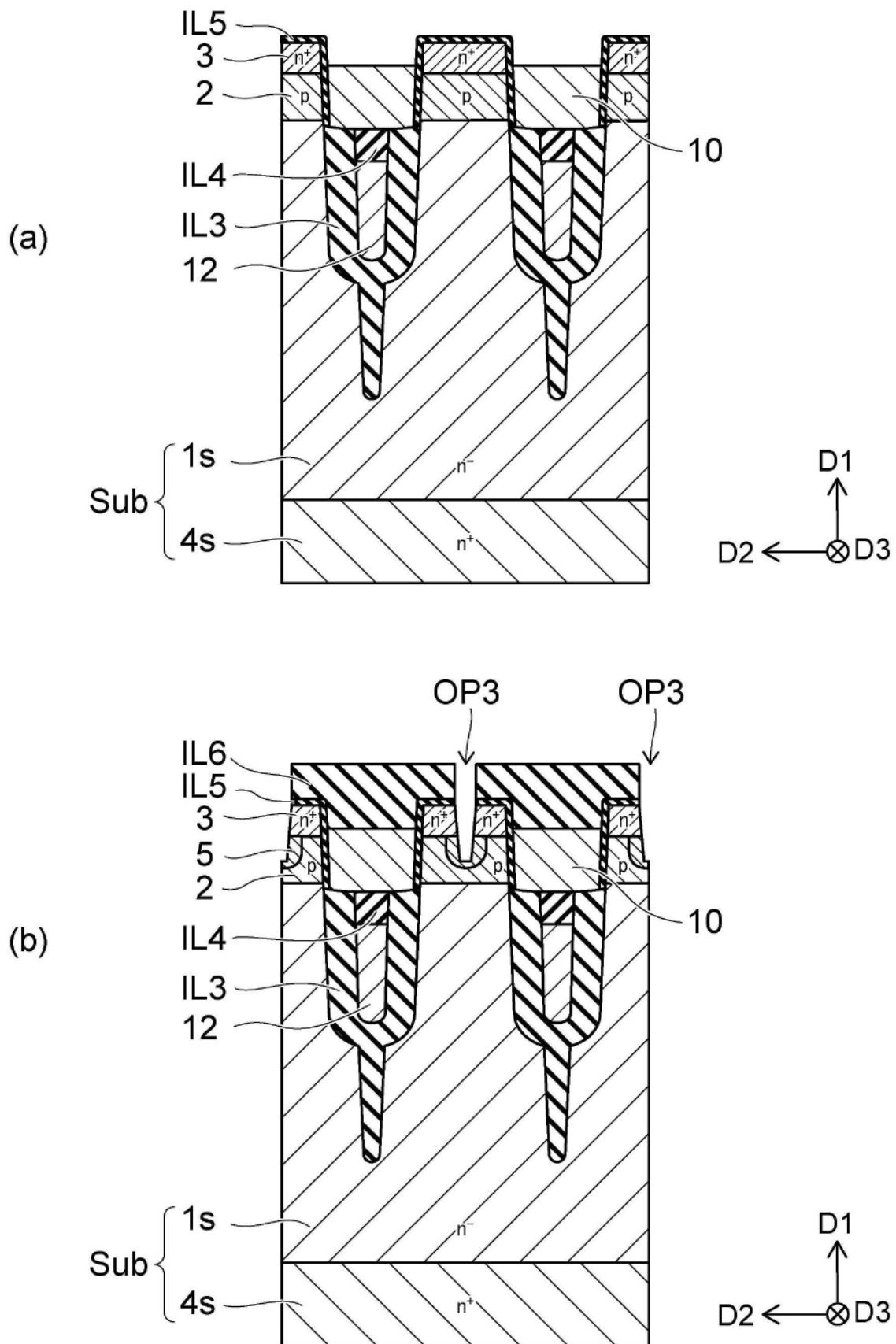

[0058] 在绝缘层IL6之上形成包含钨的金属层,填埋多个开口OP3。通过使该金属层的上表面后退,形成与多个n<sup>+</sup>型源极区域3以及多个p<sup>+</sup>型接触区域5分别连接的多个连接部31。在绝缘层IL6以及多个连接部31之上形成包含铝的金属层。通过将该金属层进行构图,形成图8(a)所示的源极电极13和未图示的栅极焊盘14。

[0059] 对n<sup>+</sup>型半导体层4s的背面进行研磨,直到n<sup>+</sup>型半导体层4s成为规定的厚度。然后,如图8(b)所示,在n<sup>+</sup>型半导体层4s的背面形成漏极电极11。通过以上的工序,制造出图1~图3所示的半导体装置100。

[0060] 上述制造工序中,在各构成要素的形成中可以使用化学气相沉积(CVD)或溅射。在各构成要素的一部分的除去中可以使用湿式蚀刻、化学干式蚀刻(CDE)或反应性离子蚀刻(RIE)。在各构成要素的上表面的后退中可以使用湿式蚀刻、CDE或化学机械研磨(CMP)。

[0061] 对第1实施方式的效果进行说明。

[0062] 第1实施方式的半导体装置100在第1绝缘部21之下具有与第1绝缘部21相连的第2绝缘部22。第1绝缘部21以及第2绝缘部22如图5(a)所示通过半导体的热氧化或氧化物的CVD形成。通过这些方法形成的第1绝缘部21以及第2绝缘部22具有压缩应力。因此,在形成了第1绝缘部21以及第2绝缘部22时,通过第1绝缘部21以及第2绝缘部22的压缩应力,位于第1绝缘部21彼此之间以及第2绝缘部22彼此之间的n<sup>-</sup>型半导体层1s在第1方向D1上被施加拉伸应力。该拉伸应力在半导体装置100的制造完成后也残存。其结果,图2所示的半导体装置100中,位于第1绝缘部21彼此之间以及第2绝缘部22彼此之间的n<sup>-</sup>型漂移区域1中发生拉伸应变。

[0063] 在半导体装置100为导通状态时,载流子沿着第1方向D1流动。换言之,拉伸应变沿着载流子流动的方向发生。如果沿着载流子流动的方向发生拉伸应变,则载流子的迁移率提高。即,通过在n<sup>-</sup>型漂移区域1发生拉伸应变,能够减小半导体装置100的导通电阻。例如,

通过设置第1绝缘部21以及第2绝缘部22双方,与仅设置第1绝缘部21的情况相比,能够使n<sup>-</sup>型漂移区域1的更大的范围发生拉伸应变。

[0064] 第2绝缘部22的第1方向D1上的长度L1比n<sup>-</sup>型漂移区域1与FP电极12之间的第1绝缘部21的厚度T1长。由此,能够使在第2绝缘部22彼此之间在n<sup>-</sup>型漂移区域1中发生的应变变大。例如,如果长度L1比厚度T1短,则在远离第2绝缘部22的区域中,不发生充分的拉伸应变,载流子的迁移率的提高小。

[0065] 此外,如果设有第2绝缘部22,则在比第1绝缘部21靠下方的区域中,电流流动的路径变窄。半导体装置100中,第2绝缘部22的第2方向D2上的长度L2比厚度T1的2倍短。因此,能够使n<sup>-</sup>型漂移区域1的第2部分1b的长度L4比n<sup>-</sup>型漂移区域1的第1部分1a的长度L5长。由此,在设有第2绝缘部22的情况下也能够抑制第2绝缘部22彼此之间的电流路径的宽度变窄。

[0066] 即,根据上述的长度L1、长度L2、以及厚度T1的关系,能够使基于由第2绝缘部22引起的拉伸应变的导通电阻减小的效果比通过设置第2绝缘部22而带来的导通电阻增加的效果大。因而,与仅设有第1绝缘部21的情况相比,能够减小半导体装置100的导通电阻。

[0067] 进而,如果长度L2比厚度T1的2倍短,则如图5(b)所示,能够在形成第1绝缘部21的一部分的同时,形成第2绝缘部22。由此,能够更容易地制造半导体装置100。

[0068] 也可以以第2绝缘部22的下端到达n<sup>+</sup>型漏极区域4的方式设置第2绝缘部22。优选的是,第2绝缘部22的下端如图2所示,在第1方向D1上与n<sup>+</sup>型漏极区域4分离。如果第2绝缘部22与n<sup>+</sup>型漏极区域4分离,则在比第2绝缘部22靠下方处,电流路径的宽度变宽。此外,第2绝缘部22的形成变得容易,能够提高半导体装置100的成品率。

[0069] 以下是优选的尺寸比的一例。

[0070] FP电极12的第1方向D1上的长度L1相对于长度L6(图3所示)的比是0.5以上2.0以下。FP电极12的第2方向D2上的长度L2相对于长度L7的比是0.5以上2.0以下。漏极电极11与第2绝缘部22之间的第1方向D1上的距离D12相对于漏极电极11与p型基底区域2之间的第1方向D1上的距离D11(图2所示)的比是0.1以上0.5以下。

[0071] 关于长度L1相对于长度L6的比,如果比过小,则发生的应变变小,导通电阻减小的效果变小。另一方面,如果比过大,则电流路径的宽度变窄,电流路径变得窄小。其结果,导通电阻增加。

[0072] 关于长度L2相对于长度L7的比,如果比过小,则发生的应变变小,导通电阻减小的效果变小。另一方面,如果比过大,则电流路径变得窄小,导通电阻增加。

[0073] 关于距离D12相对于距离D11的比,如果比过小,则电流路径变得窄小,导通电阻增加。另一方面,如果比过大,则发生的应变变小,导通电阻的减小效果变小。

[0074] 通过使长度L1相对于长度L6的比、长度L2相对于长度L7的比、以及距离D12相对于距离D11的比中的至少某一个处于上述范围,能够使由拉伸应变引起的导通电阻减小相对于由电流路径的窄小化引起的导通电阻增加的比例更大。由此,能够进一步减小半导体装置100的导通电阻。此外,通过三个比全部处于上述范围内,能够进一步减小导通电阻。

[0075] (第1变形例)

[0076] 图9是表示第1实施方式的第1变形例的半导体装置的一部分的立体截面图。

[0077] 图9所示的半导体装置110中,在多个第2绝缘部22的至少一部分设有空隙V。空隙V

是存在于第2绝缘部22的内部的空洞。例如,空隙V在第1方向D1上的尺寸比空隙V在第2方向D2上的尺寸长。空隙V也可以沿着第1方向D1设置为线状。

[0078] 如果设有空隙V,则从第2绝缘部22作用到n<sup>-</sup>型漂移区域1的应力得到缓和。例如,空隙V越大,则应力越得到缓和。通过将空隙V设置于第2绝缘部22,能够调整作用到n<sup>-</sup>型漂移区域1的应力。

[0079] 为了形成空隙V,例如在图5(a)所示的工序中通过CVD形成绝缘层IL3。此时,通过将成膜条件设为接近于供给限速的条件,能够使开口OP2的上端附近的氧化物的堆积速度比开口OP2的中部的氧化物的堆积速度更大。其结果,在材料在开口OP2的内部没有完全堆积的状态下,开口OP2的上端被封闭。由此,能够在设置在开口OP2内的绝缘层IL3的内部形成空隙V。

[0080] 但是,为了通过更小的第2绝缘部22使得在n<sup>-</sup>型漂移区域1发生更大的应变,优选的是在第2绝缘部22没有空隙V。为了抑制空隙V的形成,优选的是开口OP2的侧面相对于第1方向D1倾斜。通过使开口OP2的侧面倾斜,能够抑制在材料在开口OP2的内部没有完全堆积的状态下开口OP2的上端封闭。在开口OP2的侧面相对于第1方向D1倾斜的情况下,第2绝缘部22的第2方向D2上的长度越朝向下方越短。

[0081] (第2变形例)

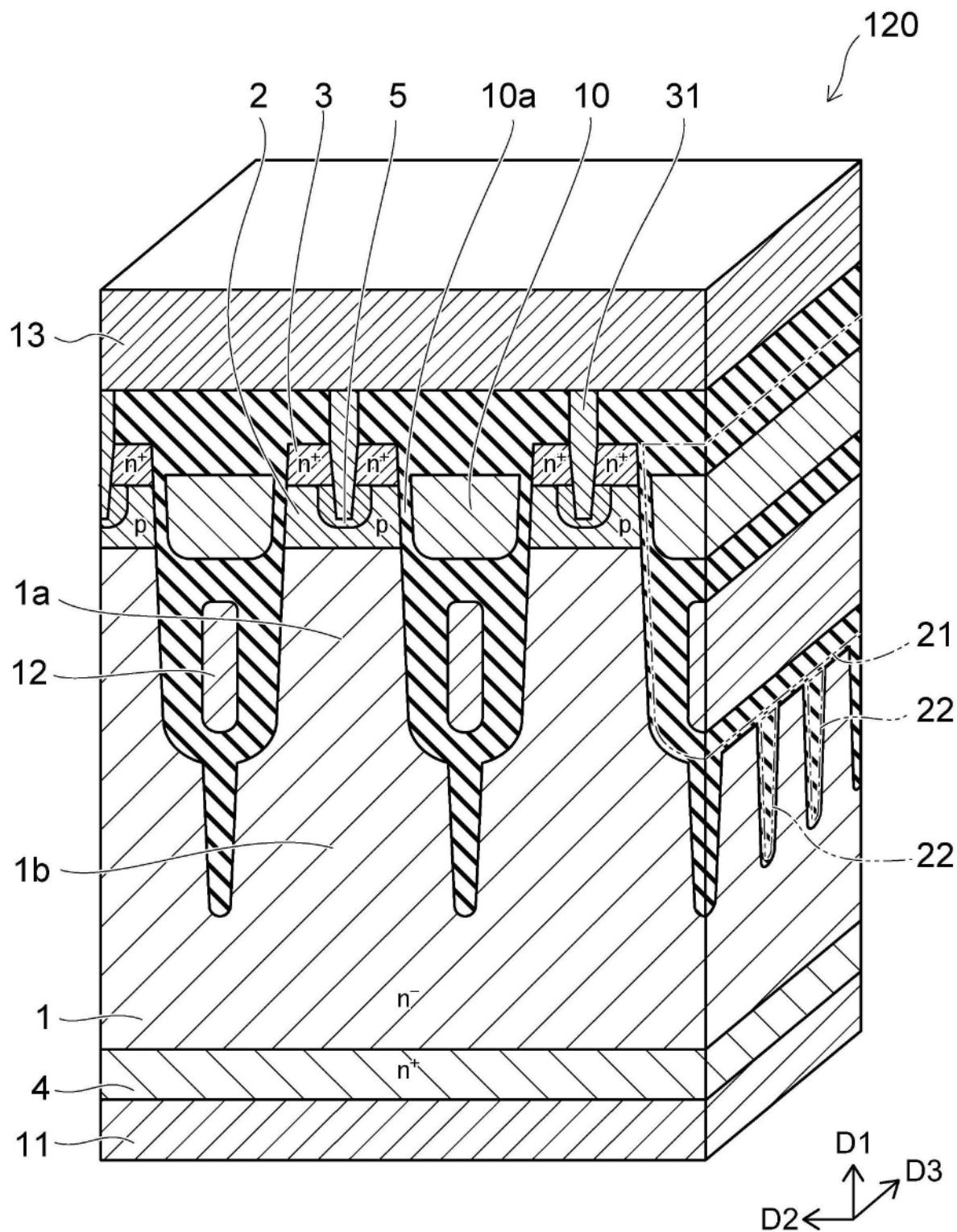

[0082] 图10是表示第1实施方式的第2变形例的半导体装置的一部分的立体截面图。

[0083] 图10所示的半导体装置120中,在一个第1绝缘部21之下设有多个第2绝缘部22。多个第2绝缘部22在第3方向D3上相互分离。因此,在半导体装置100为导通状态时,载流子能够在第3方向D3上相邻的第2绝缘部22彼此之间移动。

[0084] 根据第2变形例的半导体装置120,与半导体装置100相比,能够使第1绝缘部21的下方的电流路径的宽度更宽。因此,根据第2变形例,能够进一步减小导通电阻。

[0085] (第2实施方式)

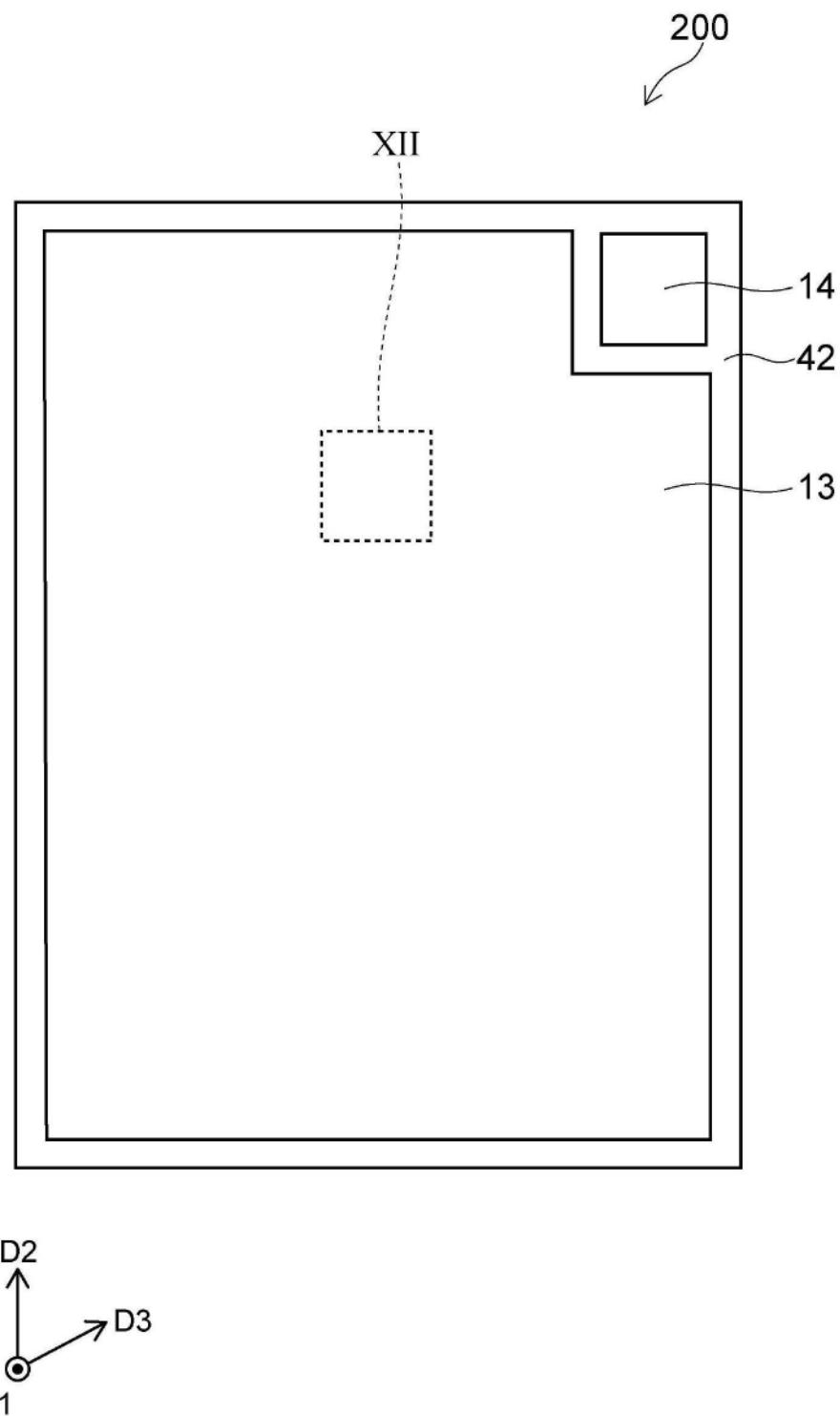

[0086] 图11是表示第2实施方式的半导体装置的俯视图。

[0087] 图12是表示图11的部分XII的俯视图。图12中省略了源极电极13、绝缘层41、以及绝缘层42。

[0088] 图13是图12的XII-XII截面图。图14是图12的XIV-XIV截面图。图15是图12的XV-XV截面图。

[0089] 第2实施方式的半导体装置200与半导体装置100相比,还具有栅极布线层15、连接部32、连接部33、绝缘层41以及绝缘层42。

[0090] 如图12~图15所示,半导体装置200中,栅极电极10、FP电极12、第1绝缘部21以及第2绝缘部22在第2方向D2以及第3方向D3上被设置多个。如图12所示,从第1方向D1观察时的栅极电极10的形状为环状。FP电极12位于栅极电极10的内侧。p型基底区域2、n<sup>+</sup>型源极区域3以及p<sup>+</sup>型接触区域5在第2方向D2以及第3方向D3上位于各第1绝缘部21的周围。

[0091] 如图13所示,栅极布线层15隔着绝缘层41而设置在栅极电极10之上。连接部32设置在栅极电极10与栅极布线层15之间,将栅极电极10与栅极布线层15电连接。源极电极13隔着绝缘层42而设置在栅极布线层15之上。连接部33设置在FP电极12与源极电极13之间,将FP电极12与源极电极13电连接。连接部31在没有设置栅极布线层15的位置处将n<sup>+</sup>型源极区域3以及p<sup>+</sup>型接触区域5与源极电极13电连接。

[0092] 如图12所示,在第3方向D3上设有多个栅极布线层15,各栅极布线层15沿第2方向D2延伸。各栅极布线层15设置在沿第2方向D2排列的栅极电极10之上,与沿第2方向D2排列的栅极电极10电连接。如图13所示,源极电极13隔着绝缘层42而设置在多个栅极布线层15之上。

[0093] 栅极焊盘14例如如图11所示设置在绝缘层42之上,与源极电极13分离。栅极布线层15和栅极焊盘14通过贯穿绝缘层42的未图示的连接部相互电连接。或者,栅极焊盘14也可以设置在绝缘层41之上。在该情况下,栅极焊盘14位于比源极电极13靠下方的位置。

[0094] 如图14所示,半导体装置200中也是第2绝缘部22的第1方向D1上的长度L1比n<sup>-</sup>型漂移区域1与FP电极12之间的第1绝缘部21的厚度T1长。第2绝缘部22的第2方向D2上的长度L2比厚度T1的2倍短。此外,如图15所示,第2绝缘部22的第3方向D3上的长度L8比厚度T1的2倍短。

[0095] n<sup>-</sup>型漂移区域1如图14以及图15所示具有第1部分1a~第4部分1d。第1部分1a位于在第2方向D2上相邻的第1绝缘部21彼此之间。第2部分1b位于在第2方向D2上相邻的第2绝缘部22彼此之间。第3部分1c位于在第3方向D3上相邻的第1绝缘部21彼此之间。第4部分1d位于在第3方向D3上相邻的第2绝缘部22彼此之间。

[0096] 第2部分1b的第2方向D2上的长度L4比第1部分1a的第2方向D2上的长度L5长。第4部分1d的第3方向D3上的长度L9比第3部分1c的第3方向D3上的长度L10长。

[0097] 根据第2实施方式,栅极电极10在第2方向D2以及第3方向D3上被设置多个。根据该构造,在半导体装置200为导通状态时,在各栅极电极10的周围形成沟道。因此,与半导体装置100相比,能够使每单位面积的沟道的面积增大,并且能够进一步减小导通电阻。

[0098] 进而,与第1实施方式同样,通过在第1绝缘部21之下设置第2绝缘部22,能够使得在第2绝缘部22彼此之间的n<sup>-</sup>型漂移区域1发生拉伸应变。此外,长度L1比厚度T1长。长度L2以及L8分别比厚度T1的2倍短。根据该关系,能够使基于由第2绝缘部22引起的拉伸应变的导通电阻减小的效果比通过设置第2绝缘部22而带来的导通电阻增加的效果大。因而,与仅设置第1绝缘部21的情况相比,能够减小半导体装置200的导通电阻。

[0099] 此外,如果长度L2以及L8分别比厚度T1的2倍短,则第2绝缘部22的形成变得容易,能够提高半导体装置200的成品率。

[0100] 关于以上说明的各实施方式中的、各半导体区域之间的杂质浓度的相对高低,例如能够使用SCM(扫描型静电电容显微镜)来确认。另外,各半导体区域中的载流子浓度可以视为与在各半导体区域中活性化的杂质浓度相等。因而,关于各半导体区域之间的载流子浓度的相对高低,也能够使用SCM来确认。此外,关于各半导体区域中的杂质浓度,例如能够通过SIMS(二次离子质量分析法)来测定。

[0101] 以上,例示了本发明的几个实施方式,但这些实施方式是作为例子来提示的,并没有要限定发明的范围。这些新的实施方式能够以其他多种形态实施,在不脱离发明的主旨的范围内能够进行各种省略、置换、变更等。这些实施方式及其变形例包含在发明的范围及主旨中,并且包含在权利要求书中记载的发明及其等效的范围中。此外,上述的各实施方式能够相互组合而实施。

图1

图2

图3

图4

图5

图6

图7

图8

图9

图10

图11

图12

图13

图14

图15